#### AN ABSTRACT OF THE THESIS OF

<u>Tao Jiang</u> for the degree of <u>Doctor of Philosophy</u> in <u>Electrical and Computer Engineering</u> presented on <u>June 10, 2013.</u>

Title: <u>Design Techniques for Low-Power Multi-GS/s Analog-to-Digital Converters.</u>

| Abstract approved: |  |

|--------------------|--|

|                    |  |

|                    |  |

|                    |  |

#### Patrick Y. Chiang

Ultra-high-speed (>10GS/s), medium-resolution (5~6bit), low-power (<50mW) analog-to-digital converter can find it application in the areas of digital oscilloscopes and next-generation serial link receivers. There are several challenges to enable a successful design, however. First, the time-interleaved architecture is required in order to achieve over 10GS/s sampling rate, with the trade-off of the number of the channels and the sampling rate in each channel. Phase misalignment and channel mismatch must be considered too. Second, timing accuracy, especially dynamic jitter of sampling clock becomes a major concern at ultra-high frequency, and certain techniques must be taken to address it. Finally, to achieve low power consumption, Flash architecture is not suitable to serve as the sub-ADC, and a low-power sub-ADC that can work at relatively high speed need to be designed.

A single channel, asynchronous successive approximation (SA) ADC with improved feedback delay has been fabricated in 40nm CMOS. Compared with a

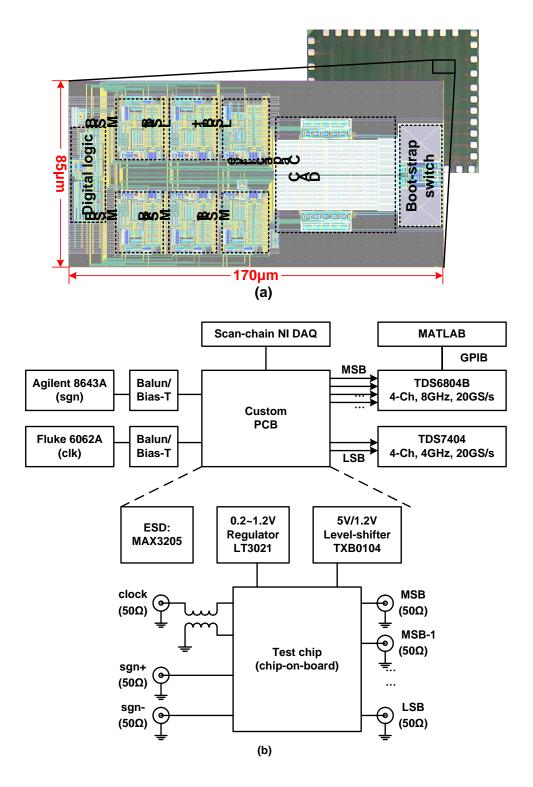

conventional SA structure that employs a single quantizer controlled by a digital feedback logic loop, the proposed SA-ADC employs multiple quantizers for each conversion bit, clocked by an asynchronous ripple clock that is generated after each quantization. Hence, the sampling rate of the 6-bit ADC is limited only by the six delays of the Capacitive-DAC settling and each comparator's quantization delay, as the digital logic delay is eliminated. Measurement results of the 40nm-CMOS SA-ADC achieves peak SNDR of 32.9dB at 1GS/s and 30.5dB at 1.25GS/s, consuming 5.28mW and 6.08mW respectively, leading to FoM of 148fJ/conversion-step and 178fJ/conversion-step, in a core area less than 170μm by 85μm.

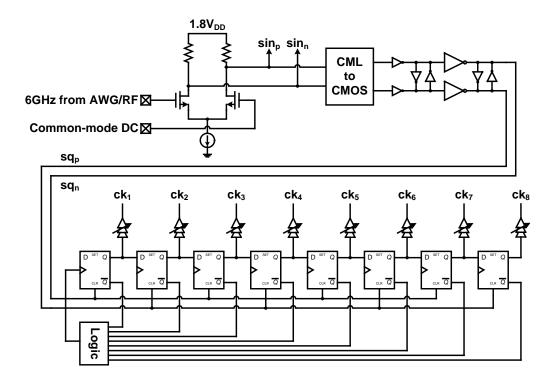

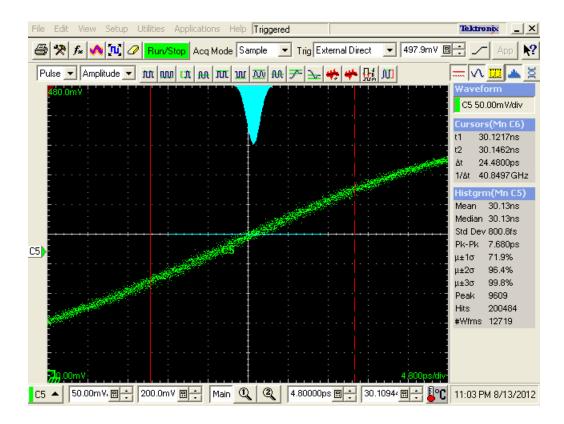

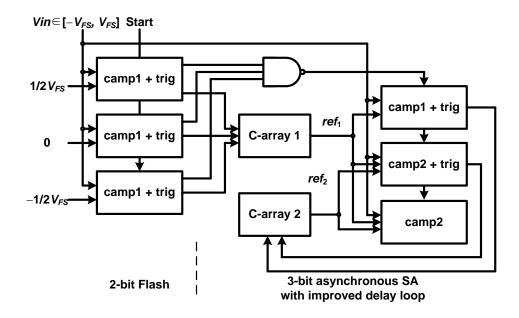

Based on the previous work of sub-ADC, a 12-GS/s 5-b 50-mW ADC is designed in 40nm CMOS with 8 time-interleaved channels of Flash-SA hybrid structure each running at 1.5GS/s. A modified bootstrapped switch is used in the track-and-hold circuit, introducing a global clock signal to synchronize the sampling instants of each individual channel, therefore improve the phase alignment and reduce distortion. The global clock is provided by a CML buffer which is injected by off-chip low-noise sine-wave signal, so that the RMS dynamic jitter is low for better ENOB performance. Measurement results show that the 12GS/s ADC can achieve a SNDR of 25.8dB with the input signal frequency around DC and 22.8dB around 2GHz, consuming 32.1mW, leading to FoM of 237.3fJ/conversion-step, in a core area less than 800μm by 500μm.

©Copyright by Tao Jiang June 10, 2013 All Rights Reserved

#### Design Techniques for Low-Power Multi-GS/s Analog-to-Digital Converters

by Tao Jiang

#### A THESIS

submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Presented June 10, 2013 Commencement June 2013

| <u>Doctor of Philosophy</u> thesis of <u>Tao Jiang</u> presented on <u>June 10, 2013</u>                                                                                                      |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                                                                                                                                                                                               |  |  |  |  |

|                                                                                                                                                                                               |  |  |  |  |

| APPROVED:                                                                                                                                                                                     |  |  |  |  |

|                                                                                                                                                                                               |  |  |  |  |

| Major Professor, representing Electrical and Computer Engineering                                                                                                                             |  |  |  |  |

|                                                                                                                                                                                               |  |  |  |  |

|                                                                                                                                                                                               |  |  |  |  |

| Director of the School of Electrical Engineering and Computer Science                                                                                                                         |  |  |  |  |

|                                                                                                                                                                                               |  |  |  |  |

|                                                                                                                                                                                               |  |  |  |  |

|                                                                                                                                                                                               |  |  |  |  |

| Dean of the Graduate School                                                                                                                                                                   |  |  |  |  |

|                                                                                                                                                                                               |  |  |  |  |

|                                                                                                                                                                                               |  |  |  |  |

|                                                                                                                                                                                               |  |  |  |  |

|                                                                                                                                                                                               |  |  |  |  |

|                                                                                                                                                                                               |  |  |  |  |

| I understand that my thesis will become part of the permanent collection of Oregon State University libraries. My signature below authorizes release of my thesis to any reader upon request. |  |  |  |  |

|                                                                                                                                                                                               |  |  |  |  |

| Tao Jiang, Author                                                                                                                                                                             |  |  |  |  |

#### **ACKNOWLEDGEMENTS**

It is hard to describe my feeling right now, when finishing the dissertation body and starting this acknowledgement part. Six years in pursuing the degree, which is almost one fifth of my current life, is not a short period of time. I value all the experience I have been through, and hope it can make me a qualified Doctor of Philosophy.

From the bottom of my heart, I want to express the most sincere gratitude of mine to the following parties.

First and the most important, I am truly grateful to Professor Patrick Yin Chiang, my major advisor. Without his insightful guidance, continuous support and inspiring encouragement, I would have never accomplished this Ph.D. work. I will not forget how he censured me for my underperformance in the first tape out, but way too much more I will never forget how supportive and tolerant he was when I failed one chip, then failed a second, before I finally succeeded in the single-channel ADC chip. He can always propose valuable suggestion whenever I need help, out of his perception and quick thinking. I admire him for his being motivated, disciplined, organized and energetic. Learning such merits from him for years, I dare not say I am even close. It is my real fortune to have him throughout my study and research these years.

I am thankful to Professor Garbor Temes, Professor Huaping Liu, and Professor Albrecht Jander, for serving on my doctoral committee. I am indebted to Professor Abi T. Farsoni for being the graduate council representative. It is an honor to have

you accompanying me in my Ph.D. student life, and all your helpful advice is much appreciated.

I also want to thank Professor Andrea Weisshaar, Professor Albrecht Jander and Professor Pallavi Dhagat, and Radu Fetche and Jeff Means of Rohde & Schwarz, for their generous donation of measurement equipment.

I want to specially thank Matthew Brown, the AMS lab manager of the school of EECS. Because I do not have previous experience in testing such high-speed ADCs, I spent a lot of time in the AMS lab for measurement. Matt was always helpful, trying his best to ensure the equipment's availability and condition.

I want to express my sincere thankfulness to the LSI corporation, for providing me such an opportunity to use the advanced 40nm CMOS technology for my ADC design, and sponsoring my projects for years. It was a wonderful experience of mine being an intern with their HyperPHY team in 2008. Special thank belongs to the team members including but not limited to: Freeman Zhong, Charlie Zhong, Wing Liu, Shaolei Quan, Cathy Liu, Gary Hom, Eric Zhang, Lijun Li, Dong Jen, Hairong Gao, as well as Rajani Rao, Venkatrao Sagar, Aradhana Deepak, Pritesh Pawaskar, and Steve Howard.

I also enjoyed the life as an intern with Koolchip, a start-up company expertizing in the SerDes area, from 2012 to 2013. With them I had the opportunity to try the idea of the 2-bit/step asynchronous SA with improved feedback loop in the very advanced 28nm CMOS technology. I am grateful to Shaolei Quan, Prasad Chalasani, Satya Rao, Wanli Chang, Hongtao Mu, Jay Chen, William Loh, and Sangeeta Chaugule, for everything they offered.

I have been much honored to work in a research group with so many extraordinary students. I will always remember all the days and nights spend with Jingguang Wang, Kangmin Hu, Changhui Hu, Jacob Postman, Joe Crop, Rui Bai, Robert Pawlwski, Jiao Cheng, Lingli Xia, Nariman Moezzi, Chao Ma, Karthik Jayaraman, Divya Kesharwani, Sirikarn Woracheewan, Ben Goska, Eric Donkoh, Ryan Albright and Neil Glover. Also, I wish to thank many exceptional students from other groups including but not limited to: Weilun Shen, Wenhuan Yu, Yan Wang, Xiaoran Gao, Chia-Hung Chen, Ming-Hung Kuo, Jiaming Lin, Jinzhou Cao, Tao Wang, Tao Tong, Xin Meng, and Wei Li in Professor Temes's group; Wenjing Yin, Jeff Pai, Rajesh Inti, Amr Elshazly, Bangda Yang and Guanghua Shu in Professor Hanumolu's group; Yue Hu in Professor Moon's group; Jinjin He, Ruiqing Ye, Stephen Redfield, Wei Liu, Zhenqiang Su and Tianzhu Qiao in Professor Liu's group; Ronghua Ni and Chao Shi in Professor Fiez's group; Na An and Han Song in Professor Jander's group; Vikas Shilimkar and Steven Gaskill in Professor Weisshaar's group; and Chen Cao and so on, for all the help and making my life fantastic in this quiet small town.

My research has also been sponsored by Intel, CDADIC, AFRL, SRC and DOE.

Thanks to them for funding as well as MOSIS for chip fabrication.

Last but not least, I wish to extend my sincere gratitude to my entire family: my wife Rong, my parents and parents-in-law, my cousin Yao, who firmly stand behind and support my graduate work.

### TABLE OF CONTENTS

|    |        |          |                                                 | <u>Pag</u> | <u>ge</u> |

|----|--------|----------|-------------------------------------------------|------------|-----------|

| 1. | In     | troduct  | ion                                             |            | 1         |

|    | 1.1.   | Motiv    | ation                                           |            | 1         |

|    | 1.2.   | Applio   | cation Background                               |            | 2         |

|    | 1.     | 2.1.     | SerDes Circuits                                 |            | 2         |

|    | 1.     | 2.2.     | Digital Storage Oscilloscope                    |            | 7         |

|    | 1.3.   | Thesis   | s Organization                                  |            | 8         |

| 2. | Tı     | radition | al Approaches                                   |            | 10        |

|    | 2.1.   | State-   | of-the-Art >10GS/s ADCs                         | •••••      | 10        |

|    | 2.2.   | High-    | Speed Sub-channel ADC                           |            | 13        |

|    | 2.     | 2.1.     | Flash Architecture                              | •••••      | 13        |

|    | 2.     | 2.2.     | SA Architecture                                 | •••••      | 15        |

|    | 2.     | 2.3.     | Binary-Search Architecture                      |            | 24        |

|    | 2.3.   | Time-    | Interleaved Track-and-Hold Circuit              | •••••      | 26        |

|    | 2.     | 3.1.     | Overview and Quantitative Analysis              | •••••      | 26        |

|    | 2.     | 3.2.     | Global Architecture                             |            | 30        |

|    | 2.     | 3.3.     | Distributed Architecture                        |            | 32        |

| 3. | A      | Singl    | e-Channel Asynchronous Successive-Approximation | ADC        | with      |

| In | nprove | ed Feed  | back Loop                                       |            | 34        |

|    | 3.1.   | Propo    | sed Architecture                                |            | 34        |

|    | 3.2.   | Circui   | t Implementation                                |            | 38        |

|    | 3.     | 2.1.     | Capacitive DAC                                  |            | 38        |

# TABLE OF CONTENTS (Continued)

|         |          |                                                                               | <u>Page</u> |

|---------|----------|-------------------------------------------------------------------------------|-------------|

| 3       | .2.2.    | Bootstrapped Switch                                                           | 40          |

| 3       | .2.3.    | Comparator with Offset Cancellation                                           | 41          |

| 3       | .2.4.    | Digital Logic                                                                 | 44          |

| 3.3.    | Metas    | stability Detection                                                           | 46          |

| 3.4.    | Measi    | urement Results                                                               | 52          |

| 3.5.    | Sumn     | nary                                                                          | 58          |

|         |          | e-Interleaved ADC with Distributed Track-and-Hold by a Global Sine-Wave Clock |             |

| 4.1.    | Propo    | osed Architecture                                                             | 59          |

| 4.2.    | Track    | -and-Hold Circuit                                                             | 62          |

| 4.3.    | Multi    | -Phase Clock Generation and Distribution                                      | 64          |

| 4.4.    | Sub-     | Channel ADC Design                                                            | 66          |

| 4       | .4.1.    | Flash-SA Hybrid Structure                                                     | 66          |

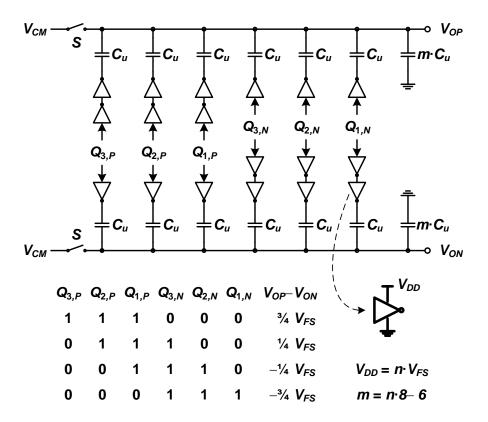

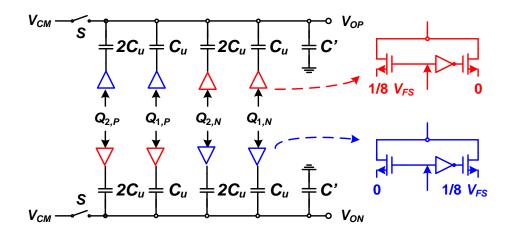

| 4       | .4.2.    | Capacitive networks                                                           | 68          |

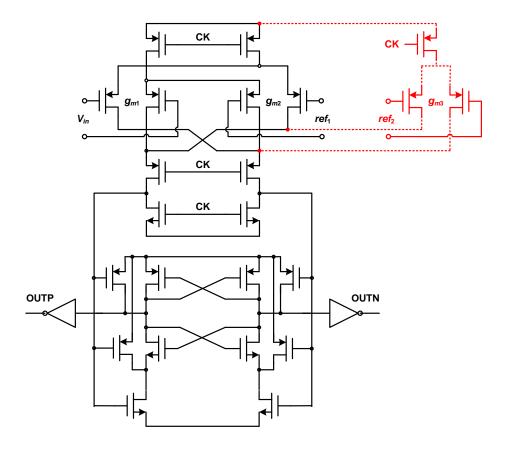

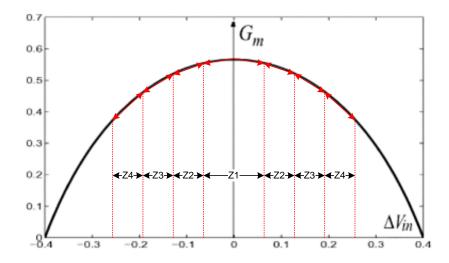

| 4       | .4.3.    | Comparator Design                                                             | 69          |

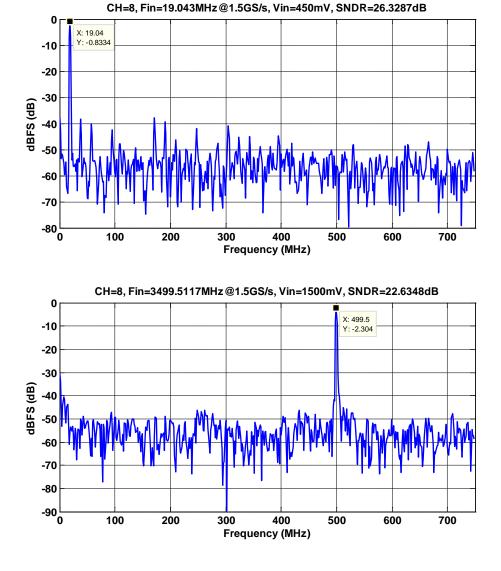

| 4.5.    | Measi    | urement Results                                                               | 72          |

| 4.6.    | Discu    | ssion                                                                         | 78          |

| 5. C    | Conclusi | on                                                                            | 81          |

| Bibliog | raphv    |                                                                               | 83          |

# TABLE OF CONTENTS (Continued)

|                                                          | <u>Page</u> |

|----------------------------------------------------------|-------------|

| Appendices                                               | 89          |

| Appendix A: Metastability in the Voltage and Time Domain | 90          |

| Appendix B: ATE (Automatic Test Equipment) Script        | 93          |

| Appendix B-1: Contact with On-Chip Scan Chain            | 93          |

| Appendix B-2: Control the Oscilloscope and Collect Data  | 94          |

### LIST OF FIGURES

| <u>Figure</u> <u>Page</u>                                                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1.1: ADC architectures and their respective fields of application. [2]                                                             |

| Figure 1.2: Intel <sup>®</sup> X58 express chipset block diagram                                                                          |

| Figure 1.3: (a) Typical SerDes architecture; (b) Transmission channel impairment 4                                                        |

| Figure 1.4: Conceptual block diagram of DFE                                                                                               |

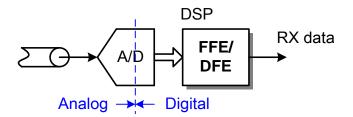

| Figure 1.5: Block diagram of ADC-based receiver                                                                                           |

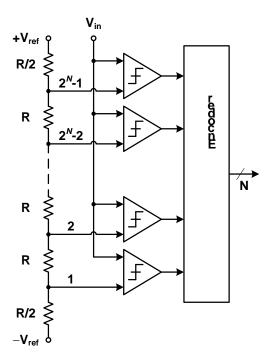

| Figure 2.1: Typical architecture of <i>N</i> -bit Flash ADC                                                                               |

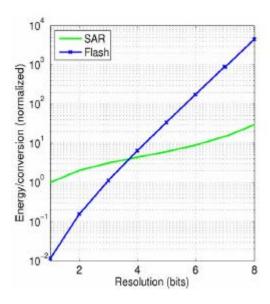

| Figure 2.2: Modeled SA and flash ADC energies vs. resolution. [29]                                                                        |

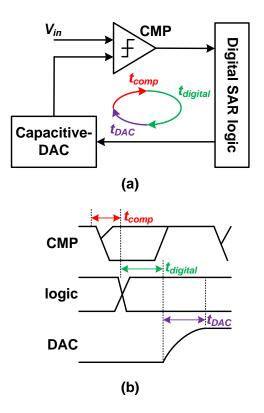

| Figure 2.3: Conventional SA architecture with critical path                                                                               |

| Figure 2.4: (a) StrongARM comparator; (b) its transient behavior. [31]                                                                    |

| Figure 2.5: Synchronous and asynchronous SA comparison                                                                                    |

| Figure 2.6: (a) Parallel connection; (b) serial connection of capacitive DAC 23                                                           |

| Figure 2.7: Block diagram of binary-search architecture                                                                                   |

| Figure 2.8: Block diagram of time-interleaved architecture                                                                                |

| Figure 2.9: Time-varying errors in TI ADC: offset, gain and timing skew                                                                   |

| Figure 2.10: ADC resolution vs. timing skew standard deviation                                                                            |

| Figure 2.11: ENOB and SNR vs. clock jitter and input frequency                                                                            |

| Figure 2.12: Global time-interleaved track-and-hold topology                                                                              |

| Figure 2.13: Distributed time-interleaved track-and-hold topology                                                                         |

| Figure 3.1: (a) Proposed architecture of the asynchronous SA ADC with improved feedback delay; (b) critical path for a one-bit conversion |

| Figure 3.2: Simulated waveforms for one single conversion period of the proposed SA ADC                                                   |

# LIST OF FIGURES (Continued)

| <u>Page</u>                                                                                                                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

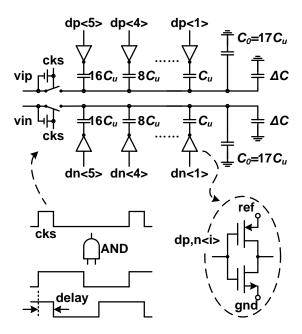

| Figure 3.3: Schematic of the capacitive DAC, and generation of the sampling clock.                                                                                   |

| Figure 3.4: Bootstrapped switch used in the capacitive DAC                                                                                                           |

| Figure 3.5: Comparator design with current steering offset cancellation circuit 42                                                                                   |

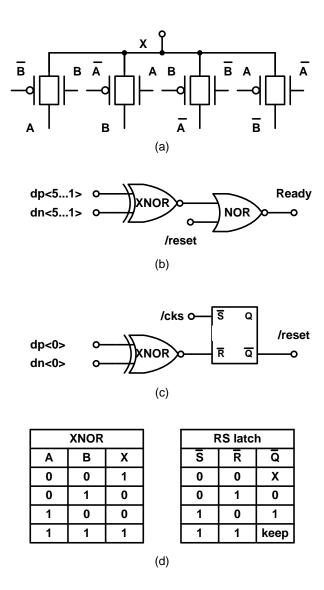

| Figure 3.6: (a) Schematic of the DPL XNOR; (b) the "ready" signal generator; (c) the "reset" signal generation circuit; (d) truth tables of the XNOR and RS latch 45 |

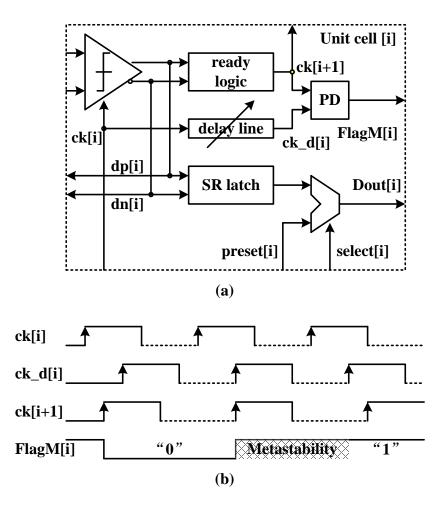

| Figure 3.7: (a) Schematic of the <i>i</i> th cell with the metastability detector circuit; (b) the illustration of the detector flag signal                          |

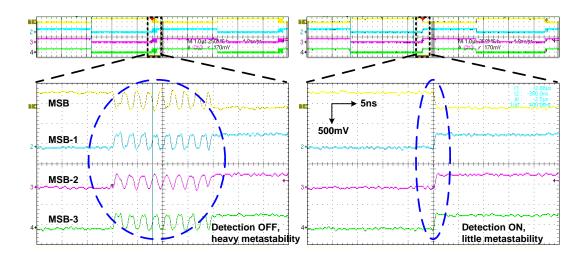

| Figure 3.8: Measured waveforms of the first four bits without (left) and with (right) the metastability detection                                                    |

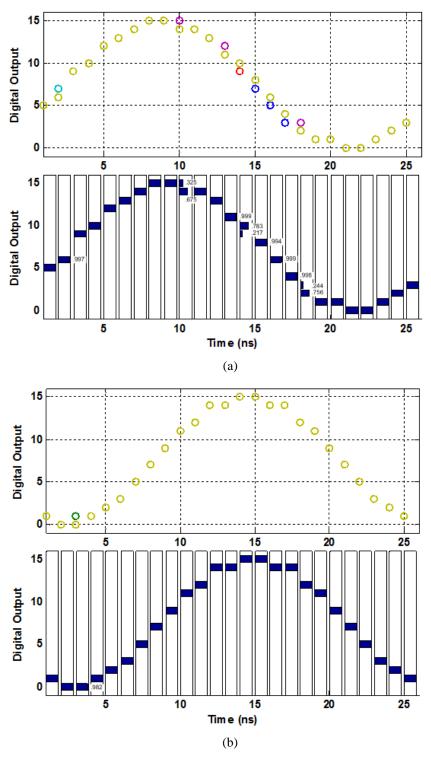

| Figure 3.9: Reconstructed sine wave of 40MHz sampled at 1GS/s with the metastability detector is (a) OFF and (b) ON                                                  |

| Figure 3.10: (a) Chip die photo and core circuit layout; (b) the measurement setup 53                                                                                |

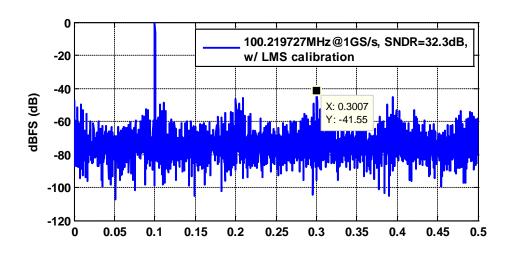

| Figure 3.11: ADC output spectra with and without LMS calibration                                                                                                     |

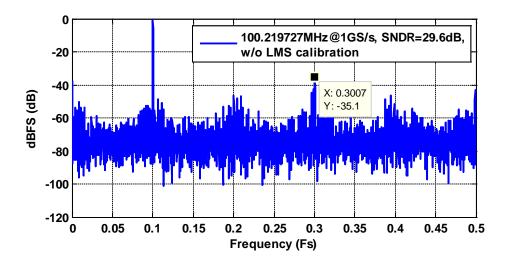

| Figure 3.12: DNL and INL performance after LMS calibration (5 bit)                                                                                                   |

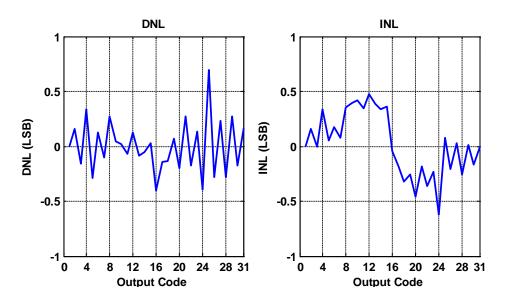

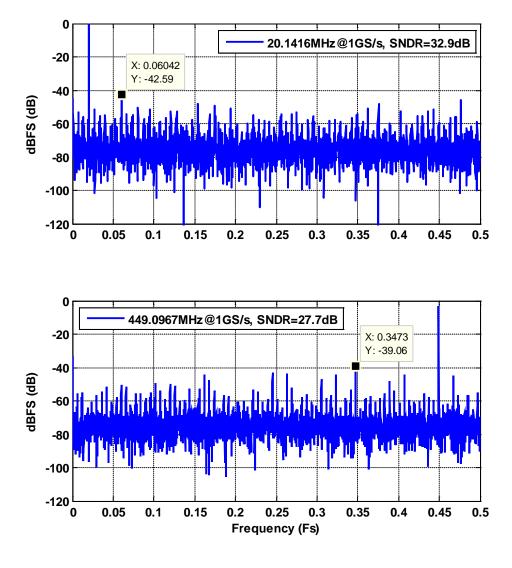

| Figure 3.13: ADC output spectra for different input frequencies with 1GS/s rate 56                                                                                   |

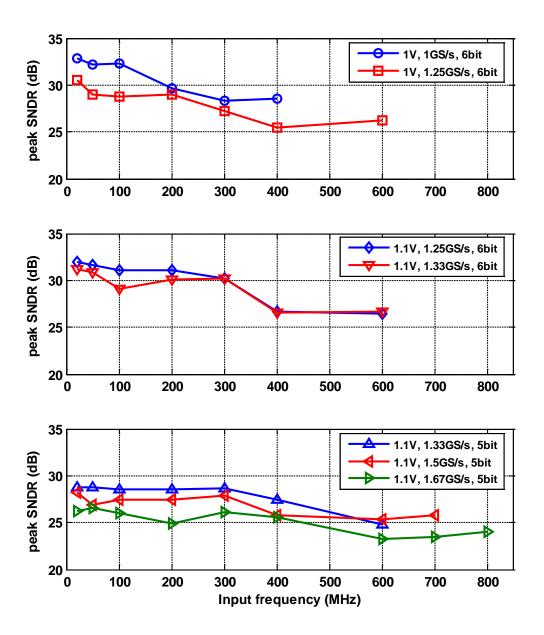

| Figure 3.14: Measured SNDR versus input frequency for ADC under different supplies, sampling rate, and number of bits                                                |

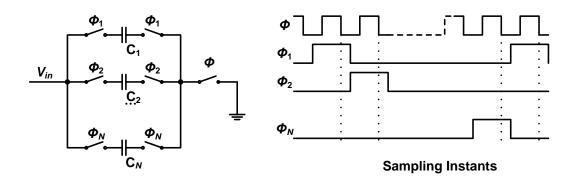

| Figure 4.1: Global passive sampling based on bottom-plate sampling 60                                                                                                |

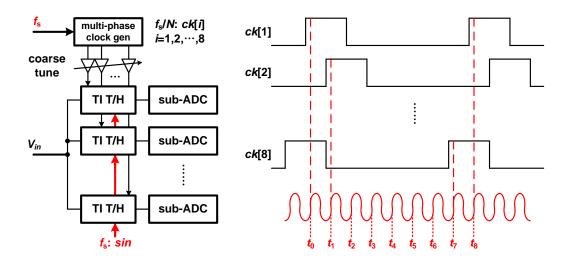

| Figure 4.2: Proposed time-interleaved T/H with a global sine-wave clock                                                                                              |

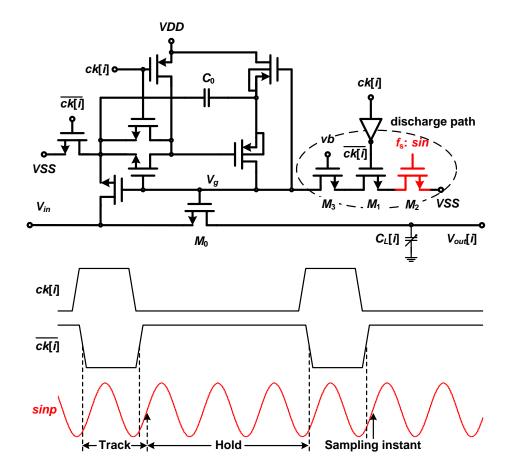

| Figure 4.3: Modified bootstrapped switch enabling global clock synchronization 63                                                                                    |

| Figure 4.4: CML clock buffer and multi-phase clock generation                                                                                                        |

| Figure 4.5: Measured dynamic jitter performance of the injected global clock 66                                                                                      |

| Figure 4.6: The Flash-SA hybrid structure of the sub-ADC                                                                                                             |

# LIST OF FIGURES (Continued)

| <u>Figure</u> <u>Page</u>                                                                                               |

|-------------------------------------------------------------------------------------------------------------------------|

| Figure 4.7: Schematic of the capacitive network C-array 1                                                               |

| Figure 4.8: Schematic of the capacitive DAC C-array 2                                                                   |

| Figure 4.9: Schematic of the designed comparator                                                                        |

| Figure 4.10: Large-signal $G_m$ as a function of the differential input                                                 |

| Figure 4.11: Output spectra of sub-ADC (CH=8) running at 1.5GS/s with input signal frequency of 19MHz and 3.5GHz        |

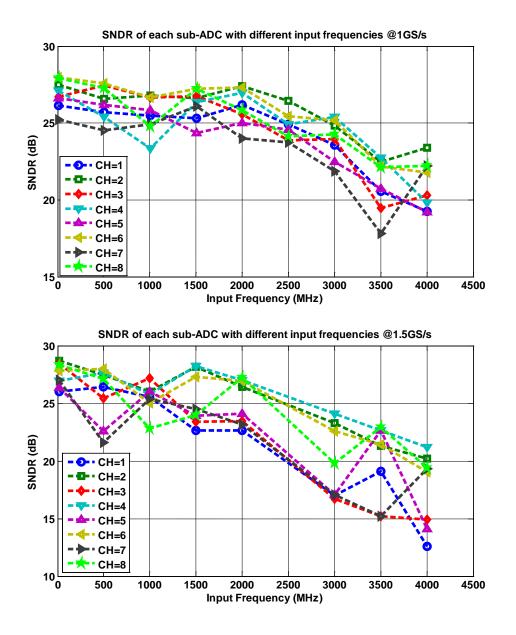

| Figure 4.12: SNDR of sub-ADC running at 1GS/s and 1.5GS/s with different input frequencies                              |

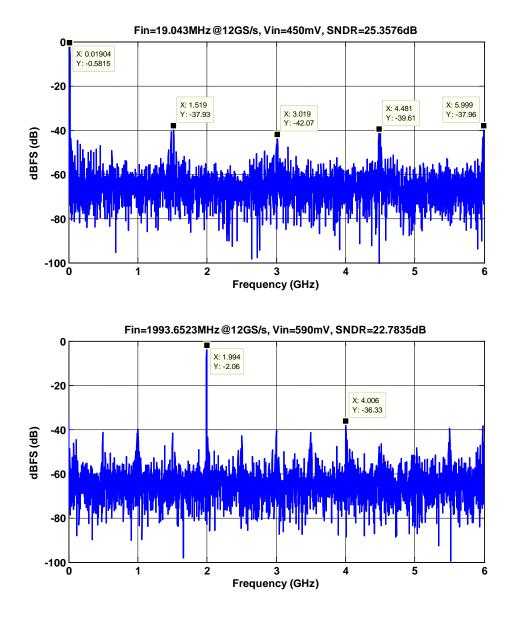

| Figure 4.13: Output spectra of the time-interleaved ADC running at 12GS/s with input signal frequency of 19MHz and 2GHz |

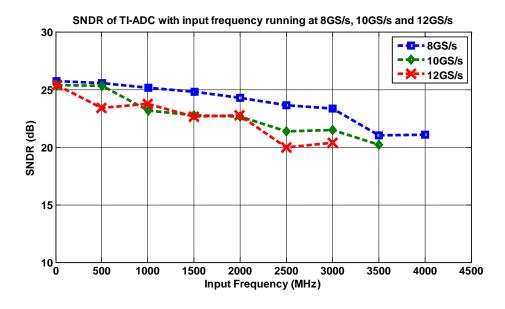

| Figure 4.14: SNDR of time-interleaved ADC running at 8GS/s, 10GS/s and 12GS/s with different input frequencies          |

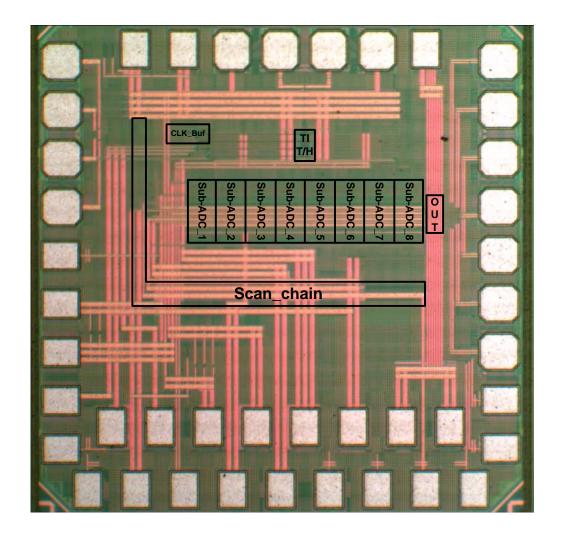

| Figure 4.15: Test chip die photo (1mm by 1.5mm, core area 800µm by 500µm) 77                                            |

### LIST OF TABLES

| <u>Table</u>                                               | <u>Page</u> |

|------------------------------------------------------------|-------------|

| Table 2.1 Summary of the state-of-the-art ADCs over 10GS/s | 11          |

| Table 3.1: Comparison with Previous Works                  | 58          |

| Table 4.1: Target specifications                           | 59          |

| Table 4.2: ADC performance summary                         | 78          |

| Table 4.3: Comparison with previous work [20].             | 80          |

# Design Techniques for Low-Power Multi-GS/s Analog-to-Digital Converters

#### 1. Introduction

#### 1.1. Motivation

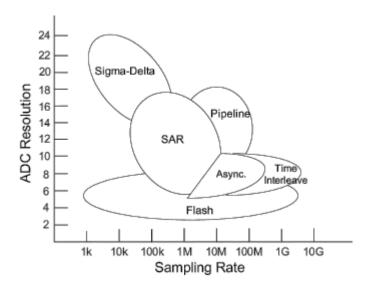

As CMOS technology scales down to the magnitude of nanometer, digital signal processing becomes increasingly more powerful because greater amount of transistors and logic gates can be integrated on a single chip with even less cost. As a result, it is a growing tendency to process the analog signal in the digital domain after appropriate data conversion, and analog-to-digital converters (ADC) have been widely employed in various applications with different requirements for resolution and sampling rate [1]. To satisfy such requirements, multiple ADC architectures have been developed, which was summarized in [2] and is quoted in Figure 1.1 as below.

Although most of the existing architectures, such as sigma-delta, flash, pipeline and

Figure 1.1: ADC architectures and their respective fields of application. [2]

SA, have been intensively studied due to their popularity in most commonly-seen areas, it is only since recent years that the multiple-giga-sample-per-second ADCs have drawn people's attention. The consistently increasing process speed in certain applications requires higher and higher data rate for the ADC employed, while on the other hand the demand for low power consumption places additional stringent requirement for the circuit design.

It is of great interest to systematically study and discuss some design methodology for such multi-GS/s, low power ADCs, and before that it is necessary to introduce some background on the applications where such ADCs are used.

#### 1.2. Application Background

#### 1.2.1. SerDes Circuits

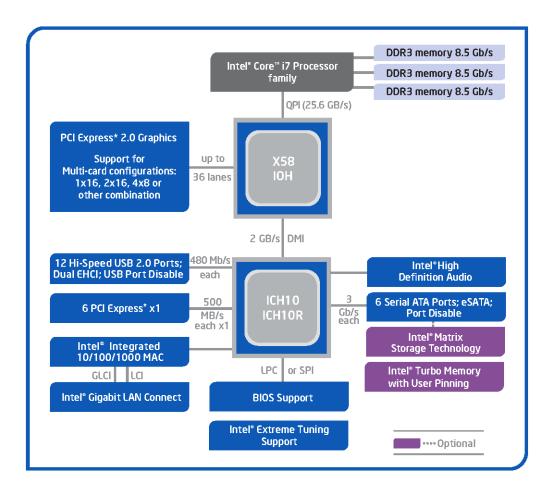

Serializer/deserializer (SerDes, also referred as serial link or wireline), is a critical component in the high-speed I/O interfaces which are widely employed in the commonly used computer systems nowadays. For example, in Figure 1.2 [3] a block diagram consisting of an Intel<sup>®</sup> Core<sup>TM</sup> i7 Processor, an X58 chipset (acting like the north bridge), and an ICH10R I/O Controller Hub (ICH, as the south bridge) is shown, demonstrating a typical computer architecture released by Intel in 2008. Different interconnect standards are used in order to communicate the X58 chipset with other blocks: the QuickPath Interconnector (QPI) is employed to connect the processor, the Direct Media Interface (DMI) is to connect the ICH, and the Peripheral Component

Figure 1.2: Intel<sup>®</sup> X58 express chipset block diagram.

Interconnect Express (PCIe) to the graphics. Even more peripherals are connected to the ICH10R via other serial links, including the Universal Serial Bus (USB) 2.0 to external devices, and the Serial AT Attachment (SATA) to mass storage devices such as hard disk drives and optical drives.

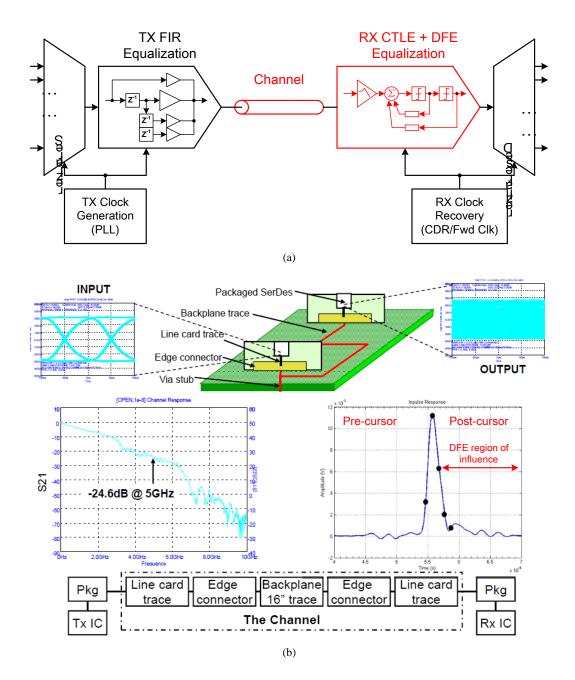

A typical SerDes architecture is shown in Figure 1.3(a), with the emphasis on the transmission channel and the receiver (RX) equalizer. It is noteworthy that in the high-speed SerDes application, transmission channel can no longer been viewed as an

Figure 1.3: (a) Typical SerDes architecture; (b) Transmission channel impairment.

ideal wire. Instead, it is usually in the form of an electrical backplane consisting of IC chip packages, PCB traces (including via stubs), and edge connectors, as shown in

Figure 1.3(b) [4]. Such non-idealities introduce significant frequency dependent loss, such as dispersion and reflection, and co-channel interference, such as far-end (FEXT) and near-end (NEXT) crosstalk, causing degraded channel response and distorted pulse response. As the result, a wide open eye diagram appearing at the output end of transmitter (TX) becomes a close one at the input end of RX, making it impossible to correctly resolve the transmitted signal bits. In order to mitigate the channel loss, certain equalization techniques must be taken, including the feed-forward equalizer (FFE) at the TX end, the continuous-time linear equalizer (CTLE) and the decision feedback equalizer (DFE) at the RX end [5].

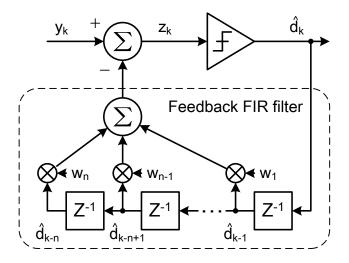

Among all the above equalization techniques, DFE has been widely used due to its many advantages. For example, unlike FFE it boosts high frequency content instead of attenuating the low frequency one; and unlike CTLE it does not amplify noise or

Figure 1.4: Conceptual block diagram of DFE.

crosstalk. The main concept of DFE is to subtract the inter-symbol interference (ISI) directly from the incoming signal via a feedback FIR filter (as shown in Figure 1.4), and the equalization equation can be given as:

$$z_k = y_k - w_1 \hat{d}_{k-1} - \dots - w_{n-1} \hat{d}_{k-n+1} - w_n \hat{d}_{k-n}$$

(1.1)

where  $y_k$  and  $z_k$  are analog signals before and after equalization,  $w_i(i=1,2,\cdots,n)$  are feedback FIR tap coefficients which models channel response, and  $\hat{d}_{k-i}(i=1,2,\cdots n)$  are symbol decision (digital outputs) of previous bits.

Traditionally, the DFE operation was in the analog circuit domain, based on CML [4] or switched-capacitor [6] summation. And with the data rate becoming higher, half-rate [4] or quad-rate [6] architecture with first feedback tap speculation [4][6] was introduced to ease the requirement for the settling time of the critical path. Recently, architectures that implemented the DFE operation in the digital domain have been published [7][8], the comprehensive theory of which has also been presented and discussed [9][10][11][12]. The block diagram is shown in Figure 1.5, with the assistant of an ADC to convert the analog incoming signal to a digital one with

Figure 1.5: Block diagram of ADC-based receiver.

adequate resolution. Such ADC-based receiver brings several benefits: first, besides the DFE which cannot cancel pre-cursor ISI (Figure 1.3(b)), an RX-side FFE can be easily employed. Second, in the digital domain it is more flexible to program the FFE/DFE coefficients to take care of different transmission channel degradation.

As the data rates of the mainstream SerDes circuits reach tens-of-giga-sample-persecond, the demand for the ADC for the aforementioned purpose also becomes high. Several ADCs for the receiver side of the SerDes have been published, including a 24-GS/s 6-bit 1.2-W ADC in 90nm CMOS [13], a 40-GS/s 6-bit 1.5-W ADC in 65nm CMOS [14], and a 56-GS/s 8-bit 9-W ADC in 65nm CMOS (scaling with technology to 63-GS/s 8-bit 5-W in 40nm CMOS) [15]. As the application of such over-10GS/s medium-resolution ADCs becomes wider, it is of great interest and importance to study and research on the related design techniques.

### 1.2.2. Digital Storage Oscilloscope

Test instrument must keep pace with new communications standards that continue to push higher data rates with increasingly tight timing margins, among which the digital storage oscilloscope (DSO) is often counted on to isolate circuit problems, debug system failures, and verify compliance to standards. The DSO features an ADC to convert the analog signal to digital data, which can be stored in memory as much as required, as well as processed by some digital signal processors. As a key selection criterion, the sampling rate of a "real-time" DSO, which is also that of the embedded ADC, needs typically to be 5 to 10 times of the input bandwidth. Sometimes a

variation of DSO called the *digital sampling oscilloscope* is used for the high-speed communication where the waveform consists of repeating pulses, sampling at a low rate deliberately and then uses signal processing to reconstruct a composite view of a typical pulse (i.e. eyediagram). Today, the best oscilloscopes in the market from the giant manufacturers feature an input signal bandwidth of 33GHz with sampling rate up to 100GS/s from Tektronics, and a signal bandwidth of 63GHz with sampling rate up to 160GS/s from Agilent.

The first GS/s ADC fabricated in CMOS technology for the oscilloscope purpose was published in 2002 [16] by Agilent, which was a 4-GS/s 8-bit ADC in 0.35μm CMOS. Another 20-GS/s 8-bit ADC in 0.18μm CMOS was published by the same group in 2003[17]. In general, power consumption is not a major consideration for the ADC designed for such purpose, while bandwidth, noise floor, time-interleaved matching and added jitter are all more important factors. To realize over 100GS/s operation, integrated circuits fabricated in silicon germanium (SiGe) or even indium phosphide (InP) technologies are used to form the heart of oscilloscopes[18].

### 1.3. Thesis Organization

The dissertation begins with an overview of the traditional techniques enabling time-interleaved ADC, including the possible implementations for the sub-ADC and the track-and-hold circuits, in Chapter 2. Due to its advantages and popularity, the successive-approximation (SA) architecture will be emphasized and discussed.

Chapter 3 introduces a single-channel, 1.25-GS/s 6-bit asynchronous SA ADC with improved capacitive DAC delay. The main purpose is to explore an architecture which can achieve fast SA conversion with acceptable power efficiency, which can be further time-interleaved to achieve even higher sampling rate. By using multiple comparators to account for each individual bit conversion, conventional digital logic in the single-comparator SA architecture can be removed, and the feedback loop from the comparator output to capacitive DAC input is essentially reduced. Theoretically in an architectural point of view, the proposed work is the fastest possible 1-bit/step SA ADC that can be realized.

Chapter 4 describes a 12-GS/s 5-bit 8-channel time-interleaved ADC with a global sine-wave clock for sampling instants synchronization. With the slight modification in the track-and-hold circuits as proposed, the timing skew in the multi-phase clock will not cause significant distortion in the reconstructed waveform, and the dynamic jitter is also reduced due to the nature of the sine-wave clock. Besides, by using a Flash-SA-hybrid architecture, the sub-ADC employed is also modified to achieve adequately fast conversion speed.

Chapter 5 summarizes the presented work, and proposes some suggestion for future work.

### 2. Traditional Approaches

Before presenting my own work, it is very necessary and helpful to review the existing techniques that enable the design of multi-GS/s ADCs. This includes two parts, the high-speed sub-channel ADC (sub-ADC) and the track-and-hold circuits (T/H, or sample-and-hold, S/H). The advantages and disadvantages of each structure will be discussed, so the space for possible improvement can be understood.

#### 2.1. State-of-the-Art >10GS/s ADCs

Features and performances of state-of-the-art ADCs running faster than 10GS/s are summarized in Table 2.1.

As listed in Table 2.1, there could be various options for the sub-ADC structure and the number of channels. To achieve the same ultra-high sampling rate, the trade-off between the circuit complication and power consumption of the sub-ADC and the clock generation and distribution must be considered when making the choice.

Generally, if the conversion speed that a single sub-ADC can achieve is low, then a large number of such sub-ADCs have to be time-interleaved to meet the total sampling rate requirement. The power consumed by the sub-ADC may be small, but the cost is the clock generation and distribution, as well as the phase error calibration circuits have to be complicated. Sometimes, the power dissipated in the clock portion may

Table 2.1 Summary of the state-of-the-art ADCs over 10GS/s

|               | [17]         | [13]            | [19]        | [8]         |

|---------------|--------------|-----------------|-------------|-------------|

| No. of bits   | 8            | 6               | 6           | 6           |

| Speed [GS/s]  | 20           | 24              | 10.3        | 10.3        |

| T/H No.       | 80           | 16              | 8           | 4           |

| 1/11 100.     | Pipeline     | TI of 10 SAR    | Pipeline    | Flash       |

| Sub-ADC       | @250MS/s     | @150MS/s        | @1.3GS/s    | @2.5GS/s    |

| Down [W/]     | 10           | 1.2             | 1.6         | 0.33        |

| Power [W]     | 6.5 @500MHz  | 4.8 @8GHz       | 5.8 @100MHz | 4.9 @100MHz |

| ENOB [bit]    |              |                 |             |             |

|               | 4.6 @6GHz    | 4.1 @12GHz      | 5.1 @5GHz   | 4.5 @5GHz   |

| Process [nm]  | 180          | 90              | 90          | 65          |

| FoM [pJ/conv] | 20.50        | 2.93            | 4.56        | 1.42        |

|               | [14]         | [15]            | [20]        | [21]        |

| No. of bits   | 6            | 8               | 5           | 6           |

| Speed [GS/s]  | 40           | 56              | 12          | 16          |

| T/H No.       | 16           | 4               | 8           | 8           |

| Sub-ADC       | TI of 10 SAR | TI of 80 SAR    | Flash       | Flash       |

| Sub-ADC       | @250MS/s     | @175MS/s        | @1.5GS/s    | @2GS/s      |

| Power [W]     | 1.5          | 9               | 0.081       | 0.435       |

| ENOD II. 41   | 4.5 @10GHz   | >5.7            | 4.3 @10MHz  | 4.8 @170MHz |

| ENOB [bit]    | 3.9 @18GHz   |                 | 3.9 @6GHz   | 4.4 @3GHz   |

| Process [nm]  | 65           | 65              | 65          | 65          |

| FoM [pJ/conv] | 2.51         | 3.09            | 0.46        | 0.96        |

|               | [22]         | [23]            |             |             |

| No. of bits   | 6            | 6               |             |             |

| Speed [GS/s]  | 10.3         | 8.5 - 11.5      |             |             |

| T/H No.       | 4            | 4               |             |             |

| Sub-ADC       | Flash        | Rectified Flash |             |             |

|               | @2.5GS/s     | @2.1~2.9GS/s    |             |             |

| Power [W]     | 0.24         | 0.195           |             |             |

| ENOB [bit]    | 5.1 @5GHz    | 4.6 @5GHz       |             |             |

| Process [nm]  | 40           | 40              |             |             |

| FoM [pJ/conv] | 0.70         | 0.59            |             |             |

even be dominant. On the other hand, if a small number of time-interleaved channels are employed, the sub-ADC has to handle very high conversion speed, usually leading

to significant power dissipation itself. Such option may be even harder if the speed requirement for the sub-ADC is beyond its ability.

The above analysis is also supported by Table 2.1, if more details are looked into. Among all the 10 works reported, [17] is the only one that utilizes more than 16 time-interleaved channels, using an 80-channel time-interleaved structure with a 250MS/s pipeline ADC digitizing input analog signal in each channel. Similar structure has not been reported thereafter, probably because there are so many channels that design complexity of the delay-locked loop (DLL), interpolators and dividers in the clock part is huge.

In the remaining works, some interesting facts can be found if the total sampling rate of 20GS/s is used as a boundary. The ADCs [13][14][15] working at higher speed than 20GS/s all employ the very similar architecture, that a small number (no more than 16) of distributed first-stage time-interleaved channels are selected, while each individual channel is made up of multiple SA ADCs which are time-interleaved in a second-stage to meet the extremely high speed requirement for sub-ADC. A smaller channel number may be preferred because the design complexity in the first-stage phase calibration circuit can be much relieved, but the penalty is that for each channel the bandwidth need to be larger and the time-interleaved sub-ADC has to implement more second-stage channels. Since the signal that each sub-ADC processes is steadily held by the first-stage T/H circuits, theoretically the phase misalignment of the multiphase clocks inside the sub-ADC won't affect the overall performance. As can be

expected, in such cascaded time-interleaved architecture, the power consumed in the clock portion dominates over that in the bottom SA ADCs, but that is inevitable for such high-speed converters.

All the other converters running at lower than 20GS/s sampling rate, employ the one-stage distributed time-interleaved architecture. Flash structure is mostly used as the sub-ADC, mainly due to its unique robust ability to handle high sampling rate. As technology scales, the sub-ADC is able to work faster than before, and it is a trend now to further reduce the number of channels to save the resource invested in the clock portion. As is listed in Table 2.1, before 2010 most works published employed 8 channels while in 2013 the latest two both employed only 4 channels.

### 2.2. High-Speed Sub-channel ADC

#### 2.2.1. Flash Architecture

Flash is the simplest ADC architecture. To achieve N bit resolution the input voltage is simultaneously compared with  $2^N$ -1 of evenly spaced reference voltages, usually generated by a resistor ladder, by means of  $2^N$ -1 comparators which are parallel placed. The block diagram is shown in Figure 2.1.

The direct benefit from the flash architecture is it can achieve very high conversion speed, since all the  $2^N$ -1 comparisons take place at the same time. The conversion period is the time for one comparison plus that for the digital encoding. Because of

Figure 2.1: Typical architecture of *N*-bit Flash ADC

this reason, the flash architecture has been exclusively used for high-speed ADCs with conversion rate above 500MHz [24][25][26][27][28].

On the other hand, the drawbacks of the flash architecture are obvious too. As the number of comparators a flash ADC employs increases exponentially with the desired resolution, the resource it consumes becomes enormous. Even though with the offset calibration techniques, each comparator size can be made relatively small, the silicon area the whole ADC occupies is still considerably large, and the power consumption it uses is still significant. What is more, the input capacitance contributed by the large number of comparators is usually so great as to limit the signal bandwidth, and make time-interleaving multiple flash ADCs to obtain even higher sampling rate impractical.

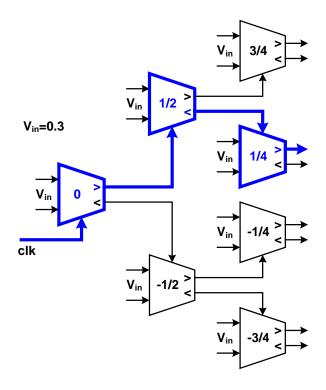

It is noteworthy however, that 2-bit flash ADC is one special case as it only has 3 comparators for the 2-bit conversion, which seems promising in power efficiency. As a matter of fact, according to [29], the flash architecture may be more energy efficient than SA (to be discussed later) if the number of bits is smaller than a certain threshold, as illustrated in Figure 2.2(Fig. 4a in [29]). Therefore, considering one SA conversion process as a cascade of multiple SA conversion processes with a smaller number of bits, it can be seen the possibility of increasing sampling frequency and/or power efficiency by replacing each sub-conversion process with the flash architecture [30].

#### 2.2.2. SA Architecture

Successive-approximation architecture is widely used due to its remarkable power efficiency. To the first order, the power consumption of SA scales linearly with its

Figure 2.2: Modeled SA and flash ADC energies vs. resolution. [29]

resolution, making it an attractive candidate in the medium-resolution ADC applications. As technology scales from 130nm CMOS to 40nm, the ability of achieving faster processing speed of SA has been improving, therefore SA has also become increasingly popular in some high-speed ADC applications.

The conventional architecture of high-speed SA ADCs is illustrated in Figure 2.3, which consists of a single comparator to compare the analog signal with certain reference voltages bit by bit, a capacitive digital-to-analog convertor (DAC) to generate the successively-approximated reference voltages for each bit comparison, and a digital logic that both decodes the corresponding comparator outputs and

Figure 2.3: Conventional SA architecture with critical path.

controls the switching of the capacitive DAC in the critical path. The total conversion time to fulfill a single bit comparison is the sum of the time required for the comparator to resolve the current bit  $t_{comp}$ , the delay through the SA algorithm digital logic  $t_{digital}$ , and the settling time for performing the charge sharing within the capacitive DAC  $t_{DAC}$ :

$$T_{critical} = t_{comp} + t_{digital} + t_{DAC} (2.1)$$

Among the above three terms in (2.1),  $t_{comp}$  for a typical StrongARM latch-type dynamic comparator is divided into several phases (as shown in Figure 2.4[31]) [32], and expressed as follows:

$$t_{comp} = \underbrace{\frac{2C_L V_{thp}}{I_o}}_{t_o} + \underbrace{\frac{C_L}{g_{m,eff}} \ln\left(\frac{1}{V_{thp}} \sqrt{\frac{I_o}{2\beta}} \frac{\Delta V_{out}}{\Delta V_{IN}}\right)}_{t_{latch}}$$

(2.2)

In (2.2), the first term represents the time taken to discharge the differential outputs

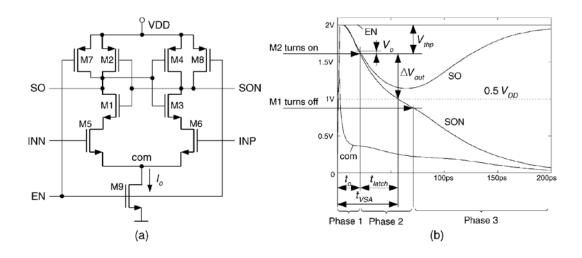

Figure 2.4: (a) StrongARM comparator; (b) its transient behavior. [31]

SO/SON from the preset value VDD to  $VDD-V_{thp}$  at which point transistor M2 is barely turned on.  $C_L$  is the loading capacitance at the outputs SO/SON,  $I_o$  is the tail current during the discharging phase, and  $V_{thp}$  is the threshold voltage of PMOS. The second term represents the time taken in the regeneration phase during which a positive feedback is performed.  $\Delta V_{IN}$  is the input difference between INP and INN,  $\Delta V_{out}$  is the voltage swing at the output at any instant of interest,  $g_{m,eff}$  is the effective transconductance of the cross-coupled inverters, and  $\beta$  is the technology-related constant. Obviously,  $t_{comp}$  is input- and technology- dependent, and is constraint by power budget  $I_o$ . Even if the power budget can be ignored, its value is still bounded by the intrinsic parasitic capacitance contained in  $C_L$ . Therefore, there is always a lower limit for  $t_{comp}$  once the precondition is set.

It is difficult to give quantitative estimation for the second term in (2.1), because such value will be different depending on various structures of the selected digital SA logic, which is employed to process the results of the current quantized bit and then controls the switches in the capacitive DAC based upon its state machine to generate corresponding analog reference voltages for the next bit comparison. The digital logic requires that the switches that have been previously set must maintain their state until the end of the entire conversion period; otherwise, the final generated digital output will be incorrect. An example given in [30] shows that this logic gate delay consumes up to 75% of the conversion period, thereby limiting any possibility for future speed improvements required for multi-gigahertz sampling rates.

Finally the third term in (2.1), the settling time of the capacitive DAC can be generally derived as below, assuming  $R_{eff}$  and  $C_{eff}$  are the effective on-resistance of the MOS switches and capacitance of the capacitive network. For the minimum amount of accuracy  $V_{LSB}$  required, sufficient settling time must be allocated such that the residual error is small:

$$t_{DAC} = R_{eff} C_{eff} \ln \frac{|V_{step}|}{V_{LSB}}$$

(2.3)

In (2.3),  $V_{step}$  is the voltage step size required for the current stage to settle, and  $V_{LSB}$  is the LSB voltage determined by the full-scale input swing and the required resolution. With improved technology, the unit capacitance can be made extremely small (< 1fF in [33]). However, this trend of decreased capacitor size is limited by thermal noise, as well as layout complexity and uncertainty in parasitic capacitances. Moreover, the on-resistance of the MOS switches cannot be infinitely small either; otherwise the sizes of the switches have to be too large. Therefore,  $t_{DAC}$  value is also constrained.

In order to improve the SA performance in term of operational speed, power consumption and accuracy, many techniques have been proposed in the past decade. Therefore it is of great benefit to review those techniques and have some discussion on their advantages and disadvantages.

#### A) Synchronous vs. Asynchronous Conversion

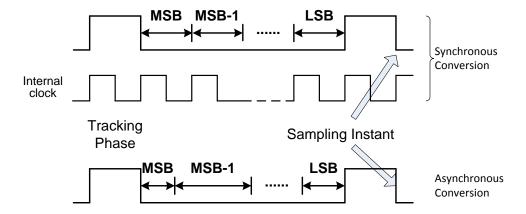

Architecture wise, the SA can be divided into synchronous [30] and asynchronous processing [2][34], which is illustrated in Figure 2.5. The synchronous processing

Figure 2.5: Synchronous and asynchronous SA comparison.

features an internal high-frequency clock which will trigger each bit comparison, and then reset the comparator. Typically, if the sampling rate of the ADC is  $F_S$ , and the targeted resolution is N, then the frequency of such internal clock need to be at least  $(N+1)\cdot F_S$ . On the other hand, the asynchronous processing does not require any internal clock, while every bit comparison is triggered by the completion of a preceding event (which can either be the sampling phase, or the last bit comparison).

According to (2.1) and (2.2), only the comparator delay  $t_{comp}$  is dependent on the comparator input signal values. Due to the nature of the SA algorithm only one of these values will fall into the small region of  $\pm 1/2$  LSB, which will lead to very long comparison delay and consequently very long conversion time  $T_{critical}$ . Therefore, as for the synchronous conversion, since the repeating internal clock has to make sure every bit conversion is fully complete, its period must be longer than the only and the largest  $T_{critical}$ . This will clearly cause a waste of time because other than the longest

conversion bit, the circuits will idle there waiting for the next rising edge of the internal clock to come, even though the current bit conversion is already settled. From this point of view, the asynchronous architecture takes great advantage of faster processing cycles, because once the current bit conversion is complete the next will be started and no time is spent waiting.

#### B) Comparator offset calibration

The input referred offset of the comparator used in the ADC will possibly degrade the overall ADC performance, so it is better to be minimized. Such offset is primarily a function of threshold mismatch and transistor dimension as below:

$$\sigma_{V_t} = \frac{A_{V_t}}{\sqrt{W \cdot L}} \tag{2.4}$$

Obviously, in order to reduce the offset by 2 times, the transistor size need to be increased by 4 times. Such calculation shows that it is not practical due to the excessive area and power consumption cost, and offset calibration is necessary to efficiently achieve good accuracy.

The basic idea for the calibration is to deliberately introduce some imbalance to compensate for the offset. Such imbalance can be either by capacitance loading [35] or current injection[36], or even voltage difference [30]. To calibrate the offset, the differential inputs of the comparator are usually tied together to a certain common-mode voltage, which should be the same as that when the comparator is really working, and the comparator output is monitored and fed back to the state machine which

controls the imbalance. When the offset is well compensated, the digitized output should have almost equal chance of logic 0's and 1's.

Depending on when the calibration is performed, the calibration structure can be divided into foreground [35][36] and background [30]. In the foreground structure, the calibration will be performed before the real circuit operation, during which the imbalance for compensation will be obtained and used all the way through the following operation. Such method is less complicated, but cannot account for any change of offset due to the long term drift of circuit voltage or temperature. Therefore, it is suitable for the application that does not require very accurate offset compensation. On the other hand, the calibration will be performed during the real circuit operation in the background structure, so that it can timely cancel the offset whenever it is drifting and is much more accurate. However, the cost is that a separate calibration phase is required every one or several period, which will affect the overall conversion speed.

#### C) Capacitive network (DAC) solutions

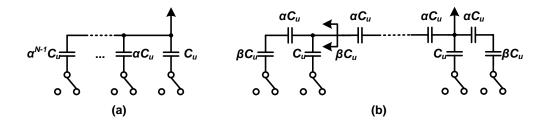

Several architectural possibilities exist for the capacitive DAC. By connection style it can be divided into parallel [37] and serial [2][33][34] structures, and by radix into binary [34][37] and non-binary [2][33] structures.

Most parallel capacitive DACs are binary ( $\alpha$ =2 in Figure 2.6(a)), which is the first structure used in SA ADC as well as the most straightforward. As is well known, such DAC generates a voltage that increases or decreases by half of the reference voltage for the first step, then by a value which is half of the previous one for the followings.

Figure 2.6: (a) Parallel connection; (b) serial connection of capacitive DAC.

For such structure, it is relatively easy to make the capacitors inside the DAC well matched to achieve good accuracy and linearity, and the effect of any parasitic capacitance can be minimized by connecting the switches to the bottom plates of the capacitors. However, the penalty is that the total capacitance of the DAC will increase exponentially with the resolution N, which will lead to large loading for preceding stage and cause significant power consumption. To reduce the power consumed by dynamic switching in the DAC, some energy-efficient structures such as capacitor-splitting [38][39] and junction-splitting [40][41] have been presented.

The schematic of a serial-connected capacitive network is shown in Figure 2.6(b). To perform successive approximation procedure, it is wanted that:

$$\begin{cases} \beta = 1 + \alpha \parallel \beta \\ Radix = 1 + (\beta/\alpha) \end{cases}$$

(2.5)

where the operator  $\|$  is defined as  $x \| y = x \cdot y / (x + y)$ . When  $\alpha = \beta = 2$ , the radix is 2 and the capacitive network is binary, otherwise it is non-binary. Non-binary network actually has a radix less than 2, which introduces redundancy to allow decision errors for faster settling. The overlapped search range can compensate for wrong decisions

made in earlier stages if they are within the error tolerance range. It can be calculated that no matter how large the resolution N is, the total input capacitance of the serial-connected capacitive network  $C_{in}$  does not increase:

$$C_{in} = [1 + 2 \cdot (\alpha \parallel \beta)] \cdot C_u \tag{2.6}$$

Despite the benefit of its small loading capacitance for fast settling, the series capacitive network heavily suffers from the parasitic capacitance. Considering the parasitic capacitance from interconnects and the top and/or bottom plates of capacitors themselves, (2.5) must be modified [2][34] accordingly. Even though, such parasitics is non-consistent thus it is impossible to accurately determine their values in the design/layout phase. Calibration based on the LMS algorithm [2] is required.

### D) SA logic improvement

Several methods have been proposed to reduce the delay of the digital SA logic, such as employing flip-flop bypass SA logic [30] and a semi-closed digital loop [34]. The former technique removes a D-flip-flop between the comparator outputs and the capacitive network, but still requires a mux to select different control bits depending on the state machine. The latter technique enables some overlapping between the comparison time and the SA logic processing time to expedite the processing.

## 2.2.3. Binary-Search Architecture

Binary-search ADC [42][43] can be viewed as a transitional structure between flash and SA ADCs. As shown in Figure 2.7, it consists of  $2^{N}$ -1 comparators as in the

Figure 2.7: Block diagram of binary-search architecture.

flash structure, but only N of them are really activated during every N bit conversion as the SA approach. Similar to the flash ADC, the reference level of each comparator can be provided by a resistor ladder, therefore it can save the settling time from the capacitive DAC as in the SA ADC. Theoretically, the binary-search architecture takes the advantages of both flash and SA, and achieves the balance between high operational speed and low power consumption. However, some disadvantages from the flash remain for the binary-search structure, including the large area and consequently large loading for preceding stage.

## 2.3. Time-Interleaved Track-and-Hold Circuit

## 2.3.1. Overview and Quantitative Analysis

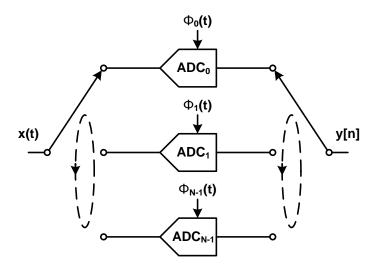

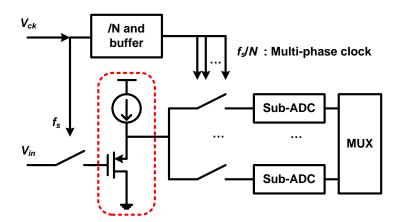

To achieve the high sampling rate of over 10GS/s, the time-interleaved (TI) architecture is the only solution. As is shown in Figure 2.8, a time-interleaved ADC is an ADC that cycles through a set of N sub-ADCs, such that the aggregate sampling rate is N times that of the individual sub-ADCs.

In the time domain, ignoring quantization, each sub-ADC output can be expressed as:

$$y_i[n] = x((nN+i)T_s)$$

(2.7)

In (2.7),  $T_s$  is the sampling period of the time-interleaved ADC, N is the number of sub-channels (so that  $N \cdot T_s$  is the sampling period of a single sub-ADC), and i=0, 1, ...,

Figure 2.8: Block diagram of time-interleaved architecture.

*N*-1 denotes the sequence of the channel. By using multiplexer at the output side, the streams from all the *N* channels are combined such that

$$y[n] = [y_0[0], y_0[0], \dots, y_{N-1}[0], y_0[1] \dots] = y_i \left[\frac{n-i}{N}\right], i = n \mod N$$

(2.8)

Combining (2.7) and (2.8), we have:

$$y[n] = x(nT_s) (2.9)$$

which is the same output as a single ADC with the sampling rate of  $1/T_s$ .

On the other hand, in the frequency domain, discrete Fourier transform (DFT) can be applied to each individual sub-ADC outputs (sampled at the sampling rate of the time-interleaved ADC), and the results add up to that when DFT is applied to the time-interleaved ADC. Given a discrete set of real number x[n], the DFT of x[n] is:

$$X(\omega) = \sum_{n=-\infty}^{+\infty} x[n]e^{-i\omega n}$$

(2.10)

and in theory the following equation holds:

$$Y[f] = \sum_{i=0}^{N-1} Y_i(f)$$

(2.11)

in which  $Y_i(f)$  is the DFT of the upsampled sub-ADC output, and N is the channel number.

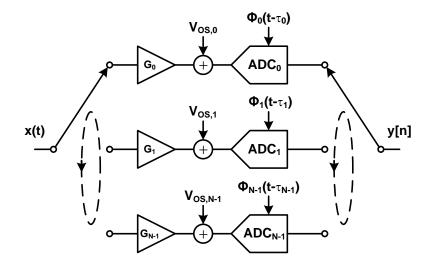

In practice, however, there exist a lot of non-ideal errors in the time-interleaved channels, including the voltage offset, gain, timing skew, bandwidth and nonlinearity, as shown in Figure 2.9. Such errors result from PVT (process, voltage, temperature) variation, layout nonidealities, and mismatch in capacitance and so on, all of which will limit the overall ADC performance. For example, the offset differences in each

Figure 2.9: Time-varying errors in TI ADC: offset, gain and timing skew.

channel will introduce spurs at frequencies  $i ext{-} f_s / N$ , and the gain differences and timing skews will cause spurs at  $f_{in}$ - $i ext{-} f_s / N$ . While it is possible to insert a programmable gain amplifier (PGA) in each sub-channel to compensate for offset and gain mismatch [8], it is more challenging to deal with the static timing skew or phase mismatch.

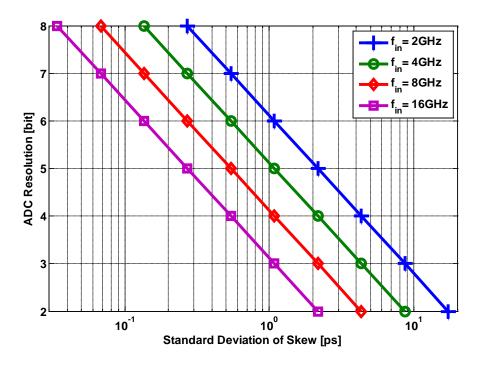

Mismatches in different time-interleaved channels in offset, gain, and sampling phase will cause degradation in the SNDR (signal to noise and distortion ratio) performance. In [44] the quantitative results of the bound on the offset, the gain, and the timing skew have been derived:

$$\sigma_{offset} = \sqrt{\frac{N}{N-1} \cdot \frac{A^2}{3 \cdot 2^{2B}}} \tag{2.12}$$

$$\sigma_{gain} = \sqrt{\frac{N}{N-1} \cdot \frac{2}{3 \cdot 2^{2B}}} \tag{2.13}$$

$$\sigma_{timing} = \sqrt{\frac{N}{N-1} \cdot \frac{2}{3 \cdot 2^{2B} \cdot (2\pi f_{in})^2}}$$

(2.14)

where N is the number of time-interleaved channels, A is the input signal amplitude,  $f_{in}$  is the input signal frequency, and B is the desired number of bits. According to (2.14), the relation between the ADC resolution and the standard deviation of timing skew for different input signal frequency can be plotted as in Figure 2.10 (N=8).

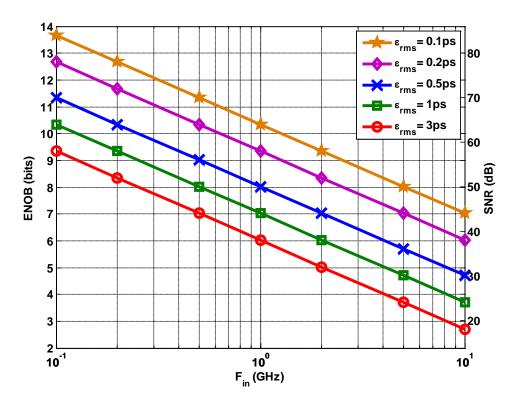

Besides the static errors as described above, the dynamic sampling clock jitter can also cause noise at the T/H output. Unlike the static errors that can be eventually calibrated, the clock jitter is more intrinsic. The SNR of T/H output due to the sampling clock jitter with RMS value of  $\varepsilon_{rms}$  is given by [1] as below:

Figure 2.10: ADC resolution vs. timing skew standard deviation.

$$SNR = -20\log(2\pi \cdot f_{in}\varepsilon_{rms}) \tag{2.15}$$

where  $f_{in}$  is the input sinusoidal signal frequency. Based on (2.15) the relation between the ENOB (effective number of bits) of ADC and the RMS jitter can also be obtained and plotted in Figure 2.11.

# 2.3.2. Global Architecture

In general, there are two types of time-interleaved T/H circuits, namely the global and the distributed architecture. The global T/H as shown in Figure 2.12 features a global buffer running at the highest sampling frequency of  $f_s$  in the front-end, whose

Figure 2.11: ENOB and SNR vs. clock jitter and input frequency.

Figure 2.12: Global time-interleaved track-and-hold topology.

output is sampled again by the multi-phase clock running at the low sampling frequency of  $f_s/N$  for the array of N sub-ADCs. Because the signal at the buffer output has already been held, the timing error in the following time-interleaved T/Hs is no longer a problem.

However, the immunity to multi-phase timing skew of the global time-interleaved T/H structure is obtained at the cost of the very high requirement for the global buffer. The buffer must be able to handle the full tracking bandwidth while driving a considerably large loading caused by multiple sub-ADCs. Besides, such buffer needs to provide very good linearity, depending on the resolution specification of the ADC. For a typical circuit used as such buffer, the source follower suffers from the nonlinearity resulted from the threshold voltage and the channel length modulation effect. In order to mitigate such problems, techniques such as replica well-biasing[45] and constant  $V_{DS}$  by additional clamping[46] have been proposed.

Because of the difficulty designing a perfect buffer at high frequency as discussed above, the global time-interleaved T/H structure is mainly used in the applications less than or around 1-GS/s sampling rates [30][33][46][47], while for multi-GS/s sampling ADCs, distributed time-interleaved T/H is more frequently employed.

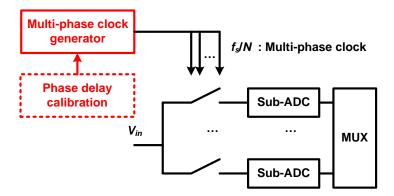

#### 2.3.3. Distributed Architecture

Distributed time-interleaved T/H driven by multi-phase clocks is a more power-efficient architecture (Figure 2.13). But the problem in this topology is the sampling timing error, which is usually caused by the mismatch in the multi-phase clock paths as well as in different signal channels, need to be minimized. Therefore complicated calibration techniques are required to detect and compensate the timing errors.

For example, [17] presents a foreground phase error calibration. Pulse train with fast edges is applied to the time-interleaved ADC, and based on FFT results phase delay of T/H is detected and adjusted. Such procedure is repeated until the phase

Figure 2.13: Distributed time-interleaved track-and-hold topology.

alignment is optimized. In [48] another foreground calibration based on histogram counting is proposed. Two quantizer-based phase detectors sample the outputs of adjacent track/hold circuits, detecting any phase offsets arising from process and dimension mismatches both in the clock path and the T/H switches. Finally, a background timing skew calibration is introduced in [20]. An extra channel with a 1-bit ADC is added, and the correlation between that extra ADC and each sub-ADC is measured. The timing skew is detected in the digital domain and minimized by adjusting digitally controlled delay lines when the correlation is maximized.

# 3. A Single-Channel Asynchronous Successive-Approximation ADC with Improved Feedback Loop

### 3.1. Proposed Architecture

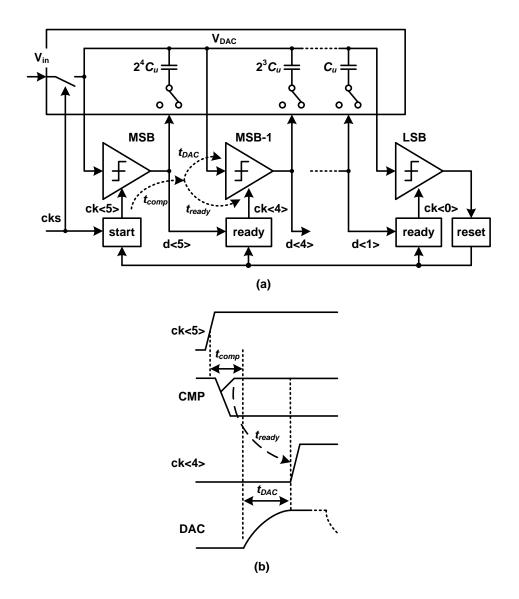

As already discussed in Section 2.2.2, in the conventional structure, the aforementioned three SA operations occur successively in time. Because the comparator must wait for the capacitive DAC to be fully settled before it can start the comparison,  $t_{comp}$  and  $t_{DAC}$  cannot occur simultaneously. However, the digital logic processing does not necessarily require separate time durations other than  $t_{comp}$  and  $t_{DAC}$ . In order to explore the timing benefits of performing the digital SA algorithm at the same time while the capacitive DAC is settling, an asynchronous SA ADC with improved feedback delay is proposed, as shown in Figure 3.1 [49].

The proposed SA ADC architecture features two new techniques. Unlike a conventional architecture that uses a single comparator followed by digital logic to determine, store, and transfer the comparison results, the new architecture uses *N* comparators for *N*-bit conversion, storing each comparison result into the digital output of each comparator. These digital outputs are utilized simultaneously in two parallel paths: one is directly to the capacitive DAC, such that the DAC can respond to the results promptly and generate the successively-approximated analog signal quickly without being delayed by any digital logic; the other is to a digital clock generator that detects the completion of the current quantization and then generates a "ready" signal

Figure 3.1: (a) Proposed architecture of the asynchronous SA ADC with improved feedback delay; (b) critical path for a one-bit conversion.

to clock the next quantization. Both paths occur simultaneously, so that the critical path is reduced to:

$$T_{critical} = t_{comp} + max[t_{ready}, t_{DAC}] = t_{comp} + t_{ready}$$

(3.1)

In order to improve the conversion as much as possible, any unnecessary buffer delays are to be avoided. Therefore, all digital logic gates were customized using logical effort [50] to optimize the gate delay and power consumption. Note that the time delay required for generating the ready signal must be made adequately longer than the settling time of the DAC. Compared to (2.1), the critical path in the proposed design is significantly improved over a conventional SA-ADC.

Second, the proposed structure makes it natural to adopt asynchronous processing, taking advantage of the average quantization delay as opposed to the worst-case delay, as there will only be one quantization when the input level is less than 1/2 LSB due to the binary SA algorithm. After the completion of the front-end track and hold, which is determined by the global periodic clock *cks*, the quantization of the MSB cell is initiated, followed by the proceeding quantizations from MSB-1 to LSB, triggered like dominoes from the outputs of the ready logic. The *reset* signal, generated from the LSB cell, will then precharge all the comparators and the capacitive DAC, preparing the entire SA-ADC for the next conversion. One additional benefit of the proposed architecture is that the resolution of the SA ADC can be easily digitally programmed by disabling the last LSB cell, using the *ready* signal of the LSB-1 cell as the *reset* signal. This programmability may be useful for applications where higher sampling rate is preferred over higher resolution.

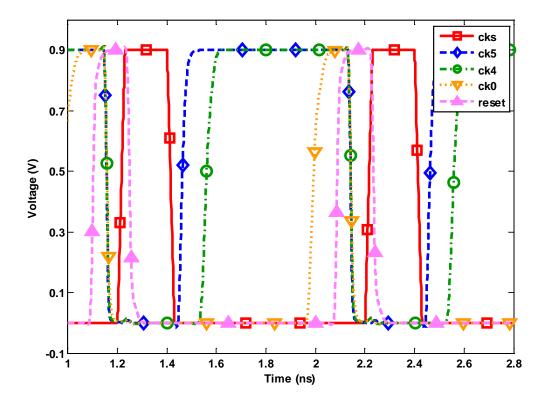

Signal voltages for a typical conversion period of the 6-bit SA ADC are simulated and shown in Figure 3.2. After the falling edge of the *cks* signal, the clocks that

Figure 3.2: Simulated waveforms for one single conversion period of the proposed SA ADC.

trigger the comparison from MSB to LSB are generated sequentially. These clocks will maintain their logic high state until the *reset* signal is generated to pull them down to a logic low value. The final *reset* signal will be disabled at the beginning of each period so as not to impact normal operation.

Besides the features previously discussed, there are some other important considerations. First, each of the six comparators starts its own quantization triggered by the preceding *ready* signal, but all quantizers are precharged and reset only when the LSB comparison is completed. During every conversion period, each of the six

comparators only makes one quantization, and afterwards they each hold the comparison results for the rest of the period to ensure that the DAC performs correctly. In comparison, a conventional 6-bit SA ADC consists of only one comparator, but that comparator performs quantization six times. Therefore, the energy consumption in the above two cases is comparable, as the static energy consumption for a dynamic comparator is negligible at this sample rate. Second, the comparison results of each comparator will be passed through an R-S latch which is not within the critical path, with all six outputs retimed as the final digital bits.

#### 3.2. Circuit Implementation

Several critical circuit blocks are described in detail in the following sections.

## 3.2.1. Capacitive DAC

A conventional parallel binary capacitive DAC (Figure 3.3) is employed, except with one minor change -- the capacitor directly connected to ground is made  $17C_u$  rather than  $C_u$ . Considering the parasitic capacitance  $\Delta C$  contributed by the six paralleled comparators is considerable, the real reference voltage should be adjusted as follows:

$$V_{ref} = 1.5 \times V_{FS} \times (1 + \Delta C/48C_u)$$

(3.2)

In this way, the reference voltage is deliberately set to be over 750mV, while the full-scale input voltage is 500mV as defined by the system specifications. The bottom

Figure 3.3: Schematic of the capacitive DAC, and generation of the sampling clock.

plates of the binary weighted capacitors are connected to ground through NMOS switches and to the reference voltage through PMOS switches, such that parasitic MOS switch capacitances do not affect the final accuracy of the DAC settling. Each pair of the MOS switches is gated by the same control signal which is either the positive or negative output of a corresponding comparator, so that the connection is similar to an inverter with the reference voltage as its supply. The reference voltage is preferred to be made large in order to improve the switching speed of the PMOS. To reduce design complexity, all the switches were designed to be the same size, even though the binary-weighted capacitors they connected varied significantly in size. For an improved future design, power consumption can be further reduced if both the

switches and the corresponding comparators are sized accordingly based on the different capacitor values. One drawback of the DAC used in the design, however, is that only one of the positive and negative outputs of the DAC is increased by the ratio of the reference voltage, making the overall differential output change up or down. Hence, while the differential voltage is generated correctly, the common-mode voltage may actually drift. This will cause the comparator offset to vary for different input common-mode values, leading to uncompensated offset for particular input voltage levels.

Given the limited time to perform data conversion when the frequency is high, the time allocated for signal sampling and conversion has to be compromised. Depending on the number of bits needed to be resolved, the on-resistance of the T/H switch R, and the loading capacitance C, the required time taken for adequate sampling can be estimated. Unfortunately, due to process variations the exact values of RC delay cannot be known, so that it is necessary to provide some calibration of the clock pulse externally. This optimized pulse width can be selected at startup, when the best SNDR performance is evaluated and then statically set.

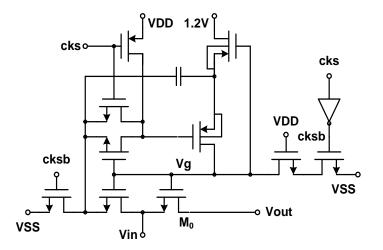

# 3.2.2. Bootstrapped Switch

Bootstrapped switches are employed (Figure 3.4) in the sampling circuit in order to achieve both smaller on-resistance and minimal signal-dependent sampling distortion. As was previously illustrated in [51], when the sampling clock cks is low, the switch  $M_0$  is shorted to ground and the capacitor is charged to near the supply voltage. When

Figure 3.4: Bootstrapped switch used in the capacitive DAC

cks is high, the large voltage difference across the capacitor will be added to the input signal and then applied to the gate of the pass switch, making the gate-source voltage of the NMOS close to that high voltage constantly. In order to reduce the onresistance of the bootstrapped switch such that the T/H circuit can meet the hard timing requirement, a 1.2V external supply voltage is used for charging the capacitor. This circuit is carefully designed so that no voltage difference between any two nodes of a single MOS transistor is larger than the nominal voltage of 1V for the technology.

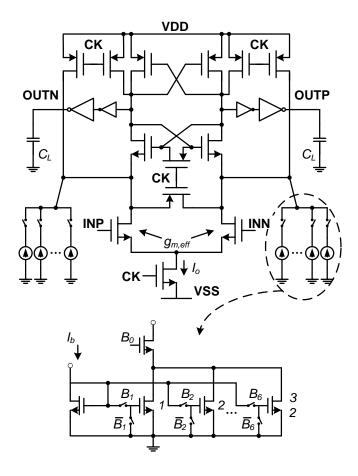

# 3.2.3. Comparator with Offset Cancellation

Six StrongARM comparators with offset cancellation [35] (Figure 3.5) are used for the entire 6-bit quantization. When the clock *ck* is reset to ground, both the positive and negative outputs are shorted to the supply voltage, shorting all the bottom plates of the capacitors in the DAC to ground. Clocked by the ready signal from the preceding

Figure 3.5: Comparator design with current steering offset cancellation circuit.

conversion, each comparator evaluates the analog input signal and the corresponding differential outputs begin to split to the supply voltage and ground, respectively. Buffered by two stages of inverters, the regenerated outputs are directly sent to the switch gates of the capacitive DAC, and are kept high until reset occurs at the end of the 6-bit conversion. The two inverters are sized such that they can provide enough drive ability while minimizing the loading seen by the regeneration nodes. To mitigate hysteresis during the quantization, all the internal nodes are also shorted to

the supply voltage during the precharge phase. Unlike a conventional structure where only one comparator is used, each of the six comparators exhibit a different mismatch such that the offset is no longer a systematic error that can be subtracted during postprocessing. Therefore, foreground offset calibration for each comparator is performed at startup, where an offset cancellation circuit composed of two sets of 7-bit binary current sources is used [36]. Since this 6-bit ADC has a relatively large LSB (approximately 15mV), the calibration requirements are not very strict. During calibration, the ADC is fed with the differential voltages that cause metastability to a specified comparator. The corresponding comparator digital output is monitored on the oscilloscope, and the control bits are tuned until metastability is observed. Current imbalance using a digitally-controllable current mirror is used, such that the effect on the regeneration speed due to the added capacitance is minimized. In addition, pseudo-common-gate isolation reduces the effect of parasitic loading on the comparator speed. In this design, the transistors in the comparator were sized large, such that the 3-sigma Monte Carlo offset was simulated to be within 50mV. In the simulation, offsets ranging from 1mV to 50mV can be cancelled when turning ON and OFF corresponding current sources. Although there will be some static current through the offset cancellation circuit during the precharge phase since the current mirror is pulled up to supply, the injected current is minor and negligible. According to simulations, the LSB value in the binary current source is around 2µA for cancelling the offset voltage.

## 3.2.4. Digital Logic