#### AN ABSTRACT OF THE DISSERTATION OF

Weilun Shen for the degree of <u>Doctor of Philosophy</u> in <u>Electrical and Computer</u> Engineering presented on July 8, 2010.

Title: <u>Low-Power Double-Sampled Delta-Sigma Modulator for Broadband</u>

<u>Applications.</u>

| Abstract approved: |  |

|--------------------|--|

|                    |  |

#### Gabor C. Temes

High speed and high resolution analog-to-digital converter (ADC) is a key building block for broadband wireless communications, high definition video applications, medical images and so on. By leveraging the down scaling of the latest CMOS technology and the noise shaping properties, delta-sigma ( $\Delta\Sigma$ ) ADCs are able to achieve wide-band operation and high accuracy simultaneously. In this thesis, two novel techniques, which can be applied to high performance  $\Delta\Sigma$  ADC design, are proposed. The first one is a modulator architectural innovation that is able to effectively solve the feedback timing constraints in a double-sampled  $\Delta\Sigma$  modulator. The second one is a transistor level improvement to reduce the hardware consumption in a standard Data Weighted Averaging (DWA) realization.

Next, charge-pump (CP) based switched-capacitor (SC) integrator is discussed. A cross-coupling technique is proposed to eliminate parasitic capacitor effect in a CP based SC integrator. Also, design methodologies are introduced to incorporate a modified CP based SC integrator into a low-distortion  $\Delta\Sigma$  modulator. A second-order  $\Delta\Sigma$  modulator was designed and simulated to verify the proposed modulator topology.

Finally, the design of a double-sampled broadband 12-bit  $\Delta\Sigma$  modulator is presented. To achieve very low power consumption, this modulator utilizes the following two key design techniques:

- 1. Double sampled integrator to increase the effective over-sampling ratio.

- 2. Capacitor reset technique allows the use of only one feedback DAC at the front end of the modulator to completely eliminate the quantization noise folding back.

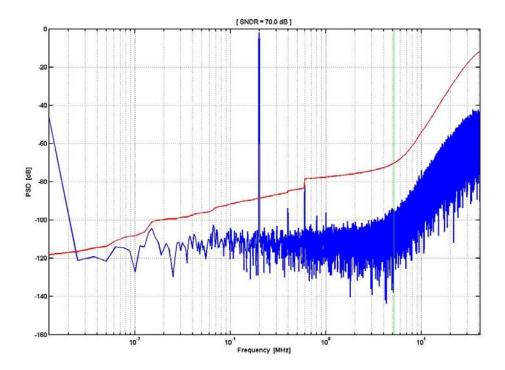

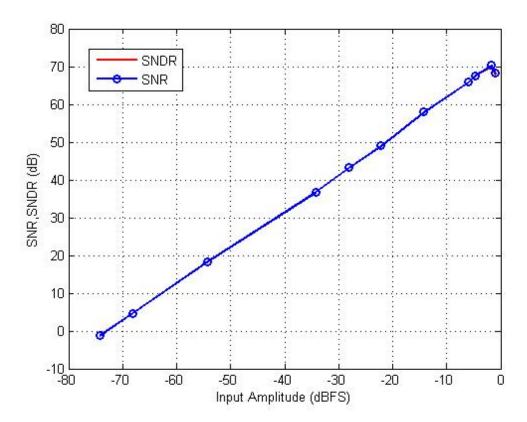

A 2+2 cascaded topology with 3-bit internal quantizer is used in this  $\Delta\Sigma$  modulator to adequately suppress the quantization noise while guaranteeing the loop stability. This  $\Delta\Sigma$  modulator was fabricated in a 90 nm digital CMOS process and achieves an SNDR of 70 dB within a 5 MHz signal bandwidth. The modulator occupies a silicon area of 0.5 mm<sup>2</sup> and consumes 10 mW with a supply voltage of 1.2 V.

©Copyright by Weilun Shen

July 8, 2010

All Rights Reserved

## Low-Power Double-Sampled Delta-Sigma Modulator For Broadband Applications

by

Weilun Shen

A DISSERTATION

submitted to

Oregon State University

in partial fulfillment of the requirement for the degree of

Doctor of Philosophy

Presented July 8, 2010

Commencement June 2011

| <u>Doctor of Philosophy</u> dissertation of <u>Weilun Shen</u> presented on <u>July 8, 2010.</u>                                                                                                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| APPROVED:                                                                                                                                                                                                 |

| Major Professor, representing Electrical and Computer Engineering                                                                                                                                         |

| Director of the School of Electrical Engineering and Computer Science                                                                                                                                     |

| Dean of the Graduate School                                                                                                                                                                               |

| I understand that my dissertation will become part of the permanent collection of Oregon State University libraries. My signature below authorizes release of my dissertation to any reader upon request. |

|                                                                                                                                                                                                           |

Weilun Shen, Author

#### **ACKNOWLEDGEMENTS**

Working towards a Ph.D degree is so similar to a long journey full of zigzags that one might very easily get lost. In our modern daily life, people traveling to an unfamiliar destination could rely on a global positioning system device to avoid any unnecessary detour. However in the pursuit of a Ph.D degree, I am positively sure I would have never achieved my goal without the help and guidance of some specific people.

First of all, I would like to express my deepest gratitude to my advisor, Professor Gabor Temes. I thank him for giving me the opportunity to be a research assistant in his group, for introducing me into the marvelous world of Delta-Sigma data converter and also for numerous advice and encouragement throughout my research work. More importantly his guidance strengthens my ability to perform research independently. For me it is really a distinct honor and highest privilege to work with him.

Then, my special appreciation goes to Professor Ken Martin at the University of Toronto. He provided generous funding to support my study and the research project. His insight into advanced integrated circuit design and his ability to keep me focus on the big picture greatly help me improve my design. Furthermore I am grateful to him for giving me a chance to join his newest company which will be another exciting venture. I am looking forward to working with him.

I feel so fortunate to get to know Dr. Afshin Razayee. He is such a nice guy that he will answer all my questions without losing patience. I truly enjoy our routine weekly

telephone meeting that lasted for almost two years when we had lots of technical discussion. I am looking forward to seeing him in Toronto soon.

I would like to thank Professor Un-Ku Moon, Professor Albrecht Jander, Professor Pavan Hanumolu, Professor Kagan Tumer and Professor Lewis Semprini for their serving on my graduate committee. I also wish to thank Professor Patrick Chiang for his kind help on setting up the process design kit.

The industry's fashion to do advance integrated circuits design is quite different from that of in academia. It is at Broadcom analog group, San Jose where I learned that kind of fashion to do circuit and layout design in very deep sub-micron CMOS process. I sincerely appreciate Dr. Tom Kwan for giving me an excellent opportunity to have a fruitful six-month internship in his group. With the help of Dr. Tom Kwan, Sumant Ranganathan, Dr. Ovidiu Bajdechi, Dr. Xinyu Yu, Dr. Mingcui Zhou and Victor Fong, my circuit and layout design ability is able to be brought to a completely new level.

I, hereby, would like to thank all my close friends and colleagues in analog group at Oregon State University. They are, without specific order in mind, Jingguang Wang, Kangmin Hu, Yan wang, Wenhuan Yu, Jinjin He, Zhenyong Zhang, Na An, Xiaoran Gao, Zhiqing Zhang, Xuefeng Chen, Tao Jiang, Changhui Hu, Tao Wang, Jiamin Lin, Ronghua Ni, Jinzhou Cao, Jeff Pai, Hurst Kuo, Jeong Seok Chae, Kyehyung Lee, Sanghyeon Lee, Rishi Gupta and Yoshio Nishida. We shared countless wonderful moments not only inside the EECS building but also during our spare time. Wish all of you the very best.

I am proud of being a Ph.D student at EECS at Oregon State University. We have one of the best EECS departments in the world because we have the best research faculties, the best students, the best hardware and the best environment to study. I benefited so much from those excellent courses which offered by EECS department. Besides, all EECS main office staffs are appreciated for their kind help through my whole Ph.D study.

### TABLE OF CONTENTS

|    |                                                                | <u>Page</u> |

|----|----------------------------------------------------------------|-------------|

| 1. | INTRODUCTION.                                                  | 1           |

|    | 1.1 Motivation.                                                | 1           |

|    | 1.1.1 ADCs for Broadband Applications                          | 2           |

|    | 1.1.2 Design Challenge in Advanced CMOS Technologies           | 3           |

|    | 1.2 Contributions of This Research                             | 6           |

|    | 1.3 Organization of the Dissertation.                          | 7           |

|    | References.                                                    | 8           |

| 2. | DOUBLE-SAMPLED $\Delta\Sigma$ MODULATOR WITH RELAXED TIMING    | 11          |

|    | 2.1. Introduction.                                             | 11          |

|    | 2.2. Timing Issues In Double-Sampled $\Delta\Sigma$ Modulators | 12          |

|    | 2.3. Proposed Double-Sampled $\Delta\Sigma$ Modulator Topology | 17          |

|    | 2.4. Simulation Results.                                       | 20          |

|    | 2.5. Summary                                                   | 22          |

|    | Reference                                                      | 23          |

| 3. | A NEW DWA REALIZATION WITH HARDWARE REDUCTION                  | 25          |

|    | 3.1. Introduction                                              | 25          |

|    | 3.2. A common DWA realization                                  | 26          |

|    | 3.3. Proposed DWA realization.                                 | 29          |

|    | 3.4. Summary                                                   | 33          |

|    | Deference                                                      | 2.4         |

## TABLE OF CONTENTS (Continued)

|    |                                                                               | <u>Page</u> |

|----|-------------------------------------------------------------------------------|-------------|

| 4. | CHARGE PUMP BASED SC INTEGRATOR                                               | 36          |

|    | 4.1. Introduction                                                             | 36          |

|    | 4.2. Charge Pump Based Switched Capacitor Integrator                          | 37          |

|    | 4.3. Parasitic Insensitive Charge Pump Based SC Integrator                    | 39          |

|    | 4.4. Low Distortion $\Delta\Sigma$ Modulator Employing CP Based SC Integrator | 46          |

|    | 4.5. Summary                                                                  | 51          |

|    | Reference.                                                                    | 52          |

| 5. | DESIGN OF A LOW POWER DOUBLE-SAMPLED $\Delta\Sigma$ MODULATOR                 | 53          |

|    | 5.1. $\Delta\Sigma$ Modulator Specifications                                  | 53          |

|    | 5.2. $\Delta\Sigma$ Modulator Architecture                                    | 55          |

|    | 5.3. Transistor Level Design.                                                 | 65          |

|    | 5.3.1. Double Sampling Technique.                                             | 65          |

|    | 5.3.2. Operational Amplifiers.                                                | 70          |

|    | 5.3.3. Switch Design.                                                         | 73          |

|    | 5.3.4. Quantizers and DWA                                                     | 74          |

|    | 5.3.5. Clock Generator.                                                       | 78          |

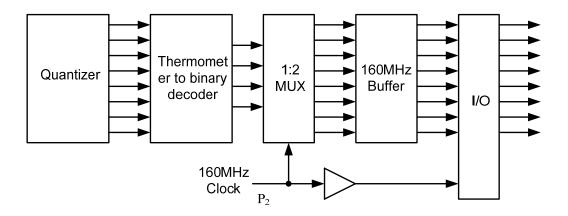

|    | 5.3.6. Interface Circuit.                                                     | 79          |

|    | 5.4. Summary                                                                  | 81          |

|    | Reference                                                                     | 82          |

| 6  | EYPERIMENTAL RESULTS                                                          | 87          |

## TABLE OF CONTENTS (Continued)

|    |                             | <u>Page</u> |

|----|-----------------------------|-------------|

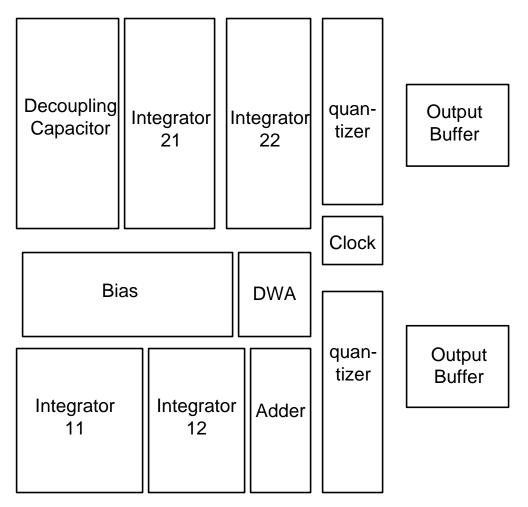

|    | 6.1. Layout Considerations. | 87          |

|    | 6.2. Test Set-up.           | 91          |

|    | 6.3. Measurement Results    | 94          |

|    | Reference.                  | 98          |

| 7. | CONCLUSIONS                 | 99          |

|    | 7.1. Summary                | 100         |

|    | 7.2. Future Work.           | 100         |

## LIST OF FIGURES

| <u>Figure</u>                                                                          | <u>Page</u> |

|----------------------------------------------------------------------------------------|-------------|

| 2.1 Single-ended version of a double-sampled SC integrator                             | 13          |

| 2.2 Double-sampled $\Delta\Sigma$ modulator with feed-forward path                     | 14          |

| 2.3 SC single-sampled $\Delta\Sigma$ modulator with relaxed feedback timing            | 15          |

| 2.4 Diagram of SC single-sampled $\Delta\Sigma$ modulator with relaxed feedback timing | 16          |

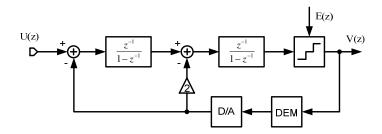

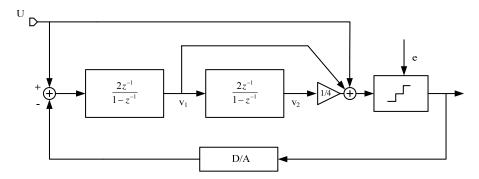

| 2.5 Double-sampled $\Delta\Sigma$ modulator with feedback topology                     | 17          |

| 2.6 Proposed double-sampled $\Delta\Sigma$ modulator with relaxed feedback timing      | 18          |

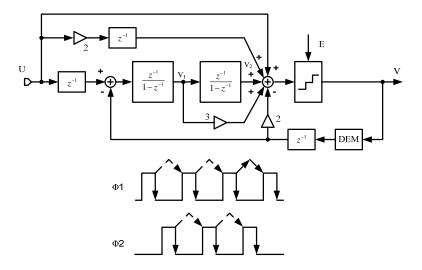

| 2.7 SC implementation of the first integrator                                          | 20          |

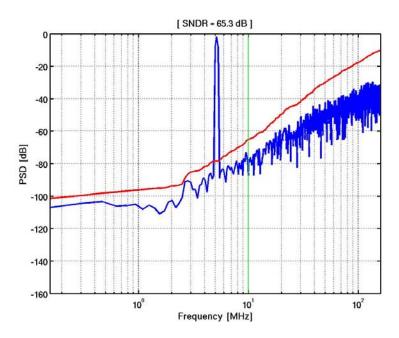

| 2.8 Simulated PSD of a second-order proposed double-sampled $\Delta\Sigma$ modulator.  | 21          |

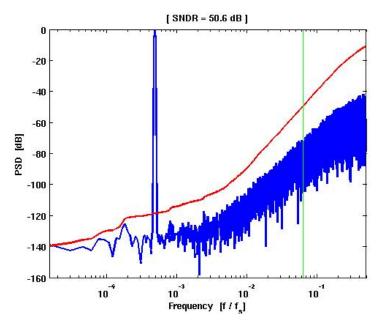

| 2.9 Simulated PSD of a second-order single-sampled $\Delta\Sigma$ modulator            | 22          |

| 3.1 $\Delta\Sigma$ modulator output spectrum with 0.1% DAC mismatch without DWA        | 26          |

| $3.2~\Delta\Sigma$ modulator output spectrum with 0.1% DAC mismatch with DWA           | 26          |

| 3.3 DWA algorithm                                                                      | 27          |

| 3.4 A second order 9-level $\Delta\Sigma$ modulator with DWA                           | 27          |

| 3.5 Detailed implementation of a DWA for a 9-level DAC                                 | 29          |

| 3.6 New DWA implementation compared with the conventional one                          | 30          |

| 3.7 A barrel shifter mapping DAC elements and quantizer output digital code            | 30          |

| 3.8 Complete mapping between DAC elements and quantizer digital output code            | 231         |

| 3.9 Block diagram of new DWA implementation (5-level DAC)                              | 32          |

| 4.1 CP based SC integrator                                                             | 38          |

| 4.2 Modified CP based SC integrator.                                                   | 39          |

## LIST OF FIGURES (Continued)

| <u>Figure</u> P                                                                            | <u>age</u> |

|--------------------------------------------------------------------------------------------|------------|

| 4.3 CP based SC integrator with parasitic capacitor                                        | 40         |

| 4.4 Fully differential CP based SC integrator with parasitic capacitor                     | 41         |

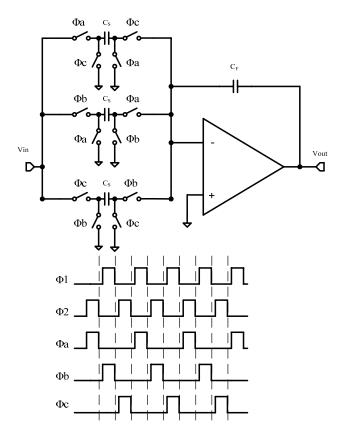

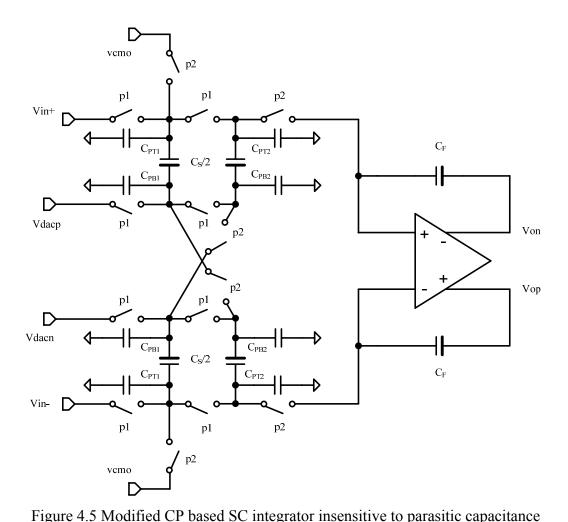

| 4.5 Modified CP based SC integrator insensitive to parasitic capacitor                     | 43         |

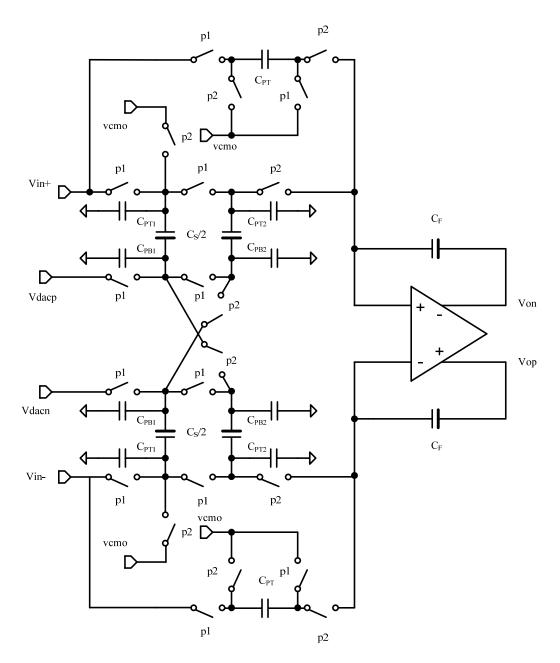

| 4.6 Modified CP based SC integrator insensitive to parasitic capacitor                     | 44         |

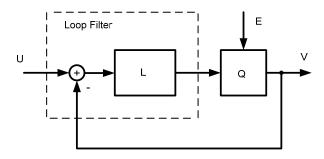

| 4.7 A general structure of a single-quantizer $\Delta\Sigma$ modulator                     | 47         |

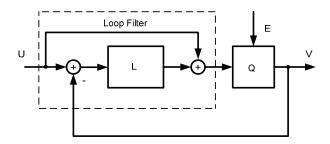

| 4.8 A general structure of a low-distortion feed-forward $\Delta\Sigma$ modulator          | 47         |

| 4.9 Proposed second order low-distortion $\Delta\Sigma$ modulator                          | 48         |

| 4.10 Switched level of the proposed second order low-distortion $\Delta\Sigma$ modulator   | 49         |

| 4.11 Simulated PSD of a $\Delta\Sigma$ modulator with modified CP based SC integrator      | 50         |

| 4.12 Simulated PSD of the first integrator output in the proposed $\Delta\Sigma$ modulator | 51         |

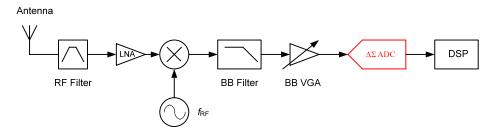

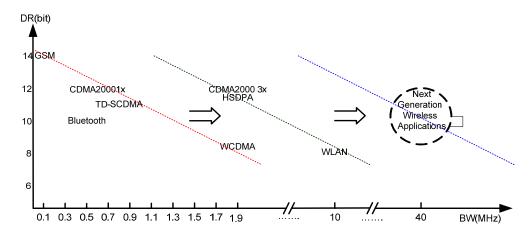

| 5.1 Block diagram of a direct conversion wireless transceiver                              | 54         |

| 5.2 Bandwidth requirements of ADCs in some wireless applications                           | 55         |

| 5.3 Block diagram of a conventional second order $\Delta\Sigma$ modulator                  | 59         |

| 5.4 Output spectrum of a conventional second order $\Delta\Sigma$ modulator                | 61         |

| 5.5 Block diagram of a low-distortion feed-forward second order $\Delta\Sigma$ modulator.  | 62         |

| 5.6 Output spectrum of a low-distortion feed-forward second order $\Delta\Sigma$ modulator | r63        |

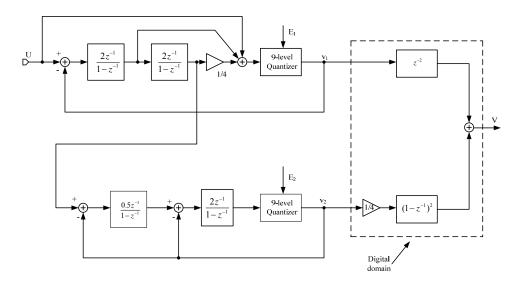

| 5.7 Block Diagram of a 2+2 $\Delta\Sigma$ cascaded modulator                               | 64         |

| 5.8 Fully floating switched capacitor integrator.                                          | 66         |

| 5.9 Double sampled integrator using capacitor reset.                                       | 68         |

| 5.10 Schematic of the two-stage opamp.                                                     | 72         |

## LIST OF FIGURES (Continued)

| <u>Figure</u>                                                         | Page |

|-----------------------------------------------------------------------|------|

| 5.11 Block diagram of a comparator.                                   | 75   |

| 5.12 Schematic of a pre-amplifier                                     | 76   |

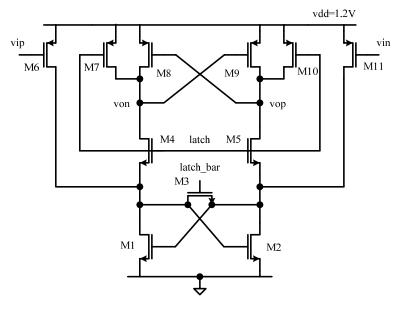

| 5.13 Schematic of the regeneration latch                              | 76   |

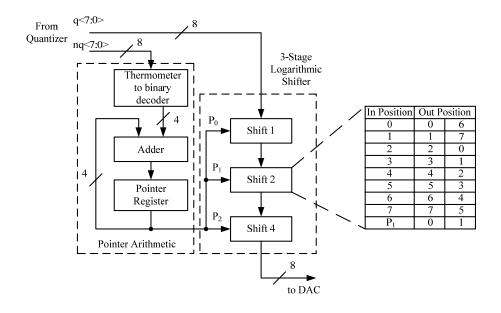

| 5.14 DWA implementation.                                              | 77   |

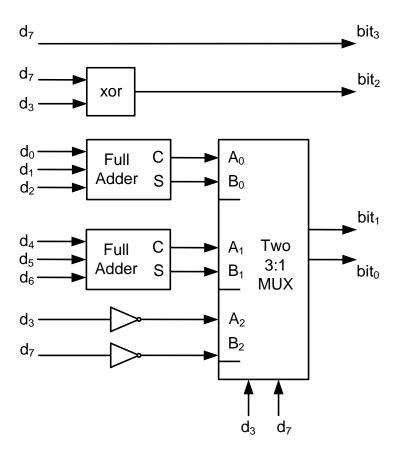

| 5.15 Thermometer to binary code converter                             | 78   |

| 5.16 Global clock generator                                           | 79   |

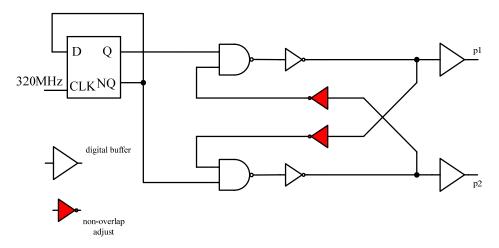

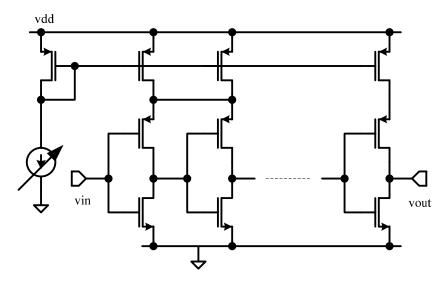

| 5.17 Delay cell in the global clock generator                         | 80   |

| 5.18 Block diagram of the interface circuit.                          | 80   |

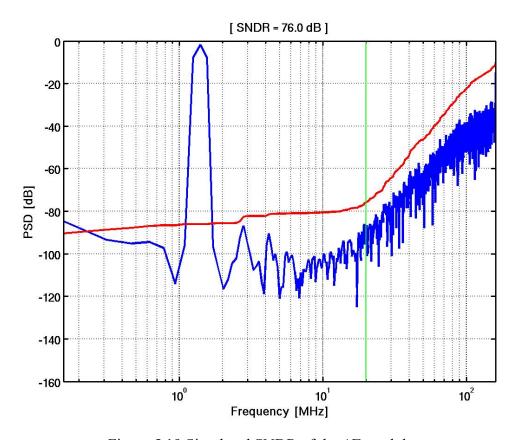

| 5.19 Simulated SNDR of the $\Delta\Sigma$ modulator                   | 81   |

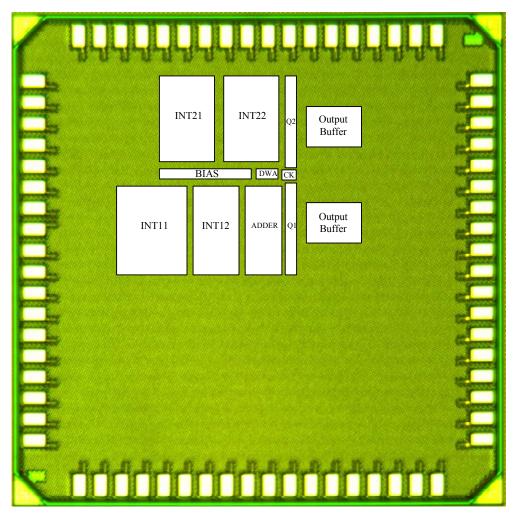

| 6.1 $\Delta\Sigma$ modulator floor plan                               | 88   |

| 6.2 Die photo                                                         | 90   |

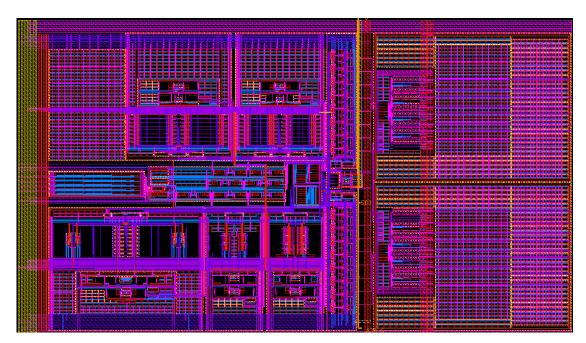

| 6.3 ΔΣ modulator Layout                                               | 91   |

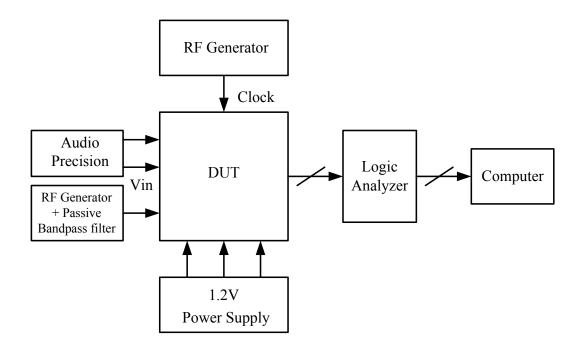

| $6.4 \Delta\Sigma$ modulator test board                               | 93   |

| 6.5 $\Delta\Sigma$ modulator test environment                         | 94   |

| 6.6 Measured output spectrum of the designed $\Delta\Sigma$ modulator | 95   |

| 6.7 Measured SNR/SNDR with different input levels.                    | 96   |

### LIST OF TABLES

| <u>Table</u>                                                           | <u>Page</u> |

|------------------------------------------------------------------------|-------------|

| 3.1 Complete mapping between DAC elements and quantizer digital output | code31      |

| 3.2 Relationship of the pointer arithmetic                             | 33          |

| 6.1 Measured ΔΣ modulator Performance Summary                          | 97          |

#### **DEDICATION**

Here, I would like to express my deepest gratitude to my family. My wife, Linling made a tremendous sacrifice during my Ph.D study. This work would have never been possible without her love and patience. I thank my mother-in-law for her great help to my family. I also wish my little boy Kenneth the best and grow with good health and brightness.

# Low-Power Double-Sampled Delta-Sigma Modulator for Broadband Applications

#### **CHAPTER 1. INTRODUCTION**

#### 1.1. Motivation

Every minute, ten hours of video is uploaded to YouTube. With hundreds of millions of videos watched and hundreds of thousands of videos uploaded every day, YouTube has emphasized an expectation among internet users: speed.

Watching films at home is one of the major recreational events in every family. Pursing high quality makes the video carriers evolved from cassettes at about twenty years ago to blue-ray DVDs nowadays. Hence, high-definition video emphasized an expectation among consumers: high performance.

It is not uncommon to see people surfing internet, receive and send their emails through their mobile phones. Battery-powered mobile devices can only be used for a limited time until its next recharge. So with more and more functionalities integrated on a single device, how long a particular device can work heavily depends on the power consumed by its constituent chips. As a result mobile devices emphasized an expectation among consumers: low power.

The price factors play a very important role in the consumer electronics market because people always want to pay less out of pocket. As a consequence, developing a new product becomes mostly cost-driven. Market emphasized an expectation among consumers: low cost.

With everything in nature stubbornly remains analog such as the video we watch and the music we listen to, analog to digital and digital to analog data converters really become a critical building block in a complicated system design. In this thesis, we describe some new techniques and the design of a delta-sigma ( $\Delta\Sigma$ ) analog to digital data converter which fulfills the aforementioned expectations: speed, high performance, low power and low cost.

#### 1.1.1. ADCs for Broadband Applications

With transistors becoming smaller and smaller, chips really become a system with both analog and digital portions inside. The fact that analog to digital data converters (ADCs) form a bridge between the two portions indicates that ADCs might become a performance bottleneck in such systems. Modern broadband communications also necessitate high speed ADCs with good resolution and low power consumption. For example, digital TV tuner requires baseband ADC to process a signal bandwidth of 8 MHz with a 13-bit resolution while in very-high-bitrate digital subscriber line (VDSL) a 17 MHz signal bandwidth ADC with 12-bit resolution is needed. Traditionally such high speed ADCs were dominated by Nyquist rate ADCs. However Nyquist rate ADCs with high resolution mandate precision analog components such as precise capacitor matching and very high gain operational amplifiers (opamps). Unfortunately, brute-force design effort to achieve high resolution for a Nyquist rate ADC in a deep sub-micron CMOS process tends to be extremely difficult. One way to improve the

accuracy of Nyquist rate ADCs is to utilize digital calibration [1] [2]. This method is very promising but adds complexity and design period.

Delta-Sigma ( $\Delta\Sigma$ ) ADCs have become more and more popular for broadband communication applications in the past couple of years. Modern advanced CMOS technology allows  $\Delta\Sigma$  ADCs to be clocked at hundreds of mega hertz with reasonable power consumption, therefore input signal bandwidth can be extended to tens of MHz. Compared to Nyquist rate ADCs;  $\Delta\Sigma$  ADCs have the ability to achieve high resolution with relaxed component matching and opamps' gain. The fact that the design of the preceding anti-aliasing filter is relaxed is another benefit of using a  $\Delta\Sigma$  ADC.  $\Delta\Sigma$  ADCs need a digital decimation filter to remove the out-of-band quantization noise and down-sample the digital bit stream to Nyquist rate. This is why, generally speaking, a  $\Delta\Sigma$  ADC trades accuracy with area as well. However this area overhead reduces dramatically with the aggressive scaling of the CMOS process.

Designing a broadband low power high resolution  $\Delta\Sigma$  ADC requires new techniques at both architectural and circuit level. So it becomes a really hot topic in recent years and is expected to continue in the next couple years [3] [4] [5] [6] [7] [8] [9] [10].

#### 1.1.2. Design Challenge in Advanced CMOS Technologies

Analog designs in the advanced CMOS technology nodes like 90nm or below are facing a great deal of challenges [11].

A. Device physical scaling.

The most prevalent phenomenon in advanced processes is that devices continue to scale down. This results in higher transistors' intrinsic cutoff frequency but higher leakage current since the gate oxide thickness has to be thinner to accommodate the threshold voltage reduction. Large leakage current can be very problematic in circuit design. For instance, in mobile applications, the leakage current will increase the power consumption while the circuits are in stand-by mode. To overcome this problem, low power (LP) process is always chosen for leakage sensitive applications. However, transistors in an LP process are much slower than their counterparts in a general process. Therefore it is quite difficult to maintain the same performance. Another issue from the device scaling is the parasitic wiring capacitance makes up a high percentage of the overall capacitance in a circuit. It is not uncommon to see a considerable amount of speed degradation in a post-layout simulation. A possible solution is to intentionally add some capacitance at the pre-layout simulation. This solution nonetheless requires good design experiences.

#### B. Device matching.

In analog designs, devices matching properties are always of top interest mainly because they severely limit performances. Taking ADC design as an example, device matching properties can influence linearity and SNR (signal-to-noise ratio) directly while power consumption and area will be affected indirectly since an effective way to improve matching is to increase the device sizes. In advanced CMOS process, device matching becomes worse and matching oriented design tends to be complicated. Statistic analysis such as Monte-Carlo simulation is mandatory. A popular and

effective measure is to utilize digital calibration method [12]. It should be noted that the calibration mechanism to reduce offset can help lower the flicker noise at the same time.

#### C. Process variation, reliability and stress.

Advanced process also shows huge variation. For instance, a MOS transistor threshold voltage will vary from 200 mV to 500 mV over process and temperature in a 65 nm LP process. In a mass production design, simulation has to be done in hundreds or even thousands of corners to guarantee product yield. Maintaining performance in such a way is hard and oftentimes will drive a designer desperate.

Reliability is another important concern in a mass product design to ensure a product's lifetime. Voltage of every node in the circuit must not exceed the foundry specified voltage limits except for a very short amount of time during start-up. Electromigration simulation should also be performed after a circuit layout to check whether or not a metal wiring carries higher current density than the foundry specified value.

In process node 90 nm or below, transistors will "feel" stressed under a certain layout pattern. Two most prevalent phenomena are shallow trench isolation (STI) and well proximity effect (WPE). Stressed transistors usually have higher threshold voltage, lower transconductance and different model parameters compared to unstressed transistors resulting performance degradation and offset. Fortunately these phenomena can be easily tackled by careful layout.

#### D. Reduced supply voltage

. Advanced CMOS processes use low supply voltage for core thin oxide transistors. Low voltage poses unprecedented challenges for analog design. Telescopic amplifier topology becomes hardly practical without some special techniques. Design of MOS switches in a switched-capacitor circuit is affected badly as well. Appropriate system architecture together with novel design techniques and circuit innovation is the key to moving the analog design into the low voltage era.

#### E. Very low transistor intrinsic gain

Operational amplifiers are so critical that they can be seen almost everywhere in analog designs. DC gain of opamps determines the quality of the virtual ground in an opamp feedback configuration which affects the linearity directly. However, transistors' intrinsic gain is so poor that the DC gain of a simple two-stage opamp barely reaches 40 dB. At the same time, reduced power supply limits the effectiveness of trying to improve DC gain through traditional methods such as cascoding. Therefore we have to explore architectures which can tolerate low gain opamps or even operate without opamps.

The main purpose of this thesis is to develop novel system architectures and new circuit implementations to overcome the aforementioned design challenges. We will take the design of a broadband low power  $\Delta\Sigma$  ADC as a platform to address these issues.

#### 1.2. CONTRIBUTIONS OF THIS RESEARCH

The major contributions of this research can be summarized as follows:

- [1] A novel double-sampled  $\Delta\Sigma$  modulator is proposed to relax the critical feedback timing issue. In this new modulator topology, the speed of quantizer and dynamic element matching (DEM) logic can be greatly reduced.

- [2] A new Data Weighted Averaging (DWA) realization is proposed to reduce the hardware complexity.

- [3] A cross-coupling technique is proposed to eliminate parasitic capacitor effect in a charge-pump (CP) based switched-capacitor (SC) integrator. Design methodologies are introduced to incorporate a modified CP based SC integrator into a low-distortion  $\Delta\Sigma$  modulator.

- [4] A broadband low power switched capacitor  $\Delta\Sigma$  modulator is designed and demonstrated in a 90 nm digital CMOS process. Through strategic design methodology at system and transistor level, this modulator achieves good performance and low power consumption.

#### 1.3. Organization of the Dissertation

This thesis mainly deals with the design of a broadband low power  $\Delta\Sigma$  modulator in advanced deep sub-micron CMOS process and techniques on how to improve the modulator performance. Both system level and circuit level designs are covered. Here is how this thesis is organized:

Chapter 2 introduces a novel double-sampled  $\Delta\Sigma$  modulator topology to relax the critical feedback timing issue. The speed of quantizer and the DEM logic can be greatly reduced to save power and improve the design robustness.

Chapter 3 presents a new Date Weighted Averaging (DWA) realization. Compared to the popular implementation, the proposed one has less hardware complexity.

Chapter 4 covers the charge-pump (CP) based switched-capacitor (SC) integrator. A cross-coupling technique is proposed to eliminate parasitic capacitor effect in a CP based SC integrator. Also, design methodologies are introduced to incorporate a modified CP based SC integrator into a low-distortion  $\Delta\Sigma$  modulator.

Chapter 5 focuses on the design of a low power double-sampled broadband  $\Delta\Sigma$  modulator. Solutions to effectively design analog building blocks such as opamps, switches and comparators in low voltage, deep sub-micron CMOS process environment are presented.

Chapter 6 discusses the modulator floor plan, layout techniques and the modulator test results.

Chapter 7 summarizes the thesis and discusses some future work.

#### References

- [1] H. Van de Vel, B.A.J. Buter, H. van der Ploeg, M. Vertregt, G.J.G.M. Geelen and E.J.F. Paulus, "A 1.2-V 250-mW 14-b 100-MS/s Digitally Calibrated Pipeline ADC in 90-nm CMOS," *IEEE J. Solid-State Circuits*, vol. 44, pp. 1047-1056, April. 2009.

- [2] S. Ray and B. Song, "A 13-b Linear 40-MS/s Pipelined ADC With Self-Configured Capacitor Matching," *IEEE J. Solid-State Circuits*, vol. 42, pp. 463-474, Mar. 2007.

- [3] G. Mitteregger, C. Ebner, S. Mechnig, T. Blon, C. Holuigue and E. Romani, "A 20-mW 640-MHz CMOS Continuous-Time ΣΔ ADC with 20-MHz Signal Bandwidth, 80-dB Dynamic Range and 12-bit ENOB," *IEEE J. Solid-State Circuits*, vol. 41, pp. 2641-2649, Dec. 2006.

- [4] P. Balmelli and Q. Huang, "A 14-b 25 MS/s 200 mW ΣΔ Modulator in 0.18-μm CMOS," *IEEE J. Solid-State Circuits*, vol. 39, pp. 2161-2169, Dec. 2004.

- [5] X. Chen, Y. Wang, Y. Fujimoto, P. L. Re, Y. Kanazawa, J. Steensgaard and G. Temes, "A 18 mW CT ΔΣ Modulator with 25 MHz Bandwidth for Next Generation Wireless Applications," in CICC Dig. Tech. Papers, Sept. 2007, pp. 73-76.

- [6] S. Paton, A. Giandomenico, L. Hernandez, A. Wiesbauer, T. Potscher and M. Clara, "A 70-mW 300-MHz CMOS Continuous-Time ΣΔ ADC with 15-MHz Bandwidth and 11 Bits of Resolution," *IEEE J. Solid-State Circuits*, vol. 39, pp. 1056-1063, July. 2004.

- [7] T. C. Caldwell and D. A. Johns, "A Time-Interleaved Continuous-Time ΔΣ Modulator with 20-MHz Signal Bandwidth," *IEEE J. Solid-State Circuits*, vol. 41, pp. 1578-1588, July. 2006.

- [8] T. Christen, T. Burger and Q. Huang, "A 0.13  $\mu m$  CMOS EDGE/UMTS/WLAN Tri-Mode  $\Delta\Sigma$  ADC with -92 dB THD," in ISSCC Dig. Tech. Papers, Feb. 2007, pp. 240-241.

- [9] P. Malla, H. Lakdawala, K. kornegay and K. Soumyanath, "A 28 mW Spectrum-Sensing Reconfigurable 20 MHz 72-dB-SNR 70dB-SNDR ΔΣ ADC for 802.11n/WiMAX Receivers," in ISSCC Dig. Tech. Papers, Feb. 2008, pp. 496-497.

- [10] Y. Fujimoto, Y. Kanazawa, P. Lo Re and M. Miyamoto, "An 80/100MS/s 76.3/70.1dB SNDR ΔΣ ADC for Digital TV Receivers," in ISSCC Dig. Tech. Papers, Feb. 2006, pp. 76-77.

- [11] L. Lewyn, T. Ytterdal, C. Wulff and K. Martin, "Analog Circuit Design in Nanoscale CMOS Technologies," *Proceedings of the IEEE*, vol. 97, pp. 1047-1056, October. 2009.

- [12] Chun-Ying Chen, M.Q Le and Kwang Young Kim, "A Low Power 6-bit Flash ADC With Reference Voltage and Common-Mode Calibration," *IEEE J. Solid-State Circuits*, vol. 44, pp. 1687-1714, April. 2009.

## CHAPTER 2. DOUBLE-SAMPLED ΔΣ MODULATER WITH RELAXED TIMING

A new double-sampled  $\Delta\Sigma$  modulator topology is proposed to relax the critical timing constraints in the modulator feedback path, thus the speed requirement of the quantizer and DEM logic can be greatly reduced. To verify the proposed modulator topology, a second-order double-sampled delta-sigma modulator was designed and simulated.

#### 2.1. Introduction

With the continuing down scaling of CMOS technology, delta-sigma ( $\Delta\Sigma$ ) analog-to-digital converters are becoming more and more popular in wideband applications such as wireless communication systems, high definition television, medical image, etc. There are two possible realizations of a delta-sigma modulator. One is based on discrete-time (DT) switched capacitor (SC) circuitry which traditionally was used to achieve very high resolution within low signal bandwidth. The other one employs continuous-time (CT) circuitry. Due to the exponential settling nature of its internal integrators, the maximum sampling frequency of a DT  $\Delta\Sigma$  modulator is a lot lower than its CT counterparts especially when low power consumption is required. As a consequence, most of the recent  $\Delta\Sigma$  ADCs incorporate CT modulators when the signal bandwidth goes beyond 10 MHz or more [1] [2]. However, compared to CT modulators, DT modulators do offer several advantages: 1. The performance is less

sensitive to clock jitter; 2. Signal transfer function (STF) and noise transfer function (NTF) rely on capacitor matching which can be made very accurate in modern CMOS technology; 3. It is very easy to scale the sampling frequency which makes the multistandard applications possible; 4. Design methodology for a DT modulator is well established. Despite the aforementioned advantages, efforts must be taken to extend the signal bandwidth of a DT modulator in a low power design. Double sampling is a very powerful technique to achieve an effective sampling frequency that is twice the actual modulator clock frequency. Since the two clock phases are no longer distinguishable, the quantization operation is performed primarily during the nonoverlapping times of the clocks. This situation gets even worse with the use of a multibit quantizer with dynamic element matching (DEM) algorithms. In order to make the modulator functional, the required speed for the quantizer and DEM logic should be much higher than the clock frequency of a  $\Delta\Sigma$  modulator. In this chapter, a novel double-sampled  $\Delta\Sigma$  modulator topology is proposed to solve this critical timing constraint.

#### 2.2. Timing Issues In Double-Sampled $\Delta\Sigma$ Modulators

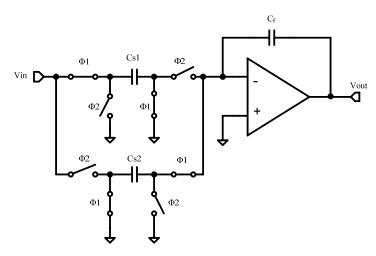

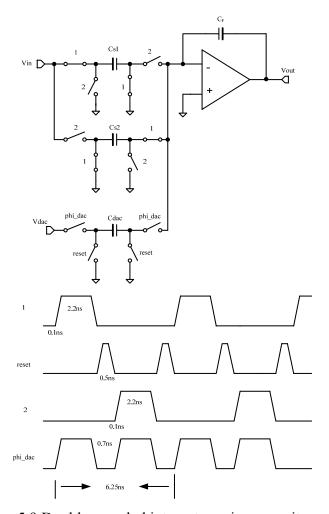

Fig. 2.1 illustrates a single-ended version of a double-sampled SC integrator that is controlled by two non-overlapping clock phases. During phase  $\Phi$ 1, Cs1 samples the input and Cs2 transfers the previously sampled charge to C<sub>F</sub>. During phase  $\Phi$ 2, Cs1 transfers its charge to C<sub>F</sub> and Cs2 samples the input. As a result, the output of the integrator is updated during both phases. The effective sampling frequency is twice the actual clock frequency. Note that double-sampling technique does not put any extra

requirements for opamp settling time.

Double-sampling is definitely desired when a DT SC  $\Delta\Sigma$  modulator processes wide bandwidth input signal. For instance, with an input signal bandwidth of 10 MHz and an oversampling ratio (OSR) of 16, instead of having a sampling frequency of 320 MHz, only 160 MHz clock frequency can be used in a double-sampled SC  $\Delta\Sigma$  modulator. Therefore, significant power savings can be anticipated.

Figure 2.1 Single-ended version of a double-sampled SC integrator

However, double sampling has several disadvantages that limit its applications. One of them is caused by the capacitor mismatch in the feedback DAC. This problem can be tackled by either using a fully floating differential SC integrator [3] or its modified version [4]. Here, this problem is not discussed and for the feedback DAC, perfectly matched capacitors are assumed during phase  $\Phi$ 1 and phase  $\Phi$ 2.

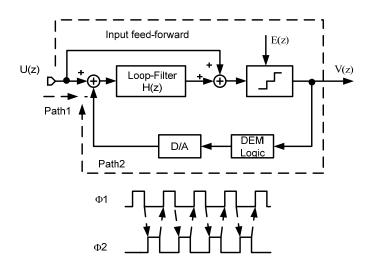

The other major disadvantage is the feedback timing constraints. Fig. 2.2 shows a double-sampled SC  $\Delta\Sigma$  modulator with a direct feed-forward path [5]. Currently this topology is widely employed in the design of wideband, low OSR SC  $\Delta\Sigma$  modulators.

Because of the direct input signal feed-forward, the modulator has a unity STF. The loop filter has to process the quantization noise only. The removal of the input signal component reduces the voltage swing of the loop filter internal nodes allowing efficient opamp configurations. In addition, distortion becomes independent of the input signal resulting in an improvement of the modulator linearity.

Figure 2.2 Double-sampled  $\Delta\Sigma$  modulator with feed-forward path

In Fig. 2.2, the input signal is sampled on the corresponding sampling capacitors at the end of each clock phase  $\Phi 1$  and phase  $\Phi 2$  which is labeled as Path1. Meanwhile at the end of  $\Phi 1$  and  $\Phi 2$ , the input signal and the output of the loop filter should be added. The result of this summation is then quantized and fed back to the input node of the loop filter to perform a subtraction with the input signal. These operations are labeled as Path2. Only when the delays of Path1 and Path2 are matched can the input signal be entirely cancelled in front of the loop filter. Due to double sampling, quantization and feedback operations must be done within the non-overlapping times

between clock phase  $\Phi 1$  and  $\Phi 2$ . In wideband applications, low OSR is always chosen in order to save power consumption. Therefore a multi-bit quantizer is introduced to improve the resolution of a  $\Delta \Sigma$  modulator. Under this circumstance, the multi-bit feedback DAC located at the input of the loop filter has to be linearized by some sorts of DEM logic so as to not degrade the overall performance. Data weighted averaging (DWA) is a popular way to linearize the DAC. A well designed DWA only adds a shifter in the modulator feedback path while the pointer calculation can be done outside the loop.

Figure 2.3 SC single-sampling  $\Delta\Sigma$  modulator with relaxed feedback timing

Even so, the DWA logic will add extra delay in the feedback path. After the design is finished and laid out, this delay will be larger with the introduced parasitic capacitance. If the overall delay is longer than the non-overlapping time, the

performance of a  $\Delta\Sigma$  modulator will be degraded, or it will not work at all. One simple solution is to increase the non-overlapping time. However it reduces the sampling and integration time. On other words, opamps in the loop filter need to be faster and consume more power.

In [6], a  $\Delta\Sigma$  modulator employs two sets of capacitors to sample the input signal. The block diagram of the  $\Delta\Sigma$  modulator is illustrated in Fig. 2.3, and Fig. 2.4 gives a detailed single-ended switched level diagram. This modulator topology allows inserting a half-cycle delay in both path1 and path2, thus half of the clock period can be allocated to the quantization and DEM logic. Note that the first integrator actually becomes a half-cycle delayed integrator. This method is very useful in the single-sampled  $\Delta\Sigma$  modulators. Unfortunately there are no half-cycle delayed integrators in a double-sampled  $\Delta\Sigma$  modulator. Therefore it is not straightforward to incorporate this technique in a double-sampled  $\Delta\Sigma$  modulator.

Figure 2.4 Diagram of SC single-sampled  $\Delta\Sigma$  modulator with relaxed feedback timing (shown single-ended for simplicity)

It is also worthwhile to mention that a double-sampled  $\Delta\Sigma$  modulator with feedback topology shown in Fig. 2.5 also suffers from feedback timing constraints: DEM logic and the quantization still have to be done during the non-overlapping times of the clock. A single-sampled  $\Delta\Sigma$  modulator with the same block diagram, however, has a half clock period to perform quantization and DEM logic.

Figure 2.5 Double-sampled  $\Delta\Sigma$  modulator with feedback topology

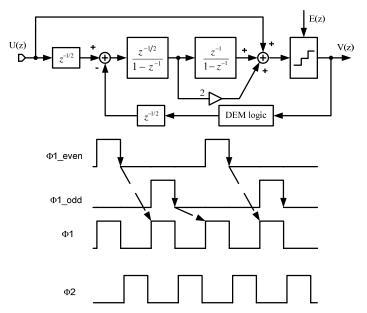

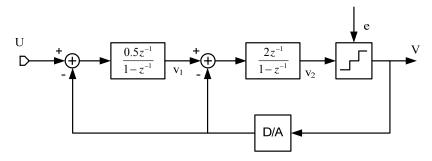

#### 2.3. Proposed Double-Sampled Delta-Sigma Modulator

A new double-sampled  $\Delta\Sigma$  modulator topology is proposed to relax the critical timing constraints [7]. This topology is based on the direct feed-forward topology in [5]. A second-order example is shown in Fig. 2.6. A full-cycle delay is inserted at both the input sampling path and the feedback path, thus a half-cycle clock period can be allocated to the quantization and DEM logic (note that in a double-sampled  $\Delta\Sigma$  modulator, a half clock period is equivalent to an effective sampling period). In most cases, this half clock period is long enough for the quantization and DEM logic. This results in a relaxed speed requirement and robust operation. However the STF of the modulator is no longer equal to 1 and the low distortion property is lost. In order to maintain the unity STF, two full-cycle delayed branches can be added. One is from

Figure 2.6 Proposed double-sampled  $\Delta\Sigma$  modulator with relaxed feedback timing

modulator input, while the other is from modulator output. Both are connected to the summing node in front of the quantizer. Since there is already a summing node in the feed-forward topology, these two branches add only minor hardware complexity.

Linearized analysis of the system in Fig. 2.6 gives:

$$STF = \frac{V(z)}{U(z)} = 1 \tag{2.1}$$

$$NTF = \frac{V(z)}{E(z)} = (1 - z^{-1})^2$$

(2.2)

$$V_1(z) = -z^{-2}(1-z^{-1})E(z)$$

(2.3)

$$V_2(z) = -z^{-3}E(z)$$

(2.4)

where E(z) is the quantization noise from the internal quantizer. The unity STF is still maintained, while the NTF becomes a second-order pure differentiator high-pass function. The first opamp output v1 contains shaped quantization noise, and the second opamp output v2 contains only the delayed version of the quantization noise As a result, the output swing and linearity requirements of the opamps can be relaxed. Hence, the proposed modulator topology achieves the low-distortion property and relaxes the feedback timing constraints simultaneously.

The key operation of the proposed modulator topology can be expressed as follows: the input signal is sampled at the end of  $\Phi 1$  (or  $\Phi 2$ ), then held for the entire  $\Phi 2$  (or  $\Phi 1$ ) and processed at the next  $\Phi 1$  (or  $\Phi 2$ ). During the holding phase, the quantization and DEM logic can be operated. This process implies that the sampling capacitor is busy for three clock phases. But input signal must be sampled at the end of both  $\Phi 1$  and  $\Phi 2$  in a double-sampled  $\Delta \Sigma$  modulator. So, instead of having two sets of sampling capacitors, in the proposed modulator topology, three sets of sampling capacitors should be used. The penalty for the proposed solution is a slightly increase in the chip area. An SC implementation for the first integrator in proposed modulator is shown in Fig.2.7 in the single-ended form for simplicity. Every sampling branch utilizes dedicated clock phases, shown as  $\Phi a$ ,  $\Phi b$  and  $\Phi c$ , which can be generated from  $\Phi 1$  and  $\Phi 2$ .

Figure 2.7 SC implementation of the first integrator

It is well known that double-sampled modulators are sensitive to the capacitor mismatch in the feedback DAC. This problem can be solved by using a modified fully-floating differential SC integrator [4]. In this design, the capacitors for the input sampling and the feedback DAC are separated to avoid the quantization noise folding back to the signal band.

#### 2.4. Simulation Results

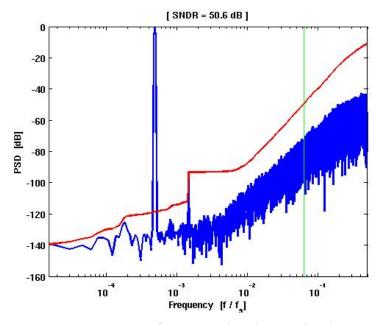

To verify the effectiveness of the proposed modulator topology shown in Fig.2.6, the transient behavior of a second order double-sampled SC  $\Delta\Sigma$  modulator circuit was

simulated in Cadence Spectre simulator. The opamps were represented by macro models with finite gains (50dB). The output digital bits were sampled and processed in MATLAB.

Figure 2.8 Simulated PSD of a second-order proposed double-sampled  $\Delta\Sigma$  modulator.

Assume a 10 MHz signal bandwidth, an oversampling ratio of 16, and a 3-bit quantizer. Because of the double sampling, the actual modulator clock frequency is 160 MHz. Fig. 2.8 shows the simulated output spectrum of the proposed second-order double-sampled  $\Delta\Sigma$  modulator with a -2 dBFS input signal. The simulated SNDR is 65.3 dB which does not include thermal noise and other circuit non-ideal effects.

As a comparison between the double-sampled  $\Delta\Sigma$  modulator and single-sampled  $\Delta\Sigma$  modulator, the second order  $\Delta\Sigma$  modulator shown in Fig. 2.6 was also simulated in the single-sampling mode with the clock frequency of 160 MHz. This clock frequency

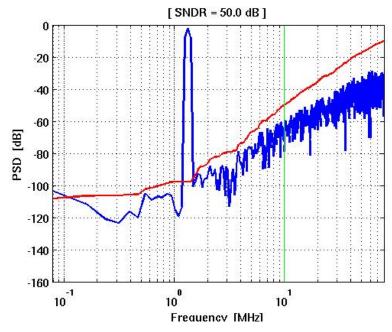

leads to the OSR of only 8 for a 10 MHz signal bandwidth. Fig.2.9 shows the simulated output spectrum of the single-sampled second order  $\Delta\Sigma$  modulator with a -2 dBFS input signal. The simulated SNDR is 50.0 dB, which is about 15 dB lower than that of a double-sampled second order  $\Delta\Sigma$  modulator. In order to achieve the same SQNR, a single-sampled second order  $\Delta\Sigma$  modulator must be clocked at 320 MHz. However this will inevitably increase the overall modulator power consumption.

Figure 2.9 Simulated PSD of a second-order single-sampled  $\Delta\Sigma$  modulator

# 2.5. Summary

A new double-sampled delta-sigma modulator topology was proposed to solve the feedback critical timing constraints. The speed requirement of the quantizer and DEM logic can be greatly relaxed. This new modulator topology also shows a unity signal transfer function, and the loop filter processes the quantization noise only. The above

features make it a good candidate for wideband, high linearity and low power applications.

#### References

- [1] G. Mitteregger, C. Ebner, S. Mechnig, T. Blon, C. Holuigue and E. Romani, "A 20-mW 640-MHz CMOS Continuous-Time ΣΔ ADC with 20-MHz Signal Bandwidth, 80-dB Dynamic Range and 12-bit ENOB," *IEEE J. Solid-State Circuits*, vol. 41, pp. 2641-2649, Dec. 2006.

- [2] X. Chen, Y. Wang, Y. Fujimoto, P. L. Re, Y. Kanazawa, J. Steensgaard and G. Temes, "A 18mW CT ΔΣ Modulator with 25MHz Bandwidth for Next Generation Wireless Applications," in CICC Dig. Tech. Papers, Sept. 2007, pp. 73-76.

- [3] D. Senderowicz, G. Nicollini, S. Pernici, A. Nagari, P. Confalonieri and C. Dallavalle, "Low voltage double-sampled ΣΔ converters," *IEEE J. Solid-State Circuits*, vol. 32, pp. 1907-1919, Dec. 1997.

- [4] K.Lee, J. Chae and G.C.Temes, "Efficient Fully-Floating Double-Sampling Integrator for  $\Delta\Sigma$  ADCs," *IEEE International Symposium on Circuits and Systems* (*ISCAS*), 2008.

- [5] J. Silva, U. Moon, J.Steensgaard and G.C.Temes," Wideband low- distortion delta-sigma ADC topology," Electronics Letters, vol.37, no.12, pp.737-738, Jun.2001.

- [6] Y. Fujimoto, Y. Kanazawa, P. Lo Re and M. Miyamoto, "An 80/100 MS/s 76.3/70.1 dB SNDR ΔΣ ADC for Digital TV Receivers," in ISSCC Dig. Tech. Papers, Feb. 2006, pp. 76-77.

[7] W. Shen, and G.C.Temes," Double-sampled  $\Delta\Sigma$  modulator with relaxed feedback timing," Electronics Letters, vol.45, no.17, pp.875-876, Aug.2009.

# CHAPTER 3. A NEW DWA REALIZATION WITH HARDWARE REDUCTION

This chapter presents a new Data Weighted Averaging (DWA) realization. Compared to the popular implementation the proposed one has less hardware consumption.

#### 3.1. Introduction

Delta-sigma ( $\Delta\Sigma$ ) modulators that process wide bandwidth input signals often utilize a multi-bit internal quantizer. The effect of this multi-bit quantizer to a  $\Delta\Sigma$  modulator is two-fold. On one hand it improves the modulator stability. On the other hand, modulator SQNR will improve by 6 dB every time the quantizer doubles its resolution. However, the feedback DAC, especially the one at the modulator input must be linearized to maintain the overall modulator performance. Among various linearization methods, data-weighted-averaging (DWA) [1] is widely deployed at both research community and industry due largely to its simplicity and effectiveness.

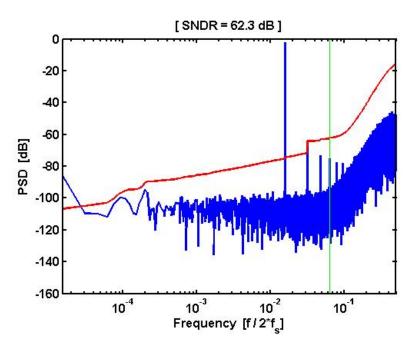

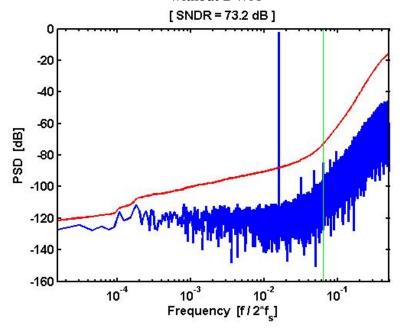

The effectiveness of DWA to a  $\Delta\Sigma$  modulator can be seen through behavioral level simulation in Matlab. In simulation, a randomly distributed 0.1% DAC unit element mismatch is added in the first DAC of a 12-bit  $\Delta\Sigma$  modulator. Fig.3.1 shows the output spectrum of the modulator with the DWA disabled. As expected, the modulator SNDR drops to 62.3 dB. Fig.3.2 shows the output spectrum of the modulator with the DWA enabled. Now modulator SNDR is brought back to 73.2 dB.

# 3.2. A common DWA realization

Figure 3.1  $\Delta\Sigma$  modulator output spectrum with 0.1% DAC mismatch without DWA

Figure 3.2  $\Delta\Sigma$  modulator output spectrum with 0.1% DAC mismatch with DWA

A general description of the DWA algorithm with a 9-level DAC is illustrated in Fig.3.3.

The DWA algorithm is simple and straightforward to understand. The DAC unit elements are in a rotated fashion. Each time the DAC elements are to be selected from the first unused element in the previous DAC operation. By performing rotation in such a way for a long time will result a first-order noise shaping for the DAC unit element error [2].

Figure 3.3 DWA algorithm

Figure 3.4 A second order 9-level  $\Delta\Sigma$  modulator with DWA

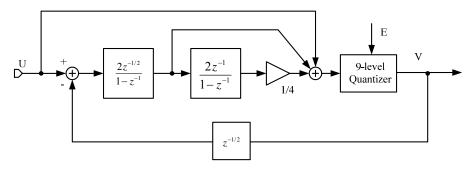

A second order  $\Delta\Sigma$  modulator with a 9-level quantizer and DWA is shown in Fig.3.4.

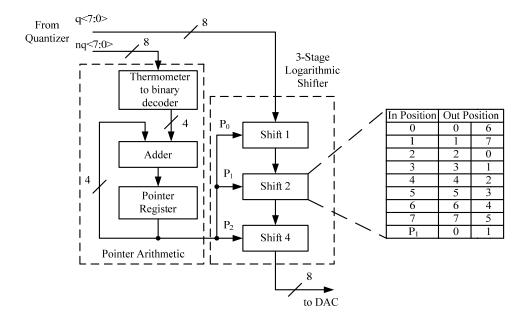

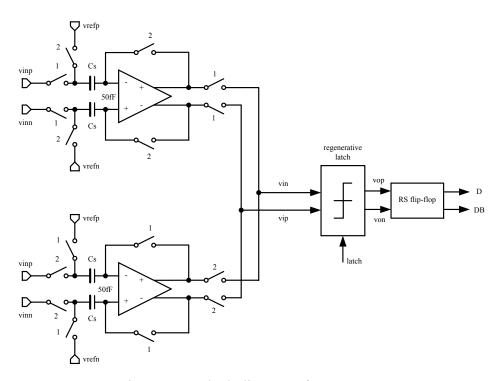

As we can see, a well designed DWA circuit adds only a shifter in the modulator feedback path [3]. The pointer calculation can be performed outside the modulator loop. Therefore, it is not necessary for the DWA control block to wait for the most recent quantizer result in order to determine the proper control word applying to the DWA scrambling block. This approach reduces the delay through the loop and enables a higher resolution quantizer. Fig.3.5 shows a simplified block diagram of the DWA system for the case of a 9-level DAC. The digital output of the quantizer is sent in a 8bit thermometer-encoded format to a shifting block and to a pointer arithmetic block. The pointer arithmetic block converts the thermometer encoded word to binary format and performs 4-bit modulus integration of the binary word with a 4-bit adder with carryout and a 3-bit pointer register. The pointer register stores the pointer control word and applies it to the shifting block and to one input of the 4-bit adder. The pointer control word is updated each sampling cycle of the ADC. The shifting block shifts the 8-bit thermometer encoded word a fixed number of digital positions in response to the pointer control word that is received from the pointer arithmetic block. The shifting block is made up of three logarithmic shifter cells that each respond individually to a single digit of the 3-bit binary control word P. The logarithmic shifter resides within the loop of the modulator and adds a small amount of delay to the loop feedback path—the equivalent of three transmission gate delays for the case of a 9-level quantizer

Note that this kind of DWA scrambles the quantizer output while fixing the DAC elements. Also a binary coded accumulator is needed to calculate the pointer.

#### 3.3. Proposed DWA realization

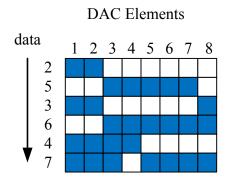

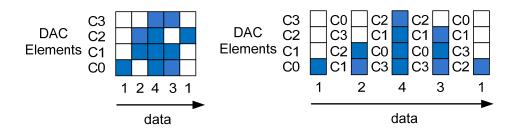

If we perform DWA in such a way that unit DAC elements are rotated while fixing the quantizer output, another DWA implementation exists. This section describes this new DWA implementation in detail. For sake of simplicity a 5-level DAC is used even though this implementation is applicable to any multi-bit DAC.

A general description of the new DWA implementation with a 5-level DAC is illustrated in Fig.3.6. As a comparison, conventional DWA implementation is also shown in the figure. It is clear that these two DWA implementations achieve the same functionality.

Figure 3.5 Detailed implementation of a DWA for 9-level DAC

Unlike conventional DWA implementation, in the proposed realization the pointer calculation is performed in the thermometer code domain. The pointer of the new implementation here only depends on the previous quantizer digital output. For example in Fig.3.6, if a pervious quantizer output is 3, with C2 is the first unused DAC element, and then next time C2 will be sitting in the bottom. Thus simpler circuit instead of digital accumulator can be used to save hardware consumption.

Figure 3.6 New DWA implementation compared with the conventional one The mapping between DAC elements and the thermometer code can be realized by a barrel shifter as shown in Fig.3.7.

Figure 3.7 Barrel shifter mapping DAC elements and quantizer output digital code

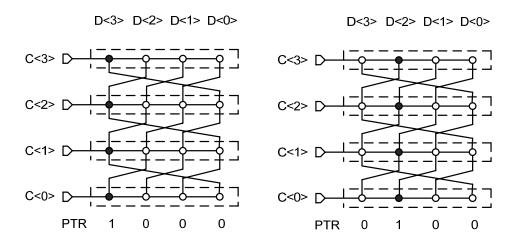

There are only four possible pointer values for a 5-level DAC case. Fig.3.7 shows two of them. A complete mapping is shown in Fig.3.8.

Generating a new pointer is very easy in this DWA implementation. It only depends on the previous pointer and previous quantizer output. Their relationship is shown in Table.3.1.

| PTR  | 1000 | 0100 | 0010 | 0001 |

|------|------|------|------|------|

| D<3> | C<3> | C<0> | C<1> | C<2> |

| D<2> | C<2> | C<3> | C<0> | C<1> |

| D<1> | C<1> | C<2> | C<3> | C<0> |

| D<0> | C<0> | C<1> | C<2> | C<3> |

Figure 3.8 Complete mapping between DAC elements and quantizer digital output code

Table 3.1 Complete mapping between DAC elements and quantizer digital output code

| Quanntizer digital output  Previous PTR | 0000/1111 | 0001 | 0011 | 0111 |

|-----------------------------------------|-----------|------|------|------|

| 1000                                    | 1000      | 0100 | 0010 | 0001 |

| 0100                                    | 0100      | 0010 | 0001 | 1000 |

| 0010                                    | 0010      | 0001 | 1000 | 0100 |

| 0001                                    | 0001      | 1000 | 0100 | 0010 |

The key point to finding the new pointer is the extraction of 0-1 transition of the previous quantizer digital output. Then the new pointer can be shifted version of the previous pointer. As a result, another logarithmic shifter can be used to obtain the new pointer.

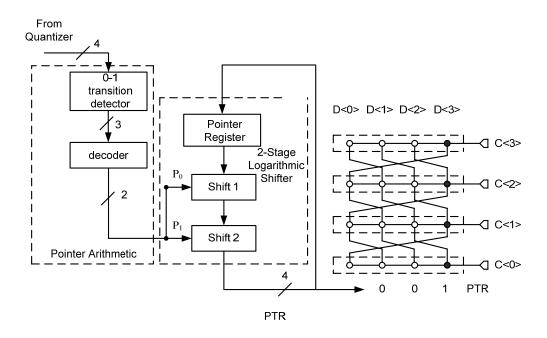

The complete new DWA implementation is illustrated in Fig.3.9.

The relationship between 4-bit quantizer digital output, 3-bit 0-1 transition detector output and 2-bit decoder output is shown in Table.3.2.

Figure 3.9 Block diagram of new DWA implementation (5-level DAC)

D<3> D<2> D<1> D<0> T<2> T<1> T<0> P<1> P<0>

Table 3.2 Relationship of the pointer arithmetic

From the above table, the pointer arithmetic is simple and can be expressed using the logic expressions (3.1) - (3.5).

$$T < 2 >= \overline{D < 3} > D < 2 > + D < 3 > \overline{D < 2} >$$

$$(3.1)$$

$$T < 1 >= \overline{D < 2 >} D < 1 > + D < 2 > \overline{D < 1 >}$$

(3.2)

$$T < 0 >= \overline{D < 1} > D < 0 > + D < 1 > \overline{D < 0} >$$

(3.3)

$$P < 1 >= (\overline{T < 2} > T < 1 > + T < 2 > \overline{T < 1} >) \cdot \overline{T < 0} >$$

(3.4)

$$P < 0 > = (\overline{T < 2} > T < 0 > + T < 2 > \overline{T < 0} >) \cdot \overline{T < 1} >$$

(3.5)

The conventional DWA implementation is based on binary code domain. Therefore thermometer to binary conversion and accumulator are needed.

This new DWA implementation is done in the thermometer code domain. As a consequence, it can be realized very easily. The hardware consumption is expected to be greatly reduced when the quantizer resolution is around 3-5 bit.

# 3.4. Summary

Compared to the conventional DWA in Fig.3.5, the proposed DWA realization

achieves the same functionality. However, the thermometer to binary decoder and the accumulator is replaced with a simple 0-1 transition detector and another logarithmic shifter. As a consequence, the hardware consumption is greatly reduced which results a smaller die area.

It is interesting to note that this new DWA implementation can be used to shuffle the reference voltages in the multi-bit quantizer [4]. This method entirely eliminates the delay in the modulator feedback path. However, doing DWA in the multi-bit quantizer means reference voltage scrambling which is in the analog domain. In deep sub-micron CMOS process, MOS switches in the middle of the supply rail barely turn on. Even though boosted clock techniques can be utilized to reduce the switch-on resistance, switch design become more complicated. For high speed application, this nevertheless poses challenges in the circuit design. In our case, scrambling is done in the digital domain that is inherently a lot more robust over process, supply voltage and temperature variation.

#### References

- [1] R. Baird and T. Fiez, "Linearity enhancement of multibit ΔΣ A/D and D/A converters using data weighted averaging," *IEEE Transactions on Circuits and SystemsII*: Analog and Digital Signal Processing, vol.42, no.12, pp.753-762, Dec 1995.

- [2] R. Schreier and G. C. Temes, "Understanding Delta-Sigma Data Converters". John Wiley & Sons, 2005.

- [3] M. Miller and C. Petrie, "A multibit sigma-delta ADC for multimode receivers," *IEEE J. Solid-State Circuits*, vol.38, pp. 475-482, Mar. 2003.

- [4] L. Dorrer et al., "10-Bit, 3 mW Continuous-Time Delta-Sigma ADC for UMTS in a 0.12μm CMOS Process," in Proc. Eur. Solid-State Circuits Conf. (ESSCIRC), Lisbon, Portugal, Sept. 2003.

#### CHAPTER 4. CHARGE PUMP BASED SC INTEGRATOR

Charge-pump (SC) based switched-capacitor (SC) integrator is a promising technique to reduce opamp power consumption. In this chapter, a cross-coupling technique is proposed to eliminate parasitic capacitor effects in a CP based SC integrator. Also, design methodologies are introduced to incorporate a modified CP based SC integrator into a low-distortion  $\Delta\Sigma$  modulator. A second-order  $\Delta\Sigma$  modulator was designed and simulated to verify the proposed modulator topology.

#### 4.1. Introduction

In recent years, broadband low power delta-sigma ( $\Delta\Sigma$ ) analog-to-digital converters are becoming more and more popular in applications such as wireless communication systems, high definition television, medical imaging, etc. There are two possible realizations of a  $\Delta\Sigma$  modulator. One is based on discrete-time (DT) switched capacitor (SC) circuitry. The other employs continuous-time (CT) circuitry. SC  $\Delta\Sigma$  modulators have some advantages over their CT counterparts, including having less sensitivity to clock jitter, and well defined signal transfer function (STF) and noise transfer function (NTF). There are ongoing efforts to effectively extend the bandwidth of an SC  $\Delta\Sigma$  modulator while maintaining low power consumption. Basically, two approaches can be explored to achieve this commitment. The first one deals with architectural innovation. Amongst various new  $\Delta\Sigma$  modulator architectures, low-distortion topology [1] is a very attractive one. The other approach focuses on transistor level design.

Recently, Nilchi and Johns came up with a charge-pump (CP) based SC integrator [2]. With the same thermal noise level as a conventional SC integrator, this CP based integrator offers smaller capacitive loading and larger feedback factor that makes it faster and consume less power. However the input full scale range of the  $\Delta\Sigma$  modulator using CP based integrator has to be halved due to the double feedback DAC voltage. Therefore the modulator will lose dynamic range by as much as 6 dB. In order to conquer this potential drawback, a modified CP SC integrator [3] is proposed here to recover the modulator's full scale input range. But the fact that the input signal and feedback signal are sampled in the same clock phase makes it not very straightforward to incorporate the modified CP SC integrator into a low-distortion  $\Delta\Sigma$  modulator topology.

In this chapter, a cross-coupling technique is proposed to eliminate parasitic capacitor effect in a CP based SC integrator. Then, design methodologies are introduced to incorporate a modified CP based SC integrator into a low-distortion  $\Delta\Sigma$  modulator. A second-order  $\Delta\Sigma$  modulator was designed and simulated to verify the proposed modulator topology.

#### 4.2. Charge Pump Based Switched Capacitor Integrator

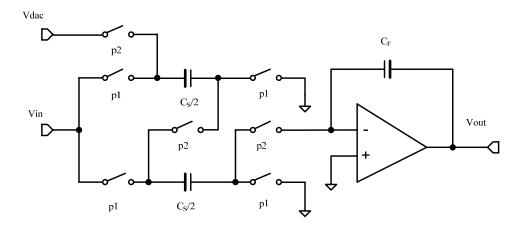

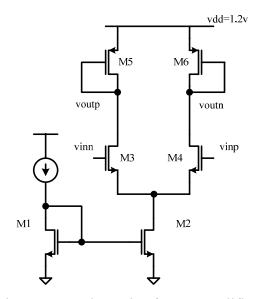

A CP based SC integrator [2] is shown in Fig.4.1 in a single–ended configuration. Vin is the input signal and Vdac comes from feedback DAC. Sampling capacitor Cs is divided into two halves with  $C_{S1}=C_{S2}=C_S/2$ . During the sampling phase p1, input signal is sampled on both capacitors. During the integration phase p2,  $C_{S1}$  and  $C_{S2}$  are

connected in series and discharge into the integrating capacitor C<sub>F</sub>. Applying charge conservation, the transfer function of this CP based SC integrator can be expressed as,

$$V_{out}[n] - V_{out}[n-1] = \frac{1}{2} \frac{C_s}{C_F} \{ (V_{in}[n-1]) - \frac{1}{2} V_{DAC} \}$$

(4.1)

As can be seen from (4.1), the integrator gain can be accurately set by the capacitor ratio. Compared to a conventional parasitic insensitive SC integrator, CP based SC integrator offers a smaller capacitive loading and a larger feedback factor when realizing the same integrator gain and same input thermal noise level. One potential drawback for this CP based SC integrator is that the 1/2Vdac term in (4.1) can reduce the modulator dynamic range by as much as 6dB which is truly undesired in a low supply voltage design.

Figure 4.1 CP based SC integrator

A modified CP based SC integrator is proposed in [3] aiming to mitigate the input dynamic range reduction while maintaining all the other advantages of the CP based SC integrator. The circuit is shown in Fig.4.2 in a single-ended configuration.

Feedback DAC voltage is sampled during p1 instead of p2. Applying charge conservation, the transfer function of this modified CP based SC integrator can be expressed as,

$$V_{out}[n] - V_{out}[n-1] = \frac{1}{2} \frac{C_s}{C_F} \{ (V_{in}[n-1]) - V_{DAC} \}$$

(4.2)

The gain of the modified CP based SC integrator remains unchanged, but the 1/2 term before the Vdac is eliminated, which means  $\Delta\Sigma$  modulator input full scale range is not limited to be less than half the Vdac.

Figure 4.2 Modified CP based SC integrator

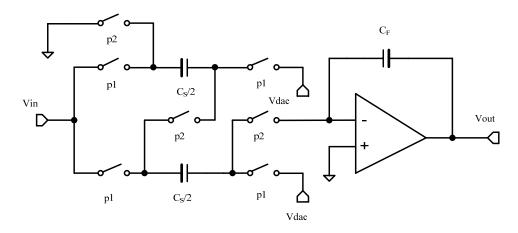

### 4.3. Parasitic Insensitive Charge-Pump-Based SC Integrator

The calculation of the integrator transfer function in the proceeding section ignored the parasitic capacitance due to the creation of the sampling capacitors as well as the nonlinear capacitance associated with the switches. The addition of such parasitic capacitance results in the circuit is shown in Fig.4.3. Here, C<sub>PT1</sub> represents the parasitic capacitance of the top plate of the upper sampling capacitor as well as the

nonlinear capacitance associated with the switches.  $C_{PB1}$  represents the parasitic capacitance of the bottom plate of the upper sampling capacitor as well as the nonlinear capacitance associated with the switches.  $C_{PT2}$  represents the parasitic capacitance of the top plate of the lower sampling capacitor as well as the nonlinear capacitance associated with the switches.  $C_{PB2}$  represents the parasitic capacitance of the bottom plate of the lower sampling capacitor as well as the nonlinear capacitance associated with the switches.

Figure 4.3 CP based SC integrator with parasitic capacitor

In accounting for these parasitic capacitances, we can immediately discard the effect of  $C_{PT2}$  since it connects to ground during p1 and virtual ground during p2. The effect of  $C_{PB1}$  is also not important. Even though this capacitor is charged to Vin

during p1, it will be discharged during p2. Applying again charge conservation with  $C_{PT1}$  and  $C_{PB2}$  the integrator transfer function can be expressed as:

$$V_{out}[n] - V_{out}[n-1] = \frac{1}{2} \frac{C_S}{C_F} \left\{ \frac{C_S + C_{PT1}}{C_S + C_{PB2} + C_{PT1}} \cdot V_{in}[n-1] - \frac{C_S}{2(C_S + C_{PB2} + C_{PT1})} \cdot V_{DAC} \right\}$$

$$(4.3)$$

Figure 4.4 Fully differential CP based SC integrator with parasitic capacitors

From (4.3), we see that the gain coefficient is highly related to the parasitic coefficient  $C_{PT1}$  and  $C_{PB2}$  which is not well controlled and would be quite nonlinear

due to the use of large input sampling switches. Therefore this effect must be addressed in high linearity applications.

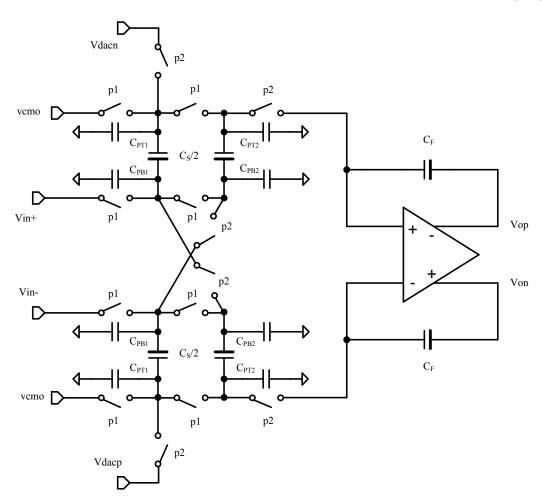

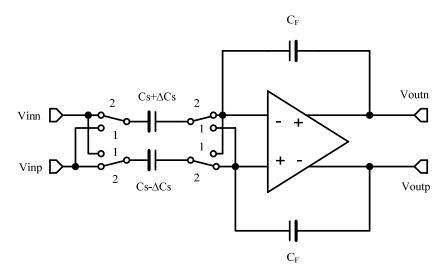

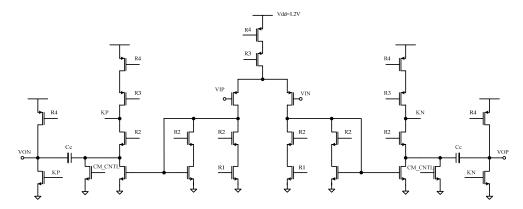

Modern integrated circuit design always employs fully differential circuit to mitigate supply and substrate noise, enhance common mode rejection and improve linearity. Fortunately, the parasitic effect in the CP based SC integrator can be completely eliminated in a fully differential configuration.

A fully differential CP based SC integrator with parasitic capacitors is shown in Fig.4.4. The key point here is to cross couple the sampling capacitor between the positive and negative sampling branch. Let us again check out the effect of parasitic capacitors one by one. Similar to the discussion before, we can discard the effect of C<sub>PT2</sub>, since it connects to ground during p1 and virtual ground during p2. The effect of C<sub>PT1</sub> is also unimportant. Even though this capacitor is charged to Vin during p1, it will be discharged during p2. Parasitic capacitors C<sub>PB1</sub> and C<sub>PB2</sub> in the positive sampling branch are charged to vin(n-1) C<sub>PB1</sub> and vin(n-1) C<sub>PB2</sub> respectively. Meanwhile, parasitic capacitors C<sub>PB1</sub> and C<sub>PB2</sub> at the negative sampling branch are charged to -vin(n-1) C<sub>PB1</sub> and -vin(n-1) C<sub>PB2</sub>. Therefore assuming perfect symmetry, by cross coupling the sampling capacitors in the positive and negative sampling branch results the complete cancellation of these parasitic charges. Without the parasitic charges, integrator transfer function shall be restored and linearity be improved.

This cross-coupling concept can be extended to the modified CP based SC integrators. A fully differential modified CP based SC integrator with parasitic capacitors is shown in Fig.4.5. In Fig.4.5, input signal and feedback DAC output are sampled simultaneously during p1. As is well known, feedback DAC output contains not only the signal content but also shaped quantization noise. In order to not degrade the integrator linearity, the top plate of the sampling capacitors is used to sample the input signal during p1 and to switch to the opamp virtual ground during p2. This

arrangement changes the polarity of the integrator transfer function which is not a problem in a fully differential implementation.

Figure 4.6 Modified CP based SC integrator insensitive to parasitic capacitor

In Fig.4.5, the effect of  $C_{PT1}$  is also unimportant as discussed before. Parasitic capacitors  $C_{PB1}$  and  $C_{PB2}$  in the positive sampling branch are charged to vdac(n-1)  $C_{PB1}$  and vdac(n-1)  $C_{PB2}$ , respectively. Meanwhile, parasitic capacitors  $C_{PB1}$  and  $C_{PB2}$  at the negative sampling branch are charged to -vdac(n-1)  $C_{PB1}$  and -vdac(n-1)  $C_{PB2}$ . Therefore by cross coupling the sampling capacitors in the positive and negative sampling branch results the cancellation of these parasitic charges.

The parasitic capacitor C<sub>PT2</sub> in Fig.4.5 is troublesome here. Its effect can be analyzed differently considering the particular CMOS process used for the design. In a mixed signal CMOS process where MIM (Metal-Insulator-Metal) capacitor is available, the top plate parasitic of a MIM capacitor is so small as to not cause significant nonlinearity and distortion. However, in the process node 130nm below, MOM (Metal-Oxide-Metal) capacitor is widely adopted. The reasons are two-fold. First, its capacitance density is higher than a normal MIM capacitor. Second, it does not require any additional process mask, which leads to a lower cost. Despite its advantages, MOM capacitors have larger parasitic capacitance at both plates. Hence, if MOM capacitors are used, the effect of C<sub>PT2</sub> can not be ignored. Under most circumstances, the sampling capacitor Cs is large. Let Cs be 2pF. Assuming a reasonable percentage of the parasitic capacitance, at the top plate is 5%. Then C<sub>PT2</sub> is 50fF. An elaborate way to cancel the parasitic charge on CPT2 is to assign a dedicated small capacitor C<sub>PT</sub> as shown in Fig.4.6. C<sub>PT</sub> is charged to -vin(n-1) C<sub>PT</sub> during p1 and switched to the opamp virtual ground during p2 to cancel the parasitic charge vin(n-1) C<sub>PT2</sub>. Complete charge cancellation is expected if C<sub>PT</sub> is equal to C<sub>PT2</sub> which is not a

very difficult task. Since  $C_{PT}$  is usually small, switches associated with it tend to be small as well. The only downside of this scheme is a slightly reduced feedback factor during the integrating phase.

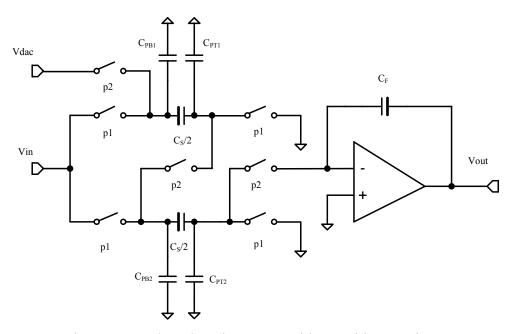

# 4.4. Low Distortion $\Delta\Sigma$ Modulator Employing CP Based SC Integrator

Fig.4.7 illustrates a general structure of a single-quantizer  $\Delta\Sigma$  modulator. This structure consists of two parts: the loop filter and the quantizer. The loop filter is a linear part, under most circumstances containing opamp based integrators. As the input signal goes directly through the loop filter, linearity requirement of the loop filter should be high enough to at least match the overall modulator's specification. In the actual design, such requirement mandates to use highly linear opamps. However, in deep sub-micron CMOS process under low supply voltage, it is a very demanding task to design an opamp with low power consumption and high linearity simultaneously.

Fig.4.8 shows the block diagram of a low-distortion  $\Delta\Sigma$  modulator. The key feature of this topology is a direct feed-forward path from modulator input to the internal quantizer. By doing this way, loop filter contains no longer the input signal but only the filtered quantization noise. Since the loop filter does not need to process the input signal, its linearity requirement can be significantly relaxed which is a great advantage. Another benefit is the reduced integrator output swing. This fact allows the use of more power efficient telescopic or folded-cascode OTAs to greatly reduce the modulator power consumption. As a result, since its inception, many  $\Delta\Sigma$  modulator

designs adopted this low-distortion topology and their experimental results demonstrated excellent linearity and power efficiency performances [4] [5].

Figure 4.7 A structure of a single-quantizer  $\Delta\Sigma$  modulator

Figure 4.8 A general structure of a low-distortion feed-forward  $\Delta\Sigma$  modulator

To achieve a broadband and low power  $\Delta\Sigma$  modulator design, it is an effective measure to combine low distortion topology and CP based SC integrator. The original CP based SC integrator can fit into the low-distortion topology without any problem. However, employing the modified CP based SC integrator is not straightforward since there is an explicit half-cycle delay in the modulator feedback path due to the fact that input signal and the feedback DAC signal are sampled at the same clock phase. Adding this half-cycle delay into the feedback path of a feed-forward  $\Delta\Sigma$  modulator

may cause instability. As a consequence, some measures should be taken to mitigate this additional half-cycle delay.

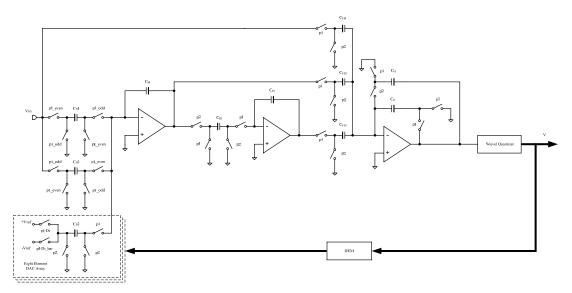

Figure 4.9 Proposed second order low-distortion  $\Delta\Sigma$  modulator

Fig.4.9 shows the proposed low-distortion  $\Delta\Sigma$  modulator topology which is able to adopt the modified CP based SC integrator as the very first integrator. A second order modulator is shown here for simplicity. Nevertheless, the concept hereby can be extended to arbitrary order of  $\Delta\Sigma$  modulator. The key point here is to make the first integrator half-cycle delayed instead of one-cycle delayed. This modification restores the NTF of the  $\Delta\Sigma$  modulator, which makes the modulator loop stable. Applying linear analysis, NTF of this particular second-order modulator is:

$$\frac{V(z)}{E(z)} = (1 - Z^{-1})^2 \tag{4.4}$$

Strictly speaking, the proposed  $\Delta\Sigma$  modulator topology is not able to achieve a perfect input signal cancellation at the input of the loop filter. So there is always a certain amount of signal energy entering the loop filter. Considering the over-sampling nature of a  $\Delta\Sigma$  modulator, the difference of the input signal samples separated by a

half clock cycle will be very small even under moderate over-sampling ratio (such as 16 or lower). Therefore the signal content at the first integrator output remains very small. Signal content at the following integrator output will become larger due to the accumulation process of the SC integrator. Fortunately, the non-linearity appearing deep inside the loop filter will be noise shaped when referring it to the modulator input. In summary, the proposed modulator topology can still maintain most of the low-distortion property, while consuming less power compared to a similar low-distortion  $\Delta\Sigma$  modulator employing conventional parasitic insensitive SC integrators.

Figure 4.10 Switch level of the proposed second order low-distortion  $\Delta\Sigma$  modulator

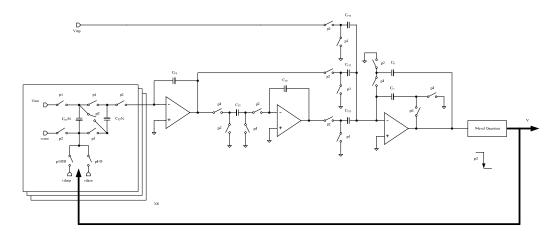

As a demonstration of the proposed topology, a feed-forward second order  $\Delta\Sigma$  modulator with modified CP based SC integrator as the first integrator was designed. Its switch level diagram is shown in Fig.4.10 in a single-end configuration for simplicity. Note that the cross coupling technique mentioned above can be applied to the fully differential implementation. Opamps here were represented by macro models with finite DC gain (50 dB). The dynamic behavior of the proposed  $\Delta\Sigma$  modulator was

simulated in Cadence Spectre simulator. The output digital bits were sampled and processed in MATLAB.

Figure 4.11 Simulated PSD of a  $\Delta\Sigma$  modulator with modified CP based SC integrator

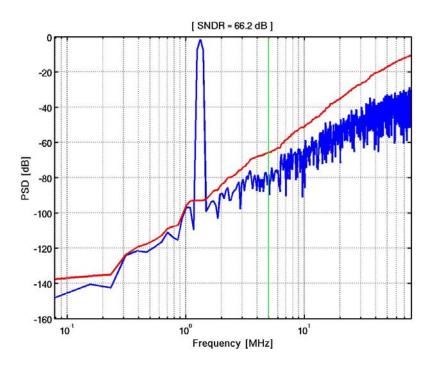

In the simulation, we assume a 5 MHz signal bandwidth, an input signal at 1.328125 MHz, an oversampling ratio of 16, and a 9-level internal quantizer. Fig. 4.11 shows the simulated output spectrum of the proposed second-order low-distortion  $\Delta\Sigma$  modulator with a -1.6 dBFS input signal. The simulated SQNR was 66.2 dB which does not include thermal noise and other circuit non-ideal effects.

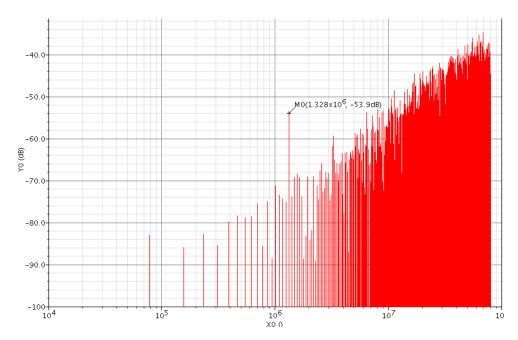

In order to verify the low-distortion property of the proposed  $\Delta\Sigma$  modulator topology, the first integrator output was also sampled and converted into the frequency domain, as shown in Fig.4.12. It can be seen that the input signal power is 54 dB

below full scale which suggests the opamp involved in the first integrator only needs to process a very small input signal. This clearly implied that the low-distortion property is retained in the proposed  $\Delta\Sigma$  modulator topology.

Figure 4.12 Simulated PSD of the first integrator output in the proposed  $\Delta\Sigma$  modulator

#### 4.5. Summary

A cross-coupling technique is proposed to eliminate parasitic capacitor effect in a CP based SC integrator. A new  $\Delta\Sigma$  modulator topology is proposed to effectively employ the modified CP base SC integrator in a low-distortion configuration. A second order  $\Delta\Sigma$  modulator with the proposed technique was designed and simulated to verify the effectiveness. The low power feature at both architecture level and transistor level makes it a good candidate for broadband, high linearity and low power applications.

#### References