#### AN ABSTRACT OF THE THESIS OF

Byoungchul Ahn for the degree of Doctor of Philosophy in Electrical and Computer Engineering presented on May 3, 1989.

Title: The Analysis and Synthesis of a Parallel Sorting Engine

# Redacted for Privacy

| Abstract approved: |                |  |

|--------------------|----------------|--|

|                    | John M. Murray |  |

This thesis is concerned with the development of a unique parallel sort-merge system suitable for implementation in VLSI. Two new sorting subsystems, a high performance VLSI sorter and a four-way merger, were also realized during the development process. In addition, the analysis of several existing parallel sorting architectures and algorithms was carried out.

Algorithmic time complexity, VLSI processor performance, and chip area requirements for the existing sorting systems were evaluated. The rebound sorting algorithm was determined to be the most efficient among those considered. The rebound sorter algorithm was implemented in hardware as a systolic array with external expansion capability.

The second phase of the research involved analyzing several parallel merge algorithms and their buffer management schemes. The dominant considerations for this phase of the research were the achievement of minimum VLSI chip area, design complexity, and

logic delay. It was determined that the proposed merger architecture could be implemented in several ways. Selecting the appropriate microarchitecture for the merger, given the constraints of chip area and performance, was the major problem. The tradeoffs associated with this process are outlined.

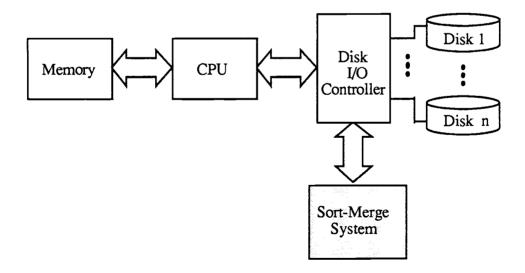

Finally, a pipelined sort-merge system was implemented in VLSI by combining a rebound sorter and a four-way merger on a single chip. The final chip size was 416 mils by 432 mils. Two micron CMOS technology was utilized in this chip realization. An overall throughput rate of 10M bytes/sec was achieved. The prototype system developed is capable of sorting thirty two 2-byte keys during each merge phase. If extended, this system is capable of economically sorting files of 100M bytes or more in size. In order to sort larger files, this design should be incorporated in a disk-based sort-merge system. A simplified disk I/O access model for such a system was studied. In this study the sort-merge system was assumed to be part of a disk controller subsystem.

# The Analysis and Synthesis of a Parallel Sorting Engine by Byoungchul Ahn

A THESIS

submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Completed May 3, 1989

Commencement June 1989

Approved:

# Redacted for Privacy

Typed by Byoungchul Ahn for Byoungchul Ahn

#### **ACKNOWLEDGEMENTS**

First of all I would like to express my gratitude to my advisor, Dr. John Murray, who has provided me with generous support, constant encouragement, and advice throughout this research study. I would also like to thank Drs. James Herzog, Theodore Lewis, and Thomas Dietterich for serving on my thesis committee and for their dedication in reading my manuscripts and offering valuable feedback. In addition, my very special thanks to Dr. Roy Rathja for helping me to get started with this study and encouraging my research work, as well as serving on my thesis committee. I would also like to thank Mr. Richard Lary who first suggested the double buffering technique used in conjunction with the four-way merger.

Finally, I am ever grateful to my wife, my son, and my parents for their patience during this long period of study. In particular, my wife and son are due my special thanks for enduring the Oregon hay fever season each spring.

#### TABLE OF CONTENTS

|    |                                                                                                                                                                                                                                                                                  | <u>Page</u>                            |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 1. | INTRODUCTION  1.1 Motivation and Objectives 1.2 Statement of the Problem 1.3 Definitions and Notation 1.3.1 Definitions 1.3.2 Notation 1.4 Organization of the Study                                                                                                             | 2<br>9<br>10<br>11                     |

| 2. | PARALLEL VLSI SORTERS  2.1 VLSI Sorters  2.2 Analysis of Parallel VLSI Sorters  2.2.1 Enumeration Sorter  2.2.2 The VLSI Sorter  2.2.3 Rebound Sorter  2.3 Comparison of Parallel VLSI Sorters  2.4 Conclusion                                                                   | 15<br>17<br>18<br>22<br>26             |

| 3. | THE REBOUND SORTER  3.1 Design Considerations 3.2 Processing and Memory Elements 3.3 Controller 3.4 Pipeline Control 3.5 System Expansion 3.6 Silicon Compilation 3.7 Functional Simulation and Timing 3.8 Floorplanning and Routing 3.9 Architectural Extension 3.10 Conclusion | 36<br>38<br>40<br>44<br>47<br>52<br>53 |

| 4. | EXTERNAL PARALLEL SORTING  4.1 VLSI Merge Sort  4.2 Analysis of the External Sortings  4.2.1 Parallel Binary Merge Sort  4.2.2 Pipelined Merge Sort  4.2.2.1 Pipelined Multi-Way Merger  4.2.2.2 Block-Merge Sort                                                                | 60<br>61<br>62<br>66                   |

# TABLE OF CONTENTS (Continued)

|    |                                           | <u>Page</u> |

|----|-------------------------------------------|-------------|

|    | 4.3 Buffer Management                     | . 74        |

|    | 4.3.1 General Implementation              |             |

|    | 4.3.2 Rebound Sorter and Buffer           |             |

|    | 4.4 VLSI Implementation Considerations    |             |

|    | 4.5 Four-Way VLSI Merger                  |             |

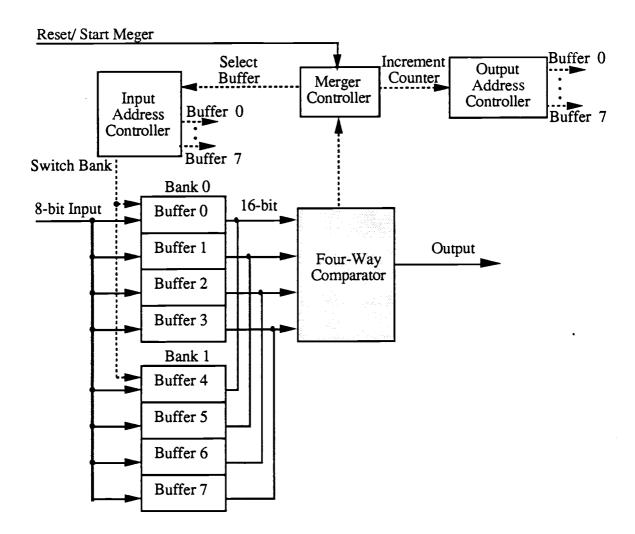

|    | 4.5.1 Buffer and Controller               |             |

|    | 4.5.2 Simulation and Timing               | 85          |

|    | 4.6 Conclusion                            | 86          |

| _  |                                           | 0.0         |

| 5. | VLSI SORT-MERGE SYSTEM                    |             |

|    | 5.1 Sort-Merge System Architecture        | 89          |

|    | 5.2 Sort-Merge Algorithm                  |             |

|    | 5.3 System Implementation                 |             |

|    | 5.3.1 Controller and System Integration   |             |

|    | 5.3.2 Simulation and Timing               |             |

|    | 5.3.3 Floorplanning and Routing           |             |

|    | 5.4 Additional Modular Sort-Merge Systems |             |

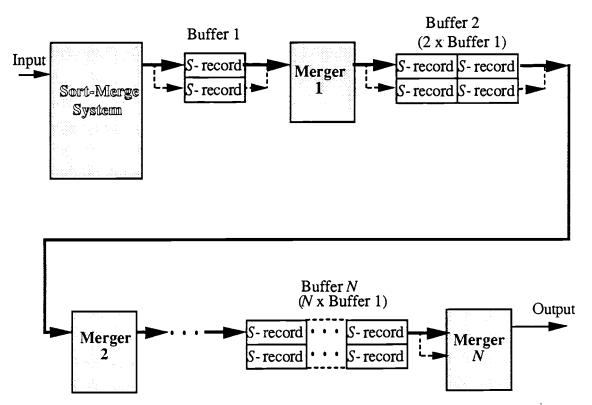

|    | 5.4.1 Iterative Sort-Merge System         |             |

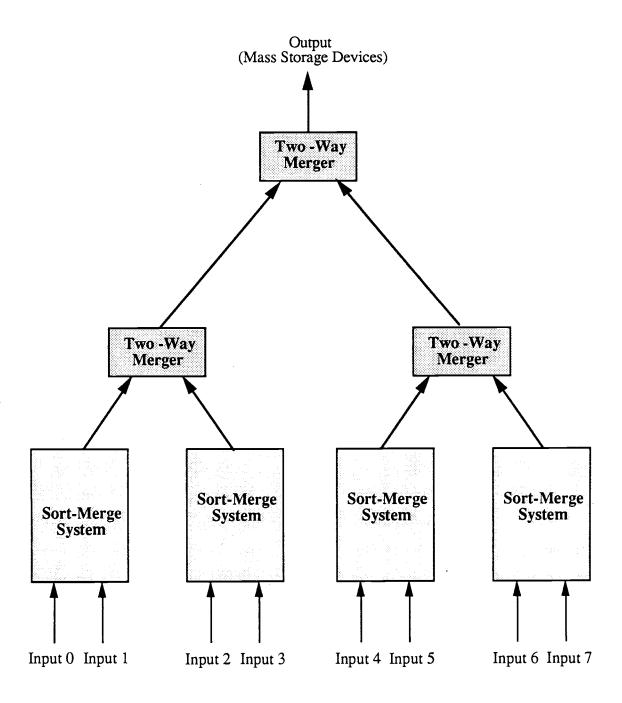

|    | 5.4.2 Tree Sort-Merge System              |             |

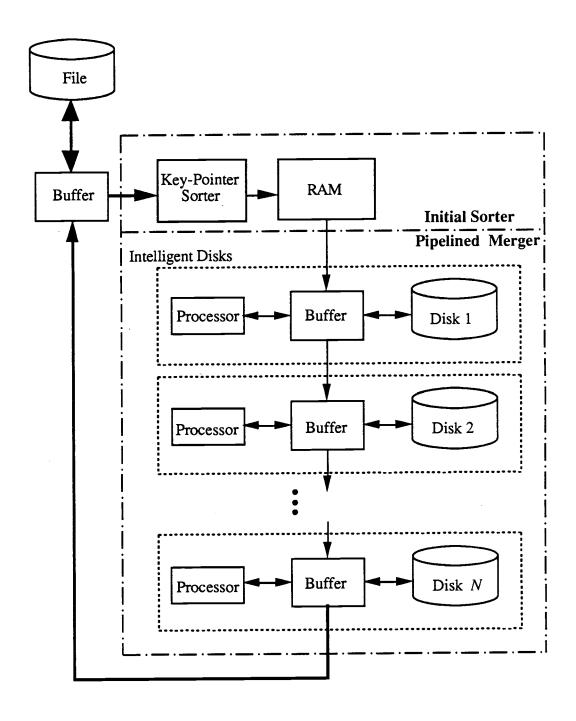

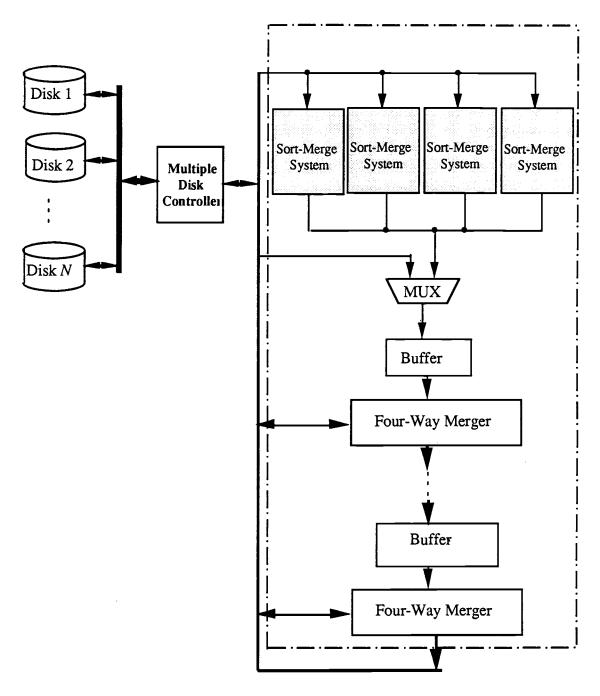

|    | 5.4.3 Disk-Based Sort-Merge System        |             |

|    | 5.4.3.1 Disk I/O Access Model             |             |

|    | 5.4.3.2 Disk-Based Sort-Merge System      |             |

|    | 5.5 Conclusion                            | 112         |

| 6  | CONCLUSIONS                               | 115         |

| υ. | 6.1 Research Contributions                |             |

|    | 6.2 Research Recommendations              |             |

|    | 0.2 Research Recommendations              | 110         |

| ΒI | BLIOGRAPHY                                | 120         |

| ΑF | PPENDICES                                 |             |

|    | APPENDIX A: LAYOUT AND ROUTE PLOTS        |             |

|    | APPENDIX B: TIMING ANALYSIS               | 133         |

#### LIST OF FIGURES

| <u>Figure</u> |                                                         |

|---------------|---------------------------------------------------------|

| 1.1           | Sort-Merge System Application                           |

| 1.2           | Input Data Structure 9                                  |

| 2.1           | Enumeration Sorter Block Diagram                        |

| 2.2           | Enumeration Sorter Operation                            |

| 2.3           | Enumeration Sort Algorithm (Algorithm 2.1) 21           |

| 2.4           | Basic Cell of the VLSI Sorter                           |

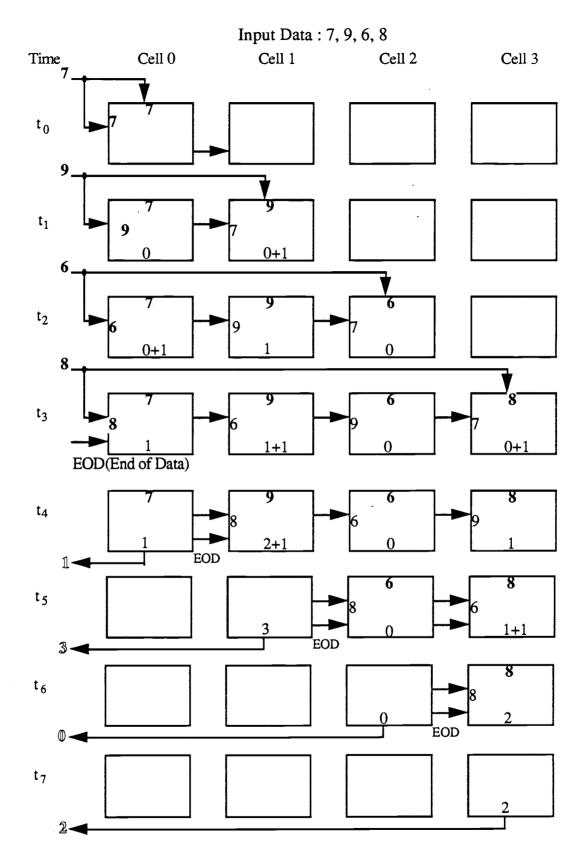

| 2.5           | The VLSI Sorter Operation                               |

| 2.6           | The VLSI Sorter Algorithm (Algorithm 2.2) 26            |

| 2.7           | Basic Structure of the Rebound Sorter 28                |

| 2.8           | Rebound Sorter Operation                                |

| 2.9           | Rebound Sorter Algorithm (Algorithm 2.3)                |

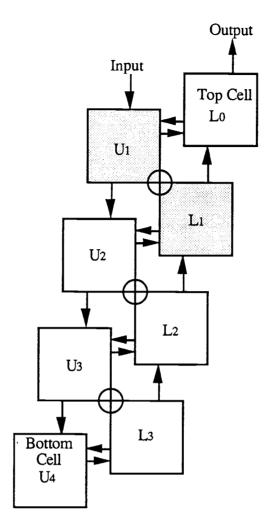

| 3.1           | Block Diagram of a Processing Element                   |

| 3.2           | Controller State Diagram                                |

| 3.3           | Initial State of the Rebound Sorter 43                  |

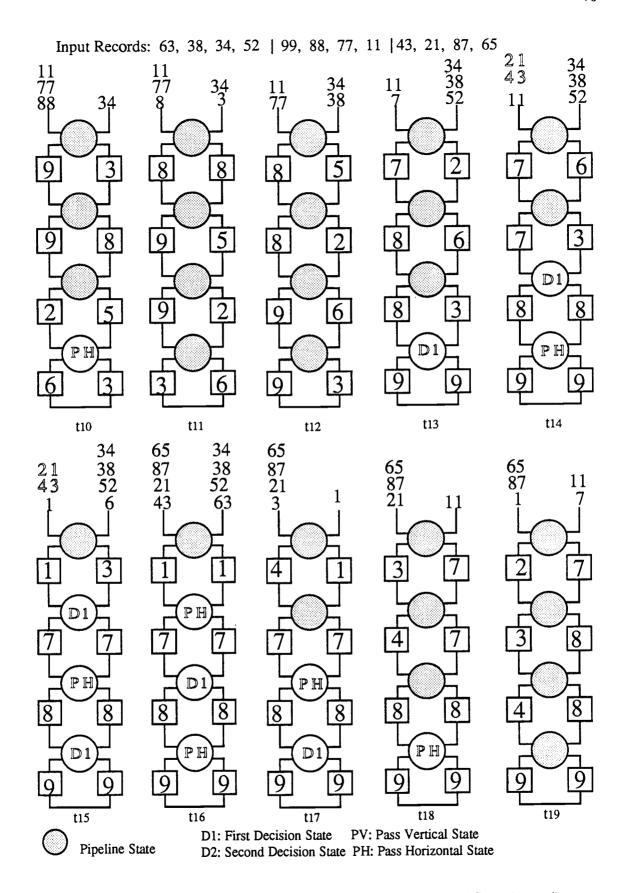

| 3.4           | Pipelined Rebound Sorter Operation                      |

| 3.5           | Pipeline Control Block Diagram and Signal Patterns 48   |

| 3.6           | Pipeline Control FSM State Diagram                      |

| 3.7           | Rebound Sorter Block Diagram                            |

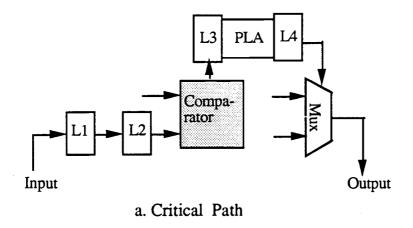

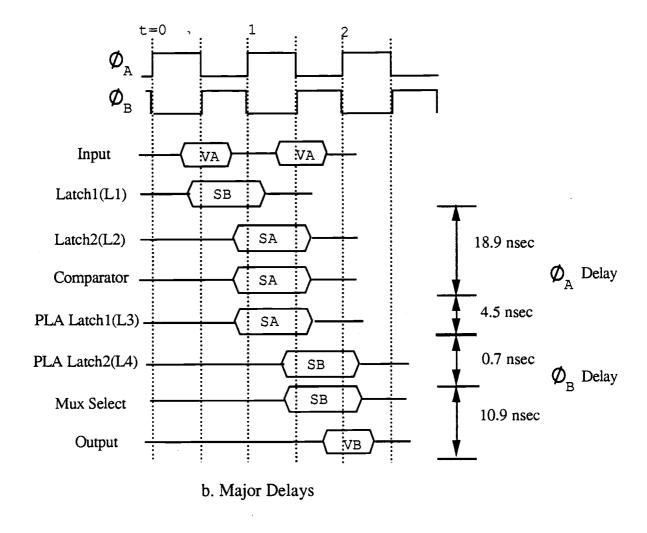

| 3.8           | Critical Path and Major Delays of the Rebound Sorter 55 |

| 3.9           | Architectural Extensions                                |

| 4.1           | Binary Merge Sort                                       |

| 4.2           | Binary Merge Sort Algorithm (Algorithm 4.1) 65          |

| 4.3           | Pipelined Merge Sort Structure                          |

# LIST OF FIGURES (continued)

| <u>Figur</u> | <u>Page</u>                                                |

|--------------|------------------------------------------------------------|

| 4.4          | Pipelined Merge Sort Operation                             |

| 4.5          | Pipelined Merge Sort Algorithm (Algorithm 4.2) 69          |

| 4.6          | Comparison of m-Way Mergers                                |

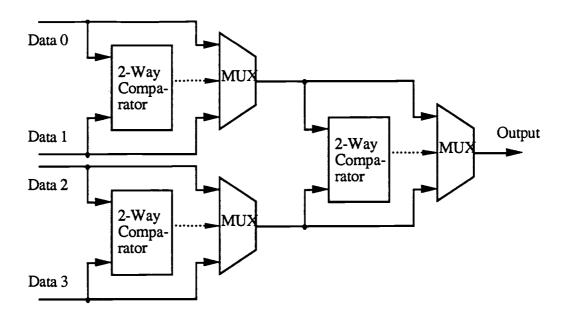

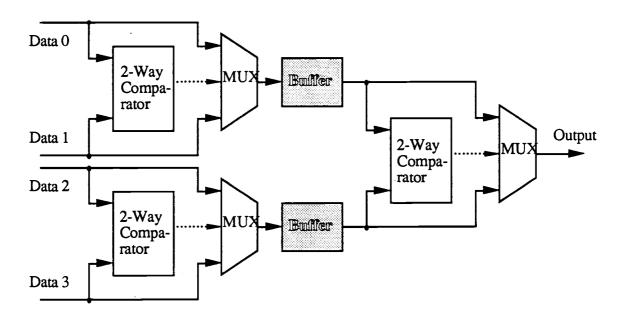

| 4.7          | Comparison of Four-Way Mergers                             |

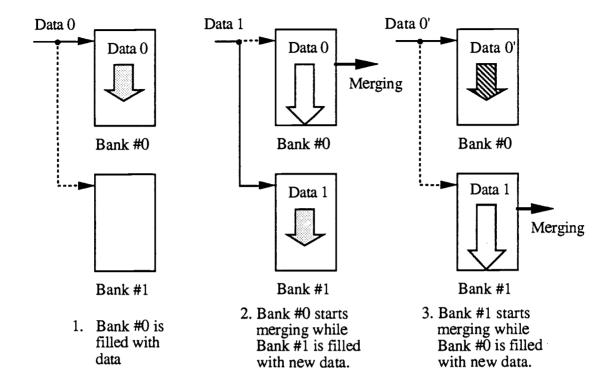

| 4.8          | Double Block Buffer Method                                 |

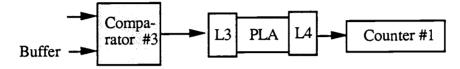

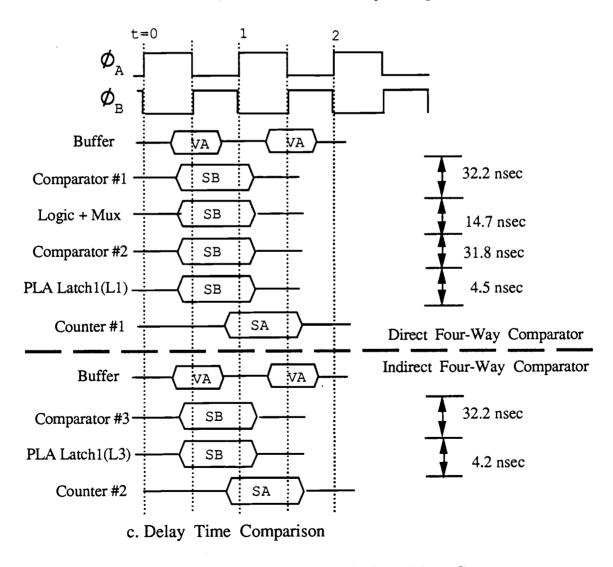

| 4.9          | Four-Way Comparator Structures                             |

| 4.10         | Timing Comparison of Four-Way Comparators 80               |

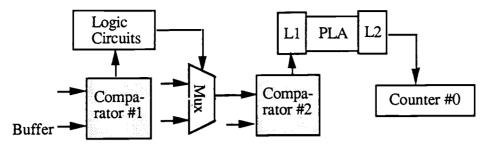

| 4.11         | Four-Way Merger Block Diagram                              |

| 5.1          | Sort-Merge System Applications                             |

| 5.2          | Sort-Merge System Block Diagram                            |

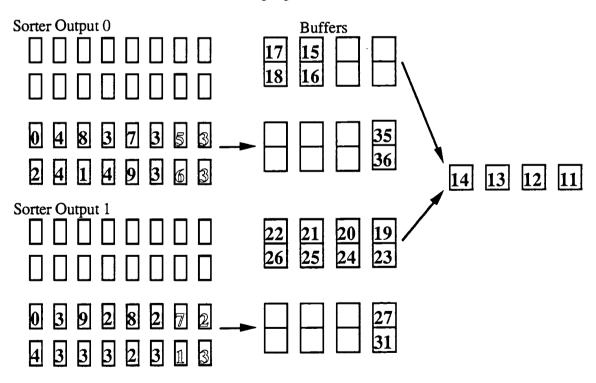

| 5.3          | Sort-Merge System Operation                                |

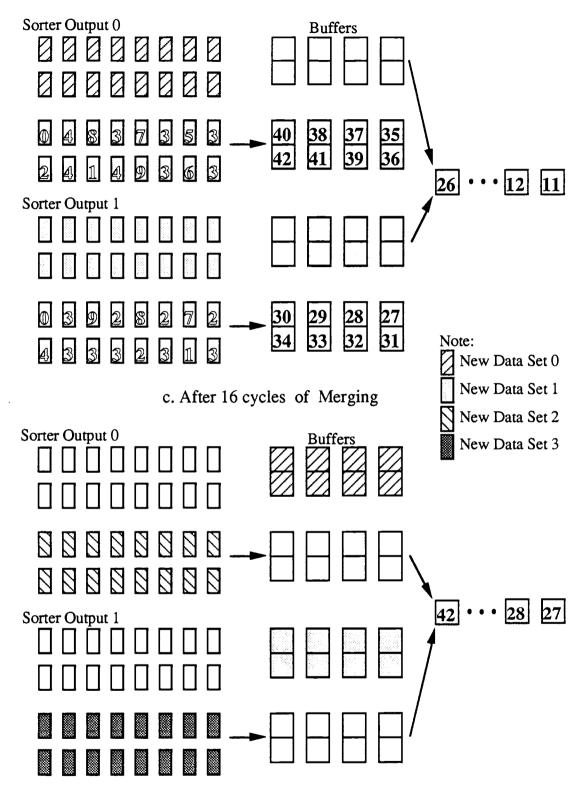

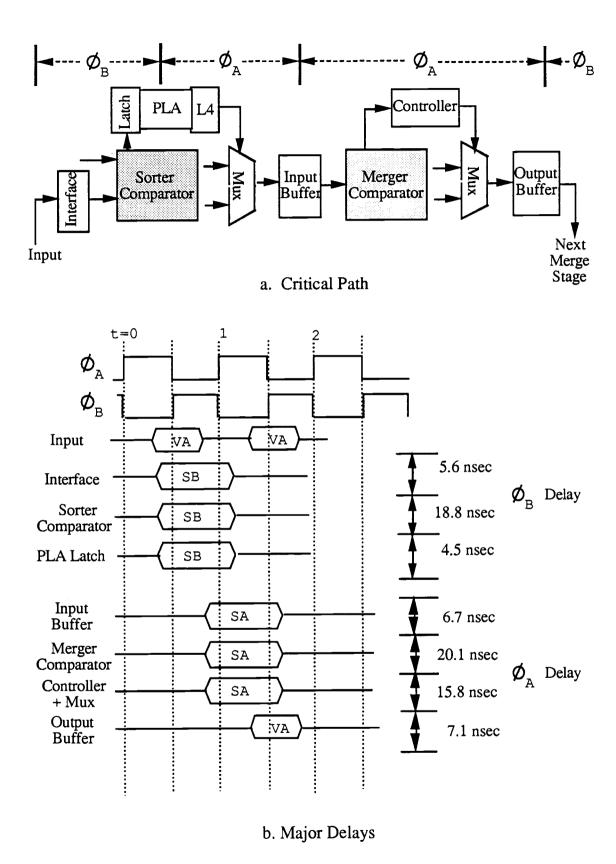

| 5.4          | Critical Path and Major Delays of the Sort-Merge System 99 |

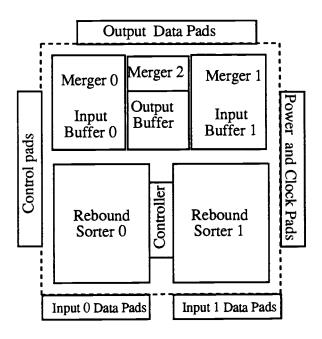

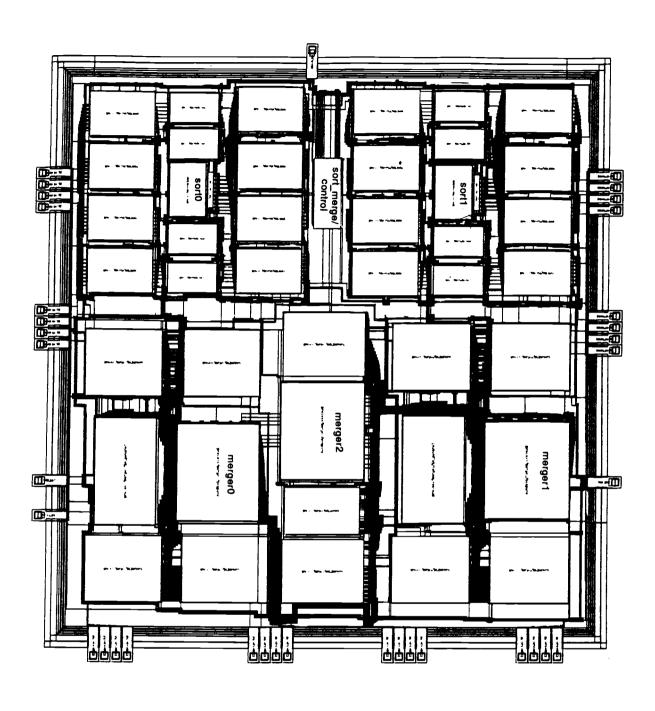

| 5.5          | Sort-Merge System Chip Floorplan                           |

| 5.6          | Iterative Sort-Merge System                                |

| 5.7          | Tree Sort-Merge System                                     |

| 5.8          | Takagi's Pipelined Sort-Merge System                       |

| 5.9          | Disk-Based Sort-Merge system                               |

## LIST OF TABLES

| Table | <u>Pag</u>                          | <u>e</u> |

|-------|-------------------------------------|----------|

| 2.1   | Comparison of VLSI Sorters          | 3        |

| 3.1   | Controller State Table 4            | 1        |

| 3.2   | Pipeline Control FSM State Table 49 | 9        |

| 4.1   | Comparison of Four-Way Comparators  | 1        |

| 5.1   | Disk I/O Access Model Analysis      | 8        |

## LIST OF APPENDIX FIGURES

| Figur | <u>re</u>                     | age  |

|-------|-------------------------------|------|

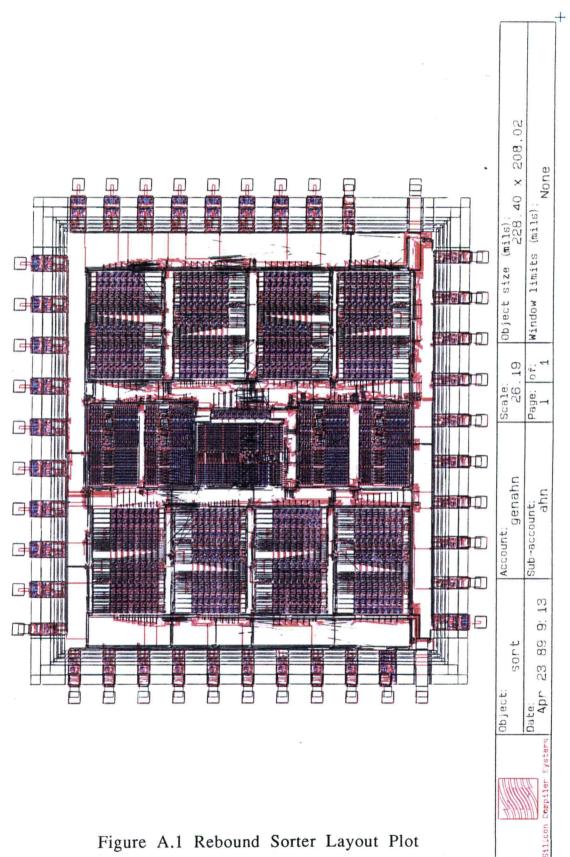

| A.1   | Rebound Sorter Layout Plot    | .126 |

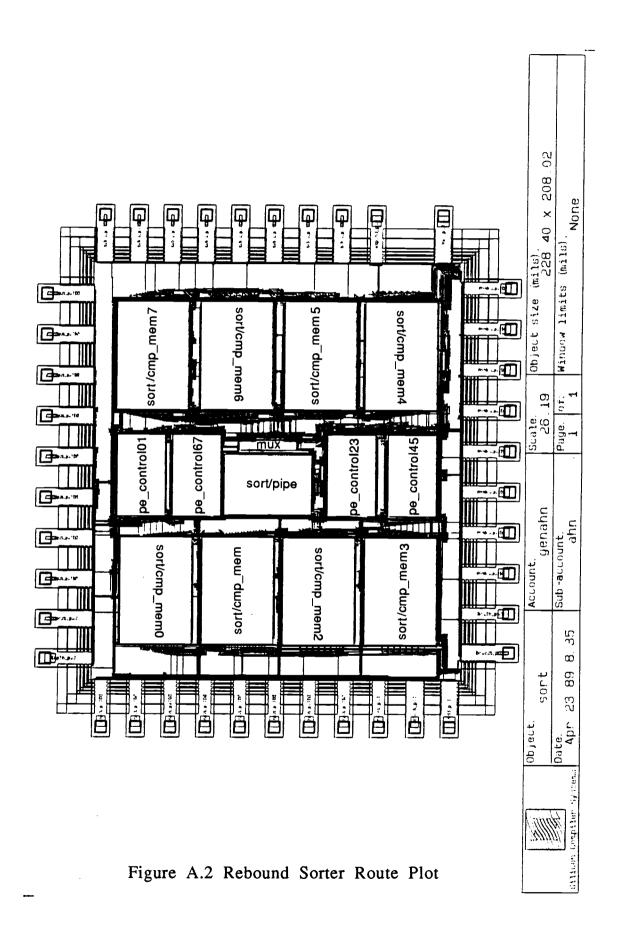

| A.2   | Rebound Sorter Route Plot     | .127 |

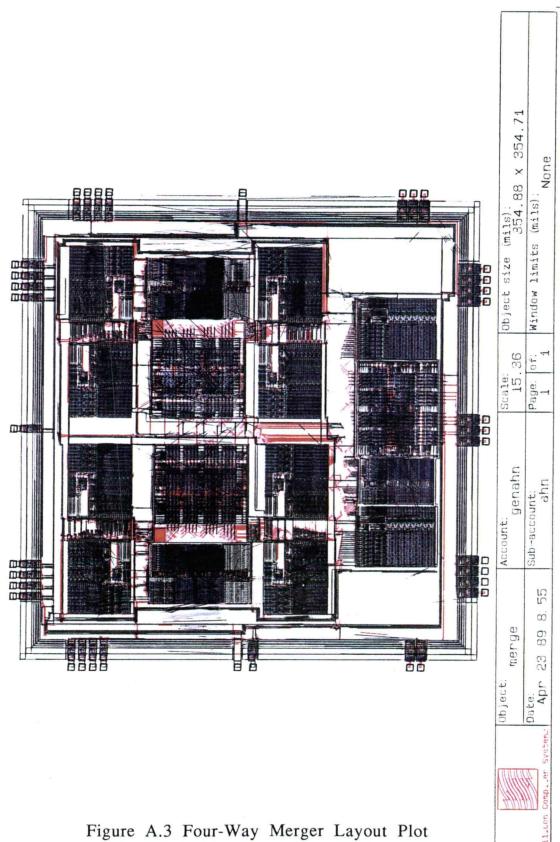

| A.3   | Four-Way Merger Layout Plot   | .128 |

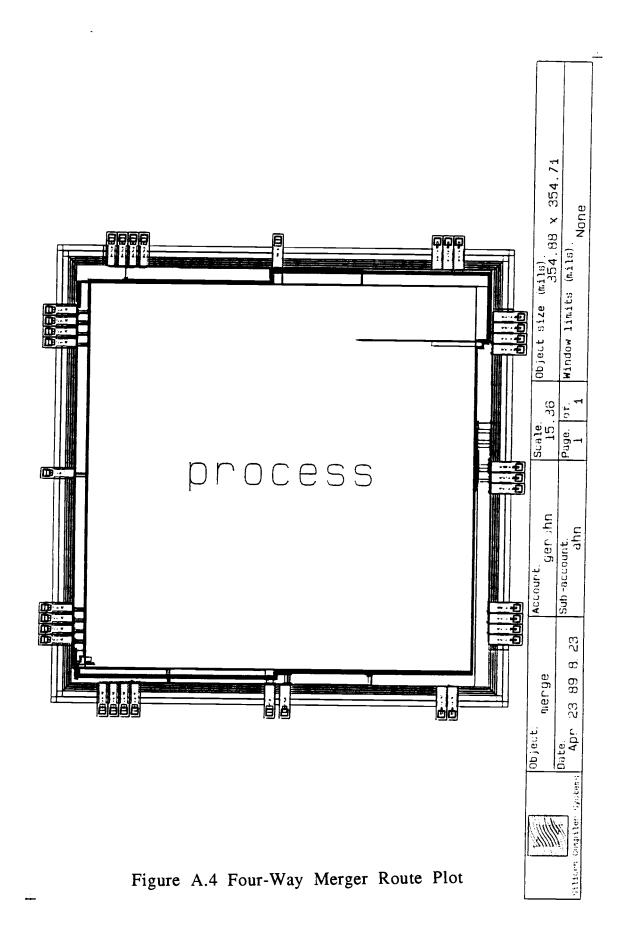

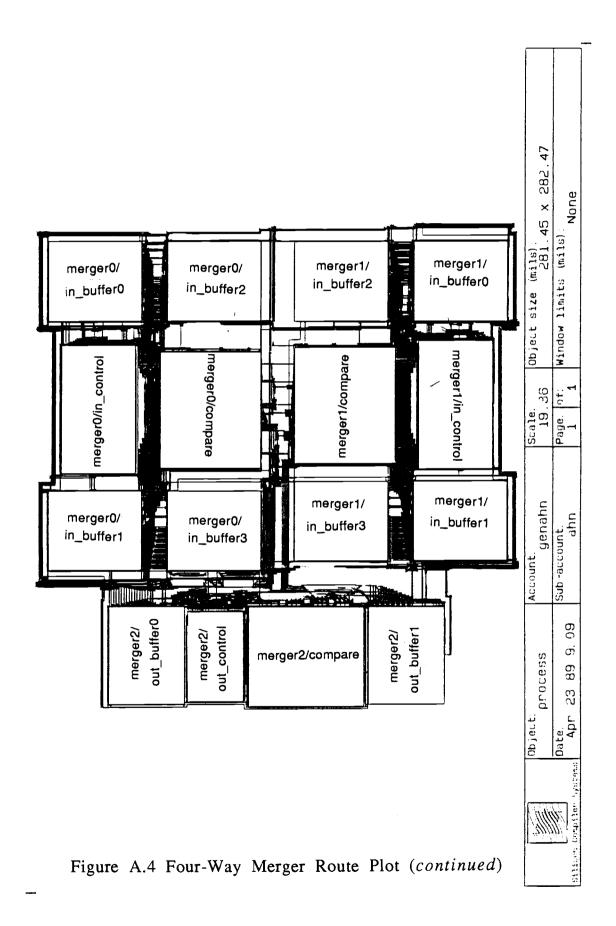

| A.4   | Four-Way Merger Route Plot    | .129 |

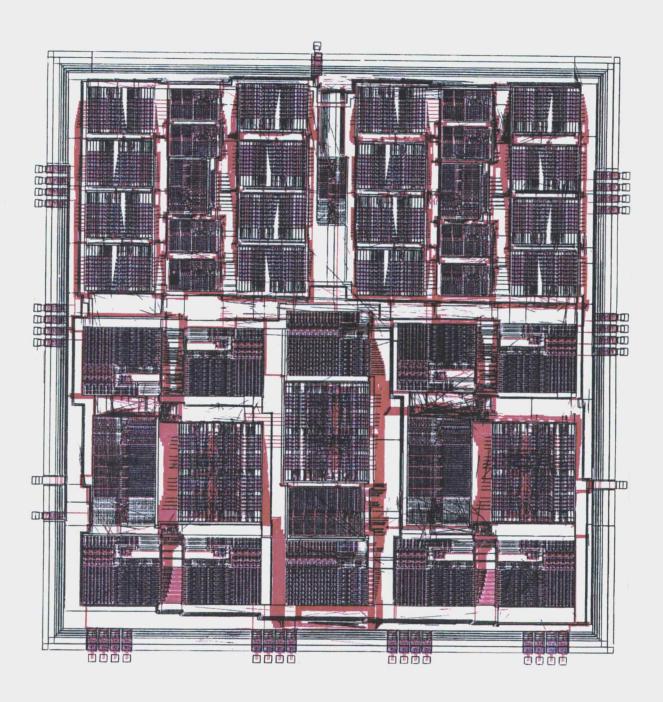

| A.5   | Sort-Merge System Layout Plot | 131  |

| A.6   | Sort-Merge System Route Plot  | 132  |

#### LIST OF APPENDIX TABLES

| Table | <u>e</u>                          | <u>Page</u> |

|-------|-----------------------------------|-------------|

| B.1   | Rebound Sorter Timing Analysis    | 134         |

| B.2   | Four-Way Merger Timing Analysis   | 136         |

| B.3   | Sort-Merge System Timing Analysis | 138         |

# THE ANALYSIS AND SYNTHESIS OF A PARALLEL SORTING ENGINE

#### 1. INTRODUCTION

Recent advances in very large scale integration (VLSI) technology have resulted in a significant rate of increase in general purpose computer performance. One consequence of this increase in performance has been a corresponding increase in the amount of data requiring computer processing. The development of VLSI systems for performing specialized processing functions on large volumes of data has lagged behind the development of more general purpose computing systems. The development of special purpose VLSI systems is expected to provide high performance in certain application areas at a reasonable cost. One application area, that of sorting large files, appears amenable to a hardware solution. VLSI parallel sorters have the potential for sorting very large files efficiently and economically.

This study includes the development of a parallel VLSI sortmerge system suitable for implementation on silicon. An analysis of parallel sorting architectures and algorithms is also accomplished. A new parallel sorting algorithm is not developed, *per se*. Rather, the unique design of a VLSI sort-merge system is accomplished by the interconnection of a number of new sorting subsystems. These include a parallel hardware sorter, merger, and associated support hardware. Through the combination of these subsystems, a high performance sort-merge system was obtained. This strategy saved substantial design time and effort over that involved in the creation and implementation of a conceptually new sort-merge algorithm. The resulting sort-merge system can be extended to accommodate a wide range of needs for sorting applications ranging from 10<sup>3</sup> to 10<sup>12</sup> bytes in size. The system has the ability to provide increased performance in executing many of the basic operations required by various specialized processing systems at relatively low cost and with high performance.

#### 1.1 Motivation and Objectives

Sorting has been one of the most widely studied areas of computer data processing and a problem area recognized as long ago as 1945 when Von Neumann and Goldstine collaborated on the development of the EDVAC (electronic discrete variable automatic computer). Since 1973, the most complete reference on sequential sorting is Knuth's three volume study, *The Art of Computer Programming*. In his third volume, *Sorting and Searching* [26, p.3], Knuth indicated that:

Computer manufacturers estimate that over 25 percent of the running time on their computers is currently being spent on sorting, when all

their customers are taken into account. There are many installations in which sorting uses more than half of the computing time.

In 1985, Linderstrom pointed to the importance of sorting operations in a discussion of the amount of sorting time required for bank applications [31]. He estimated that when using conventional disk merge-based methods, major banks spent two or more hours each night sorting demand deposit accounts. These accounts must be processed prior to opening on the next business day. The sorted files in question were on the order of several hundred megabytes (10<sup>6</sup> bytes) in size, a figure which is expected to increase by an order of magnitude before the end of this decade. In this case, even with the current generation of faster disks, an optimized merge sort would take 10 to 15 hours. Currently, larger banking applications encompass sorting files as large as 800 million bytes, which may include 2 million records, with 400 bytes per record, and 50 bytes per key. Within this decade file sizes in applications other than banking are expected to reach more than 10 gigabytes (109 bytes), or 10 million records with 1000 bytes per records and 100 bytes or more per key. Therefore, the need for the development of faster and more cost effective sorting methods is obvious.

Conceptually, it is possible that the demand for special purpose rapid sorting systems could be diminished due to the recent increases in general purpose computing performance and low cost, high capacity memory systems. However, for the foreseeable future,

the problem of sorting will remain as a dominant need in computer information processing.

There are several reasons for this conclusion. First, there is an increasing demand for database operations which can accommodate the large amounts of data required by some applications, including office automation processes, computer-aided design and computeraided manufacturing (CAD/CAM), graphics, and image processing systems [20,38,42]. For these applications, data continues to be stored in peripheral disks or tape. As the amount of data, the number of records, the record lengths, and field sizes continue to grow, the necessity for sorting will be unavoidable despite improvements in processor speed and memory capacity. Fast and efficient database operations involving large amounts of data are primarily concerned with performing general purpose sorting functions and relational operations. Efficient sorting computations are the most effective method of completing merge operations that eliminate duplicate records as well as performing other data base operations [10,19,32,34,37].

Second, many parallel sorting algorithms have been developed to improve the sorting performance compared with serial sorting on traditional sequential machines. Many of these parallel sorting algorithms concentrate on massively interconnected networks or processors. These algorithms focus on sorting operations, without regard to the means of data transfer to and from the sorting hardware [4,7,28,35,40,44]. When parallel sorting algorithms are evaluated, the costs of reading and writing data to peripheral devices

should be incorporated in their formulation, rather than ignored, i.e., there is no guarantee that a parallel sorting algorithm of the  $O(\log N)$  time complexity is optimal when the data input and output transfer rate is  $O(N^2)$ . Thus, the issue of data input and output time is equally as important as the actual sorting operation itself when very large files are involved.

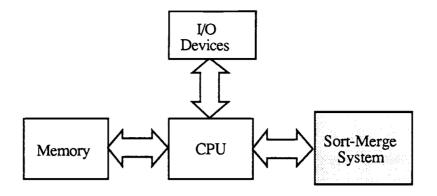

Finally, VLSI developments, particularly the availability of small geometry CMOS devices and the emergence of high level VLSI CAD technology, has encouraged the design of inexpensive and fast The fact that dynamic and static RAM capacities have sorters. continued to increase and costs decrease has also helped make special purpose VLSI sort-merge system solutions attractive. The type of system under consideration can be incorporated as part of either a database machine, or an independent sorting system with a high capacity RAM memory, plus a serial disk, fast parallel disk, or a RAM disk as required. The VLSI sort-merge system in this context will eliminate a part of the computational burden on the general purpose central processing unit (CPU) contained in almost all computing system configurations, allowing it to concentrate upon more valuable general purpose computing tasks.

To solve the above problems, special purpose parallel hardware should be designed which can utilize the advantages inherent in VLSI technology rather than conducting sorting operations by software on traditional computers or on parallel computers. The performance capabilities of an N processor parallel sorting algorithm implemented in VLSI can be linearly proportional to the number of

items to be sorted. Indeed, several VLSI sorting algorithms have shown impressive performance, performance significantly greater than that obtained in sequential systems or parallel systems [1,5,36,39,50].

Most parallel VLSI algorithms are of O(N) or  $O(\log N)$  time complexity with N processors. In contrast, sorting algorithms for traditional sequential computers provide  $O(N \log N)$  to  $O(N^2)$ performance in sorting N items [26]. When parallel VLSI architectures are used for sorting, the size of the files which can be sorted is often limited by the number of processing elements and the amount of local memory available. Performance will be highest if a large number of processing elements and a substantial amount of high speed local memory are available. For reasons stated at the beginning of this study, external sorting techniques are generally a necessity for sorting very large files [9,12,21,24]. In 1988, Beck and Francis evaluated the application of parallel external sorting to parallel computers and were able to show significant improvements However, they used a merge-sort in sorting performance [6,22]. algorithm rather than a special purpose hardware sorter. To date. practical high capacity VLSI-based external sort-merge systems have not been realized.

Therefore, the objective of this study is the design of a special purpose parallel VLSI sort-merge system in which efficient sorting and merging algorithms can be implemented to solve high performance parallel sorting problems. The proposed sort-merge system includes several VLSI subsystems. These subsystems not

only provide pipelined sorting capability, but also provide the initial presorting when sorting very large files. The merge function is designed to utilize pipelining capabilities for the improvement of overall sorting performance, based on the use of O(logN) processors.

The most efficient sorting algorithm was selected for implementation in VLSI following the analysis and comparison of several parallel sorting algorithms. The VLSI system design process included the high level simulation of the proposed algorithm, as well as the functional simulation and verification of the resulting chip. These steps were performed in order to assure the correctness of the hierarchical design methodology and careful documentation process were utilized. The system was implemented using a commercial silicon compiler. Although a parallel VLSI sorter of O(N) time complexity was developed, it can be shown to be both complex and expensive to build an isolated N-processor VLSI sorting engine for large values of N. Therefore, a VLSI merger was incorporated with the VLSI sorter to improve the overall sorting capacity while maintaining reasonable hardware costs. The merger plus presorter combination performs not only the internal sorting of small files into sorted strings, but also provides an external sort capability for sorting extremely large files in conjunction with external memory structures and/or peripheral storage devices. external sorting performance of the sort-merge system is closely related to the input and output operations of the mass storage devices utilized, e.g., magnetic disks. For external sorting, I/O processing is a significant performance factor because the data must

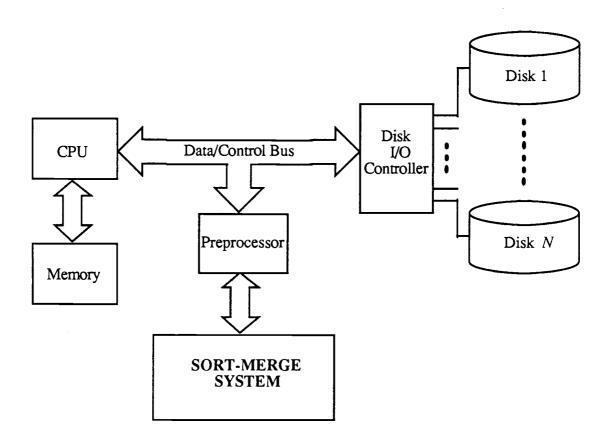

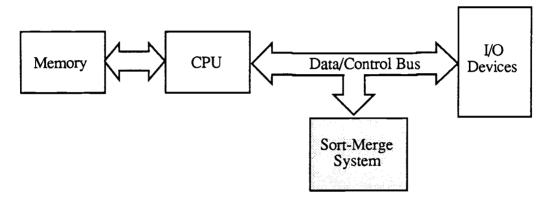

be transported between main memory and the storage devices a number of times during sorting operations. Therefore, it is necessary to carefully define an appropriate disk device I/O model for sort-merge functions. Such a model will provide information regarding collective system performance. The sort-merge system developed may be utilized in a variety of system configurations. A general application is illustrated in Figure 1.1.

Figure 1.1 Sort-Merge System Application

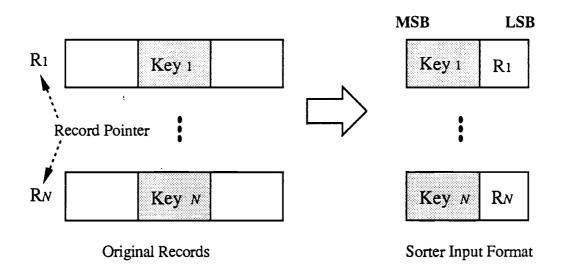

Figure 1.2 Input Data Structure

#### 1.2 Statement of the Problem

Typically a data file is divided into records, the basic units of data processing. Each record is composed of one or more fields and an ordered subset of the fields is designated as the key field or key. Sorting is defined to be the process of rearranging records in ascending or descending order by the relative magnitude of the key fields. When a file to be sorted is loaded into the memory of a local processing unit and the results of the sorting activity are placed in memory as well, the sort is defined to be an internal sort; otherwise, it is an external sort.

The input data structures for a typical hardware sorter are indicated in Figure 1.2. The key fields are extracted from each record and the keys plus associated pointers are compared. When the key field is extracted the record pointer is added to the key so

that the original record order may be preserved. This procedure is accomplished by a sort preprocessor, which retrieves the keys and record pointers for each record before sorting, and restores the original records following sorting, if desired.

The most common methods of organizing disk files are sequential, partitioned, indexed sequential, and direct organization The disk I/O access model is dependent upon the file [13]. organization, the I/O blocking factor, the disk scheduling method, and The output of an external merge sorter is a the disk access time. sequence of records in ascending or descending order. Records are generally distributed on the disk, prior to sorting, in random order. For all practical purposes, file organization can be defined as a partitioned sequential organization since the output of the external merge sort is a sequence of sorted records. The final output will have one partitioned sequence which corresponds to the entire file, while the initial input of an external merge sort will have one record per partitioned sequence. A partitioned sequential file can be stored and retrieved in a indexed sequential order for each input and output operation.

#### 1.3 Definitions and Notation

The following is a summary of the notation and terms used throughout this study. When additional notation and terms specific to individual sections and/or chapters are introduced, they are defined at the point of introduction.

#### 1.3.1 Definitions

$\log x = \log_2 x$  logarithm based on 2,

$\lceil x \rceil$  = the least integer greater than or equal to x,

$\lfloor x \rfloor$  = the greatest integer less than or equal to x,

$[a,b] = \{x \mid a \le x \le b\}$  or the range of values that lie between a and b inclusively,

$(a,b) = \{x \mid a < x < b\}$  or the range of values that lie between a and b exclusively.

#### 1.3.2 Notation

B =buffer size in bytes,

N = number of records in the input file,

P = number of processors,

S = number of a presorted sequence,

r = record size in bytes,

m = order of merge,

$\alpha$  = disk assess time,

$\beta$  = average rotational latency time (= 1/2 disk rotation time),

$\theta_r$  = disk read time,

$\theta_w = \text{disk}$  write time,

$\delta$  = physical disk block size in bytes,

$\gamma$  = disk cylinder size in bytes,

$\tau$  = total number of blocks (=  $rN/\delta$ ),

- p(n) = complexity of processor,

- t(n) = complexity of time,

- b(n) = complexity of buffer size,

- c(n) = total cost (= p(n) x t(n)).

#### 1.4 Organization of the Study

This study is presented in six chapters, including the introductory chapter. Chapter 2 provides an analysis of existing parallel sorting algorithms. Several previously implemented VLSI sorters are also briefly considered. In addition, three VLSI sorting algorithms with similar structural characteristics are compared and their architectural complexities and concepts are explained. The implementations of these sorters in VLSI are compared in terms of chip area and processing speed. In order for the comparison to be meaningful, they were all implemented with the Genesil silicon compiler [23] in 2-micron CMOS technology.

Chapter 3 presents design methods for the implementation of a rebound sorter originally conceived by Chen et al. [18]. The rebound sort algorithm constitutes the most efficient type of algorithm with respect to chip area and processing time found. Improved and modified features, as well as pipelining control capability and expandability, were added to Chen's original concept. Functional simulation, timing, floorplanning, and routing were performed and are discussed.

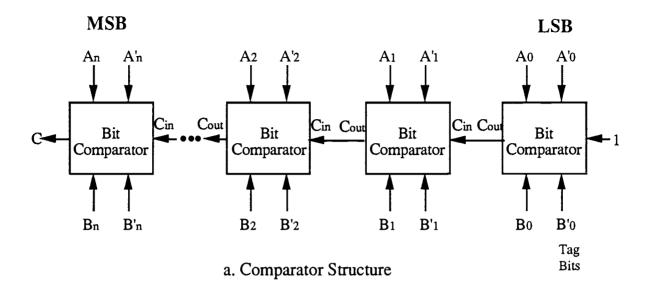

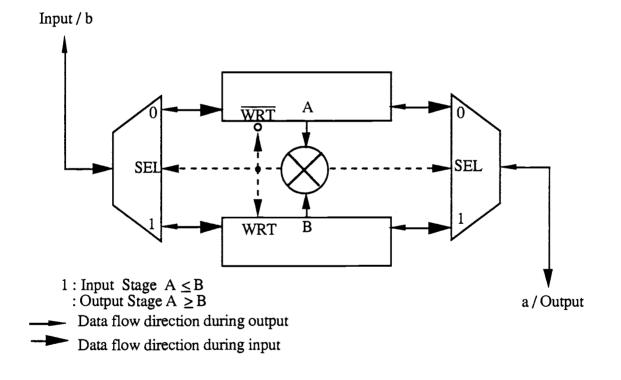

In Chapter 4, several merge sort algorithms are analyzed in terms of VLSI implementation. These algorithms include a parallel binary merge sort algorithm [9,21] and a pipelined merge-sort algorithm [25,47]. Since the disadvantage of external mergers is the requirement of large external buffers, buffer management schemes for reducing on-chip and external RAM size are discussed. Two comparator implementation methods, the first an indirect four-way comparator and the second a direct four-way comparator, are provided for the improvement of processing speed. A VLSI four-way merger is implemented using the indirect four-way comparator technique.

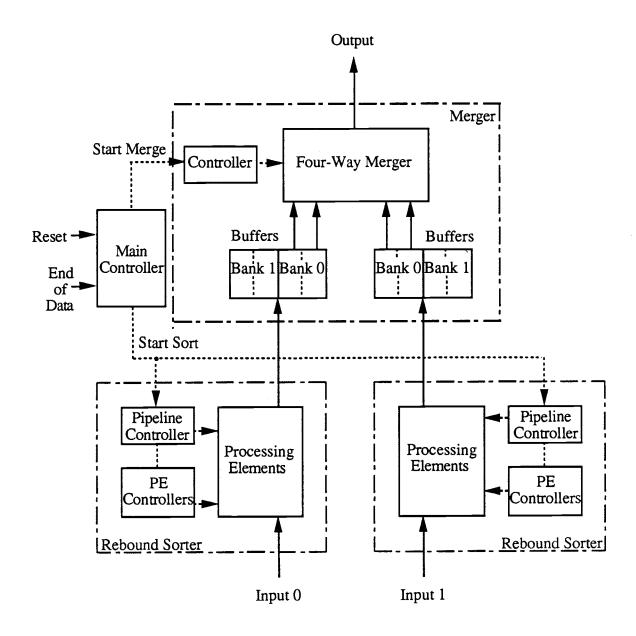

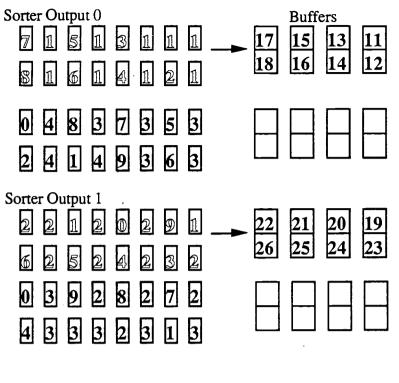

Chapter 5 presents an integrated sort-merge system which combines two rebound sorters and the four-way merger. The system is designed to reduce merger stages and disk I/O access time, based upon the analysis provided in chapter 4. The sort-merge system is designed for implementation on a single chip. This system may be modified if a larger sort-merge system is desired. Additional modular sort-merge systems, which connect individual sorter and merger chips for implementation of more efficient systems are examined. These include an iterative sort-merge system, a tree sortmerge system, and a disk based sort-merge system. The simple disk I/O access model is defined, analyzed, and applied to the external sort-merge system.

Chapter 6 summarizes the results of the study and suggests interesting avenues for further research.

#### 2. PARALLEL VLSI SORTERS

The theory of parallel sorting algorithms has been explored in a number of studies. Some of these algorithms have been implemented in hardware. A few parallel sorting algorithms have been implemented with parallel processors and their performance has been demonstrated [6,22,43]. In this chapter, several sorting algorithms are discussed briefly. Criteria related to the time complexity of each algorithm and its implementation feasibility are presented. According to Akl [3] and Bitton et al. [11], parallel sorting algorithms may be broadly classified in three categories: (1) network sorting algorithms, (2) shared memory sorting algorithms, and (3) parallel file sorting algorithms.

Most of these algorithms require a large number of processors. The number of processors is proportional to N or, at a minimum,  $\log N$  when sorting N keys. Furthermore the size of the keys to be sorted is limited by the internal memory size. The sort performance and cost can be improved when N special VLSI processors are used instead of general purpose processors. Moreover, when sorting very large files, the data I/O transmission time between main memory and the storage devices cannot be ignored. Therefore, external sorting is more desirable than the internal sorting for sorting very large files. The most interesting aspect of parallel internal sorting algorithms is whether or not they can be implemented in VLSI and

whether or not the input and output times can be overlapped with the sorting time.

Five parallel sorting algorithms can be considered, which meet the above criteria: (1) The enumeration sort proposed by Yasuura et al. [50], (2) the VLSI sorter proposed by Miranker et al. [36], (3) the rebound sorter proposed by Chen et al. [18], (4) pipeline merge sort proposed by Todd et al. [47], and (5) the hardware sort-merge system proposed by Takagi et al. [45]. The first three algorithms are analyzed and compared in this chapter, while (4) is discussed in Chapter 4 and (5) is discussed in Chapter 5.

#### 2.1 VLSI Sorters

Sorting algorithms for magnetic bubble memory systems were proposed by Chung et al. [16] and Lee et al. [29] in 1980 and 1981, respectively. Earlier a number of sorting algorithms for other technologies were proposed by Chen and Todd in 1978. VLSI sorting systems which have been implemented were developed by Carey et al. in 1982, Yasuura in 1982, Miranker in 1983, Rajgopal in 1985, and Bate in 1988.

Carey et al. implemented a parallel version of the classic bubble sort algorithm, using a stack-based microarchitecture on silicon [15]. This system has O(N) time complexity and uses a chip area of O(N). The chip is not pipelined and requires 2N cycles to sort an N-element data stream in which 16-bit records, 8-bit integer keys and 8-bit record pointers, are pushed into a single stack. When

records are popped from the stack, they are returned in ascending order. The core chip area was 7000 microns by 7000 microns (280 mils by 280 mils), excluding the power and I/O pads. Each chip has the capability of producing 32 16-bit sorted records at its output. The maximum estimated speed achieved by this system was about 0.84 MHz. The chip, which can be cascaded, may be used as a disk block buffer for a database machine.

Rajgopal et. al implemented Yasuura's parallel enumeration sort [39]. This implementation was also not pipelined. Its time complexity were approximately the same as the sorter developed by Carey et al. Rajgopal's implementation requires 2N cycles to sort an N element data stream and a single chip can sort 8 16-bit keys. Following the sorting activity, the index of the sorted key value is returned. Given the 8-key limit of each chip, 32 chips can be directly cascaded to sort up to 256 keys. The total die area was 9200 microns by 7900 microns (368 mils by 316 mils) in 4-micron NMOS technology. No speed performance estimates were given for this chip.

Bate implemented the rebound sorter in pipelined VLSI architecture [5]. This implementation achieved O(N) time and area complexity, requiring 2N cycles to sort an N element data stream. A single chip is capable of sorting 16 16-bit keys and cannot be chained. The total area of the chip is about 10000 microns x 10000 microns (400 mils x 400 mils) in 2-micron CMOS technology and it achieves speeds up to 5.7 MHz. The chip pipeline controller design is very complex.

Segal described a content-addressable, sequential management chip for the performance of sort and search operations The data management chip consists of an articulated in 1986 [42]. (adjustable) first-in, first-out (FIFO) register and a binary search By implementation of an articulated FIFO register to engine. manipulate data files, sorting times are up to 500 times faster than software sorting routines and the time complexity and area were almost proportional to N. With 1024 bytes of internal RAM, the chip treats each key as if it had two constant width fields, i.e., a key field of 1 to 255 bytes and a pointer of 0 to 255 bytes. Up to 256 of these chips may be cascaded, enabling the sorting of 256 Kilo(10<sup>3</sup>) bytes of data. The chip is fabricated with 1.6 micron CMOS technology and data speeds of 2.6M bytes per second at a clock rate of up to 16 MHz have been achieved. It is a powerful commercial sorting chip, but has 8-bit data bus to transfer data to and from the chip.

#### 2.2 Analysis of VLSI Parallel Sorters

Many parallel sorting algorithms have been proposed for hardware or software implementation [2,4,7,14,18,36,40,44,47,50]. Few of these algorithmic architectures are suitable for implementation in VLSI [27]. The VLSI implementations must be small and capable of high performance in order to be commercially feasible. Many of the proposed implementations do not satisfy these criteria. Thompson [46] discussed the time-area complexity of VLSI sorters for 13 algorithms in order to find the existence of an area x time<sup>2</sup> tradeoff sorting problem. The area x time<sup>2</sup> performance

figures for most of the designs were close to the theoretical minimum value,  $O(N^2 \log N)$ . In addition, Leighton and Bilardi conducted a study of the upper and lower bounds for this problem [8, 30]. These studies concentrated on the time-area complexity of the number of circuits, including the wires and gates, number of bits, and the time required to sort N keys. Possible restrictions on input and output times were removed.

In the following sections, three other algorithms, each requiring N processors for sorting N keys, having an area proportional to N, are considered in more detail from the standpoint of time and processor complexity: (1) the enumeration sorter [50], (2) the VLSI sorter [36], and (3) the rebound sorter [18].

#### 2.2.1. Enumeration Sorter

The enumeration sort can be regarded as two separate procedures, an ordering process and an arranging process. Ordering is the process of determining the order of each key in the set of keys,  $K = \{k_1, k_2, ..., k_n\}$ . When  $k_i$  is the  $i^{th}$  smallest key in the set of keys, K, the result returns the order  $c_i$  equal to i-1 corresponding to  $k_i$ . The order  $c_i$  is calculated by counting the results of comparisons between  $k_i$  and all of the keys in K. In turn, rearranging is performed by software, through the host computer or a memory device with special mechanisms. A block diagram for this algorithm is shown in Figure 2.1 and an example of the enumeration sorter operation is shown in Figure 2.2.

a. Parallel Enumeration Sorter Block Diagram

b. Enumeration Sorter Cell Block Diagram

Figure 2.1 Enumeration Sorter Block Diagram

Figure 2.2 Enumeration Sorter Operation

```

begin

for i=1 to N do in parallel

c_i=0

for j=1 to i-1 do /* k_i=k_i and i < j > c_i < c_i */

if k_i \ge k_j then

c_i=c_i+1

end if

end for

for j=i to N do

if k_i > k_j then

c_i=c_i+1

end if

end for

end for

```

Figure 2.3 Enumeration Sort Algorithm (Algorithm 2.1)

Algorithm 2.1 shown in Figure 2.3 assures that two or more keys are not stored in the same location and that if  $k_i = k_j$  and i < j, then  $c_i < c_j$ . N processor elements execute Algorithm 2.1 and compute orders in parallel. Keys and their orders are transmitted serially between the memory device and a sorting circuit which

performs the ordering process. Input/output time completely overlaps the sort processing time.

The number of processors, p(N), for Algorithm 2.1 is N. The total time required is  $O(N^2)$ . The time complexity for N processors is,

$$p(N) = N,$$

$$t(N) = \frac{O(N^2)}{O(N)} = O(N),$$

and the total cost, c(N), is

$$c(N) = p(N) \times t(N) = O(N^2)$$

The ordering process requires 2N cycles. The algorithm requires a host computer rearranging process following completion of the ordering process. The reordering process is of O(N) time complexity.

#### 2.2.2. The VLSI Sorter

The VLSI sorter proposed by Miranker et al. [36] are similar to the basic operations of the bubble sorter proposed by Lee et al. [29]. However, the cell microarchitecture is considerably different. This sorter consists of a linear array of  $\lceil N/2 \rceil$  cells, each of which has an array of 1-bit comparators and memory elements. For instance, n-bit basic cells, dibit cells, are connected with each other to sort n-bit key fields. Each cell is connected to the cells above and below it in order to establish data communication and proper data movement during sorting. The block diagram of the basic dibit cell and the overall comparator structure is shown in Figure 2.4 and a sorting example of the VLSI sorter is provided in Figure 2.5.

### b. Dibit Cell Block Diagram

Figure 2.4 Basic Cell of the VLSI Sorter

Figure 2.5 The VLSI Sorter Operation

The VLSI sorter can sort keys in ascending or descending order by modifying the data flow direction. Each sorting step has two phases:

- 1. Compare Phase: Two keys in each cell are compared each other.

- 2. Transfer Phase: Depending on the result of the comparison, one of the two keys is transferred to a neighboring cell and the original cell receives an item from its remaining adjacent cell.

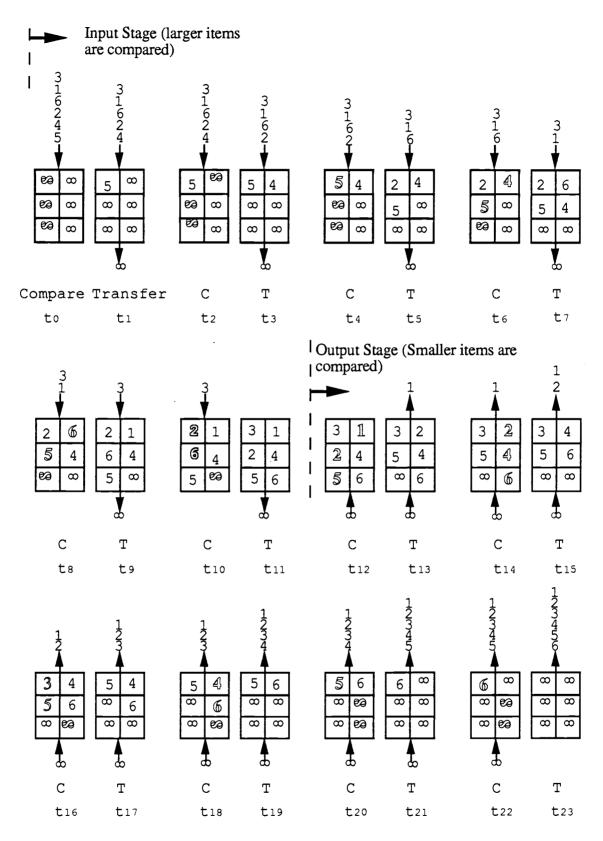

The VLSI sorter cell contains two stages, an input stage and an output stage. In the input stage, the larger of the two keys in each cell is transferred downward so that the smallest key is located in the top cell and the largest key is located in the bottom cell. In general, the  $i^{th}$  smallest key must be in one of the top i cells. In the output stage, the smaller of two keys in each cell is transferred upward (Figure 2.6, Algorithm 2.2).

The time required for Algorithm 2.2 is  $O(N^2)$ . When N/2 processors are used, the time complexity is O(N):

$$p(N) = N/2 = O(N),$$

$$t(N) = \frac{O(N^2)}{O(N)} = O(N) ,$$

and

$$c(N) = p(N) \times t(N) = O(N^2)$$

.

This algorithm can be used to sort one ascending order and one descending sequence. The total sorting time is 4N cycles to sort N keys with N/2 processors.

```

begin

for j = 1 to N/2 in parallel

/* Input stages */

for i = 1 to N

if a_j \le b_j then /* larger data are transferred */

a_{j+1} = b_j \text{ or } b_{j+1} = b_i

b_{i} = \max(a_{i-1}, b_{i-1})

else

a_{j+1} = a_j or b_{j+1} = a_i

a_i = \max(a_{i-1}, b_{i-1})

end if

end for

for i = N+1 to 2N /* Output Stage */

if a_i < b_i then /* smaller data are transferred */

b_{i-1} = a_i or a_{i-1} = a_i

a_i = \min(a_{i+1}, b_{i+1})

else

a_{i-1} = b_i or b_{i-1} = b_i

b_i = \min(a_{i+1}, b_{i+1})

end if

end for

end for

end

```

Figure 2.6 The VLSI Sorter Algorithm (Algorithm 2.2)

#### 2.2.3. Rebound Sorter

The rebound sorter is a new sorting scheme based upon an improvement of the uniform ladder sorter [48], which is an N-loop shift register structure capable of holding N keys with one key per

loop [17]. This storage structure is suitable for hardware implementation. The algorithm is a variation of the odd-even transposition sort algorithm. If the time for circulating data within a loop is called a period, then N keys stored in the ladder can be sorted in (N+1)/2 periods, using (N-1) comparators.

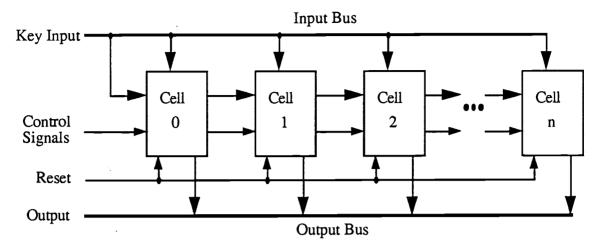

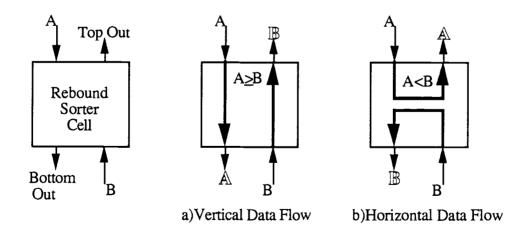

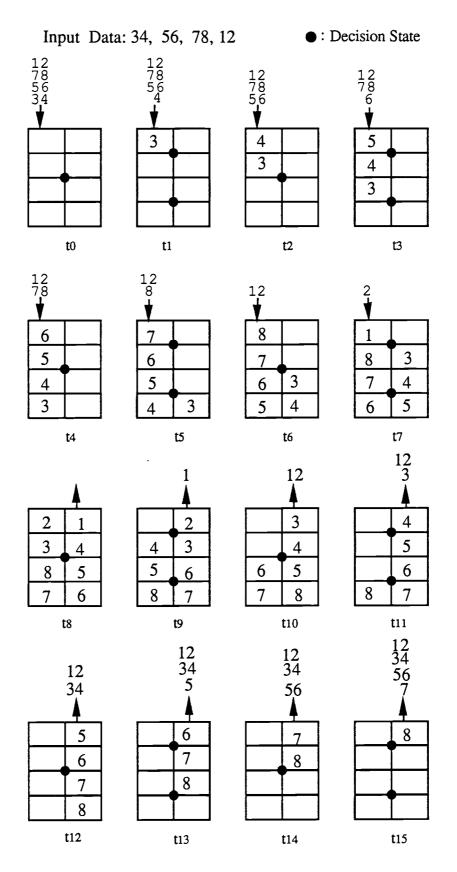

Input and output time completely overlap sorting time. The rebound sorter cell consists of a controller, memory elements, and a data steering unit. Multiple instances of the basic cell are used to compose the complete sorter. The basic building block known as the steering unit, contains an upper-left cell, U, and a lower-right cell, L, as shown in Figure 2.7. A sorter for N keys is assembled by connecting (N-1) steering units, plus the top and bottom cells. An example of the rebound sorter operation is shown in Figure 2.8.

In the rebound sorter, keys are divided into two parts: the most significant and the least significant parts. The most significant part of a key is fed into the sorter and the least significant part of the key follows after one clock period. Thus, in order to sort an N key sequence, 4N cycles are required.

The sorter alternates between two states: the decision state and the continuation state. The latter state may be a pass data vertical state, a pass data horizontal state, or a second decision state. In the decision state, each steering unit compares the key stored in its upper-left  $(U_i)$  and lower-right  $(L_i)$  cells, steering the halves of the keys either vertically or horizontally, depending on the comparison results. In the continuation state, each steering unit steers the keys in a direction determined from the previous decision state.

a. Rebound Sorter Structure

b. Rebound Sorter Cell Data Flow

Figure 2.7 Basic Structure of the Rebound Sorter

Figure 2.8 Rebound Sorter Operation

```

begin

for j = 1 to N in parallel

for i = 0 to 2N-1 do

if mod(i,2) = 0 then /* Even processors start */

if L_i \ge U_j then

(1)

L_{j+1} = L_j /* vertical data movement */

U_{j-1} = U_{j}

else if L_{j} < U_{j} then

L_{j+1} = U_j /* horizontal data movement */

U_{j-1} = L_i

end if

else

if L_i < U_j then /* L_i = U_j at cycle (i-1) */

(2)

L_{j+1} = U_j

U_{j-1} = L_j

/* Odd processors start */

else

L_{i+1} = L_i /* L_i > U_i at cycle (i-1) */

(3)

U_{i-1} = U_i

L_{j+1} = U_j /* L_j < U_j at cycle (i-1) */

U_{j-1} = L_j^{\prime}

end if

end for

end for

e n d

```

Figure 2.9 Rebound Sorter Algorithm (Algorithm 2.3)

<sup>1.</sup> Item (1) is the first decision state, item (2) is the second decision state and item (3) is the continuation state.

<sup>2.</sup> Even processors start in the first decision state(1) and odd processors start in the pass vertical state(3)

Algorithm 2.3 (Figure 2.9) requires  $O(N^2)$  time. The time complexity for N processors is

$$p(N) = N - 1 = O(N),$$

$$t(N) = \frac{O(N^2)}{O(N)} = O(N) ,$$

and

$$c(N) = O(N^2).$$

The algorithm requires 4N cycles to sort N keys, but this number can be reduced to 2N cycles if the rebound sorter is pipelined. When the number of comparisons are considered, the rebound sorter exhibits two extreme cases. For the best case, each comparator requires N comparisons to sort N keys; for the worst case, 2N times are required for each comparator. When the values of the half-key are the same, i.e., 2411, 2412 etc., the worst case can be applied. Although the sorter operates according to the worst case, the total time complexity is O(N) with N processors, including the input and output times. No time penalty is incurred for the additional comparison in the hardware implementation of this algorithm. If the algorithm were implemented in software, a time penalty would be incurred.

The time complexity for sorting, in addition to data input/output time is O(N) since pipelining introduces latency in the system only for a particular key. The record division and merge time for the rebound sorter is also absorbed in the sorting time through the employment of a unique buffer management scheme (analyzed in Section 4.3).

### 2.3 Comparison of Parallel VLSI Sorters

In the previous section, three sorting algorithms amenable to implementation in VLSI were analyzed. These algorithms can be further analyzed from the point of view of total chip area and system performance. Table 2.1 provides the performance and chip area data for the three parallel VLSI sorters [1]. Representative internal blocks from each of these sorters were synthesized on a silicon compiler in order to obtain these area and performance estimates.

The VLSI sorter (Algorithm 2.2) of Miranker  $et\ al.$  [36] has the smallest overall chip area, using N/2 cells to sort N keys. The parallel enumeration sorter (Algorithm 2.1) developed by Yasuura  $et\ al.$  [50] requires the largest chip area. Though the chip area of the rebound sorter is slightly larger than that of the VLSI sorter, its performance is much better, i.e., the processing speed of the rebound sorter is twice as great as the VLSI sorter.

Among all of the parallel VLSI sorters analyzed to implement using silicon compilation technology, the comparators determined the critical timing path. The comparators were built using subtracter blocks included within a parallel datapath, which is a fundamental microarchitectural element contained in the silicon compiler's building block library. Other comparator structures, such as those implemented with programmable logic arrays (PLA) and random logic (or logic gates), used excessive chip area and their performance were poor due to the excessive wiring requirement.

Table 2.1 Comparison of VLSI Sorters

|                       | Functional Blocks<br>of 1 Sorter Cell                                                                   | Area of Each<br>Functional Block<br>(mils x mils)      | Total Area<br>of N Cells<br>(mils x mils) | No of<br>Clock<br>Cycles | Maximum<br>Clock<br>Frequency |

|-----------------------|---------------------------------------------------------------------------------------------------------|--------------------------------------------------------|-------------------------------------------|--------------------------|-------------------------------|

| Enumeration<br>Sorter | <ul><li>2 16-bit data register</li><li>1 16-bit comparator</li><li>1 8-bit counter</li></ul>            | 2× 3.60 x115.19<br>52.24 x 11.81<br>16.67 x 27.98      | N × 1903.31                               | 2 <i>N</i>               | 6 MHz                         |

| The VLSI<br>Sorter    | <ul><li>2 16-bit data register</li><li>1 16-bit comparator</li><li>2 16-bit 2-way multiplexer</li></ul> | 2 × 3.60 × 115.19<br>52.24 × 11.81<br>2 × 3.96 × 46.80 | N/2 × 1807.54                             | 4 <i>N</i>               | 6 MHz                         |

| Rebound<br>Sorter     | 2 8-bit data register 1 8-bit comparator 2 8-bit 2-way multiplexer                                      | 2× 3.60 × 62.75<br>30.89 × 11.81<br>2× 3.96 × 24.83    | N × 1013.27                               | 2N (pipelined)           | 17 MHz                        |

Note: Assumes equal area for controllers

The 8-bit comparator utilized by the rebound sorter is much faster than the 16-bit comparators used in the other sorters. In order to increase the processing speed for the 16-bit comparators, the area must be increased to twice that shown in Table 2.1. The estimated maximum frequency for the resulting high speed comparators is 6 MHz, when static carry technology is employed and 14 MHz when a precharged carry chain is used. When a precharged carry chain is implemented, it is necessary to add additional circuitry to overcome the significant timing problems which result. Therefore, the rebound sorter is the most feasible structure for VSLI implementation in terms of performance and overall chip area.

#### 2.4 Conclusion

Three parallel VLSI sorting algorithms which have very similar characteristics were analyzed for time complexity. Although there were slight differences, each achieved O(N) time complexity with O(N) processing elements. The enumeration sorter proposed by Yasuura et al. [50] fails to consider the internal delay of the counter for each cell and the rearranging process time. The more the total number of processors is increased, the greater the counter delay time and the larger the counter area must be in order to reduce delay time.

The VLSI sorter proposed by Miranker et al. [36] has a suitable algorithm for VSLI implementation since it requires fewer processors, N/2 processors, than the others. However, its speed is twice as slow as the others. Considered by itself, the VLSI sorter

comparator achieves only one-half the speed of its rebound sorter counterpart. To improve comparator speed, other design methods or the application of lower level VLSI CAD tools should be considered. Consequently, the rebound sorter is the most efficient in terms of processing speed and chip area. Processing speed is twice that of the others and the chip area is one-half of the enumeration sorter area and only slightly larger than the VLSI sorter. However, for the rebound sorter an external preprocessor is required to decompose the records and merge them following the sort. Implementation methods for merging two half-keys are discussed in Chapter 4.

#### 3. THE REBOUND SORTER

In the previous chapter, three parallel VLSI sorting algorithms [18,36,50] with O(N) time complexity were analyzed in terms of processing speed and chip area and the rebound sorter was determined to be the most cost effective. In this chapter, processing elements, pipeline control, and the expandability of the VLSI implementation of the rebound sorter are discussed. Detailed design methods, including floorplanning and timing issues, are discussed as well as the functional simulation of the chip for purpose of design verification.

To build each module of the sorter, several possible design methods were considered and compared. The smallest chip area and the lowest delay times were selected and a basic processing element was designed and replicated in order to build the complete rebound sorter with the capability of sorting eight 16-bit keys. For VLSI design, delay time considerations of block modules were an important factor since the delay time affects overall system chip size and performance.

# 3.1 Design Considerations

To formulate a simple design process the following assumptions were necessary:

- 1) The order of sorting is performed such that keys emerge from the sorter in ascending order. Larger keys will descend to the bottom of the sorter upon entry, while smaller keys ascend toward the top.

- 2) Keys to be sorted are directed to the rebound sorter's input port and sorted keys exit through the output port.

- 3) The size of each key is 16 bits. In general, key size is arbitrary and this requirement can be made variable by hardware modification (refer to Section 3.9).

- 4) If the number of keys exceeds the capacity of the sorter, additional sorting chips can be chained; alternatively, an external merger can be used to merge numbers of sorted strings for sorting more than N keys.

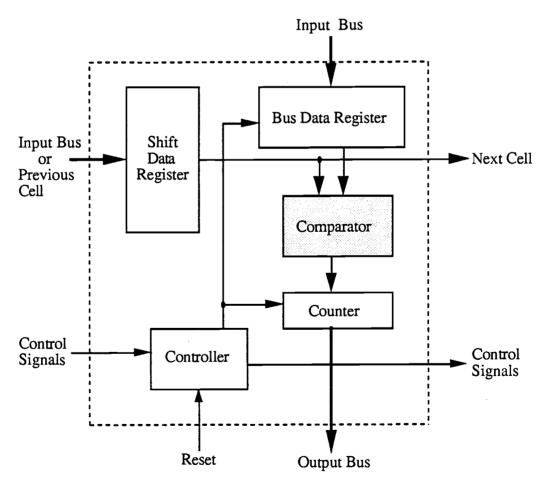

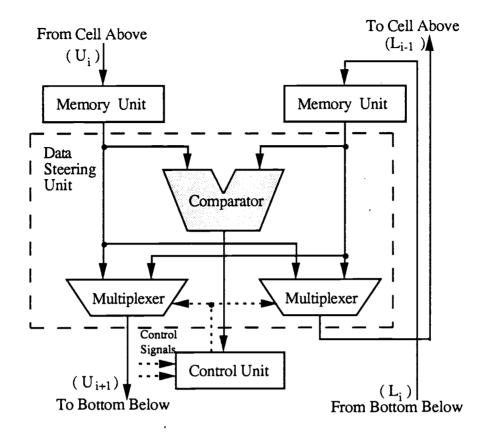

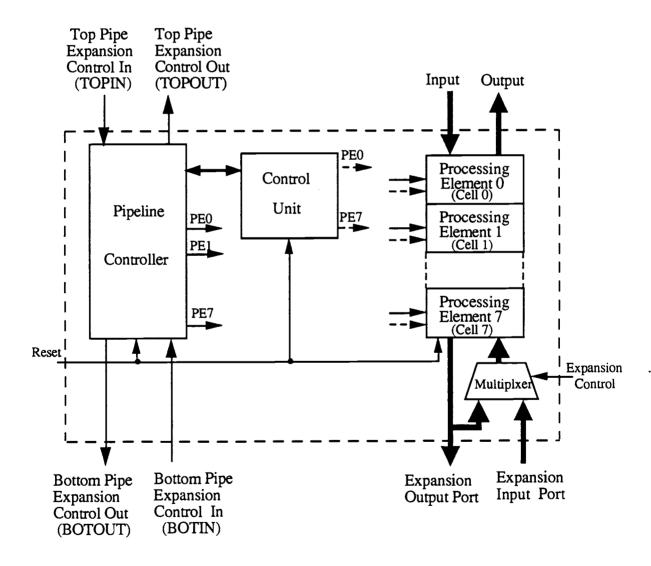

To sort N keys, the rebound sorter includes N identical processing elements and one pipeline controller. Each processing element is composed of two memory units, two data steering units, and a control unit. A block diagram of the processing element is shown in Figure 3.1.a [1]. The memory unit, the comparator, and the data steering unit are designed as a single datapath module, using silicon compilation technology, to minimize chip area and reduce interconnections among the separate modules. The control unit is a finite state machine (FSM) built using a programmable logic array (PLA).

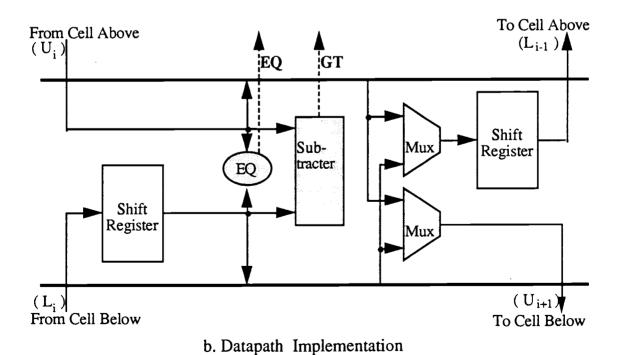

# 3.2 Processing and Memory Elements

The steering and memory units for the processing element are included within the same datapath module as indicated in Figure 3.1.b. The memory unit consists of two transparent latches, which retain the data for a complete clock cycle. New data is loaded into the first latch on phase A and into the second latch on phase B. The comparator is composed of a subtracter plus an equal flag unit within the datapath module. Comparator output signals are "greater-than" and "equal-to" and are provided as inputs to the PLA FSM controller during the same clock phase.

The steering unit, consisting of a comparator and two multiplexers, compares two keys, one-half of a key at a time. functional terms, the most significant half-key of a particular key from the sorter cell above is applied to the upper left input  $(U_i)$  of the cell in question, while the most significant half-key of a second key from the cell below is applied to the lower right input  $(L_i)$  of The steering unit moves the input half-keys through the the cell. cell vertically or horizontally, depending upon their relative magnitudes as determined by the comparator. The smaller value of the two half-keys ascends to the upper right output  $(L_{i-1})$ , while the larger value of the two half-keys descends to the left lower output  $(U_{i+1})$ . If the values of the two half-keys are equal, data movement is vertical and in the next clock cycle the least significant half-keys which follow are compared. Data comparison and movement of the least significant half-keys in the second clock

a. Processing Element of Rebound Sorter Cell

Fig 3.1 Block Diagram of a Processing Element

cycle are conceptually identical to those for the most significant half-keys. All controller signals are dependent upon the comparison results and multiplexers are used to change data flow direction.

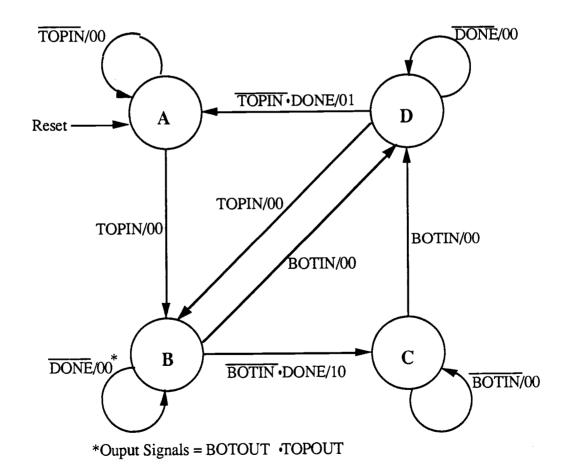

#### 3.3 Controller

The controller for the processing element consists of a finite Three possible implementation methods were state machine. this combinational considered for unit: Α pure implementation, the use of a read only memory (ROM), and the use of a programmable logic array. The PLA approach allowed for rapid design, due to the existence of a PLA generator in the silicon compiler. The controller receives inputs from the comparator and, when pipelining is implemented, from an external controller. on these inputs, the controller determines the next state of the state machine, and provides multiplexer outputs to steer incoming halfkeys in the proper direction during each clock cycle.

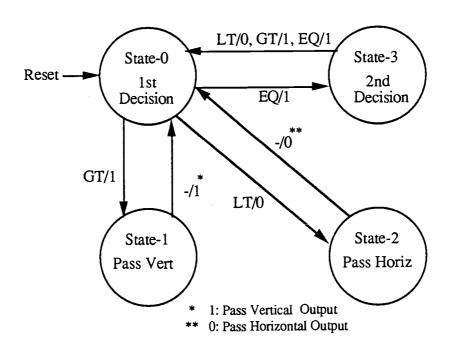

The controller state table is shown in Table 3.1 and its state diagram is shown in Figure 3.2 [1]. In Figure 3.2, each node in the diagram represents a controller state and each edge represents the state transition and its associated inputs and outputs as illustrated. The left and the right sides of the "/" are, respectively, input and output, while the dash, "-" indicates a "don't care" condition. The input signals are reset, GT (greater than) and EQ (equal to) and the output signal which controls the multiplexers is pass-vertical if output = 1 and pass-horizontal if output = 0.

Table 3.1 Controller State Table

|                 | Next State, Output * |                  |    |              |

|-----------------|----------------------|------------------|----|--------------|

|                 | GT•EQ                |                  |    | 10           |

| Present State   | 00                   | 01               | 11 | 10           |

| D1 (State-0)    | <b>PH</b> ,0         | <b>D2</b> ,1     | X  | <b>PV</b> ,1 |

| PV (State-1)    | <b>D1</b> ,1         | <b>D1</b> ,1     | X  | <b>D1</b> ,1 |

| PH (State-2)    | <b>D1</b> ,0         | <b>D1</b> ,0     | X  | <b>D1</b> ,0 |

| D2<br>(State-3) | <b>D1</b> ,0         | <b>D1</b> ,1     | X  | <b>D1</b> ,1 |

| Reset           |                      | n PE -<br>I PE - |    |              |

D1: First Decision

PV: Pass Vertical

PH: Pass Horizontal

D2: Second Decision

X: Don't cares

\*1: Pass Vertical Output

0: Pass Horizontal Output

Figure 3.2 Controller State Diagram

The controller has four states as follows:

- 1) At State-0 (State-D1), the initial decision state, comparison of the two half-keys is performed, *i.e.*, the most significant halves of the pair of keys in question. One half-key is provided at the upper left input  $(U_i)$ , while the other half-key appears at the lower right input  $(L_i)$ . These are moved vertically if the upper left half-key  $(U_i)$  is greater than or equal to the lower right half-key  $(L_i)$ . When the upper left input  $(U_i)$  is less than lower right input  $(L_i)$ , the half-keys are moved horizontally.

- 2) State-1 (State-PV) is entered when the half-key  $(U_i)$  is greater than the half-key  $(L_i)$ . In this case, the second or least significant half-keys are also passed vertically, a process which occurs because the initial decision has already determined which half-key is larger and no additional magnitude decisions are required.

- 3) State-2 (State-PH), in which the second or least significant half-keys are passed horizontally, is entered when the upper left input half-key  $(L_i)$ , is less than the lower right half-key  $(U_i)$ .

- 4) State-3 (State-D2) is entered if the upper left input half-key  $(U_i)$ , is equal to the lower right half-key  $(L_i)$ . This is a second decision state, which compares the least significant half-keys to determine proper data flow direction.

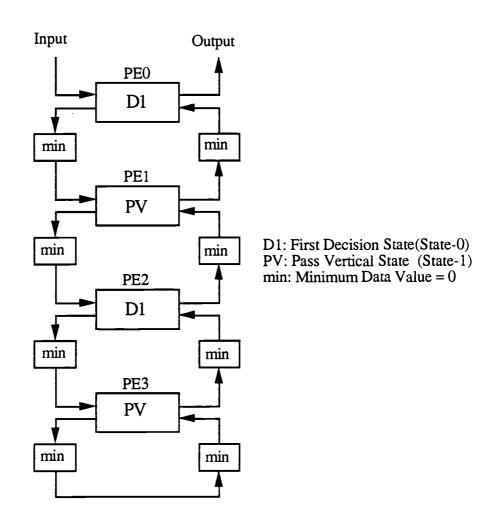

All processing elements operate synchronously. The PE control units, shown in Figure 3.3, are initialized as follows:

- 1) Even PEs from the input stage, e.g., PE0, PE2, are initially set to State-D1 when the reset signal is received.

- 2) Odd PEs from the input stage, e.g., PE1, PE3, are initially set to State-PV when the reset signal is received.

Figure 3.3 Initial State of the Rebound Sorter

### 3.4 Pipeline Control

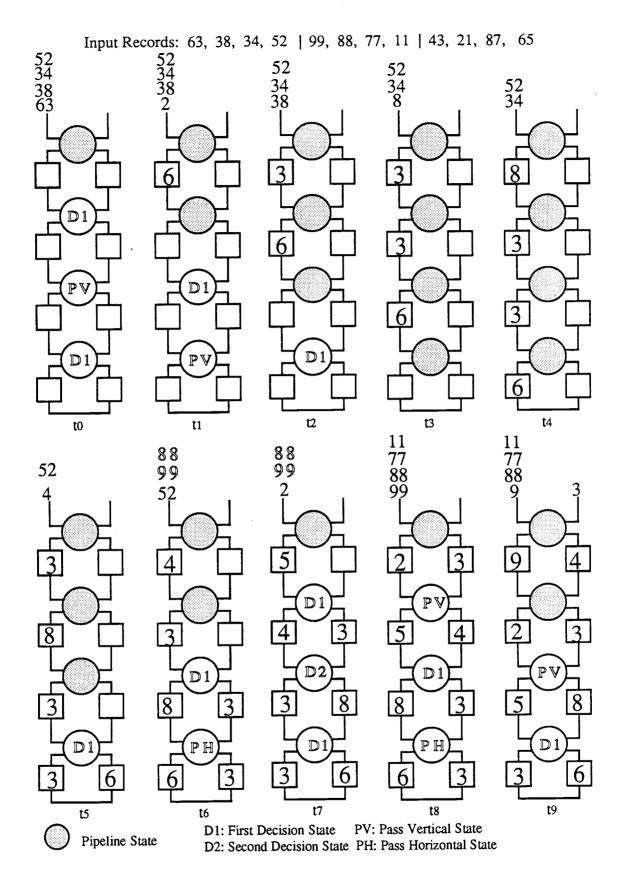

The rebound sorter is capable of holding and processing N keys, producing sorted strings of the same length at its output. In order to maximize performance, input and output operations must take place simultaneously. This requires presentation to the sorter of new, unsorted keys while the previously sorted keys associated with earlier input data are emerging at the output. This process is referred to as pipelining. An example of the pipelined rebound sorter operation is provided in Figure 3.4.

In the pipelined rebound sorter, it is assumed that the sorter is filled with data currently in the process of being sorted. New unsorted keys enter as input and descend through the system without being sorted for 2N clock cycles. On completion of 2N cycles, the new half-keys are compared, while the remaining half-keys within the sorter associated with an earlier input sequence continue to emerge, undisturbed, from the sorter's output.

A specialized controller provides the necessary control signals to each sorter cell for the correct implementation of pipelining, which is implemented as follows:

- 1) First, the incoming N keys are isolated from the current set of N keys

- 2) When the new incoming keys descend to the bottom cell of the sorter, comparison is initiated and the previously sorted data ascends vertically to the output port.

Figure 3.4 Pipelined Rebound Sorter Operation

Figure 3.4 Pipelined Rebound Sorter Operation (Continued)

3) The pipeline control signals produced by the specialized PLA FSM to assure correct operation during pipelining are illustrated in Figure 3.5.a.

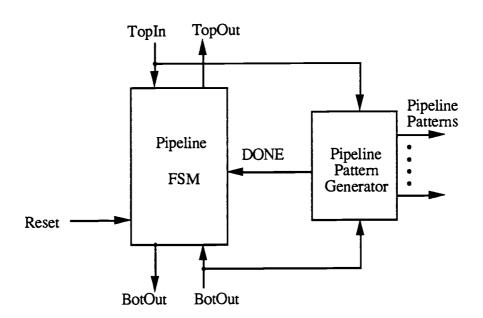

The PLA pipeline control signals are implemented in two stages. First a pipeline FSM, as indicated in Figure 3.5.b produces a control sequence. A pipeline pattern generator then translates this sequence into the appropriate pipeline control pattern. For ease of design and maintenance, this method is preferable to the combination of two blocks in a single FSM. The pipelined state machine controller may be expanded if it is desired to chain several sorters together. The pipelined FSM state table and diagram are shown in Table 3.2 and Figure 3.6, respectively.

# 3.5 System Expansion

Since the sorter chip is capable of maintaining only N keys internally, large files must be sorted using multiple sort chips. To provide this expansion capability, the rebound sorter of Chen et al. [18] was modified to encompass multiple chips chained in series. The design requirements resulting from this decision include the following [1]:

1) Pipeline control signals have the capacity to pass across multiple chained chips.

|                 | <b>t</b> 0 | t1 | t2 | t3 | t4 | t5 | t6 | t7 |

|-----------------|------------|----|----|----|----|----|----|----|

| PE <sub>0</sub> | 1          | 1  | 1  | 1  | 1  | 1  | 1  | 1  |

| PE <sub>1</sub> | 0          | 1  | 1  | 1  | 1  | 1  | 1  | 0  |

| PE2             | 0          | 0  | 1  | 1  | 1  | 1  | 0  | 0  |

| PE3             | 0          | 0  | 0  | 1  | 1  | 0  | 0  | 0  |

1: Pipeline control signal0: Normal operation

# a. Pipeline Control Signal Patterns

b. Pipeline Control FSM Block Diagram

Figure 3.5 Pipeline Control Block Diagram and Signal Patterns

| Table | 3.2 | Pipeline | Control | FSM | State | Table |

|-------|-----|----------|---------|-----|-------|-------|

|-------|-----|----------|---------|-----|-------|-------|

|               | Next State, Output (BOTOUT, TOPOUT)                 |                                                     |  |  |

|---------------|-----------------------------------------------------|-----------------------------------------------------|--|--|

|               | DONE = 0                                            | DONE = 1                                            |  |  |

|               | TOPIN BOTIN                                         | TOPIN •BOTIN                                        |  |  |

| Present State | 00 01 10 11                                         | 00 01 10 11                                         |  |  |

| A             | A,00 A,00 B,00 B,00                                 | A,00 A,00 B,00 B,00                                 |  |  |

| В             | <b>B</b> ,00 <b>D</b> ,00 <b>B</b> ,00 <b>D</b> ,00 | C,10 D,00 C,10 D,00                                 |  |  |

| С             | C,00 D,00 C,00 D,00                                 | C,00 D,00 C,00 D,00                                 |  |  |

| D             | <b>D,00 D,00 B,00</b> , <b>B,00</b>                 | <b>A</b> ,01 <b>A</b> ,01 <b>B</b> ,00 <b>B</b> ,00 |  |  |

Figure 3.6 Pipeline Control FSM State Diagram

2) All chained chips are aware of their own position in the chain, i.e., chips at the top of the chain perform I/O operations in correct order and chips at the bottom of the chain automatically connect their lower-left output to their lower-right input.

A block diagram of the complete VLSI rebound sorter chip with expansion capability is shown in Figure 3.7 [1]. The control unit recognizes the expansion by triggering the control signals, which are described as follows:

- 1) The reset signal initializes all chip controllers simultaneously, including the pipeline control FSM.

- 2) The expansion control signal determines the source of the data applied to the lower processing element (cell) of the sorting chip. Data input originates either from another chip or from its own lower-left output port.

- 3) The top/bottom pipe control expansion input/output signals are used to enable pipelined pattern generation for a chain of chips.

The input and output of the data bus is processed through an expansion multiplexer as follows:

- 1) When the expansion control signal is low, the lower cell input is routed directly from the lower-left chip cell.

- 2) When the expansion control signal is high, lower cell input is routed from another chip.

- 3) When the sorting chip is the lowest of the chained chips, the bottom input and output of the pipe control expansion signals are connected directly.

- 4) When the sorting chip is the highest chained chip in a series, the top input and output of the pipe control expansion signals are connected directly.

Figure 3.7 Rebound Sorter Block Diagram

## 3.6 Silicon Compilation

The Genesil silicon compiler is the computer-aided design (CAD) tool for VLSI design used in implementing this architecture. Silicon compilation allows a hierarchical design methodology to be employed whereby large systems are decomposed into datapath modules, general modules, blocks (e.g. RAM, ROM, PLA, I/O Pads, etc.) and random logic. Both timing verification and sophisticated logic simulation capabilities are provided by this CAD tool.

The rebound sorter shown in Figure 3.7 is composed of the Genesil silicon compiler building blocks [23]. The basic sorter processing element, steering unit and memory unit, was implemented with a parallel datapath module, resulting in the reduction of chip area and in increased performance in comparison to other possible logical implementations. The memory units were also included within the datapath module to reduce chip area, and the sorter cell and the pipeline controllers were implemented with PLA finite state machines.

The total die area, including the power ground, clock, and input and output data pads consumes 5801 microns by 5283 microns (228 mils by 208 mils) in 2-micron CMOS technology. This chip can be packaged in a 48-pin pin-grid array, although only 40 of the pins are utilized. Since the chip core area is 159.2 mils by 146.8 mils, the chip potentially could be expanded to include up to 32 processing elements within an area of 400 mils by 400 mils.

## 3.7 Functional Simulation and Timing

Simulation was performed on functional models constructed from the compiler block specification tools. Successful design verification required that both switch-level and functional models pass the same set of test vectors. Using a synchronized two-phase clocking system, the individual modules, PLAs, and blocks were simulated, verifying their functionality and performances. When a basic module or block was designed, functional verification was used to debug each element in the design hierarchy prior to moving to a higher design level. Top-down architectural definition and decomposition into an appropriate microarchitecture, followed by bottom-up implementation and verification, proved to be a successful methodology.

Four test verification procedures were conducted for: (1) A complete sorted input sequence (ascending order); (2) A complete sorted sequence (descending order); (3) An unsorted random sequence;, and (4) A sorted sequence consisting of the most significant half-keys of keys with the same digits, e.g., 1123 and 1122. The test sequences were recorded in a set of test vector files. All of the above sequences verified the operation of the rebound VLSI sorter at the chip level.

Timing analysis provided a design consistency check (type checking) against the block level timing attributes used in the logic design process. Using a two phase, non-overlapping clocking method, the timing references for all logically associated clocked devices were checked. All of the data and control signals for a

block instance were classified as either valid, stable, or propagate with respect to the phase pair associated with the specific block. This verification tool also automatically calculated worst-case signal propagation delays through all timing paths, plus the input setup and hold times. It also provided the maximum attainable system clock rate. The rebound sorter design achieved a performance rate of 17M bytes/sec. The critical path and major block delay times of the rebound sorter chip are shown in Figure 3.8.

## 3.8 Floorplanning and Routing

Floorplanning consists of the placement of design objects on the chip, the assignment of routing channels, and the implementation of appropriate external connections. Floorplanning was conducted in three steps: placement, fusion, and pinout. Placement specified the initial location of objects, fusion defined the wiring channels, and pinout specified the external inputs and outputs.

Design objects for the rebound sorter consist of eight processing elements, one controller, and one pipeline controller. To reduce chip area and propagation delays and minimize wiring complexity, the 10 modules were given an adjacent placement and aligned with their respective signal ports. From this position they may be turned, rotated, and/or flipped. A number of trial-and-error attempts were repeated in order to obtain the final placement. Upon completion of floorplanning, the core size without pads was 159 mils by 146 mils.

Figure 3.8 Critical Path and Major Delays of the Rebound Sorter

### 3.9 Architectural Extension

The rebound sorter has an 8 keys, 16-bit per key sorting capacity, as noted previously. In the architecturally expanded version of the rebound sorter, the key length can be increased in 16-bit increments. This scheme is shown in Figure 3.9. The performance of the expanded sorter increases because of the additional parallelism provided. At the same time, the clock rate decreases slightly with expansion due to the carry propagation across multiple chips. The only special design requirement is the addition of an external controller. In order to use variable key lengths, a dynamic method of configuration may be considered. In systems where a small number of large keys are required, the sorter subsystems would operate in parallel; in systems where a large number of small keys are to be sorted, the sorter subsystems could be configured serially.

#### 3.10 Conclusion

The proposed design is only one illustration of several possible methods of implementation of the rebound sorter architecture, as modified and extended. The feasibility of implementing the proposed sorting engine using silicon compilation technology has been demonstrated.

A simple and efficient processor element design for this sorter has been achieved. The pipeline control unit consists of a pipeline FSM and a pipeline pattern generator, a methodology which makes for ease of maintenance and provides for future expansion. The overall size is less than one-half the area of Bate's design [5], achieving a speed which is three times as fast.

The proposed chip is capable of sorting eight 16-bit keys. It can readily be expanded to handle larger files, through either the use of smaller geometry technology or chaining, or in conjunction with an appropriate external hardware merger structure. The increase of the key length was discussed. The proposed design is based upon 16-bit data, but the length of the key can be extended to much larger sizes, dependent upon specific processor application speeds.

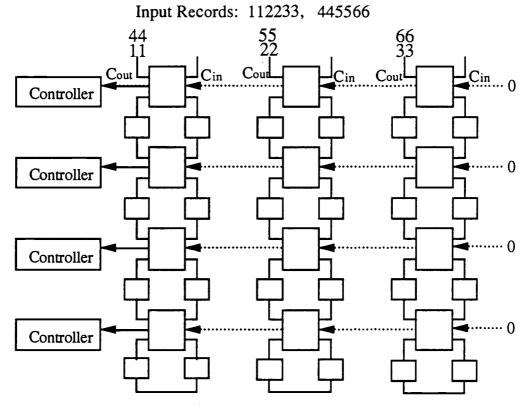

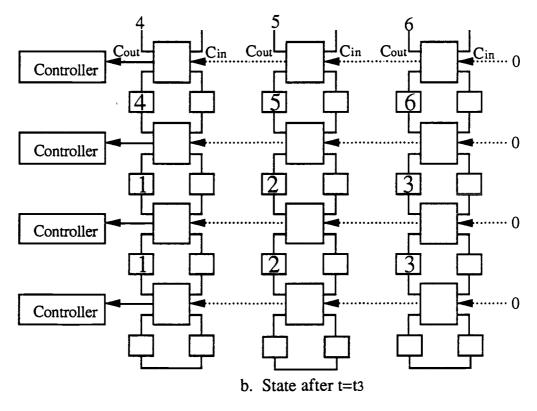

a. Connection Diagram and Initial State at t=t0

Figure 3.9 Architectural Extensions

### 4. EXTERNAL PARALLEL SORTING

External sorting is a process based on the repeated merging of a number of sorted strings. External sorting is appropriate when the files to be sorted are too large to fit in main memory. Mass storage devices such as disks or magnetic tapes are used to hold the large volumes of data involved in the process. The basic objective of the merge sort, a form of external sorting, is the generation of a single large sorted string from two or more sorted data strings. The algorithms and techniques for merging two sorted strings are less complicated than those for sorting single files since the merge input are a sequence of sorted data. The parallel sorters analyzed in Chapter 2 use N processors to sort N records, where as the external sort-merge sort uses only  $\log_m N$  processors, where m is the order of merge.

A number of performance evaluation studies of serial and parallel external sorting have been conducted [11,12,21,22,24,25,47]. Performance modeling and analysis of either the serial or parallel external merge sort is a complex process since access time, disk scheduling, and the file distribution and organization of the mass storage devices is often necessary. External sorting algorithm analysis must also consider the architectural characteristics of the mass storage devices used in order to obtain satisfactory results. A simple I/O access model is analyzed in Chapter 5.

This chapter begins with an analysis of external sorting techniques. In particular, the characteristics of the external parallel merge sort are considered since high performance algorithms for the internal merge sort have already been thoroughly analyzed for use with parallel computers [6,22]. Several parallel merge sort algorithms are discussed to implement and methods of memory management are considered. Following this analysis, the VLSI implementation of a 4-way merge sorter is considered

## 4.1 VLSI Merge Sort

Even [21] proposed two methods for parallel tape-sorting based upon a serial, two-way, external merge sort algorithm. In the first method, all processors must initiate the merge simultaneously, sorting a group of files in parallel. In the best case, this method performs  $(N/P)\log N + 3N$  unit times using  $P \leq \log N$ , where N is the number records to be sorted and P is the number of processors. For the second method, processors were added one at a time to implement a pipelined sorting algorithm. This resulted in the use of  $\log P$  processors and  $4 \times \lceil \log P \rceil$  tape units for the sort of  $3.2 \lceil \log N \rceil$  write cycles, where N > P. These sorting methods were complicated by the necessity of rewinding the tapes before they could be read.

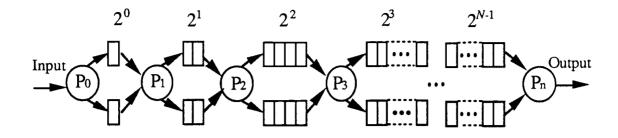

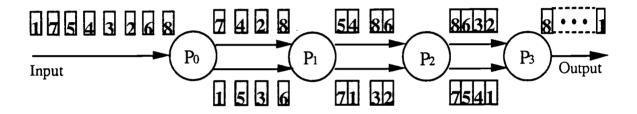

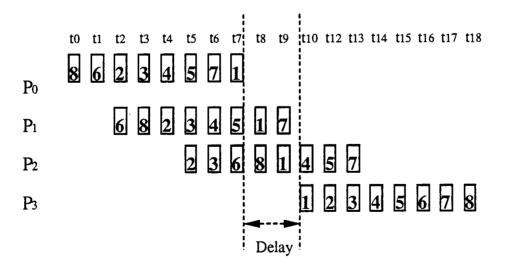

Todd [47] formulated a pipelined merge sort technique based on Even's algorithm [21]. More sophisticated hardware, including bubble memory and faster RAM of less complex design, was used. The algorithm allowed logN processors to sort N records in just over

2N write cycles. This pipelined merge sorter was implemented by Kitsuregawa et al. [25] in 1983, sorting data streams at 3M bytes/sec.

In 1982, Bitton [9, 11] analyzed a variety of parallel sorting algorithms and architectures. The best performance was achieved by a parallel binary merge algorithm, which was a modified parallel two-way merge sort based upon the Even algorithm. In 1985, Takagi [45] applied Todd's pipelined merge sort algorithm to disks with initial sorters. The idea was to provide IBM disk storage systems with internal intelligent disk processor subsystems capable of performing sorting directly. Takagi noted a number of limitations of these subsystems, including problems associated with the synchronization of data transmissions and avoidance of I/O latency time.

# 4.2 Analysis of the External Sortings

The merge sort, a form of external sorting, is suitable for hardware implementation. This approach may readily be pipelined and can achieve a throughput rate is O[N]. The processing overhead for this system is only that associated with pipeline latency. Separate input and output ports are assumed. The most difficult factor in implementing the merge sort is buffer management. Buffering is required since it is used for storing sorted data between each of the merge steps. In order to produce an economical hardware system, it is important to synthesize an efficient scheme of merge buffer management. Techniques for efficient buffer management methods are discussed in Section 4.3. For purposes of

analysis, it is assumed that the total number of records to be sorted is always a power of m, for an m-way merge. If the number of records is less than a power of m, dummy records are added to satisfy this requirement. Two merge sort algorithms are analyzed: Bitton's [9] parallel binary merge sort and Todd's [47] pipelined merge sort.

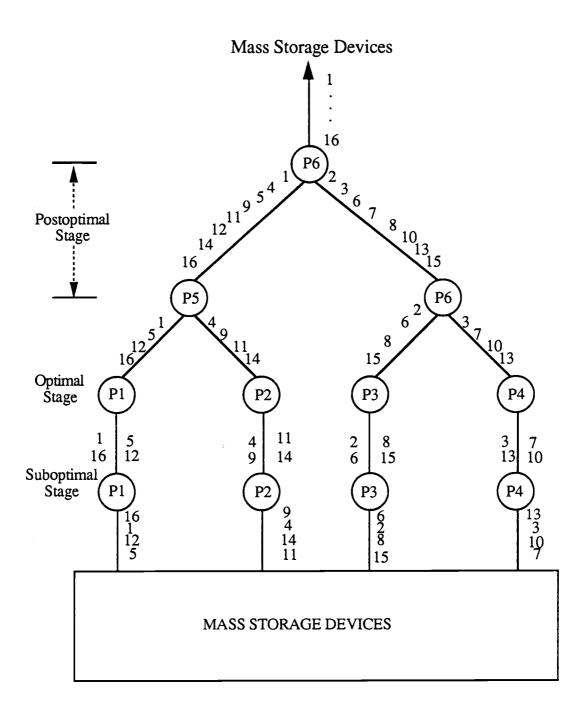

### 4.2.1 Parallel Binary Merge Sort

The algorithm proposed by Bitton for implementation on disk requires a binary tree connection between processors, as shown in Figure 4.1 [9,11]. The disk storage system was modified by simplification of a moving head disk. In 1988, Beck [6] applied this algorithm to a backend multiprocessor built around a fast packet bus, resulting in a system which was judged to be more cost-effective.