#### AN ABSTRACT OF THE THESIS OF

Nilakantan Seshan for the degree of Master of Science in

Electrical and Computer Engineering presented on January 25, 2002.

Title: Design of Low Power 2.4GHz CMOS LC Balanced Oscillators with Low

Phase Noise and Large Tuning Range.

## Redacted for Privacy

| Abstract approved:   | <br>         |        |  |

|----------------------|--------------|--------|--|

| . rostract approved. | <br>0        |        |  |

|                      | Kartikeya Ma | ayaram |  |

The design of two 2.4GHz CMOS LC balanced oscillators in the  $0.25\mu m$  National BiCMOS process for Bluetooth specifications is presented. These oscillators achieve low phase noise with low power consumption. At a frequency offset of 500KHz from the 2.11GHz carrier, the measured phase noise is -101.9dBc/Hz for the NMOS oscillator with a power dissipation of 12.5mW. The complementary oscillator has a phase noise of -103.6dBc/Hz at 500KHz offset from the 2.19GHz carrier and a power disipation of 6.25mW from a 2.5V power supply. A wide tuning range of 16% is obtained by means of a PMOS varactor in conjunction with an array of switched capacitors.

©Copyright by Nilakantan Seshan January 25, 2002 All Rights Reserved

## Design of Low Power 2.4GHz CMOS LC Balanced Oscillators with Low Phase Noise and Large Tuning Range

by

Nilakantan Seshan

#### A THESIS

submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Master of Science

Completed January 25, 2002 Commencement June 2002

| $\underline{Master}$ | of Science | thesis of | of . | <u>Nilakantan</u> | Seshan | ${\bf presented}$ | on | January | 25, | 2002 |

|----------------------|------------|-----------|------|-------------------|--------|-------------------|----|---------|-----|------|

|                      |            |           |      |                   |        |                   |    |         |     |      |

APPROVED:

## Redacted for Privacy

Major Professor, representing Electrical and Computer Engineering

## Redacted for Privacy

Head of the Department of Electrical and Computer Engineering

## Redacted for Privacy

Dean of the Gyaduate School

I understand that my thesis will become part of the permanent collection of Oregon State University libraries. My signature below authorizes release of my thesis to any reader upon request.

## Redacted for Privacy

Nilakantan Seshan, Author

#### ACKNOWLEDGMENT

At the very onset, let me begin by thanking my advisors Dr. Karti Mayaram and Dr. Terri Fiez. They both have, with their thought-provoking observations, enabled me to think independently. Their pointed questions kept me forever questioning my premise and thus honing my knowledge. Their emphasis on perfection and presentation skills have definitely inspired me to produce quality work. I am also grateful to Jay Rajagopalan from National Semiconductors for his invaluable help and constructive criticism, which have given me a different perspective of understanding circuit design. Constantly guiding me with their sharp insights and suggestions, they all have been the wind beneath my wings. I would also like to acknowledge Dr. Gabor Temes and Dr. Keith Levien, for showing interest in my work and serving on my defense committee.

I thank CDADIC for supporting this work and National Semicondutor for fabricating the chip. I am also grateful to several industry members who have contributed to this project through their feedback at CDADIC meetings. I appreciate the efforts of Bijoy Chatterjee, Jeff Huard, Mike Schwartz, Mike Leister and Peter Welty of National Semiconductor, who took time out of their schedules to read my weekly reports and for all their help during fabrication and testing.

I express my deepest appreciation for Dr. Peter Lauritzen from University of Washington and Ruby Young from Washington State University, without whose help I would not have made it to the United States. I also thank Ferne Simendinger and Sarah O'Leary for all their help and co-operation during my schooling at OSU.

The AMS lab with a plethora of talent has indeed been a great learning experience. First and foremost, I thank my mentor Radu for his guidance during the initial stages of my project. I thank Robert, Shanthi, Uma, Edgard, Xena,

Taras, Kalyan, Yutao, Ruoxin, Vova, Zhimin, Oleg, Yuxian, Jose' and Cheng-gang for helping me with technical problems. I especially thank my roommates Madhu and Vinay for their help and constant support. I remain thankful to my friends Sachin, Ravikanth, Kannan, Prashanth, KP. Mohana, Ragini, Trimmy, Anurag, Vinay, Aarti, Maithily, Madhuri, Reshma, Omkar, Shekhar, Ashish and Eashwar for helping me recreate my homeland in the US. Most of all, I am indebted to Nathen, Aline, and Dicle for making my days at OSU memorable. Time spent with them is going to be a chunk of my nostalgic memories of OSU. I feel fortunate to have a few of my treasured friends as my colleagues as I start my first job.

On this occasion, I also take the opportunity to express my indebtedness to my parents who created an atmosphere of trust, love and understanding for my brother and myself to grow up. I thank my brother for his love, support and faith in me. My heartfelt gratitude goes to my grandmother and uncle whose support and care has gone a long way in shaping my personality. They have been a pillar of strength and inspiration, and I owe my success to them. The help and support of Rahul, Pooja, John, Usha, Ulhas, Dhaval, Kishore, Rama, Anindya, Suresh and Mithat does deserve mention.

I would like to thank my alma maters - Don Bosco High School, D. G. Ruparel College, V. J. T. I., Washington State University and Oregon State University. As I end my academic career at Oregon State University, I feel I have benefited a lot - not just as a student but also as a person. Walking out of this esteemed Institute, I also feel proud to have contributed my bit to this vast pool of knowledge. I feel that this place has prepared me to be among the best and I look forward to begin my life as a professional.

Above all, I thank God for everything.

## TABLE OF CONTENTS

|   | <u>.</u>                         | <u>Page</u> |

|---|----------------------------------|-------------|

| 1 | INTRODUCTION                     | 1           |

| 2 | OSCILLATORS AND PHASE NOISE      | 4           |

|   | 2.1 Introduction to Oscillators  | 4           |

|   | 2.2 Oscillator Topologies        | 7           |

|   | 2.3 Phase Noise                  | 12          |

|   | 2.4 Tunability of Oscillators    | 15          |

|   | 2.4.1 Inductively Tuned VCOs     | 16          |

|   | 2.4.2 Capacitively Tuned VCOs    | 18          |

| 3 | INDUCTORS                        | 20          |

|   | 3.1 Introduction                 | 20          |

|   | 3.2 Simple Inductors             | 21          |

|   | 3.3 Stacked Inductors            | 23          |

|   | 3.4 Symmetric Spiral Inductors   | 24          |

|   | 3.5 Comparison of Inductors      | 25          |

|   | 3.6 Inductor Layout              | 29          |

| 4 | VARACTORS                        | 34          |

|   | 4.1 Introduction                 | 34          |

|   | 4.2 MOS Varactors                | 34          |

|   | 4.2.1 Inversion Mode Varactor    | 35          |

|   | 4.2.2 Accumulation Mode Varactor | 37          |

|   | 4.2.3 Gated Varactor             | 38          |

|   | 4.3 MOS Transistors as Varactors | 40          |

## **TABLE OF CONTENTS (Continued)**

|   |                                                            | Page     |

|---|------------------------------------------------------------|----------|

|   | 4.4 Varactor Implementation Using Switched Capacitor Array | 44       |

|   | 4.5 Varactor Layout                                        | 48       |

| 5 | PHASE NOISE IN OSCILLATORS                                 | 50       |

|   | 5.1 Contributors of Phase Noise                            | 50       |

|   | 5.2 Factors Influencing Phase Noise                        | 51<br>52 |

|   | 5.2.2 Inductor Series Resistance                           | 57       |

|   | 5.2.3 Oscillator Bias Current                              | 60       |

|   | 5.2.4 Tail Current Source Dimensions                       | 61       |

|   | 5.2.5 Differential Operation of Inductors                  | 63       |

|   | 5.3 Supply and Substrate Noise                             | 67       |

| 6 | OSCILLATOR DESIGN                                          | 75       |

|   | 6.1 Specifications                                         | 75       |

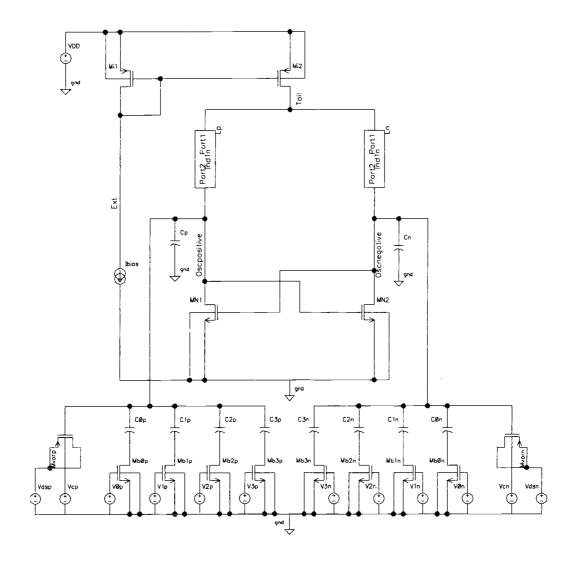

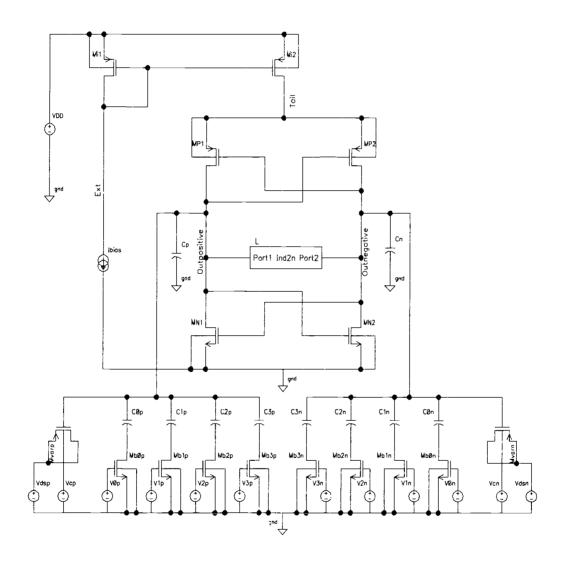

|   | 6.2 Design of the Oscillator Core                          | 75       |

|   | 6.3 Buffer Design                                          | 88       |

|   | 6.4 Layout Considerations                                  | 93       |

|   | 6.5 Simulated Performance                                  | 97       |

| 7 | MEASUREMENTS                                               | 104      |

|   | 7.1 Measurement Set-up                                     | 104      |

|   | 7.2 Measurement Results                                    | 105      |

|   | 7.3. Comparison of Various Oscillators                     | 112      |

## **TABLE OF CONTENTS (Continued)**

|                                                                 | <u>Page</u> |

|-----------------------------------------------------------------|-------------|

| 8 CONCLUSION                                                    | 115         |

| BIBLIOGRAPHY                                                    | 116         |

| APPENDICES                                                      | 120         |

| APPENDIX A NMOS oscillator core schematic from CADENCE          | 121         |

| APPENDIX B Complementary oscillator core schematic from CADENCE | 122         |

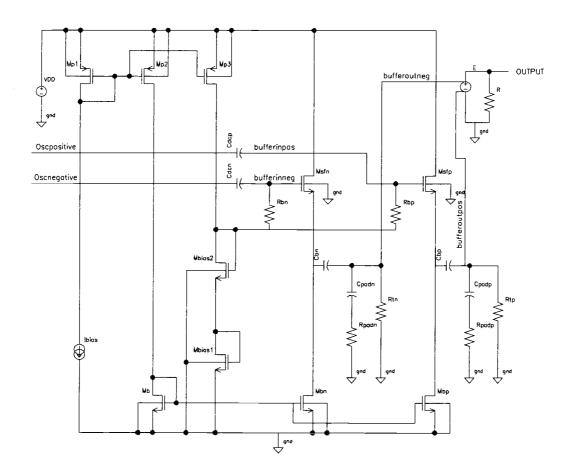

| APPENDIX C Buffer schematic from CADENCE                        | 123         |

## LIST OF FIGURES

| Figu | re Page                                                                                                                                         |    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.1  | The block diagram of a phase-locked loop                                                                                                        | 2  |

| 2.1  | The block diagram of an oscillator. The positive-feedback loop consists of an amplifier and a frequency-selective network                       | 4  |

| 2.2  | Circuit to illustrate how the Barkhausen criterion is applied to oscillators.                                                                   | 6  |

| 2.3  | (a) Tank circuit shows decaying response due to circuit losses. (b) With the addition of a negative resistance, oscillations can be stabilized. | 7  |

| 2.4  | Circuit demonstrating the condition for start-up using the negative resistance concept                                                          | 8  |

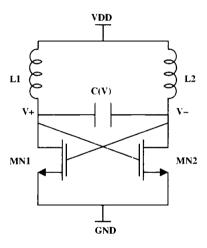

| 2.5  | NMOS oscillator.                                                                                                                                | 9  |

| 2.6  | PMOS oscillator.                                                                                                                                | 10 |

| 2.7  | Complementary oscillator.                                                                                                                       | 10 |

| 2.8  | Voltage biased oscillator                                                                                                                       | 11 |

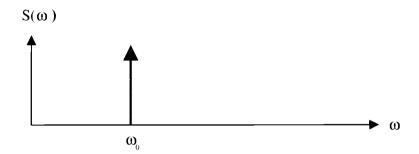

| 2.9  | Power spectrum of an ideal oscillator                                                                                                           | 13 |

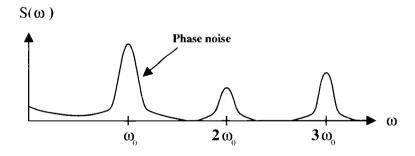

| 2.10 | Power spectrum of an actual oscillator                                                                                                          | 13 |

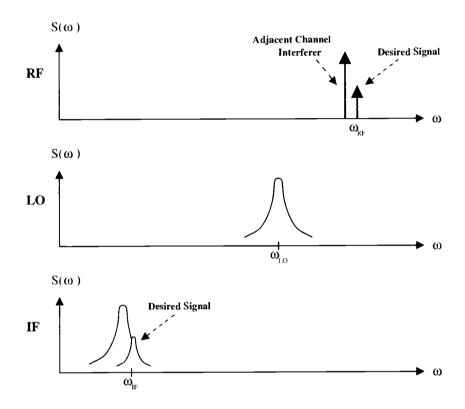

| 2.11 | Effect of a strong adjacent channel interferer in the presence of LO phase noise                                                                | 14 |

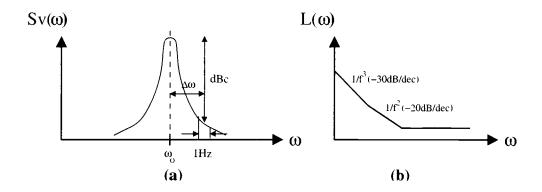

| 2.12 | Phase noise of an oscillator (a) Characterization of phase noise. (b) Various regions in a typical phase noise curve                            | 15 |

| 2.13 | Schematic of the inductively tuned oscillator                                                                                                   | 17 |

| 2.14 | Tuning characteristics of the inductively tuned oscillator                                                                                      | 18 |

| 3.1  | Layout of an on-chip spiral inductor                                                                                                            | 22 |

| 3.2  | Inductor model provided by ASITIC. The components shown by dashed lines are included in more accurate inductor models                           | 22 |

| 3.3  | Stacking metal layers to improve the inductor quality factor. The 5th and 4th metal layers have been stacked                                    | 24 |

| Figu | re $re$ $re$ $re$                                                                                                         |    |

|------|---------------------------------------------------------------------------------------------------------------------------|----|

| 3.4  | Layout of a symmetric spiral inductor                                                                                     | 25 |

| 3.5  | Circuit to obtain the inductor quality factor under single-ended excitation                                               | 27 |

| 3.6  | Circuit to obtain the inductor quality factor under differential excitation                                               | 27 |

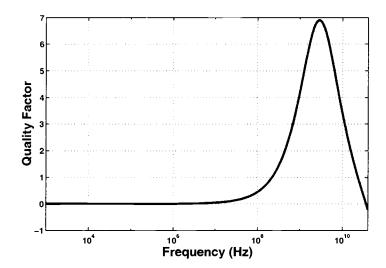

| 3.7  | Quality factor versus frequency plot for the 1nH inductor                                                                 | 30 |

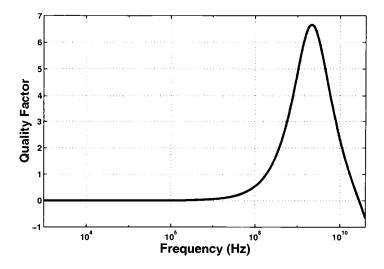

| 3.8  | Quality factor versus frequency plot for the 2nH inductor                                                                 | 30 |

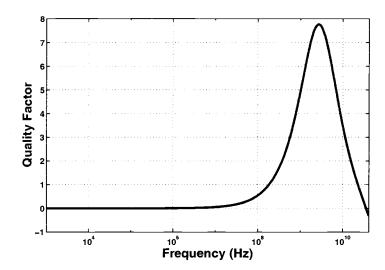

| 3.9  | Differential quality factor plot for the 2nH inductor                                                                     | 31 |

| 3.10 | Layout of the 1nH inductor                                                                                                | 32 |

| 3.11 | Layout of the 2nH inductor                                                                                                | 33 |

| 4.1  | Cross-section of the different varactors: (a) Inversion mode varactor. (b) Accumulation mode varactor. (c) Gated varactor | 35 |

| 4.2  | C-V characteristics of the MOS capacitor                                                                                  | 36 |

| 4.3  | C-V characteristics of the inversion mode varactor                                                                        | 3  |

| 4.4  | C-V characteristics of the accumulation mode varactor                                                                     | 38 |

| 4.5  | C-V characteristics of the gated varactor                                                                                 | 39 |

| 4.6  | Circuit used to determine the C-V characteristics of the varactor based on a MOS transistor                               | 41 |

| 4.7  | C-V characteristics of an NMOS transistor when the bulk voltage is varied                                                 | 41 |

| 4.8  | C-V characteristics of a PMOS transistor when the bulk voltage is varied                                                  | 4: |

| 4.9  | C-V characteristics of an NMOS transistor with varying Vd/s                                                               | 43 |

| 4.10 | C-V characteristics of a PMOS transistor with varying Vd/s                                                                | 43 |

| 4.11 | Binary weighted switched capacitor circuit to provide higher tuning range without increasing the VCO gain                 | 45 |

| Figu | $\underline{\underline{\text{Page}}}$                                                                                                                                                                                                                                                                                                                                                        |    |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

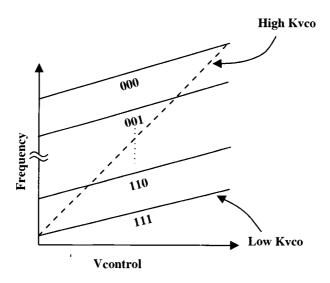

| 4.12 | Tuning characteristics explaining the principle of switched tuning                                                                                                                                                                                                                                                                                                                           | 45 |

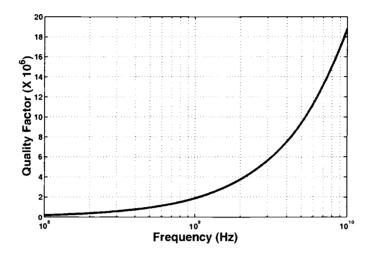

| 4.13 | Quality factor of the switched capacitor circuit when all switches are OFF                                                                                                                                                                                                                                                                                                                   | 47 |

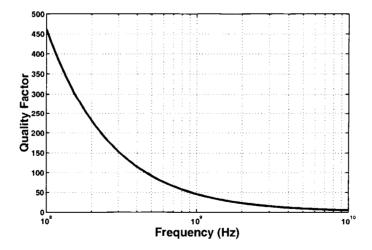

| 4.14 | Quality factor of the switched capacitor circuit when all switches are ON                                                                                                                                                                                                                                                                                                                    | 47 |

| 4.15 | Layout of the capacitor bank used in the varactor circuitry                                                                                                                                                                                                                                                                                                                                  | 49 |

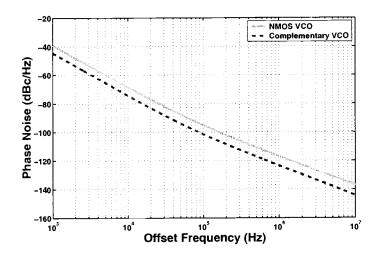

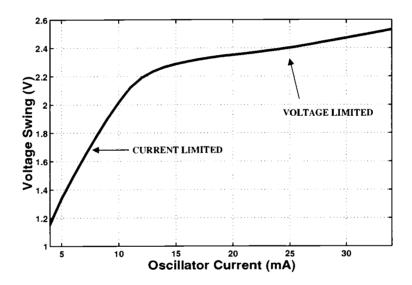

| 5.1  | Comparison of the complementary and the NMOS oscillator for identical currents                                                                                                                                                                                                                                                                                                               | 53 |

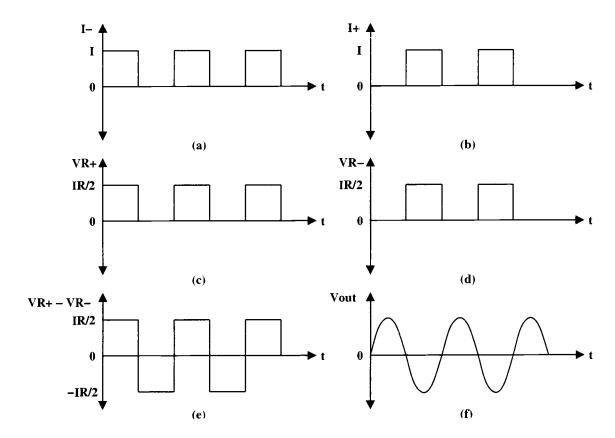

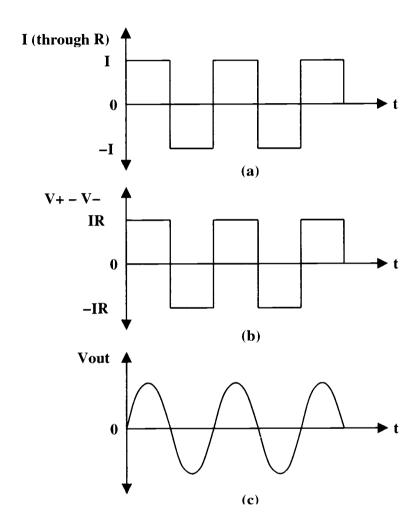

| 5.2  | Current and voltage waveforms for the NMOS oscillator. (a) Current through MN2. (b) Current through MN1. (c) Voltage drop across the inductor connected to the drain of MN1. (d) Voltage drop across the inductor connected to the drain of MN2. (e) Pre-filtered voltage across the differential output. (f) Differential output voltage after the harmonics have been filtered by the tank | 54 |

| 5.3  | Current and voltage waveforms for the complementary oscillator. (a) Current through the inductor. (b) Pre-filtered voltage across the inductor. (c) Differential output voltage after the harmonics have been filtered by the tank                                                                                                                                                           | 55 |

| 5.4  | Comparison of the phase noise performance of the NMOS and the complementary topologies                                                                                                                                                                                                                                                                                                       | 57 |

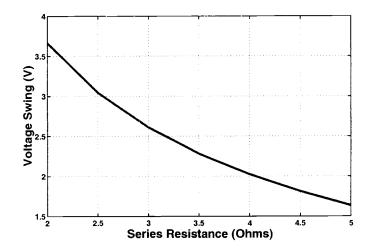

| 5.5  | Effect of inductor series resistance on the voltage swing                                                                                                                                                                                                                                                                                                                                    | 58 |

| 5.6  | Effect of inductor series resistance on phase noise at the following frequencies: (a) 1kHz offset from the carrier. (b) 100kHz offset from the carrier. (c) 1MHz offset from the carrier                                                                                                                                                                                                     | 59 |

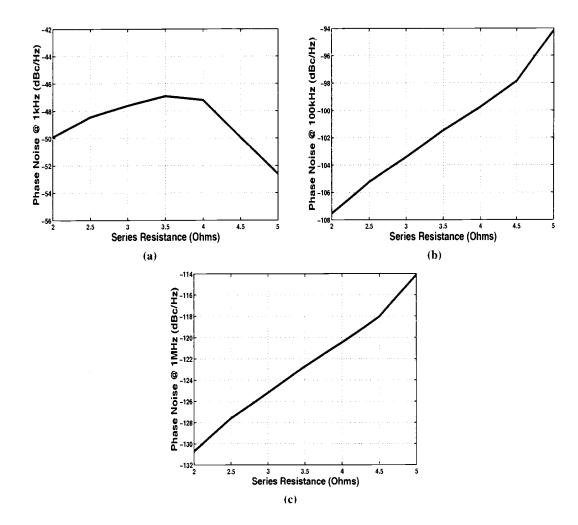

| 5.7  | Voltage swing versus oscillator bias current                                                                                                                                                                                                                                                                                                                                                 | 60 |

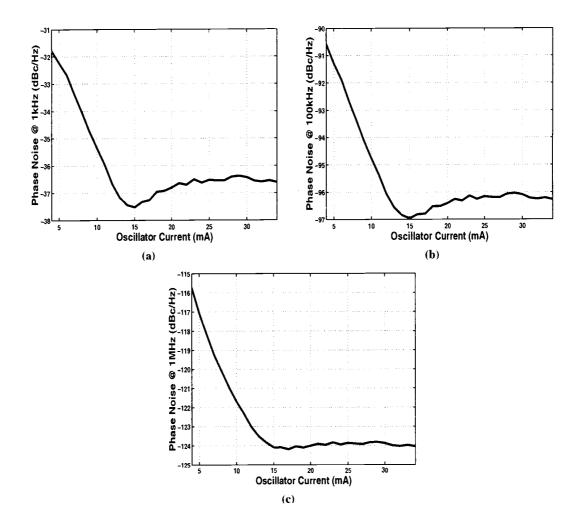

| 5.8  | Effect of varying the oscillator current on phase noise at the following frequencies: (a) 1kHz offset from the carrier. (b) 100kHz offset from the carrier. (c) 1MHz offset from the carrier                                                                                                                                                                                                 | 62 |

| Figu | $\underline{\underline{\text{Page}}}$                                                                                                                                                                       |    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

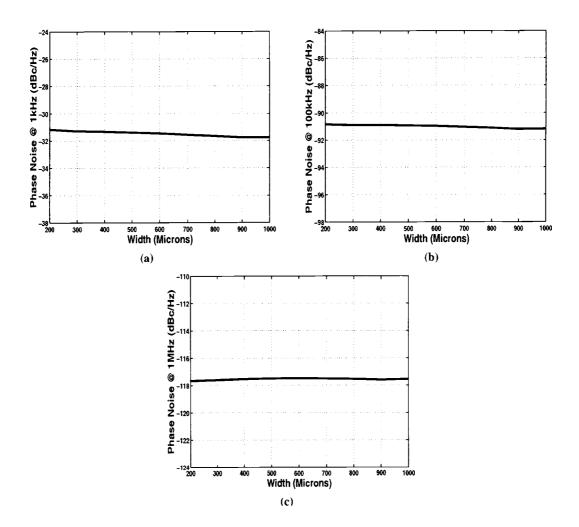

| 5.9  | Effect of varying the width of the tail current source on phase noise at the following frequencies: (a) 1kHz offset from the carrier. (b) 100kHz offset from the carrier. (c) 1MHz offset from the carrier  | 64 |

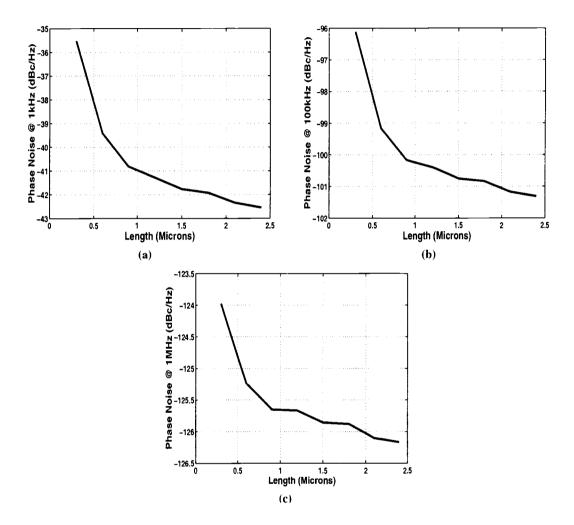

| 5.10 | Effect of varying the length of the tail current source on phase noise at the following frequencies: (a) 1kHz offset from the carrier. (b) 100kHz offset from the carrier. (c) 1MHz offset from the carrier | 65 |

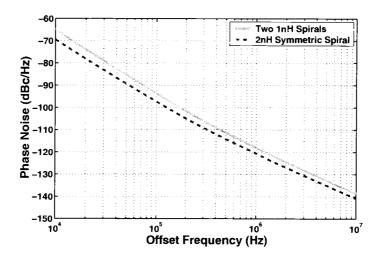

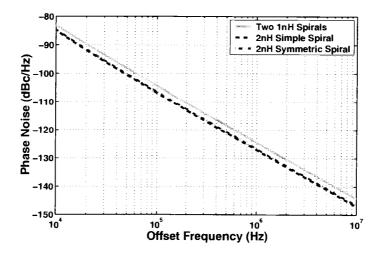

| 5.11 | Comparison of phase noise performance of NMOS oscillator with different inductors                                                                                                                           | 66 |

| 5.12 | Comparison of phase noise performance of complementary oscillator with different inductors                                                                                                                  | 66 |

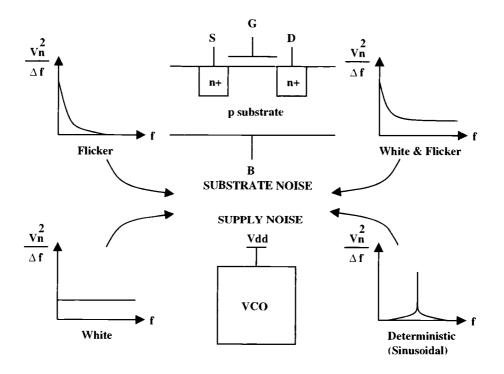

| 5.13 | Injection of noise of various power spectral densities to Vdd or bulk to study the effect of supply noise and substrate noise on phase noise.                                                               | 68 |

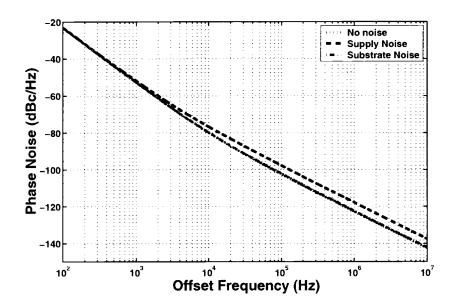

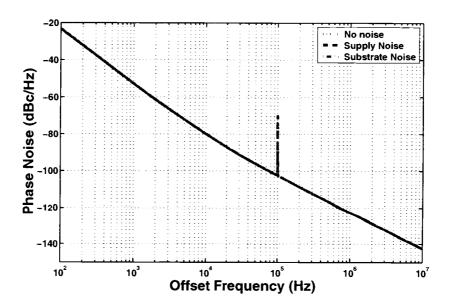

| 5.14 | Phase noise in the presence of white noise in the supply and substrate.                                                                                                                                     | 69 |

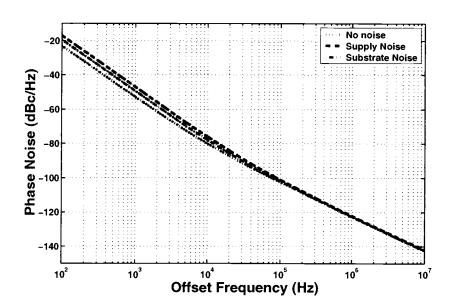

| 5.15 | Effect of flicker noise in the supply and substrate on phase noise                                                                                                                                          | 70 |

| 5.16 | Phase noise in the presence of deterministic noise in the supply and substrate                                                                                                                              | 71 |

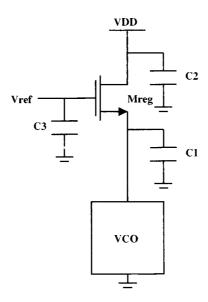

| 5.17 | Schematic of supply voltage regulator                                                                                                                                                                       | 73 |

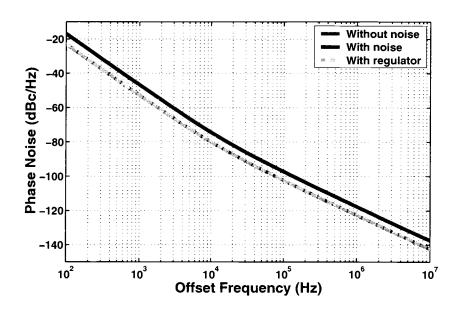

| 5.18 | Comparison of phase noise in the absence and presence of a supply voltage regulator.                                                                                                                        | 74 |

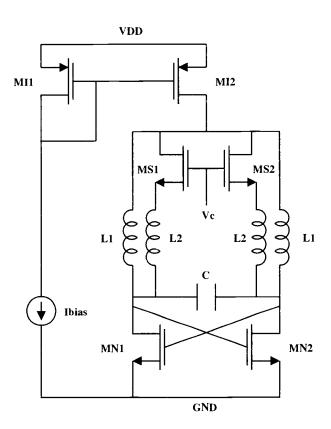

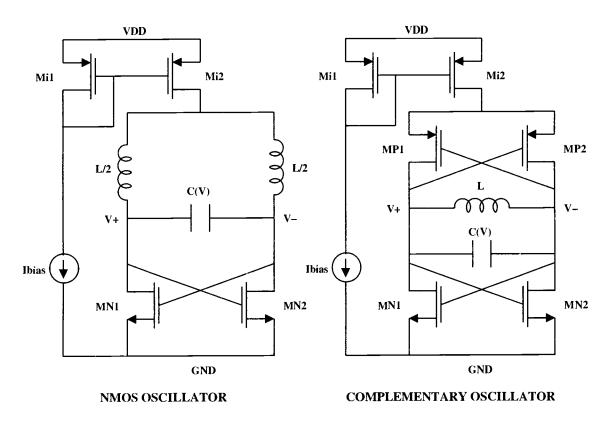

| 6.1  | Oscillator core for complementary and the NMOS topologies with tail current sources.                                                                                                                        | 76 |

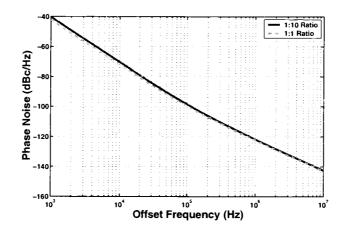

| 6.2  | Comparison of phase noise for different current mirroring ratios                                                                                                                                            | 79 |

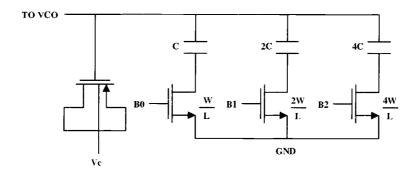

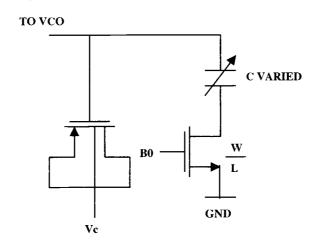

| 6.3  | Capacitive tuning block consisting of PMOS varactor and four binary weighted capacitors                                                                                                                     | 81 |

| 6.4  | Tuning characteristics desired from the varactor of Fig. 6.3                                                                                                                                                | 82 |

| 6.5  | Tuning range of the PMOS varactor                                                                                                                                                                           | 82 |

| 6.6  | Varactor circuit to determine the value of C                                                                                                                                                                | 83 |

|     | Page Page                                                                                                                                                  | F'igu |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

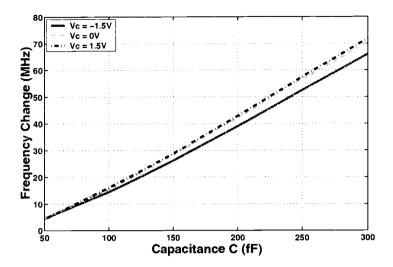

| 84  | Oscillation frequency change plotted as a function of the capacitor value.                                                                                 | 6.7   |

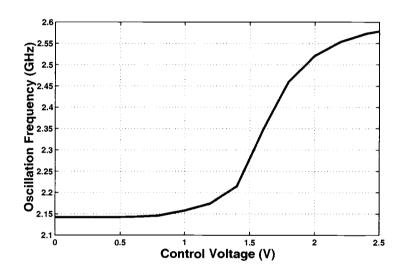

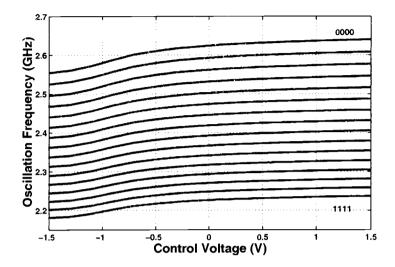

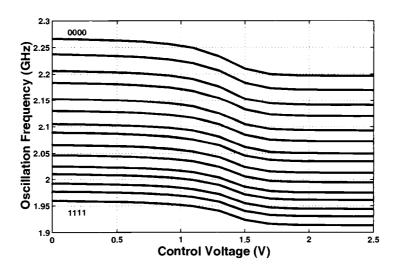

| 87  | Tuning range of the NMOS oscillator                                                                                                                        | 6.8   |

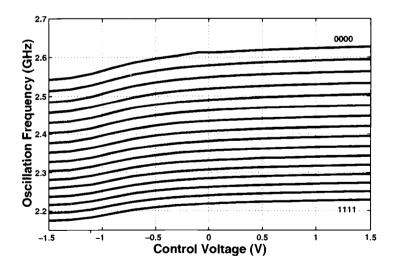

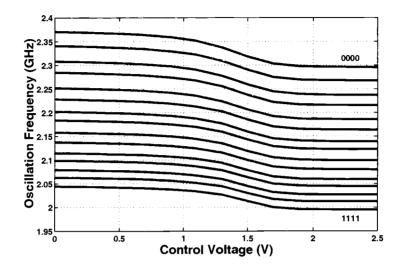

| 87  | Tuning range of the complementary oscillator                                                                                                               | 6.9   |

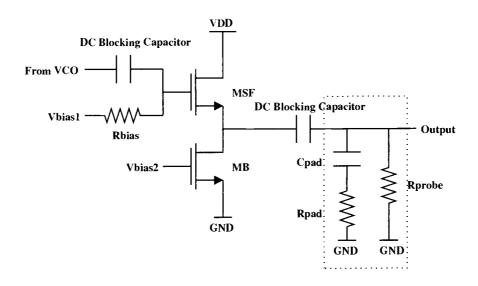

| 89  | Simplified schematic of the buffer                                                                                                                         | 6.10  |

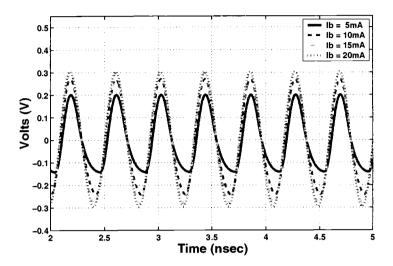

| 90  | Output waveform of the buffer for different buffer currents                                                                                                | 6.11  |

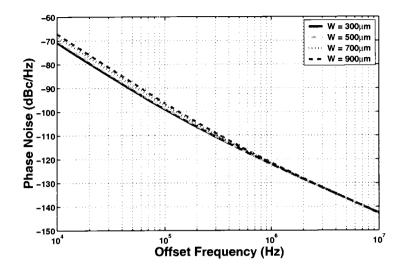

| 91  | Phase noise plot for different values of the source follower transistor width                                                                              | 6.12  |

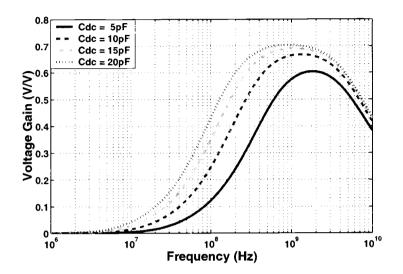

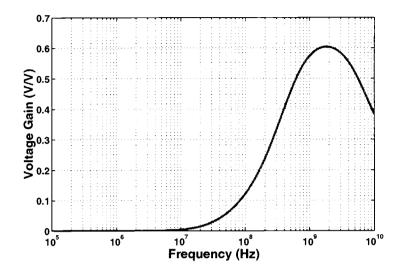

| 92  | AC response of the buffer for various values of the DC blocking capacitor                                                                                  | 6.13  |

| 93  | Frequency response of the buffer, including the effect of the dc blocking capacitors                                                                       | 6.14  |

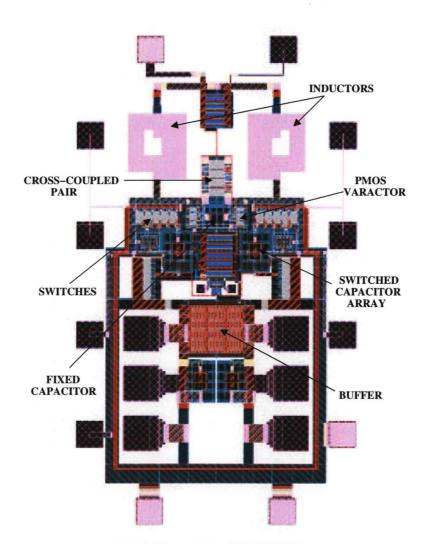

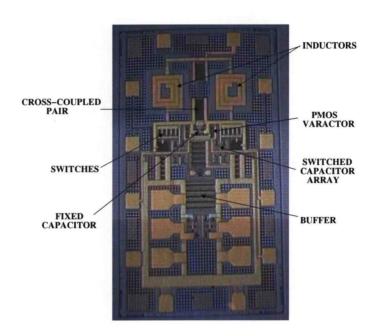

| 95  | Layout of the NMOS oscillator                                                                                                                              | 6.15  |

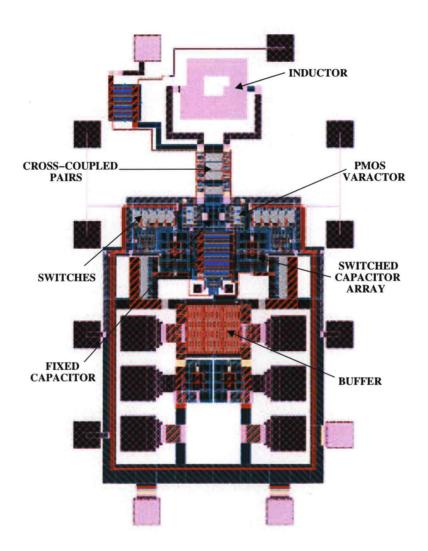

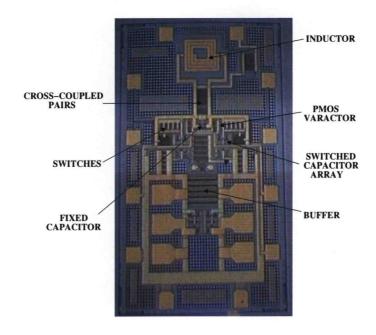

| 96  | Layout of the complementary oscillator                                                                                                                     | 6.16  |

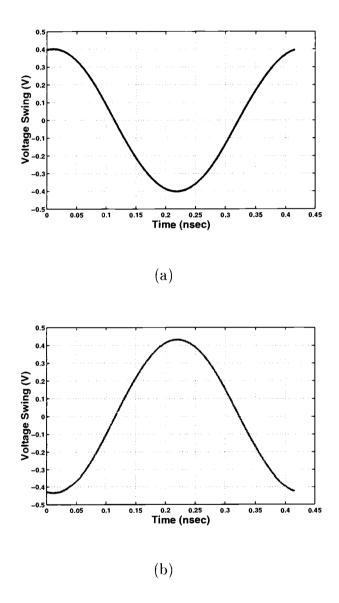

| 98  | Simulated output voltage waveforms. (a) NMOS oscillator. (b) Complementary oscillator                                                                      | 6.17  |

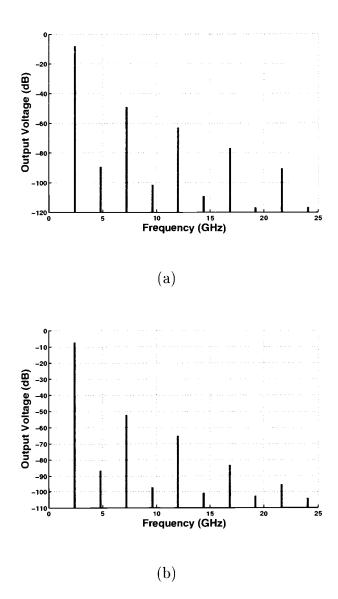

| 99  | Fundamental and the harmonics in the output waveforms. (a) NMOS oscillator. (b) Complementary oscillator                                                   | 6.18  |

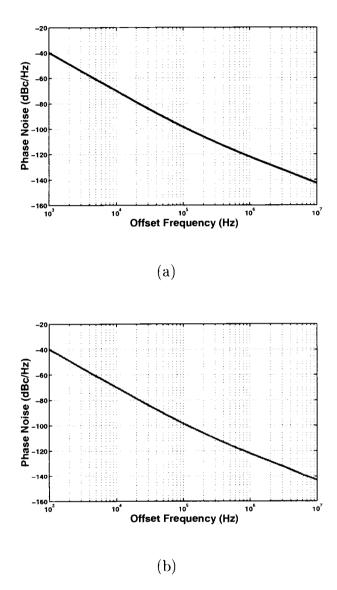

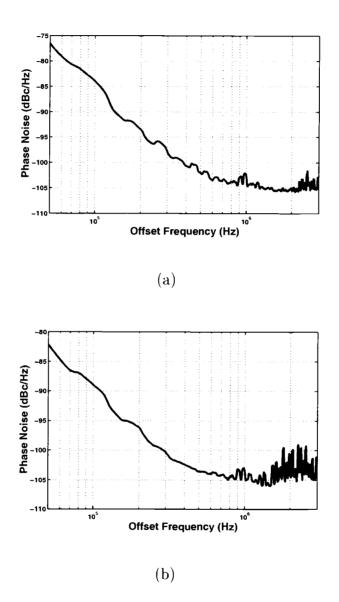

| 101 | Simulated phase noise plots. (a) NMOS oscillator. (b) Complementary oscillator                                                                             | 6.19  |

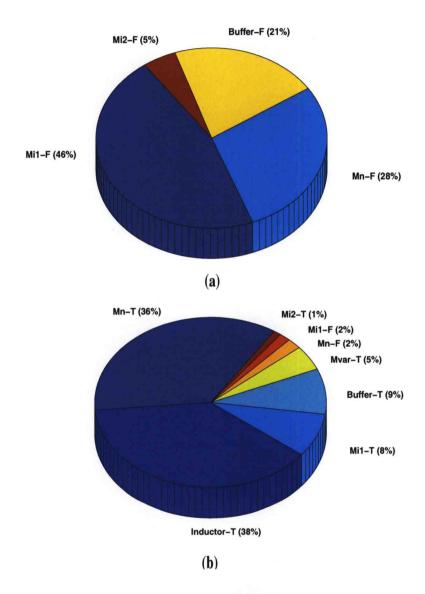

| 102 | Phase noise contributors in the NMOS oscillator at the following frequencies: (a) 1kHz offset from the carrier. (b) 3MHz offset from the carrier           | 6.20  |

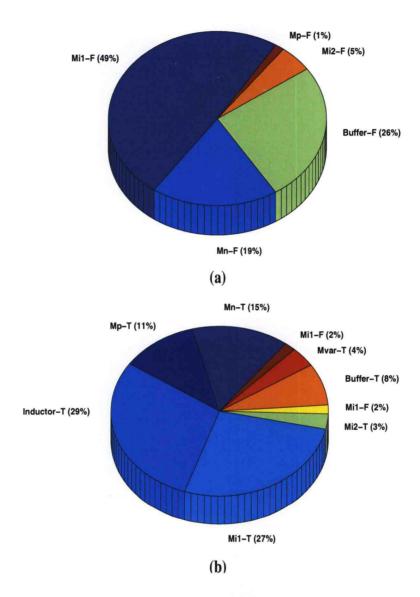

| 103 | Phase noise contributors in the complementary oscillator at the following frequencies: (a) 1kHz offset from the carrier. (b) 3MHz offset from the carrier. | 6.21  |

| 104 | Die photo of the NMOS oscillator                                                                                                                           | 7.1   |

| Figure | $\frac{P_a}{-}$                                                                                            | age |

|--------|------------------------------------------------------------------------------------------------------------|-----|

| 7.2    | Die photo of the complementary oscillator                                                                  | .05 |

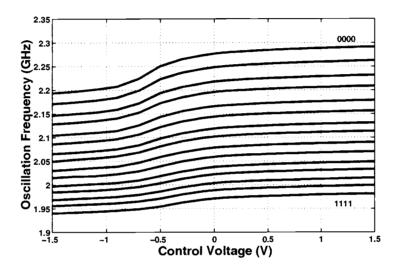

| 7.3    | Tuning range of the NMOS oscillator with the bulk terminal swept 1                                         | .06 |

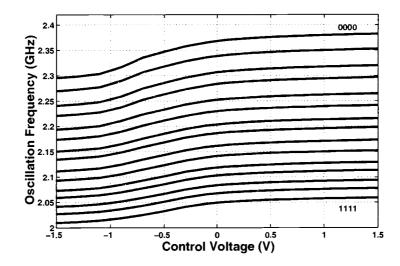

| 7.4    | Tuning range of the complementary oscillator with the bulk terminal swept                                  | .07 |

| 7.5    | Tuning range of the NMOS oscillator with the drain-source terminals swept                                  | .07 |

| 7.6    | Tuning range of the complementary oscillator with the drain-source terminals swept                         | .08 |

| 7.7    | Measured phase noise plots. (a) NMOS oscillator. (b) Complementary oscillator                              | .10 |

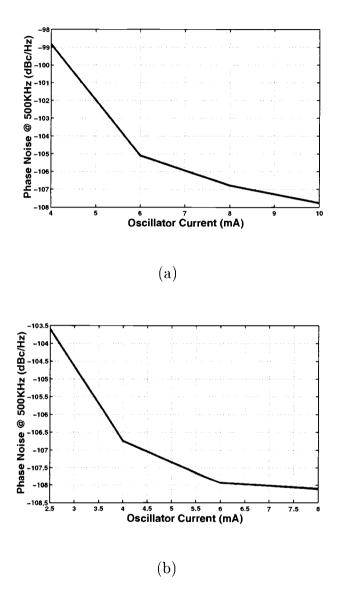

| 7.8    | Effect of varying the oscillator current on phase noise. (a) NMOS oscillator. (b) Complementary oscillator | 13  |

## LIST OF TABLES

| <u>Table</u> |                                                                 | Page  |

|--------------|-----------------------------------------------------------------|-------|

| 3.1          | Comparison of inductors                                         | . 26  |

| 6.1          | Designed values of the oscillator core                          | . 80  |

| 6.2          | Variation of ON resistance and OFF capacitance with switch size | . 85  |

| 6.3          | Designed values of the tuning circuit                           | . 86  |

| 6.4          | Designed values of the buffer circuit                           | . 92  |

| 6.5          | Comparison of specifications with simulated results             | . 100 |

| 7.1          | Comparison of specifications with measured results              | . 111 |

| 7.2          | Performance comparison of various oscillator designs            | . 114 |

## LIST OF APPENDICES

| <u>Appendix</u> |   |                                                      | <u>Page</u> |

|-----------------|---|------------------------------------------------------|-------------|

|                 | A | NMOS oscillator core schematic from CADENCE          | 121         |

|                 | B | Complementary oscillator core schematic from CADENCE | 122         |

|                 | C | Buffer schematic from CADENCE                        | 123         |

# DESIGN OF LOW POWER 2.4GHz CMOS LC BALANCED OSCILLATORS WITH LOW PHASE NOISE AND LARGE TUNING RANGE

#### 1. INTRODUCTION

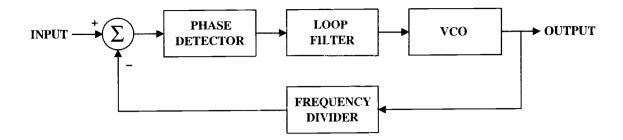

The past decade has seen tremendous growth in wireless communication. The reduction in the channel spacing and demand for low power, low cost solutions has made wireless system design even more challenging [1], [28]. VCOs are critical blocks of frequency synthesizers and phase-locked loops (PLLs) which are key components in wireless systems. Fig. 1.1 shows the block diagram of a phase-locked loop. It consists of a phase comparator or a phase detector followed by a loop filter and a VCO in a feedback loop. The phase detector compares the phases of the input and the output and generates an error signal. The loop filter is a lowpass filter which filters out the high frequency components and presents a dc level to the oscillator. The output of the filter is the control voltage to the VCO which varies the oscillation frequency until the loop is locked and the phases are aligned. The frequency divider may or may not be required depending on the application. In case the input frequency should be multiplied by a factor M, a frequency divider  $(\div M)$  can be used in the feedback loop as shown in Fig. 1.1.

Two important considerations in VCO designs are phase noise and tuning range. The phase noise of the system outside the loop bandwidth of the PLL is

Figure 1.1. The block diagram of a phase-locked loop.

determined by the VCO phase noise. Hence, it is imperative to minimize the phase noise of the VCO. In order for the PLL to lock-on to the reference frequency, a high tuning range is desired. At the same time, it is necessary to maintain a small VCO gain to prevent amplification of any noise on the control node and deterioration of phase noise [6].

A significant amount of work has been done in the past in the area of VCO design [2] - [6], [20] - [33]. However, the competitive nature of the wireless market is forcing designers to explore new techniques to reduce phase noise and improve tuning range. The lack of accurate RF models for MOSFETs, inductors and varactors adds to the difficulties of RF design. Another obstacle to faster and better designs is the lack of simulators capable of predicting phase noise. Presently SpectreRF, Agilent EEsof ADS and EldoRF are the only commercially available tools to simulate phase noise. In [3], Hajimiri and Lee have presented a linear time-variant model to predict phase noise. Although the model provides insight into the conversion of device noise into phase noise, its automated implementation requires significant effort. All the above mentioned factors have added to the complexity of RF design and the design

of VCOs with low phase noise and high tuning range still poses a challenge for circuit designers.

In this thesis, two low power CMOS VCO designs targeted for Bluetooth specifications are presented. The Bluetooth standard is gaining acceptance around the world for personal area networks. Both these oscillators provide low phase noise with low power consumption and offer a wide tuning range. These two oscillators have been fabricated in the  $0.25\mu m$  National BiCMOS process.

The emphasis of this research has been to reduce the power consumption of the oscillators while maintaining good phase noise performance. Various techniques for reducing phase noise have been studied and implemented. The design has been done completely in CMOS and the use of a PMOS transistor as a varactor has been studied. The thesis is organized as follows. A brief introduction to oscillators and phase noise is provided in Section 2. Sections 3 and 4 describe the tank components, namely, on-chip spiral inductors and varactors, respectively. Section 5 presents a detailed analysis of phase noise in oscillators validated by simulations. The design of the oscillators and the buffer is explained in Section 6, followed by the measurement results in Section 7. Conclusions and future work are presented in Section 8.

#### 2. OSCILLATORS AND PHASE NOISE

#### 2.1. Introduction to Oscillators

Oscillators are closed loop systems which employ a positive feedback loop. Oscillators can be classified as resonatorless oscillators or ones that have a resonator. Examples of resonatorless oscillators are ring oscillators and relaxation oscillators, whereas LC oscillators fall in the latter category. Resonatorless oscillators are not popular in RF design due to their low quality factor and the presence of many noisy active and passive devices in the signal path. Therefore LC oscillators are more suitable for low noise applications [36]. At present LC oscillators are being designed for several GHz and higher. In order to understand the principle of operation of the oscillator, consider the feedback system shown in Fig. 2.1.

Figure 2.1. The block diagram of an oscillator. The positive-feedback loop consists of an amplifier and a frequency-selective network.

The closed loop gain of the system is given by

$$A_f(s) = \frac{A(s)}{1 - A(s)\beta(s)} \tag{2.1}$$

where A(s) represents the gain of the amplifier and  $\beta(s)$  is the gain of the feedback network. The loop gain of the circuit is given by

$$L(s) = A(s)\beta(s). \tag{2.2}$$

If at a specific frequency  $\omega_0$  the loop gain L(s) is equal to unity, then the closed loop gain from Eq. (2.1) will be infinite. This implies that at that specific frequency  $\omega_0$ , the output will be finite even if the input is zero. Thus the condition for oscillation at a frequency of  $\omega_0$ , called the *Barkhausen criterion*, is given by

$$L(j\omega_0) = A(j\omega_0)\beta(j\omega_0) = 1. \tag{2.3}$$

This provides the condition for oscillations at  $\omega_0$ : the magnitude of the loop gain should be unity and the phase of the loop gain must be zero [34].

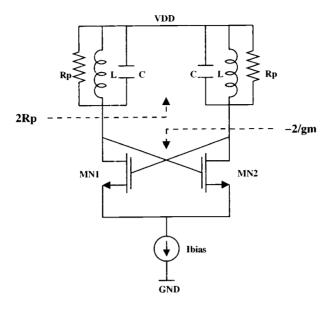

To apply the Barkhausen criterion to a circuit, consider the oscillator circuit shown in Fig. 2.2. The gain from the gate of  $M_{N1}$  to its drain is  $-g_{m1}R_P$ , where  $g_m$  is the transconductance of the transistor and  $R_P$  is the tank resistance at resonance. Similarly, the gain from the gate of  $M_{N2}$  to its drain is  $-g_{m2}R_P$ . The loop gain is then  $g_{m1}R_Pg_{m2}R_P$ , with a phase of 360°. Thus the condition required to start the oscillations is given by

$$g_{m1}R_Pg_{m2}R_P \ge 1. (2.4)$$

If the above condition is satisfied, the circuit will amplify any small noise present in the circuit and steady oscillations would be obtained.

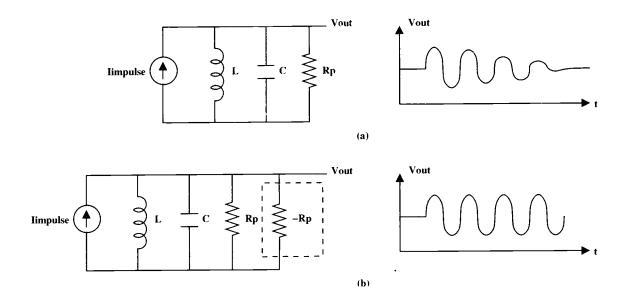

An alternative perspective of looking at oscillators is by considering the negative resistance. The lossy tank can be modeled as an inductor L, capacitor C and

Figure 2.2. Circuit to illustrate how the Barkhausen criterion is applied to oscillators.

resistor  $R_P$  in parallel. If a current impulse is injected into the tank, the voltage waveform is a decaying sinusoid due to the resistive losses as shown in Fig. 2.3. But if a negative resistance is added to the circuit to cancel the losses due to the resistance  $R_P$ , the decaying behavior disappears and the resulting waveform is shown in Fig. 2.3. Thus, nullifying the resistance in the tank guarantees steady oscillations.

For the circuit shown in Fig. 2.4, the resistance looking into the tank from the differential output terminals is  $2R_P$ . The resistance looking into the cross-coupled devices is  $-2/g_m$ , assuming a perfectly symmetrical circuit. Since both the resistances are in parallel, the effective resistance of the circuit is

$$R_T = \frac{-2/g_m 2R_P}{2R_P - 2/g_m}. (2.5)$$

If the resistance  $R_T$  is negative, there won't be any losses in the circuit and oscillations will be sustained. Therefore, for stable oscillations, we require

Figure 2.3. (a) Tank circuit shows decaying response due to circuit losses. (b) With the addition of a negative resistance, oscillations can be stabilized.

$$2R_P - 2/g_m \ge 0 \Rightarrow g_m R_P \ge 1. \tag{2.6}$$

As seen from (2.4) and (2.6), the start-up loop gain conditions are different. Therefore it is necessary to understand the context in which each can be used. If the circuit has the sources of the cross-coupled devices grounded, as in Fig. 2.2, (2.4) should be used. On the other hand, if the circuit has the sources of the cross-coupled devices connected to some current source, as shown in Fig. 2.4, (2.6) should be used.

### 2.2. Oscillator Topologies

There are various types of oscillators employing an LC tank including Colpitts oscillators, Hartleys oscillators, transformer coupled oscillators or LC balanced oscillators. All these oscillators use a LC tank which determines the frequency of

Figure 2.4. Circuit demonstrating the condition for start-up using the negative resistance concept.

oscillation. The tank in these oscillators provides considerable attenuation to signals at frequencies other than the oscillation frequency. Amongst all the oscillators mentioned, the LC balanced oscillators are widely employed. Consequently the focus of this research is on LC balanced oscillators. Since differential structures provide better immunity from external sources of noise, the LC balanced oscillators were designed for differential operation.

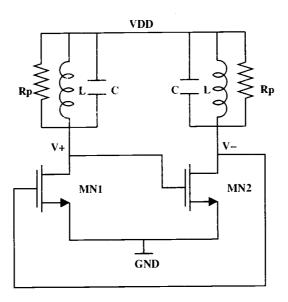

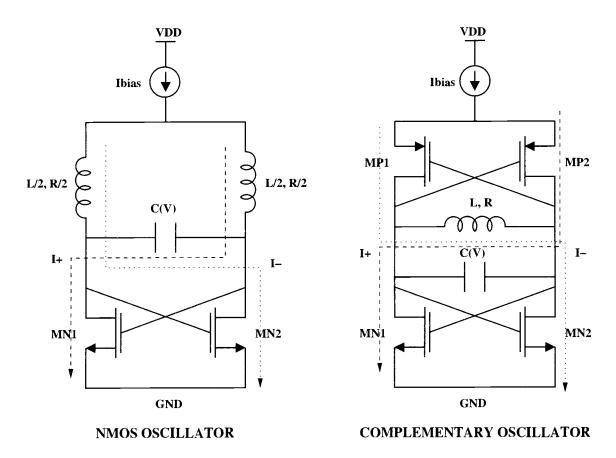

LC balanced oscillators comprise of either cross-coupled NMOS or PMOS transistors or both. The schematic of the oscillators with just NMOS or PMOS transistors is shown in Figs. 2.5-2.6. The cross-coupled transistors provide the necessary start-up loop gain for oscillations to build up. Since the  $g_m$  of the PMOS transistors is smaller than that of the NMOS transistors for identical currents, the

size of the PMOS devices for the same start-up loop gain would be much larger than the NMOS devices. This would cause the tank capacitance to vary with temperature because of the large temperature dependent capacitances of the PMOS transistors. Thus the NMOS cross-coupled LC balanced oscillator is a better choice than the PMOS cross-coupled one.

Figure 2.5. NMOS oscillator.

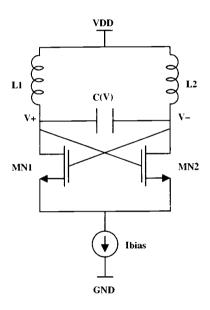

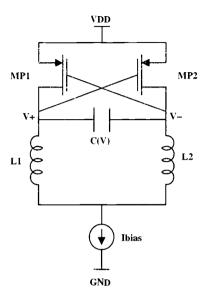

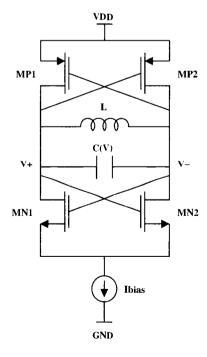

A combination of the PMOS and NMOS cross-coupled pairs gives the complementary oscillator topology. The two cross-coupled stages in the complementary oscillator provide the necessary start-up loop gain for smaller values of current as compared to the ones with just the NMOS or PMOS cross-coupled pair. Fig. 2.7 shows the complementary oscillator circuit.

The biasing current source is called the tail current source. This tail current source could be implemented as either PMOS or NMOS current mirrors, although

Figure 2.6. PMOS oscillator.

Figure 2.7. Complementary oscillator.

NMOS is implied in Figs. 2.5-2.7. Since PMOS transistors have lower flicker noise as compared to NMOS transistors [5], the PMOS tail current source is preferred.

For completeness, the oscillator circuit without the tail current source is shown in Fig. 2.8. The oscillators described earlier were all current biased oscillators. For this oscillator, the supply voltage needs to be adjusted for the desired oscillator current, accordingly it is a voltage biased oscillator. The disadvantages of this oscillator are that it consumes more current as compared to the current biased oscillators and any supply voltage variation may cause the oscillation frequency to deviate from the desired value.

Figure 2.8. Voltage biased oscillator.

The other oscillator circuits such as Colpitts, Hartleys etc., have a different tank configuration and these are not included here since the focus is on LC balanced oscillators.

The start-up loop gain ensures that any noise in the circuit gets amplified and the output voltage begins to increase due to the positive feedback. As the signal continues to increase, the nonlinearity of the cross-coupled pair prevents the amplitude from rising indefinitely. Due to its bandpass characteristics, the LC tank filters out signals at frequencies other than the frequency at which the tank resonates. Therefore only the oscillation frequency is present at the oscillator output. The oscillation frequency for all the oscillators discussed is given by

$$f_{OSC} = \frac{1}{2\pi\sqrt{LC}} \tag{2.7}$$

where L is the tank inductance and C is the tank capacitance which includes the parasitic capacitance of the cross-coupled pair.

The next two sections present some of the performance metrics of an oscillator.

#### 2.3. Phase Noise

Phase noise is an important performance specification for VCOs [2], [3], [35]. Phase noise can be defined as the short term random frequency fluctuations. To understand what this means, consider the frequency spectrum of an ideal oscillator shown in Fig. 2.9. For an ideal oscillator oscillating at frequency  $\omega_0$ , the spectrum is an impulse at  $\omega_0$ . An actual oscillator has a skirt around  $\omega_0$  as illustrated in Fig. 2.10. Since this skirt around the carrier is a result of the various noise sources in the oscillator, it is called the phase noise sideband. The oscillator spectrum also has harmonics at  $2\omega_0$ ,  $3\omega_0$ ,..., etc. as shown in Fig. 2.10.

The significance of phase noise can be understood by considering an example of a receiver [37]. The mixer downconverts the RF signal into the signal at IF by means of a local oscillator (LO). If the desired RF signal is weak, but has a large adjacent channel signal, then in the absence of LO phase noise, both the signals are downconverted to IF without any interference. But if the LO has phase

Figure 2.9. Power spectrum of an ideal oscillator.

Figure 2.10. Power spectrum of an actual oscillator.

noise, the downconverted adjacent channel signal may interfere with the desired downconverted signal as seen in Fig. 2.11. This adjacent channel interference is highly undesirable and it may completely mask out the desired signal if the interferer is large. Hence phase noise specifications are very stringent [25], [28].

Figure 2.11. Effect of a strong adjacent channel interferer in the presence of LO phase noise.

Phase noise is characterized in terms of single sideband noise spectral density. Single sideband phase noise is given by

$$L\{\Delta\omega\} = 10log_{10}\left(\frac{P_{sideband}(\omega_0 + \Delta\omega, 1Hz)}{P_{carrier}}\right)$$

(2.8)

where  $P_{carrier}$  is the power at the oscillator fundamental frequency and  $P_{sideband}(\omega_0 + \Delta\omega, 1Hz)$  represents the single sideband noise power measured in a one Hertz band-

width at a frequency offset of  $\Delta\omega$  from the carrier. This is illustrated in Fig. 2.12 along with the magnified portion of the phase noise curve. It can be observed that the plot of  $L(\Delta\omega)$  has three distinct regions:  $1/f^3$  (-30 dB/decade) region due to the flicker noise,  $1/f^2$  (-20 dB/decade) region due to thermal noise and the flat region due to the noise floor. The mechanisms responsible for these features are explained in detail in [3], [4], [35].

Figure 2.12. Phase noise of an oscillator (a) Characterization of phase noise. (b) Various regions in a typical phase noise curve.

Another way of quantifying the same phenomenon in the time domain rather than the frequency domain is timing jitter or clock jitter. Jitter represents the random fluctuations in the transition points of a periodic waveform. This definition is mostly used when ring oscillators are considered. Since the focus of this work is on wireless applications, phase noise is a more suitable performance metric.

#### 2.4. Tunability of Oscillators

All oscillators which are used in phase-locked loops (PLLs) are designed to be tunable. The reason for this is that the free-running oscillation frequency of the tank would be different from the reference frequency. Thus in order to synchronize the oscillator frequency with the reference frequency, the oscillator frequency needs to be adjustable. Most applications specify the tuning range in absolute units such as 200MHz or in terms of percentage of the center frequency such as 10% tuning.

Since the frequency of oscillation is determined by the inductor and the capacitance in the tank, changing any one of these varies the oscillation frequency. The variation in frequency is obtained by varying the control voltage which changes the tank inductance or capacitance, consequently the name voltage controlled oscillators. The rate of change of oscillation frequency with respect to the control voltage is defined as the VCO gain( $K_{VCO}$ ) and is given by the following expression

$$K_{VCO} = \frac{df_{OSC}}{dV_C} \tag{2.9}$$

where  $f_{OSC}$  is the oscillation frequency and  $V_C$  is the control voltage. A larger  $K_{VCO}$  implies a larger variation in the frequency for a given voltage change, i.e., a large tuning range. However, a larger gain will amplify any noise present on the control node, resulting in the degradation of the phase noise performance of the oscillator. One way of overcoming this problem is explained in Section 4.4.

#### 2.4.1. Inductively Tuned VCOs

As the name suggests, inductively tuned VCOs are tuned by varying the tank inductance by means of a control voltage. This can be done either by selecting a different inductor for the tank from a bank of inductors for different control voltages [6], [7] or by switching ON/OFF an inductor in the circuit for a certain time interval depending on the control voltage [8].

Fig. 2.13 shows the schematic of an inductively tuned oscillator employing the latter method. The circuit has two inductors in parallel. One of the inductors is switched ON or OFF depending on the control voltage applied to the gate of the switching transistors  $M_{S1}$  and  $M_{S2}$ . When the control voltage is 0 volts, the switching transistors are OFF, and the frequency of oscillation is determined by the inductor  $L_1$  and is the minimum value. On the other hand, when  $V_{DD}$  is applied to the gate, both the inductors are in parallel and the frequency of oscillation is the largest. Between these two extremes, the effective inductance is  $L_1$  in parallel with a fraction of  $L_2$ , where the fraction is proportional to the time duration the transistors are ON in one cycle.

Figure 2.13. Schematic of the inductively tuned oscillator.

The tuning characteristics for the inductively tuned VCO are shown in Fig. 2.14. The current consumption of the VCO was 4.4mA from a 2.5V power supply. The highest frequency of oscillation is 2.584GHz whereas the lowest frequency of oscillation is 2.143GHz giving a tuning range of 441MHz which corresponds to 18.375% tuning. This oscillator has a  $K_{VCO}$  of around 180MHz/V. This value of  $K_{VCO}$  is very large making this oscillator very susceptible to noise on the control node.

Figure 2.14. Tuning characteristics of the inductively tuned oscillator.

#### **2.4.2.** Capacitively Tuned VCOs

Another means of tuning the oscillator is by using voltage dependent capacitances in the LC tank. Junction diodes and MOS varactors are most commonly used for tuned VCOs. These devices show a variation of capacitance with voltage.

The advantage of capacitively tuned VCOs over inductively tuned ones is that they occupy less die area and have better phase noise performance [8]. The oscillators may employ just a single varactor when the VCO gain is small or a varactor in combination with switchable capacitors when the gain is large. A detailed description of the different types of varactors is given in Section 4.

#### 3. INDUCTORS

#### 3.1. Introduction

Inductors form an integral part of the resonating tank used in LC oscillators. Both off-chip and on-chip inductors are used in oscillators. Because of the present trend of designing a system-on-a-chip, on-chip inductors are preferred. This also reduces the losses due to interconnects and sensitivity to noise when off-chip inductors are used. Although inductors consume a large amount of die-area, their size decreases with higher oscillation frequencies. Thus on-chip inductors are popular in RF LNAs and oscillators.

On-chip spiral inductors are widely used when inductance values smaller than 10nH are desired [35]. These inductors are capable of providing quality factors up to 15. The capacitance to the substrate determines the self-resonating frequency of the inductor. The self-resonance frequency limits the use of the inductor beyond a certain frequency. For higher quality factors and larger self-resonance frequencies, bond-wire inductors are commonly used.

Since inductors determine the oscillation frequency and also influence the phase noise, an accurate prediction of both requires good inductor models. Modeling of passive devices still poses a difficult problem to circuit designers. Accurate modeling of inductors requires an in-depth understanding of electromagnetism and inductor parasitics which become very important at RF [9], [10]. The accuracy with which the frequency of oscillation or the phase-noise of the oscillator can be predicted depends directly on the accuracy of the inductor model. ASITIC (Analysis and simulation of Inductors and Transformers for ICs) [39] and Agilent EEsof ADS-MOMENTUM are two software tools available for characterizing inductors.

ASITIC is an interactive tool capable of simulating spiral on-chip inductors in the IC environment. Depending on the dimensions of the inductor provided by the user, ASITIC generates a pi model for the inductor which can be included in simulations.

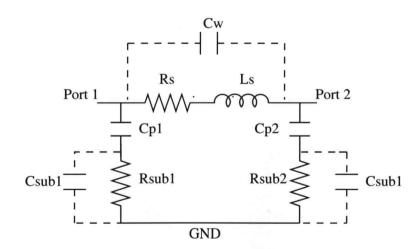

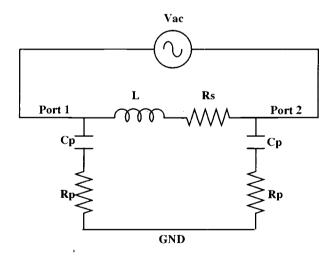

# 3.2. Simple Inductors

The layout and the physical model of a spiral inductor obtained from ASITIC are shown in Figs. 3.1 and 3.2, respectively. The dashed lines represent the components which are not modeled by ASITIC. In Fig. 3.2,  $L_S$  represents the series inductance and  $R_S$  represents the series resistance of the spiral and the underpass. The series resistance symbolizes the energy loss due to the skin effect at RF in the spiral, as well as due to the induced eddy currents in any conducting media close to the inductor such as the substrate [10]. The oxide capacitance between the spiral and the silicon substrate is modeled by  $C_{P1}$  and  $C_{P2}$ . The silicon substrate can be modeled by a resistances  $R_{SUB}$  or by a parallel combination of a resistance  $R_{SUB}$  and a capacitance  $C_{SUB}$ . The capacitance  $C_W$  between the input and output ports is due to the coupling between the underpass and the spiral.

The quality of an inductor is determined by its quality factor Q which is defined as

$$Q = \omega \frac{Energy\ stored}{Average\ power\ dissipated}.$$

(3.1)

For an inductor, the magnetic energy is of interest. The parasitic capacitances are responsible for the electric energy which is counter productive. Thus the energy stored represents the difference in the magnetic and the electric energy. The average power dissipated is the resistive loss in the inductor. For this reason, the

Figure 3.1. Layout of an on-chip spiral inductor.

Figure 3.2. Inductor model provided by ASITIC. The components shown by dashed lines are included in more accurate inductor models.

key to obtaining high Q inductors is to lower the series resistance of the inductor and reduce the parasitics to the substrate.

Another important factor determining the inductor performance is the self-resonance frequency. It is the frequency at which the peak magnetic and electric energies are equal. Consequently the quality factor of the inductor reduces to zero at the self-resonance frequency. Beyond the self-resonance frequency, no net magnetic energy is available from the inductor. Therefore the self-resonance frequency places a limit on the maximum useful frequency. Since this frequency is determined by the series inductance and the parasitic capacitances, it can be increased by reducing the parasitic capacitances.

In most technologies, the top most metal layer has the lowest sheet resistance. Therefore inductors are mostly laid out on the top most metal layer. This reduces the series resistance of the inductor. As an example, in the  $0.35\mu m$  TSMC 4 metal layer process, the top most metal layer has a sheet resistance of  $51 m\Omega/\Box$  whereas the lower 3 layers have a sheet resistance of  $80\text{-}83 m\Omega/\Box$ . Also the distance of the top metal layer from the substrate is larger giving smaller parasitic capacitances. Both of these are favorable from the view point of quality factor and the self-resonance frequency.

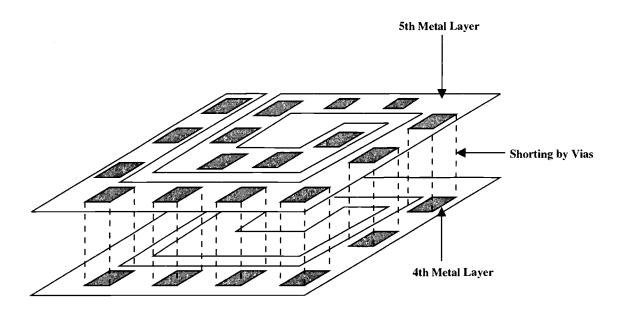

### 3.3. Stacked Inductors

It has been shown in [12] that stacking improves the quality factor of the inductors. Stacking metal layers means shorting adjacent metal layers with vias so that the effective thickness of the inductor increases as demonstrated in Fig. 3.3. This causes the series resistance of the inductor to reduce. Although this means the spacing between the inductor and the substrate decreases, causing an increase in the

parasitic capacitances, this is overshadowed by the decrease in the series resistance of the inductor, thereby increasing the quality factor. But stacking more and more layers eventually causes this benefit to diminish. Accordingly the number of layers to be stacked should be cautiously chosen.

Figure 3.3. Stacking metal layers to improve the inductor quality factor. The 5th and 4th metal layers have been stacked.

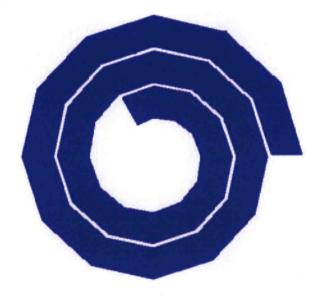

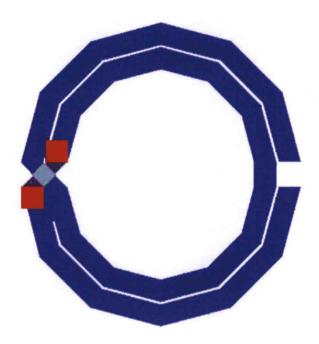

# 3.4. Symmetric Spiral Inductors

Since most oscillators designed are differential, differential operation of inductors is gaining importance. As shown in [11] and Section 3.5, differential operation of inductors shows better quality factor than single-ended operation. The layout of a symmetric center-tapped inductor, which can be used in such cases, is shown in Fig. 3.4. The difference between the simple inductor and the symmetric spiral is the absence of the underpass at one end of the symmetric spiral. When the symmetric

spiral is connected to the two differential terminals of the circuit, the differential outputs see the same inductance. Also the presence of the center-tap makes it possible to connect the center terminal to the power supply. Symmetric spiral inductors can be stacked.

Figure 3.4. Layout of a symmetric spiral inductor.

# 3.5. Comparison of Inductors

This section compares three different inductors, all of which have been modeled using ASITIC, for the  $0.35\mu m$  TSMC 4 metal layer process. These include a 1nH simple inductor, a 2nH simple inductor and a 2nH symmetrical spiral inductor. Only the top most metal layer was used for these inductors. The values of the inductance and the quality factors is tabulated in Table 3.1.  $Q_S$  represents the

single-ended quality factor of the inductors, whereas  $Q_D$  is the differential quality factor of the inductors, both of which are given by ASITIC.

| Inductor        | Inductance | Series Resistance | $Q_S$ | $Q_D$ |

|-----------------|------------|-------------------|-------|-------|

| 1nH Simple      | 1nH        | $2.23\Omega$      | 6.327 | 6.557 |

| 2nH Simple      | 1.98nH     | $3.34\Omega$      | 6.538 | 7.654 |

| 2nH Symmetrical | 2nH        | $3.41\Omega$      | 6.38  | 7.457 |

Table 3.1. Comparison of inductors.

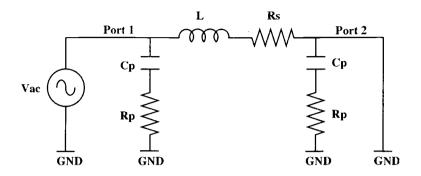

It can be observed from Table 3.1 that the differential quality factors are larger than the single-ended quality factors. This can be explained by considering Figs. 3.5-3.6 [13]. Fig. 3.5 shows the equivalent circuit of the inductor under single-ended operation, whereas Fig. 3.6 shows the same under differential operation. For single-ended operation, port 2 is grounded and the signal is applied to port 1, whereas for differential operation, the signal is applied across the two ports.

As seen from Fig. 3.5, the input impedance looking through port 1 is the parallel combination of the two components: one due to the inductance(L) in series with the resistance( $R_S$ ) and the second due to the parasitic capacitance( $C_P$ ) and resistance( $R_P$ ). Thus, the input impedance for the single-ended case is given by

$$Z_S = (R_S + jX_L)||(R_P - jX_C)$$

(3.2)

where  $X_L = 2\pi f L$  and  $X_C = 1/2\pi f C_P$  Therefore, on simplification,

$$Re(Z_S) = \frac{R_S^2 R_P + R_S R_P^2 + R_P X_L^2 + R_S X_C^2}{(R_S + R_P)^2 + (X_L + X_C)^2}$$

(3.3)

Figure 3.5. Circuit to obtain the inductor quality factor under single-ended excitation.

Figure 3.6. Circuit to obtain the inductor quality factor under differential excitation.

where  $Re(Z_S)$  represents the real part of the input impedance.

For the differential excitation, as seen from Fig. 3.6, the input impedance is again a combination of two terms: the first component is the same as for the single-ended case, i.e. the series L- $R_S$  combination, whereas the second is the series combination of the two parasitic  $C_P$ - $R_P$  circuits. The input impedance for the differential case is given by

$$Z_D = (R_S + jX_L)||(2R_P - j2X_C)$$

(3.4)

which yields

$$Re(Z_D) = \frac{2R_S^2 R_P + 4R_S R_P^2 + 2R_P X_L^2 + 4R_S X_C^2}{(R_S + 2R_P)^2 + (X_L + 2X_C)^2}.$$

(3.5)

Assuming  $R_S \ll R_P$  and  $X_L \ll X_C$ , which are generally true, gives

$$Re(Z_S) = R_S + \frac{R_S^2 R_P + R_P X_L^2}{R_P^2 + X_C^2}$$

(3.6)

and

$$Re(Z_D) = R_S + \frac{R_S^2 R_P + R_P X_L^2}{2R_P^2 + 2X_C^2}. (3.7)$$

The quality factor of the inductor can be written as

$$Q = \frac{2\pi f L}{Real(Z_{INPUT})}. (3.8)$$

Comparing (3.6) and (3.7), we observe that the real part of the input impedance is the same for single-ended and differential excitation at low frequencies. This is because the parasitics do not affect the inductors due to the high capacitive impedance. Accordingly both cases will have similar quality factors at low frequencies. However, as the frequency increases, the impedance of the parasitics increases more for the differential case, causing the real part of the input impedance to drop, as evident from (3.7). This results in an improvement of the quality factor.

## 3.6. Inductor Layout

The inductors used in the VCOs designed were stacked inductors. The National process had five metal layers. The inductors were formed by stacking the metal layers 2, 3, 4 and 5. Metal layer 1 was used for the underpass. The vias were placed at minimum allowable separation to allow maximum shorting between the stacked layers.

The value of the inductors used were 1nH and 2nH. The quality factor and the self-resonance frequency of the two inductors were obtained using the inductor model provided by National. The quality factor can be obtained in simulations by applying an ac signal of magnitude one to the relevant inductor port and using the following expression:

$$Q = \frac{\frac{1}{I_{IMAG}}}{\frac{1}{I_{REAL}}} \tag{3.9}$$

where  $I_{REAL}$  and  $I_{IMAG}$  are the real and imaginary parts of the ac current through the voltage source. The quality factor of the two inductors is shown in Figs. 3.7-3.8.

It can be observed from the plots that the quality factor for the 1nH inductor is 6.77 at 2.4GHz and the self-resonance frequency is 36GHz. The 2nH inductor has a quality factor of 6.61 at 2.4GHz with a self-resonance frequency of 28GHz. The above mentioned quality factors are single-ended quality factors, which means they are obtained with one port of the inductor grounded and the signal applied to the other port.

Fig. 3.9 shows the quality factor plot of the 2nH inductor when it is differentially operated. The signal is applied between the two ports. It can be observed that the quality factor at 2.4GHz is 7.69 and the self resonance frequency is 34GHz. Thus differential operation of inductors does enhance the quality factor of the inductor.

Figure 3.7. Quality factor versus frequency plot for the 1nH inductor.

Figure 3.8. Quality factor versus frequency plot for the 2nH inductor.

Figure 3.9. Differential quality factor plot for the 2nH inductor.

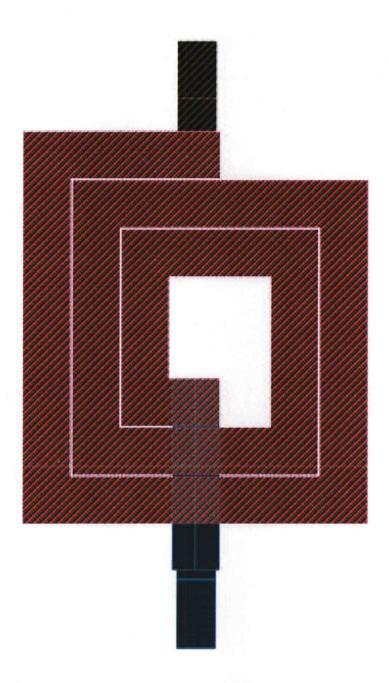

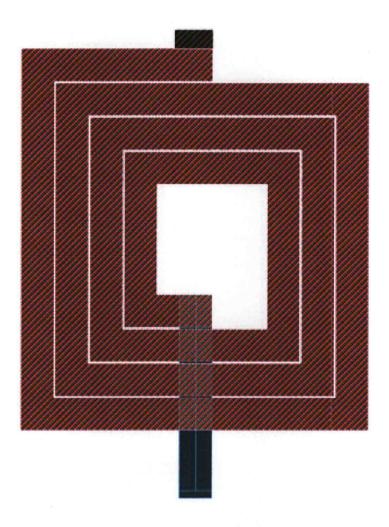

The layout of the two inductors is shown in Figs. 3.10-3.11. The 1nH inductor occupies an area of  $175\mu m \times 200\mu m$  whereas the 2nH inductor spans an area of  $182\mu m \times 200\mu m$ .

Figure 3.10. Layout of the 1nH inductor.

Figure 3.11. Layout of the 2nH inductor.

#### 4. VARACTORS

## 4.1. Introduction

Although inductors can be used for tuning an oscillator, voltage dependent capacitors (varactors) are more commonly used for varying the frequency of oscillation. Varactors can be of various types: p-n junctions, MOS transistors and MOS transistors in conjunction with binary weighted switched capacitors. All of these are capable of providing a voltage dependent capacitance variation. Ideally it is expected that the tuning characteristic is linear, since a non-linear characteristic will have a steeper slope for the same voltage variation. This means that the  $K_{VCO}$  would be larger, causing the control node to be sensitive to noise.

The varactor should have a large quality factor, ideally infinite. This is possible only when the series resistance is zero. Another desired feature of the varactor is the ratio of the maximum capacitance to the smallest capacitance be large for a larger tuning range. Practically most of the varactors are non-linear and have a limited  $C_{MAX}/C_{MIN}$  ratio. Also the parasitic resistances cause a degradation in the quality factor.

The most popular type of varactor used in CMOS technologies is the MOS varactor.

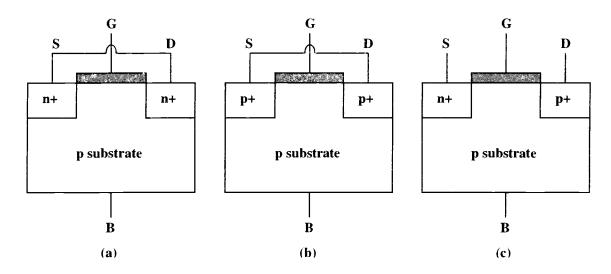

## 4.2. MOS Varactors

MOS varactors can be of three types, namely inversion mode varactors, accumulation mode varactors and gated varactors [14], [15], [16]. Fig. 4.1 shows the

cross-section of the three different varactors. The description of each varactor is discussed below.

Figure 4.1. Cross-section of the different varactors: (a) Inversion mode varactor. (b) Accumulation mode varactor. (c) Gated varactor.

#### **4.2.1.** Inversion Mode Varactor

The C-V characteristics of the MOS capacitor shown in Fig. 4.1(a), with the drain, source and bulk terminals tied, is shown in Fig. 4.2. The capacitance per unit width of the transistor is plotted against the gate-source voltage. The simulations for C-V characteristics of the varactors were performed using MEDICI [40], which is a two-dimensional device simulator.

Three distinct regions can be observed from the C-V characteristics. In the accumulation region, which occurs when  $V_{GS} \ll V_{TH}$ , the interface between the gate oxide and silicon is negative allowing the holes to move freely. As  $V_{GB}$  increases, the holes are repelled and a depletion layer is formed below the oxide, and the transistor

Figure 4.2. C-V characteristics of the MOS capacitor.

operates in the depletion region. As the voltage increases further, negative charges get attracted to the positively charged gate oxide giving rise to the inversion mode of operation. Depending on the density of negative charge carriers in the interface, this region of operation is subdivided into weak, moderate and strong inversion regions. In the accumulation and the strong inversion regions, the MOS capacitance reaches a value of  $C_{OX}$ , the gate oxide capacitance.

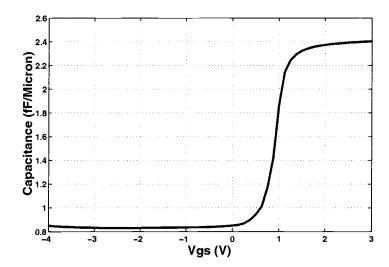

For an inversion mode varactor, the device should not enter the accumulation region [14], [15]. This is accomplished by connecting the bulk to the appropriate bias so that the pn junctions of the transistors are always reverse biased. Fig. 4.3 shows the tuning characteristics of the varactor shown in Fig. 4.1(a), with the bulk tied to the most negative supply.

Figure 4.3. C-V characteristics of the inversion mode varactor.

It can be observed that for positive voltages, the n+ drain-source regions provide the electrons for the formation of the inversion layer, and the device operates in the inversion region. The device doesn't enter the accumulation region since the bulk is never positive as compared to the gate. A capacitance variation  $(C_{MAX}/C_{MIN})$  of 2.82 is observed.

## **4.2.2.** Accumulation Mode Varactor

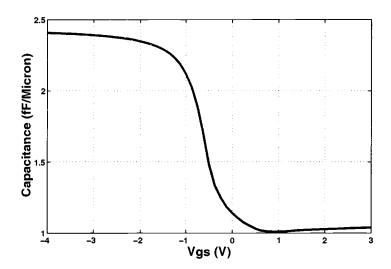

Another alternative for obtaining the capacitance tuning is by operating the transistor in accumulation and depletion regions only [14], [15], [27]. Since the inversion regime is undesired, the doping profile of the drain-source regions is changed. For the accumulation mode varactor in Fig. 4.1(b), the drain-source diffusions are p+ type. The capacitance variation of this varactor is depicted in Fig. 4.4.

Figure 4.4. C-V characteristics of the accumulation mode varactor.

It is seen from these characteristics, that the device operates in the accumulation region for negative voltages and flattens out at positive voltages. The capacitance variation  $(C_{MAX}/C_{MIN})$  obtained with this varactor is 2.32.

## 4.2.3. Gated Varactor

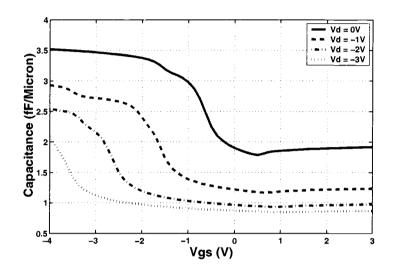

Another varactor which is capable of providing a wide tuning range is the gated varactor [16], [17]. The inversion mode and accumulation mode varactors are two terminal varactors, in the sense that the voltage of one terminal (gate) is varied with respect to the other (source). The gated varactor is a three terminal varactor as shown in Fig. 4.1(c). For the gated varactor, the device capacitance is defined as the capacitance seen from the drain, unlike the inversion mode and accumulation mode varactors, where the device capacitance was the capacitance looking through

the gate. A family of C-V curves can be obtained by sweeping the gate voltage with the drain voltage fixed and then repeating this for different drain voltages. The capacitance variation for the gated variator is depicted in Fig. 4.5.

Figure 4.5. C-V characteristics of the gated varactor.

With the drain voltage fixed, a variation in the gate voltage causes the capacitance under the gate to vary in a manner similar to the accumulation mode varactor. Reducing the gate voltage causes the gate-bulk capacitance to increase from  $C_{OX}$  in series with  $C_{DEPLETION}$  to  $C_{OX}$ . The capacitance looking through the drain is the parallel combination of the gate-bulk capacitance and the source-bulk depletion capacitance. Therefore the largest capacitance for this varactor is larger than that for the inversion and accumulation mode varactors, i.e.  $C_{OX}$ . As the drain voltage is decreased, the source-bulk voltage increases causing the depletion layer to increase. This reduces the source-bulk depletion capacitance thereby decreasing

the capacitance seen through the drain. Thus, by changing the drain and the gate voltage simultaneously, it is possible to move from one curve to the other. The capacitance variation  $(C_{MAX}/C_{MIN})$  for this variation is around 4, which is much greater than that obtained with the inversion or accumulation mode variators.

# 4.3. MOS Transistors as Varactors

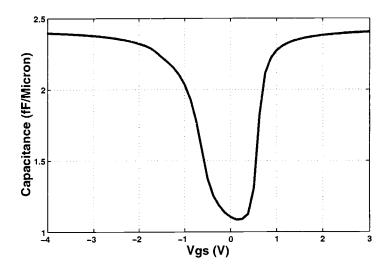

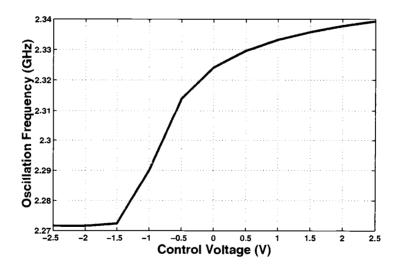

In the absence of models for the varactors explained in the previous section, the designer has to rely on the MOS transistor for use as a varactor. The tuning characteristics of NMOS and PMOS transistors are explained in this section. All the simulations were performed using HSPICE with a transistor size of  $300\mu\text{m}/0.24\mu\text{m}$ .

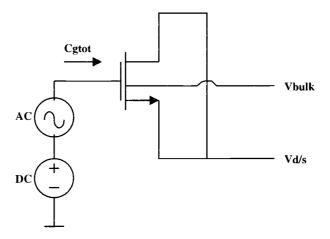

The gate of the transistors was connected to the oscillator and the control voltage was applied to either the bulk terminal or the drain-source terminal. For each of the transistors (NMOS and PMOS), two set of simulations were performed to obtain the capacitor tuning characteristics. The gate of the transistor was biased at the same potential as in the oscillator circuit. An ac signal was superimposed on the gate to observe the frequency dependent capacitances. The value of *Cgtot* gives the total capacitance seen from the gate node. One of the circuit schematics used for simulation is given in Fig. 4.6

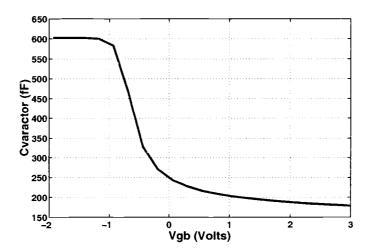

The C-V plot obtained for the NMOS transistor, with the bulk terminal swept from -2.5V to 2.5V and the drain-source terminals connected to 2.5V to prevent the p-n junction diode from turning ON, is shown in Fig. 4.7.

Increasing the bulk potential causes the transistor to move from the accumulation region to the depletion region. The gate-bulk capacitance changes from  $C_{OX}$  in the accumulation region to  $C_{OX}$  in series with  $C_{DEPLETION}$  in the depletion region. Similar characteristics were obtained for the PMOS transistor with the bulk

Figure 4.6. Circuit used to determine the C-V characteristics of the varactor based on a MOS transistor.

Figure 4.7. C-V characteristics of an NMOS transistor when the bulk voltage is varied.

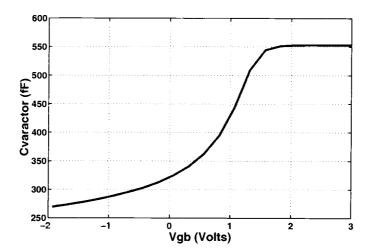

node swept and the drain-source terminals connected to -2.5V. The result for the PMOS transistor is illustrated in Fig. 4.8.

Figure 4.8. C-V characteristics of a PMOS transistor when the bulk voltage is varied.

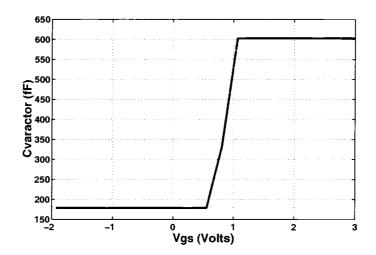

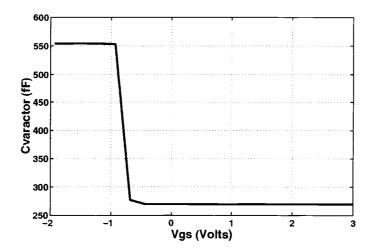

The results obtained for the NMOS and PMOS transistors with the drainsource terminals swept and the bulk terminal biased appropriately to reverse bias the junctions are shown in Figs. 4.9-4.10.

Applying the control voltage to the drain-source terminal causes the junction depletion capacitance to change. The device is in the depletion region when  $|V_{GS}| < |V_{TH}|$  and in the inversion region when  $|V_{GS}| > |V_{TH}|$ . Accordingly the capacitance seen from the gate changes sharply as the device moves from one region of operation to the other.

It can be observed from Figs. 4.7-4.10 that the C-V characteristics obtained are smoother when the bulk is varied. Therefore the bulk node was chosen as the

Figure 4.9. C-V characteristics of an NMOS transistor with varying Vd/s.

Figure 4.10. C-V characteristics of a PMOS transistor with varying Vd/s.

control terminal in the oscillators designed. Since the bulk terminal needs to be varied, only a PMOS transistor can be used for the varactor, as its bulk terminal is available in an N-well process. Although the capacitance variation in Fig. 4.10 is small, a high tuning range was achieved by using this varactor in conjunction with an array of binary weighted capacitors as described in the next section.

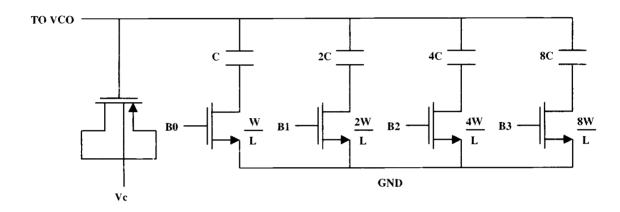

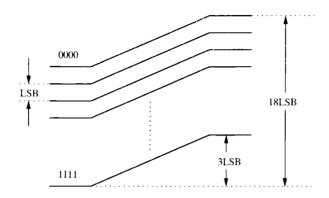

# 4.4. Varactor Implementation Using Switched Capacitor Array

Increasing the tuning range of the varactors increases the  $K_{VCO}$ . This increase in the VCO gain implies a larger gain for any noise coupling to the control node. This in turn, will degrade the phase noise performance of the VCO. Consequently a circuit which has a large tuning range but a small  $K_{VCO}$  is desirable. One such circuit is shown in Fig. 4.11 [6]. The varactor is designed to provide a small tuning range with a small  $K_{VCO}$ , preferably in the range of 20-30MHz/V. The fixed capacitors are switched ON or OFF by means of a switch realized by the NMOS transistor. Thus the varactor is responsible for the fine tuning and the switched capacitor provides the necessary coarse tuning. The typical tuning curves for this circuit are shown in Fig. 4.12. Tuning elements corresponds to the switch state (ON/OFF). Any variations during fabrication could cause the frequency tuning to be discontinuous. Therefore a certain amount of overlap between the curves is necessary.

The capacitances in the switched capacitor implementation are chosen as C, 2C and 4C. When the switches are turned ON in a binary sequence from 000 to 111, the capacitances C, 2C, 3C, 4C... get added to the tank capacitance. The switch sizes are chosen as W/L, 2W/L and 4W/L. This ensures that the capacitance of the

Figure 4.11. Binary weighted switched capacitor circuit to provide higher tuning range without increasing the VCO gain.

Figure 4.12. Tuning characteristics explaining the principle of switched tuning.

switch scales linearly with the binary capacitances, thereby providing more uniform tuning curves.

The use of this circuit in an actual implementation would require a digital control block which would track the frequency provided by the oscillator and accordingly control the varactor control voltage in case of small variations or change the bits to move on the other tuning curves for larger frequency variations. The greater the number of switched capacitors, the smaller the tuning range of the varactor to span the same frequency tuning range. Increasing the number of switched capacitors would require a smaller capacitance making it difficult to realize well matched capacitances. Accordingly a trade-off is necessary to decide the number of steps to be used.

The quality factor of the switched capacitor array affects the tank quality factor. Hence it is necessary to know the quality factor of the varactors when the switch is ON or OFF. Fig. 4.13 shows the quality factor of only the switched capacitor array when all the switches are OFF, whereas Fig. 4.14 depicts the quality factor when all the switches are ON.

It can be observed from Fig. 4.13, that the quality factor is very large when the switches are OFF, and the capacitor bank doesn't deteriorate the tank quality factor. When the switches are ON, the quality factor drops down by several orders of magnitude and affects the tank quality factor. The parasitics and gate resistance would further degrade the quality factor. Consequently the start-up condition for the oscillators should be determined with all the switches ON. This will ensure oscillations under all varactor switch settings.

Figure 4.13. Quality factor of the switched capacitor circuit when all switches are  ${\rm OFF}.$

Figure 4.14. Quality factor of the switched capacitor circuit when all switches are ON.

# 4.5. Varactor Layout

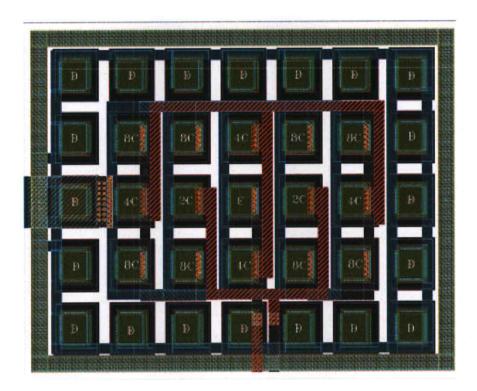

The layout of the varactor is crucial since the tuning curves depend directly on the binary weighted capacitances and the matching between them. The polysubstrate oxide capacitance was used for generating the capacitors. The layout of the array of capacitors used for switched tuning is illustrated in Fig. 4.15. The smallest capacitance C was chosen to be the unit capacitance and was repeated depending on the capacitance value desired. Thus for 2C, two unit capacitors were connected in parallel. The binary weighted capacitors were arranged such that the linear gradients along the x-direction and y-direction were minimized. The letter D indicates the dummy capacitors used around the array for matching purposes. Although the dummy capacitors used in this case were the same as the unit capacitance, smaller dummy capacitors could be used to save area.

Figure 4.15. Layout of the capacitor bank used in the varactor circuitry.

## 5. PHASE NOISE IN OSCILLATORS

## 5.1. Contributors of Phase Noise