#### AN ABSTRACT OF THE THESIS OF

| Yaohua Yang    | for the degree of    | Master of Science     | in Elec   | trical & | & Com-   |

|----------------|----------------------|-----------------------|-----------|----------|----------|

| puter Engineer | ring presented on Fe | ebruary 20, 1993.     |           |          |          |

| Title: Effects | and Compensation     | of the Analog Integra | tor Nonid | ealities | in Dual- |

| Quantization I | Delta-Sigma Modula   | Redact                | ed for    | · Priv   | vacv     |

| Abstract appro | oved:                | Gasor C. Teme         |           |          | - ·      |

Oversampled delta-sigma ( $\Delta\Sigma$ ) modulators have been more and more widely used in the high-resolution analog-to-digital (A/D) data conversions. These converter architectures trade the high speed of circuit operation and the high degree of complexity in the digital signal processing (DSP) circuitry for the high resolution in data conversion which is otherwise hard to achieve under current VLSI technology [1].

Stability limitation in single-stage single-bit  $\Delta\Sigma$  modulators makes their implementations more difficult [1]. And although the multibit single-stage  $\Delta\Sigma$  modulators do not have stability limitations, they suffer from the nonlinearity error in the multibit digital-to-analog (D/A) converter in the feedback loop [1]. Thus another kind of modulators, namely dual-quantization  $\Delta\Sigma$  modulators have attracted more and more attentions recently. Without stability limitation, this kind of modulators can ideally achieve very high signal-to-noise-ratio (SNR) at a relatively low oversampling ratio (OSR). However, this kind of modulators rely on the perfect matching between the analog and digital circuit transfer functions which is

hard to achieve. As a result, the SNRs of the A/D converters based on this kind of modulators are far below the ideal SNRs.

This thesis studies the effects of the nonideal analog circuitry on the SNR performance in various kinds of dual-quantization  $\Delta\Sigma$  modulators. The possibility of digital estimation and compensation of these nonidealities is explored. Estimation algorithms and compensation schemes are presented. Both theory and simulation results showed that 10-20 dB SNR recovery is possible using these compensation schemes at a cost of a little more complicated digital circuitry.

### Effects and Compensation of the Analog Integrator Nonidealities in Dual-Quantization Delta-Sigma Modulators

by

Yaohua Yang

A THESIS

Submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of Master of Science

Completed February 12, 1993

Commencement June 1993

#### APPROVED:

### Redacted for Privacy

| ~~~~~~~~~~~                                                       |

|-------------------------------------------------------------------|

| Professor of Electrical & Computer Engineering in charge of major |

| respect of Escential & Computer Engineering in charge of major    |

| Dodootod for Drive ov                                             |

| Redacted for Privacy                                              |

| 110000000                                                         |

| ricaacica for i fivacy                                  |  |

|---------------------------------------------------------|--|

| Head of Department of Electrical & Computer Engineering |  |

| Redacted for Privacy                                    |  |

| Dean of Graduate School | 1 |  |  |

|-------------------------|---|--|--|

| ( )                     | V |  |  |

| Date thesis is presented | February 20, 1993 |  |

|--------------------------|-------------------|--|

| Typed by                 | Yaohua Yang       |  |

#### TABLE OF CONTENTS

| CHAPTER 1. INTRODUCTION                                                                                        | 1       |

|----------------------------------------------------------------------------------------------------------------|---------|

| 1.1 How Oversampled Delta-Sigma A/Ds Work                                                                      | 1       |

| 1.2 How Dual-Quantization Delta-Sigma Modulators Work                                                          | 3       |

| 1.3 Nonidealities in the Analog Integrators                                                                    | 5       |

| CHAPTER 2. EFFECTS OF INTEGRATOR NONIDEALITIES ON SNR ODUAL-QUANTIZATION DELTA-SIGMA MODULATORS                | OF<br>8 |

| 2.1 First-order Leslie-Singh Modulator                                                                         | 8       |

| 2.2 Second-order Leslie-Singh Modulator                                                                        | 12      |

| 2.3 Cascade 2-1 Modulator with Multibit Second-Stage                                                           | 17      |

| 2.4 Cascade 2-2 Modulator                                                                                      | 21      |

| CHAPTER 3. DIGITAL COMPENSATION OF ANALOG INTEGRATOR NONIDEALITIES IN DUAL-QUANTIZATION DELTA-SIGMA MODULATORS |         |

| 3.1 Compensation for First-order Leslie-Singh Modulator                                                        | 25      |

| 3.2 Compensation for Second-order Leslie-Singh Modulator                                                       | 27      |

| 3.3 Compensation for Cascade 2-1 Modulator                                                                     | 29      |

| 3.4 Compensation for Cascade 2-2 Modulator                                                                     | 29      |

| 3.5 Decimation Filtering for Compensated Dual-Quantization                                                     |         |

| Delta-Sigma modulators                                                                                         | 31      |

| CHAPTER 4. OFF-LINE ESTIMATION OF INTEGRATOR POLE ERRORS IN DUAL-QUNATIZATION DELTA-SIGMA MODULATORS           | 35      |

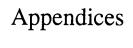

| 4.1 Precharge Phase                                                                                            | 36      |

| 4.2 Initialization and Discharge Phase                                                                         | 37      |

| 4.3 Effects of Circuit Nonidealities on Pole Error Estimation                                                  | 39      |

| 4.4 SWITCAP Simulation Results                                                                                 | 43      |

| 4.5 Calculation Phase                                                                           | 47           |

|-------------------------------------------------------------------------------------------------|--------------|

| BIBLIOGRAPHY                                                                                    | 49           |

| APPENDIX 1. FIRST-STAGE LEAKAGE NOISE CALCULATION FIRST-ORDER LESLIE-SINGH MODULATOR            | OF THE<br>50 |

| APPENDIX 2. FIRST-STAGE LEAKAGE NOISE CALCULATE HIGH-ORDER DUAL-QUANTIZATION DELTA-SIGMA MODULA |              |

#### LIST OF FIGURES

| Figure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Page         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Oversampled delta-sigma converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1            |

| 2. First-order Leslie-Singh modulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4            |

| 3. Switched-capacitor integrator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5            |

| 4. SNR versus analog integrator opamp DC gain curves in 1-bit/8-bit Leslie-Singh modulator with -10 dB input and an oversampling rational curves and an oversampling rational curves are supplied to the control of the curves and curves are supplied to the curves are |              |

| 5. SNR versus second-stage quantizer resolution curves in a first-o Singh modulator with a -10 dB input and an integrator opamp DC dB and an oversampling ratio of 128.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | rder Leslie- |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 13           |

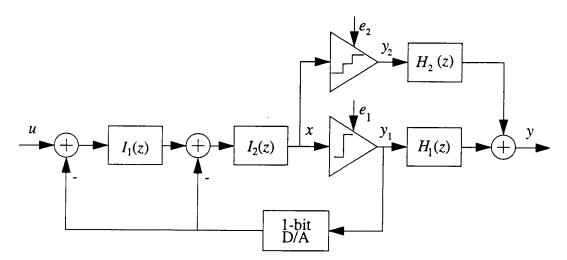

| 6. Second-order Leslie-Singh modulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 14           |

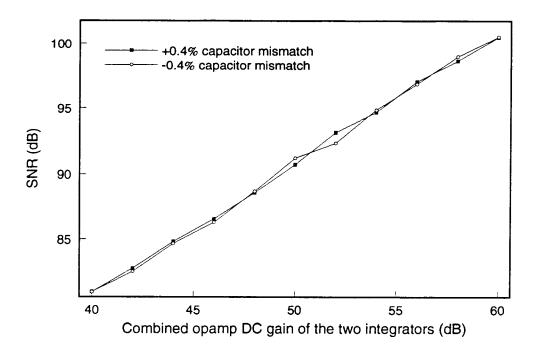

| 7. SNR versus combined integrator opamp DC gain curves of a 1-b ond-order Leslie-Singh modulator with -10 dB input and an oversar of 64. (Both opamps have the same DC gain.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15           |

| 8. SNR versus combined integrator opamp DC gain curves in a 1-b ond-order Leslie-Singh modulator with -10 dB input and an oversar of 64. (Individual opamps have different DC gains.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15           |

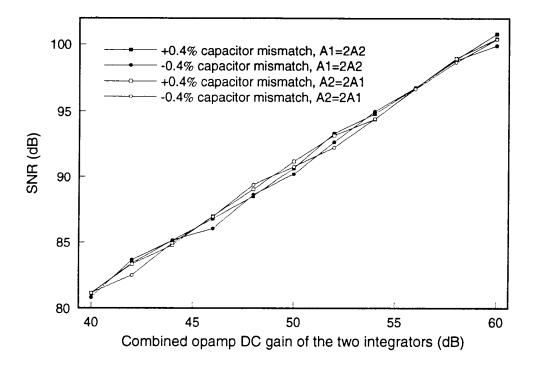

| 9. SNR versus second-stage quantizer resolution curves in a second-or Singh modulator with a -10 dB input, an oversampling ratio of 64 bined opamp DC gain of 65 dB. (Both opamps have the same DC g                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4 and com-   |

| 10. SNR versus second-stage quantizer resolution curves in a se                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |

| Leslie-Singh modulator with a -10 dB input, an oversampling ratic combined opamp DC gain of 65 dB. (Individual opamps have digains.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | o of 64 and  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 16           |

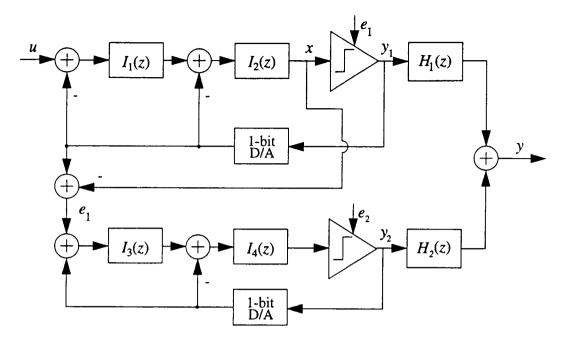

| 11. Block diagram of a multibit cascade 2-1 modulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 18           |

12. SNR versus combined integrator opamp DC gain of the first-stage integrators curves in a 1-bit/8-bit cascade 2-1 modulator with a -10 dB input and an oversampling ratio of 64. (Both opamps have the same DC gain.)

19

13. SNR versus combined integrator opamp DC gain of the first-stage integrators curves in a 1-bit/8-bit cascade 2-1 modulator with a -10 dB input and an oversampling ratio of 64. (Individual opamps have different DC gains, A<sub>3</sub>=50 dB)

20

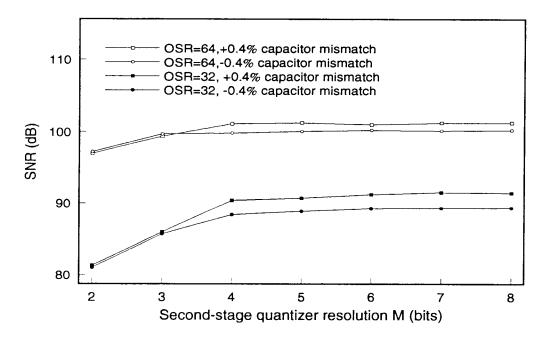

14. SNR versus second-stage quantizer resolution curves in a multibit cascade 2-1 modulator with a -10 dB input and an oversampling ratio of 32 or 64,  $A_3$ =50 dB,  $A_1$ = $A_2$ =63.01 dB, (first-stage combined opamp DC gain = 60 dB).

20

15. Block diagram of a cascade 2-2 modulator

22

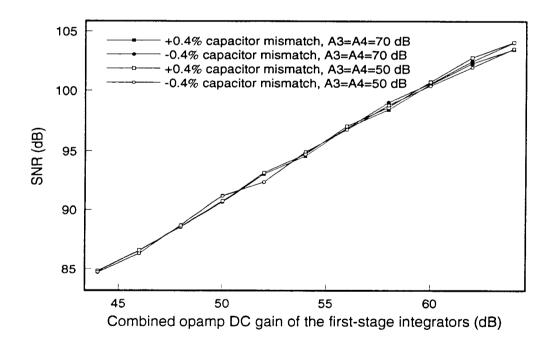

16. SNR versus combined integrator opamp DC gain of the first-stage integrators curves in a single-bit cascade 2-2 modulator with a -10 dB input and an oversampling ratio of 64. (Both opamps in the first stage have the same DC gain.)

22

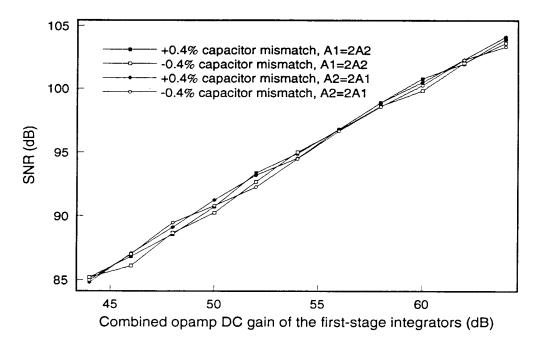

17. SNR versus combined integrator opamp DC gain of the first-stage integrators curves in a single-bit cascade 2-2 modulator with a -10 dB input and an oversampling ratio of 64, A<sub>3</sub>=A<sub>4</sub>=50 dB (Individual opamps in first stage have different DC gains.)

23

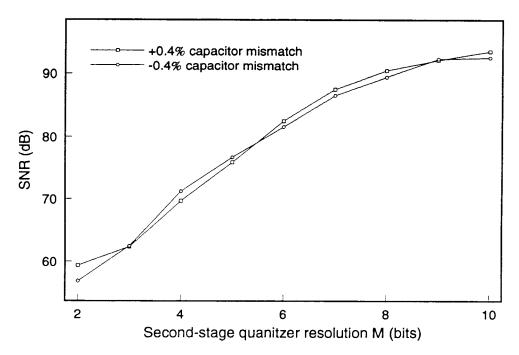

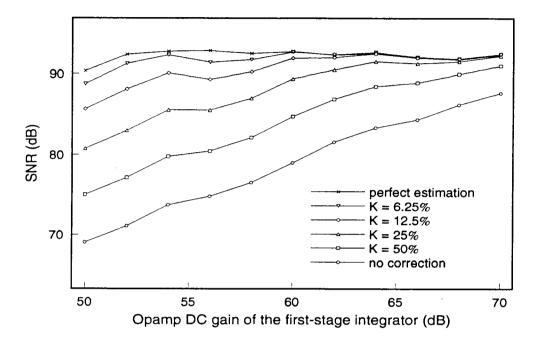

18. SNR versus opamp DC gain of the first-stage integrator in a compensated 1-bit/10-bit first-order Leslie-Singh modulator with different estimation accuracy of the integrator pole error (0.4% capacitor mismatch, OSR=128, -10 dB input).

26

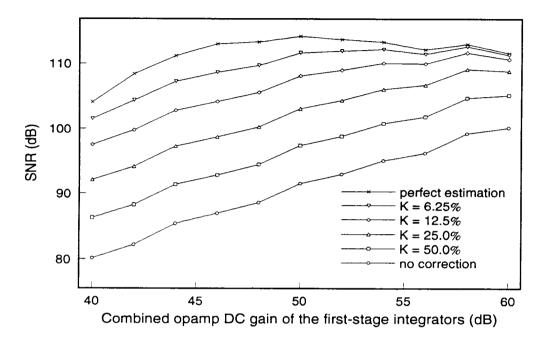

19. SNR versus the combined opamp DC gain of the first-stage integrators in a compensated 1-bit/10-bit second-order Leslie-Singh modulator with different estimation accuracy of the integrator pole error (0.4% capacitor mismatch, OSR=64, -10 dB input).

28

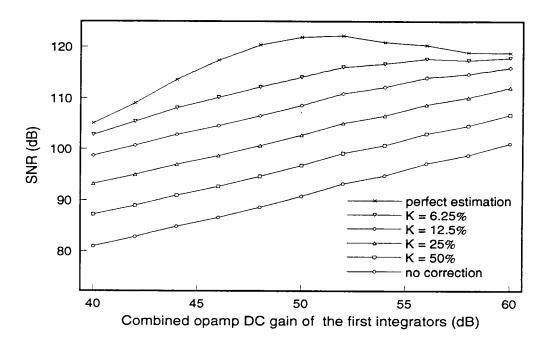

20. SNR versus combined opamp DC gain of the first-stage integrators in a com-

pensated 1-bit/10-bit cascade 2-1 modulator with different estimation accuracy of the integrator pole error (0.4% capacitor mismatch, OSR=64, -10 dB input, second-stage opamp DC gain 50 dB).

30

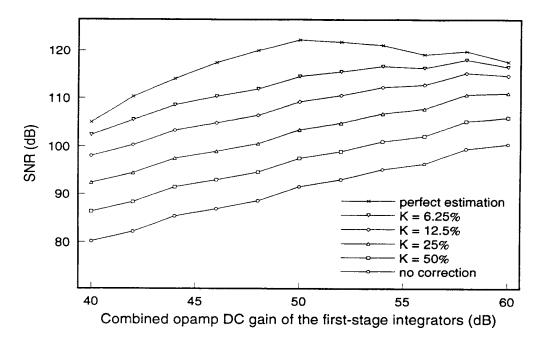

21. SNR versus combined opamp DC gain of the first-stage integrators in a compensated 1-bit/3-bit cascade 2-2 modulator with different estimation accuracy of the integrator pole error (0.4% capacitor mismatch, OSR=64, -10 dB input, second-stage opamp DC gain 50 dB).

30

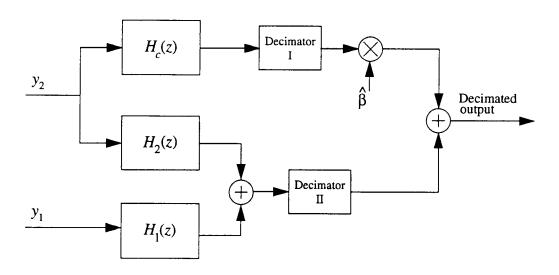

22. Block diagram of post-decimation digital compensation for integrator nonidealities in dual-quantization delta-sigma modulators

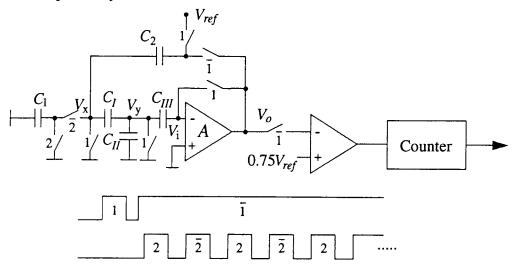

23. Single-ended version of estimation circuit

24. Effects of the opamp offset voltage on the estimation accuracy

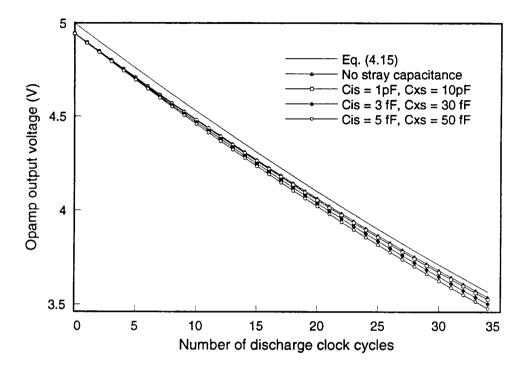

25. Effects of stray capacitances on the estimation accuracy

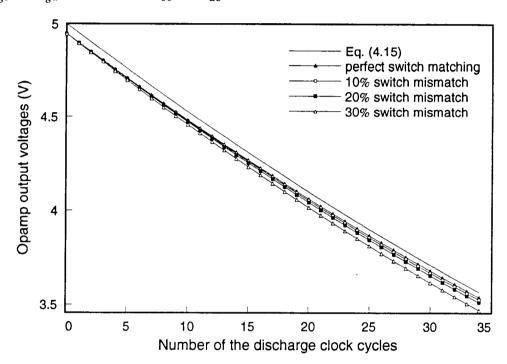

26. Effects of the clock feedthrough noise on the estimation accuracy

27. Effects of circuit nonidealities on the estimation accuracy

47

# Effects and Compensation of the Analog Integrator Nonidealities in Dual-Quantization Delta-Sigma Modulators

#### Chapter 1. Introduction

#### 1.1 How Oversampled Delta-Sigma A/Ds Work

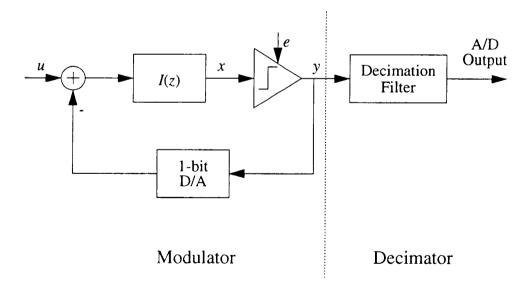

As an example, consider the first-order oversampled  $\Delta\Sigma$  A/D shown in Figure 1, where  $I(z)=z^{-1}/(1-z^{-1})$ . The modulator consists of an analog filter, a one-bit A/D converter (also called quantizer) and a one-bit D/A converter in the feedback loop. It converts the analog input, a signal bandlimited by  $f_s$  but sampled at a much higher clock frequency  $f_c$ , to a one-bit digital signal at the same clock rate. The digital decimation filter following the modulator decimates the modulator output, which is a low resolution but high frequency digital signal, to a high-resolution signal at the Nyquist rate  $(2f_s)$ .

Figure 1. Oversampled  $\Delta\Sigma$  A/D converter

The input-output relationship of the modulator can be shown as

$$y(nT) = u(nT-T) + e(nT) - e(nT-T),$$

(1.1)

where e = y - x is the quantization error of the one-bit quantizer, and T is the clock period. Thus the z domain input-output relationship of the modulator is

$$Y(z) = z^{-1} \cdot U(z) + (1 - z^{-1}) E(z), \qquad (1.2)$$

where  $z^{-1}$  is the signal transfer function (STF) of the modulator, and  $1-z^{-1}$  is the noise transfer function (NTF). Thus the input signal is passed to the output without any change except for a delay, which is usually insignificant, and the quantization noise e is filtered by a high-pass transfer function so that it has less spectrum density in the low frequency range, where the input signal has most of its energy in. Most of the noise energy is in the frequency range of  $[f_s, f_c/2]$ , and are removed by a low-pass digital decimation filter following the modulator.

If we model signal e as a white noise, the noise energy from  $[0, f_s]$  is

$$n_0^2 = \frac{\pi^2}{3 \cdot OSR^3} \cdot \sigma_e^2 \tag{1.3}$$

[1], where OSR is defined as  $f_c/2f_s$ , and  $\sigma_e^2$  is the mean square value of the quantization noise.

It can be shown that if the transfer function of the analog filter in the modulator shown in Figure 1 is modified, more efficient NTFs can be achieved [1]. More specifically, the z domain input-output relationship of an Lth-order  $\Delta\Sigma$  modulator is

$$Y(z) = z^{-1} \cdot U(z) + (1 - z^{-1})^{L} E(z), \qquad (1.4)$$

and its in-band noise energy is

$$n_0^2 = \frac{\pi^{2L}}{(2L+1) \cdot OSR^{2L+1}} \cdot \sigma_e^2 \tag{1.5}$$

[1]. From the above equation we know that with a given OSR, the higher the modulator order is, the less the in-band noise energy. However, this kind of straightforward design has a severe limitation, namely the high-order (L>2) single-stage single-bit modulators are usually unstable [1]. Although they can be stabilized by using IIR NTFs [2], the SNRs may be degraded significantly compared to those achieved by the modulators with transfer functions shown in Eq. (1.4). Single-stage multibit modulators can be guaranteed to be stable if the multibit quantizer has enough resolution, and can achieve the NTFs shown in Eq. (1.4), but they suffer from the nonlinearity error introduced by the multibit feedback D/A. Without the above limitations dual-quantization  $\Delta\Sigma$  modulators have attracted more and more attentions recently as introduced below.

#### 1.2 How Dual-Quantization Delta-Sigma Modulators Work

Dual-quantization  $\Delta\Sigma$  modulators usually have a low order modulator as its first stage, and feed the first-stage quantization noise or the input of the first-stage quantizer to the second stage, which is usually another low order modulator or simply a multibit quantizer, and then the outputs of the two stages are combined appropriately to give the final output of the modulator. Because there are no high-order modulators in either stage, and there are no feedbacks between the two stages, stability is guaranteed.

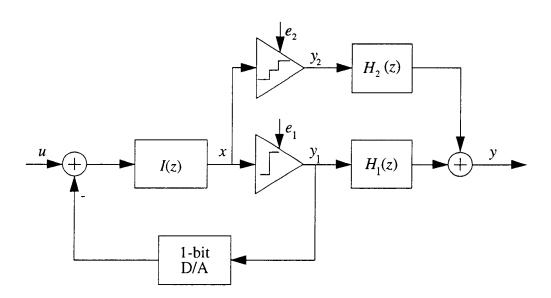

As an example, consider the first-order Leslie-Singh modulator [3] shown in Figure 2. If the analog integrator is ideal, namely

$$I(z) = \frac{z^{-1}}{1 - z^{-1}},\tag{1.6}$$

and the outputs of the two stages are combined properly by choosing

$$H_1(z) = z^{-1} (1.7)$$

and

$$H_2(z) = 1 - z^{-1}, (1.8)$$

it can be shown that its z domain input-output relationship is

$$Y(z) = z^{-1} \cdot U(z) + (1 - z^{-1}) \cdot E_2(z) , \qquad (1.9)$$

where  $e_2 = y_2 - x$  is the second-stage quantization noise. It is obviously from Eq. (1.9) that ideally the first-stage quantization noise  $e_1$  is perfectly cancelled, and the only noise which appears in the final output is the second-stage quantization noise, which is smaller due to the high resolution of the second-stage quantizer. Thus the in-band noise energy is much reduced and the SNR improved. Using similar ideas, higher order modulators can be designed. However, the above results are based the fact the analog transfer function shown in Eq. (1.6) can be ideally achieved, otherwise it can be shown the first-stage quantization noise will not be completely cancelled, instead a small part of its energy will appear in the final output and thus degrade the overall SNR of the modulator.

Figure 2. First-order Leslie-Singh Modulator

#### 1.3 Nonidealities in the Analog Integrators

For most  $\Delta\Sigma$  modulators the integrators are the most important analog circuit blocks, and are usually implemented by switched capacitor (SC) circuits. Thus understanding its nonidealities is important to the  $\Delta\Sigma$  modulator design.

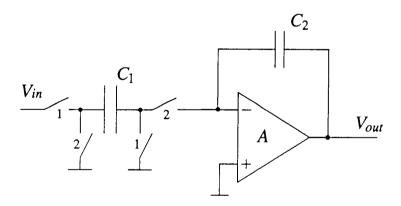

Consider the delaying SC integrator shown in Figure 3, where nominally  $C_1 = C_2$ , and  $A = \infty$ . It can be shown that if the opamp has an finite DC gain of A, and a capacitor mismatch  $\delta$  defined as  $C_1/C_2-1$ , its z domain transfer function is

$$\frac{V_{out}(z)}{V_{in}(z)} = \frac{(1-\alpha)z^{-1}}{1-(1-\beta)z^{-1}}$$

(1.10)

[4], where

$$\alpha = \frac{2/A + \delta/A - \delta}{2/A + \delta/A + 1},\tag{1.11}$$

$$\beta = \frac{1/A + \delta/A}{2/A + \delta/A + 1}.\tag{1.12}$$

Thus the integrator has both the gain error  $\alpha$  and the pole error  $\beta$ . In the usual  $\Delta\Sigma$

Figure 3. Switched Capacitor Integrator

A/D circuit implementations, the opamp DC gains are in the range of 55 - 70 dB depending on the design specifications. Thus if we define  $\mu = 1/A$ ,  $\mu$  is in the

range from 0.0003 to 0.002. On the other hand, the capacitance mismatch between two unit capacitors can be quite small, usually in the range of 0.1% to 0.4%, therefore  $\delta$  is in the range from -0.004 to 0.004. Thus to a good approximation, Eq. (1.11) and (1.12) can be simplified as follows,

$$\alpha \approx 2\mu - \delta,\tag{1.13}$$

$$\beta \approx \mu$$

. (1.14)

Notice that the above derivation assumes that nominally  $C_1/C_2 = \kappa = 1$ , it can be shown that generally if  $\kappa \neq 1$  the gain and pole errors are

$$\alpha \approx \mu (\kappa + 1) - \delta,$$

(1.15)

$$\beta \approx \mu \kappa$$

, (1.16)

where  $\delta = C_1/C_2 - \kappa$ . Notice that if  $\kappa < 1$  effectively the integrator pole error is reduced. Throughout the rest of the thesis,  $\kappa = 1$  is assumed for simplicity of discussion.

Thus the gain error  $\alpha$  is usually in the range from -0.0034 to 0.008, and the pole error  $\beta$  is usually in the range from 0.0003 to 0.002. One interesting observation is that the pole error is only caused by the opamp finite gain but the gain error is caused by both the opamp finite gain and the capacitor mismatch.

Notice that other opamp nonidealities such as DC offset, finite bandwidth, etc., may also affect the overall performance. However these nonidealities are usually less significant in terms of the SNR degradation or can be remedied by proper design techniques. For example, the opamp DC offset voltages only affect the DC characteristics of the converters, and the DC offset voltages of the converters are usually cancelled during the power-up calibration time. The ratio between the opamp unity-gain bandwidth and the sampling clock frequency determines the settling of the integrator. Incomplete settling is usually equivalent to an additional gain error apart from the one indicated in Eq. (1.11) as long as the settling is linear.

In high resolution applications, usually enough settling time is allowed to eliminate the possibility of the harmonic distortion introduced by nonlinear settling. In this thesis it is assumed that enough settling is allowed so that the gain error of the integrator is only introduced by the opamp finite gain and capacitor mismatch.

## Chapter 2. Effects of Integrator Nonidealities on SNR of Dual-Quantization Delta-Sigma Modulators

In this chapter, the effects of gain and pole error of the SC integrators on the SNR of the dual-quantization  $\Delta\Sigma$  modulators are discussed. Due to the unavoidable mismatch between the analog and digital circuit transfer functions, the cancellation of the first-stage quantization noise is incomplete. Therefore the SNRs of this category of modulators may be limited by the amount of the first-stage quantization noise leaking into the final output. And it is shown that the pole error is much more crucial in terms of the SNR degradation than the gain error. The impacts of these nonidealities on the choice of design parameters are also discussed.

#### 2.1 First-order Leslie-Singh Modulator

As discussed in Chapter 1.2, ideally first-order Leslie-Singh modulator can perfectly cancel the first-stage quantization noise  $e_1$  and the only noise source in the final output will be the second-stage quantization noise  $e_2$ . From Eq. (1.9) and Eq. (1.5), ideally the in-band noise energy is that of the second-stage quantization noise,

$$n_2^2 = \frac{\pi^2 \cdot \sigma_{e_2}^2}{3 \cdot OSR^3}. (2.1)$$

If no significant overloading occurs, we can assume  $e_2$  is a random signal uniformly distributed in the range of  $[-\Delta/2, \Delta/2]$ , where  $\Delta$  is the quantization step [1]. For an M-bit quantizer with a non-overloading input voltage range of  $[-V_{ref}, +V_{ref}]$ ,  $\Delta = 2V_{ref}/2^M$ . Thus if for simplicity we assume  $V_{ref} = 1$ , the energy of the second-stage quantization noise can be calculated as

$$\sigma_{e_2}^2 = \frac{\Delta^2}{12} = \frac{1}{3 \cdot A^M}.$$

(2.2)

From Eq. (2.1) and Eq. (2.2) we can get the root-mean-square (RMS) value of the ideal in-band noise as the following,

$$\overline{n_2} = \frac{\pi \cdot 2^{-M}}{3 \cdot OSR^{3/2}}. (2.3)$$

For the simplicity of later discussion, we express the noise energy in dB,

$$\overline{n_2}$$

(dB) =  $-6.02M - 9.03osr + 0.4$ , (2.4)

where osr is defined as  $log_2OSR$ .

One thing to notice here is that Eq. (2.3) and Eq. (2.4) are obtained based on the assumption that the input to the multibit quantizer seldom exceeds the nonoverloading conversion range of the multibit quantizer. However this is usually not true, especially in high-order dual-quantization modulators. In circuit implementations, the reference voltages of the first and the second-stage quantizer are usually made the same for hardware simplicity. It can be shown that this arrangement will cause frequent overloading of the second-stage quantizer. Notice that the overloading occurs much more frequently for the multibit quantizer than the single-bit one because the non-overloading input range for the former is only  $\pm (V_{ref} + \Delta/2)$ while the latter has a non-overloading input range as large as  $\pm 2\,V_{ref}$ . Also the consequence of the overloading in the second-stage quantizer is much more severe than in the first-stage quantizer because it will increase the energy of the secondstage quantization noise, which is directly present in the modulator output. One solution to this problem is to place a gain stage with a gain G smaller than 1, in front of the second-stage quantizer to prevent overloading. Typical values of G are 0.6 to 1.0 for first-order Leslie-Singh modulator, and 0.25 to 0.5 for the high-order dual quantization modulators depending on the second-stage quantizer resolutions. But after the quantization is finished, the quantized signal usually needs to be amplified by 1/G to maintain the original loop gain. The consequence is that the second-stage quantization noise is also amplified by the same factor. It can be

shown that other arrangements such as using two different reference voltages for the two quantizers will result in the same conclusion, that is, the overloading make the second-stage quantization noise increases by a factor of 1/G. Thus Eq. (2.4) becomes

$$\overline{n_2}$$

(dB) =  $-6.02M - 9.03osr + 0.4 - 20\log G$ . (2.5)

One very interesting thing here is that since usually G<1 is implemented by making the feedback capacitor larger than the input capacitor in the integrator, the pole error of the integrator is reduced according Eq. (1.16). And as discussed below, this will help reduce the first-stage leakage noise.

As shown in Chapter 1.2 and Figure 2, if there is any gain or pole error in the analog integrator, the cancellation of the first-stage quantization noise is incomplete and the leakage noise can be expressed in z domain as

$$E_{lk}(z) = E_1(z) \cdot (NTF_1(z) - H_2(z))$$

(2.6)

where  $NTF_1$  is the NTF of the first-order  $\Delta\Sigma$  modulator. If the transfer function of the analog integrator has gain and pole errors as shown in Eq. (1.10), it can be shown that

$$NTF_1(z) = \frac{1 - bz^{-1}}{1 + (a - b)z^{-1}},$$

(2.7)

where  $a = 1 - \alpha$ , and  $b = 1 - \beta$ . As shown in Appendix 1 and [4], the in-band leakage noise energy is approximately

$$\overline{n_{lk}}$$

(dB)  $\cong -3.01 osr - A$  (dB)  $-4.8$  (2.8)

as long as the opamp DC gain is between 40 dB to 75 dB, and the oversampling ratio is over 32. If the opamp DC gain is so high that the SNR degradation caused by the integrator pole error is so small that the SNR degradation caused by the integrator gain errors can no longer be neglected, Eq. (2.8) will not be valid and Eq. (A.1.7) must be instead.

Thus both the first-stage leakage noise and the second-stage quantization noise contribute to the noise in the final output. If we assume these two noise sources are uncorrelated, the final in-band noise energy is

$$\overline{n_o} = \sqrt{n_2^2 + n_{lk}^2}. (2.9)$$

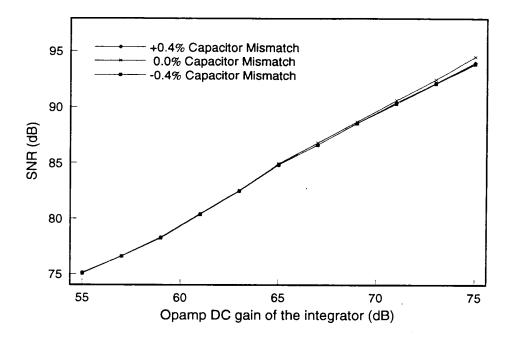

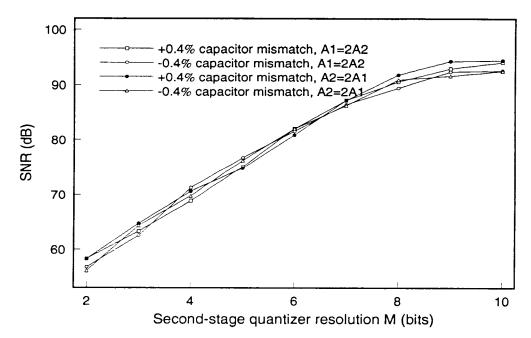

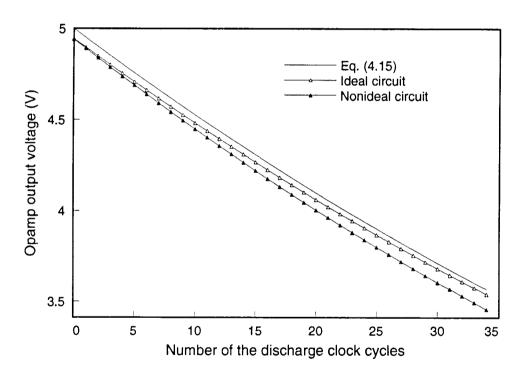

Shown in Figure 4 are the simulated SNR versus integrator opamp DC gain curves when the first-stage leakage noise dominates the overall in-band noise energy. The curves agree with Eq. (2.8) quite well and show the conclusion that the SNR degradation is approximately independent of the capacitor mismatches. Notice that the zig-zags in the curves are caused by the non-random character of the quantization noise despite of the dither signal. Shown in Figure 5 are the SNR versus second-stage quantizer resolution curves. They show that for small M the first-stage leakage noise is negligible and thus if the M increases by 1 bit, the second-stage quantization noise decreases by 1 bit or 6 dB and the overall SNR increases by 6 dB. However if M is so high that the first-stage leakage noise can not be neglected, the SNR increase becomes smaller and finally saturates. Figure 5 shows that Eq. (2.8) predicts the leakage noise energy (around -90 dB) accurately.

From Figure 5 we see that in dual-quantization modulators the choice of the second-stage quantizer resolution depends on the first-stage leakage noise energy. This is true because the increase in the second-stage quantizer resolution M, which means the increase in hardware complexity, does not always increase the overall SNR by the same amount as shown in Figure 5. In fact, it is cost-effective to increase M only when the second-stage quantization noise dominates the overall in-band noise. In other words, a cost-effective design for an uncompensated dual-quantization modulators must make the second-stage noise the dominant noise source. Thus for a given design problem, one should start with the estimation of the leakage noise energy, from Eq. (2.8) in this case, and obtain the required opamp gain for the integrator and the oversampling ratio. If the required opamp

Figure 4. SNR versus analog integrator opamp DC gain curves in a 1-bit/8-bit first-order Leslie-Singh modulator with -10 dB input and an oversampling ratio of 128.

DC gain and the OSR are practical then the second-stage quantizer resolution can be determined accordingly otherwise different modulator topology with less leakage noise must be chosen.

#### 2.2 Second-order Leslie-Singh Modulator

Shown in Figure 6 is the block diagram of a 1-bit/M-bit second-order Leslie-Singh modulator which employs a second-order modulator as its first stage and a multibit quantizer as its second stage with the digital correction transfer functions of  $H_1(z) = z^{-1}(2-z^{-1})$  and  $H_2(z) = (1-z^{-1})^2$ . It can be shown that if both integrators in the modulator are ideal, i.e., if  $I_1(z) = 1/(1-z^{-1})$  and  $I_2(z) = z^{-1}/(1-z^{-1})$  are satisfied, the cancellation of the first-stage quantization noise is perfect and the input-output relationship is

Figure 5. SNR versus second-stage quantizer resolution curve in a first-order Leslie-Singh modulator with a -10 dB input and an integrator opamp DC gain of 65 dB and an oversampling ratio of 128.

$$Y(z) = z^{-1} \cdot U(z) + (1 - z^{-1})^{2} E_{2}(z) . {(2.10)}$$

Thus from Eq. (1.5) it can be shown the in-band second-stage quantization noise energy is

$$\overline{n_2}$$

(dB) =  $-6.02M - 15.05osr + 8.13 - 20log G$ , (2.11)

where G<1 is the gain of the second-stage quantizer to prevent overloading as discussed in Chapter 2.1.

However, if the integrators have phase and gain errors, the cancellation of the first-stage quantization noise is incomplete and as shown in Appendix 2, the inband leakage noise energy is approximately

$$\overline{n_{lk}}(dB) \cong -9.03 osr - \overline{A}(dB) + 0.8$$

, (2.12)

where  $\overline{A} = 1/(1/A_1 + 1/A_2) = A_1A_2/(A_1 + A_2)$  is the combined opamp DC

gain of the two integrators, while  $A_1$  and  $A_2$  are the DC gains of the opamps in the first and second integrator respectively. Again the above equation is only valid for opamp DC gains below 75 dB and oversampling ratios over 32, otherwise Eq. (A.2.9) must be used instead. The total in-band noise energy can be easily obtained from Eq. (2.9) assuming the two noise sources are uncorrelated.

Figure 6. Second-order Leslie-Singh Modulator

Figure 7 and Figure 8 show the simulated SNR versus  $\overline{A}$  curves when the first-stage leakage noise energy dominates the overall in-band noise energy. These curves agree with Eq. (2.12) quite well by showing the fact that the first-stage leakage noise energy is nearly independent of the capacitor mismatch and individual opamp DC gains of the integrators as long as the combined DC gain of the two opamps remains the same. Figure 9 and Figure 10 show the simulated SNR versus second-stage quantizer resolution curves. Again, the increase in the second-stage quantizer resolution M is efficient only when the second-stage quantization noise energy is significantly larger than that of the first-stage leakage noise.

Comparing the first and second-order Leslie-Singh modulators it is obvious that the latter has a much smaller leakage noise. Thus the requirement on the opamp DC gain of the integrators is much lower for a given SNR and OSR specifi-

Figure 7. SNR versus combined integrator opamp DC gain curves of a 1-bit/8-bit second-order Leslie-Singh modulator with -10 dB input and an oversampling ratio of 64. (Both opamps have the same DC gain.)

Figure 8. SNR versus combined integrator opamp DC gain curves in a 1-bit/8-bit second-order Leslie-Singh modulator with -10dB input and an oversampling ratio of 64. (Individual opamps have different DC gains.)

Figure 9. SNR versus second-stage quantizer resolution curves in a second-order Leslie-Singh modulator with a -10dB input, an oversampling ratio of 64 and combined integrator DC gain of 65 dB. (Both opamps have the same DC gain.)

Figure 10. SNR versus second-stage quantizer resolution curve in a second-order Leslie-Singh modulator with a -10dB input, an oversampling ratio of 64 and a combined opamp DC gain of 65 dB. (Individual opamps have different DC gains.)

cation. However, the second-stage quantization noise energy of second-order Leslie-Singh modulator is not low enough because it is only second-order high-pass shaped and the overloading demands an amplification of 1/G in its amplitude, thus the second-stage quantizer must have a quite high resolution, about 8 bits, to achieve a SNR around 90 dB under a reasonable oversampling ratio such as 64. This means increased hardware complexity in both the second-stage quantizer and the decimation filter. To avoid this problem, higher order dual-quantization modulators are introduced.

#### 2.3 Cascade 2-1 Modulator with Multibit Second-Stage

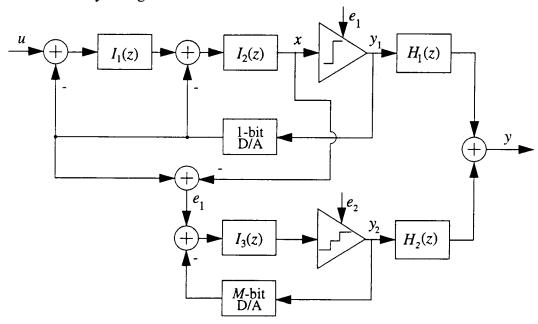

Shown in Figure 11 is the block diagram of a cascade 2-1 multibit modulator where the modulator employs a second-order single-bit modulator as its first stage and a first-order multibit modulator as its second stage, this structure is also known as Brandt-Wooley structure, named after its inventors [5].

It can be shown that if all the integrators in the modulator are ideal, namely  $I_1(z) = 1/(1-z^{-1})$ , and  $I_2(z) = I_3(z) = z^{-1}/(1-z^{-1})$ , the first-stage quantization noise is perfectly cancelled and the third-order shaped second-stage quantization noise is the only noise source appearing in the final output with an inband energy of

$$\overline{n_2}$$

(dB)  $\approx -6.02M - 21.07 osr + 16.6 - 20 log G, (2.13)$

where G here is the inter-stage scaling factor to avoid overloading in the second stage. Notice that the second-stage quantization noise is not perfectly third-order shaped because due to the phase and gain errors in the second-stage integrators the NTF of the second-stage first-order modulator noise changes from perfect high-pass function  $1-z^{-1}$  to a leaking one  $1-\beta_3 z^{-1}$ , however as shown in [1] and can be proved from Eq. (A.1.4.), as long as the opamp DC gain is at least twice as large

as the OSR, which is almost always the case, the increase in the in-band noise energy due to a leaking NTF is less than 0.3 dB. Moreover, it is followed by the digital transfer function  $H_2(z)$ , which is a perfect second-order high-pass transfer function  $(1-z^{-1})^2$ , thus the in-band energy of the second-stage quantization noise is hardly changed from the ideal situation.

Figure 11. Block diagram of a multibit cascade 2-1 modulator

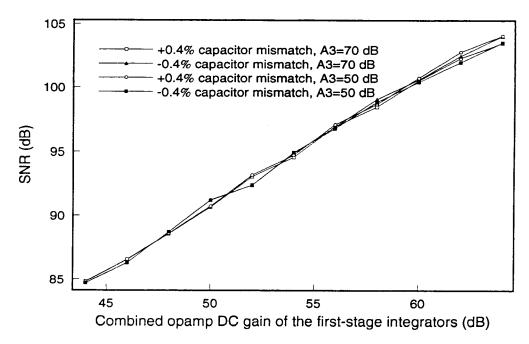

If the integrators have pole and gain errors, the cancellation of the first-stage quantization noise is incomplete and as shown in Appendix 2.2, the in-band leakage noise energy is approximately

$$\overline{n_{lk}}$$

(dB)  $\approx -9.03 osr - \overline{A}$  (dB) + 0.4, (2.14)

where  $\overline{A} = A_1 A_2 / (A_1 + A_2)$  is the combined opamp DC gain of the first-stage integrators, while  $A_1$  and  $A_2$  are the DC gains of the opamps in the first and second integrator respectively. In other words, this modulator has approximately the same in-band leakage noise energy as the second-order Leslie-Singh modulator. Therefore, its leakage noise energy is nearly independent of the pole and gain errors of the second-stage integrator and thus the opamp DC gain of the second-stage inte-

grator  $A_3$ . As before, the above equation is valid for low or medium opamp DC gains and medium to high oversampling ratios.

Figure 12. SNR versus combined opamp DC gain of the first-stage integrators curves in a 1-bit/8-bit cascade 2-1 modulator with a -10dB input and an oversampling ratio of 64. (Both opamps in the first-stage have the same DC gain.)

Figure 12 and 13 show the fact that the leakage noise energy is nearly independent of integrator gain errors, second-stage integrator pole error, and individual opamp DC gains of the first-stage integrators as long as the combined opamp DC gain remains the same. Figure 14 shows the fact that due to the increase in the order of the modulator, the in-band energy of the second-stage quantization noise is much reduced and consequently the required second-stage quantizer resolution for a given SNR is much lowered. With the same first-stage combined opamp DC gain, this modulator needs only a 4-bit second-stage quantizer at the oversampling ratio of 32 to achieve an overall SNR around 90 dB, while a second-order Leslie-Singh modulator needs to have a 8 or 9-bit second-stage quantizer. Also, the high order of noise shaping makes it suitable for high-speed medium SNR applications [5]. It can be expected that the further increase in the order of the modulator can

Figure 13. SNR versus combined opamp DC gain of the first-stage integrators curves in a 1-bit/8-bit cascade 2-1 modulator with a -10dB input and an oversampling ratio of 64. (Individual opamps in first-stage have different DC gains,  $A_3=50 \text{ dB}$ .)

Figure 14. SNR versus second-stage quantizer resolution curves in a multibit cascade 2-1 modulator with a -10dB input, an oversampling ratio of 32 or 64,  $A_3=50 \text{ dB}$ ,  $A_1=A_2=63.01 \text{ dB}$ , (first-stage combined opamp DC gain = 60 dB).

even eliminate the necessity of a multibit second-order quantizer, a single-bit one can be used instead.

#### 2.4 Cascade 2-2 Modulator

Shown in Figure 15 is the block diagram of a single-bit cascade 2-2 modulator where  $H_1(z)=z^{-1}$  and  $H_2(z)=(1-z^{-1})^2$ . It can be shown that if  $I_1(z)=I_3(z)=1/(1-z^{-1})$  and  $I_2(z)=I_4(z)=z^{-1}/(1-z^{-1})$ , the cancellation of the first-stage quantization noise is perfect and the only noise source appearing in the final output is the perfectly fourth-order shaped second-stage quantization noise  $e_2$  with an in-band energy of

$$\overline{n_2}$$

(dB) = -27.09 osr + 25.5 - 20 log G, (2.15)

where G is the inter-stage scaling factor used to avoid overloading in the second stage. As before, the nonidealities in the second-stage will change the NTF of the second-stage quantization noise but again, both theory and simulation results show that for reasonably high opamp DC gains and practical OSRs the increase in the inband energy of the second-stage quantization noise due to the second-stage integrator gain and pole errors is negligible.

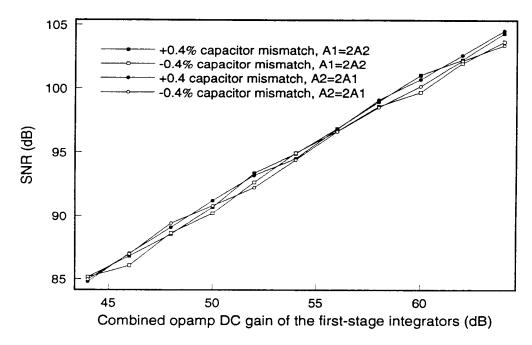

If there are pole and gain errors in the integrators, the noise cancellation of the first-stage quantization noise is incomplete and it is shown in Appendix 2.2 that the in-band leakage noise energy is approximately

$$\overline{n_{leak}} (dB) \cong -9.03 osr - \overline{A} (dB) + 0.4, \tag{2.16}$$

where  $\overline{A}$  is the combined opamp DC gain of the first-stage integrators defined the same way as before. Again the in-band leakage noise is nearly independent of the integrator gain errors and also independent of the pole errors of the second-stage integrators for low to medium opamp DC gains and medium to high oversampling ratios.

Figure 15. Block diagram of cascade 2-2 modulator

Figure 16. SNR versus combined opamp DC gain of the first-stage integrators curves in a single-bit cascade 2-2 modulator with a -10dB input and an oversampling ratio of 64. (Both opamps in the first stage have the same DC gains.)

Figure 16 and 17 support the above conclusion and show that the even with a

single-bit second-stage quantizer the second-stage quantization noise is still negligible compared with the in-band leakage noise for reasonable opamp DC gains at an oversampling ration of 64. As a matter of fact, from Eq. (2.15) even for an OSR of 32 the in-band second-stage noise energy is still around -100 dB, which is sufficient for most applications. If, however, the specification demands an even lower OSR and a relatively high SNR, it may be necessary to use a multibit second-stage quantizer.

Figure 17. SNR versus combined opamp DC gain of the first-stage integrators curves in a single-bit cascade 2-2 modulator with a -10dB input and an oversampling ratio of 64,  $A_3=A_4=50$  dB. (Individual opamps in the first stage have different DC gains.)

# Chapter 3. Digital Compensation for Analog Integrator Non-idealities in Dual-Quantization Delta-Sigma Modulators

We saw in Chapter 2 that in dual-quantization  $\Delta\Sigma$  modulators due to the mismatch between the analog and digital transfer functions caused by the nonidealities in the analog integrators, the first-stage quantization noise will not be completely cancelled and will appear in the final output, and thus degrade the SNR of the modulator. However, if the estimation of the above nonidealities is available, digital compensation can be implemented by modifying the digital transfer function so that a better matching between the analog and digital transfer functions and consequently a better cancellation of the first-stage quantization noise can be achieved, and therefore the SNR of the modulator can be increased. Generally speaking, digital compensation can, at the price of more complicated digital circuitry, get higher conversion accuracy out of a dual-quantization  $\Delta\Sigma$  modulator with poor analog integrators or, more specifically, with low integrator opamp DC gains. This technique may also increase the conversion rate of the modulator because the opamps, which usually cause the speed limitation of the whole modulator, can now be faster since its DC gain requirement is much lowered by using the digital compensation.

Apart from these merits, digital compensation may be quite costly in implementation due to the following facts: firstly, it requires estimation circuits for the integrator nonidealities, which will be discussed in Chapter 4; secondly, it increases the decimator complexity significantly; and thirdly, since the digital compensation only reduces the first-stage leakage noise, to reduce the total in-band noise energy the second-stage quantization noise must be reduced as well by increasing either the second-stage quantizer resolution or the order of the modulator. In this chapter, digital compensation and its corresponding decimation schemes are discussed for various dual-quantization  $\Delta\Sigma$  modulators.

#### 3.1 Compensation for First-Order Leslie-Singh Modulator

From Chapter 2.1 we know that to cancel perfectly the first-stage quantization noise, the first-stage leakage noise transfer function (LNTF) must be equal to zero,

$$LNTF = NTF_1 \cdot H_1 + (NTF_1 - 1) \cdot H_2 = 0, \tag{3.1}$$

where all the transfer functions in the above equations are defined in Chapter 2. It can be shown that if  $H_1$  and  $H_2$  are FIR functions, there is a unique solution, except for a common factor, to Eq. (3.1), namely  $H_1 = \alpha z^{-1}$ , and  $H_2 = 1 - (1 - \beta) z^{-1}$ .

Thus if the estimation of the integrator gain error, denoted by  $\hat{\alpha}$ , and the estimation of the integrator pole error, denoted by  $\hat{\beta}$ , are available the digital compensation can be implemented by choosing  $H_1 = \hat{\alpha}z^{-1}$ , and  $H_2 = 1 - (1 - \hat{\beta})z^{-1}$ . However, both theoretical derivation and computer simulation showed that the correction for all integrator nonidealities is unnecessary for common circuit parameters. Therefore, to save the hardware complexity in both estimation and decimation circuitry only the correction for the integrator pole errors is implemented. Thus the correction transfer function of the compensated first-order Leslie-Singh modulator is

$$H_1 = z^{-1}, H_2 = 1 - (1 - \hat{\beta})z^{-1}.$$

(3.2)

As shown in Appendix 1, the in-band leakage noise energy after compensation is then approximately

$$n_{lkc}^2 \cong \sigma_{e_1}^2 \cdot \frac{\left(\beta - \hat{\beta}\right)^2}{OSR} \cong n_{lk}^2 \cdot K^2. \tag{3.3}$$

where  $K = (1 - \hat{\beta}/\beta)$  is the relative estimation error of  $\beta$ , and  $n_{lk}^2$  is the in-band leakage noise energy of the uncompensated scheme. The value of K usually ranges from 0.05 to 0.15 if the estimation algorithm described in Chapter 4 is used. In

other words, the reduction of the in-band leakage noise energy due to the digital compensation is around 17-26 dBs. Figure 18 shows the compensated SNR versus opamp DC gain curves with different values of K.

Figure 18. SNR versus the opamp DC gain of the first-stage integrator in a compensated 1-bit/10-bit first-order Leslie-Singh modulator with different estimation accuracy of the integrator pole error (0.4% capacitor mismatch, OSR=128, -10 dB input).