This paper is a postprint of a paper submitted to and accepted for publication in Electronics Letters and is subject to Institution of Engineering and Technology Copyright. The copy of record is available at IET Digital Library

## Teraohm on-chip resistance realisation using switched capacitor topologies

## W. Li, T. Wang, J. Cao and G.C. Temes

Two large-resistance realisation schemes are proposed using switched-capacitor circuits. The equivalent resistance of the array realisation increases as the third power of the number of capacitor pairs, and that of the ladder realisation increases exponentially. The equivalent resistance for the ladder scheme also grows with the capacitance ratio. Using these schemes, large resistances can be fabricated with standard CMOS process in an affordable chip area. Simulation results show that very low pole frequency (~9 Hz in the example) can be achieved with practical element values, and with a capacitance spread of only 10 in a three-stage ladder.

Introduction: Standard CMOS technology based biosensors are widely used in biomedical applications [1]. A programmable-gain amplifier (PGA) is commonly used as the front-end stage [2]. In biomedical and communication applications, there is often the need to suppress the input offset of the signal by the PGA using a very low-frequency pole [3], which requires a large R-C time constant. However, large resistors are usually hard to fabricate, and occupy a large chip area. In this Letter, we proposed two switched-capacitor schemes, which promise to be practical ways to realise resistances in the teraohm range.

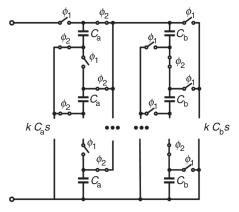

Large resistance topologies: A switched capacitor circuit containing four capacitors was proposed in [4]. The principle can be generalised as shown in Fig. 1.

Fig. 1 Switched capacitor array for large resistor realisation

$\Phi_1$  and  $\Phi_2$  are non-overlapping clock phases at a frequency  $f_{\rm s}$ . The equivalent resistance R is then

$$R = \frac{k(k^2C_a + C_b)}{f_sC_aC_b}$$

(1)

When  $C_a >> C_b$ , or  $k \gg 1$ , R increases as the third power of the number of capacitor pairs (k):

$$R \simeq \frac{k^3}{f_{\rm s}C_{\rm b}} \tag{2}$$

Hence, a very large resistance can be obtained using reasonably-sized elements. Note that the operation of the circuit is somewhat affected by parasitic capacitors loading the floating nodes.

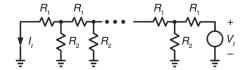

An *n*-stage resistor ladder topology is shown in Fig. 2. This scheme can generate even larger equivalent resistance when used as a feedback resistor. Denote

$$r = R_1/R_2 > 1, \quad A = \begin{bmatrix} 1 & 1 \\ r & 1+r \end{bmatrix}$$

(3)

The equivalent resistance R can be obtained from the nth power of A:

$$R = \frac{V_t}{I_t} = \begin{bmatrix} 1 & 1 \end{bmatrix} A^n \begin{bmatrix} 0 \\ 1 \end{bmatrix} R_1 \tag{4}$$

$A^n$  can readily be found using eigenvalue methods, or available software. If  $r \gg 1$ , the stages do not load their next neighbour very

much, so the approximation

$$R \simeq (1+r)^n R_1 \tag{5}$$

may be used. As (5) shows, the equivalent resistance grows nearly exponentially with the number of stages. Thus, a large equivalent resistance can be realised without fabricating many stages of resistors, or using large-resistance components.

Fig. 2 Resistor ladder

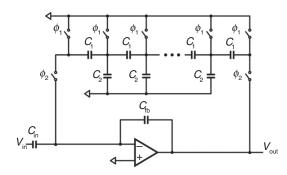

As an alternative to the resistor ladder, a switched-capacitor ladder may be used. The realisation of a SC PGA is shown in Fig. 3. A single-ended example is shown for simplicity, although the real circuit is differential. The switches are clocked at a frequency  $f_{\rm s}$ ;  $\Phi_{\rm 1}$  and  $\Phi_{\rm 2}$  are non-overlapping clocks phases.

Fig. 3 Switched capacitor ladder realisation

The transfer function has a zero at f = 0, and a low-frequency pole at

$$f_{\rm p} = \frac{1}{2\pi R C_{\rm p}} \tag{6}$$

R can be calculated using (4), with

$$R_1 = \frac{1}{f_c C_1}$$

and  $r = \frac{C_2}{C_1}$  (7)

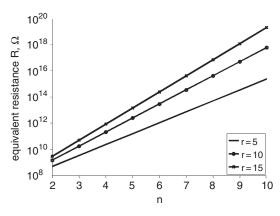

Simulation results: The equivalent resistance of the switched capacitor ladder was simulated by setting  $C_1 = 100$  fF, and  $f_{\rm s} = 1$ MHz. The equivalent resistance grows rapidly with capacitance ratio r, and the growth is even faster for a ladder with more stages. The equivalent resistance grows exponentially with the number of stages, as shown in Fig. 4, and as predicted by (5). The simulation results and the predicted values coincide with each other. An equivalent resistance of teraohms can be achieved with five stages, and a capacitance spread less than 10.

Fig. 4 Equivalent resistance against number of stages for different capacitance ratios

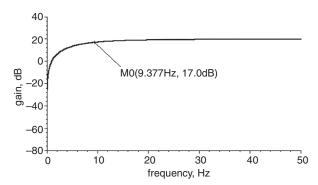

The PGA of Fig. 3 was simulated with a 10 pF input capacitor, 1 pF feedback capacitor, 1 MHz sampling clock, and a three-stage ladder structure with the capacitance ratio of 10. The frequency response of the whole circuit (implemented in a fully differential mode) is shown in Fig. 5. The low frequency highpass pole occurs at 9.4 Hz, which is consistent with the ideal value 9.3 Hz calculated from (6). The number of stages, as well as the capacitance ratio, can be simply adjusted to get different pole frequencies as needed.

Fig. 5 Frequency response of PGA with switched-capacitor resistors

Owing to the reduced feedback factor caused by the ladder, the opamp input offset ( $V_{\rm ios}$ ), will be amplified. The resulting output offset ( $V_{\rm oos}$ ) can be calculated from the opamp DC gain ( $A_{\rm dc}$ ), along with (4) and (7):

$$V_{\rm oos} = \frac{RA_{\rm dc}V_{\rm ios}}{R + R_1A_{\rm dc}} \tag{8}$$

If necessary, the opamp offset can be reduced using correlated double sampling [5].

Conclusion: Proposed is a switched-capacitor array, and a switched-capacitor ladder implementation of a large equivalent resistance.

Using these schemes, the size of the on-chip resistance is not limited by fabrication feature size, or chip area. With realistic capacitance spread, and only a few stages, teraohm resistance can be achieved. Circuit simulation results verified the feasibility of realising a low frequency pole for a PGA used in the biosensor system.

Acknowledgment: This work was supported by the NSF Center for the Design of Analog-Digital Integrated Circuits.

© The Institution of Engineering and Technology 2012 7 March 2012

doi: 10.1049/el.2012.0767

W. Li, T. Wang, J. Cao and G.C. Temes (School of Electrical Engineering and Computer Science, Kelley Engineering Center, Oregon State University, Corvallis, OR 97331-5501, USA)

E-mail: liw2@eecs.oregonstate.edu

## References

- 1 Sellami, L., and Newcomb, R.W.: 'A MOSFET bridge fluid biosensor'. ISCAS, Orlando, FL, USA, 1999, Vol. 5, pp. 140–143

- 2 Yan, L., Yoo, J., Kim, B., and Yoo, H.: 'A 0.5-μV<sub>rms</sub> 12-μW wirelessly powered patch-type healthcare sensor for wearable body sensor network', *IEEE J. Solid. State Circuits*, 2010, 45, (11), pp. 2356–2365

- Mak, P., U, S., and Martins, R.: 'On the design of a programmable-gain amplifier with built-in compact dc-offset cancellers for very low-voltage WLAN systems', *IEEE Trans. Circuits Syst. I*, 2008, 55, (2), pp. 496–509

- 4 Verma, N., Shoeb, A., Bohorquez, J., Dawson, J., Guttag, J., and Chandrakasan, A.: 'A micro-power EEG acquisition SoC with integrated feature extraction processor for a chronic seizure detection system', *IEEE. J. Solid. State Circuits*, 2010, 45, (4), pp. 804–816

- 5 Enz, C., and Temes, G.: 'Circuit techniques for reducing the effects of op-amp imperfections: autozeroing, correlated double sampling, and chopper stabilization', *Proc. IEEE*, 1996, 84, (11), pp. 1584–1614