#### AN ABSTRACT OF THE THESIS OF

<u>Lo'ai Ali Tawalbeh</u> for the degree of <u>Doctor of Philosophy</u> in <u>Electrical & Computer Engineering</u> presented on <u>October 28, 2004</u>. Title: <u>A Novel Unified Algorithm and Hardware Architecture for Integrated Modular</u> <u>Division and Multiplication in GF(p) and  $GF(2^n)$  Suitable for Public-Key</u> Cryptography.

Abstract approved: \_

#### Çetin Kaya Koç

The spread of the internet and communications techniques increases the necessity for security in applications that involves sharing or exchange of secret or private information. Public-key cryptography is widely used in establishing secure communication channels between the users on the Internet, for E-commerce transactions, and in network security protocols. Public-key cryptography relies on algorithms from computer arithmetic, number theory and algebra. The modular arithmetic operations, modular division, and modular multiplication over finite fields  $(GF(p) \text{ and } GF(2^n))$  are extensively used in many public-key cryptosystems, such as RSA, ElGamal cryptosystem, Diffie-Hellman key exchange algorithm, elliptic curve cryptography (ECC), and the Digital Signature Standard including the Elliptic Curve Digital Signature Algorithm. In our research, we have mainly concentrated on hardware realization of the ECC since it seems to provide similar amount of security using smaller key size.

The modular multiplication operation with a large modulus is very important in many public-key cryptosystems. One of the most efficient ways to compute modular multiplication is the Montgomery algorithm. Many efficient Montgomery multiplier designs were proposed up to now. On the other hand, computing modular division (inverse) is a time-consuming process and cannot be avoided completely. It was claimed that a gain in performance can be obtained when implementing the division (inverse) in hardware. In this work, we propose, with a mathematical proof, an efficient unified division algorithm to compute the modular division operation in GF(p) and  $GF(2^n)$ . The algorithm uses a counter to keep track of the difference between two field elements and this way eliminates the need for comparisons which are usually expensive and timeconsuming. An hardware architecture implementing the algorithm is also proposed.

The unified division algorithm is integrated with a unified Montgomery multiplication algorithm to obtain a novel Unified Division/Multiplication Algorithm (UDMA). The UDMA computes division (inverse) and multiplication in a very efficient way in both GF(p) and  $GF(2^n)$  fields. Also, we propose a unified hardware architecture that efficiently supports all operations in the UDMA and uses carry-save unified adders for reduced critical path delay, making the proposed architecture faster than other previously proposed designs.

Experimental results obtained by synthesizing the hardware design for AMI  $0.5\mu m$ CMOS technology and FPGA VertixII chip (xc2vp50 - 7ff148 technology) are shown and compared with other proposed dividers and multipliers. ©Copyright by Lo'ai Ali Tawalbeh October 28, 2004 All Rights Reserved A Novel Unified Algorithm and Hardware Architecture for Integrated Modular Division and Multiplication in GF(p)and  $GF(2^n)$  Suitable for Public-Key Cryptography

by

Lo'ai Ali Tawalbeh

#### A THESIS

#### submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Presented October 28, 2004 Commencement June 2005 Doctor of Philosophy thesis of Lo'ai Ali Tawalbeh presented on October 28, 2004

APPROVED:

Major Professor, representing Electrical & Computer Engineering

Associate Director of the School of Electrical Engineering and Computer Science

Dean of the Graduate School

I understand that my thesis will become part of the permanent collection of Oregon State University libraries. My signature below authorizes release of my thesis to any reader upon request.

Lo'ai Ali Tawalbeh, Author

#### ACKNOWLEDGMENTS

First of all, I am grateful to the GOD, most mighty, most merciful, who created me and gave me the ability to think and search for the truth.

I would like to thank my major advisor, prof. Çetin Kaya Koç, for his help, support, encouragement, and valuable directions towards accomplishing this work. Also, I want to thank Dr. Alexandre F. Tenca who was my advisor during my Master study (September 2001- October 2002), and part of my PhD study. Dr. Tenca's discussions, directions, reviews and comments helped me much in conducting this research and writing conference and journal publications which formed as the bases of this thesis. I also thank the other members of my graduate committee for their valuable input.

I am thankful to my research colleagues in the Information Security Laboratory of Oregon State University. In particular, I acknowledge Mohammad Sinky, Song Park, Ajay Shantilal, Minho Kim, Colin Van Dyke, Onur Aciiçmez and Gökay Saldamli, for providing valuable feedback during different research phases.

The financial support for my PhD education is from a scholarship provided by Jordan University of Science and Technology (JUST)- Jordan, and NSF CAREER grant CCR-0093434- "Computer Arithmetic Algorithms and Scalable Hardware Designs for Cryptographic Applications".

Finally, this work will not have been possible without the love and moral support of my father (Ali Tawalbeh), my patient, great and wonderful mother, my brothers (Qosai, Ahmad and Mohammad), my sisters, and my aunts (Um Anas and Um Ibrahim). I am deeply thankful to all of them for their support and warm feelings during my study years overseas.

> Lo'ai Ali Tawalbeh Corvallis, Oregon, USA October , 2004

### TABLE OF CONTENTS

|    |      | <u>F</u>                                                                                                                          | Page           |

|----|------|-----------------------------------------------------------------------------------------------------------------------------------|----------------|

| 1. | INTF | RODUCTION                                                                                                                         | 1              |

|    | 1.1. | Motivation                                                                                                                        | 2              |

|    | 1.2. | Literature Review                                                                                                                 | 3              |

|    | 1.3. | Montgomery Modular Multiplication                                                                                                 | 6              |

|    | 1.4. | Thesis Organization                                                                                                               | 8              |

| 2. |      | UNIFIED MODULAR DIVISION ALGORITHM AND HARDWARE HITECTURE IN $GF(P)$ AND $GF(2^N)$ .                                              | 10             |

|    | 2.1. | Mathematical Concepts and Notation                                                                                                | 10             |

|    | 2.2. | Unified Modular Division Algorithm (UMD)                                                                                          | 11             |

|    |      | 2.2.1. Numerical Example2.2.2. Mathematical Proof                                                                                 | 14<br>14       |

|    | 2.3. | Hardware Architecture of The Unified Modular Divider                                                                              | 16             |

|    |      | <ul><li>2.3.1. Adders Scheduling for Efficiency</li><li>2.3.2. Datapath</li><li>2.3.3. Improving The System Performance</li></ul> | 17<br>18<br>21 |

| 3. |      | EL UNIFIED MODULAR DIVISION AND MULTIPLICATION ALGO-<br>IM (UDMA) IN $GF(P)$ AND $GF(2^N)$                                        | 23             |

|    | 3.1. | Unified Algorithm for Modular Division and Montgomery Modular Mul-<br>tiplication                                                 | 23             |

|    | 3.2. | Multiplication Mode                                                                                                               | 25             |

|    |      | 3.2.1. Numerical Example:Computing Montgomery Multiplication Us-<br>ing The UDMA                                                  | 26             |

|    | 3.3. | Division Mode                                                                                                                     | 27             |

|    |      | 3.3.1. Numerical Example:Computing Modular Division Using The UDMA                                                                | 27             |

## TABLE OF CONTENTS (Continued)

|    |      |                                                                 | 1 age |

|----|------|-----------------------------------------------------------------|-------|

|    | 3.4. | Mathematical Proof During Computing Montgomery Multiplication   | 29    |

|    |      | 3.4.1. Product modulo p         3.4.2. Product is Reduced       |       |

| 4. |      | LABLE AND UNIFIED MODULAR DIVIDER/MULTIPLIER HARD-<br>RE DESIGN |       |

|    | 4.1. | Overall Hardware System Architecture                            | 33    |

|    |      | 4.1.1. Register File4.1.2. UMDM Datapath4.1.3. Control Block    | 34    |

|    | 4.2. | Scalable Divider/Multiplier Architecture                        | 42    |

|    |      | 4.2.1. Implementation Details                                   | 43    |

| 5. | EXP  | ERIMENTAL RESULTS AND COMPARISONS                               | 45    |

|    | 5.1. | The Number of Iterations                                        | 45    |

|    | 5.2. | Synthesis Results                                               | 48    |

|    | 5.3. | FPGA Synthesis Results for The Scalable Design                  | 51    |

|    |      | 5.3.1. Area Results5.3.2. Critical Path Delay Results           |       |

| 6. | CON  | CLUSIONS AND FUTURE WORK                                        | 54    |

|    | 6.1. | Conclusion                                                      | 54    |

|    | 6.2. | Future work                                                     | 55    |

| BI | BLIO | GRAPHY                                                          | 57    |

# Page

## TABLE OF CONTENTS (Continued)

|    |      | P                                                                     | age |

|----|------|-----------------------------------------------------------------------|-----|

| AF | PENI | DICES                                                                 | 61  |

| Α  | THE  | GREATEST COMMON DIVISOR.                                              | 63  |

| В  | REL  | ATED ALGORITHMS                                                       | 66  |

|    | B1.  | The Euclidean Algorithm                                               | 66  |

|    | B2.  | The Binary GCD Algorithm                                              | 68  |

|    | B3.  | The Plus-Minus Algorithm                                              | 69  |

|    | B4.  | The Extended Binary GCD Algorithm for Modular Division                | 70  |

| С  |      | ERICAL EXAMPLE FOR COMPUTING MODULAR INVERSE US-<br>UDMA IN $GF(P)$ . | 71  |

### LIST OF FIGURES

| Fig | gure                                                                                                                                                                    | Page |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1.1 | Modular multiplication using MM                                                                                                                                         | . 7  |

| 1.2 | Modified version of the unified Montgomery multiplication algorithm presented in [6].                                                                                   | . 9  |

| 2.1 | Unified Modular Division Algorithm (UMD)                                                                                                                                | . 13 |

| 2.2 | Top level organization of the modular divider which implements the UMD Algorithm.                                                                                       | . 16 |

| 2.3 | Scheduling of adders in the modular divider that implements the UMD algorithm                                                                                           | . 18 |

| 2.4 | The Unified Datapath of the Modular Divider                                                                                                                             | . 19 |

| 2.5 | The two possible configurations of the Swapping Network.                                                                                                                | . 21 |

| 2.6 | The delay paths of the Modular Divider.                                                                                                                                 | . 22 |

| 3.1 | Unified modular Division/Multiplication Algorithm (UDMA) for $GF(p)$<br>and $GF(2^n)$ .                                                                                 | . 24 |

| 3.2 | Computing Montgomery multiplication in $GF(p)$ and $GF(2^n)$ using the UDMA.                                                                                            | . 28 |

| 3.3 | Computing modular division in $GF(p)$ and $GF(2^n)$ using the UDMA                                                                                                      | . 32 |

| 4.1 | Top Level Hardware Architecture of the Unified Modular Divider/Multipl<br>(UMDM).                                                                                       |      |

| 4.2 | Unified datapath of the Modular Divider/Multiplier (UMDM datap-<br>ath).                                                                                                | . 35 |

| 4.3 | Unified Carry-Save Adder with Complement (UCSA1) for 1-bit and<br><i>n</i> -bit precision.                                                                              | . 36 |

| 4.4 | Unified Carry-Save Adder with integrated AND gate for 1-bit and n-bit precision                                                                                         | . 37 |

| 4.5 | Data dependency between the words of the scalable design                                                                                                                | 43   |

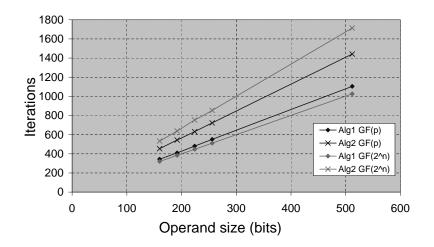

| 5.1 | The number of iterations as a function of operand size required by $Alg1$ (UDMA) and $Alg2$ (presented in [10]) to compute the modular inverse in $GF(p)$ and $GF(2^n)$ | . 46 |

# LIST OF FIGURES (Continued)

| Fig | ure                                                                                                                                                                             | Page |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

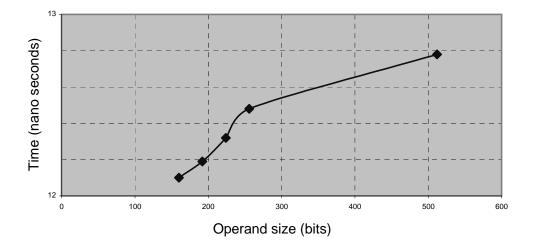

| 5.2 | The critical path delay of the UMDM in <i>nano</i> -seconds (operand size from 160-512 bits).                                                                                   | . 49 |

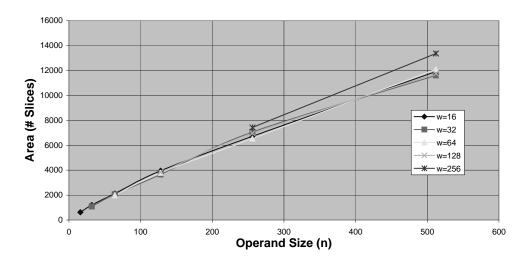

| 5.3 | The Area (FPGA Technology) of the scalable UMDM in number of slices for combinations of operand size $(n)$ form 16-512 bits, and data-<br>path word size $(w)$ from 16-256 bits | . 52 |

## ge

### LIST OF TABLES

| Tal | ble                                                                                                                                                                                | Page |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1.1 | Area and time complexity of some inversion designs                                                                                                                                 | . 4  |

| 2.1 | A modular division by the UMD algorithm in $GF(p)$                                                                                                                                 | . 15 |

| 3.1 | The operations performed by the UDMA during Montgomery multipli-<br>cation                                                                                                         | . 26 |

| 3.2 | Montgomery multiplication example by the UDMA in $GF(p)$                                                                                                                           | . 27 |

| 3.3 | The operations performed by the UDMA during modular division                                                                                                                       | . 28 |

| 3.4 | A modular division by the UDMA in $GF(2^4)$                                                                                                                                        | . 29 |

| 4.1 | Loading phase for multiplication and division                                                                                                                                      | . 39 |

| 4.2 | The operation of the UMDM during Montgomery multiplication                                                                                                                         | . 40 |

| 4.3 | The UMDM operation during computing division when $c_0 = 0$                                                                                                                        | . 41 |

| 4.4 | The UMDM operation during division when $c_0 = 1$                                                                                                                                  | . 42 |

| 5.1 | Average number of additions for $Alg1$ and $Alg2$ to compute the modular inverse in $GF(p)$ and $GF(2^n)$ .                                                                        | . 47 |

| 5.2 | The Area of the UMDM Design in gates for different operand sizes                                                                                                                   | . 50 |

| 5.3 | The critical path delay (clock period) of the scalable UMDM in <i>nano</i> -<br>seconds for combinations of operand size (16-512 bits), and datapath<br>word size from 16-256 bits | . 53 |

### LIST OF APPENDIX TABLES

| Tab | ble                                                            | Page |

|-----|----------------------------------------------------------------|------|

| C.1 | A modular inverse computation by the UDMA algorithm in $GF(p)$ | . 72 |

To my mother and my father, with love ..

# A NOVEL UNIFIED ALGORITHM AND HARDWARE ARCHITECTURE FOR INTEGRATED MODULAR DIVISION AND MULTIPLICATION IN GF(P)AND $GF(2^N)$ SUITABLE FOR PUBLIC-KEY CRYPTOGRAPHY

#### 1. INTRODUCTION.

The spread of the internet and communications techniques increases the necessity for security in applications that involves sharing or exchange of secret or private information. Public-key cryptography is widely used in establishing and verifying communications between the users on the web, E-commerce transactions, and network security protocols.

Among the modular arithmetic operations, modular division (notice that division includes computing the inverse) and multiplication over finite fields  $(GF(p) \text{ and } GF(2^n))$ are extensively used in many cryptographic applications, such as ElGamal cryptosystem [1], Diffie-Hellman [2] key exchange algorithm, RSA [3], elliptic curve cryptography, and the Digital Signature Standard including the Elliptic Curve Digital Signature Algorithm[4].

In this work, we: first, propose an efficient unified modular division algorithm to compute modular division in GF(p) and  $GF(2^n)$  and its hardware architecture. We also provide a mathematical proof for the algorithm. The algorithm uses a counter to keep track of the difference between two field elements and this way eliminates need for comparisons which are usually expensive and time-consuming. The hardware architecture that implements the algorithm is also proposed.

Second, knowing that the Montgomery multiplication algorithm [5] is one of the most efficient ways to compute modular multiplication, we modify the unified Montgomery multiplication algorithm proposed by other members of our research group in [6] to have a control flow similar to the proposed division algorithm.

After that, we integrate the proposed unified division algorithm in this work with the unified Montgomery multiplication algorithm in [6] to get a novel Unified modular Division/Multiplication Algorithm (UDMA). The UDMA computes division (inverse) and multiplication in a very efficient way in both GF(p) and  $GF(2^n)$  fields. Also, we propose the hardware architecture of the algorithm which efficiently supports all the operations in the UDMA, and uses carry-save unified adders for reduced critical path delay, making the proposed architecture faster than other previously proposed designs. The added scalability feature of the proposed divider/multiplier allows a fixedarea datapath to handle operands of any size. Also, the word size of the datapath can be adjusted to meet the area and performance requirements.

Experimental results obtained by synthesizing the hardware design for AMI  $0.5\mu m$ CMOS technology and FPGA *VertixII* chip (xc2vp50 - 7ff148 technology) are shown and compared with other proposed dividers and multipliers.

Next section of this Chapter presents the motivation behind conducting this research. Section 2 shows previous work related to computing modular division (inverse) and Montgomery multiplication in hardware. Section 3 describes Montgomery multiplication, and presents a modified version of the unified Montgomery multiplication algorithm proposed in [6]. The organization of this thesis is presented in Section 4.

### 1.1. Motivation

Modular arithmetic operations such as division and multiplication over finite fields  $(GF(p) \text{ and } GF(2^n))$ , are widely used in several cryptographic applications. The modular multiplication operation with a large modulus is very important in many public-key cryptosystems such as the RSA algorithm [3].

On the other hand, modular division and modular inverse are time consuming operations and they cannot be avoided completely in practical applications. For instance, they are used in the ElGamal [1] public-key cryptosystem and the Diffie-Hellman key exchange method [2]. Modular inversion is also considered as an essential operation in the Elliptic Curve Cryptography (ECC) [4, 7, 8]. This research is targeted mainly toward the ECC utilization because of its promise to replace several older cryptographic systems [9, 10]. Researchers have claimed that a gain in performance can be obtained when modular division and inversion are implemented in hardware [9, 11]. Also, for cryptographic applications, it is more secure to implement all the computations in hardware than performing some computations in software with others processed in hardware. This is because software implementations are supported by operating systems, which can be interrupted and trespassed by intruders, compromising the application security. On the other hand, such a security threat is not so easily attained in hardware implementations [9].

In general, there is an increasing demand for dedicated hardware to accelerate the huge amount of computations required by public-key cryptographic algorithms. An algorithm and hardware implementation that is able to compute modular division and multiplication in both GF(p) and  $GF(2^n)$  is definitely advantageous and has great importance to systems that need to quickly switch between these fields, such as network servers. The scalability feature of a hardware module is very useful and allows the users to use a fixed-area module to handle operands of any size. The word size of the module can be adjusted to meet the best area/performance requirements.

### 1.2. Literature Review

The Extended Euclidean Algorithm (EEA) is an efficient way to compute modular division [12, 13]. There are several proposed design in the literature that computes modular division (inverse) [9, 11, 14, 15, 16, 17, 18, 19, 20, 21] based on the EEA or one of its modifications [22]. Most of the proposed designs compute the inverse in the binary extension fields –  $GF(2^n)$  [14, 17, 18, 19, 20, 21, 23]. The designs proposed in

| The Design                           | Area Complexity | Time Complexity |

|--------------------------------------|-----------------|-----------------|

|                                      |                 |                 |

| Guo and Wang [17]                    | O(nlogn)        | O(n)            |

| Choudhury and Barua [18]             | O(n)            | $O(n^2)$        |

| Kovac, Ranganathan and Varanasi [25] | $O(n^3)$        | O(1)            |

| Guo and Wang [24]                    | O(n)            | O(n)            |

| Daneshbeh and Hasan [14]             | O(n)            | O(n)            |

TABLE 1.1: Area and time complexity of some inversion designs

[20, 23] suffer from signal broadcasting problem which should be avoided in high-speed VLSI circuits [12].

Other designs are based on the concept of systolic array structures [14, 17, 18, 24, 25]. A systolic array is an arrangement of interconnected logic cells in array where data flow synchronously between the adjacent cells. Systolic arrays are simple and has regular communications and control structures which make it suitable for VLSI implementations. But, on the other hand, a huge amount of hardware area is needed in order to gain computation speed [26]. Table 1.1 shows the area and time complexities of some inversion designs.

A VLSI algorithm for modular division based on the Binary GCD algorithm was proposed in [27]. The algorithm is based on the plus-minus algorithm presented in [28] which is a modification of the binary method for calculating the Greatest Common Divisor (GCD). The redundant binary representation is used to avoid carry propagation. The same author with cooperation with another researcher proposed in [29] a VLSI algorithm to compute division and multiplication in GF(p) only, which uses the same algorithm proposed in [27] for division. The algorithm was implemented in a linear array structure that uses signed digit representation and performs *n*-bit modular multiplication in  $\lfloor \frac{2(2n+3)}{3} \rfloor + 3$  clock cycles and modular division in 2n + 5 clock cycles. The public-key processor presented in [16] implements operations required for Elliptic Curve Cryptography (ECC) including modular inverse in  $GF(2^n)$ . Its has a reconfigurable datapath. The processor hardware is more energy efficient and faster than software implementations. But, on the other hand, it has a very large area.

Another work in [15] presents a simple dual-field arithmetic unit, however, an unified algorithm for modular inverse/division was not shown. The unit performs one addition in each clock cycle, and the redundant adder in the architecture is used to convert from the carry-save form to the non-redundant representation, significantly increasing the number of clock cycles.

The Montgomery multiplication algorithm proposed in [5] is considered a very efficient way to compute modular multiplication. An implementation of Montgomery multiplication should consider the tradeoff between chip area and computational speed [30, 31].

A flexible multiplier can be integrated into a system as an autonomous co-processor attached to the system bus [6, 32]. Also, the multiplier can be integrated as a functional unit to the main CPU. With the idea of implementing more cryptographic operations in hardware, this approach is becoming increasingly attractive [33, 34].

A single chip, 1024-bit RSA implementation is shown in [35]. The multiplication part is implemented as an array multiplier. This approach for multiplication requires multiple clock cycles to complete. Another approach to perform modular multiplication, is to use a core with a small bit size and reuse it with bit portions of the operands [30]. It is shown in [36] that limiting the size of the computing unit has certain advantages.

Implementing the multiplier using reconfigurable hardware provides the means of solving problems for both high-precision and variable-precision computation [30]. The main candidates for flexible hardware are FPGAs [32, 37]. Thus, in this work, we are implementing the proposed hardware architecture in FPGAs in addition to the ASIC implementation.

A very good representative of Montgomery multiplier implementation is the unified multiplier architecture for both finite fields, GF(p) and  $GF(2^m)$ , is presented in [6]. It shows that a Montgomery multiplication module can operate in both fields without significant increases in the design area compared to a multiplier that works on GF(p) only.

### **1.3.** Montgomery Modular Multiplication

In this Section, we explain briefly the Montgomery multiplication algorithm. We rewrote the algorithm and used the same notation as in the unified modular division algorithm proposed in this work to emphasize the similitude between the two algorithms. The similarities between the two algorithms are used to get a novel Unified modular Division and Multiplication Algorithm (UDMA) which is described in Chapter 3.

The Montgomery multiplication algorithm generates the product of two *n*-bit integers Y (multiplier) and X (multiplicand) in modulo p according to the following expression:

$$MM(Y,X) = YXr^{-1} \mod p$$

where  $r = 2^n$ . p is chosen such that the greatest common divisor of r and p is one  $(\gcd(r,p) = 1)$ , which indicates that r and p should be relatively prime. This condition is easily achieved by choosing p as an odd integer, since  $r = 2^n$  is an even number. We usually have  $2^{n-1} . The Montgomery image of an integer can be obtained by multiplying it by the constant <math>r$  and taking it modulo p:  $\bar{a} = ar \mod M$ .

The Montgomery multiplication over the images  $\bar{a}$  and  $\bar{b}$  results in:

$$\bar{c} = cr \mod M = MM(\bar{a}, b) = abr \mod M$$

which corresponds to the image of  $c = ab \mod M$ , the modular product of a and b.

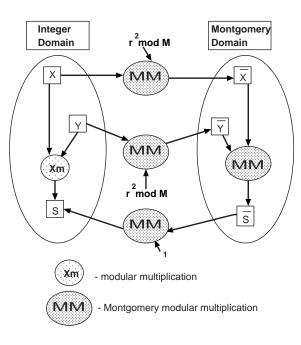

Figure 1.1 shows the transformation between the integers and their images performed using MM. This process can be explained as follows:

to transform an integer a to its image \(\alpha\), we do: \(\alpha\) = MM(a, r^2) = ar^2r^{-1} modM = ar mod M.

FIGURE 1.1: Modular multiplication using MM.

• to transform from an image  $\bar{a}$  to the integer a, we compute:  $a = MM(\bar{a}, 1) = arr^{-1} \mod M = a \mod M$ .

Observe that the constant  $r^2 \mod M$  is pre-computed and used in the process as shown in Figure 1.1.

The radix-2 unified Montgomery multiplication algorithm is shown in Figure 1.2 [6].

The Montgomery multiplication algorithm performs n iterations. In each iteration one bit of the multiplier is tested (we are considering C = Y at the beginning). If  $c_0 = 1$ , the C variable is shifted one bit to the right, and one multiple of the multiplicand X is added to the partial product U. If  $c_0 = 0$ , only a shift right is done on C and the next bit is tested. Note that U is always bounded by 2p through all iterations. Therefore, the last correction step (modular reduction) assures that the output is correctly presented in modulo p. In order to use the result of one multiplication as the input to another one without modular reduction, we need to use two extra bits of precision (n + 2 bits)[38, 33].

### 1.4. Thesis Organization

The rest of this thesis is organized as follows: Chapter 2 presents A new unified division algorithm and it's hardware architecture that computes modular division (inverse) in GF(p) and  $GF(2^n)$ . A novel Unified Division and Multiplication Algorithm (UDMA) which is able to compute both modular division (inverse) and Montgomery multiplication in GF(p) and  $GF(2^n)$  fields, is presented in Chapter 3. We propose a scalable and unified modular divider/multiplier hardware architecture for the UDMA in Chapter 4. The architecture is implemented in ASIC and Field Programmable Gate Arrays (FPGAs). The experimental results are presented and compared with previous designs in Chapter 5. The conclusions and future work are shown in Chapter 6. [Montgomery Modular Multiplication in GF(p) and  $GF(2^n)$  fields]

**Inputs**:  $0 \le X, Y < p, 2^{n-1} < p < 2^n, Field, n$

**Output**:  $Z = XY2^{-n} \mod p$  when Field = GF(p),  $Z(x) = X(x)Y(x)2^{-n} \mod p(x)$ when  $Field = GF(2^n)$

#### Algorithm:

C = Y, U = 0, W = X

FOR i = 1 To nIF  $c_0 = 0$  THEN C := C >> 1ELSE /\*  $c_0 = 1$  \*/ C := C >> 1, U := (U + W)END IF;  $U := (U + u_0 * p) >> 1$ END FOR; IF  $U \ge p$  THEN Z := U - pELSE Z := UEND IF;

FIGURE 1.2: Modified version of the unified Montgomery multiplication algorithm presented in [6].

# 2. NEW UNIFIED MODULAR DIVISION ALGORITHM AND HARDWARE ARCHITECTURE IN GF(P) AND $GF(2^N)$ .

This Chapter presents an algorithm to compute modular division in both GF(p)and  $GF(2^n)$  fields (also called *unified*). Since computing division includes computing the inverse, we will use the term division because it is more general. In the following Section, we review some mathematical concepts and introduce the notation to be used in this Chapter. In Section 2.2, we present the Unified Modular Division (UMD) algorithm with its mathematical proof. The hardware architecture that implements the UMD algorithm is described in Section 2.3.

#### 2.1. Mathematical Concepts and Notation

The binary extension field element,  $Y(x) \in GF(2^n)$ , is a non-zero polynomial of degree less than n, when the polynomial basis is used to represent the field elements (which is the case in this thesis). Each element has coefficients in GF(2), which are represented by the values  $\{0, 1\}$ . On the other hand, the elements in the prime field GF(p) are integers in the range  $\{0, ..., p-1\}$  where p is a n-bit prime modulus in the range  $2^{n-1} . Bit vectors are used to represent the elements in both fields as$ follows:

$$GF(2^{n}): Y(x) = \sum_{i=0}^{n-1} y_{i} * x^{i}$$

$$GF(p): Y = \sum_{i=0}^{n-1} y_{i} * 2^{i}$$

where  $y_i \in \{0, 1\}$  in both cases. The polynomial Y(x) is denoted as Y in the algorithm description for simplicity.

The addition operation of the elements is different in each field. Addition of two polynomials in  $GF(2^n)$  is done by a bitwise logic exclusive OR operation ( $a \operatorname{xor} b = a \oplus b$  = a'b + ab') between the two bit vectors being added. In other words the additions in  $GF(2^n)$  are done modulo 2 [15], as shown in the following equation:

$$Y(x) + W(x) = \sum_{i=0}^{n-1} y_i * x^i + \sum_{i=0}^{n-1} w_i * x^i = \sum_{i=0}^{n-1} (y_i \ xor \ w_i) x^i$$

Subtraction and addition in  $GF(2^n)$  are equivalent. Intermediate results of operations in  $GF(2^n)$  that are represented by polynomials of degree greater or equal to n are reduced using a field polynomial p(x) of degree n (irreducible polynomial) [39].

Moreover, the addition of two elements Y and W in GF(p) is done as a conventional integer addition. The propagation of carries in this case depends on the use of redundant or non-redundant representation of elements. Carry-Save (CS) representation is used in this work. Modular reduction is required when the sum exceeds the value of p to keep the result in the set  $\{0, ..., p-1\}$ .

#### 2.2. Unified Modular Division Algorithm (UMD)

The Unified Modular Division (UMD) algorithm is shown in Figure 2.1. The algorithm is based on the Extended Binary GCD algorithm [27]. Most of the modular division (inverse) algorithms [11, 16, 15, 14, 21, 17] have integer and polynomial degree comparisons as part of their control flow. Differently from them, the UMD algorithm uses a counter variable to keep track of the difference between field elements, and this way, eliminates the need for comparisons and complex tests which are usually expensive and time consuming. Using the counter results in a less complex iterations [40], and it can be implemented using fast up/down counters as the ones described in [41].

The UMD algorithm computes the modular division in  $GF(2^n)$  when  $Field = GF(2^n)$   $(Z(x) = \frac{X(x)}{Y(x)} \mod p(x))$ , and in GF(p) when Field = GF(p). In both cases,  $Y \neq 0$ . If X is set to one, the UMD algorithm computes the modular inverse. We must say that the operations on the control variable  $\delta$  are always integer operations regardless of what is the specified field. On the other hand, specifying a field forces all the additions/subtractions to be done in this field. Swap of values between two variables

is indicated by the symbol  $\Leftrightarrow$ . The notation for the least-significant bits of C and U is  $c_0$  and  $u_0$ , respectively. The symbol >> indicates right shift by one bit (divide by 2 in GF(p) or by x in  $GF(2^n)$ ). Notice that inputs to the UMD algorithm (X, Y) are bit vectors that represent elements in GF(p) and  $GF(2^n)$ .

The algorithm is based on the following facts to compute the division in GF(p)[12, 27, 40]: If C is even and D is odd, then gcd(C, D) = gcd(C/2, D). If C and D are both odd, then 4 divides either C + D or C - D. If the first is true, then gcd(C, D) =gcd((C + D)/2, D) = gcd((C + D)/4, D), and  $|(C + D)/4| \leq max(|C/2|, |D/2|)$ . If 4 divides (C - D) then gcd(C, D) = gcd((C - D)/2, D) = gcd((C - D)/4, D), and  $|(C - D)/4| \leq max(|C/2|, |D/2|)$ . In the algorithm, these operations are performed by C := (C + kD)/2 in one iteration and C := C/2 in the following iteration. In any case, since the result of these operations is stored back into C, when C > D, the size of the bit vector C is reduced by 1 bit. If C < D, the size of the bit vector may not be reduced, and the counter is used to limit the number of iterations when the algorithm stays in this situation, forcing the swap of variables to the condition C > D which is required for convergence.

In  $GF(2^n)$  one can show that gcd(C, D) = gcd((C+D)/x, D) (addition is the same as subtraction in this field) but the divisibility by 4 can not be enforced. Therefore, when Field = 0, the test  $(C + D) \mod 4 \neq 0$  is not applicable. When deg(C) > deg(D), we can see that  $deg((C + D)/x) \leq deg(C/x) = deg(C) - 1$ , and therefore, C will have its degree reduced in each iteration.

The combination of the two expressions: U = (U + kW) and  $U := (U + u_0 p) >> 1$ , where  $u_0$  is the least-significant bit of U, implements the operation U := (U + kW) >>1 mod p. This way the modular reduction is done by a simple conditional addition of the modulus in GF(p) or irreducible polynomial in  $GF(2^n)$ .

The UMD algorithm can be used to compute the inverse in Montgomery domain by the use of pre-computed constants. Considering the Montgomery images r (corresponds to 1) and Y as inputs, where  $r = 2^n$ , we get  $Z = \frac{r}{Y} \pmod{p} = Y^{-1}r \pmod{p}$  which is **Function**: Modular Division in GF(p) and  $GF(2^n)$  fields

**Inputs**:  $0 \le X < p$ , 0 < Y < p,  $2^{n-1} , Field$ **Output** $: <math>Z = \frac{X}{Y} \mod p$  when Field = GF(p),  $Z(x) = \frac{X(x)}{Y(x)} \mod p(x)$  when  $Field = GF(2^n)$

#### Algorithm:

```

C = Y, U = X, D = p, W = 0, \delta = 0

WHILE C \neq 0

IF c_0 = 0 THEN

C := C >> 1

\delta := \delta - 1 /* Integer Operation */

ELSE

IF \delta < 0 THEN C \Leftrightarrow D, U \Leftrightarrow W, \delta := -\delta

END IF;

k := 1

IF((C + D) \mod 4 \neq 0 \text{ AND } Field = GF(p)) THEN k := -1

ELSE \delta := \delta - 1

END IF;

C := (C + k * D) >> 1, U := (U + k * W);

END IF;

U := (U + u_0 * p) >> 1

END WHILE;

IF D = 1 THEN Z := W

ELSE Z := p - W

END IF;

```

FIGURE 2.1: Unified Modular Division Algorithm (UMD)

the inverse in the Montgomery domain. But, if we use r and Yr as inputs, the algorithm computes the inverse in the integer domain  $(Z = Y^{-1} \pmod{p})$ .

#### 2.2.1. Numerical Example

Table 2.1 shows a numerical example of modular division using the UMD algorithm. The algorithm computes  $\frac{213}{108} \mod 251$  in GF(p). The Table shows the values of the variables: delta, C, D, U, and W. The first column shows the operation performed by the division algorithm. For instance,  $C \gg 1$  indicates that the *THEN* portion was executed (C is even), and so, C was shifted and  $\delta$  was decremented. On the other hand, the expression  $C := (C \pm D) \gg 1$  indicates that the *ELSE* portion was executed (C is odd), and so,  $U := (U \pm W)$  was also performed. The operation *swap* means that  $C \Leftrightarrow D$  and  $U \Leftrightarrow W$ , and the sign of  $\delta$  was flipped ( $\delta = -\delta$ ). Notice that the modular reduction step ( $U := (U + u_0 * p) \gg 1$ ) is performed every iteration regardless of Cbeing odd or even.

The computations are done when C = 0 and the result is W = 246 as can be seen form the Table.

#### 2.2.2. Mathematical Proof

The algorithm proposed in [27] computes division in GF(p) only. It applies the Plus-Minus algorithm of Brent and Kung presented in [28]. This last, is a modification of the standard Binary algorithm to compute the GCD [42]. We adopted similar approach used in [27] with many modifications including extending the algorithm to compute division in both GF(p) and  $GF(2^n)$  fields in a more efficient way, and simpler flow to be more suitable for hardware implementation.

In both possible cases of fields, the main justification of the success of the algorithm is that throughout the computation, one has the two congruences:

| Operations              | δ  | C   | D   | U   | W   |

|-------------------------|----|-----|-----|-----|-----|

| Initialization          | 0  | 108 | 251 | 213 | 0   |

| C >> 1                  | -1 | 54  | 251 | 232 | 0   |

| C >> 1                  | -2 | 27  | 251 | 116 | 0   |

| swap, C := (C - D) >> 1 | 2  | 112 | 27  | -58 | 116 |

| C >> 1                  | 1  | 56  | 27  | -29 | 116 |

| C >> 1                  | 0  | 28  | 27  | 111 | 116 |

| C >> 1                  | -1 | 14  | 27  | 181 | 116 |

| C >> 1                  | -2 | 7   | 27  | 216 | 116 |

| swap, C := (C - D) >> 1 | 2  | 10  | 7   | -50 | 216 |

| C >> 1                  | 1  | 5   | 7   | -25 | 216 |

| C := (C+D) >> 1         | 1  | 6   | 7   | 221 | 216 |

| C >> 1                  | 0  | 3   | 7   | 236 | 216 |

| C := (C - D) >> 1       | 0  | -2  | 7   | 10  | 216 |

| C >> 1                  | -1 | -1  | 7   | 5   | 216 |

| swap, C := (C - D) >> 1 | 1  | 4   | -1  | 231 | 5   |

| C >> 1                  | 0  | 2   | -1  | 241 | 5   |

| C >> 1                  | -1 | 1   | -1  | 246 | 5   |

| swap, C := (C + D) >> 1 | 1  | 0   | 1   | 0   | 246 |

TABLE 2.1: A modular division by the UMD algorithm in GF(p)

$CX \equiv UY \mod p$

$$DX \equiv WY \mod p$$

;

Indeed, this is clearly true upon initialization: C = Y; U = X and D = p, W = 0. Thereafter, we either: swap ordered pairs (C, U) with (D, W); or, replace (C, U) by  $((C + kD)\xi^{-1}, (U + kW + v_0p)\xi^{-1})$ , with a shared value of k and with  $v_0 \in \{0, 1\}$ , and  $\xi^{-1}$  is either 2 or x depending on the field to be GF(p) or  $GF(2^n)$ , respectively. These two operations obviously preserve our pair of congruences.

Hence, once we show that the WHILE loop ends with D = 1, it is clear that Wthen yields  $XY^{-1} \mod p$ . However, the iterates of the values (C, D) are calculating the greatest common divisor of Y and p in the appropriate ring:  $\mathbb{Z}$  or (GF(2))[x]; that is, in any iteration, (C, D) is the value of consecutive remainders in a modified extended Euclidean algorithm applied to (Y, p). Since this pair are relatively prime, the GCD calculation ends with one of C, D being a unit, the other being zero. On the other hand, it is easily seen that D is such that  $d_0 = 1$  throughout any division phase. Hence, we eventually find C = 0 and D = 1.  $\Box$

# 2.3. Hardware Architecture of The Unified Modular Divider

Figure 4.1 shows the top level organization of the unified modular divider that implements the UMD algorithm. The main functional blocks are *Registers*, *Swapping Network (Multiplexers)*, *Control and Datapath*.

FIGURE 2.2: Top level organization of the modular divider which implements the UMD Algorithm.

The registers C, U, D, and W are initialized with the inputs (X, Y, p) when Load = 1 through three-state buffers. When Load = 0, the registers receive their values from

$U_{out}$  and  $C_{out}$  coming from the datapath.  $U_{out}$  is fed back to either U or W registers depending on *Load* U and *Load* W, respectively. Also,  $C_{out}$  is fed back to C or Dregisters depending on *Load* C or *Load* D, respectively. All these signals are generated by the control block.

The swap operations  $(C \Leftrightarrow D, U \Leftrightarrow W)$  are realized by the Swapping Network which is a set of two-input muxes, controlled by the *SEL* signal provided by the control block and takes its value based on the value of  $\delta$  (kept internally). More detail are provided in the dtatpath Section.

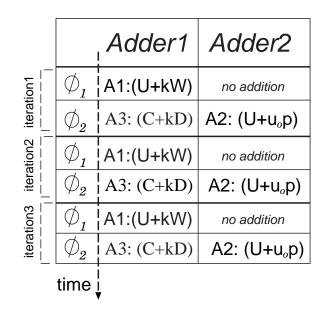

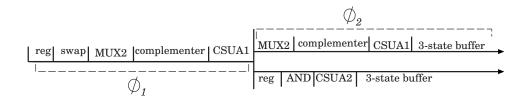

### 2.3.1. Adders Scheduling for Efficiency

The UMD algorithm performs in the worst case (*else* part of the algorithm) 3 additions in each iteration which are shown in Figure 2.3. Using 3 adders will increase the area of the design significantly especially for large precision inputs. Another alternative is to use a single adder in more than one clock cycle to complete one iteration. Such a solution would increase the overall time to compute the division but would be a solution when the area is too restrictive. Therefore for this implementation of an isolated division unit the use of two adders is the best choice.

In this worst case scenario (Figure 2.3), there is data dependency between additions  $A1 \ (U + k * W)$  and  $A2 \ (U + u_0 * p)$ . Therefore, one iteration is complete only after two consecutive additions are performed. If we assign addition A1 to one adder (adder1) and addition A2 to another adder (adder2), each adder will be working for only half of the clock cycle time. Based on this observation, we propose a solution that uses adder1 to compute addition 3 (A3) in the second half of the iteration cycle, while adder2 is computing A2. This solution requires a register or latch between the two adders, clocked at twice the clock frequency at which iterations are executed.

As can be seen from Figure 2.3, Adder1 receives the operands to compute A1 during phase 1 ( $\phi_1$ ). At the end of  $\phi_1$ , the adder output is registered and another set of input values is applied to compute A3 during  $\phi_2$ . Note that during  $\phi_1$  the Adder2 is

Ai: Addition Operations

FIGURE 2.3: Scheduling of adders in the modular divider that implements the UMD algorithm

not used anyway because the signals are still propagating in the first half of the circuit. Another observation is that phase  $\phi_2$  can be shorter than  $\phi_1$  in order to keep the hardware units working most of the time.

### 2.3.2. Datapath

An *n*-bit datapath was designed to support the computations described by the UMD algorithm and it is shown in Figure 4.2. Each iteration of the algorithm is implemented in one clock cycle. The critical path delay (the clock cycle time) is determined by the datapath and control block, and it will be addressed in more detail in Section 2.3.3.

The proposed datapath uses two Carry-Save Unified Adders (CSUAs) to perform addition in both GF(p) and  $GF(2^n)$  fields. The CSUA is basically formed by dual-field adders which were described in [6] for a (3,2) design (3 inputs and 2 outputs) and in [43] for a (4,2) design. The (3,2) dual-field adder is similar in complexity to a full-adder and it performs bit addition with and without carry. This functionality is enabled by the

FIGURE 2.4: The Unified Datapath of the Modular Divider

input FSEL (Field Select). When FSEL = 0, the carry out bits are forced to 0 and the dual-field adder performs bitwise modulo-2 addition of its inputs. When FSEL = 1, the dual-field adder performs the bitwise addition with carry (addition in GF(p)). Another implementations of unified adders can be used as the one proposed in [44].

CSUA1 was implemented using (4,2) dual-field adders and CSUA2 was implemented using (3,2) dual-field adders. The use of redundant form of the operands enables the circuit to have a critical path that is less sensitive to the operand precision. The addition time is less than the time for non-redundant adder, especially for large precision. A binary vector X is represented in CS form by two vectors XC and XS such that X = XC + XS. Therefore, the cost of CS representation comes from more registers and buses. The three control lines: S, Z, and N in MUX2 corresponds to select, zero, and negate, respectively. When Z = 1 the output of the mux is forced to zero regardless of S. N = 1 produces a bit-complement of the input. Since we are dealing with numbers in two's complement represented in CS form, the change of sign is done by complementing each vector and adding 1. Thus, N is inserted as carry input into both CSUAs to get the change of sign operation in this system.

The latch between the two carry-save unified adders lets the information at its input pass through during  $\phi_1$  and holds the information at its output when it is  $\phi_2$ .

The UMD algorithm computes the modular division in GF(p) when Field = GF(p). The select signal S is synchronized with the latch. MUX2 is used to implement k \* D and k \* W, where  $k \in \{-1,1\}$ . In the case k = -1, the negative D and the negative W are obtained by setting N = 1. Both signals Z and N are synchronized with the main clock (clk).

If C is even, then it is shifted right one bit and the counter  $\delta$  is decremented by one. If not, we test  $\delta$ , if it is negative, the circuits swap the values of C and D, and U and W, and change the sign of  $\delta$ . The swap operation is performed by the Swapping Network that precedes the datapath and takes its inputs from the C, U, D, and W registers.

The test  $(C + D) \mod 4 \neq 0$  can be implemented using a small two-level gate network.

The addition U := (U+k\*W) which corresponds to A1 in Figure 2.3, is performed in the first phase of the clock signal  $(\phi_1)$  using the CSUA1. During  $\phi_2$ , two separate additions happen: C := (C+k\*D) (A3 in Figure 2.3) using CSUA1, and  $U := (U+u_0*p)$ (A2) using CSUA2. Both outputs are shifted to the right by one bit to complete the algorithm operations.

An AND gate is used to select between the value 0 or the modulus p depending whether U is even or odd, respectively.

If the algorithm is computing the modular division in  $GF(2^n)$ , the same procedure described above is followed, except that the test  $(C + D) \mod 4 \neq 0$  is not applicable (Field = 0). For both fields, the computation is done when C = 0, and the result is Z = W.

It can be shown that the UMD algorithm does not change the values of the operands once C = 0. Therefore, the test C = 0 can take several clock cycles. Another observation shows that the non-redundant representation of C = 0 takes only some particular values, what makes this test easier. So, using these two features we can make the test of zero for the CS representation simple and multi-cycle, allowing the design to be fast without a significant increase in area. Another possibility is to use counters to estimate when C reaches 0.

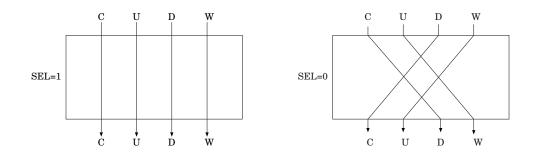

The Swapping Network shown in the datapath is composed of two-input muxes. The control signal (SEL) selects between the inputs. The two possible configurations of the Swapping Network are shown in Figure 2.5 (when SEL=0 or 1).

FIGURE 2.5: The two possible configurations of the Swapping Network.

## 2.3.3. Improving The System Performance

Figure 2.6 shows the critical path of the unified divider which will determine the clock period of the design.

$$clock \ period = max(delay\phi_1, delay\phi_2)$$

From the figure it is clear that  $\phi_1$  is longer than  $\phi_2$ . There are two possibilities for the delays in  $\phi_2$  as shown in Figure 2.6, coming from the paths that include CSUA1 or CSUA2. Noticing that the delay of CSUA2 is smaller than the delay of CSUA1, the upper path is longer, so it is considered as the delay of  $\phi_2$ .

FIGURE 2.6: The delay paths of the Modular Divider.

Since that  $delay\phi_1 > delay\phi_2$ , the delay of  $\phi_1$  determines the clock period of clk2x, which is half the clock period of clk. In this case clk will have a 50% duty cycle. More performance could be extracted from the circuit if  $\phi_2$  could be made shorter. However, such a solution would involve critical implementation details for the design of the clock signal generator and clock distribution network.

# 3. NOVEL UNIFIED MODULAR DIVISION AND MULTIPLICATION ALGORITHM (UDMA) IN GF(P) AND $GF(2^N)$ .

This Chapter presents a novel Unified modular Division and Multiplication Algorithm (UDMA) in GF(p) and  $GF(2^n)$ . To the best of our knowledge, the UDMA is the first algorithm to compute modular division and multiplication in both GF(p) and  $GF(2^n)$  fields (*Unified*). The UDMA is based on the Extended Binary GCD algorithm for modular division, and on the Montgomery's method for modular multiplication. In the next Section we present the UDMA, followed by details about the multiplication mode in Section 3.2. The modular division mode of the UDMA is explained in Section 3.3. A mathematical proof of the algorithm is presented in Section 3.4.

# 3.1. Unified Algorithm for Modular Division and Montgomery Modular Multiplication

Figure 3.1 shows the Unified modular Division/Multiplication Algorithm (UDMA) for both GF(p) and  $GF(2^n)$  fields. Up to our knowledge, this is the first algorithm that integrates the computation of modular division and Montgomery modular multiplication in both GF(p) and  $GF(2^n)$  fields. The UDMA mode of operation is controlled by the input Op (div or mult), and the finite field is controlled by the input Field (GF(p) or  $GF(2^n)$ ). For simplicity, the polynomials X(x), Y(x), and p(x) are denoted as X, Y, and p, respectively, which corresponds to the bit-vector representation of these polynomials.

Most of the arithmetic operations in the algorithm are common to both modes of operation. The initialization of variables depends on that division or multiplication being performed by the algorithm. For a given field, all the additions/subtractions are done in the field, besides the arithmetic operations on  $\delta$  (decrement and change of sign) which are always integer operations. Decrementing  $\delta$  in both division and multiplication modes, can be implemented using fast up/down counter as the ones proposed in [41].

**Function**: Modular Division and Multiplication in GF(p) and  $GF(2^n)$ **Inputs**:  $0 \le X < p, \ 0 < Y < p, \ 2^{n-1} < p < 2^n$ , Field, Op, n **Output**:  $Z = XY2^{-n} \mod p$  when Op = mult,  $Z = \frac{X}{V} \mod p$  when Op = div. Algorithm: C = Y./\* Multiplication Mode \*/ IF Op = mult THEN  $D = 0, U = 0, W = X, \delta = n$ ELSE /\* Division Mode \*/  $D = p, U = X, W = 0, \delta = 0$ END IF; WHILE  $[(C \neq 0 \text{ AND } Op = div) \text{ OR } (\delta \neq 0 \text{ AND } Op = mult)]$ IF  $c_0 = 0$  THEN C := C >> 1 $\delta := \delta - 1$  /\* Integer Operation \*/ ELSE k = 1IF (Op = div) THEN IF  $\delta < 0$  THEN  $C \Leftrightarrow D, U \Leftrightarrow W, \delta := -\delta$  END IF; /\* Swapping \*/ IF $((C+D) \mod 4 \neq 0 \text{ AND } Field = GF(p))$  THEN k = -1ELSE  $\delta := \delta - 1$  END IF; ELSE /\* Op = mult \*/ $\delta := \delta - 1$ END IF;  $C := (C + k * D) >> 1, \quad U := (U + k * W)$ END IF;  $U := (U + u_0 * p) >> 1$ END WHILE; IF Op = div THEN Z := W ELSE Z := UEND IF;

FIGURE 3.1: Unified modular Division/Multiplication Algorithm (UDMA) for GF(p)and  $GF(2^n)$ .

In this work, we used a similar counter to the one used in [29] as explained in the next Chapter. The >> operator indicates a 1-bit right shift operation.

The unified division/multiplication algorithm (UDMA) presented in this section, computes modular multiplication using Montgomery's method. Section 3.2 shows the operation of the UDMA when performing Montgomery multiplication. The correctness of the UDMA is proven mathematically in Section 3.4.

The UDMA computes modular division using the same structure used by the modular division algorithm presented in the last Chapter, which in turn, is based on the Extended Binary GCD Algorithm [40, 27]. The operation of the UDMA during computing modular division is shown in Section 3.3.

More details about the operation and hardware implementation of the UDMA are presented in the next Chapter.

#### **3.2.** Multiplication Mode

To perform Montgomery multiplication using the UDMA, we set the variable Op = mult, and we choose the field to be either GF(p) or  $GF(2^n)$ . Figure 3.2 shows the resulting operations performed by the UDMA during computing Montgomery multiplication after removing the control signals and tests that are required during division mode.

The UDMA performs n iterations to compute Montgomery multiplication using an n bit modulus p. The counter  $\delta$  is initialized with value n, and in each iteration it is decremented by one. The variables used in the algorithm are initialized as: C = Y, D = 0, U = 0, and W = X. The partial product U is reduced *mod* p in each iteration. In both fields, addition is used in the operations that update C (k = 1 always).

Table 3.1 shows the operation of the unified modular division/mulitipliaction algorithm when performing Montgomery multiplication in either GF(p) or  $GF(2^n)$  fields. Shifting the multiplier C happens in each iteration (notice that the value of D stays

| $c_0 = 0 \ (\mathbf{THEN})$ | $c_0 = 1 \ (\mathbf{ELSE})$               |  |  |  |  |

|-----------------------------|-------------------------------------------|--|--|--|--|

| $U := (U + u_0 * p) >> 1$   | $U := (U + k * W)  U := (U + u_0 * p) >>$ |  |  |  |  |

|                             | $C >> 1, \delta = \delta - 1$             |  |  |  |  |

TABLE 3.1: The operations performed by the UDMA during Montgomery multiplication

zero during computing Montgomery multiplication, and so the expression C := (C + k \* D) >> 1 is reduced to C >> 1).

Notice that the addition in  $GF(2^n)$  is done without carry propagation. The final result is ready (Z = U) when  $\delta = 0$ . If Z > p then Z = U - p. In order to use the intermediate result of one multiplication as the input to another one without subtracting p, we need to use two extra bits of precision (n + 2 bits) [38, 33].

# 3.2.1. Numerical Example:Computing Montgomery Multiplication Using The UDMA

To explain the operation of the UDMA more clearly, we show in Table 3.2 a numerical example to compute Montgomery multiplication using the UDMA. The computations are done in the prime field with p = 503, (and so the precision  $n = 9 \Rightarrow$  $r = 2^n$ ). We want to compute  $(483 \times 301 \times r^{-1} \mod p$ . The Table shows the intermediate values of the variables: delta, C, U, and W. Notice that D is set to zero during the multiplication mode. The operations performed by the UDMA is also shown (C >> 1or U := (U + k \* W)). The reduction mod p is performed in each iteration.

The computation is completed when the counter  $\delta = 0$ . The result can be read from  $U,301 \times 483 \times 2^{-9} \mod 503 = 393$ . Notice that C is also zero at the end. This indicates that the algorithm scanned all the n bits of the multiplier.

| Operations     | δ | C   | U   | W   |

|----------------|---|-----|-----|-----|

| Initialization | 9 | 301 | 0   | 483 |

| ELSE           | 8 | 150 | 493 | 483 |

| IF             | 7 | 75  | 498 | 483 |

| ELSE           | 6 | 37  | 742 | 483 |

| ELSE           | 5 | 18  | 864 | 483 |

| IF             | 4 | 9   | 432 | 483 |

| ELSE           | 3 | 4   | 709 | 483 |

| IF             | 2 | 2   | 606 | 483 |

| IF             | 1 | 1   | 303 | 483 |

| ELSE           | 0 | 0   | 393 | 483 |

TABLE 3.2: Montgomery multiplication example by the UDMA in GF(p)

#### 3.3. Division Mode

The unified modular division/multiplication algorithm computes modular division when the variable Op = div in both fields depending on the value of the variable *field*. We show in Figure 3.3 the algorithm during modular division computations.

The variables are initialized as: C = Y, D = p, U = X, W = 0, and  $\delta = 0$ . If the division is computed in GF(p), UDMA tests the least significant two bits of C and D  $((C + D) \mod 4 \neq 0)$  to conditionally subtracts C from D (set k = -1). Otherwise, C is always added to D in both fields. The division is completed when C = 0, and the final result is available in W. Table 3.3 summarizes the operations performed by the UDMA when computing modular division.

# 3.3.1. Numerical Example:Computing Modular Division Using The UDMA

Table 3.4 shows a modular division example by the UDMA. The computations are done in  $GF(2^4)$  (we choose a small field for simplicity) with an irreducible polynomial  $p(t) = t^4 + t^3 + 1$ . The algorithm computes  $(\frac{t^3+t+1}{t^3+1} \mod p(t))$ . The intermediate values

Function: Multiplication Mode of The UDMA **Inputs**:  $0 \le X < p, 0 < Y < p, 2^{n-1} < p < 2^n$ , Field, n **Output**:  $Z = XY2^{-n} \mod p$ Algorithm: C = Y. Op = mult THEN  $D = 0, U = 0, W = X, \delta = n$ WHILE (  $\delta \neq 0$  ) IF  $c_0 = 0$  THEN C := C >> 1 $\delta := \delta - 1$  /\* Integer Operation \*/ ELSE k = 1 $\delta := \delta - 1$  $C := (C + k * D) >> 1, \quad U := (U + k * W)$ END IF;  $U := (U + u_0 * p) >> 1$ END WHILE; Z := U

$c_0 = 0 \; (\text{THEN})$   $c_0 = 1 \; (\text{ELSE})$

C >> 1 C := (C + k \* D) >> 1

$U := (U + u_0 * p) >> 1$  U := (U + k \* W)

$U := (U + u_0 * p) >> 1$   $U := (U + u_0 * p) >> 1$

FIGURE 3.2: Computing Montgomery multiplication in GF(p) and  $GF(2^n)$  using the UDMA.

| Operations     | δ  | C           | D               | U               | W |

|----------------|----|-------------|-----------------|-----------------|---|

| Initialization | 0  | $t^{3} + 1$ | $t^4 + t^3 + 1$ | $t^3 + t + 1$   | 0 |

| ELSE           | -1 | $t^3$       | $t^4 + t^3 + 1$ | $t^{3} + 1$     | 0 |

| THEN           | -2 | $t^2$       | $t^4 + t^3 + 1$ | $t^3$           | 0 |

| THEN           | -3 | t           | $t^4 + t^3 + 1$ | $t^2$           | 0 |

| THEN           | -4 | 1           | $t^4 + t^3 + 1$ | t               | 0 |

| ELSE           | 3  | $t^3 + t^2$ | 1               | 1               | t |

| THEN           | 2  | $t^2 + t$   | 1               | $t^{3} + t^{2}$ | t |

| THEN           | 1  | t+1         | 1               | $t^{2} + t$     | t |

| ELSE           | 0  | 1           | 1               | t               | t |

| ELSE           | -1 | 0           | 1               | 0               | t |

TABLE 3.4: A modular division by the UDMA in  $GF(2^4)$

of the variables: delta, C, D, U, and W are shown in the Table with the corresponding performed operation by the UDMA. The Table also shows which portion of the algorithm was carried out (*THEN* or *ELSE*). Notice that the modular reduction step (U := $(U + u_0 * p) >> 1$ ) is performed every iteration.

As can be seen form the Table, the computations are done when C = 0, and the final result is W = t.

# 3.4. Mathematical Proof During Computing Montgomery Multiplication

The UDMA performs modular division based on the Extended Binary GCD algorithm and the unified modular division algorithm which we proposed with its mathematical proof in Chapter 2, and it will not be mentioned here to avoid repetition. In this Section we prove the correctness of computing Montgomery multiplication by the UDMA.

Since the UDMA operates in both fields, we use  $\xi$  to denote either 2, or x, depending upon the context of field being GF(p) or  $GF(2^n)$ , respectively.

Input X, Y as well as n and p, we are to output  $Z = XY\xi^{-n}$ .

#### 3.4.1. Product modulo p

The multiplication algorithm employs a standard idea. First, writing Y as  $\sum_{j=0}^{n-1} y_j \xi^j$ , we have

$$XY\xi^{-n} = X\xi^{-n} \sum_{j=0}^{n-1} y_j \xi^j$$

=  $\sum_{j=0}^{n-1} y_j X \xi^{j-n}$

=  $(\cdots (((y_0 X \xi^{-1} + y_1 X) \xi^{-1} + y_2 X) \xi^{-1} + \cdots + y_{n-2} X) \xi^{-1} + y_{n-1} X$

=  $(\cdots ((((y_0 X + v_0 p) \xi^{-1} + y_1 X + v_1 p) \xi^{-1} + y_2 X + v_2 p) \xi^{-1} + \cdots$

$\cdots + y_{n-2} X + v_{n-2} p) \xi^{-1} + y_{n-1} X + v_{n-1} p \mod p$ ,

where the  $v_i \in \{0, 1\}$ . In this article, single shifts to the right correspond to multiplication by  $\xi^{-1}$ . In the algorithm, U begins at zero; the value of Y is given to C, and that of X to W. Thus, whenever  $y_j = 0$ , we find that U is replaced by  $(U+u_0*p)\xi^{-1}$ . Whenever  $y_j = 1$ , U is replaced by  $[(U + X) + (u_0 + x_0) * p]\xi^{-1}$ . We conclude that Uevaluates the product  $XY\xi^{-n} \mod p$  in the form displayed above.

# 3.4.2. Product is Reduced

All field elements are represented by the standard complete set of residue class representatives,  $\{0, 1, \ldots, p-1\}$ , or  $\{0, 1, x, x+1, \ldots\}$  except, of course, p or p(x). Rather than evaluate the product in either ring  $\mathbb{Z}$  or (GF(2))[x] and then in a final step reduce modulo the appropriate prime element p, the algorithm uses the standard "interleaving" process for reduction. Indeed, we claim that at the end of each iteration (of the WHILE loop), U is reduced.

Initially, U = 0. For a proof by induction, we thus assume that U is reduced at the beginning of any arbitrary iteration. Now, upon completion of the iteration, (1) U is replaced by (1)  $(U + u_0 p)\xi^{-1}$ ; or, (2) we first find U + X (in reduced form) and then  $[(U + X) + (u_0 + x_0) * p]\xi^{-1}$ , where the multiplication by  $\xi^{-1}$  is effected by a right shift. Since for any reduced element say V,  $(V + v_0 p)\xi^{-1}$  is easily seen to be reduced, we are done. Function: Division Mode of The UDMA

**Inputs**:  $0 \le X < p, 0 < Y < p, 2^{n-1} < p < 2^n$ , Field **Output**:  $\frac{X}{Y} \mod p$ Algorithm: C = Y.  $D = p, U = X, W = 0, \delta = 0$ WHILE  $(C \neq 0)$ IF  $c_0 = 0$  THEN C := C >> 1 $\delta := \delta - 1$  /\* Integer Operation \*/ ELSE k = 1IF  $\delta < 0$  THEN  $C \Leftrightarrow D, U \Leftrightarrow W, \delta := -\delta$  END IF; /\* Swapping \*/ IF $((C+D) \mod 4 \neq 0 \text{ AND } Field = GF(p))$  THEN k = -1ELSE  $\delta := \delta - 1$  END IF;  $C := (C + k * D) >> 1, \quad U := (U + k * W)$ END IF;  $U := (U + u_0 * p) >> 1$ END WHILE; Z := W

FIGURE 3.3: Computing modular division in GF(p) and  $GF(2^n)$  using the UDMA.

# 4. SCALABLE AND UNIFIED MODULAR DIVIDER/MULTIPLIER HARDWARE DESIGN.

In this Chapter, we propose a Unified Modular Divider/Multiplier hardware that implements the Unified modular Division and Multiplication Algorithm (UDMA) presented in Chapter 3. In the next Section, we present the overall hardware system architecture and the implementation details. The datapath of the proposed architecture has a variable word size that can be adjusted to meet the area and performance requirements. In Section 4.2, we modify the proposed divider/multiper architecture to get a scalable hardware that can handle operands of any size.

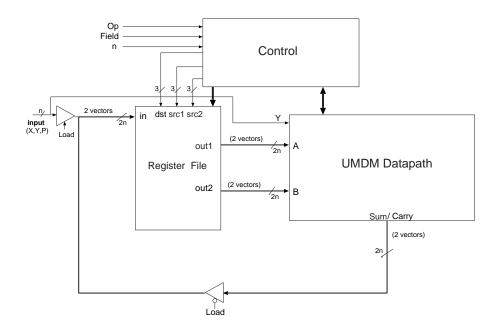

#### 4.1. Overall Hardware System Architecture

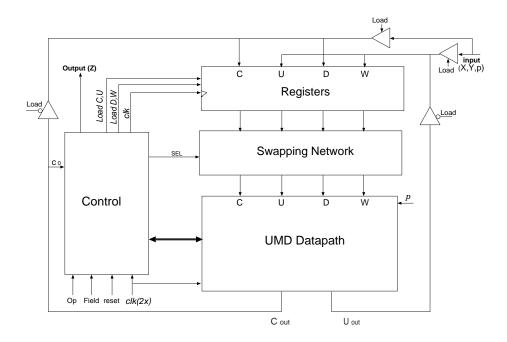

Figure 4.1 shows the top level architecture of the Unified Modular Divider/Multiplier (let us call it UMDM) that implements the UDMA. The main functional blocks are *Reg*-ister File, *Datapath*, and *Control*.

The following subsections provide the implementation details of the functional blocks of the UMDM and explains the design approaches used to implement the proposed architecture [45].

#### 4.1.1. Register File

The register file has five registers (R1 to R5). Since the computations are done in Carry-Save form [46], each intermediate variable (C, U, D, W) is represented in two vectors (sum,carry). So, the registers inside the register file are designed to store two *n*-bit vectors. In other words, the  $i^{th}$  register  $R_i$  is represented as  $R_i = (sum, carry) =$ ( $R_is, R_ic$ ).

FIGURE 4.1: Top Level Hardware Architecture of the Unified Modular Divider/Multiplier (UMDM).

The register file has one input, and two output ports. The Control block provides the register file with the signals necessary to perform reading/writing operations. The 3-bit signal *dst* determines the destination register to be written. The signals *src1*, *src2* (3-bits each), specify the registers to be read at output ports *out1*, *out2*, respectively.

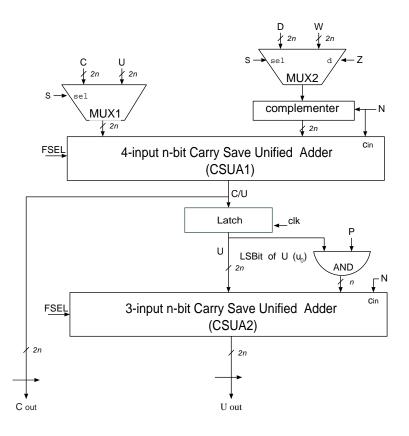

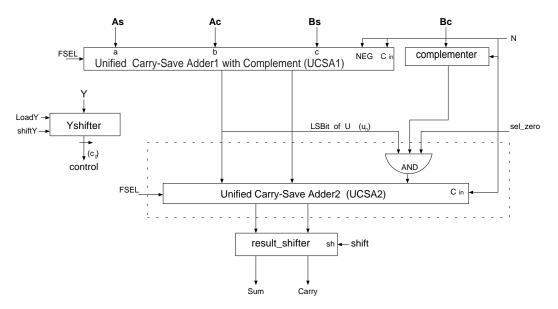

## 4.1.2. UMDM Datapath

The *n*-bit datapath implementing the UDMA is shown in Figure 4.2. Each "while iteration" of the algorithm is implemented in one clock cycle for multiplication mode, and in three clock cycles for division mode if C is odd, and 2 clock cycles if C is even, as explained later.

The proposed datapath has two inputs (A,B) represented in carry-save form as A=(As,Ac) and B=(Bs,Bc) which receive their values from the output ports (*out1,out2*) of the register file, respectively.

FIGURE 4.2: Unified datapath of the Modular Divider/Multiplier (UMDM datapath).

The main components of the datapath are two (3-2) Unified Carry-Save Adders (UCSAs) used to perform addition in either GF(p) or  $GF(2^n)$  fields. The Unified Adders (UAs) [6, 47] are similar in complexity to full-adders and are capable of doing bit addition with or without carry. It has an input called *FSEL* (Field Select) that enables this functionality.

The unified adder may be used to implement a redundant or non-redundant adder which may also be a full-precision or multi-precision adder. The use of non-redundant form of the operands and results reduces the register area but increases significantly the addition time (because of carry propagation), when compared with redundant adders. We decided to use Carry Save adders to make the addition time constant and independent of the operand's precision.

#### 4.1.2.1. Unified Carry-Save Adders

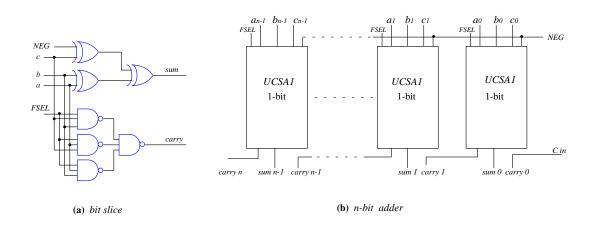

The first adder in the datapath is a Unified Carry-Save Adder with complement (UCSA1). Figure 4.a shows the bit slice diagram for this adder and Figure 4.b shows the connection of n slices to form an n-bit adder.

FIGURE 4.3: Unified Carry-Save Adder with Complement (UCSA1) for 1-bit and n-bit precision.

Equation 4.1.2.1. defines the outputs of the UCSA1 in terms of the inputs. The input signal *FSEL* determines in which field the addition or subtraction of operands are performed. Note that in  $GF(2^n)$  addition is the same as subtraction.

$$(sum, carry) = \begin{cases} a+b+c & \text{, when } NEG = 0 \text{ and } Cin = 0\\ a+b-c & \text{, when } NEG = 1 \text{ and } Cin = 1 \end{cases}$$

As we can see from Figure 4.3, the change of sign operation inside the UCSA1 is done in parallel with the addition operation, and so, it does not add to the critical path.

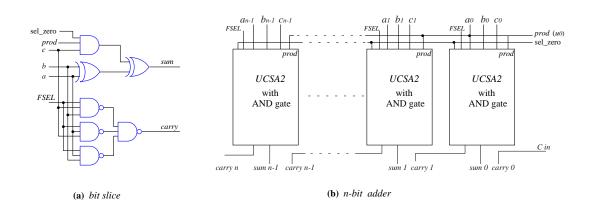

The AND gate shown at the top of UCSA2 in Figure 4.2 is used to select between the value 0 or the modulus p depending whether U is even or odd (this is indicated by testing  $u_0$ ), respectively. The input signal *sel\_zero* when asserted forces the third input of the UCSA2 to zero. The delay of the UMDM datapath  $(t_{datapath})$  is determined by the delay of the two unified adders, the delay of the AND gate between them, and the delay of the *result\_shifter* which has the delay of 2-input multiplexer  $(t_{MUX} \simeq t_{XOR})$ . Subsection 4.1.2.2. describes the shifters used in the datapath. By integrating the AND gate with the second adder (shown in dashed box in Figure 4.2), its delay will not add to the path delay as shown in Figure 4.4. Figure 4.4 shows the integration of the AND gate to the UCSA2 at the bit level and as an *n*-bit adder. Knowing that each UCSA has a delay of a full adder  $(t_{FA} = 2t_{XOR})$ , we get:

$t_{datapath} = t_{USCA1} + t_{UCSA2} + t_{result\_shifter} = 4t_{XOR} + t_{MUX} = 5t_{XOR}$

FIGURE 4.4: Unified Carry-Save Adder with integrated AND gate for 1-bit and n-bit precision

#### 4.1.2.2. Shifters

The *Yshifter* shown in Figure 4.2 is a shift register that is used to implement the 1-bit right shift operation  $(C \gg 1)$  only in the multiplication mode. The *Yshifter* is loaded with the input Y (multiplier) when laodY = 1. In both cases when C (remember

that C = Y is even or odd, it is shifted right by 1-bit when shiftY = 1. The least significant bit of the shifted C goes to the control section to perform the test  $c_0 = 0$ .

The outputs of the datapath (Sum and Carry) are shifted 1-bit to the right by correct wiring. The result\_shifter at the output of the UCSA2 is used to choose between these outputs and their shifted values. This module is implemented as two 2-input multiplexers with select line shift. When shift = 1, the shifted outputs are selected.

# 4.1.3. Control Block

This subsection describes the Control block and the system operation during division and multiplication modes and the design techniques used to implement the proposed UMDM architecture.

When Load = 1, the registers inside the register file are accessible for external input (from the user) and are initialized with the inputs X, Y, and p depending on the operation to be performed by the algorithm.

While the algorithm is in division mode, the test  $C \neq 0$  must be done. The vector C is in Carry Save form. Simulation results show that C = 4 or -4 at the end of computation. If more iterations than required are performed, the result is still correct. In the proposed UMDM design, the test  $C \neq 0$  is replaced by testing the bit vector C for specific values (4 or -4), and no need to compare all the bits of C with zero.

#### 4.1.3.1. Multiplication Mode

The proposed multiplier/divider performs one iteration of the algorithm in each clock cycle when computing Montgomery multiplication in both fields. Only three registers are used. Table 4.1 shows the loading phase for multiplication and division (initialization of the intermediate variables) as described by the algorithm.

| Multipli                            | cation                    | Division             |                         |  |

|-------------------------------------|---------------------------|----------------------|-------------------------|--|

| Variables/parameters Loading the RF |                           | Variables/parameters | Loading the RF          |  |

| represented by $R$                  | $R \leftarrow (Rs, Rc)$   | represented by $R$   | $R \leftarrow (Rs, Rc)$ |  |

| W  and  p                           | $R_1 \leftarrow (X, p)$   | W                    | $R_1 \leftarrow (X,0)$  |  |

| U                                   | $R_2 \leftarrow (0,0)$    | U                    | $R_2 \leftarrow (0,0)$  |  |

| p                                   | $R_3 \leftarrow (0,p)$    | D                    | $R_3 \leftarrow (p,0)$  |  |

| Variable                            | Loading the Shifter       |                      | $R_4 \leftarrow (Y,0)$  |  |

| С                                   | $YShifter \leftarrow (Y)$ | p                    | $R_5 \leftarrow (0,p)$  |  |

TABLE 4.1: Loading phase for multiplication and division

Table 4.2 shows the operation of the unified divider/mulitplier when performing Montgomery multiplication in either GF(p) or  $GF(2^n)$  fields. It shows the main control signals to the register file and the datapath to compute multiplication. I assumed that the signals which are not mentioned in the Table have their values equal to zero. Depending on C being even or odd, a different set of signals are used. The Table also shows the interpretation of these signals on the datapath, and the corresponding operation in the UDMA. When  $c_0 = 1$ , two additions  $(U := (U + k * W) \text{ and } U := (U + u_0 * p) >> 1)$ are performed by the datapath.

As mentioned in subsection 4.1.2.2., the variable C is shifted right one bit using the *Yshifter* in every cycle (*shiftY*  $\leftarrow$  1). The counter  $\delta$  is initialized with n to indicate the number of iterations. Since  $\delta$  is decremented by one in each iteration (*dec\_delta* = 1), the computation ends when  $\delta = 0$ , and the result can be read form  $R_2$ .

#### 4.1.3.2. Division Mode

Each modular division iteration in the proposed UMDM architecture requires 2 clock cycles if C is even and 3 clock cycles if C is odd independent of the field. The initialization of variables was shown in Table 4.1.

Let us assume that the algorithm is computing modular division in GF(p). Tables 4.3 and 4.4 show the control signals during division when C is even and odd, re-

|                           | = 0 (then)                     | $c_0 = 1 \; (else)$       |                                |  |

|---------------------------|--------------------------------|---------------------------|--------------------------------|--|

| Control                   | Datapath                       | Control                   | Datapath                       |  |