#### AN ABSTRACT OF THE THESIS OF

| KI SUK CHANG                                                                          | for the   | MASTER OF SCIENCE                         |

|---------------------------------------------------------------------------------------|-----------|-------------------------------------------|

| (Name)                                                                                |           | (Degree)                                  |

| Electrical and in Electronics Engineer: (Major)                                       | ing prese | ented on <u>June 1216, 1969</u><br>(Date) |

| Title: AN INTEGRATED MOS ADDRESSING CIRCUIT  Redacted for privacy  Abstract approved: |           |                                           |

|                                                                                       | James     | C. Looney                                 |

This paper is a study of the design of an integrated MOS addressing circuit by using the modified two-phase dynamic shift register. This modified circuit is compared to the conventional two-phase dynamic SR and discussed briefly. The resulting circuit shows several advantages to improve the essential conditions of integrated circuit design and fabrication.

Four stages of this dynamic SR are designed on a single monolithic chip. Each stage consists of seven devices and two intentionally added capacitors. A suggestion to imply that more stages can be used in any sequential digital system is given.

It is shown that the operation is at AC and the operating frequency is ranged between 200 KHz and 1 MHz clock rates.

# An Integrated MOS Addressing Circuit

by

Ki Suk Chang

#### A THESIS

submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Master of Science

June 1970

#### APPROVED:

# Redacted for privacy

Associate Professor of Electrical and Electronics Engineering

in charge of major

# Redacted for privacy

Head of Department of Electrical and Electronics Engineering

# Redacted for privacy

Dean of Graduate School

| Date thesis is presented | Henry        | 1 x the      | 1969 |

|--------------------------|--------------|--------------|------|

|                          | a di<br>Rusi |              | /    |

| Typed by Clover Redfern  | for          | Ki Suk Chang |      |

#### **ACKNOW LEDGMENT**

The author wishes to express his gratitude to Professor James

C. Looney, his major professor for guidance and invaluable comments during the course of this study and preparation of this thesis.

His appreciation also goes to Mr. Dave W. Chen, senior engineer at Texas Instruments, Inc., Mr. Pen C. Chou, Mr. Mehdi N. Araghi and Mr. David M. Tao, research assistants in Solid-State laboratories, for their helpful suggestions.

# TABLE OF CONTENTS

| Chapter |                                                      | Page |

|---------|------------------------------------------------------|------|

| I.      | INTRODUCTION                                         | 1    |

| II.     | THEORETICAL ANALYSIS                                 | 2    |

|         | Operating Principles of the MOS Transistor           | 2    |

|         | Electrical Characteristics of MOS Devices            | 2    |

|         | High Input Impedance                                 | 2    |

|         | Bilateral Current Flow                               | 4    |

|         | Coupling Device                                      | 4    |

|         | Temporary Storage                                    | 4    |

|         | MOS Resistor                                         | 5    |

|         | MOS Current Equations                                | - 5  |

|         | Threshold Voltage                                    | 9    |

|         | Back Gate Bias                                       | 12   |

|         | Capacitance                                          | 14   |

|         | MOS Inverter                                         | 16   |

|         | Power Consumption of the MOS Inverter                | 19   |

|         | Transient Response and Switching Time Consideration  | 20   |

|         | Load Device, Substrate Common to Source,             | _    |

|         | Saturation Region                                    | 20   |

|         | Load Device, Substrate to Source, Triode Region      | 23   |

|         | Load Device, Substrate Common to Ground              | 27   |

|         | Comparison of Two Types of 2¢ Dynamic Shift Register | 28   |

|         | Ratio Type Circuit Operation                         | 28   |

|         | The Ratioless Type Circuit Operation                 | 30   |

|         | Addressing Circuit Using Dynamic Shift Register      | 35   |

| III.    | DESIGN METHODS                                       | 39   |

|         | Design Calculations                                  | 39   |

|         | High Temperature                                     | 39   |

|         | Low V <sub>DD</sub>                                  | 39   |

|         | Low V <sub>GG</sub>                                  | 39   |

|         | High $V_{	extbf{T}}$                                 | 40   |

|         | Fabrication Process and Results                      | 53   |

| IV.     | EXPERIMENTAL RESULTS                                 | 58   |

|         | Characteristics of Devices Used for Tests            | 58   |

|         | The Results of the Circuit                           | 59   |

| v.      | CONCLUSION                                           | 64   |

| Chapter      | Page |

|--------------|------|

| BIBLIOGRAPHY | 65   |

| APPENDIX     | 67   |

| Appendix A   | 67   |

| Appendix B   | 73   |

# LIST OF FIGURES

| Figu | re                                                                                                 | Page       |

|------|----------------------------------------------------------------------------------------------------|------------|

| l.   | Typical V-I characteristics and notation of an MOS device.                                         | 3          |

| 2.   | Threshold voltage variation vs. back-gate bias.                                                    | 15         |

| 3.   | P-diffusion capacitance vs. reverse bias voltage.                                                  | 17         |

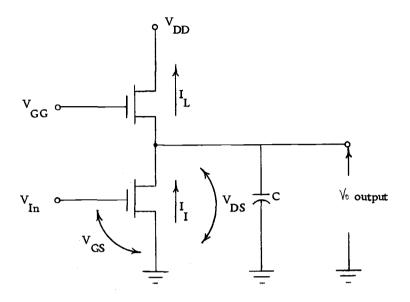

| 4.   | Turn-on case of an MOS inverter.                                                                   | 18         |

| 5.   | Turn-off case of an MOS inverter.                                                                  | 18         |

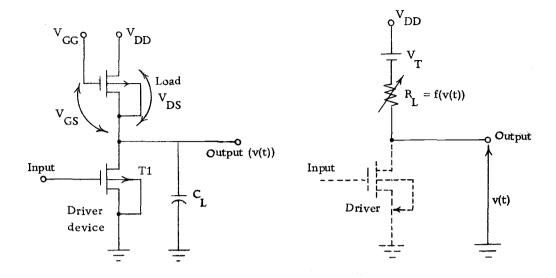

| 6.   | Inverter circuit using an MOS load and its equivalent circuit.                                     | 21         |

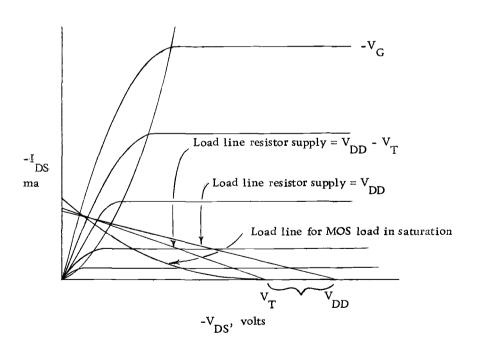

| 7.   | MOS load line and linear-resistor characteristic super-<br>imposed upon the driver characteristic. | 21         |

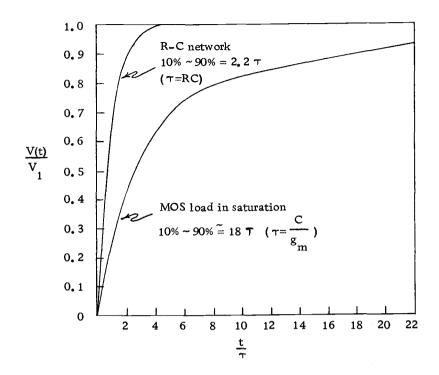

| 8.   | Switching time response of an MOS in the saturation region, with an R-C network for comparison.    | 26         |

| 9.   | Switching time response of an MOS load in the triode region $(m = 0 \text{ to } m = 1)$ .          | 26         |

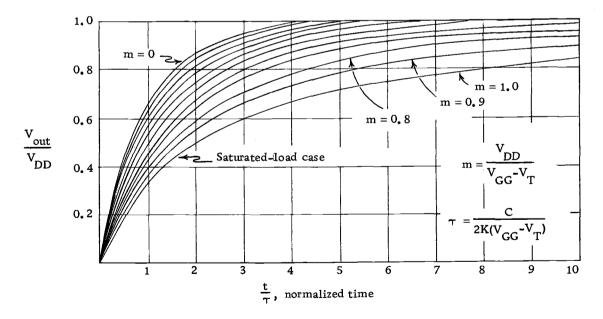

| 10.  | Two-phase dynamic shift register schematic (ratio type).                                           | 29         |

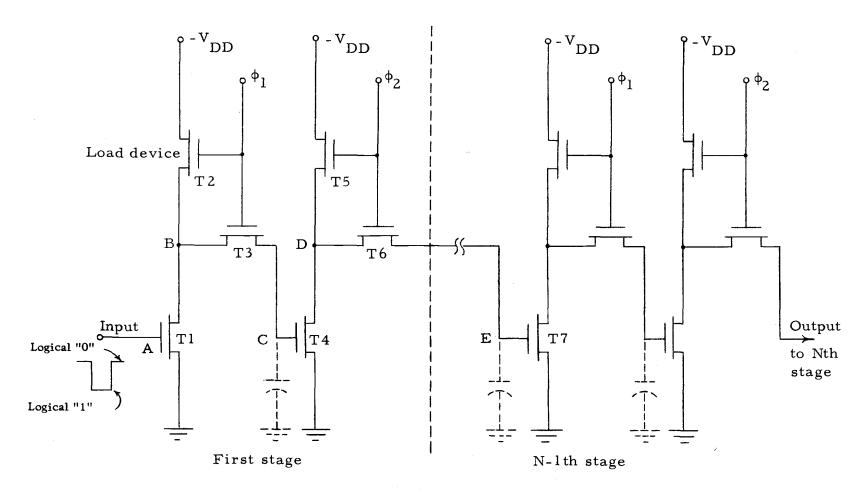

| 11.  | Two-phase dynamic shift register schematic (ratioless type).                                       | 31         |

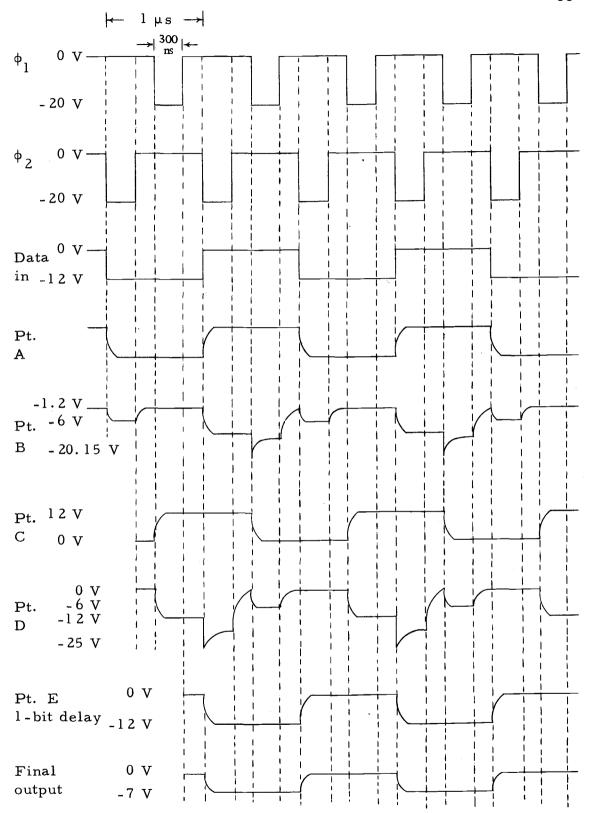

| 1 2. | Timing diagram of each node point for the ratioless type of dynamic shift register.                | 33         |

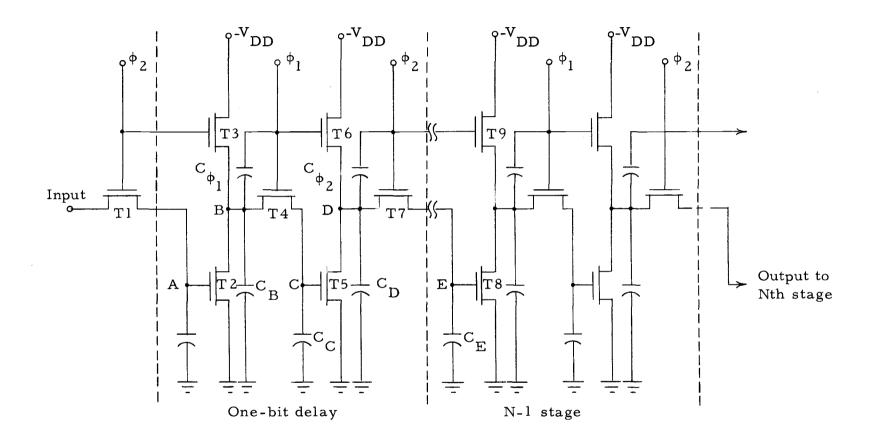

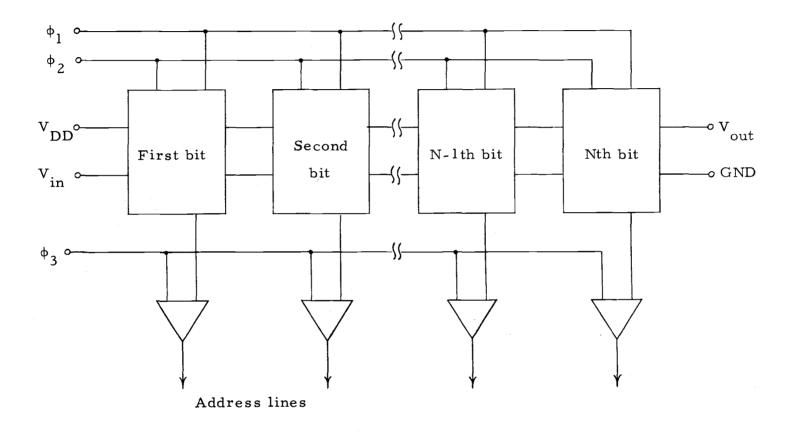

| 13.  | Functional block diagram showing address line connections.                                         | 37         |

| 14.  | Two-phase, N-bit delay, addressing circuit.                                                        | 38         |

| 15.  | Cross-sectional structure of the device.                                                           | 56         |

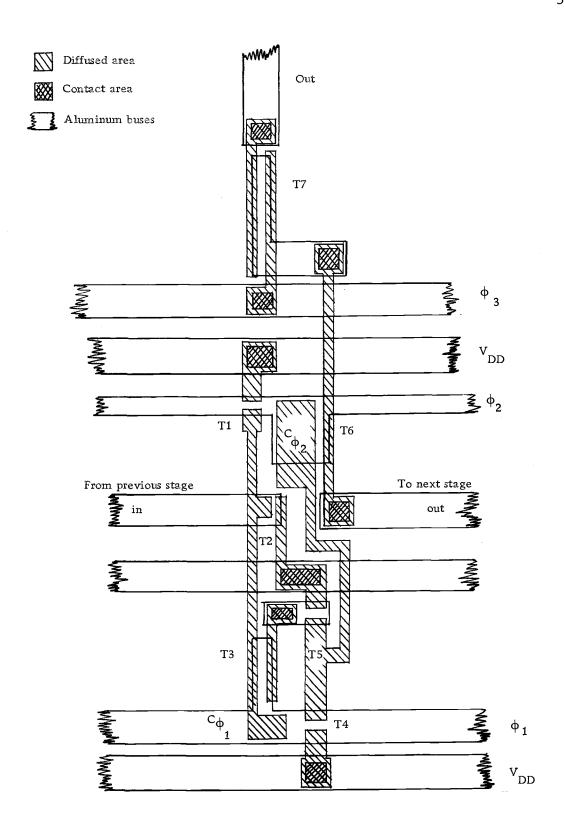

| 16.  | Layout of the dynamic SR basic one-bit cell.                                                       | 5 <b>7</b> |

| Figure |                                                   | Page |

|--------|---------------------------------------------------|------|

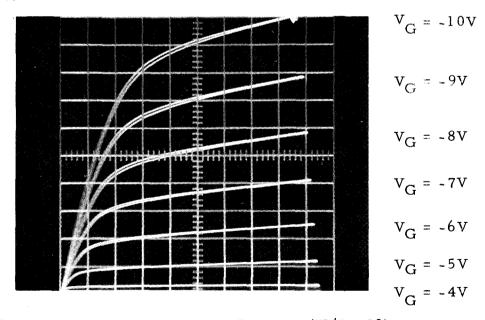

| 17.    | Characteristic curve of T7 device ( $W/L = 20$ ). | 58   |

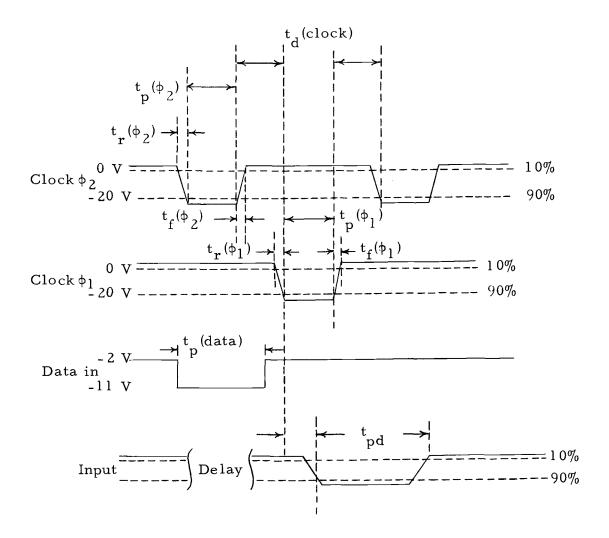

| 18.    | Analysis of voltage waveforms.                    | 61   |

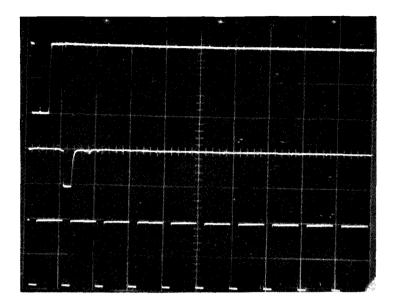

| 1 9.   | One-bit delay waveform.                           | 62   |

| 20.    | Two-bit delay waveform.                           | 62   |

| 21.    | Three-bit delay waveform.                         | 63   |

| 22.    | Four-bit delay waveform.                          |      |

# LIST OF TABLES

| Table |                             | $\operatorname{Pag}\epsilon$ |

|-------|-----------------------------|------------------------------|

| 1.    | W/L ratios of each device.  | 53                           |

| 2.    | Capacitance values.         | 53                           |

| 3.    | Device characteristics.     | 58                           |

| 4.    | Operating conditions.       | 59                           |

| 5.    | Electrical characteristics. | 60                           |

#### AN INTEGRATED MOS ADDRESSING CIRCUIT

#### I. INTRODUCTION

Multiphase metal-oxide semiconductor (MOS) integrated circuits have been developed in digital circuit fields. The development of large scale integration has put added emphasis on the development of new circuit techniques which makes it possible to build circuits of small size, high initial yield, and low power dissipation (18). Several advantages were obtained by using a dynamic shift register (SR) in an addressing circuit.

The circuit approach used in this SR is somewhat similar to that of an earlier type of two-phase dynamic shift register. The modification is that the external clock pulses drive a coupling device in addition to the load resistor, of the following inverter stage, rather than the previous load device (14). By this simple change, the circuit is able to function with the use of all minimum geometry devices. This allows substantial reduction of both the size of the inverter and the load device and the intrinsic capacitance of each node, thus allowing the cell to operate at a higher frequency. In addition, the power dissipation is much lower than in most two-phase systems.

This paper is primarily concerned with the theoretical analysis, design methods, and fabrication process and results of the integrated MOS addressing circuit. A general discussion of the existing MOS techniques is also included for background and prospective.

#### II. THEORETICAL ANALYSIS

#### Operating Principles of the MOS Transistor

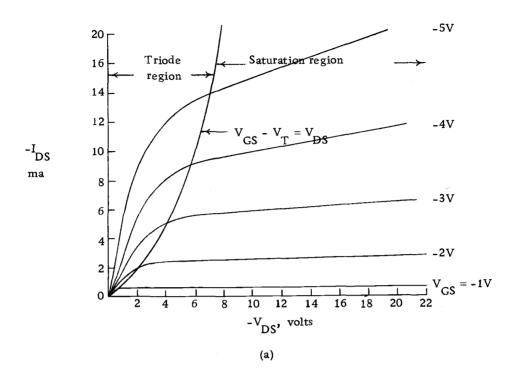

The MOS transistor shown in Figure 1a, operates as follows: when the source, substrate and gate are grounded and the drain is at some  $-V_{\mbox{DD}}$  level, no current will flow between the source and the drain, since the drain to the body P-N junction is reverse-biased.

When a negative bias greater than the threshold voltage is applied to the gate, the surface of the N-type silicon inverts. That is, it changes from an N-type to a P-type region, thus forming a channel from the source to the drain. The formation of this channel provides an ohmic path for the majority of carriers to flow between the source and the drain. A typical V-I characteristic curve is also illustrated in Figure 1b, which shows two different regions of operation.

#### Electrical Characteristics of MOS Devices

There are several pertinent electrical characteristics of an MOS transistor which make it particularly suitable for both digital and analog applications. These are:

#### High Input Impedance

The MOS transistor has virtually an infinite impedance  $(10^{14} \ \text{ohm})$  at the gate input due to the characteristics of the "no-

Figure 1. Typical V-I characteristics (a) and notation of an MOS device (b).

junction input" terminal, i.e., the gate is completely isolated from the drain and source region by a thin layer of silicon dioxide. The drain and source input terminals exhibit an impedance characteristic in the order of  $10^{10}$  ohm when the transistor is in the "OFF" state. This result is due to the reverse biased P-N junction.

#### Bilateral Current Flow

Since the MOS transistor is a symmetrical device, i.e., the physical construction of the drain and source are identical and therefore interchangeable, the current can flow in either direction in the channel. Therefore the device can be used as an ideal switch, providing in the "ON" state, current flow in either direction or, in the "OFF" state, virtually an infinite resistance.

#### Coupling Device

Because of the bilateral nature of an MOS device, it can be used as an ideal switch or coupling device. The use of a coupling device is one of the essential elements which make possible the implementation of an extremely simplified static or dynamic register cell.

#### Temporary Storage

The gate-to-source capacitance of an MOS device can be used as a temporary memory-storage element. The storage time is

dependent directly on the capacitance and the leakage characteristics of the gate oxide, and the drain or source to the body junction of its preceding coupling stage.

#### MOS Resistor

The most dramatic characteristic of an MOS device is its ability to act as an active load resistor. Although the resistance characteristic is nonlinear, i.e., the resistance varies as a function of the gate to source bias, large resistance values in the order of 100 Kohm to 400 Kohm can be fabricated within an area of less than 1 mil<sup>2</sup>. Coupled with its ability to exhibit large resistance values in an extremely small area, the MOS load device can be turned "ON" and "OFF" by applying a negative clock pulse to its gate. Power dissipation now becomes a function of the duty cycle of the clock. For very low duty cycles, extremely low power dissipation is obtainable even in the most complex circuits.

#### MOS Current Equation

The basic current equations for the non-saturated and saturated regions of operation are (4):

Non-saturated region

$$|\mathbf{v}_{\mathbf{GS}}^{-}\mathbf{v}_{\mathbf{T}}^{-}| \ge |\mathbf{v}_{\mathbf{DS}}^{-}|$$

$$I_{DS} = \frac{\overline{\mu}_{p \text{ ox}}}{2t_{OX}} \left[ 2(V_{GS} - V_{T})V_{DS} - V_{DS}^{2} \right]$$

(1)

Saturated region

$$|V_{GS}^{-}V_{T}^{-}| \leq |V_{DS}^{-}|$$

$$I_{DS}^{-} = \frac{\frac{\mu_{p} \cdot \epsilon_{OX}}{2t_{OX}} (V_{GS}^{-}V_{T}^{-})^{2}$$

(2)

where

$V_{\mathbf{GS}}$  is the voltage from gate to source

$\boldsymbol{V}_{T}$  is the threshold voltage

$V_{\mathrm{DS}}$  is the voltage from drain to source

$I_{DS}$  is the current from drain to source

$\stackrel{-}{\mu}_p$  is the average surface mobility of holes and units are in  $$cm^2/V\mbox{-sec}$$

$\epsilon_{ox}$  is the oxide dielectric constant: assumed as 1/3pf/cm

t is the oxide thickness (1200 Å)

W is the channel width (perpendicular to current flow)

L is the effective channel length in the direction of current flow

Defining two parameters K and K' such that

$$K = K' \frac{W}{I}$$

$$K' = \frac{\frac{\mu}{p} \cdot ox}{2t}$$

The above Eqs. (1) and (2) become

$$I_{DS} = K[2(V_{GS} - V_T)V_{DS} - V_{DS}^2]$$

(3)

for a non-saturated region, and

$$I_{DS} = K[V_{GS} - V_T]^2$$

(4)

for a saturated region.

The value of K in the above equation is determined by certain process constants which may be lumped together and called K', and the ratio of the width W and the length L of the device channel. Since the resistance of a device is inversely proportional to its K value, a large ratio of

$$\frac{K_{I}}{K_{L}} = (W_{I}/L_{I})/(W_{L}/L_{L})$$

(5)

(where  $K_{I}$  and  $K_{L}$  are the process constants of the inverter and the load, respectively) is equivalent to a large load resistance. Most of the voltage is then dropped across the load, and the output zero level is low. In general, the lower the output zero level requires for given "1" input, the larger the ratio of  $K_{I}/K_{L}$  must be.

The "gain" parameter of the MOSFET is the forward transfer-conductance ratio. This expresses the output-current variation for an input voltage variation. Therefore, transconductance is defined as the ratio of a small variation in the drain current to the variation in gate voltage which produces the current, and is symbolized as  $\mathbf{g}_{\mathbf{m}}$ .

Mathematically, this can be written as (4, p. 53)

$$g_{\mathbf{m}} = \frac{\partial I}{\partial V_{\mathbf{G}}} \Big|_{V_{\mathbf{D}}}$$

(6)

which is determined in the active operating region, the saturated region.

Differentiating the Eq. (6) yields

$$\frac{\partial (I_D)}{\partial V_G} = \frac{\partial K(V_{GS} - V_T)^2}{\partial V_{GS}} = 2K(V_{GS} - V_T)$$

(7)

where

$$I_D = K(V_{GS} - V_T)^2$$

This expression tells that  $g_m$  is directly proportional to the ratio of W/L, and also to the voltage  $(V_{GS}-V_T)$ . Thus  $g_m$  can be varied in one of two ways. First, the gate bias  $V_G$  may be varied, or second, the geometry of the device may be varied. Another

parameter which is of interest to the switching device application is the resistance  $R_{on}$  of the device when it is turned on and operated in the non-saturated regions.

$$R_{on} = \frac{\partial V_{D}}{\partial I_{D}} |_{V_{GS}} = \frac{1}{K[2(V_{GS} - V_{T}) - 2V_{DS}]}$$

(8)

In the non-saturated region, the characteristic curves of MOS are nearly linear, thus this expression can be approximately rewritten when  $V_{DS}$  goes to 0.

$$R_{on} \approx \frac{1}{2K(V_{GS}-V_{T})} = \frac{1}{g_{m}}$$

(9)

And for load device,  $R_{L}$  is expressed as (4, p. 90)

$$R_{L} = \frac{2}{g_{mL}}$$

(10)

## Threshold Voltage

The threshold voltage expression is as follows (4):

$$V_{T} = \frac{Q_{SS}^{+Q}D}{C}$$

(11)

where

$Q_{SS}$  = effective surface-state charge density per unit area.

$\mathbf{Q}_{\mathrm{D}}^{}$  = bulk charge per unit area associated with the channel

depletion region.

C = capacitance of the gate to channel per unit area  $\frac{\epsilon}{\text{ox}} / \text{t}$ .

Physically,  $V_{\rm T}$  is the gate voltage required to neutralize, in effect, the immobile charge above and below the channel region. The charge above the channel is  $Q_{\rm SS}$ , while the charge below the channel consists of that within the depletion region located in the bulk.

Depletion-region charge  $Q_{\overline{D}}$  is derived from an application of the simple P-N junction theory, where the number of charge carriers in the channel is much greater than that of the substrate.

$Q_{D}^{-1} = \text{depletion-region thickness}$   $(X_{D}^{-1})$  substrate charge density

$$= \sqrt{\frac{2\epsilon_S \phi_S}{qN}} \ qN$$

where

$\phi_{\mathbf{F}}$  = Fermi function; the amount of the fermi level which is displaced from the intrinsic level, and the unit is expressed in volts.

$\phi_{\mathbf{S}}$  = surface potential

$$\phi_{S} = 2\phi_{F}$$

$Q_{D} = \sqrt{q\epsilon_{S}N} \sqrt{2\phi_{F}}$

where

$N = N_D$  for an N-type substrate device (P-channel)

$N = N_A$  for a P-type substrate device (N-channel)

The voltage on the gate necessary to support this charge from Eq. (11) is

$$V_{I_{T}} = + \frac{Q_{D}}{C} = -K_{1}$$

(12)

where  $K_1 = \pm (t_{ox}/\epsilon_{ox})\sqrt{q\epsilon_S N}$  (+ for P-channel, - for N-channel)

Equation (12) might be considered an "intrinsic" threshold voltage for a "perfect" device with zero surface-state charge density  $(Q_{SS} = 0).$  This will be of the enhancement-mode type with a low threshold voltage equal to  $V_{TT}$ .

The surface-state charge  $\,^{Q}_{SS}\,^{}$  is assumed to be constant and to lie close to the silicon-oxide interface. The bulk charge  $\,^{V}_{SS}\,^{}$  is

$$V_{SS} = -\frac{Q_{SS}}{C} = -\frac{t_{ox}}{\epsilon_{ox}} Q_{SS}$$

(13)

$Q_{SS}$  is generally an ionized donor and thus acts as a positive charge center, giving  $V_{SS}$  a negative sign in Eq. (13).

The total threshold voltage is the algebraic sum of the intrinsic threshold voltage and that due to surface states. From Eqs. (12) and (13)

$$V_{T} = V_{T} + V_{SS}$$

(14)

$$V_{T} = -K_{l} \sqrt{\phi_{S}} + V_{SS}$$

(15)

where

$$K_{1} = \pm (t_{ox}/\epsilon_{ox})\sqrt{2q\epsilon_{S}N}$$

$$\phi_{S} = 2\phi_{E}$$

For typical values where  $N_D = 10^{15}$ ,  $t_{ox} = 1500 \text{ Å}$ ,  $\epsilon_{ox} = 1/3 \text{ pf/cm}$  Fermi potential.

$$V_{IT} = -0.6 V,$$

and

$$V_{SS} = -2.88 \text{ V}.$$

Therefore, the resultant total threshold voltages for a P-channel device and for an N-channel device are -3.48 V and -2.28 V, respectively.

In this paper, the threshold voltage will be assumed to be -5 V.

#### Back Gate Bias

When a bias is applied to the substrate, modulation of the channel conductance results. Thus the substrate can act as a second gate, and in fact, is sometimes referred to as the back gate. Because a P-N junction is formed with the source and drain diffusions to the substrate, some of its characteristics tend to be more like the gate of a junction FET than the gate of an insulated device.

The theory of operation of the back-gate bias can be explained by an extension of the insulating depletion region layer into the substrate. As the reverse bias on the substrate increases, the depletion region extends further into the substrate as mobile electrons are depleted and imobile holes are decreased, just as in the P-N junction theory. For a fixed gate voltage, there will now be less mobile channel charge, and therefore a decrease in conduction.

The expression for the threshold voltage as a function of the backgate bias can be written directly from Eq. (15). It is assumed that all the applied voltage will appear across the depletion region and none across the bulk semiconductor. A polarity of back gate bias  $V_{\mbox{BG}} \quad \mbox{is assumed such that when the substrate is reverse-biased with respect to the source,} \quad V_{\mbox{BG}} \quad \mbox{and} \quad \mbox{$\phi_S$} \quad \mbox{have the same polarity.}$  These will give the following results (4):

$$V_{T} = -K_{1} \sqrt{\pm (\phi_{S} - V_{BG})} + V_{SS}$$

(16)

where

$$\phi_{\mathbf{S}} = 2\phi_{\mathbf{F}}$$

It is often convenient to express  $V_T$  in terms of a fixed value (where  $V_{BG} = 0$ ) plus a variable term  $\Delta V_T$ , which is a function of  $V_{BG}$ . The following analysis derives  $\Delta V_T$  by starting with Eq. (15)

$$V_{T}(V_{BG}) = V_{SS} - K_{1} \sqrt{2\phi_{F}^{+}V_{BG}^{-}}$$

$K_1^{\sqrt{2\varphi_F}}$  is added and subtracted to the right-hand side of the equation:

$$V_{T}(V_{BG}) = V_{SS} - K_{l}\sqrt{2\phi_{F}} + K_{l}\sqrt{2\phi_{F}} - K_{l}\sqrt{2\phi_{F}}+V_{BG}$$

$$V_{T}(V_{BG}) = V_{T} + \Delta V_{T}$$

(17)

so that

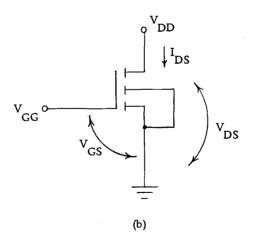

$$\Delta V_{T} = -K_{I} \left( \sqrt{2\phi_{F} + V_{BG}} - \sqrt{2\phi_{F}} \right)$$

(18)

This result is plotted in Figure 2.

#### Capacitance

Two kinds of capacitance will be associated with the MOS device. One is the oxide capacitance, and the other is the capacitance of the silicon P-N junction which is due to the depletion region.

The oxide capacitance is due to evaporating a metal electrode over the oxide and using this electrode and the semiconductor as the parallel plates of a capacitor whose dielectric is the oxide. It may be determined solely from geometry, and is given by (4)

$$C_{\text{ox}} = \frac{\epsilon_{\text{ox}}}{t} \cdot A \tag{19}$$

where  $\epsilon$  is the dielectric constant of silicon oxide, and t is the thickness of the silicon oxide.

The overlap thick oxide capacitance due to the gate overlapping into the drain and source areas will be considered by the above expression.

Figure 2. Threshold voltage variation vs. back-gate bias (4).

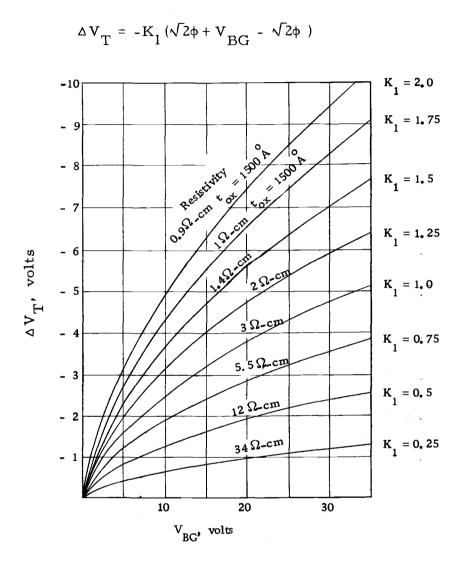

The P-N junction capacitance is related to the back-bias diffused junctions of the drain and source. With increasing voltage the depletion region widens, resulting in a decrease in the depletion capacitance. Its reverse bias voltage vs. capacitance relation is given by the formula (1).

$$C = \frac{0.08}{\sqrt[3]{0.6 + V_R}} \, \text{pf/mil}^2$$

(20)

where  $V_R$  is the amount of the reverse bias voltage. The above expression is plotted in Figure 3.

#### MOS Inverter

The MOS inverter circuit is a basic building block of digital subsystem. A common inverter circuit with an MOS as a load resistor configuration is shown in Figures 4 and 5 (10).

The basic DC inverter consists of a switch tied to the ground and a load-resistor tied to the power supply. The negative voltage above the threshold voltage  $V_{T}$  to the P-channel device applied to the gate turns the device on and pulls the output voltage  $V_{DD}$  near to the ground. In the  $2\phi$  technique, the resistor is clocked on for a convenient period of time. The clock can also be used to sample and hold the inverter information onto a storage capacitor.

The theoretical expression for the voltage characteristics of an

Figure 3. P-diffusion capacitance vs. reverse bias voltage (1).

Figure 4. Turn-on case of an MOS inverter.

Figure 5. Turn-off case of an MOS inverter.

MOS inverter device and its associated load will be developed.

The analysis will be progressed for two different types of loads:

(1) an MOS device biased in the saturated mode; and (2) an MOS device biased in the non-saturated mode.

From Figure 4 it is obvious that

$$V_{GS} = V_{IN}$$

$$V_{DS} = V_{o}$$

The current in the inverter can be found by substituting the above equations into equations (3) and (4)

$$I_{T} = K_{T}(V_{TN} - V_{T})^{2}$$

(21)

for the condition of the saturated region, and

$$I_{I} = K_{I}[2(V_{IN} - V_{T})V_{O} - V_{O}^{2}]$$

(22)

for the condition of the non-saturated region.

#### Power Consumption of the MOS Inverter

The DC power consumption of the MOS inverter in each stage is associated with the drain current flow  $\ I_D$ . Therefore, the expression in the saturation region is

$$p = V_{DD} \cdot I_{D}$$

$$= V_{DD} K(V_{CS} - V_{T}) \quad \text{watts.}$$

(23)

In the non-saturated region, the DC power expression is

$$p = V_{DD}^{K(2(V_{GS} - V_{T})V_{DS} - V_{DS}^{2})}$$

(24)

When the complementary MOS devices are used, power is dissipated only during the switching interval.

#### Transient Response and Switching Time Consideration

The following discussion for an MOS load device whose substrate is returned to the source terminal can be used to determine the "worst case" conditions of a grounded substrate in an actual IC case.

They are as follows:

#### Load Device, Substrate Common to Source, Saturation Region

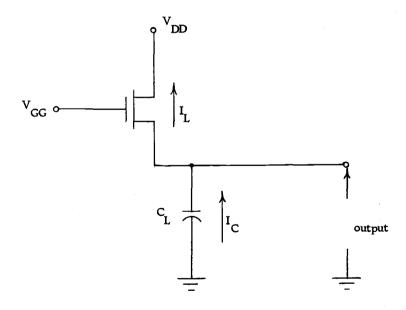

It is generally desirable to use an MOS as a load resistor in ICs. Figures 6 and 7 show how a device can be biased as a load, and illustrate the load's non-linear characteristics superimposed upon the output curves of the driver device (4, p. 78-83).

Figure 6 is arranged to discuss the switching time of these load devices. The driver device is turned on, allowing  $C_L$  to discharge completely. Tl is then switched off, thus effectively removing it

Figure 6. Inverter circuit using an MOS load and its equivalent circuit (4).

Figure 7. MOS load line and linear-resistor characteristic superimposed upon the driver characteristic (4).

from the circuit and allowing the MOS load to charge  $\,^{\rm C}_{\rm L}$ . T1 is assumed to have zero storage time. The current charging  $\,^{\rm i}_{\rm C}_{\rm L}$  is not a constant, and is a function of the voltage across  $\,^{\rm C}_{\rm L}$ . Because the load gate is returned to the drain and the device is assumed to be an enhancement-mode device, the operation is in the saturation region, and the biasing must satisfy the condition that

$$|\mathbf{v}_{GG} - \mathbf{v}_{T}| \le |\mathbf{v}_{DD}|$$

From Figure 6,

$$V_{GS} = V_{GG} - v(t)$$

(25)

$$V_{DS} = V_{DD} - v(t)$$

(26)

The theoretical expression for the current in the saturated device is

$$I_{L} = K_{L} (V_{GS} - V_{T})^{2}$$

(27)

and the capacitor current  $i_{C}$  is

$$i_{C_{L}} = C_{L} \frac{dv(t)}{dt}$$

(28)

The drain and capacitor  $C_L$  current are equated and yield

$$C_{L} \frac{dv(t)}{dt} = K_{L} \left[ V_{GG} - v(t) - V_{T} \right]^{2}$$

(29)

where v(t) is the capacitor output voltage.

Solving the equation for v(t) gives the time response for the MOS load and capacitor combination:

$$\frac{\mathbf{v}(t)}{\mathbf{V}_1} = \frac{\mathbf{t}/\mathbf{T}}{2+\mathbf{t}/\mathbf{T}} \tag{30}$$

where

$$V_{1} = V_{GG} - V_{T}$$

$$T = C/g_{m}$$

$$g = -2K(V_{GG} - V_{T})$$

Equation (30) is plotted in Figure 8.

This result is not an exponential the same as an R-C network, but it is still comparable.

This is an expected characteristic for the MOS, since as the output voltage across  $C_L$  increases toward  $V_{GG}$  -  $V_T$ , the MOS delivers less and less charging current to  $C_L$ . When the v(t) increases, the voltage across R decreases, thus naturally decreasing the current across  $C_L$ . This is analogous to a capacitor being charged by a nonlinear resistor whose resistance value increases as a function of capacitor voltage (see Figure 6). The speed of the circuit in Figure 8 is calculated to be approximately 18 T.

## Load Device, Substrate to Source, Triode Region

The higher the gate voltage, the more linear the load V-I

characteristics become, as shown in Figure 7. In the limit as  $V_{GG}$  approaches to infinity, the switching characteristic of a fixed resistor will be 2.27, whose speed is that of the R-C network.

This result will be analyzed by equating the capacitor and device current, which is in the non-saturated region. The biasing parameter must satisfy the condition that

$$|\mathbf{v}_{GG} - \mathbf{v}_{T}| \ge |\mathbf{v}_{DD}|$$

The theoretical expression for the current in this region is

$$I_{L} = -K_{L} \left[ 2(V_{GS} - V_{T})V_{DS} - V_{DS}^{2} \right]$$

(31)

and the capacitor current  $i_{C_{T}}$  is

$$i_{C_{L}} = C_{L} \frac{dv(t)}{dt}$$

(32)

Substituting Eqs. (25) and (26) into Eq. (31) yields

$$I_{L} = -K_{L} \left[ 2(V_{GG} - v(t) - V_{T})(V_{DD} - v(t)) - (V_{DD} - v(t))^{2} \right]$$

(33)

Equating Eqs. (32) and (33), then it becomes

$$C_{L} \frac{dv(t)}{dt} = -K_{L} \left[ 2(V_{GG} - v(t) - V_{T})(V_{DD} - v(t)) - (V_{DD} - v(t))^{2} \right]$$

(34)

Rearranging the terms yields

$$-\frac{C_{L}}{2K_{L}(V_{GG}-V_{T})}\frac{dv(t)}{dt} = V_{DD} - v(t) + \frac{v(t)^{2}-V_{DD}}{2(V_{GG}-V_{T})}$$

(35)

By dividing both sides by  $V_{DD}$ , using  $g_{m} = -2K(V_{GG} - V_{T})$ , and introducing parameter  $m = V_{DD}/V_{GG} - V_{T}$ , which is the biasing parameter, the following normalized differential equation is obtained:

$$\frac{C}{g_{m}} \frac{d[v(t)/V_{DD}]}{V_{DD}} = 1 - \frac{v(t)}{V_{DD}} + \frac{1}{2} \left[ \left( \frac{v(t)}{V_{DD}} \right)^{2} - 1 \right] m$$

(36)

Letting  $C/g_{m} = T$  and separating the variables yield

$$\int_{0}^{t} \frac{dt}{\tau} = \int_{0}^{v(t)/V_{DD}} \frac{d[v(t)/V_{DD}]}{\frac{1}{2}m[v(t)/V_{DD}]^{2} - [v(t)/V_{DD}] + (1 - \frac{1}{2}m)}$$

(37)

The integration of Eq. (37) is the relation between the normalized output voltage and the normalized time. The final result becomes

$$\frac{v(t)}{V_{DD}} = \frac{(2-m)[1-e]}{-(\frac{t}{\tau})(1-m)}$$

$$\frac{v(t)}{V_{DD}} = \frac{(2-m)[1-e]}{-(\frac{t}{\tau})(1-m)}$$

$$2-m[1+e]$$

(38)

The above equation is plotted in Figure 9, where the normalized voltage parameter m results in a family of curves. The parameter m varies from 0 to 1 for the case which  $V_{GG}$  approaches infinity and  $V_{DD} \geq V_{GG} - V_{T}$ , respectively. When m = 1,

Figure 8. Switching time response of an MOS in the saturation region, with an R-C network for comparison (4).

Figure 9. Switching time response of an MOS load in the triode region (m = 0 to m = 1) (4).

Eq. (38) can be reduced by the use of L'Hospital's rule to Eq. (30).

$$\lim_{m \to 1} \frac{(2-m)[1-e^{-(\frac{t}{T})(1-m)}]}{-(\frac{t}{T})(1-m)}$$

$$= \lim_{m \to 1} \frac{(-1)(1-e^{-(\frac{t}{T})(1-m)})}{(-1)(1-e^{-(\frac{t}{T})(1-m)})+(2-m)(-e^{-(\frac{t}{T})(1-m)})}$$

$$= \lim_{m \to 1} \frac{(-1)(1-e^{-(\frac{t}{T})(1-m)})}{(-\frac{t}{T})(1-m)}$$

$$= \frac{-\frac{t}{T}}{-2-\frac{t}{T}} = \frac{\frac{t}{T}}{2+\frac{t}{T}}$$

(39)

Above results come out the same as those of Eq. (30), which say that the device is now operating in the saturation region with a 18 T switching time.

## Load Device, Substrate Common to Ground

This is the actual transient case for the IC case. Eq. (38) shows the switching characteristic to be dependent upon T and T both of which are functions of T. Also, the variation of T is due to the output voltage (back gate bias) for the ground substrated configuration. Therefore, in this case, T and T must be rearranged to represent the threshold voltage variation.

$$\mathbf{m} = \frac{\mathbf{v}_{DD}}{\mathbf{v}_{GG} - (\mathbf{v}_{T} + \Delta \mathbf{v}_{T})}$$

$$\tau = \frac{c_L}{-2K[v_{GG} - (v_T + \Delta V_T)]}$$

(40)

and

$$g_{m} = 2K[V_{GG} - (V_{T} + \Delta V_{T})]$$

Notice in Eq. (40) that as  $\ \Delta V_{\mbox{$T$}}$  increases, the terms  $\mbox{$m$}$  and  $\mbox{$T$}$  also increase. By using these properties, one can approach the "worst-case" design.

This result is particularly evident at the lower gate voltage, where  $\Delta V_{\rm T}$  causes a larger percentage of change in m and T than at the higher voltages.

## Comparison of Two Types of 2¢ Dynamic Shift Register

There are two types of dynamic shift register circuits. These are: the ratio type, which has a large geometry ratio between load and inverter devices and the ratioless type, which has the same geometry size on both load and inverter devices. The following explanation tells the differences.

## Ratio Type Circuit Operation

The earliest ratio type of the two-phase delay stage is shown in Figure 10 (4). This circuit functions as follows: with a logic "1" fed

Figure 10. Two-phase dynamic shift register schematic (ratio type).

into the input at node A, transistor Tl turns "ON" allowing node B to discharge to ground. During clock  $\phi_1$ , T2 and T3 turn "ON", allowing the charge that was previously stored on the node C to discharge through Tl and T3. It must be pointed out that, in order for node B to obtain an adequate logic "0" level, a resistance ratio of at least 10 to 1 is required between transistors TlТ2. and This implies that the physical geometry of Tl must be much larger than that of T2, which in turn greatly increases the physical size of these two elements. Furthermore, when  $\phi_2$  goes negative, T6 turn "ON"; however, since the gate of T4 is at a logic "0" level, nodes D and E are allowed to charge to a logic "1" level. If, however, node C was at a logic "l" level and clock  $\phi_2$  goes negative, T4, T5 and T6 turn "ON", allowing the charge stored on nodes D and E to discharge to a logic "0" level. To insure an adequate "0" level at node D and E, the resistance ratio of T4 and T5 must be at least 10 to 1 or greater for the circuit to operate correct-The need for a resistance ratio between load and inverter devices T2, T3 and T5, T6 greatly increases the cell area and in turn effectively reduces the maximum operating speed of the devices.

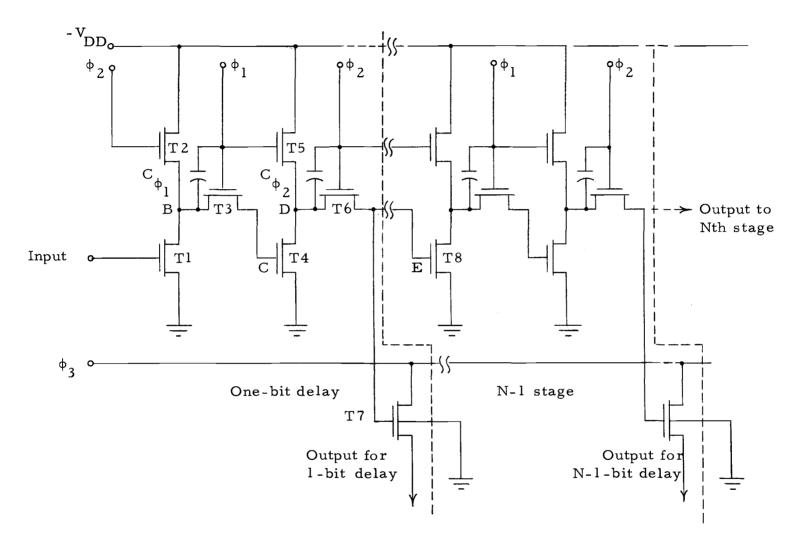

## The Ratioless Type Circuit Operation

The ratioless type circuit which is shown in Figure 11 is somewhat similar to that of Figure 10 (14).

Figure 11. Two-phase dynamic shift register schematic (ratioless type).

The difference is that clock  $\phi_1$  drives a coupling transistor in addition to the load resistor of the following inverter stage rather than the previous load devices as in Figure 10. Likewise,  $\phi_2$  drives coupling transistor T7 and the load of the following inverter stage T9. Each delay stage consists of two inverters in conjunction with a clocked load register followed by two coupling devices T4 and T7. The concept of operation is such that information is clocked from one stage to the next, where it is temporarily stored on the inherent nodal capacitance associated with each MOS transistor. Alternate stages are clocked by clock  $\phi_1$  and  $\phi_2$ , respectively. As can be seen from the timing diagram, Figure 12, the sequence of operation is as follows: if a logic "1" level is present at the input during  $\phi_2$  time, both T1 T3 turn "ON", allowing the voltage at node B to assume a value which is determined by the ratio of the load and inverter devices respectively. Since both T2 and T3 are almost the same minimum geometry devices, the "ON" resistance of the load and inverter are approximately equal, thus placing node B at  $V_{\mathrm{DD}}^{\prime}/2$ . However, when clock  $\phi_2$  returns to ground (logic "0" level), T3 turn "OFF", storing a "1" level at node A, allowing to remain in the "ON" state, thus continuing to discharge node B to a logic "0" level. When clock  $\phi_1$ , goes negative (logic "1" level), T4 and T6 turn "ON", allowing previous information stored at

Figure 12. Timing diagram of each mode point for the ratioless type of dynamic shift register.

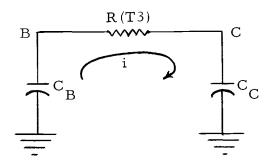

node C to discharge through T4 and T2, placing it at a logic "0" level. The energy coupled into node B through the intentionally added capacitance  $C_{\phi_1}$  is discharged to the ground through T2. Because the logic level at node C is "0", T5 is in the "OFF" state, allowing T6, which is in the "ON" state, to charge node D to  $V_{DD}$ . When clock  $\phi_1$  returns to the ground (logic "0" level), T4 and T6 turn "OFF", allowing node C to remain at a logic "0" level. Likewise, the "1" level developed at node D is temporarily stored on the node capacitance  $(C_D)$ . Again, when clock  $\phi_2$  goes negative (logic "1" level), T7 and T9 turn "ON", electrically connecting nodes D and E, allowing the voltage at node D to seek a level determined by the ratio of  $C_D$  and  $C_E$ .

Simultaneously, the energy which is coupled through the overlap capacitance  $C_{\varphi_2}$  during  $\varphi_2$  increases the voltage level at node E by a capacitance ratio established by  $C_D$ ,  $C_E$  and  $C_{\varphi_2}$ . Note that the capacitance  $C_B$ ,  $C_C$  and  $C_{\varphi_1}$  and  $C_D$ ,  $C_E$  and  $C_{\varphi_2}$  will be chosen such that the resultant voltage at its respective nodes exceeds the threshold voltage level of each inverter stage. The signal at node E is used to drive another stage or several stages to produce a series of shift register cells.

To summarize the circuit operation: during the time that  $\phi_2$  is negative, each stage will read its input and store that input (inverted) at its respective nodes. When  $\phi_1$  is negative, the stored

information from the previous stage is inverted and transferred to the following stage, thus providing a one-bit delay. In other words, information at A appears at E delayed by one clock period.

According to the above explanation for the two types of circuit, the ratioless type circuit is able to function with the use of all minimum geometry devices, since its driver-device geometry size is almost the same as its load size. This similarity allows a substantial reduction of both the cell size and the intrinsic capacitance of each node, thus permitting the cell to operate at a higher frequency. The power consumption is much lower than in most two-phase systems, since the smaller the size, the larger the turn-on resistance, allowing less current flow during the transition period.

# Addressing Circuit Using Dynamic Shift Register

An addressing circuit was designed and is shown in Figure 14.

Operation is as follows: according to the above operation of the dynamic shift register chain in which the first is coupled to the second, the second to the third, and so on, the logical input information will be delayed a certain amount of time.

Consider a chain with N stages. If the time interval between pulses is T, then the output from any stage is a pulse train of period NT, with each pulse of duration T. The output pulse of one stage is delayed by a time T from a pulse in the preceding stage.

In other words, the information is addressed in a certain specific location where the data should be stored in a memory.

By connecting the amplifying device at the end of each stage, the delayed information can be ready to be used in a certain location. When the  $\phi_3$  is clock pulses, which are different from those of the  $\phi_1$  and  $\phi_2$  clock, it may control the only desired address line during its delay function. Otherwise, the information is delayed on all output lines. The functional clock diagram is presented in Figure 13.

Figure 13. Functional block diagram showing address line connections.

Figure 14. Two-phase, N-bit delay, addressing circuit.

#### III. DESIGN METHODS

### Design Calculations

This circuit will be designed for "worst-case" conditions.

The conditions are:

# High Temperature

The hole mobility  $\mu_p$  is a function of temperature which decreases with increasing temperature; therefore  $I_L$  decreases with increasing temperature. A lower charge current results in lower speed.

# Low V<sub>DD</sub>

With a lower  $\ensuremath{V_{DD}}$ ,  $\ensuremath{C_L}$  charges to a smaller final voltage, and therefore takes longer to reach the voltage to turn on the next device.

# Low V<sub>GG</sub>

From Eq. (40), a low  $V_{\mbox{GG}}$  means a higher value of m, and therefore switching time will be slower.

# High V<sub>T</sub>

$\begin{array}{ccc} & \text{High} & \text{$V_{\rm T}$} & \text{means less effective gate drive voltage, and again,} \\ & \text{less speed.} \end{array}$

The design parameters are determined as follows:

$$V_{DD} = -12 V$$

$$V_{T} = -5 V$$

$$V_{in} = -11 V$$

$$\phi_{1} = \phi_{2} = -20 V$$

$$\phi_{3} = -12 V$$

$$t \text{ oxide} = 1200 \text{ Å (gate area)}$$

$$F_{\phi} = 1 \text{ MHz}$$

$$V_{o} = -6 V$$

$$I_{o} = 3 \text{ ma}$$

where

${

m ^{V}_{DD}}$  is drain supply voltage

$V_{\overline{GG}}$  is gate supply voltage

V is data input voltage

$\phi$  is clock input voltage

t oxide is the thickness of oxide under the gate

V is final out-put voltage

I is output current level

As the voltage range for a logic "1" is from -8 V to -12 V, any input voltage within this range will turn on an inverter. Because the voltage range for a logic "0" is 0 V to -3 V, any input voltage within this range will turn off an inverter (see Appendix B).

Also, it may be assumed that the threshold voltage range is from -3 V to -5 V to satisfy the above input voltage ranges.

Thus the capacitance values from Eq. (19) are

1) Thin oxide (oxide thickness 1200 Å)

$$\frac{\epsilon_{\text{ox}}}{t} = 0.19 \text{ pf/mil}^2 \approx 0.2 \text{ pf/mil}^2$$

2) Thick oxide (oxide thickness 8000 A)

$$\frac{\epsilon_{\text{ox}}}{\epsilon_{\text{ox}}} = 0.03 \text{ pf/mil}^2$$

3) Junction capacitance  $C_{diff} = 0.05 \text{ pf/mil}^2$ .

The threshold voltage variation  $~\Delta V_{\rm T}~$  is -2 V, since the starting material resistivity is ~7 -  $10\,\Omega$  cm (see Figure 3).

The geometrical size will be determined from the output device T7, whose substrate is grounded. It is assumed that the output current is needed 3 ma; therefore the turn-on resistance for the output device is approximately 2.5 K $\Omega$ . The resultant transconductance for the output device will be 400  $\mu$ mhos.

From Eq. (40)

$$g_{m} = 2K(V_{GG} - (V_{T} + \Delta V_{T}))$$

$$\frac{W}{L} = \frac{2 \frac{\epsilon_{ox}}{t_{ox}} \mu_{p} [V_{GG} - (V_{T} + \Delta V_{T})]}{g_{m}}$$

$$= \frac{(5)(10^{-6})(11 - 7)}{(400)(10^{-6})}$$

$$\approx 20$$

And this device is in the saturated region, since it satisfies the condition  $V_{GS}$  -  $V_{T}$  <  $V_{DD}$ , 11 - 7 < 12.

Capacitance calculation over the thin oxide gate area will be developed as follows:

- 1) Geometrical channel length is 0.4 mil

- 2) Side diffusion is 0.1 mil for both diffused areas

- 3) Actual device channel length is 0.3 mil.

Using an actual length of 0. 3 mil yields a width of 6 mil for a W/L ratio of 20.

From Eq. (19) and Eq. (20), the sum of the capacitance for the output device which is due to the gate area, the diffused area and the thick oxide region for the output terminal is approximately 1.38 pf, since the gate area capacitance is

0.

$$2 \text{ pf/mil}^2 \times 0.4 \text{ mil} \times 6 \text{ mil} = 0.48 \text{ pf},$$

the diffused junction capacitance is

0.05

$$pf/mil^2 \times 6 mil^2 = 0.3 pf$$

and the thick oxide capacitance is

0. 03

$$pf/mil^2 \times 20 mil^2 = 0.6 pf$$

Charging node D with  $C_{\phi_2}$  added at t=0 when the  $\phi_1$  clock has just turned on,  $V_D^{(0)}$  float -12 V, and  $V_D^{(0^+)}$  will be

$$V_D(0^+) = -12 V(\frac{C_{\phi_2}}{C_D^{+C_{\phi_2}}})(-20)$$

Choosing  $C_{\phi_2} = 1.2 \text{ pf}$ ,  $C_D = 0.6 \text{ pf}$ , since the  $C_{\phi_2} + C_D$  should be greater than  $C_E$ , so that the final voltage for node D should be great enough to turn on the next device.

Then

$$V_D(0^+) = -12 V + (\frac{(-20)(1.2)}{1.8}) = -12 - 12.5 V = -24.5 V$$

From Eqs. (13) and (14) in Appendix A

$$V_{E}(t) = V_{D}(0^{+}) \frac{C_{D}^{+}C_{\phi_{2}}}{C_{D}^{+}C_{\phi_{2}}^{+}C_{E}} \left[1 - e^{-\frac{C_{D}^{+}C_{\phi}^{+}C_{E}^{-}}{RC_{E}(C_{D}^{+}C_{\phi_{2}^{-}})}} t\right]$$

$$V_{D}(t) = -V_{D}(0^{+}) \frac{C_{D}^{+}C_{\phi_{2}}}{C_{D}^{+}C_{\phi_{2}}^{+}C_{E}} + V_{D}(0^{+}) \left(\frac{C_{D}^{+}C_{\phi_{2}}}{C_{D}^{+}C_{\phi_{2}}^{+}C_{E}} - 1\right) e^{-\frac{C_{D}^{+}C_{\phi_{2}}^{+}C_{E}}{RC_{E}(C_{D}^{+}C_{\phi_{2}})} t$$

$$V_{E}(t) = (-24.5)(0.6)(1-e^{-\frac{t}{0.6RC_{E}}})$$

since

$$\frac{{}^{C}_{D}^{+C}_{\phi_{2}}^{+C}}{{}^{C}_{D}^{+C}_{\phi_{2}}^{+C}_{E}} = \frac{1 \cdot 8}{3} = 0.6$$

$$-\frac{t}{0.6 RC_{E}}$$

$$= -15(1-e)$$

Solving for the time  $\,t\,$  which is required to charge up the node E to -11 V,

$$-\frac{t}{0.6RC_{E}}$$

-11 = -15(1-3)

$$t = 0.78RC_{E}$$

At this time  $V_{D}(t)$  is

$$V_{D}(t) = (-25)(0.6) + 25(0.4)e$$

$$= -15 - 10(e^{-1.3}) = -17.7 \text{ V}$$

R for T6 device will be derived from this t value, which is 10 nsec or less because of necessity of faster switching time.

Choosing t = 3 nsec,  $R_{on}$  will be

$$R_{on} = \frac{3 \times 10^{-9}}{0.78 \times 1.4^{-12}} = 2.7 \text{ K}.$$

T6 is saturated since it satisfies the condition

$$V_{GG} - (V_T + \Delta V_T) < V_{DD}, -20 + 7 < 17.7$$

Therefore

$$\left(\frac{W}{L}\right)_{T6} = \frac{1}{2K(V_{GG} - (V_{T} + \Delta V_{T})(R_{on}))}$$

$$= \frac{1}{(5)(10^{-6})(13)(2.7)(10^{3})}$$

$$= 6$$

To make  $g_{m}$  large enough to ensure faster switching and better conduction, a somewhat larger value was used in this design. Therefore,

$$\left(\frac{W}{L}\right)_{T6} = 10$$

From Eq. (40)  $g_{m}$  will be

$$g_{m} = 2K(V_{GS}-(V_{T}+\Delta V_{T})$$

$$= 150 \mu \text{mhos at } V_{GS} = -10 \text{ V}$$

The load device T5 is non-saturated, since it satisfies the condition  $V_{GG}$  -  $(V_T + \Delta V_T) > V_{DD}$ , 20 - 7 > 12. And from Eq. (40) the

biasing parameter m will be

$$m = -\frac{-12}{(-20+6)} = \frac{-12}{-14} = 0.9$$

Therefore, eight time constants are required to reach 90% charge for  $C_{\phi_2} + C_D = 1.6 \text{ pf}$  from Figure 9.

$$t = 8 RC_{E}$$

Choosing t = 200 nsec or less, since the clock pulse width is 300 nsec,  $R_{T}$  will be

$$R_L = \frac{(200)(10^{-9})}{(12.8)(10^{-12})} \approx 16 \text{ K}$$

where  $R_{T}$  is resistance for load device T5 from Eq. (9)

$$g_{m} = \frac{2}{R_{T}}$$

Therefore

$$(\frac{W}{L})_{T5} = \frac{2}{2K(V_{GG}^{-}(V_{T}^{+} \Delta V_{T}^{-}))R_{L}}$$

$$= \frac{2}{(16)(10^{3})(13)(5)(10^{-6})} = 1.0 = 2$$

$$g_{m} = 30 \ \mu \text{mhos}$$

when the gate voltage is -10 V. The inverter device T4 changes

from saturated into non-saturated operation.  $t_f$  is the time required to discharge  $C_L = C_{\varphi} + C_D$  to 10% of  $v_{\varphi}$ , the off-level voltage and t' is the time required that the T4 device changes from saturated into non-saturated operation.

For  $0 \le t \le t'$ , T4 is saturated. Combining Eqs. (27) and (28), then

$$C_L \frac{dv_o}{dt} = K(V_{GS} - V_T)^2$$

$$\frac{C_{L}}{K(V_{GG}-V_{T})^{2}} \int_{-11}^{-5} dv_{o} = \int_{0}^{t'} dt$$

$$t' = \frac{C_L}{6^2 K} (11-5)$$

$$= \frac{6C_L}{36K}$$

For  $t' \le t \le t_f$ , T4 is non-saturated.

Combining Eqs. (31) and (32), then

$$C_{L} \frac{d v_{o}}{dt} = K[2(V_{GS} - V_{T}) v_{o} - v_{o}^{2}]$$

$$\int_{-6}^{-1.2} \frac{dv_{o}}{-v_{o}^{2}+12v_{o}} = \frac{L}{C_{L}} \int_{t'}^{t_{f}} dt$$

$$t_{f} - t' = -\frac{C_{L}}{6K} \tanh^{-1} \left( \frac{-v_{o}^{-6}}{6} \right) \Big|_{-6}^{-1.2}$$

$$= -\frac{C_{L}}{6K} (-1.1)$$

$$t_{f} = \frac{1.1C_{L}}{6K} + \frac{6C_{L}}{36K}$$

$$= \frac{12.6C_{L}}{36K}$$

Assuming  $t_f = 100$  nsec for a faster fall time, then W/L ratio of T4 is

$$\left(\frac{W}{L}\right)_{T4} = \frac{(1.8)(10^{-12})(12.6)}{(36)(2.5)(10^{-6})(100)(10^{-9})}$$

= 2.5

$$g_{m} = 40 \ \mu \text{mhos}$$

From Eq. (19), the capacitance for this device which is due to the gate area is approximately 0.05 pf, the diffusion capacitance due to the diffused junction 0.02 pf and aluminum contact thick oxide capacitance 0.03 pf. Therefore total capacitance will be approximately 0.1 pf.

Performing the same procedure as the nodes D and E, the capacitances  $C_{\phi}$  and  $C_{B}$  may be calculated to be 0.4 pf and 0.35 pf, respectively.

Then

$$V_B(0^+) = -12 V + \frac{0.4}{0.75}(-20) = -22 V$$

since

$$\frac{C_{\phi_1}}{C_B + C_{\phi_1}} = \frac{0.4}{0.75}$$

and

$$V_{C}(t) = -22 \times 0.87(1-e^{-\frac{t}{0.87RC_{C}}}),$$

since

$$\frac{C_B + C_{\phi_1}}{C_B + C_{\phi_1} + C_C} = \frac{0.75}{0.85} = 0.87$$

when

$$V_C^{(t)} = -11 V$$

$$-\frac{t}{0.87RC_C}$$

-11 = (-22)(0.87)+(10)e

Therefore

$$t = 0.76 RC_{C}$$

and

$$V_B$$

at the time  $t = 0.76RC_C$  is

$$-\frac{0.76RC_C}{0.87RC_C}$$

$$V_B(t) = -19 - (2.86 e)$$

$$= -19 - (2.86 e^{-0.87})$$

$$= -19 - 1.15 V$$

$$= -20.15 V.$$

T3 is saturated since it satisfies the condition

$$V_{GG} - (V_T + \Delta V_T) < V_{DD}$$

, 20 - 7 < 20.15

R for T3 device will be derived from this t, for which a faster switching time is required. The t may be calculated as 0.3 nsec.

Therefore

$$R_{on} = \frac{(0.3)(10^{-9})}{(0.76)(10^{-13})} = 4 \text{ K}$$

and

$$\left(\frac{W}{L}\right)_{T3} = \frac{1}{(5)(10^{-6})(4)(10^{-3})(13)}$$

$\approx 4$

A somewhat larger (W/L) ratio was needed for this coupling device to ensure faster switching speed and better conduction.

(W/L) ratio was increased as 10. The load device T2 is non-saturated. The condition is  $V_{GG} - (V_T + \Delta V_T) > V_{DD}$ , 20 - 7 > 12. The biasing parameter from Eq. (40) m is

$$m = \frac{-12}{(-20+7)} = 0.9$$

Therefore, eight time constants are required to reach 90% charge for  $C_{\varphi_1} + C_B = 0.75 \text{ pf from Figure 9.} \quad \text{Therefore } t = (8)(0.75 \text{ pf}) \, \text{R}_L.$  Choosing  $t = 100 \, \text{nsec}$ , since the clock pulse width is 300 nsec,  $R_L \quad \text{will be}$

$$R_L = \frac{(100)(10^{-9})}{(6)(10^{-12})} = 17 \text{ K}$$

where this R<sub>L</sub> is the resistance for the load device T2. From Eq. (9)

$$g_{m} = \frac{2}{R_{L}}$$

Therefore,

$$\left(\frac{W}{L}\right)_{T2} = \frac{2}{(17)(10^3)(65)(10^{-6})} = 1.8 = 2$$

Tl changes from saturated into non-saturated operation. Similar to the T4 calculation, Tl is saturated for 0 < t < t'. Combining Eqs. (27) and (28)

$$C_L \frac{dv_o}{dt} = K(V_{GS} - V_T)^2$$

where  $C_L$  is  $C_{\phi_1} + C_B$

$$\frac{C_{L}}{K(V_{CS}-V_{T})^{2}} \int_{-11}^{-5} dv_{o} = \int_{0}^{t} dt$$

$$t = \frac{C_L}{36K} (11-5) = \frac{6C_L}{36K} = \frac{C_L}{6K}$$

For  $t' \le t \le t_f$ , T1 is non-saturated. Combining Eqs. (31) and (32)

$$C_{L} \frac{dv_{o}}{dt} = K[2(V_{GS} - V_{T})v_{o} - v_{o}^{2}]$$

$$\int_{-6}^{-1.2} \frac{dv}{-v_o^2 + 12v_o} = \frac{K}{C_L} \int_{t'}^{t_f} dt$$

$$t_f - t' = \frac{C_L}{6K} \tanh^{-1} \left(\frac{-v_o - 6}{6}\right) \Big|_{-6}^{-1.2}$$

$$t_f = t' + \frac{1.1C_L}{6K}$$

$$= \frac{C_L}{6K} + \frac{1.1C_L}{6K}$$

$$= \frac{2.1C_L}{6K}$$

Assuming that  $t_f = 50$  nsec for a faster response, then (W/L) ratio will be

$$\left(\frac{W}{L}\right)_{T1} = \frac{(0.75)(10^{-12})(2.1)}{(6)(2.5)(10^{-6})(50^{-7})(10^{-8})}$$

$$\tilde{=} 2$$

Power consumption for each stage will dissipate in one inverter where both the load and driver device turn on simultaneously. From Eq. (23) and (17)

$$P = -V_{DD}K[V_{GS} - (V_{T} + \Delta V_{T})]^{2}$$

$$= (12)(2.5)(10^{-6})(13^{2})$$

$$= 6.06 \text{ m W}$$

The resultant W/L ratios of the devices of this dynamic shift register basic stage are summarized in Table 1. The actual widths and lengths shown in this table are the dimensions of the first oxidation removal patterns on the fabrication mask to diffuse P type material. The calculated R and g which are determined at the gate voltage -10 V are shown in Table 1. Each capacitance of the devices is also shown in Table 2.

Table 1. W/L ratios of each device.

| Devices | W/L  | w            | L    | g <sub>m</sub> | R         |

|---------|------|--------------|------|----------------|-----------|

|         |      | <del>_</del> |      |                | <u>on</u> |

| Tl      | 2    | 0.6          | 0.3  | 30 µmhos       | 33K       |

| Т2      | 2    | 0.6          | 0.3  | 30 µmhos       | 33K       |

| Т3      | 10   | 3            | 0.3  | 150 µmhos      | 7K        |

| T4      | 2. 5 | 0.75         | 0.3  | 40 µmhos       | 25 K      |

| Т5      | 2    | 0.6          | 0.3  | 30 µmhos       | 33K       |

| т6      | 10   | 3            | 0.3  | 150 µmhos      | 7K        |

| T7_     | 20   | 6            | 0. 3 | 400 µmhos      | 2. 5K     |

Table 2. Capacitance values.

| $C_{\phi_1}$ | С <sub>ф 2</sub> | СВ      | СС      | CD     | $^{\mathrm{C}}_{\mathrm{E}}$ |

|--------------|------------------|---------|---------|--------|------------------------------|

| 0.4 pf       | 1. 2 pf          | 0.35 pf | 0. l pf | 0.6 pf | 1. 4 pf                      |

# Fabrication Process and Results

The MOS fabrication process is simpler and inherently more reliable than conventional triple--diffused junction--transistor integrated circuitry. The MOS also has a size advantage over conventional

integrated circuits. The use of the active load resistor in place of conventional diffused resistors also further reduces the size of MOS integrated circuits. Because of this smaller size, and of the higher yields of the MOS process, the complexity of integrated circuits can be increased by an order of magnitude (17).

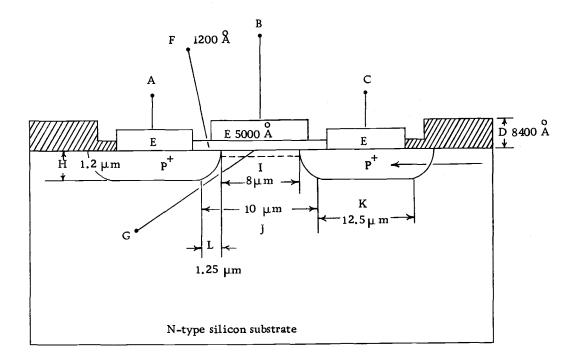

This paper, however, presents larger scale of designing parameters in order to have some flexibility for experimental purposes. Design parameters are listed below:

### 1. Geometry parameters

- a. Chip size is  $1000 \times 1000 \mu m$  (40 mils x 40 mils).

- b. All interconnecting leads are 25  $\mu m$  (1 mil) with 12.5  $\mu m$  ~ 50  $\mu m$  (0.5 mil ~ 2 mil) spacings.

- c. Bonding pads are  $100 \, \mu m \times 100 \, \mu m$  (4 mils x 4 mils).

- d. P to P spacings are  $10 \mu m$  (0.4 mil) long.

- e. Contact holes are 12.5 ~ 25  $\mu$ m<sup>2</sup> (0.5 ~ 1 mil<sup>2</sup>).

- f. Gate mask overlaps are 6. 25  $\mu$ m (0. 25 mil).

### 2. Oxide thickness

- a. Thick oxide is 8400 Å thick.

- b. The oxide over the diffusions is 1200 A thick.

- c. The gate oxide is 1200 A.

- 3. The crystal orientation <100>.

- 4. The junction depth is 1.2  $\mu m$ .

- 5. The implied starting-resistivity is  $7 \sim 10 \text{ ohm} \text{cm}$ .

# 6. Sheet resistance after diffusion is $18 \Omega/\square$ .

The expected cross-sectional structure of this design is presented in Figure 15 and the total physical layout for the basic 1-bit cell is shown in Figure 16. The gate area, contact holes and metal mask are superimposed upon the diffusion area mask. This basic cell is repeated by using the photo-mask making technique to get a desired nth-bits delay stage mask.

- A) Drain terminal

- B) Gate terminal

- C) Source terminal

- D) Thick oxide

- E) Metal electrodes

- F) Gate region thin oxide

- G) Channel

- H) Junction depth

- I) Actual channel length

- J) Geometry channel length

- K) Diffusion region width

- L) Side diffusion

Figure 15. Cross-sectional structure of the device.

Figure 16. Layout of the dynamic SR basic one-bit cell.

#### IV. EXPERIMENTAL RESULTS

## Characteristics of Devices Used for Tests

The characteristics of the four devices whose geometry sizes are different from each other were measured and listed in the following table.

Table 3. Device characteristics.

| Parameter               | $T1\left(\frac{W}{L}=2\right)$ | $T4(\frac{W}{L}=2.5)$ | $T3\left(\frac{W}{L}=10\right)$ | $T7(\frac{W}{L}=20)$ | Units |

|-------------------------|--------------------------------|-----------------------|---------------------------------|----------------------|-------|

| $v_{_{\mathrm{T}}}^{-}$ | -4. 2                          | -4. 1                 | -3.1                            | -3.56                | V     |

| g <sub>m</sub>          | 50                             | 40                    | 220                             | 420                  | μmho  |

| BV <sub>DS</sub>        | -55                            | -50                   | -45                             | -45                  | V     |

The photographed characteristics of the T7 device are shown in Figure 17.

Figure 17. Characteristic curve of T7 device (W/L = 20). Vertical 200  $\mu$ a/major division, horizontal 2V/major division, V<sub>GG</sub> 1 V/step (V<sub>G</sub> levels are also shown).

# The Results of the Circuit

Table 4. Operating conditions.

|                                                       | Designed value |      | Lab measurement |       |       |      |

|-------------------------------------------------------|----------------|------|-----------------|-------|-------|------|

| Parameters                                            | Min            | Max  | Min             | Тур   | Max   | Unit |

| Supply voltage V <sub>DD</sub>                        | · - 8          | -12  | -11             | -14   | -17   | V    |

| Supply voltage $V_{\overline{GG}}$                    | -16            | - 20 | -16             | -18   | - 23  | V    |

| Supply voltage $V_{\phi_3}$                           | ··-8           | -12  | -11             | -14   | -17   | V    |

| Width of data pulse, t (data) (see Figure 18)         |                | 1    | . 2             | . 6   | . 85  | μs   |

| Width of clock pulses, $t_p(\phi_1)$ (see Figure 18)  | . 3            | 3    | . 2             | . 4   | 2     | μs   |

| , $t_p(\phi_2)$ (see Figure 18)                       | . 3            | 3    | . 2             | . 6   | 2     | μs   |

| Rise time of clock pulse, $t_f(\phi)$ (see Figure 18) |                |      | 0.1             |       |       | μs   |

| Fall time of clock pulse, $t_f(\phi)$ (see Figure 18) |                |      | 0.1             |       |       | μs   |

| Clock repetition rate                                 | . 2            | 1    | . 01            | 0. 22 | 1. 2  | MHz  |

| Temperature variation                                 |                |      | 25° C           | 25° C | 120°C | ° C  |

Table 5. Electrical characteristics.

|                                                                                          |                                                                     | Lab measurement       |      |              |      |

|------------------------------------------------------------------------------------------|---------------------------------------------------------------------|-----------------------|------|--------------|------|

| Parameters                                                                               | Test conditions                                                     | Min                   | Тур  | Max          | Unit |

| V <sub>in</sub> (l) input voltage (logical l)                                            |                                                                     | - 9                   | -10  | -15          | V    |

| V <sub>in</sub> (0) input voltage (logical 0)                                            |                                                                     | 0                     |      | - 2          | V    |

| $V_{in}^{(l)\phi}$ input voltage (logical 1) at either clock input                       |                                                                     | -16                   | -18  | <b>- 2</b> 5 | v    |

| $V_{in}^{(0)\phi}$ input voltage (logical 0) at either clock input                       |                                                                     | 0                     |      | - 2          | v    |

| V (1) logical 1 output voltage                                                           | f = 500 KHz                                                         | -11                   | -12  | -14          | V    |

| V (0) logical 0 output voltage                                                           | $f_{clock}$ = 500 KHz                                               |                       |      | - 1          | V    |

| V out voltage at each stage                                                              | $R_L = 20 \text{ K}\Omega \text{ to GND}$                           | <b>-</b> <sup>3</sup> | - 5  | - 7          | V    |

| C capacitance of data                                                                    | $V_{in} = -10V$ $f = 500 \text{ KHz}$<br>$TA = 25^{\circ}\text{ C}$ |                       |      | 0. 1         | pf   |

| $C_{in}^{\ \phi_l}$ capacitance of clock $\phi_l^{\ input}$                              | $V_{in} \phi_1 = -18 V$ f = 500 KHz<br>TA = 25° C                   |                       |      | 0.4          | pf   |

| $C_{in}^{\phi}_{2}$ capacitance of clock $\phi_{2}$ input                                | $V_{in} \phi_2 = -18 V$ f = 500 KHz<br>TA = 25° C                   |                       |      | 1.2          | pf   |

| $^{\mathrm{I}}_{\mathrm{DD}}$ supply current into $^{\mathrm{V}}_{\mathrm{DD}}$ terminal | $V_{DD} = -14 V$ , $V_{GG} = -18 V$                                 | . 43                  | . 6  | . 9          | ma   |

| $^{ m I}_{ m GG}$ supply current into $^{ m V}_{ m GG}$ terminal                         | $V_{DD} = -14 V$ , $V_{GG} = -18 V$                                 |                       |      | 1.2          | ma   |

| Power dissipation/stage                                                                  | $V_{DD} = -14 \text{ V}, V_{GG} = -18 \text{ V}$                    |                       | 8. 4 | 13.5         | mW   |

Figure 18. Analysis of voltage waveforms.

The photographed output waveforms are shown in Figures 19, 20, 21, and 22 for a one-bit delay, a two-bit delay, a three-bit delay and a four-bit delay, respectively.

Figure 19. One-bit delay waveform. (Top, data input; center, output; bottom, clock; Vertical: 5V/division for top and center, 10V/division for bottom; Horizontal: 2 µsec/division.)

Figure 20. Two-bit delay waveform. (Vertical: 5V/division for top and center, 10V/division for bottom; Horizontal: 2 μsec/division.)

Figure 21. Three-bit delay waveform. (Vertical: 5V/division for top and center, 10V/division for bottom; Horizontal:  $2 \mu sec/division$ .)

Figure 22. Four-bit delay waveform. (Vertical: 5V/division for top and center, 10V/division for bottom; Horizontal:  $2 \mu sec/division$ .)

#### V. CONCLUSION

An integrated addressing circuit has been designed. It has been shown that the ratioless type technique offers several advantages in certain circuit applications which cannot be equaled by any of the other types of techniques. In particular, the final results show that the ratioless type circuit can have a smaller geometry size and less nodal capacitance over the ratio-type technique in a two-phase dynamic shift register circuit. The power-dissipation is also lower than that of the others.

The performance of this circuit was also enhanced by the presence of a low threshold voltage ( $V_T = -3.1 \, \mathrm{V}$ ). This explains why the clock and supply voltage amplitudes are required to be only -16 and -8 volts, respectively. The intentionally added capacitors assured a higher voltage on the gate at node B.

In regard to applicability of this ratioless technique in this addressing circuit, it appears that the sequentially added stage may be used in digital systems.

#### BIBLIOGRAPHY

- 1. Bazin, B., R.H. Crawford and L.J. Sevin. Theoretical effects of overlap capacitance upon MOS inverter circuit. Proceedings of the IEEE 56:1088-1089. 1968.

- 2. Bogert, H. Z. Metal oxide silicon integrated circuits. Semiconductor Products and Solid-State Technology 9(3):30-35. 1966.

- 3. Burns, J.R. Switching response of complementary symmetry MOS transistor logic circuits. RCA Review 25:627-661. 1964.

- 4. Crawford, R.H. MOSFET in circuit design. New York, McGraw-Hill, 1967. 136 p.

- 5. Grove, A.S. Physics and technology of semiconductor devices. New York, Wiley, 1967. 366 p.

- 6. Igarashi, R., T. Kurosawa and T. Yarta. A 150-nanosecond associative memory using integrated MOS transistor. International Solid-State Circuit Conference, Digest of Technical Papers 9:104-105. 1966.

- 7. Josephs, H. C. A figure of merit for digital systems. Microelectronics and Reliability 4:345-350. 1966.

- 8. Kane, J. FET's make digital switching a snap. Part II. Electronic Design 14(14):72-79. 1966.

- 9. Switch over to field-effects. Part I. Electronic Design 14(24):54-60. 1966.

- 10. Karp, J. and E. de Atley. Use four-phase MOS IC logic. Electronic Design 15(7):62-66. 1967.

- 11. Lohman, R.D. Application of MOSFET's in microelectronics. Semiconductor Products and Solid-State Technology 9(3):23-29. 1966.

- 12. Lynn, D. C., C. S. Meyer and D. Hamilton. Analysis and design of integrated circuits. New York, McGraw-Hill, 1967. 545 p.

- 13. Millman, J. and H. Taub. Pulse, digital and switching waveforms. New York, McGraw-Hill, 1965. 958 p.

- 14. National Semiconductor Corporation. Reliability report: MOS integrated circuits. Santa Clara, 1968. 20 p.

- 15. O'Reilly, T. J. The transient response of insulated-gate field-effect transistor. Solid-State Electonics. 8:947-956. 1965.

- 16. Redwine, D. Unpublished research on MOS transient calculations. Dallas, Texas Instruments, 1967.

- 17. Vadasz, L., R. Navala, W. Sander and R. Seeds. A systematic engineering approach to complex arrays. International Solid-State Circuits Conference, Digest of Technical Papers 9:120-121. 1966.

- 18. Watkins, B. G. A low power multiphase circuit technique. IEEE Journal of Solid-State Circuits 2:213-220. 1967.

- 19. Weinberger, A. Large scale integration of MOS complex logic: A layout method. IEEE Journal of Solid-State Circuits 2:182-190. 1967.

### APPENDIX A

# Charging Node B Without $C_{\phi}$ Added

The equivalent circuit diagram when  $\phi_2$  has just turned on is shown below.

At t = 0 when  $\phi_1$  turns on

$$V_{F}(0^{+}) = V_{F}(0^{-}) = -12 \text{ volts}$$

where  $V_F^{(0)}$  is the voltage that  $\phi_l$  just turns on and  $V_F^{(0)}$  is the voltage that node B was at -12 volts and T2 has just turned off.

The voltage equation for the circuit becomes

$$V_{B} = V_{C} + iR \tag{A-1}$$

$$\frac{1}{C_{B}} \int i dt + V_{B}(0) = \frac{1}{C_{C}} \int_{0}^{t} i dt + i(t)R$$

(A-2)

By using the Laplace transforms, the above Eq. (A-2) will be

$$-\frac{1}{C_{B}} \frac{I(s)}{s} + \frac{V_{B}(0)}{s} = \frac{1}{C_{C}} \frac{I(s)}{s} + I(s)R$$

$$i(s)[-\frac{1}{sC_{B}} - \frac{1}{sC_{C}} - R] = \frac{-V_{B}(0)}{s}$$

$$i(s) = \frac{\frac{V_{B}(0)}{s}}{\frac{1}{sC_{C}} + \frac{1}{sC_{C}} + R} = \frac{V_{B}(0)sC_{B}C_{C}}{(C_{C} + C_{B} + RC_{C}C_{B}s)}$$

$$V_{C}(0)C_{C}C_{C}$$

$$= \frac{\frac{V_{B}^{(0)}C_{B}^{C}C}{RC_{C}^{C}B}}{s \frac{RC_{C}^{C}B}{RC_{C}^{C}B} + \frac{C_{C}^{+C}B}{RC_{C}^{C}B}}$$

$$= \frac{V_{B}^{(0)}}{c \frac{C_{C}^{+C}B}{RC_{C}^{C}C}}$$

(A-3)

Its inverse is readily recognized as

$$i(t) = \frac{V_B(0)}{R} e^{-(\frac{C_C^{+C}B}{RC_CC_B})t}$$

(A-4)

And  $V_{c}(t)$  will be

$$v_{c}(t) = \frac{1}{C_{C}} \int_{0}^{t} i(t)dt = \frac{v_{B}(0)}{C_{C}R} \int_{0}^{t} e^{-(\frac{C_{C}+C_{B}}{RC_{C}C_{B}})t} dt$$

$$= -\frac{v_B^{(0)}}{c_C^R} \frac{Rc_C^C}{c_C^{+C}_B} e^{-\frac{C_C^{+C}_B}{Rc_C^C}} + \frac{v_B^{(0)}}{c_C^R} \frac{Rc_C^C}{c_C^{+C}_B}$$

(A-5)

Let  $t = \infty$ ; for the final  $V_C$  value

$$v_{c}(\infty) = V_{B}(0) \frac{C_{B}}{C_{C}+C_{B}} = -12(\frac{0.35}{0.45}) = -9.3$$

volts

This is the voltage for the final value at node C.

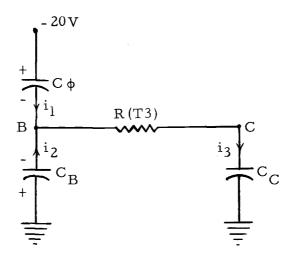

# Charging Node B With C

The purpose of the added capacitance,  $C_{\varphi}$  is to determine a final value of  $V_{C}$  after node C is changed to -11 volts.

The equivalent circuit diagram when the clock  $\phi_2$  has just turned on is shown below. From the following equivalent circuit, the current equation will be

$$i_1 + i_2 = i_3$$

(A-6)

The differential equations between current and voltage for each capacitance, and their transforms are

$$i_1 = C_{\phi} \frac{d(-20 - V_B)}{dt} = -C_{\phi} \frac{d(V_B)}{dt}$$

(A-7a)

$$i_2 = -C_B \frac{d(V_B)}{dt}$$

(A-7b)

$$i_3 = C_C \frac{dV_C}{dt}$$

(A-7c)

$$i_1(s) = -C_{\phi}(sV_B(s) - V_B(0))$$

(A-8a)

$$i_2(s) = -C_B(sV_B(s) - V_B(0))$$

(A-8b)

$$i_3(s) = C_C(sV_C(s) - V_C(0))$$

(A-8c)

Substituting the Eqs. (A-8a, b, c) into Eq. (A-6),

then

$$-(C_B + C_{\phi})(sV_B(s) + V_B(0)) = C_C(sV_C(s))$$

(A-9)

and the voltage relation is

$$V_{B}(s) = V_{C}(s) + Ri_{3}(s)$$

$V_{B}(s) = V_{C}(s) + RC_{C}(s)V_{C}(s)$  (A-10)

By simultaneous solution of Eqs. (A-9) and (A-10)

$$V_{C}(s) = \frac{-V_{B}(0)(C_{B}+C_{\phi})}{s(C_{B}+C_{\phi})(RC_{C}s)+s(C_{B}+C_{\phi})+C_{C}s}$$

(A-11)

After some algebraic manipulation, then

$$V_{C}(s) = \frac{-V_{B}(0)}{RC_{C}} \frac{1}{s[s + \frac{C_{B} + C_{\phi} + C_{C}}{RC_{C}(C_{B} + C_{\phi})}]}$$

(A-12)

And its inverse will be

$$V_{C}(t) = -V_{B}(0) \frac{C_{B} + C_{\phi}}{C_{B} + C_{\phi} + C_{C}} \left[ 1 - e^{-\left(\frac{C_{B} + C_{\phi} + C_{C}}{RC_{C}(C_{B} + C_{\phi})}\right)t} \right]$$

(A-13)

Solving for the  $V_{B}(t)$  by the same procedure:

$$V_{B}(t) = -V_{B}(0^{+}) \frac{C_{B} + C_{\phi}}{C_{B} + C_{\phi} + C_{C}} + V_{B}(0^{+}) (\frac{C_{B} + C_{\phi}}{C_{B} + C_{\phi} + C_{C}} - 1)e^{-\frac{C_{B} + C_{\phi} + C_{C}}{RC_{C}(C_{B} + C_{\phi})}t}$$

(A-14)

the final  $V_B$  voltage will be determined when  $t=\infty$

$$V_{B}(\infty) = -V_{B}(0^{+}) \frac{C_{B}^{+} C_{\phi}}{C_{B}^{+} C_{\phi}^{+} C_{C}}$$

$$= (-22V)(0.87) = -19V$$

since

$$\frac{C_B + C_{\phi}}{C_B + C_C + C_{\phi}} = 0.87$$

Therefore, the intentionally added capacitor  $C_{\varphi}$  assures -11 volts at node B, instead of the -9.3 volts.

### APPENDIX B

In order to determine the operating input voltage level, the threshold voltage,  $\ V_{T}$  variation during the fabrication process should be considered.

Considering  $V_T = -3.5V$  from the theoretical calculation (see page 12), the typical values of the threshold voltage variation may be assumed from -3V to -5V with which the calculation will be started.

In case  $V_{T}$  is -3V and both the load and the driver devices are turned on, the voltage on node B in Figure 14 is  $V_{DD}/2$  which this must be at least -3V to turn on the next device. And supply voltage  $V_{DD}$  must be at least -6V since the geometry of the load and the driver device is approximately the same.

To verify that the voltage on node B, -3V can turn on the next device T4, the following calculations will be done.

When the  $~\varphi_1~$  clock has just turned on,  $~V_{\hbox{\footnotesize B}}(0^-)~$  is floating at -6V, and  $V_{\hbox{\footnotesize B}}(0^+)~$  will be

$$V_B(0^+) = -6 + (-6)(\frac{0.4}{0.75}) = -9.5 V$$

since

$$\frac{C_{\phi_1}}{C_B + C_{\phi_1}} = \frac{0.4}{0.75}.$$

And substituting the above values into Eq. (13) in Appendix A yields

$$V_{C}(t) = -9.5 \times 0.87(1-e^{-\frac{t}{0.87RC_{C}}})$$

since

$$\frac{C_B + C_{\phi_2}}{C_B + C_{\phi_2} + C_C} = \frac{0.75}{0.85} = 0.87.$$

When

$$V_C(T) = -3V$$

$$-\frac{t}{0.87RC_C}$$

$$-3 = -9.5 \times 0.87(1-e)$$

Therefore,

$$t = 0.07RC_{C}$$

From Eq. (14) in Appendix A  $V_B(t)$  at the time  $t = 0.07RC_C$  will be

$$V_{B}(t) = -6 \times (0.87) + (-6) \times (0.13) \times (e$$

$$= -5.2 - 0.4 = -5.6 \text{ V}$$

when  $t = \infty$ , the  $V_B(\infty)$  will be

$$V_B(\infty) = -5.2V$$

This is the final voltage for the node B, which can of course, turn on the next device. To avoid the noise margin,  $V_{\mbox{DD}}$  may be chosen as -8V as its minimum operating value. Naturally voltages

less than -3V will not be able to turn on the driver device.

The clocks  $\phi_1$  and  $\phi_2$ , which are the gate input voltages for both the load and the coupling device in this circuit, can be determined from the following.

The load device should be in non-saturated condition, that is,  $V_{GG} - (V_T + \Delta V_T) > V_{DD} \quad \text{(Eq. 40)}. \quad \text{Therefore}$

$$V_{GG} > -8V - 5V = -13V$$

since  $V_T = -3V$  and  $\Delta V_T$  due to the back gate bias effect is approximately -2V from Figure 3.

However, from Eq. (40), the biasing parameter m will be

$$m = {V_{DD} \over V_{GG}^{-}(V_{T}^{+\Delta}V_{T}^{-})} = {-8 \over -13.5} = 1$$

When m=1, the switching time constant must be at least 18T from Figure 8. Therefore  $V_{GG}$  should be at least 16V to make m smaller, thus improving the operation of the circuit.

When the threshold voltage is -5V, which is the "worst case",  $V_{DD}$  and  $V_{GG}$  will be determined as -12V and -20V, respectively, by a similar procedure as above.

As far as the clock pulse rates are concerned, it has been assumed that the desired operating frequency range is from 200 KHz to 1 MHz and the two clock pulses,  $\phi_1$  and  $\phi_2$ , do not overlap

each other. Therefore, the minimum time interval becomes  $1~\mu$  second for each clock cycle and the allowed pulse width could be at most  $0.3~\mu$ sec for 1~MHz clock repetition rate.

In case of a 200 KHz clock rate, the allowable pulse width will be 3  $\mu$ sec. And the pulse width for the data input may be the same as the clock cycle.

The voltage level for  $\phi_3$  is chosen in the same way as the  $V_{\mbox{DD}}$  level, to turn on the output device. All the values determined in this fashion are listed in Table 4.