#### AN ABSTRACT OF THE THESIS OF

<u>Sridhar V. Kotikalapoodi</u> for the degree of <u>Master of Science</u> in <u>Electrical and Computer Engineering</u> presented on <u>September 7, 1994.</u>

Title: <u>Fine-Grain Parallelism On Sequential Processors</u>

# Redacted for Privacy

| Abstract approved: |             |  |

|--------------------|-------------|--|

|                    | Dr. Ben Lee |  |

There seems to be a consensus that future Massively Parallel Architectures will consist of a number nodes, or processors, interconnected by high-speed network. Using a von Neumann style of processing within the node of a multiprocessor system has its performance limited by the constraints imposed by the control-flow execution model. Although the conventional control-flow model offers high performance on sequential execution which exhibits good locality, switching between threads and synchronization among threads causes substantial overhead. On the other hand, dataflow architectures support rapid context switching and efficient synchronization but require extensive hardware and do not use high-speed registers.

There have been a number of architectures proposed to combine the instruction-level context switching capability with sequential scheduling. One such architecture is Threaded Abstract Machine (TAM), which supports fine—grain interleaving of multiple threads by an appropriate compilation strategy rather than through elaborate hardware. Experiments on TAM have already shown that it is possible to implement the dataflow execution model on conventional architectures and obtain reasonable performance. These studies also show a basic mismatch between the requirements for fine—grain

parallelism and the underlying architecture and considerable improvement is possible through hardware support.

This thesis presents two design modifications to efficiently support fine-grain parallelism. First, a modification to the instruction set architecture is proposed to reduce the cost involved in scheduling and synchronization. The hardware modifications are kept to a minimum so as to not disturb the functionality of a conventional RISC processor. Second, a separate coprocessor is utilized to handle messages. Atomicity and message handling are handled efficiently, without compromising per-processor performance and system integrity. Clock cycles per TAM instruction is used as a measure to study the effectiveness of these changes.

# Fine-Grain Parallelism On Sequential Processors

by

Sridhar V. Kotikalapoodi

A THESIS

submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Master of Science

Completed September 7, 1994 Commencement June, 1995

| APPROVED:                                                                     |  |  |

|-------------------------------------------------------------------------------|--|--|

| Redacted for Privacy                                                          |  |  |

| Assistant Professor of Electrical and Computer Engineering in charge of major |  |  |

| Redacted for Privacy                                                          |  |  |

| Head of Department of Electrical and Computer Engineering                     |  |  |

|                                                                               |  |  |

| Redacted for Privacy                                                          |  |  |

| Dean of Graduate School                                                       |  |  |

|                                                                               |  |  |

|                                                                               |  |  |

|                                                                               |  |  |

| Date thesis is presented: September 7, 1994                                   |  |  |

|                                                                               |  |  |

Typed by Kotikalapoodi V. Sridhar for : Kotikalapoodi V. Sridhar

#### **ACKNOWLEDGMENTS**

This thesis is dedicated to my parents and my sister Raju, but for whose understanding and support it would not have been possible. I am also very grateful to my brother-in-law for his unconditional help.

Special thanks to my major professor, Dr. Lee, for his inspiring guidance and for constantly challenging me to think in new directions. I owe most of the knowledge that I acquired in this field to his unconditional support and advice. Heart filled thanks to Dr. Lu for being available always for discussions. Also, special thanks to my committee members: Dr. Arthur and Dr. Pattee for making time for this defense amidst their tight schedules.

I extend my gratitude to Sridhar Jasti and Greg for their help in installing the tools for simulations.

Many thanks to all my very special friends – Ravi (Bulky), Satish, Patta, Sudhi, Praveen, Ashu, Bundy, Sameer, Dutta, Manoj R., Jasleen, Rajeev, Sanjeev and Sudha for making my stay at Oregon pleasant and unforgettable.

I would also like to thank the TAM group at UC, Berkeley for providing the TL0 to SPARC translator. Special thanks go to Klaus Schauser and Seth Goldstein for many fruitful interactions. I am also grateful to Computation Structures Group at MIT, including Andy Shaw and Boon Ang.

## **Table of Contents**

| 1. INTRODUCTION                               |     |  |

|-----------------------------------------------|-----|--|

| 1. 1. Motivation                              | 2 5 |  |

| 2. WHY MULTITHREADING                         | 6   |  |

| 2. 1. Dataflow Architectures                  | 6   |  |

| 2. 2. Shortcomings of dataflow model          | 8   |  |

| 2. 3. ETS Model                               | 9   |  |

| 2. 4. Hybrid Architectures and Multithreading | 11  |  |

| 2. 4. 1. Hybrid Architectures                 | 12  |  |

| 2. 4. 2. P-Risc                               | 12  |  |

| 2. 4. 3. TAM                                  | 13  |  |

| 3. THREADED ABSTRACT MACHINE (TAM)            | 15  |  |

| 3. 1. TAM Program Structure                   | 15  |  |

| 3. 2. Storage Model                           | 19  |  |

| 3. 3. Execution Model                         | 20  |  |

| 3. 4. Compiling to TAM                        | 22  |  |

| 3. 4. 1. A simple program in TLO              | 23  |  |

| 4. IMPLEMENTATION OF TAM                      | 27  |  |

| 4. 1. TL0 on the CM-5 multiprocessor          | 28  |  |

| 4. 1. 1. Storage model                        | 28  |  |

| 4. 1. 2. Arithmetic and logic instructions    | 29  |  |

| 4. 1. 3. Sending messages                     | 29  |  |

| 4. 1. 4. Receiving messages                   | 31  |  |

| 4. 1. 5. Thread scheduling                    | 33  |  |

| 4. 1. 6. Frame scheduling                     | 33  |  |

| 4. 1. 7. Heap access                          | 36  |  |

| 4. 2. Measurements                            | 37  |  |

| 4. 2. 1. Control Overhead                     | 38  |  |

| 5. DESIGN FOR EFFICIENT THREAD SCHEDULING     | 42  |  |

| 5. 1. The Proposed Method                     | 42  |  |

|   | 5. 2. Implementation for the SPARC                                         | 43 |

|---|----------------------------------------------------------------------------|----|

|   | 6. MESSAGE HANDLING                                                        | 47 |

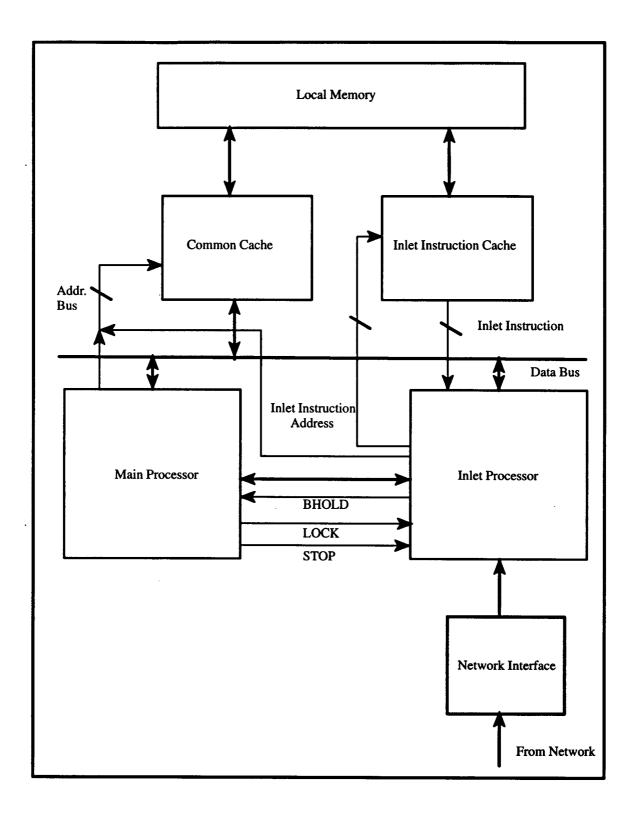

|   | 6. 1. Design using a Coprocessor                                           | 48 |

|   | 6. 2. Coprocessor versus Polling for inlets                                | 53 |

|   | 6. 3. Performance                                                          | 55 |

|   | 7. HARDWARE MODIFICATIONS AND CONCLUSION                                   | 60 |

| · | 7. 1. Hardware modifications required to implement the proposed changes 60 |    |

|   | 7. 1. 1. SPARC processor pipeline                                          | 60 |

|   | 7. 1. 2. Internal Instructions                                             | 61 |

|   | 7. 1. 3. Pipeline stages for cdbp instruction                              | 62 |

|   | 7. 1. 4. Hardware changes needed to implement the cdbp instruction         | 64 |

|   | 7. 1. 5. Hardware required to implement the ldi and std instructions       | 66 |

|   | 7. 1. 6. Implementation of the Double Ended Queue                          |    |

|   | for the LCV                                                                | 66 |

|   | 7. 1. 7. Hardware to assert the LOCK signal                                | 66 |

|   | 7. 2. Future work and conclusion                                           | 66 |

|   | BIBLIOGRAPHY                                                               | 70 |

# **List of Figures**

| Figure 2. 1. | Organization of a dynamic dataflow machine                                                                             | 8  |

|--------------|------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2. 2. | Illustration of Code-block invocation, Instruction and Frame memory in Monsoon.                                        | 11 |

| Figure 3. 1. | TAM activation tree and embedded scheduling queue.                                                                     | 16 |

| Figure 3. 2. | State transitions taken by frames due to POST and SWAP instructions.                                                   | 22 |

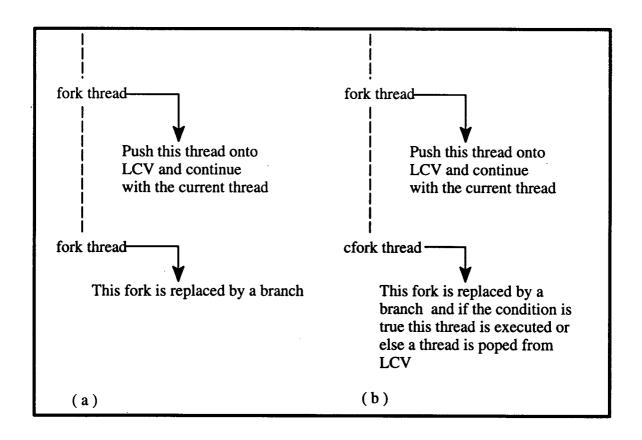

| Figure 4. 1. | Control transfer using FORK                                                                                            | 39 |

| Figure 6. 1. | Inlet Processor interface with the system                                                                              | 49 |

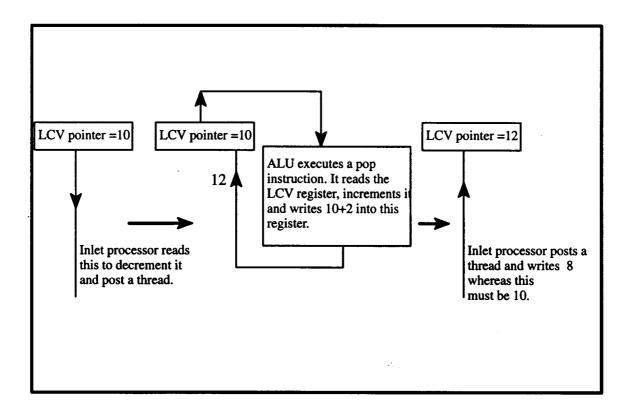

| Figure 6. 2. | Concurrent POST and FORK instructions resulting in the erroneous execution.                                            | 51 |

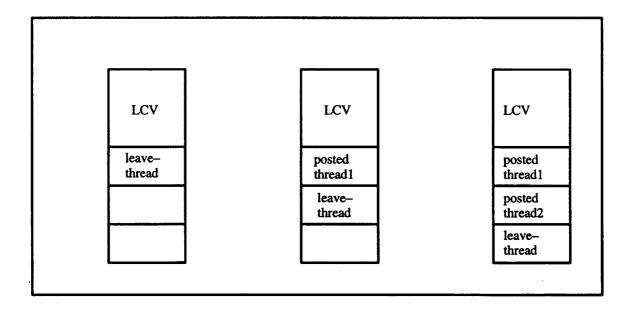

| Figure 6. 3. | LCV implementation                                                                                                     | 52 |

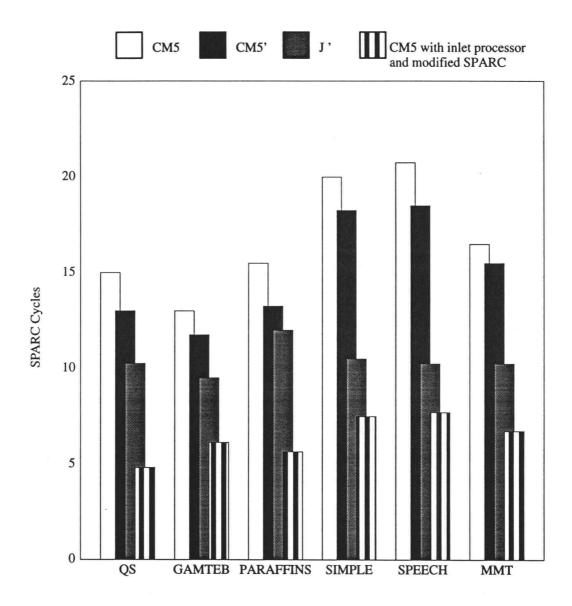

| Figure 6. 4. | Cycles per TL0 instruction comparison of the CM5, J-machine and the CM5 using modified SPARC chip and inlet processor. | 59 |

| Figure 7. 1. | SPARC processor's four stage pipeline                                                                                  | 61 |

| Figure 7. 2. | Execution of the store instruction                                                                                     | 62 |

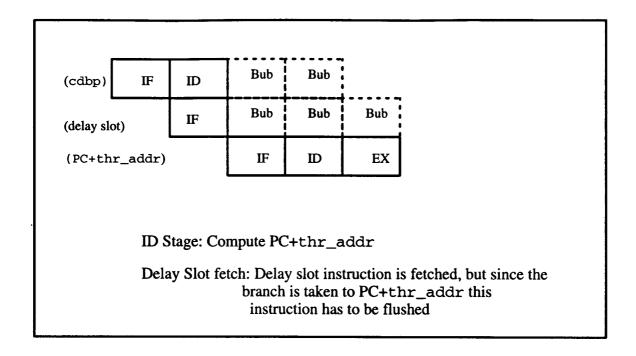

| Figure 7. 3. | Execution of cdbp instruction when the count is not zero.                                                              | 63 |

| Figure 7. 4. | Execution of cdbp instruction when the count is zero.                                                                  | 65 |

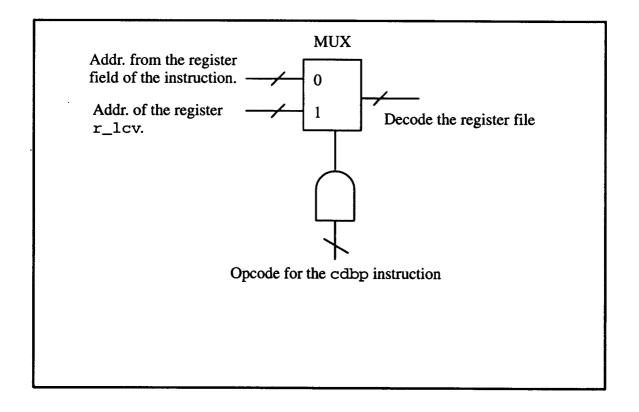

| Figure 7. 5. | Decoding the register file for the cdbp instruction                                                                    | 65 |

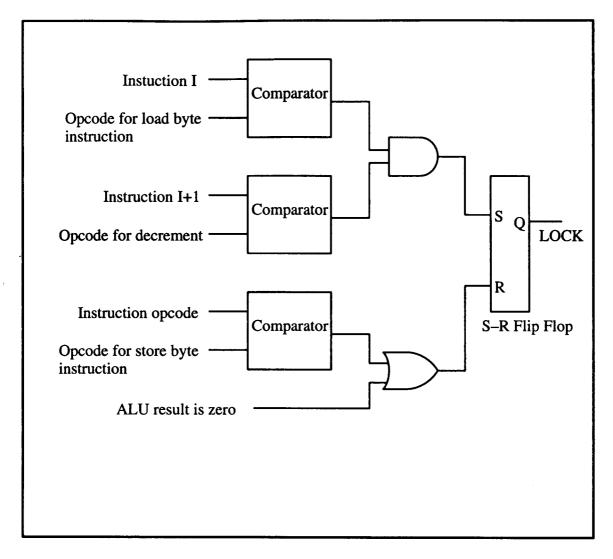

| Figure 7. 6. | Circuit to assert the LOCK signal                                                                                      | 67 |

# **List of Tables**

| Table 3. 1.  | A brief description of some of the most important TAM concepts                        | 18 |

|--------------|---------------------------------------------------------------------------------------|----|

| Table 4. 1.  | Access cost to each level of the local storage hierarchy on a SPARC node.             | 30 |

| Table 4. 2.  | Reserved special purpose registers                                                    | 30 |

| Table 4. 3.  | Mapping of TL0 arithmetic and logic instructions to the SPARC.                        | 31 |

| Table 4. 4.  | Cost for sending a message limited to three 32-bit arguments.                         | 32 |

| Table 4. 5.  | Cost of polling the network and of running an inlet                                   | 32 |

| Table 4. 6.  | Mapping of TAM POST instructions on to SPARC                                          | 34 |

| Table 4. 7.  | Cost of TL0 frame synchronization and scheduling operations.                          | 35 |

| Table 4. 8.  | Cost of accessing global data structures with synchronization on a per-element basis. | 37 |

| Table 4. 9.  | Dynamic instruction mix statistics for the benchmark programs.                        | 39 |

| Table 4. 10. | Mapping of TAM thread scheduling instructions on to SPARC.                            | 40 |

| Table 4. 11. | Cost and frequencies of TLO thread synchronization and scheduling instructions        | 41 |

| Table 5. 1.  | Scheduling and Synchronization costs for the modified SPARC.                          | 46 |

| Table 6. 1.  | Dynamic thread and inlet characteristics under TAM                                    | 56 |

| Table 6. 2.  | Work load distribution between the two processors                                     | 56 |

| Table 6. 3.  | Overhead cost due to the addition of a coprocessor                                    | 57 |

| Table 6. 4.  | Comparison of a Single processor system with a Inlet                                  | 58 |

#### Fine-Grain Parallelism On Sequential Processors

#### 1. INTRODUCTION

In the early days of computing, the issue of constructing a multiple-processor computing system was viewed as little more than an interesting intellectual exercise; after all, it seemed clear that machines could be made to operate faster simply by increasing the speed of the underlying technology. Given this view, it seemed that the style of machine organization for potential multiprocessing was not of overriding importance. The von Neumann organization, because of its sequential nature, was conceptually simple and easy to realize. Hence, it is not surprising that an entire academic community and industry was born with a built—in bias towards sequential computing. While understandable, this assumption about machine organization has inherent limits which, from our present vantage point, sit just beyond the horizon.

Attention has been focused in the recent past on constructing multiprocessor systems – attention derived from a desire for more performance. There seems to be little debate that the general purpose supercomputers of the future will be massively parallel architectures consisting of a number of nodes interconnected a high speed interconnection network [15]. What has not been done sufficiently is a reevaluation of the underlying assumptions. This is painfully clear when one observes that von Neumann style of processing still forms the building block for the majority of multiprocessor projects or proposals. Many variations on the von Neumann theme have been explored (e.g., pipelining, multiple functional units, vector instructions), but not much has been done with the sequential control required for instruction execution.

#### 1. 1. Motivation

Using a von Neumann style of processing within the node of a multiprocessor system has its performance limit imposed by the constraints of the control-flow execution model [2]. One serious problem with distributing work over several von Neumann processors is the implied shared memory. A single processor can mask the time to fetch an item from memory with a variety of techniques such as registers, caches, etc. However, when there are multiple processors in a system, parallel tasks, which are executed on different nodes, may require simultaneous access to a shared memory cell or one task may require the result of another task. Hence, a node has to fetch the contents of the memory on a remote node. The latency of remote memory access typically grows with the machine size.

Classically, caches are used to mask memory latency, and a cache can be added to hold copies of remote locations. However, cache coherence then becomes a significant problem. Further, a processor may still idle when there is a cache miss. Although caches can be used to alleviate the remote memory access latency to some extent, it does not offer anything for the synchronizing load problem. To illustrate this problem, let us consider the case where a process running on a node requires the result from another process running on a remote node. To ensure that the remote load reads the value only after the correct value is written, some form of synchronization is required. Unlike the remote load problem, the latency here is not just an architectural property – it also depends on scheduling, and the time it takes to compute the result, which may be much longer than the transit latency.

Another problem with the von Neumann style of processing is that of programming for parallel execution. Compilers can be used to analyze and transform sequential programs into parallel ones. However, anti-dependence and aliasing detection by compilers has been achieved only on very few programs with simple structures, thus restraining parallelism in most cases.

.

Due to these limitations, von Neumann model of computation does not readily carry over to multiprocessors. An alternative to the von Neumann model of computation is the dataflow model of computation. The dataflow model of computation can maximally exploit parallelism in a program [11]. In addition, the functional and asynchronous characteristics of the dataflow model of computation overcome many of the problems associated with the control—flow method of exploiting parallelism. First, there is no concept of a shared storage. Instead, operands are communicated as tokens of values rather than addresses of variables. Thus, the dataflow model of computation does not produce side—effects such as the inadvertent modification of a shared variable. Second, since the data is transmitted between instructions in the form of tagged tokens, where the tag carries control information (the context) for the destination instruction, there is no overhead involved in context switching. Hence, context switching can be effectively used to mask the memory latency.

Although, dataflow model of computation offers several advantages such as rapid context switching and side-effect free execution as well as exploits maximum parallelism by executing any operation on any processor, it has some shortcomings which prevent it from being practical alternative to the traditional methods of parallel computing [8]. First, it requires a matching store to hold the state of the overall computation. Given its associative nature, it is impractical to make the matching store extremely large, so deep recursion or extensive parallelism cause the store to fill up and the program to deadlock. Second, the pipeline of the dataflow processor tends to be inefficient. Third, it does not use the high-speed registers.

In light of this discussion, there have been a number of architectures proposed to combine the instruction—level context switching capability with sequential scheduling [11]. Multithreaded architectures retain the advantages of the dataflow model, like fast context switching and cheap synchronization [4]. In addition, by allegating the task of scheduling to compiler, multithreaded architectures based on the dataflow model require little hardware modifications to support the efficient thread scheduling and synchronization. In the context

of multithreading, a thread is a sequence of statically ordered instructions where once the first instruction in the thread is executed, the remaining instructions execute without interruption. As a result, a thread defines the basic unit of work from the dataflow point—of—view that requires synchronization only at the beginning of a thread. Observations of current dataflow projects show that there is a trend towards adopting multithreading as a viable method to build hybrid architectures that combine features of dataflow and control—flow execution models [11].

One such project at UC Berkeley, called Threaded Abstract Machine (TAM), supports fine—grain interleaving of multiple threads by an appropriate compilation strategy rather than through elaborate hardware [7]. Experiments on TAM have already shown that it is possible to implement the dataflow execution model on conventional architectures and obtain reasonable performance [7]. These studies also show a basic mismatch between the requirements for fine—grain parallelism and the underlying architecture and considerable improvement is possible through hardware support.

Based on the aforementioned discussions, this work presents two design modifications required to efficiently support fine—grain parallelism on a conventional RISC architecture. First, a modification to the instruction set architecture is proposed to reduce the cost involved in scheduling and synchronization. The hardware modifications are kept to a minimum so as not to disturb the functionality of a conventional RISC processor. Second, a separate coprocessor is utilized to handle messages. Atomicity and message handling are handled efficiently, without compromising per—processor performance and system integrity. Clock cycles per TAM instruction is used as a measure to study the effectiveness of these changes. Although the discussion is based on the SPARC architecture, the design issues apply to other RISC processors as well.

### 1. 2. Thesis Organization

Chapter 2 starts with an overview of dataflow architectures. It further discusses the advantages and disadvantages of the dataflow model of execution. Then an overview of hybrid architectures are provided and these discussions unfold the architectural features required of modern parallel machines.

Chapter 3 describes the Threaded abstract machine (TAM), developed at University of California, Berkeley. It describes the program structure, storage model, and execution model in detail. In addition, compilation of high-level parallel language to TAM is explained.

Chapter 4 explains the issues involved in mapping of TAM to traditional processor architectures. In addition, it also presents the dynamic measurements from running benchmark programs on TAM.

Chapter 5 presents our work to reduce the overhead involved in thread scheduling. It also presents the measurements obtained from the proposed change.

Chapter 6 discusses the overhead involved in message handling. It also discusses the issues involved in message handling like atomicity and coherence. It then presents our implementation for efficient message handling and then discusses the results.

Chapter 7 summarizes the hardware modifications required for the proposed changes and concludes with the brief overview of the work.

#### 2. WHY MULTITHREADING

von Neumann style of sequential execution is not very efficient for scalable multiprocessing because of its inability to tolerate increased latencies and to handle greater synchronization requirements [2]. In recent years research has been focused on alternative architectures for scalable multiprocessing. In this chapter, a general description of these architectures is provided. The advantages and shortcomings of these machines are also discussed.

#### 2. 1. Dataflow Architectures

Dataflow machines can directly execute dataflow graphs [11]. Dataflow graph is a directed graph in which vertices or nodes correspond to instructions and the data dependencies which exist between these instructions are represented by edges connecting these nodes. The data values are carried by tokens. These tokens travel along the arcs to the destination instructions. To distinguish between the different instances of a node, a tag is associated with each token that identifies the context in which a particular token was generated. Thus, typically a tagged—token has processor address, codeblock name, initiation number to identify the instance of the node and the address of the instruction with in the code block appended to the data value. A node can be executed or said to be fired when all its input arcs contain a set of tokens with identical tags.

Dataflow models can be in turn classified as either static or dynamic. The static dataflow model exploits only a limited amount of parallelism and lacks the general support for programming constructs essential for any modern programming environment (e.g., procedure calls and recursion) [11]. On the other hand, dynamic dataflow model exploits all the parallelism in the program. For example, a loop can be unfolded dynamically, thus allowing the execution of the multiple instances of the loop concurrently. For this reason, current dataflow research efforts indicate a trend towards the dynamic dataflow model.

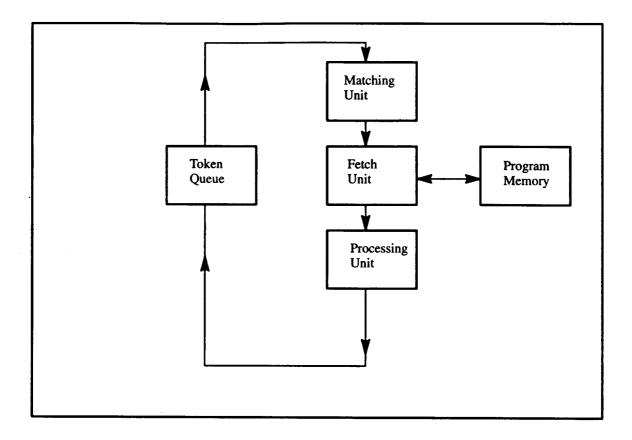

The general organization of the dynamic dataflow machine is shown in Figure 2.1 [11]. Tokens are received by the *Matching Unit*, which is memory containing a pool of tokens waiting for their partners. The basic operation of the Matching Unit is to bring together the tokens with identical tags. If a match exists, the corresponding token is extracted from the Matching Unit and the matched token set is passed on to the Fetch Unit. If no match is found, the token is stored in the Matching Unit to await a partner. In the Fetch Unit, the tags of the token pair uniquely identify an instruction to be fetched from the Program Memory. A typical instruction consists of an operational code, a literal/constant field, and destination fields. The fetched instruction together with the token pair is sent to the Processing Unit. The Processing Unit executes the enabled instructions and produces result tokens to be sent to the Matching Unit via Token Queue.

The simplicity of this model derives from the implicit allocation of storage and scheduling associated with each message arrival. Any operation can execute on any processor, simply by sending the tokens to that processor.

The dataflow model of execution offers many attractive properties for parallel processing. First, the dataflow model of execution is asynchronous, i.e., the execution of an instruction is based on the availability of its operands. Thus, it exposes all the parallelism in the program. Second, data is appended with the address of the destination instruction. Therefore, the synchronization of parallel activities is implicit in the dataflow model. Moreover, since the data carries with it the control information (the context) with it, context switching is fast. This allows efficient exploitation of fine—grain parallelism at instruction level.

Figure 2. 1. Organization of a dynamic dataflow machine

Although the dataflow model offers several advantages like rapid context switching, cheap synchronization, and exposes all parallelism in a program, it has several short-comings which prevent it from being practical.

#### 2. 2. Shortcomings of dataflow model

Several shortcoming have been identified with the dataflow model of computing. These shortcomings include:

- Overhead involved in matching tokens is heavy;

- Inefficient resource allocation; and

- The dataflow instruction cycle is inefficient.

Detection of matching tokens belonging to the same instance of an instruction is one of the most important aspects of the dataflow computation model. A failure to find a match implicitly allocates memory within the matching hardware. Thus, when a code—block is mapped to a processor, an unspecified commitment is placed on the matching unit of the processor. Given its associative nature, it is impractical to make the matching store extremely large, so deep recursion or extensive parallelism cause the store fill up and the program to deadlock [5].

Another subtle problem with the dataflow model is, it does not not utilize the high speed registers for computation. So there is no means by which the compiler can organize the program to make efficient use of processor resources [8].

A more general criticism leveled at dataflow model is the inefficiency in its instruction cycle. For example, matching tokens is more complex than simply incrementing a program counter. Similarly, generating and communicating result tokens impose inordinate amount of overhead compared to simply writing the result to a memory location or a register. These inefficiencies in the pure dataflow model tend to degrade performance for programs having a low–degree of parallelism.

#### 2. 3. ETS Model

In the past few years, there have been several proposals which try to overcome the shortcomings of a pure dataflow model. For example, The ETS model embodied in Monsoon is a partial remedy to these problems [16]. Implicit allocation of the matching store is eliminated by explicitly allocating a storage, called an *activation frame*, to hold the local storage for each function invocation. Synchronization bits are associated with each frame location to support a dyadic match.

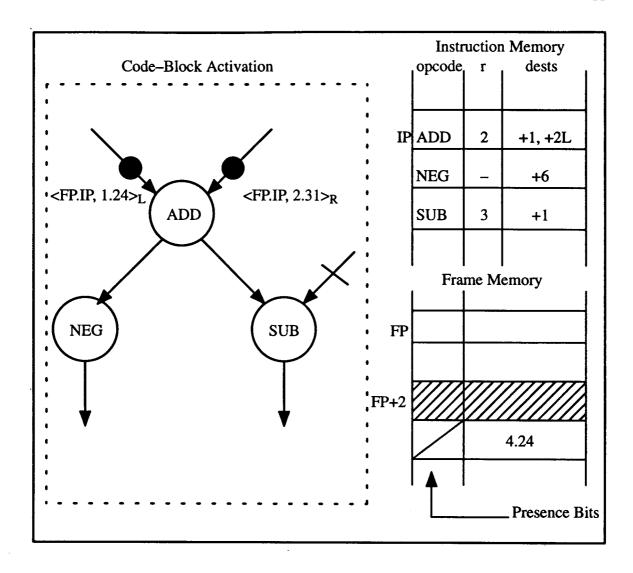

To illustrate the operations of direct matching in more detail, consider the token matching scheme used in Monsoon. An example of the ETS code-block invocation and its

corresponding Instruction and Frame Memory is shown in Figure 2.2. In a direct matching scheme, any computation is completely described by a pointer to an instruction (IP) and a pointer to an activation frame (FP). The pair of pointers, <FP.IP>, is called a *continuation* and corresponds to tag part of a token. When a token arrives at an actor (e.g., ADD), the IP part of the continuation points to the instruction that contains an offset r as well as displacement(s) for the destination instruction(s). The actual matching is achieved by checking the slot in the Frame Memory pointed to by FP+r. If the slot is empty, the value of the token is written in the slot and its presence bit is set to indicate that the slot is full. If the slot is full, the value is extracted, leaving the slot empty, and the corresponding instruction is executed. The result token(s) generated from the operation is communicated to the destination instruction(s) by updating the IP according the displacement(s) encoded in the instruction (e.g., execution of the ADD operation produces two result tokens <FP.IP+1, 3.55> and <FP.IP+2, 3.55>1).

Thus, in the ETS model, the implicit allocation of the Associative Matching Store is eliminated. However, the token buffer remains. When a message arrives, storage is allocated for it in a large queue. Although Monsoon allows short instruction *threads* to be scheduled, using frame slots and a small set of registers to convey the data between instructions in a thread, the arbitrary interleaving of tokens in the queue is unlikely to provide any useful locality. Furthermore, the machine cycle time is limited by the read–modify–write on the frame synchronization bits and the frame access per instruction.

Figure 2. 2. Illustration of Code-block invocation, Instruction and Frame memory in Monsoon

## 2. 4. Hybrid Architectures and Multithreading

As mentioned in section 2.1, one major advantage of architectures based on the dataflow model of computation is the instruction-level context-switching capability. That is, context-switching can occur on a per-instruction basis since each datum carries context identity with it (i.e., in the form of a tag). This provides the ability to tolerate long and unpredictable memory latencies. On the other hand, the processor resources like registers are not used in the dataflow model. The instruction-level context-switching capability combined with sequential scheduling, which provide a different perspective on dataflow architectures – multithreading, combines the advantages of the both. In the context of multithreading, a thread is a sequence of statically ordered instructions where once the first instruction in the thread is executed, the remaining instructions execute without suspending. As a result, a thread defines the basic unit of work from the dataflow model point—of—view that requires synchronization only at the beginning of a thread.

### 2. 4. 1. Hybrid Architectures

The Hybrid proposal was the first to observe the interplay between register allocation and thread scheduling [10]. This model provides a machine language of multiple threads operating against an activation frame and registers. However, each frame slot includes presence bits, like the ETS. A thread is suspended upon access to a frame slot marked not—present. The suspension is accomplished by building a queue of instruction pointers into waiting threads. The queue is rooted in the frame slot, so the eventual store of the value enables the threads. Since no registers are saved upon suspension, the compiler is required to evacuate the registers across any potential point of suspension. This elaborate suspension, queuing and scheduling mechanism is part of the basic model and required in any machine that implements it. Moreover, scheduling is outside the programming model, so there is no means by which the compiler can organize the program to make efficient use of processor resources.

#### 2. 4. 2. P-Risc

P-Risc observed that presence-bits can be kept in the frame like local data, rather than as special tags, and that matching could be simulated by toggling the tag bit atomically and suspending on the result [14]. This means that for synchronizing threads, rather than checking the presence bits a count, which is stored in the frame memory like data, is checked to see whether the thread is ready for execution. This eliminates the need for including pres-

.

ence bits with each slot and results in efficient machine cycle. In addition, P-Risc eliminated the notion of suspension with in a thread. Thus synchronization is required only at the starting of a thread. However, P-Risc failed to retain the distinction between registers and frames of the Hybrid model. Instead the entire frame is viewed as a set of registers. Like the hybrid model, scheduling is outside the execution model. Thus when a thread completes, any enabled thread could execute next, so there is no means by which the compiler can develop a higher level strategy for utilizing processor resources while tolerating latency.

#### 2. 4. 3. TAM

Dataflow research has focused on the obvious costs: scheduling and synchronizing threads. However as seen in the above sections, optimizing scheduling costs while ignoring the effects on the storage hierarchy leads to unrealistic solutions. Instead, the Threaded Abstract Machine (TAM) exposes the scheduling of threads so that the compiler can coordinate scheduling with the usual management of the storage hierarchy [7]. To aid in this coupling, TAM allows groups of related threads to be scheduled together. This reduces the cost of scheduling and permits the compiler to manage storage resources, e.g., registers and local variables, across several threads. Finally, giving priority to related threads tends to improve cache behavior. Overall, the effect is that data can be kept at smaller and faster levels of the storage hierarchy.

Thus TAM supports asynchronous parallelism while tolerating memory latency and overcomes the shortcomings which are inherent in the dataflow model like:

Matching Overhead: Matching is done by checking a count rather than using associative memory or presence bits. Since the count is stored in the memory like any other data, matching overhead is reduced.

- Inefficient resource allocation: Since the scheduling of threads is storage driven

and managed by the compiler, related threads can be scheduled together. Hence,

data can be passed in registers across several threads.

- Inefficient Instruction Cycle: The processor pipeline is uniform and does not include the inefficient operations like token matching or checking and updating presence—bits. In addition, TAM can mapped effectively onto a sequential RISC processor.

## 3. THREADED ABSTRACT MACHINE (TAM)

The Threaded Abstract Machine (TAM), developed at University of California, Berkeley, refines dataflow execution models to address the critical constraints that modern parallel architectures place on the compilation of general–purpose parallel programming languages [7]. TAM defines a self–scheduled machine language of parallel threads, which provides a path from dataflow–graph program representations to conventional control flow. The most important feature of TAM is the way it exposes the interaction between the handling of asynchronous message events, the scheduling of computation, and the utilization of the storage hierarchy.

Since our work is based on TAM, this chapter provides a complete description of TAM and codifies the model in terms of a machine language TLO. Issues in compilation from a high level parallel language to TLO are discussed in general and specifically in regard to the Id90 language [13].

## 3. 1. TAM Program Structure

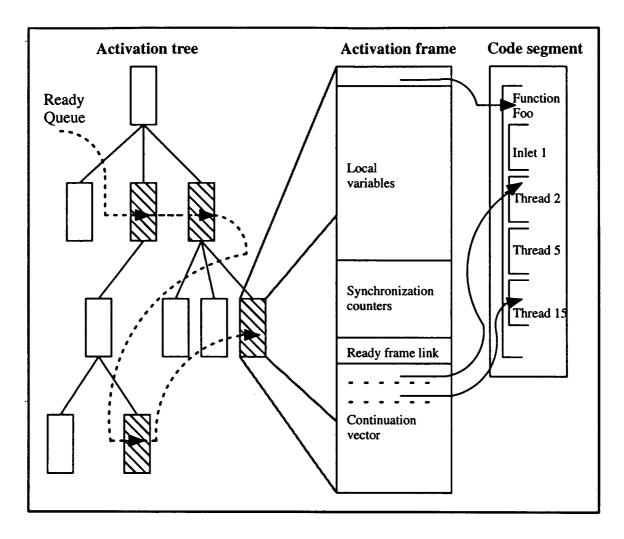

A TAM program consists of a collection of *code-blocks* where each code-block typically represents a loop-body or a function. Each code-block comprises of several *threads* and *inlets*. The *activation frame*, which is analogous to the stack frame for conventional subroutine calls, is the central storage resource. Invoking a code-block involves allocating an activation frame, depositing argument values into the frame and enabling threads for execution within the context of the frame. Initialization also consists of setting the values of *synchronization counters* stored within the frame. The caller does not suspend upon invoking a child code-block so it may have multiple concurrent children. Thus, as shown in Figure 3. 1, the dynamic call structure forms a tree, rather than a stack, represented by a tree of frames.

Figure 3. 1. TAM activation tree and embedded scheduling queue

An activation frame may be in one of three states: idle, ready, or running. Every processor has exactly one running (or current, or resident) frame, the frame pointed by the FP register. All local memory accesses that occur either in threads or inlets are relative to the current frame.

To support thread level scheduling, every frame has a remote continuation vector, the RCV, and the processor has a local continuation vector, the LCV. The LCV holds the enabled threads for the running frame. On the other hand, the RCV contains the enabled

<sup>1.</sup> Threads are said to be enabled if they are ready for execution.

threads for a ready frame. Every code-block specifies the size of the continuation vector that must be allocated for a new frame. The high-level language compiler is responsible for determining the size by analyzing the structure of the threads in the code-block.

An idle frame is one which has no threads in its RCV. A ready frame has at least one thread in its RCV and is waiting to be scheduled, or, in other words, waiting to become the running frame. There may be zero or more idle or ready frames per processor.

The ready frame queue is maintained using the frame slots of the ready frames. The head of the queue is kept in the QP register. Every other frame in the queue points to the next ready frame. Thus, all the data structures needed for both scheduling levels are maintained in the frames; once a frame is allocated all its scheduling resources have been allocated as well.

A thread is a collection of non-suspending instructions. Two instructions are in the same thread if they can be statically ordered. There are no jumps or branches within a thread, and synchronization occurs only at the beginning of a thread. FORK attempts to enable a thread in the current activation. If the thread is an unsynchronizing one, it pushes the pointer to the thread onto the LCV, which contains pointers to the all enabled threads. If the thread requires synchronization, the counter associated with the thread is decremented and if it's zero then the thread is pushed on the LCV; otherwise, the decremented count is stored back. A SWITCH instruction forks one of two threads depending on a condition. A STOP instruction stops the current thread and causes some other enabled thread to begin execution. This is done by poping a thread from the LCV. When there are no enabled threads or it has executed the current code—block completely, the processor executes a swap instruction, which transfers control to a frame from the ready frame queue. A quantum is the set of threads executed during a single residency of the frame.

The arguments to the code-block, results from other frames and responses to the global heap accesses are received by *inlets*. Inlets, as shown in Table 3.1, are compiler gene-

Table 3. 1. A brief description of some of the most important TAM concepts

| Code Structures          |                                                           |

|--------------------------|-----------------------------------------------------------|

| Codeblock                | A collection of threads and inlets that corresponds to a  |

|                          | single function (or loop body) in the original program.   |

| Thread                   | A sequence of instructions with a single entry and sing-  |

|                          | le exit point that can be executed without suspension.    |

| Inlet                    | A sequence of instructions tailored to handle the receipt |

|                          | of a message for a target frame.                          |

| Data Structures          |                                                           |

| Activation Frame         | Similar to an stack frame in a sequential language, it is |

|                          | the unit of storage of each codeblock invocation.         |

| Continuation Vector      | The data structure used to store enabled threads.         |

| Ready Queue              | The data structure used to keep track of frame that are   |

|                          | ready to execute, i.e., frames with enabled threads that  |

|                          | are not running.                                          |

| Synchronization Counters | Counters used to enforce synchronization between          |

|                          | threads.                                                  |

| Operations               |                                                           |

| Fork                     | The FORK instruction is used to enable threads for the    |

|                          | currently running frame.                                  |

| Post                     | The POST instruction is executed in inlets and is used    |

|                          | to enable threads for the target frame. It will also, if  |

|                          | necessary, enqueue the frame on the ready queue.          |

| Swap                     | The SWAP instruction schedules a frame from the ready     |

|                          | queue.                                                    |

rated message handlers that copy the arguments into the frame and enable computation depending on the message. The SEND operation delivers a sequence of data values to an inlet relative to the target frame. The inlet specified in the message receives the message through a RECEIVE instruction and stores the data into the specified location and enables a thread by executing a POST instruction. Enabling a thread from inlet is slightly different from enabling one from a thread. An inlet can enable a thread for execution in a different frame where as the one enabled from a thread is with in the current frame and is closely coupled to the current processor state. Inlets may preempt threads, but they may not preempt other inlets.

### 3. 2. Storage Model

The TAM storage model includes four distinct regions: code storage, frame storage, registers, and heap storage. TAM code storage contains code—blocks representing the compiled form of the program. It appears identical to all processors and is accessible through fast local operations.

Frame storage is assumed to be distributed over processors, but each frame is local to some processor and only accessed from that processor. Work is distributed over processors on a frame invocation basis. Inter–frame communication is potentially interprocessor communication and is realized by sending values to inlets relative to the target frame.

A TAM processor contains data registers of various types and four special address registers: FP, the address of the current frame, IP, the address of the current thread instruction, IFP, the address of the target frame for the current inlet while it is executing, and IIP, the address of the current inlet instruction. A frame is running on a processor when it is referenced by the FP. Instructions can access registers or frame slots, relative to FP.

Heap storage contains objects that are not local to a code-block, including statically and dynamically allocated arrays. Accessing the global heap does not cause the processor

to stall, rather it is treated as a special form of message communication. A request is sent to the memory module containing the accessed location while threads continue to execute. The request specifies the frame and inlet that will handle the response. If the response returns during the issuing quantum, the inlet integrates the message into the on—going computation by depositing the value in a frame or register and enabling a thread. However, if a different frame is active when the response returns, the inlet deposits the value into the inactive frame and posts a thread in that frame without disturbing the register usage of the currently active frame.

Global data structures in TAM provide synchronization on per-element basis to support I-structure and M-structure semantics [3]. If the I-structure element is empty, a read is deferred until the corresponding write takes place. A remote I-structure operation generates a request for a particular heap location and the corresponding response is received by an inlet. Meanwhile, the processor continues with other enabled threads. In TAM, these split-phase transactions are supported by instructions, such as IFETCH and ISTORE, which are used to read and write to the data structures, respectively.

#### 3. 3. Execution Model

The processor executes instructions within the current thread sequentially until a STOP is executed. At that point a thread address is removed from the LCV and loaded into IP, initiating the next thread. When no threads remain in the LCV, STOP transfers control to a *leave-thread* specified in the frame. The leave-thread typically loads the next frame pointer into FP, loads the *enter-thread* address from that frame into the LCV and performs a STOP. The enter-thread typically copies the threads accumulated in the RCV to the LCV and performs a STOP, thereby starting the new quantum.

The TAM scheduling queue is a data structure obtained by linking together frames. The compiler defines the representation of this frame level structure by the code it places in the leave—thread. The compiler can also insert register saves in the leave thread and restores in the enter thread, if register values are carried across quanta.

In translating TAM to a conventional machine, the LCV is simply a stack. The leave—thread address is placed at the bottom of the stack. FORK pushes an instruction address; STOP pops an address and jumps to it. Code generators will typically combine the last fork in a thread with the stop, producing a simple branch instead of push—pop—jump.

Inlet execution may preempt the current thread when a message arrives. The address of the inlet is loaded into the register IIP and the frame address specified in the message is loaded into the register IFP. If the message is for the current activation (i.e., if IFP = FP) the thread registers can be used in the inlet to deliver the data into registers instead of frame slots. However, if IFP  $\neq$  FP, the POST enables a thread in the target frame. In addition, if the frame was not ready before the POST, the frame has to be linked to the ready frame list.

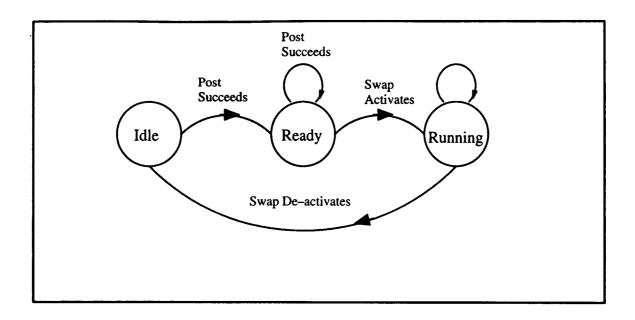

Invoking a code—block involves first allocating a frame. The caller sends arguments to inlets in the code—block relative to the newly allocated frame. The inlets are executed upon message arrival (possibly interrupting a thread on the processor holding the frame), store the values in the frame, and post threads of the code—block for later execution. The activation thereby becomes ready, meaning that it has threads waiting to be executed, and it is linked into a pool of ready frames. Execution then continues with the interrupted thread. Eventually, the new frame is scheduled when there are no enabled threads in the running frame by executing a SWAP instruction. The SWAP instruction removes one of the ready frames from the ready list and enables it by making it the current frame and executing the enter—thread as described above. The state transitions taken by the frames is shown in Figure 3. 2.

Figure 3. 2. State transitions taken by frames due to POST and SWAP instructions

Depending on its communication pattern, an invocation goes through one or more scheduling quanta. At some point it usually sends return values back to inlets of its caller. The frame is explicitly released when it is no longer required. The means of determining when frames are allocated and released depends on the high–level language; no automatic management is embedded in TAM.

#### 3. 4. Compiling to TAM

The overall goal in compiling to TAM is to produce code that is latency tolerant, yet obtains processor efficiency and locality. TAM exposes parallelism, scheduling, and communication to the compiler and makes each cost explicit. Exposing the costs gives the compiler a clear optimization goal and allows it to map the various constructs of the parallel language to the best suited TAM primitives. On the other hand, TAM places the responsibility for correctly resolving several issues, such as management of frames, ordering of threads, and usage of local storage on the compiler. Although the source language for the compiler

is the dataflow language Id90, the TAM parallel execution model is well suited for implementing other parallel languages. This section discusses the key aspects of the compilation process from a high-level parallel language down to TAM, including the representation of parallelism, communication, synchronization, scheduling, storage management, and the use of the storage hierarchy. These issues are addressed both in general and in the context of Id90.

## 3. 4. 1. A simple program in TL0

To illustrate some of the TLO conventions and present a concrete TLO program, we consider the following trivial program which computes the Fibonacci numbers. The recursive calls to fib are the sources of parallelism. Arguments must be communicated to these parallel calls and the final result requires synchronization of the partial results.

The code for calculating a Fibonacci number recursively,

```

def fib n = if (n < 2) then 1 else fib (n-1) + fib (n-2)

```

is compiled into the TLO code, which is shown below.

```

CBLOCK FIB.pc

FRAME_BODY RCV=3 LCV=5

% frame layout, RCV size is 3 threads, LCV

% size is 5 threads

islot0.i islot1.i islot2.i

%argument and two results

pfslot1.pf pfslot2.pf

%frame pointers of recursive calls

sslot0.s

%synch variable for thread 6

retfp.pf retip.j

%return frame pointer and inlet

REGISTER

%registers used

breg0.b ireg0.i

%boolean and integer temps

INLET 0

%recv parent frame ptr and return inlet

RECEIVE retfp.pf retip.j

FINIT

%initialize frame

SET_ENTER 7.t

%set enter-activation thread

SET_LEAVE 8.t

%set leave-activation thread

SEND retfp.pf[retip.j+-1.i] <- fp.pf</pre>

%send back the address to caller

STOP

INLET 11

%receive argument

RECEIVE islot0.i

```

```

POST 0.t "default"

STOP

INLET 14

%receive frame pointer of first recursive call

RECEIVE pfslot1.pf

POST 3.t "default"

STOP

INLET 15

%receive result of first call

RECEIVE islot1.i

POST 5.t "default"

STOP

INLET 16

%receive frame pointer of second recursive

RECEIVE pfslot2.pf

%call

POST 4.t "default"

STOP

INLET 17

%receive result of second call

RECEIVE islot2.i

POST 5.t "default"

STOP

.THREAD 0

%compare argument against 2

LT breg0.b = islot0.i 2.i

SWITCH breg0.b 1.t 2.t

STOP

THREAD1

%argument is < 2

MOVE ireg0.i = 1.i

%result for base case

FORK 6.t

STOP

THREAD 2

%argument >=2, allocate frames for calls

MOVE sslot0.s = 2.s

%initialize synchronization counter

FALLOC 14.j = FIB.pc "default"

%invoke first child

FALLOC 16.j = FIB.pc "default"

%invoke second child

STOP

THREAD 3

%got FP of first call, send its arg

SUB ireg0.i = islot0.i 1.i

%argument for first call

SEND pfslot1.pf[0.i/FIB.pc] <- ireg0.i %sendit

STOP

THREAD 4

%got FP of second call, send its arg

SUB ireg0.i = islot0.i 2.i

%argument for second call

SEND pfslot2.pf[0.i/FIB.pc] <- ireg0.i %sendit

STOP

THREAD 5

%got results from both calls

SYNC sslot0.s

%synchronize

ADD ireg0.i = islot1.i islot2.i

%add results

FORK 6.t

STOP

THREAD 6

%done

```

```

SEND retfp.fp[retip.j] <- ireg0.i</pre>

%send result to parent

FFREE fp.pf "default"

%deallocate own frame

SWAP "default"

%swap to next activation

STOP

THREAD 7

%enter-activation thread

STOP

%no registers to restore

THREAD 8

%leave-activation thread

SWAP "default"

%swap to next activation

STOP

%no registers to save

```

Consider the execution after the invocation of some frame f of the function fib. The first thread to be executed is Thread 0 which contains the conditional expression, with a test of the integer argument contained in the frame location islot1 and a fork of either Thread 1 or Thread 2 based on the result of the comparison.

Thread 2 generates parallelism by allocating two frames for the recursive calls. The FALLOC sends a request to a system inlet that handles frame allocation. FALLOC is a split—phase operation, because the allocation may require sending a request to another processor. The responses to the frame allocations are returned to inlets 14 and 16, respectively. Let's assume that the first allocation request completes before Thread 2 finishes. Then inlet 14 is likely to interrupt Thread 2. Inlet 14 enables Thread 4 for execution. Therefore, at the end of Thread 2, f will continue with Thread 4, after which f will have no more enabled threads (unless the other allocation has already returned), so a SWAP is performed (via Thread 8) to another ready frame on the local processor (possibly the newly allocated frame). Eventually, Inlet 16 will be triggered to receive a pointer to the remotely allocated frame into the frame pfslot1. Inlet 16, posts Thread 3 using the default frame scheduling policy and enables the frame.

Thread 3 computes argument value in a register and sends it to Inlet 11 of the frame for the first recursive call. The argument/result linkage of a parallel call can be viewed as a very general form of split—phase operation; eventually, the result will return to Inlet 15. In the meantime, the argument message triggers Inlet 11 for the callee frame, which receives

the three values into the frame, initializes the frame with an empty RCV, sets the enter and leave threads and posts Thread 0, where our description began. Eventually the callee sends back its result.

The results from the recursive calls trigger Inlets 15 and 17, both of which post Thread 5, a synchronizing thread using sslot0 as a counter. The second post is successful, so when f is run the addition is performed and the result is sent back to the caller in Thread 6. This final thread also releases the frame f.

The register usage policy in this example is to have the registers vacant across potential suspension points. However, the result value is carried in a register from either Thread 1 or Thread 5 to Thread 6, since no synchronization point intervenes in either case.

This simple example illustrates the interplay between representation of parallelism, communication, synchronization, scheduling, storage management and the use of the storage hierarchy.

#### 4. IMPLEMENTATION OF TAM

This chapter describes an implementation of TAM on the CM-5 multiprocessor. TAM is codified in a pseudo machine language TL0. TL0 is a machine independent assembly language for TAM and the concrete target for the compilation from a high level parallel language. By dividing up the compilation process into two separate phases, from high level parallel language to TL0 and then from TL0 to native machine code, high level compilation issues can be isolated from the specific hardware support for threaded execution.

A TLO program is composed of code-blocks. Codeblocks in turn consist of the activation frame layout, registers, and the code for the threads and inlets which execute relative to the frame. Each frame slot and register is statically typed. The TLO storage hierarchy consists of an unlimited number of machine registers, frame storage and the global heap. TLO instructions can operate directly on registers or on the activation frame. TLO has five different instruction categories.

**ALU** instructions have three-address format and can operate on variables in registers and the local frame.

**Network Access** is provided by SEND and RECEIVE instructions. SEND is used in threads to send values to an inlet of another frame. RECEIVE instruction, which appears in an inlet, stores the message data fields into frame slots or registers.

Thread control is achieved by FORK and SWITCH instructions, and each thread is terminated by a STOP instruction.

Frame scheduling is expressed using POST and SWAP instructions.

**Heap access** is provided by IFETCH and ISTORE instructions. These instructions simply send a message to the memory controller holding the designated location. The response for a fetch is received by an inlet, but there are no explicit acknowledgments of stores.

The remainder of this chapter presents the mapping of the storage model and the implementation of these instruction categories on the CM-5 processor.

### 4.1. TL0 on the CM-5 multiprocessor

The CM-5 is a massively parallel MIMD computer based on the SPARC RISC processor chip-set (including FPU, MMU and 64 KByte direct-mapped write-through cache), 8 MBytes of local DRAM memory and a network interface. The nodes are interconnected in two identical disjoint hypertrees.

#### 4. 1. 1. Storage model

Program code is placed on every processor and the activation frames are allocated in local memory which can be kept in the cache. The heap is divided into two regions, one for small arrays which are allocated local to a node and the other for large arrays which are spread across the nodes such that logically consecutive elements are mapped onto different processors.

TL0 registers are mapped onto SPARC registers. Since TL0 does not limit the number of available registers, it is the responsibility of the code generator to spill excess TL0 registers to the activation frame. Since TL0 instructions allow frame relative addressing, operands to instructions residing in the frame must be temporarily loaded into registers. Table 4.1, summarizes the cost of accessing operands at the various levels of the storage hierarchy.

The TLO registers are implemented on the CM-5 as a flat register file in a single register window. The single register window is divided into three categories: special-function

registers, thread registers and inlet registers. The special-purpose registers are (g0-g7), as shown in Table 4.2, hold important variables and constants used by the TL0 implementation. The TL0 IP and IIP registers are both mapped to the SPARC Program Counter (PC) register. There are sixteen thread registers (i0-i7 and 10-17) which are fully under control of the register allocator. The eight inlet registers (o0-o7) are generally reserved for inlets but may be used by the register allocator between successive network polls to hold thread temporaries.

### 4. 1. 2. Arithmetic and logic instructions

Most TL0 arithmetic and logic operations map into a single machine instruction. Integer divition, and multiplication are implemented by calling the appropriate library routine. Table 4.3 summarizes the costs of the basic instructions.

# 4. 1. 3. Sending messages

The TLO SEND instruction can send a message of arbitrary length to an inlet of another frame. Since the CM-5 limits the message to three 32-bit words of arguments, the code generator will convert a SEND of longer messages into multiple sends.

The cost of SEND is shown in Table 4.4. The cost of a SEND is relatively high because the network interface (NI) is attached to the node MBUS and hence access to the NI requires uncached loads and stores. For this reason, sends to the local node are special—cased in software, even though the CM-5 hardware supports loop—back.

Table 4. 1. Access cost to each level of the local storage hierarchy on a SPARC node

| Operand (32-bits) location | access       | access costs |  |  |

|----------------------------|--------------|--------------|--|--|

|                            | instructions | cycles       |  |  |

| Register                   | 0            | 0            |  |  |

| Constant                   | 0–2          | 0–2          |  |  |

| Cache                      | 1            | 2–3          |  |  |

| DRAM                       | 1            | 20           |  |  |

Table 4. 2. Reserved special purpose registers

| Registe | er   | Function                                    |

|---------|------|---------------------------------------------|

| Zero    | (g0) | Hard-wired to 0                             |

| LCV     | (g1) | Pointer to top of local continuation vector |

| Self    | (g2) | Node ID                                     |

| FP      | (g3) | Frame pointer                               |

| Cbbase  | (g4) | Pointer to origin of current code-block     |

| Izero   | (g5) | Offset to base of heap tags                 |

| NI      | (g6) | Network Interface base address              |

| Queue   | (g7) | Pointer to frame scheduling queue           |

Table 4. 3. Mapping of TLO arithmetic and logic instructions to the SPARC

| Operation                 | costs        |        |  |

|---------------------------|--------------|--------|--|

|                           | instructions | cycles |  |

| Integer arithmetic        |              |        |  |

| Add, sub, logical         | 1            | 1      |  |

| Integer multiply          | 19–54        | 21–56  |  |

| Divide                    | 15–40        | 30–100 |  |

| Floating-point arithmetic | 1            | 5–7    |  |

# 4. 1. 4. Receiving messages

In TLO, when a message is received an inlet is invoked. The first instruction of the inlet is a RECEIVE, which specifies the frame slots where the message data is to be stored. Arrival of a message can be detected either by enabling message interrupts or by polling the network regularly. Dispatching a message interrupt into the user program incurs approximately 140 cycles of overhead and is expensive. The strategy employed in the CM-5 implementation is to explicitly poll the network once in every thread. If the thread contains an instruction which might access the network, for example SEND, then the poll is combined with that instruction. All other threads have an explicit poll inserted at the end of the thread. If a message has arrived, the appropriate inlet is called. Table 4.5 shows the cost of polling the network and the cost of running an inlet.

Table 4. 4. Cost for sending a message limited to three 32-bit arguments

| Operation                    | costs        |        |  |

|------------------------------|--------------|--------|--|

|                              | instructions | cycles |  |

| Send message to local frame  |              |        |  |

| Overhead                     | 4            | 4      |  |

| Push word                    | 1            | 1      |  |

| Send message to remote frame |              |        |  |

| Overhead                     | 10           | 25     |  |

| Push word                    | 1/2          | 4      |  |

Table 4. 5. Cost of polling the network and of running an inlet

| Operation            | costs        |        |  |  |

|----------------------|--------------|--------|--|--|

|                      | instructions | cycles |  |  |

| Explicit poll        | 3            | 9      |  |  |

| Poll as part of send | 2            | 2      |  |  |

| Message handling     |              |        |  |  |

| Inlet overhead       | 6 .          | 13     |  |  |

| Receive 32-bit word  | 11/2         | 6      |  |  |

# 4.1.5. Thread scheduling

In TLO, thread control is realized by the FORK, SWITCH, and STOP instructions. The synchronizing are distinguished from the non synchronizing threads by including a SYNC statement placed at the beginning of synchronizing threads. Although the SYNC declaration is placed at the beginning of the thread, the synchronization test (decrement and test for zero) is performed as part of the FORK instruction. Non–synchronizing FORKs do not require the decrement and test and thus are cheaper than synchronizing ones.

Conditional control flow is implemented in TL0 through compare instructions which set a boolean variable and a SWITCH instruction which forks one of two threads depending on a boolean.

# 4. 1. 6. Frame scheduling

The compiler uses default, local, remote, cyclic policies for frame allocation and default, fifo and lifo frame scheduling policies.

FALLOC instruction allocates the frame for a new activation and passes a number of arguments to its inlet 0. The choice of processor is controlled by the policy attached to the instruction. The FFREE instruction deallocates a frame, possibly the current frame. Typically, this is followed by a SWAP which terminates the current activation.

For the SPARC, the RCV is implemented using 16-bit offsets from the code-block base. The pointer to the top of the RCV is kept in the frame, not in a register. As messages for the activation arrive, inlets are executed and enable threads into the RCV using the POST instruction. The mapping of the various POST instructions onto SPARC are shown in Table 4.6. The cost of a POST (shown in Table 4.7) is generally higher than that of a FORK and depends not only on whether the target thread is synchronizing or not, but also on the state

Table 4. 6. Mapping of TAM POST instructions on to SPARC

| Operation               | SPARC instructions |                   |                                   | Cycle               |

|-------------------------|--------------------|-------------------|-----------------------------------|---------------------|

| POST a non sync. thread |                    |                   |                                   |                     |

| To a running frame      | cmp                | fp,ifp            | ;is inlet frame running           | 1                   |

| -                       | set                | Lthr-cbbase, tmp2 | ;tmp2+-thread offset              | 1                   |

|                         | be                 | isrunning         | -                                 | 1                   |

|                         |                    |                   |                                   |                     |

|                         | isrunnir           | _                 |                                   |                     |

|                         | sth                | tmp2,[lcv]        | ;Store the offset                 | 3                   |

|                         | sub                | lcv,2,lcv         | ;Decrement the pointer            | 1                   |

| To an idle frame        | cmp                | fp,ifp            | ;is inlet frame running           | 1                   |

|                         | set                | Lthr-cbbase, tmp2 | ;tmp2←thread offset               | 1                   |

|                         | be                 | isrunning         |                                   | 2                   |

|                         | ld                 | Frcv[ifp],tmp3    | tmp3←rcv top;                     | 2                   |

|                         | sth                | tmp2,[tmp3]       | ;push thread addr.                | 3                   |

|                         | cmp                | tmp3,ifp          | ;was rcv empty?                   | 1                   |

|                         | sub                | tmp3,2,tmp3       | ;update rcv                       | 1                   |

|                         | st                 | tmp3,Frcv[ifp]    | ;save back rcv                    | 3                   |

|                         | bnz                | continue          | ;nz-already enqueued              | 0                   |

|                         | st                 | que, Fqueue[ifp]  | store queue head ptr in frame     | 3                   |

|                         | mov                | ifp,que           | ;make ifp head of queue           | 1                   |

|                         | jmp                | continue          | 4                                 | 0 <sup>†</sup>      |

| To a ready frame        | cmp                | fp,ifp            | ;is inlet frame running           | 1                   |

|                         | set                | Lthr-cbbase, tmp2 | ;tmp2←thread offset               | 1                   |

|                         | be                 | isrunning         |                                   | 2                   |

|                         | 1d                 | Frcv[ifp],tmp3    | ;tmp3←rcv top                     | 2                   |

|                         | sth                | tmp2,[tmp3]       | _                                 | 3                   |

|                         | cmp                | tmp3,ifp          | ;was rcv empty?                   | 1                   |

|                         | sub                | tmp3,2,tmp3       | ;update rcv                       | 1                   |

|                         | st<br>             | tmp3,Frcv[ifp]    | ;save back rcv                    | 3<br>0 <sup>†</sup> |

|                         | bnz                | continue          | ;nz→already enqueued              | 0'                  |

| POST to a sync. thread  | 1db                | sync[ifp],tmp1    | ;Load the count into<br>reg. tmp1 | 2                   |

|                         | subcc              | tmp1,1,tmp1       | ;Decrement the count              | 1                   |

|                         | bne,a              |                   |                                   | 1 or 2              |

|                         | stb                | tmp1,sync[fp]     | ;Store the count                  | 3                   |

|                         | code for           | a nonsync. threa  | ıd                                |                     |

<sup>†</sup>POST is always the last instruction in the inlet and thus jump or branch would disappear in favor of a retl instruction from the inlet. Thus it has no cost.

Table 4. 7. Cost of TL0 frame synchronization and scheduling operations

| Operation                | costs                                                |    |  |

|--------------------------|------------------------------------------------------|----|--|

|                          | no. of instr. and memory cycles accesses(load/store) |    |  |

| Post a thread from inlet |                                                      |    |  |

| Idle frame               |                                                      |    |  |

| unsynchronizing          | 12(1/3)                                              | 18 |  |

| successful sync.         | 15(2/3)                                              | 23 |  |

| unsuccessful sync.       | 4(1 / 1)                                             | 7  |  |

| Ready frame              |                                                      |    |  |

| unsynchronizing          | 9(1/2)                                               | 14 |  |

| successful sync.         | 12(2 / 2)                                            | 19 |  |

| unsuccessful sync.       | 4(1 / 1)                                             | 7  |  |

| Running frame            |                                                      |    |  |

| unsynchronizing          | 5(0 / 1)                                             | 7  |  |

| successful sync.         | 8(1 / 1)                                             | 12 |  |

| unsuccessful sync.       | 4(1 / 1)                                             | 7  |  |

| Swap to next frame       |                                                      |    |  |

| first 3 threads          | 14                                                   | 26 |  |

| per extra 4 threads      | 6                                                    | 12 |  |

of the frame. If the frame is idle (i.e., it has no enabled threads in its RCV), then it has to be enqueued onto the ready queue. In addition for both idle and ready frames, the cost of manipulating the pointer to the top of the RCV is higher than for the LCV since it is in the frame, not a register.

If the target thread is for the running frame, then instead of pushing onto RCV, the POST instruction can push the thread onto LCV. Thus, for the cost of a compare between the FP and IFP, the cost of a POST can be brought down to that of a FORK.

If there are no enabled threads, then the leave thread of the activation is executed; it is responsible for switching to the next frame.

#### **4. 1. 7.** Heap access

TL0 provides a special syntax for issuing remote references (e.g., IFETCH and ISTORE). Each instruction specifies the base and offset of the I-structure being accessed. The expansion first calculates the node and address of the element being accessed. Then, the expansion determines if the access is a local access and if so, performs it inline. Otherwise, a request is sent to the node that contains the element. The costs of the different cases are shown in Table 4.8.

Table 4. 8. Cost of accessing global data structures with synchronization on a per-element basis

| Operation                      | costs                              |                                    |  |

|--------------------------------|------------------------------------|------------------------------------|--|

|                                | instructions                       | cycles                             |  |

| I-structure fetch              |                                    |                                    |  |

| Local, data present            | 8                                  | 11                                 |  |

| Local, data not-present        | 25                                 | 58                                 |  |

| Remote                         |                                    |                                    |  |

| Initiate request               | 18                                 | 38                                 |  |

| Service, data present          | 29                                 | 91                                 |  |

| Service, data not-present      | 39                                 | 115                                |  |

| I-structure store              |                                    |                                    |  |

| Local, no waiting fetches      | 9                                  | 15                                 |  |

| Local, waiting fetches         | 18                                 | 30                                 |  |

| Remote                         |                                    |                                    |  |

| Initiate request               | 18                                 | 38                                 |  |

| Service                        | 13                                 | 44                                 |  |

| I-structure allocate (N words) | 5+4[ <sup>N</sup> / <sub>8</sub> ] | 6+7[ <sup>N</sup> / <sub>8</sub> ] |  |

#### 4. 2. Measurements

In this section measurements obtained from running benchmark programs on a single SPARC processor are presented and analyzed. These programs were written in Id and then compiled to TAM. The TAM code is then translated to SPARC. Six benchmarks ranging from 50 to 1,000 lines are used. QS is a simple quicksort using accumulation lists. GAM-TEB is a MonteCarlo neutron transport code which is highly recursive with many conditionals. Paraffins enumerates the distinct isomers of paraffins. Simple is a hydrodynamics and

heat conduction code. Speech determines cepstral coefficients for speech processing. MMT is a simple matrix operation that involves creating two identity matrices, multiplying them and subtracting from a third.

Table 4.9 shows that the control overhead varies from 5% to 48% depending on the nature of the program. Message overhead varies from 0.5% to 11%. Message overhead goes up to 28%, depending on the scheduling, for the same benchmarks if these are run on a multiprocessor configuration with 64 processors [7]!.

#### 4. 2. 1. Control Overhead