#### AN ABSTRACT OF THE DISSERTATION OF

<u>Sunwoo Kwon</u> for the degree of <u>Doctor of Philosophy</u> in <u>Electrical and Computer Engineering</u> presented on <u>March 27, 2009</u>. Title: A Multi-Bit Hybrid DSM over Full-Scale Range without Feedback DEM.

Abstract approved: \_

#### Un-Ku Moon

Evolution of the mobile communication standards and proliferation of handheld devices mandate stringent Analog-to-Digital Converter (ADC) specifications. Among various ADCs, a  $\Delta\Sigma$  ADC is best known as a power-efficient ADC when more than 12b is required. However, a conventional discrete-time (DT)  $\Delta\Sigma$  Modulator ( $\Delta\Sigma$ M) is inadequate for low-power wideband applications due to the opamp settling requirement. Alternatively, a continuous-time (CT)  $\Delta\Sigma$ M can be used to decrease power consumption but has its own disadvantages such as clock jitter sensitivity, RC time constant variation, and excess loop delay.

The wideband modulators are often implemented as single-loop high-order modulators in a deep submicron process. The high-order modulator typically has a quantizer overloading problem as the input signal approaches to a full-scale range. A pole-optimization method can be used to extend the linear input range but it inevitably decreases signal to quantization noise ratio. This causes power penalty since it limits the maximum input power available.

Another challenge is linearizing a nonlinear multi-bit Digital-to-Analog Converter (DAC). On one hand, the DAC can be linearized by element sizing, sorting, and calibration but these increase silicon area and power consumption. On the other hand, a Dynamic Element Matching algorithm (DEM) linearizes the DAC by averaging and shaping the mismatches with minimal design overhead. However, the DEM causes additional delay inside the feedback path. This can make the modulator unstable.

In this thesis, a multi-bit 3rd-order hybrid  $\Delta\Sigma M$  with over full-scale range and no DEM in the critical feedback path is presented. Removing the DEM in the critical path enables the modulator to minimize latency in the feedback path. A digital feedforward structure allows processing the input signal over the full-scale reference voltage. Combined benefits of the CT/DT implementation help to reduce power consumption and to mitigate the loop delay. Measurement results from a prototype demonstrate the effectiveness of the proposed ideas. <sup>©</sup>Copyright by Sunwoo Kwon March 27, 2009 All Rights Reserved

#### A Multi-Bit Hybrid DSM over Full-Scale Range without Feedback DEM

by

Sunwoo Kwon

## A DISSERTATION

submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Presented March 27, 2009 Commencement June 2009 Doctor of Philosophy dissertation of <u>Sunwoo Kwon</u> presented on March 27, 2009

APPROVED:

Major Professor, representing Electrical and Computer Engineering

Director of the School of Electrical Engineering and Computer Science

Dean of the Graduate School

I understand that my dissertation will become part of the permanent collection of Oregon State University libraries. My signature below authorizes release of my dissertation to any reader upon request.

Sunwoo Kwon, Author

#### ACKNOWLEDGMENTS

Staying in Corvallis, OR for almost three years, I learned a lot of good things. These, of course, cannot be obtained without the help of people around me. I want to thank them for helping me survive during my graduate school years.

First of all, I would like to express my deepest gratitude to my advisor, Prof. Un-Ku Moon. He allowed me to come to Oregon State University (OSU) when I was a nomad. I am truly indebted for his providing financial support, giving the freedom to research any topic. His advice and help always make me think thoroughly. Without his brilliant guide and never-ending perseverance, I could not complete this work.

Prof. Ted Brekken, Prof. Pavan Kumar Hanumolu, and Prof. Huaping Liu served as my committee members. Prof. Brady Gibbons of Material Science, Department of Mechanical Engineering also served as a Graduate Council Representative. I thank them for sharing their precious time with me and for providing valuable feedbacks.

I also appreciate Prof. Kartikeya Mayaram and Prof. Gabor C. Temes for serving committee members during my early phase of Ph.D. study. Their technical comments enable me to improve my research.

Prof. Franco Maloberti from University of Pavia, Pavia, Italy who encouraged me to pursue Ph.D. degree at OSU and shared his opinion whenever I met him in conferences. I am grateful for his generosity.

My personal life has been enriched by my fellow graduate students. David Gubbins, Pavan Kumar Hanumolu (at that time, a graduate student), Christopher and Amy Hanken, Min-Gyu Kim, Jim and Thuy Le, Nema Talebbydokhti, and visiting student Won-Seok Hwang and Attila Sarhegyi, helped me settle down the town quickly. Having a cup of coffee in the afternoon, conversation, and occasional lunch/dinner with them relaxed me. Hanging around with them is one of the best memories I can recall. Also, I appreciate them for technical discussion.

I enjoyed talking to Nima Maghari, Tawfiq Musah, Hanaan Tawfiq, and Igor Vytaz (and Ira, too). Much appreciation for technical discussion but what made me more happy was talking about something even irrelevant to my research.

I am thankful to Prof. Hanumolu's students, Abhijith Arakali, Sarvesh Bang, Amr Elshazly, Rajesh Inti, and Brian Young who helped me broaden my knowledge in other fields.

Christopher Hanken, Volodymyr Kratyuk, and Igor Vytaz helped me to set up the process I used and to fix simulation issues that I could not easily solve. Discussion about the issues allowed me to understand how simulators works especially in continuous-time domain. I am grateful for their help/discussion.

Tawfiq Musah, Hari Prasath Venkatram, and Brian Young kindly proofread my dissertation and helped me to correct errors. I appreciate for their time and feedback.

Korean friends from the group (Jeong-Seok Chae, Seok-Min Jung, Youn-Jae Kook, Ho-Young Lee, Sang-Hyeon Lee, and their family members) helped me not to forget the Korean language. I also loved to have a dinner with them.

Samsung Electronics, Yongin, Korea, funded my research and fabricated my chips. Special thanks to Sang-Ho Kim, Sung-No Lee, Seung-Bin You, Ho-Jin Park, and Jae-Whui Kim.

Lytech Solutions, Inc., Salem, OR provided me an excellent PCB assembly service, although PCB footprints are tiny. I am grateful for the help.

Friends from Korea encouraged me. To name a few, Bong-Gunn, Hyeon-Min, James, Jae-Won, Jin-Seok, Jun-Young, Ki-Hyuk, Sang-Heum, Sang-Hoon, Seung-Jae, Tae-Jin, Won-Seok, and Yun-Young. Their friendship and supports are appreciated.

Finally, I want to thank my parents, my sister, and her family for their supports, patience, sacrifice and love. Without them, I could not know the joy of life and study. This thesis is dedicated to them.

## TABLE OF CONTENTS

Page

| 1. | INT  | RODUCTION                                                 | 1  |

|----|------|-----------------------------------------------------------|----|

|    | 1.1  | ADC Literature Survey                                     | 1  |

|    | 1.2  | Delta-Sigma Modulator for Wideband Application            | 2  |

|    | 1.3  | Discrete-Time and Continuous-Time Implementation          | 4  |

|    | 1.4  | Linearizing Multi-Bit Digital-to-Analog Converter         | 4  |

|    | 1.5  | Thesis Organization                                       | 5  |

| 2. |      | VIEW OF PROPERTIES AND MULTIBIT DAC LINEARIZATION HNIQUES | 6  |

|    | 2.1  | Frequency Scalability and Pole/Zero Location              | 6  |

|    | 2.2  | Clock Jitter Sensitivity                                  | 8  |

|    | 2.3  | Finite Opamp DC gain                                      | 10 |

|    | 2.4  | Finite Opamp GBW: Settling Error                          | 10 |

|    | 2.5  | Excess Loop Delay                                         | 12 |

|    | 2.6  | Finite Opamp GBW: Additional Delay                        | 13 |

|    | 2.7  | Delay Allocation                                          | 16 |

|    | 2.8  | Anti-aliasing Filtering                                   | 16 |

|    | 2.9  | Thermal Noise                                             | 18 |

|    | 2.10 | Comparison: CT versus DT Implementation                   | 20 |

|    | 2.11 | Multi-Bit DAC Linearization Techniques                    | 21 |

| 3. | PRC  | POSED $\Delta\Sigma$ MODULATOR                            | 26 |

|    | 3.1  | Modulator Specification                                   | 26 |

|    | 3.2  | Modulator Topology                                        | 26 |

## TABLE OF CONTENTS (Continued)

|    | 3.3  | Proposed Modulator                   | 31 |

|----|------|--------------------------------------|----|

|    | 3.4  | Elimination of DEM in Feedback Path  | 32 |

|    | 3.5  | Hybrid Loop Filter Implementation    | 35 |

|    | 3.6  | Over-Full-Scale Input Signal Process | 37 |

|    | 3.7  | RC Time Constant Tuning Circuit      | 38 |

|    | 3.8  | MATLAB/Simulink Modeling             | 40 |

| 4. | CIR  | CUIT IMPLEMENTATION                  | 43 |

|    | 4.1  | Loop Filter Implementation           | 43 |

|    | 4.2  | Opamps                               | 43 |

|    | 4.3  | Quantizers                           | 48 |

|    | 4.4  | Digital-to-Analog Converters         | 49 |

|    | 4.5  | RC Time Constant Tuning Circuit      | 51 |

|    | 4.6  | Digital Blocks                       | 52 |

|    | 4.7  | Modulator Simulation Result          | 54 |

| 5. | MEA  | ASUREMENT RESULTS                    | 57 |

| 6. | CON  | NCLUSION                             | 64 |

| BI | BLIO | GRAPHY                               | 65 |

#### LIST OF FIGURES

| Figu | ure                                                                                                                                                                              | Page |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

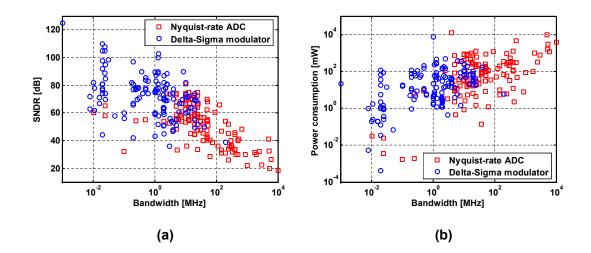

| 1.1  | Performance comparison between Nyquist-rate ADCs and $\Delta\Sigma$<br>modulators: (a) SNDR versus bandwidth and (b) Power con-<br>sumption versus bandwidth.                    |      |

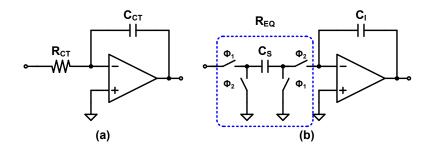

| 2.1  | Integrator implementation: (a) Continuous-time integrator and (b) Discrete-time integrator.                                                                                      |      |

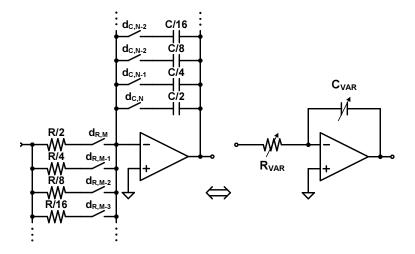

| 2.2  | RC time constant tuning circuit for a continous-time integrator using a N-bit capacitive array and a M-bit resistive array                                                       |      |

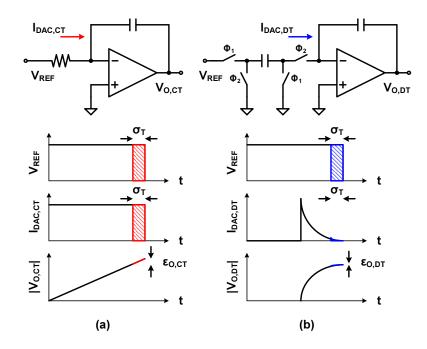

| 2.3  | DAC clock jitter effect in: (a) Continuous-time integrator and (b)<br>Discrete-time integrator.                                                                                  |      |

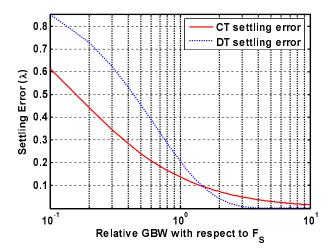

| 2.4  | GBW-induced settling error in continuous-time integrator (red solid) and discrete-time integrator (blue dotted). Opamp GBW is normalized to sampling frequency, $F_S$            |      |

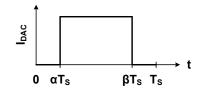

| 2.5  | Definition of $\alpha$ and $\beta$ in a current mode DAC                                                                                                                         | 12   |

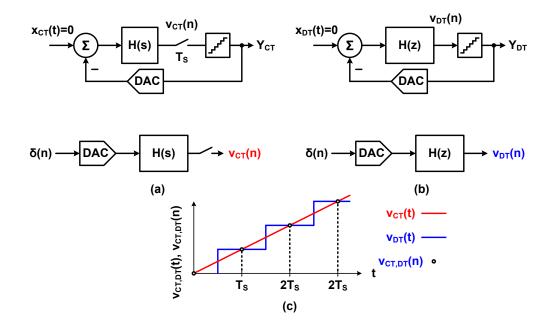

| 2.6  | Impulse response of open-loop filters: (a) Continuous-time filter<br>(b) Discrete-time filter, and (c) Output waveforms                                                          |      |

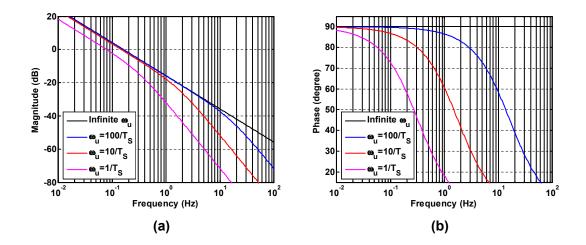

| 2.7  | Frequency response of CT integrator when finite GBW is in-<br>cluded: (a) Magnitude response and (b) Phase response                                                              |      |

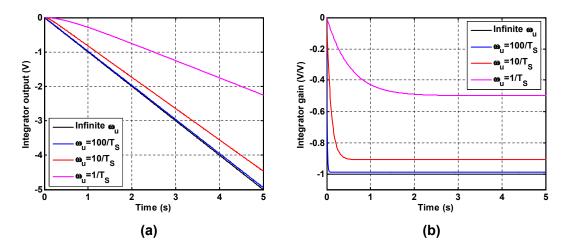

| 2.8  | Additional delay of CT integrator due to finite opamp GBW: (a)<br>Transient response when unit step applied and (b) Integrator gain<br>variation.                                | L    |

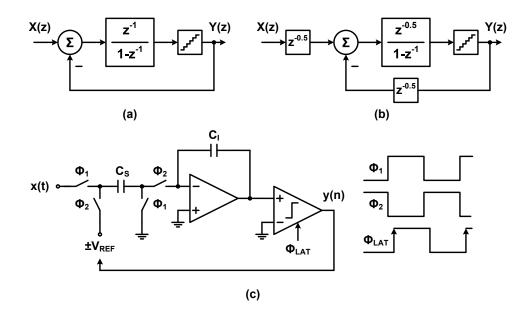

| 2.9  | Allocation of half-delay in first-order $\Delta \Sigma M$ : (a) Full-delay integrator (b) Half-delay integrator and half-delay quantizer, and (c) Circuit implementation of (b). |      |

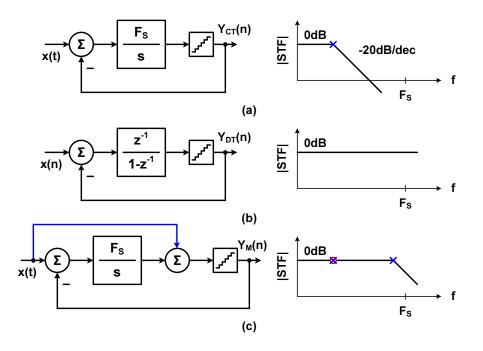

| 2.10 | Block diagram and signal transfer function magnitude response of:<br>(a) CT $\Delta \Sigma M$ (b) DT $\Delta \Sigma M$ , and (c) CT $\Delta \Sigma M$ with feedforward path.     |      |

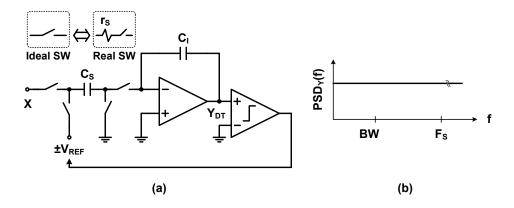

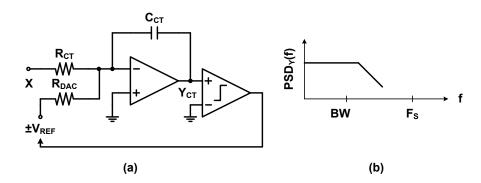

| 2.11 | First-order DT $\Delta \Sigma M$ : (a) Circuit implementation and and (b)<br>Thermal noise power spectral density due to switch resistance, re-                                  |      |

| 2.12 | First-order CT $\Delta\Sigma$ M: (a) Circuit implementation and (b) Ther-<br>mal noise power spectral density due to resistor, R <sub>CT</sub> .                                 |      |

#### LIST OF FIGURES (Continued)

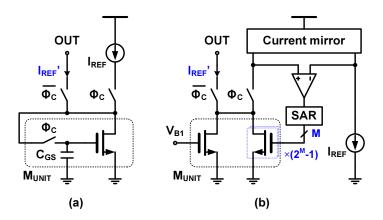

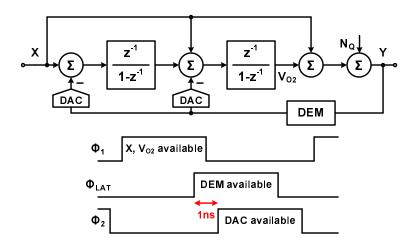

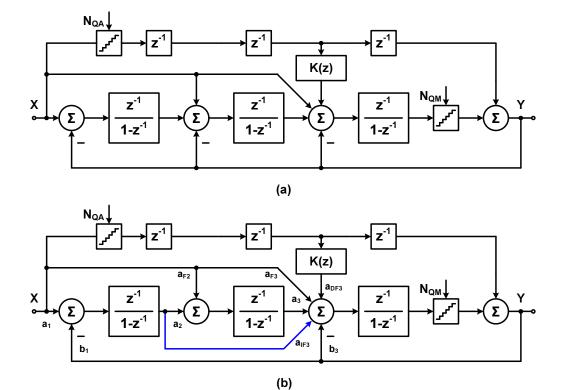

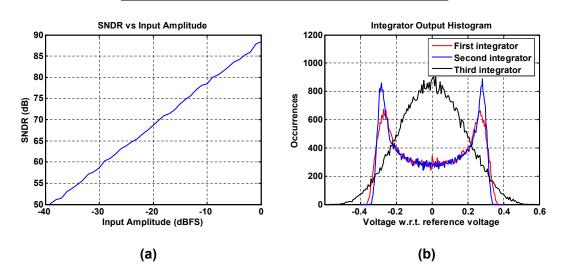

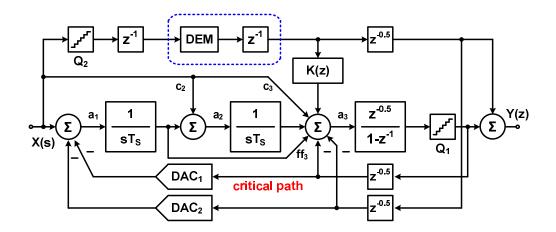

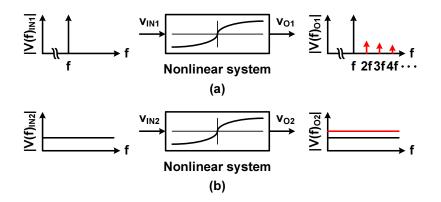

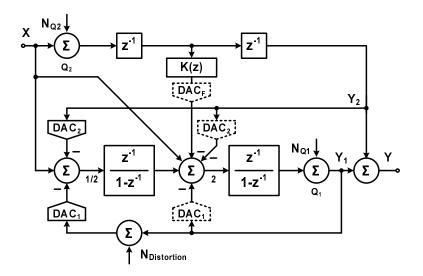

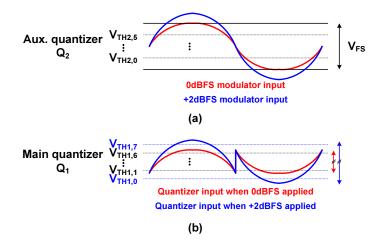

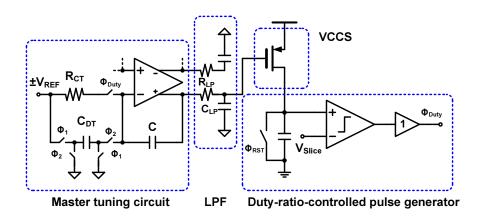

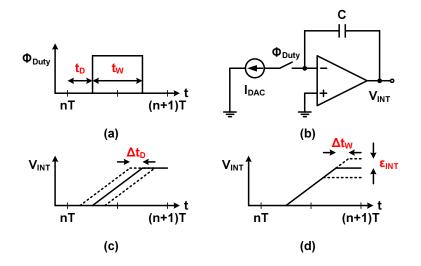

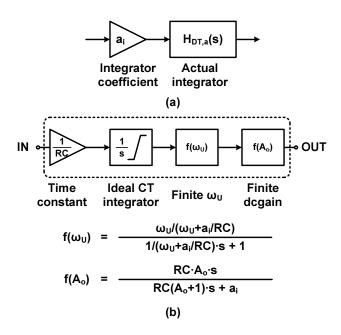

#### Figure 2.13 DAC calibration techniques in analog domain by using: (a) Transistor gate capacitance and (b) Auxiliary opamp and SAR. ..... 232.14 Second-order wideband $\Delta \Sigma M$ with timing diagram..... 243.1Third-order digital feedforward DT $\Delta \Sigma M$ : (a) With distributed feedback paths and (b) With internal feedforward path.... 293.2Third-order DT $\Delta\Sigma$ modulator: (a) SNDR versus input amplitude and (b) Integrator output histogram when a -1 dBFS sinusoidal signal is applied. 30 3.3 Proposed multi-bit 3rd-order hybrid $\Delta\Sigma$ modulator. The dotted line represents the DEM logic including finite gate delay. ..... 313.4 Nonlinear system output frequency spectra when (a) single-tone and and (b) random noise is injected. 32 Linearized model of a 2nd-order digital feedforward structure with 3.5separate DACs. 33 Frequency spectra from 3 different types of DACs combinations: 3.6(a) $DAC_{1,2}$ are 10b linear (blue dotted), (b) $DAC_1$ is 10b linear and $DAC_2$ is 14b linear (red solid), and (c) $DAC_{1,2}$ are ideal (black dashed)..... 343.7SNDR variation due to path mismatch between $DAC_{1,2}$ .... 353.8 Hybrid CT/DT loop filter implementation with a dedicated halfdelay for the quantizer. 36 3.9SRMC-based CT integrator additional delay absorption..... 36 3.10 Quantizer input waveforms when 0 dBFS and +2 dBFS signals are applied to the proposed modulator: (a) Auxiliary quantizer, $Q_2$ , and (b) Main quantizer, $Q_1$ .... 37 3.11 RC time constant tuning circuitry. ..... 39 3.12 Effect of clock jitter on a SRMC-based integrator: (a) Definition of pulse width and delay, (b) SRMC-based integrator diagram, (c) Integrator output depending on pulse delay jitter, and (d) Integrator output depending on pulse width jitter..... 39

#### Page

## LIST OF FIGURES (Continued)

| Figu | ure                                                                                                                               | Page |

|------|-----------------------------------------------------------------------------------------------------------------------------------|------|

| 3.13 | CT integrator modeling: (a) Simulink modeling block and (b)<br>Actual CT integrator modeling block.                               |      |

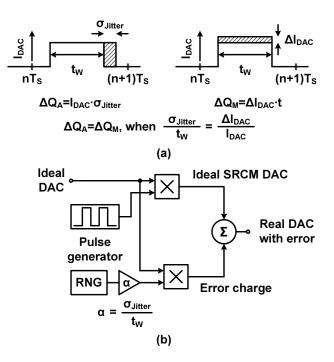

| 3.14 | DAC clock jitter modeling: (a) Actual jitter effect (left) and mod-<br>eled jitter effect (right) and (b) Real DAC modeling block |      |

| 4.1  | Proposed $\Delta \Sigma M$ loop filter implementation                                                                             | . 44 |

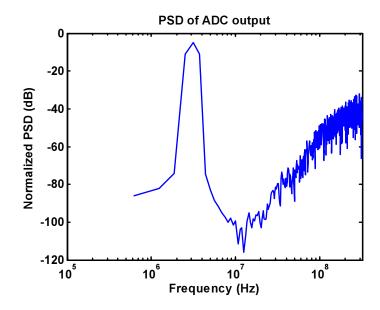

| 4.2  | Power spectral density using ideal components                                                                                     | . 45 |

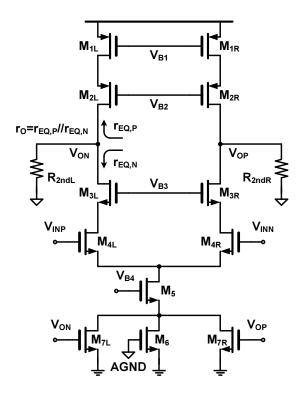

| 4.3  | Single-stage telescopic opamp for first integrator.                                                                               | . 46 |

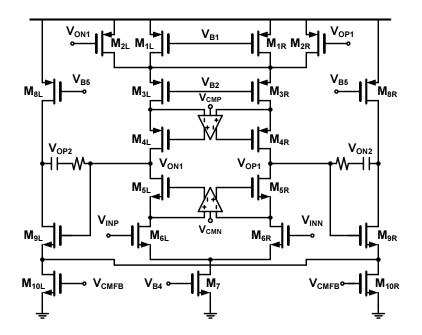

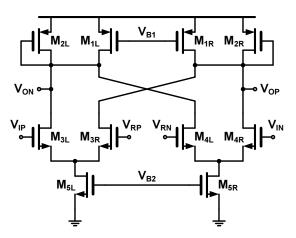

| 4.4  | Two-stage gain-boosted opamp for third integrator                                                                                 | . 47 |

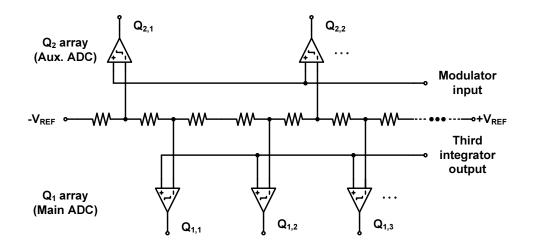

| 4.5  | Quantizer and resistive ladder configuration                                                                                      | . 48 |

| 4.6  | Four-input preamplifier                                                                                                           | . 49 |

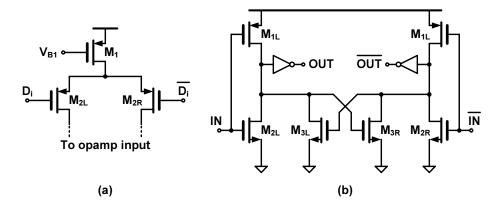

| 4.7  | Current-steering DAC: (a) DAC Unit cell and (b) DAC driver                                                                        | . 50 |

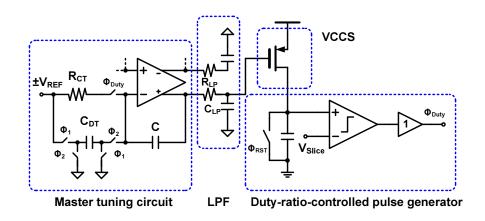

| 4.8  | RC time constant tuning circuitry                                                                                                 | . 51 |

| 4.9  | Single-ended opamp for slicer                                                                                                     | . 52 |

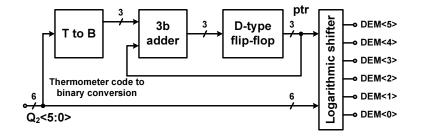

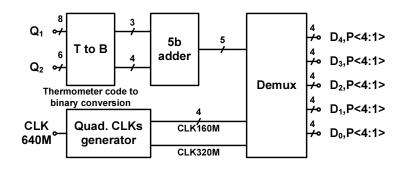

| 4.10 | Block diagram of dynamic element matching (DEM) circuit                                                                           | . 53 |

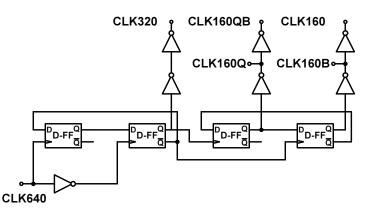

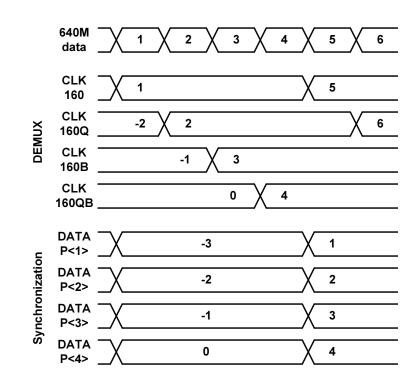

| 4.11 | Frequency divider and quadrature clock generation circuit                                                                         | . 54 |

| 4.12 | Modulator output and demuxed output timing diagram                                                                                | . 55 |

| 4.13 | Block diagram of interface circuit                                                                                                | . 55 |

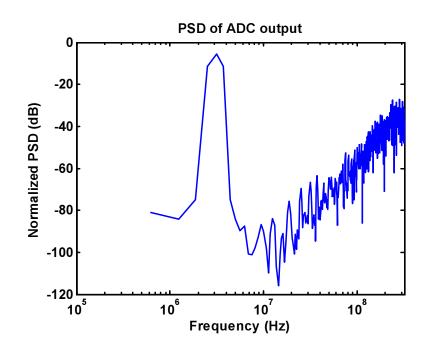

| 4.14 | Power spectral density using real components                                                                                      | . 56 |

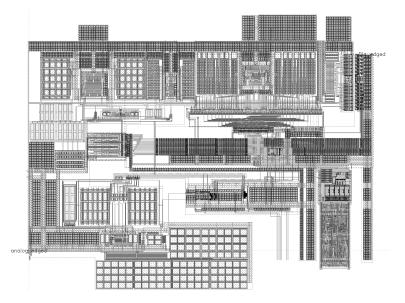

| 5.1  | Die photo (temporarily replaced with layout).                                                                                     | . 57 |

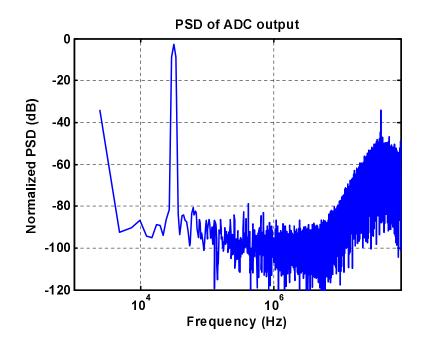

| 5.2  | Measured output spectrum when $\mathrm{F}_{\mathrm{S}}$ at 100 MHz                                                                | . 58 |

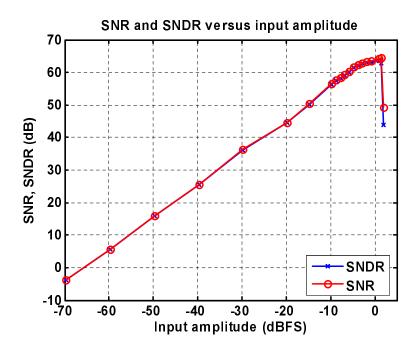

| 5.3  | Measured SNR and SNDR versus input amplitude when $F_S$ at 100 MHz                                                                |      |

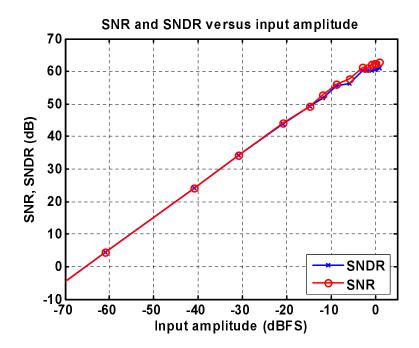

| 5.4  | Measured SNR and SNDR versus input amplitude when $F_S$ at 160 MHz                                                                |      |

| 5.5  | Measured output spectrum when $F_S$ at 160 MHz                                                                                    | . 60 |

#### D

# LIST OF FIGURES (Continued)

| Fig | ure                                                                             | Page |

|-----|---------------------------------------------------------------------------------|------|

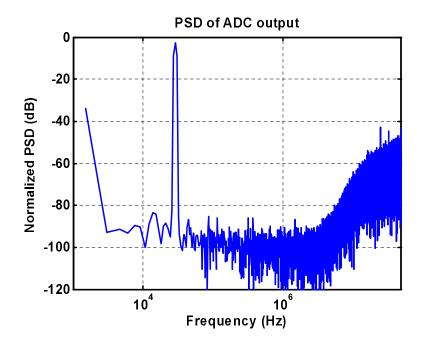

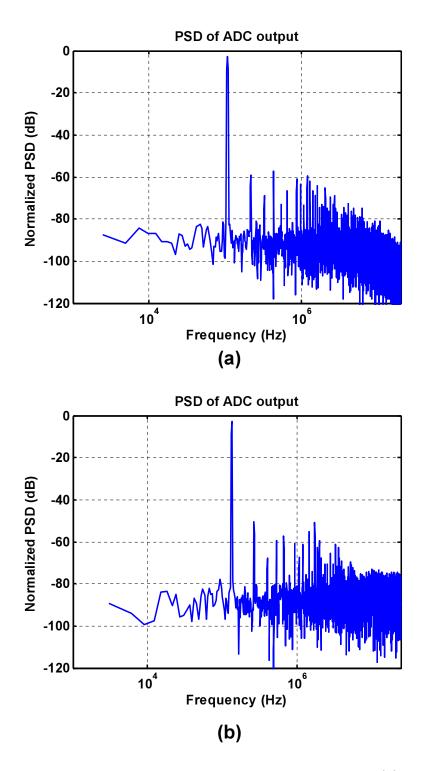

| 5.6 | Measured decimated output spectrum when $F_S$ is at: (a) 640 MH and (b) 800 MHz |      |

### LIST OF TABLES

| Tal |                                                                                                                       | Page |

|-----|-----------------------------------------------------------------------------------------------------------------------|------|

| 1.1 | 20-40 MSPS 12-14b ADC performance comparison                                                                          | 3    |

| 2.1 | Impulse-invariant transformation: s-domain equivalency for z-<br>domain pole. See Fig. 2.5 for $\alpha$ and $\beta$ . | 13   |

| 2.2 | Influence of finite $\omega_{u}$ on CT integrator                                                                     | 16   |

| 2.3 | Comparison between continuous-time and discrete-time $\Delta\Sigma Ms.$                                               | 21   |

| 3.1 | Modulator target specification.                                                                                       | 27   |

| 3.2 | Possible modulator order, OSR, and quantizer resolution                                                               | 27   |

| 3.3 | Modulator coefficient summary.                                                                                        | 30   |

| 4.1 | Opamp performance summary.                                                                                            | 48   |

| 5.1 | Performance summary of $\Delta\Sigma$ ADC, $F_S$ at 100 MHz                                                           | 61   |

| 5.2 | Performance summary of $\Delta\Sigma$ ADC, $F_S$ at 160 MHz                                                           | 63   |

# A MULTI-BIT HYBRID DSM OVER FULL-SCALE RANGE WITHOUT FEEDBACK DEM

#### CHAPTER 1. INTRODUCTION

Evolution of the mobile communication standards and proliferation of handheld devices mandate stringent Analog-to-Digital Converter (ADC) specifications: low power consumption for extended battery-operation time, wide bandwidth (BW) for fast data conversion, and high resolution/dynamic range for clear signal conversion without being corrupted by noise and interferers. As an example, one of the recent communication standards called Wireless Broadband requires signal BW larger than 9MHz and high data rate over 100Mbps [1] with minimum power consumption.

There are three candidates to meet the requirements: a pipeline ADC, a successive approximation ADC, and a  $\Delta\Sigma$  Modulator ( $\Delta\Sigma$ M). The following section helps to select which type of ADC is best suited for the above demands.

#### 1.1 ADC Literature Survey

Among various ADCs, the  $\Delta\Sigma M$  is best known as a power-efficient ADC when more than 12b is required. Fig. 1.1 shows comparison result between the Nyquist-rate ADCs and the  $\Delta\Sigma M$ s, published from 2001 to 2009. Traditionally, the  $\Delta\Sigma M$ s have been extensively utilized for low frequency applications whose signal BW is lower than several MHz ranges as demonstrated in Fig. 1.1. This is due

Figure 1.1: Performance comparison between Nyquist-rate ADCs and  $\Delta\Sigma$  modulators: (a) SNDR versus bandwidth and (b) Power consumption versus bandwidth.

to the fact that, oversampling enables the modulator to reduce capacitor size and to tolerate circuit imperfections, e.g., finite opamp DC gain and Gain-BandWidth product (GBW) and noise shaping further suppresses in-band quantization noise and circuit imperfections. Consequently, the  $\Delta\Sigma M$  comprises simple analog circuitry in concert with less stringent circuit design requirements compared with the Nyquist-rate ADCs, which allows the  $\Delta\Sigma M$  to achieve more power-efficient signal conversion. At several MHz ranges, the  $\Delta\Sigma M$ s has comparable performance to the Nyquist-rate ADCs. In the following section, it can be seen that the  $\Delta\Sigma M$  can extend signal BW over several tens MHz while maintaining its power-efficiency.

### 1.2 Delta-Sigma Modulator for Wideband Application

Recently, there are several efforts to increase  $\Delta \Sigma M$ 's signal BW. Table 1.1 compares performance of the Nyquist-rate ADC and the  $\Delta \Sigma M$  whose BW is larger than 10 MHz and Signal-to-Noise-Distortion Ratio (SNDR) is higher than 70 dB.

|                                                                         | ADC             | BW<br>[MHz] | SNDR<br>[dB] | Power<br>[mW] | FoM<br>[pJ/Cn]                        | L <sub>MIN</sub><br>[um] |

|-------------------------------------------------------------------------|-----------------|-------------|--------------|---------------|---------------------------------------|--------------------------|

|                                                                         | Honda [2]       | 15          | 71           | 102           | 1.17                                  | 0.25                     |

|                                                                         | Siragusa [3]    | 20          | 72           | 394           | 3.03                                  | 0.18                     |

|                                                                         | Matsui [4]      | 10          | 70           | 34            | 0.66                                  | 0.18                     |

|                                                                         | Liu [5]         | 10          | 74           | 233           | 2.84                                  | 0.18                     |

| Δ                                                                       | Hesner [6]      | 20          | 81           | 66            | 0.18                                  | 0.13                     |

| 0                                                                       | Moyal [7]       | 12          | 79           | 75            | 0.43                                  | 0.25                     |

| 0                                                                       | Bosi [8]        | 10          | 74           | 240           | 2.93                                  | 0.18                     |

| 0                                                                       | Mitteregger [9] | 20          | 74           | 20            | 0.12                                  | 0.13                     |

| 0                                                                       | Malla [10]      | 20          | 70           | 28            | 0.27                                  | 0.09                     |

| $FoM = \frac{Power}{2BW \cdot 2^{\left(\frac{SNDR-1.76}{6.02}\right)}}$ |                 |             |              | Oversa        | st-rate ADC<br>ampled AD<br>Sigma mod | с                        |

Table 1.1: 20-40 MSPS 12-14b ADC performance comparison..

References [2], [3], [4], [5] are pipeline ADCs. Reference [6] is an oversampled successive-approximation ADC. References [7], [8], [9], [10] are  $\Delta\Sigma$ Ms. As a metric of power efficiency, Figure of Merit (FoM) is used in the table. It is clear that the  $\Delta\Sigma$ Ms can extend BW over 10 MHz more efficiently compared to the Nyquist-rate ADCs.

However, increasing signal BW of the  $\Delta\Sigma M$  is a difficult task. This is owing to the fact that the maximum sampling frequency is usually limited by technology and that the stability of  $\Delta\Sigma M$  degrades as the order of the  $\Delta\Sigma M$  increases [11]. Given that the sampling frequency and the order of the  $\Delta\Sigma M$  are fixed, the choice of implementation method heavily affects power efficiency. The next section provides a brief comparison between Discrete-Time (DT) and Continuous-Time (CT) implementation methods.

#### **1.3** Discrete-Time and Continuous-Time Implementation

A DT  $\Delta\Sigma$ M requires higher GBW than a CT counterpart since the settling error of a CT integrator is less than that of a DT integrator, when GBW is relatively small [11]. References [8], [10] are implemented in DT domain, whereas [7], [9] are implemented in CT domain.

In spite of the power efficiency of the CT implementation, it has its own disadvantages, such as RC time constant variation, DAC clock jitter sensitivity, and excess loop delay. Hence, it is vital to understand the pros and cons of each implementation method. These are discussed in Chapter 2.

#### 1.4 Linearizing Multi-Bit Digital-to-Analog Converter

A multi-bit quantizer/DAC is frequently utilized in the recent  $\Delta\Sigma$ Ms since it provides numbers of benefits compared to a single-bit quantizer/DAC [11], [12]. Nonetheless, a physically built multi-bit DAC is inherently nonlinear, so a linearization technique should be applied so as not to degrade modulator performance. A calibration in analog domain can linearize the multi-bit DAC, but it usually increases silicon area and power consumption. On the other hand, a Dynamic Element Matching (DEM) technique [13] linearizes the DAC with minimal overhead. However, this introduces latency between the quantizer and the DAC. Consequently, at high clocking frequencies, it is difficult to perform the DEM algorithm.

The main focus of this thesis is linearizing the multi-bit DAC with minimal overhead and delay. By eliminating the DEM in the critical feedback path and by putting the DEM in a forward path, a proposed modulator can have minimized feedback latency. More details can be found in Chapter 3.

## 1.5 Thesis Organization

Chapter 2 provides review of DT and CT implementation method, and DAC linearization techniques since appreciating the design challenges is a key for successful implementation. Chapter 3 presents a novel  $\Delta\Sigma$  modulator which enables eliminating the DEM in the feedback path. Detailed system design method is provided. Circuit implementation is described in Chapter 4. Silicon measurement results are shown in Chapter 5. Conclusion for this thesis is drawn with a summary of the work.

# CHAPTER 2. REVIEW OF PROPERTIES AND MULTIBIT DAC LINEARIZATION TECHNIQUES

Design challenges in wideband  $\Delta\Sigma$ Ms and DAC linearization methods are reviewed. Several properties which impact modulator performance are discussed in this chapter.

## 2.1 Frequency Scalability and Pole/Zero Location

Integrators can be implemented in either DT or CT domain as shown in Fig. 2.1. The DT implementation, also known as Switched-Capacitor (SC) implementation, utilizes an equivalent resistor, a periodically charged/discharged capacitor. The equivalent resistance is given by (2.1). Note that the time constant of the DT implementation,  $\tau_{\rm DT}$ , is determined by clock period, T<sub>S</sub>, and relative ratio between C<sub>S</sub> and C<sub>I</sub>.

$$\tau_{DT} = R_{EQ}C_I = T_S \frac{C_I}{C_S}, \text{ where } T_S = \frac{1}{F_S}$$

$$(2.1)$$

$$\tau_{CT} = R_{CT}C_{CT} \tag{2.2}$$

On the other hand, the time constant of the CT implementation,  $\tau_{\rm CT}$ , is determined by absolute value of capacitor and resistor as shown in (2.2). Process, voltage, and temperature variation cause the time constant to deviate from an ideal value, thus a time constant tuning scheme is required for the CT implementation. The tuning scheme helps the CT integrator to have frequency scalability, but the scalability is limited by the tuning range of the scheme. Tuning circuitry can be an

Figure 2.1: Integrator implementation: (a) Continuous-time integrator and (b) Discrete-time integrator.

Figure 2.2: RC time constant tuning circuit for a continous-time integrator using a N-bit capacitive array and a M-bit resistive array.

array of resistors and/or capacitors as illustrated in Fig. 2.2, but increases silicon area due to routing and segmentation.

The discrete-time time constant,  $\tau_{\rm DT}$ , depends on the ratio between C<sub>S</sub> and C<sub>I</sub>, and sampling time which is precise. As a result, pole/zero location of the DT filter is accurately controlled to within  $\pm 0.1$  %. However, the continuous-time time constant,  $\tau_{\rm CT}$ , varies typically  $\pm 20$  % since two different materials cannot have the same variation. This variation can be controlled by the tuning circuit but the resolution of the tuning circuit still limits accurate pole/zero positioning. For

example, a time constant tuning circuit shown in Fig. 2.2 has a M+N-bit tuning accuracy. Time constant deviation from the ideal value will appear as integrator gain error and actual time constant,  $\tau_{CT,a}$ , can be expressed by

$$\frac{1}{\tau_{CT,a}} = \frac{1}{R_{CT,a}C_{CT,a}} = \frac{1}{R_{CT}C_{CT}(1+\Delta_R\Delta_C)}$$

$$\approx \frac{1}{R_{CT}C_{CT}}(1-\Delta_R\Delta_C) \text{ when } \Delta_R\Delta_C \ll 1 \qquad (2.3)$$

This gain variation changes the Noise Transfer Function (NTF) of a CT  $\Delta\Sigma M$ . As a result, integrator output swing increases (decreases) and the modulator performance improves (degrades) since a higher NTF pushes more noise to higher frequency and increases out of band gain. It is worth mentioning that the modulator becomes unstable when the time constant becomes relatively small, depending on the modulator topology and opamp swing range.

#### 2.2 Clock Jitter Sensitivity

Apart from the input path of a modulator, in which the input frequency is always less than sampling frequency, a feedback DAC path processes all the frequency contents inside the modulator loop. As a result, any jitter induced on the DAC severely deteriorates modulator performance. Fig. 2.3 shows the effect of the DAC clock jitter for two implementation methods, especially when a single-bit DAC is used. Assuming that the opamp in the CT integrator is ideal, the waveform of  $I_{DAC,CT}$  is rectangular. When the jitter is induced on  $V_{REF}$  at the falling edge by  $\sigma_T$ , the jitter decides sampling instance of  $I_{DAC,CT}$ . Consequently, the output of the CT integrator,  $V_{O,CT}$  has an error voltage,  $\varepsilon_{O,CT}$ . This error is proportional to the amount of current and jitter.

On the other hand, the waveform of  $I_{DAC,DT}$  is exponentially decaying due

Figure 2.3: DAC clock jitter effect in: (a) Continuous-time integrator and (b) Discrete-time integrator.

to the nature of charge transfer with limited speed. The time constant of this exponential behavior depends on transconductance of opamp, equivalent resistance of switches, and capacitor values. The jitter forces charge integration to stop, but the output of the DT integrator,  $V_{O,DT}$ , has less deviation since major portion of charge is already transferred to the output. This is why the DT implementation has less jitter sensitivity compared to the CT implementation.

To mitigate the DAC clock jitter in the CT integrator, a Switched-Capacitor Resistor (SCR) technique [14], [15] can be used. The SCR is a variation of the DT implementation which has a large resistor to limit a peak current value. Increasing the number of levels of the DAC also helps to decrease the jitter-induced error since the multi-bit DAC has a smaller voltage step. For example, a N-bit DAC can have a minimum voltage step of  $V_{REF}/2^{N-1}$  compared to the single-bit DAC of which voltage step is  $V_{REF}$ .

## 2.3 Finite Opamp DC gain

Finite opamp DC gain,  $A_O$ , causes not only integrator gain error,  $\lambda_{dc}$ , but also phase erorr,  $\gamma$ . The transfer function of actual DT integrator can be modeled by (2.4) [16], [17]. The CT integrator also has modified transfer function which can be modeled by (2.5). Circuit implementation of each integrator can be referred to Fig. 2.1.

$$H_{DT,a}(z) \approx (1 + \lambda_{DT,dc}) \frac{C_S}{C_I} \frac{z^{-1}}{1 - (1 + \gamma_{DT})z^{-1}}, \qquad (2.4)$$

where  $\lambda_{DT,dc} \approx -\frac{1}{\beta A_O}$  and  $\gamma_{DT} \approx -\frac{1}{\beta A_O}$

$$H_{DT,a}(s) \approx (1 + \lambda_{CT,dc}) \frac{1}{R_{CT}C_{CT}} \frac{1}{s + \gamma_{CT}}, \qquad (2.5)$$

where  $\lambda_{CT,dc} \approx -\frac{1}{A_O}$  and  $\gamma_{CT} \approx -\frac{1/R_{CT}C_{CT}}{A_O}$

#### 2.4 Finite Opamp GBW: Settling Error

The opamp is one of the most power-hungry building blocks in the  $\Delta\Sigma M$ . Hence, reducing power consumption of the opamp enables a desinger to improve power efficiency of the  $\Delta\Sigma M$ . However, decreasing GBW causes integrator gain error,  $\lambda_{GBW}$ .

First, consider an ideal DT integrator whose transfer function,  $H_{DT,i}$ , is given by (2.6). Assuming that GBW is finite and settling behavior is not limited by slew rate, the transfer function of the actual DT integrator,  $H_{DT,a}$ , is modified [16], [18]

Figure 2.4: GBW-induced settling error in continuous-time integrator (red solid) and discrete-time integrator (blue dotted). Opamp GBW is normalized to sampling frequency,  $F_S$

and given by (2.7). Note that  $\frac{C_I}{C_S+C_I}$  is the feedback factor of the DT integrator.

$$H_{DT,i}(z) = \frac{C_S}{C_I} \frac{z^{-1}}{1 - z^{-1}}$$

(2.6)

$$H_{DT,a}(z) \approx (1 + \lambda_{DT}) \frac{C_S}{C_I} \frac{z^{-1}}{1 - z^{-1}}, \qquad (2.7)$$

where  $\lambda_{DT, GBW} \approx -exp \left( -\pi \frac{C_I}{C_S + C_I} \frac{GBW}{F_S} \right)$

Now, consider an ideal CT integrator whose transfer function,  $H_{CT,i}$ , is given by (2.8). Using the same assumption and ignoring the finite delay, the transfer function of the actual CT integrator,  $H_{CT,a}$ , is modified and given by (2.9).

$$H_{CT,i}(s) = \frac{1}{sR_{CT}C_{CT}}$$

$$(2.8)$$

$$H_{CT,a}(s) \approx (1 + \lambda_{CT}) \frac{1}{sR_{CT}C_{CT}},$$

$$where \ \lambda_{CT,\ GBW} \approx -\frac{1/R_{CT}C_{CT}}{\omega_{T}} = -\frac{1/R_{CT}C_{CT}}{2\pi GBW}$$

$$(2.9)$$

Comparing (2.7) with (2.9) reveals that, as GBW decreases,  $\lambda_{DT, GBW}$  grows exponentially and  $\lambda_{CT, GBW}$  grows linearly. Fig. 2.4 shows the settling errors

Figure 2.5: Definition of  $\alpha$  and  $\beta$  in a current mode DAC.

depending on the finite GBW in both integrators. It is assumed that both integrators have the same gain of 1 and the same sampling frequency. When  $\text{GBW}_{\text{CT}} =$  $\text{GBW}_{\text{DT}} = \text{F}_{\text{S}}$ ,  $\lambda_{CT, \ GBW}$  is 0.137 and  $\lambda_{DT, \ GBW}$  is 0.208. Although this comparison depends on a DT integrator feedback factor and a CT integrator coefficient, its tendency for the CT integrator to require less GBW remains unchanged.

#### 2.5 Excess Loop Delay

The CT  $\Delta\Sigma M$  has a well known problem of excess loop delay [19]. This problem results from additional delay in the feedback paths around a quantizer. As a result, the transfer function of a CT loop filter is not equivalent to that of a DT loop filter. The speed of the feedback is limited by the regeneration time of a latch, DAC switching logic, and opamp delay. This is explained in Section 2.6. Depending on amount of the delay, the order of the  $\Delta\Sigma M$  may increase, thus causing the modulator to become unstable [19].

To mitigate the problem, the transfer functions of the CT and DT loop filter should match each other. This can be achieved by a impulse-invariant transformation method [19]. The transformation is shown in Table 2.1 and the definition of  $\alpha$  and  $\beta$  is demonstrated in Fig. 2.5. When the same impulse is applied to each loop filter, the outputs of each filters should be identical as illustrated in Fig. 2.6.

| z-domain pole        | s-domain                                                                                     | s-domain when $z_k = 1$                                       |

|----------------------|----------------------------------------------------------------------------------------------|---------------------------------------------------------------|

| $\frac{1}{z-z_k}$    | $\frac{r_o}{s-s_k} \times \frac{1}{z_k^{1-\alpha} - z_k^{1-\beta}}$                          | $\frac{r_o}{s}$                                               |

|                      | $r_0 = s_k$                                                                                  | $r_0 = \frac{1}{\beta - \alpha}$                              |

| $rac{1}{(z-z_k)^2}$ | $\frac{r_1 s + r_0}{(s - s_k)^2} 	imes \frac{1}{z_k (z_k^{1 - \alpha} - z_k^{1 - \beta})^2}$ | $\frac{r_1s+r_0}{s^2}$                                        |

|                      | $r_1 = q_1 s_k + q_0$                                                                        | $r_1 = \frac{1}{2} \frac{\alpha + \beta - 2}{\beta - \alpha}$ |

|                      | $r_0 = q_1 s_k^2$                                                                            | $r_0 = \frac{1}{\beta - \alpha}$                              |

|                      | $q_1 = z_k^{1-\beta}(1-\beta) - z_k^{1-\alpha}(1-\alpha)$                                    |                                                               |

|                      | $q_0 = z_k^{1-\alpha} - z_k^{1-\beta}$                                                       |                                                               |

Table 2.1: Impulse-invariant transformation: s-domain equivalency for z-domain pole. See Fig. 2.5 for  $\alpha$  and  $\beta$ .

Previous efforts to alleviate the problem are summarized in [19]: Returnto-Zero DAC, coefficient tuning, and direct feedback path. Recent compensation methods are based on the direct feedback compensation technique [20]: analog compensation with dedicated adder [21], digital compensation [22], analog compensation merged in last integrator [9], [23]. Although these techniques effectively compensate the excess loop delay, loop filter synthesis becomes complicated [9]. On the other hand, the DT  $\Delta\Sigma$ M can easily alleviate the problem. More details are shown in Section 2.7.

## 2.6 Finite Opamp GBW: Additional Delay

As mentioned briefly in Section 2.4, the finite opamp GBW causes integrator gain error, as shown in Fig. 2.7 (a). Furthermore, the CT integrator has a different

Figure 2.6: Impulse response of open-loop filters: (a) Continuous-time filter (b) Discrete-time filter, and (c) Output waveforms.

phase response as shown in Fig. 2.7 (b). The phase shift can be modeled by (2.10).

$$H_{CT,a}(s) \approx H_{CT,i}(s) \frac{1}{s+\tau_D}, \text{ where } \tau_D \approx \frac{1}{\omega_u + 1/R_{CT}C_{CT}}$$

(2.10)

The phase shift introduces additional delay in time domain,  $\tau_{\rm D}$ , which makes the loop filter slow. Consequently, it contributes to the excess loop delay. Fig. 2.8 demonstrates the influence of the additional delay in the CT integrator depending on unity-gain radian frequency,  $\omega_{\rm u}$ . Table 2.2 summarizes the effect of the finite  $\omega_{\rm u}$ . Notice that the lower  $\omega_{\rm u}$  is, the longer is the delay. This delay causes additional error at the output of the CT integrators. As an example, when  $\omega_u = \frac{1}{T_s}$ , expected output voltage at 4 s (0.5×4) is equal to -2 V but the output actually becomes -2 V at 4.5 s.

Although the additional delay can be considered during the transformation phase, the delay can vary after fabrication. This uncertainty causes a peaking

Figure 2.7: Frequency response of CT integrator when finite GBW is included: (a) Magnitude response and (b) Phase response.

Figure 2.8: Additional delay of CT integrator due to finite opamp GBW: (a) Transient response when unit step applied and (b) Integrator gain variation.

around half the sampling frequency [9], [24], [25]. Depending on the location of the peaking, the out of band gain increases or decreases. As a result, the modulator has a different swing range.

|                                  | Infinite $\omega_{\rm u}$ | $\omega_{\rm u} = \frac{100}{T_{\rm S}}$ | $\omega_{\rm u} = \frac{10}{T_{\rm S}}$ | $\omega_{\rm u} = \frac{1}{T_{\rm S}}$ |

|----------------------------------|---------------------------|------------------------------------------|-----------------------------------------|----------------------------------------|

| Ideal integrator gain(V/s)       | 1                         | 1                                        | 1                                       | 1                                      |

| Actual integrator gain(V/s)      | 1                         | 0.990                                    | 0.909                                   | 0.500                                  |

| Expected output voltage @ 5 s    | 5                         | 4.95                                     | 4.54                                    | 2.50                                   |

| (actual gain (V/s) $\times$ 5 s) |                           |                                          |                                         |                                        |

| Actual output voltage @ 5 s      | 5                         | 4.95                                     | 4.46                                    | 2.25                                   |

| Delay (ms)                       | 0                         | 9.9                                      | 90.9                                    | 500.0                                  |

Table 2.2: Influence of finite  $\omega_{u}$  on CT integrator.

#### 2.7 Delay Allocation

Unlike the CT  $\Delta\Sigma$ Ms, the DT  $\Delta\Sigma$ Ms can easily overcome the excess loop delay problem. As an example, Fig. 2.9 (a) shows a first-order  $\Delta\Sigma$ M with a fulldelay integrator. The full-delay can be split into two half-delays. One of them can be allocated to the integrator and the other to the quantizer as illustrated in Fig. 2.9 (b). Its circuit implementation is shown in Fig. 2.9 (c).

### 2.8 Anti-aliasing Filtering

Actual sampling of the CT  $\Delta\Sigma$ M occurs at the quantizer. The nature of the CT integrator offers an inherent low-pass filtering function, as illustrated in Fig. 2.10 (a). This filtering offers an *inherent* Anti-Aliasing Filtering (AAF). In case of the distributed feedback structure [12], the order of AAF is equal to the number of integrators.

Figure 2.9: Allocation of half-delay in first-order  $\Delta\Sigma M$ : (a) Full-delay integrator (b) Half-delay integrator and half-delay quantizer, and (c) Circuit implementation of (b).

On the other hand, the DT  $\Delta\Sigma$ M samples the signal on sampling capacitor, C<sub>S</sub>, as shown in 2.9 (c). Moreover, the signal transfer function (STF) of a DT  $\Delta\Sigma$ M is a form of all pass filter as shown in Fig. 2.10 (b). As a result, any blocker that goes into the modulator corrupts signal conversion, unless an explicit AAF exists in front of the DT  $\Delta\Sigma$ M.

Although the frequency of the blocker signal varies from system to system, it is worth noting that a feedforward path in the CT  $\Delta\Sigma M$  diminishes the inherent AAF function since the feedforward path creates a zero in STF. Furthermore, a direct feedforward from the DT modulator input to quantizer input tends to cause out-of-band signal peaking unless carefully designed [26]. The peaking increases the requirement of an AAF to achieve comparable amount of blocker suppression.

Figure 2.10: Block diagram and signal transfer function magnitude response of: (a) CT  $\Delta \Sigma M$  (b) DT  $\Delta \Sigma M$ , and (c) CT  $\Delta \Sigma M$  with feedforward path.

### 2.9 Thermal Noise

Practically, thermal noise from resistor/active element is a limiting factor which keeps a  $\Delta\Sigma M$  from achieving expected Signal to Quantization Noise Ratio (SQNR). This is due to the fact that thermal-noise-limited design helps to save power consumption. This section provides thermal noise limitation of each implementation. The following comparison assumes that resistors are the only noise sources and modulator are implemented in single-ended fashion.

A DT integrator processes thermal noise due to periodic sampling with switch that has a resistance,  $r_s$ , as shown in Fig. 2.11 (a). The noise directly appears at the output,  $Y_{DT}$ , since the gain of STF is equal to 1, shown in Fig. 2.11 (b). Noise power at  $Y_{DT}$  is given by (2.11). (This noise varies depending on opamp

Figure 2.11: First-order DT  $\Delta\Sigma$ M: (a) Circuit implementation and (b) Thermal noise power spectral density due to switch resistance,  $r_s$ .

Figure 2.12: First-order CT  $\Delta \Sigma M$ : (a) Circuit implementation and (b) Thermal noise power spectral density due to resistor,  $R_{CT}$ .

transconductance and the resistance [11] but is assumed to be 2kT/C here.)

$$v_{n,DT}^2 \approx \frac{2kT}{C_S} \frac{1}{OSR}$$

(2.11)

A CT integrator also has thermal noise from input resistor,  $R_{CT}$ , as illustrated in Fig. 2.12 (a). The thermal noise from the resistor is low-pass filtered by the integrator unlike the DT  $\Delta\Sigma M$ . However, this shaped noise still can be considered as white noise since power spectral density is flat within the bandwidth of interest as shown in Fig. 2.12 (b). As a result, the noise power within the BW can be described by

$$v_{n,CT}^{2} = 4kTR_{CT} \times BW = 4kTR_{CT} \times \frac{F_{S}}{2OSR}$$

$$= 4kTR_{CT} \times \frac{1}{R_{CT}C_{CT}} \times \frac{1}{2OSR}, if 1/R_{CT}C_{CT} = 1/F_{S}$$

$$= \frac{2kT}{C_{CT}}\frac{1}{OSR}$$

(2.12)

Eq. (2.11) and (2.12) can be generalized assuming that input path and feedback path have the same component values. Let  $\alpha_{\rm DT} = \frac{C_{\rm S}}{C_{\rm I}}$  and  $\alpha_{\rm CT} = \frac{1}{R_{\rm CT}C_{\rm CT}}\frac{1}{F_{\rm S}}$ , where  $\alpha$  is the gain of each integrator.

$$v_{n,DT}^{2} \approx \frac{2kT}{\alpha_{DT}C_{I}} \frac{1}{OSR}$$

$$v_{n,CT}^{2} = \frac{2kT}{\alpha_{CT}C_{CT}} \frac{1}{OSR}$$

(2.13)

Note that the CT  $\Delta\Sigma$ M does not sample any signal at Y<sub>CT</sub> before the quantizer. Once sampled by the quantizer, the noise power due to R<sub>CT</sub> will decrease depending on the ratio between noise cut-off frequency and sampling frequency [27].

It should be mentioned that the DT integrator shown in Fig. 2.11 can share  $C_S$  for input sampling and feedback DAC operation. On the other hand, the CT modulator cannot share  $R_{CT}$  and  $R_{DAC}$ . Thus, the DT  $\Delta\Sigma M$  with the capacitor sharing scheme can have less noise assuming that the sharing does not introduce significant signal distortion. (Although the concept of distortion is different from that of noise, distortion can be an actual performance limiting factor.)

### 2.10 Comparison: CT versus DT Implementation

Various properties of the CT and DT  $\Delta\Sigma$ Ms are reviewed. Comparison results are summarized in Table 2.3, where  $\beta$  is the feedback factor of a DT integrator  $\left(\frac{C_I}{C_S+C_I}\right)$ .

|                                 | $\mathrm{CT}\ \Delta\Sigma\mathrm{M}$                         | DT $\Delta \Sigma M$                                                   |  |

|---------------------------------|---------------------------------------------------------------|------------------------------------------------------------------------|--|

| Frequency scalability           | No                                                            | Yes                                                                    |  |

| Time constant variation         | $\pm 20~\%$                                                   | $<\pm0.1~\%$                                                           |  |

| DAC clock jitter sensitivity    | Poor                                                          | Fair                                                                   |  |

| Integrator gain error (GBW)     | $-\frac{1/R_{CT}C_{CT}}{2\pi GBW}$                            | $-\exp\left\{-\pi\frac{\beta \text{GBW}}{\text{F}_{\text{S}}}\right\}$ |  |

| Integrator gain error (DC gain) | $-\frac{1/R_{CT}C_{CT}}{A_O}$                                 | $-\frac{1}{\beta A_{O}}$                                               |  |

| Integrator phase error          | $-\frac{1/R_{CT}C_{CT}}{A_O}$                                 | $-\frac{1}{\beta A_{O}}$                                               |  |

| Integrator delay                | $\frac{1}{\omega_{\rm u}+1/{\rm R}_{\rm CT}{\rm C}_{\rm CT}}$ | $z^{-0.5} \text{ or } z^{-1}$                                          |  |

| Quantizer delay compensation    | Required                                                      | Not required                                                           |  |

| Delay allocation                | Complicated                                                   | Easy                                                                   |  |

| Inherent AAF effect             | Yes                                                           | No                                                                     |  |

| Thermal noise                   | $\frac{2kT}{OSR \cdot C_{CT}}$                                | $\frac{2kT}{OSR\cdot C_S}$                                             |  |

Table 2.3: Comparison between continuous-time and discrete-time  $\Delta \Sigma Ms$ .

# 2.11 Multi-Bit DAC Linearization Techniques

In spite of several advantages of a multi-bit quantizer/DAC over a single-bit quantizer/DAC [12], the multi-bit DAC should be linearized to overcom process gradient. Otherwise, it directly degrades modulator performance since it is located at the front-end of the modulator. There are various DAC linearization techniques. This section reviews some of the techniques.

#### Element Sizing

The simplest linearization technique is increasing element size [28]. Increasing the size reduces random variation, thus improving linearity. Mismatch between DAC element can be calculated by (2.14),

$$\frac{\sigma(I_D)}{I_D}[\%] = \left[\frac{\sigma^2(\beta)}{\beta} + \frac{4\left\{100\sigma(V_{TH})\right\}^2}{(V_{GS} - V_{TH})^2}\right]^{0.5}$$

$$= \left[\frac{A_\beta^2}{WL} + \frac{4A_{TH}^2}{WL(V_{GS} - V_{TH})^2}\right]^{0.5}$$

(2.14)

where  $\beta$ , V<sub>TH</sub>, V<sub>GS</sub>, A<sub> $\beta$ </sub>, and A<sub>TH</sub> are current factor, transistor threshold voltage, gate-source voltage, current coefficient, and threshold voltage coefficient, respectively. The general rule is that every doubling device size improves linearity by 0.5b. However, matching property is highly sensitive to temperature, voltage and layout pattern. As a result, linearity is limited to around 13b or so [29], [30]. For the case of a current-steering DAC in a submicron process, the accuracy is further compromised by gate leakage current since the device size is so large [31].

#### Element calibration in analog domain

This method separately measures and tunes each element using analog circuitry [32]. Fig. 2.13 (a) demonstrates a basic principle: during calibration mode  $(\Phi_{\rm C})$ , the reference current, I<sub>REF</sub> is converted into a voltage and then the voltage is stored on C<sub>GS</sub>. During normal operation mode ( $\overline{\Phi_{\rm C}}$ ), the stored voltage acts as an bias voltage, thus, generating a matched current. However, this requires a frequent update since the gate voltage drops otherwise. Fig. 2.13 (b) shows a solution for the leaky gate voltage. With the help of a successive approximation register (SAR) logic, comparison results are stored in a static storage. In spite of

Figure 2.13: DAC calibration techniques in analog domain by using: (a) Transistor gate capacitance and (b) Auxiliary opamp and SAR.

high linearity more than 12b, the method increases power consumption and area due to additional transistor array (blue dotted box), opamp, and SAR logic.

## Element Sorting

Sorting technique uses an algorithm: evaluate, sort, sum, re-sort, and arrange (or pick just matched element instead of sum, re-sort, and arrange) [33], [34], [35]. It also reduces random error since this dynamic sequencing is executed after chip fabrication. However, the technique utilizes complex biasing and routing schemes which increases parasitic capacitance. The large parasitic capacitance degrades settling behavior and introduces harmonics at high frequency. Furthermore, massive number of registers is necessary to store the evaluated result, especially when each DAC element is segmented to small size.

Figure 2.14: Second-order wideband  $\Delta \Sigma M$  with timing diagram.

#### Dynamic Element Matching

A Dynamic Element Matching (DEM) has been frequently utilized in  $\Delta\Sigma$ Ms since the nonlinearity from the multi-bit DAC is high-pass filtered. Moreover, it can be easily implemented by using simple digital circuits, such as shifter and adder. As a result, the DEM consumes negligible amount of power while it helps to achieve excellent linearity [36].

However, the DEM increases latency in the DAC feedback path, which can cause instability of the modulator. This is due to the fact that the latency aggravates the excess loop delay as mentioned in Section 2.5. As an example, a data-weighted average technique for a 4b DAC implemented in 0.18  $\mu$ m CMOS eats up approximately 1 ns [37] in the feedback path. Considering the finite regeneration time of latches and the setup/hold times of flip-flop, the feedback path delay tends to be significant in high-speed operation. This can be demonstrated with the help of Fig. 2.14. Ideally, the DEM should be executed before the DAC operation starts (or during the nonoverlapping phase between  $\Phi_1$  and  $\Phi_2$ ), but it burdens the opamps when the execution takes more time. In other words, the opamps should be much faster to guarantee proper settling during the DAC operation. It should be noted that the CT  $\Delta\Sigma M$  has the same problem although the DT modulator is shown as an example. Practically, the latency in the CT  $\Delta\Sigma M$  is more detrimental since it usually operates at much higher sampling frequency.

The DEM latency has became one of the main bottlenecks on implementing  $\Delta\Sigma$ Ms [38], [39]. The main contribution of this thesis is proposing a novel  $\Delta\Sigma$ M without the DEM latency problem while the power consumption of the modulator is minimized.

Hybrid  $\Delta\Sigma$  modulator system design is discussed in this chapter. Modulator requirements are specified and a suitable topology is selected to meet the design requirements. A novel Delta-Sigma modulator is proposed to have low latency in the feedback path. To solve the problems of a CT and a DT implementation, a hybrid implementation is presented with a RC time constant tuning scheme. Moreover, processing input signal over a full-scale range is described. MATLAB/Simulink modeling method is also discussed.

## 3.1 Modulator Specification

As a demonstration vehicle, Wireless Broadband is chosen. Although signal BW of 9 MHz and 12b resolution satisfies its ADC requirement [1], the design specification for this work is further extended to show fast clocking operation. Table 3.1 summarizes the new specifications. Power consumption includes the modulator, and a RC tuning circuit which facilitates operating frequency of CT integrators.

## 3.2 Modulator Topology

The most difficult task in this design is achieving 20 MHz BW. Table 3.2 shows possible candidates for the target specification by varying modulator order, OverSampling Ratio (OSR), and quantizer resolution. An 87 dB peak Signal-to-

| Bandwidth         | 20 MHz     |

|-------------------|------------|

| SNDR              | > 74  dB   |

| Power supply      | 1.2 V      |

| Design process    | 65 nm CMOS |

| Power consumption | < 40  mW   |

Table 3.1: Modulator target specification.

Table 3.2: Possible modulator order, OSR, and quantizer resolution.

| Order                      | 2nd  | 2nd  | 3rd  | 3rd  | 4th  | 4th  |

|----------------------------|------|------|------|------|------|------|

| Guaranteed Stability       | Yes  | Yes  | No   | No   | No   | No   |

| Quantizer resolution (bit) | 4    | 5    | 4    | 5    | 4    | 5    |

| Oversampling ratio         | 33   | 25   | 16   | 13   | 11   | 9    |

| SQNR (dB)                  | 88.3 | 88.6 | 88.2 | 88.2 | 88.8 | 87.2 |

| Sampling frequency (MHz)   | 1032 | 1000 | 640  | 520  | 440  | 360  |

Quantization-Noise Ratio (SQNR) is assumed to account for design margin. SQNR for each case is obtained based on (3.1) assuming a sinusoidal input signal applied

$$SQNR (dB) = 10 \log \left[ \frac{0 dBFS \ signal \ power}{Quantization \ noise \ power} \right]$$

$$= 10 \log \left[ \frac{3(2k+1)OSR^{2k+1}(2^N-1)^2}{2\pi^{2k}} \right], \qquad (3.1)$$

where k and N are modulator order and quantizer resolution, respectively.

Remember that improving the resolution of quantizer increases quantizer/DAC design complexity, unless quantization noise truncation and cancellation/suppression are applied [40], [41]. A 4b quantizer is selected since it enhances SQNR with rea-

sonable design complexity.

The order of a modulator influences the stability of the modulator [12]. Pole optimization can be used to decrease the out-of-band gain, hence improving stability, but degrades SQNR. To counteract this degradation, zero optimization can be used [11]. However, this requires well matched passive components with relatively large ratio between a resonator path and integrator path. This is due to the fact that the location of the zero directly impacts SQNR. Moreover, the zero optimization increases in-band noise power due to additional component. Hence, no pole-zero optimization is used in this work.

Another factor that should be considered is clock frequency. Although the second order modulator guarantees stability, clock frequency of over 1GHz brings out another issue of inherent transistor switching speed. The switching speed is determined by the ratio of the transistor transconductance to its gate-source capacitance. The fourth-order modulators are clocked at lower frequency but they are more prone to a quantizer overload problem and may suffer from instability. Consequently, modulator design is based on third-order, 4b quantizer with 640 MHz clocking frequency and OSR of 16.

Once the order, quantizer, and OSR are fixed, a proper structure should be chosen. Among various structures published so far, a digital feedforward structure [42] is selected since this structure can achieve high power efficiency by decreasing the total number of comparators and by reducing internal signal swing at each integrator. Fig. 3.1 (a) shows a linearized block diagram of the chosen modulator topology. Although this modulator is able to reduce the total number of comparators, the output swing of second integrator is relatively large compared to a reference voltage. This is due to the fact that modulator has an STF equal to  $z^{-3}$ , instead of a high-pass filter form which introduces STF out-of-band peaking. The

Figure 3.1: Third-order digital feedforward DT  $\Delta \Sigma M$ : (a) With distributed feedback paths and (b) With internal feedforward path.

wide swing range of the second integrator can be processed by using a two-stage opamp but this mandates more power consumption.

To mitigate the swing requirement, the internal feedforward path,  $a_{IF3}$ , is introduced while the second feedback path is removed as illustrated in Fig. 3.1 (b). This topology allows to use a single-stage opamp in the second integrator. Table 3.3 lists the coefficients for a DT prototype. Fig. 3.2 shows SQNR versus input amplitude and histogram of each integrator output when a -1 dBFS sinusoidal signal is applied. As demonstrated, the modulator can process a large signal up to 0 dBFS. This is due to the fact that the auxiliary quantizer,  $Q_A$ , quantizes the

|                   | $a_i$ | $\mathbf{b_i}$ | $a_{Fi}$ | $a_{\rm DFi}$ | $a_{\rm IFi}$ |

|-------------------|-------|----------------|----------|---------------|---------------|

| First integrator  | 1/3   | 1/3            | -        | -             | -             |

| Second integrator | 1     | -              | -1/3     | -             | -             |

| Third integrator  | 3     | 3              | 1        | -1            | 9             |

Table 3.3: Modulator coefficient summary.

Figure 3.2: Third-order DT  $\Delta\Sigma$  modulator: (a) SNDR versus input amplitude and (b) Integrator output histogram when a -1 dBFS sinusoidal signal is applied.

input signal, X, and only the residue of the quantizer is fed into the loop filter. In other words, the loop filter always processes a small signal compared to the reference. As a result, the main quantizer,  $Q_M$ , never becomes saturated. This is explained in more detail in Section 3.6.

Figure 3.3: Proposed multi-bit 3rd-order hybrid  $\Delta\Sigma$  modulator. The dotted line represents the DEM logic including finite gate delay.

#### 3.3 Proposed Modulator

The proposed multi-bit 3rd-order hybrid  $\Delta\Sigma M$  is illustrated in Fig. 3.3. The proposed modulator is based on [42]. In conventional  $\Delta\Sigma M$ s, the DEM is inside the feedback path, denoted as *critical path* in Fig. 3.3, which causes extra delay. Instead, the proposed  $\Delta\Sigma M$  has the DEM in the forward path since the delays in the forward path can be utilized for executing the DEM. The first two integrators are continuous-time (CT) integrators to reduce power consumption and the last integrator is a discrete-time (DT) integrator to alleviate the loop delay and the quantizer timing problem [9], [24]. The main quantizer, Q<sub>1</sub>, is effectively a 4b quantizer which uses a 9-level quantizer (+2 dBFS) instead of a 7-level quantizer (0 dBFS). Adding two more comparators enables the proposed modulator to process over full scale signal. Detailed descriptions on each method are explained in the following Sections.

K(z) is a noise cancellation filter [42] and merged with the last DT integrator

Figure 3.4: Nonlinear system output frequency spectra when (a) single-tone and and (b) random noise is injected.

to relieve digital hardware complexity. The auxiliary quantizer,  $Q_2$ , is a 3b, 7-level quantizer. The front-end DACs are switched-mode current-steering DACs. The internal feedforward path, ff<sub>3</sub>, is used to reduce the swing of the second integrator and to remove second feedback DACs. Third DACs are implemented by a switchedcapacitor DAC.

## 3.4 Elimination of DEM in Feedback Path

The output of a  $\Delta\Sigma$ M always contains an input signal plus shaped quantization (random) noise. Fig. 3.4 shows output frequency spectra of a nonlinear block (here, nonlinear DAC) when a single-tone and random noise are applied to the block. Fig. 3.4 (a) can be explained by a simple mathematical equation [43]. Fig. 3.4 (b) can be understood intuitively. Each frequency content introduces its own harmonics as in the single-tone case. However, the harmonics from each content will be spread over the entire BW, since random noise has an almost equal amount of frequency content over a given BW. As a result, random noise just increases the

Figure 3.5: Linearized model of a 2nd-order digital feedforward structure with separate DACs.

noise floor when it passes through the nonlinear block instead of creating tones.

For the sake of simplicity, a linearized model of a 2nd-order digital feedforward structure is shown in Fig. 3.5 to demonstrate how the DEM can be eliminated in the critical path. Assume, for now, that  $Q_2$  and DAC<sub>2</sub> are ideal. Each integrator only processes random noise since the input signal, X, and the output of DAC<sub>2</sub>, Y<sub>2</sub>, cancel each other. Consequently, Y<sub>1</sub> only contains the *random quantization error*. DAC<sub>1</sub> raises noise floor instead of creating harmonics as a lowdistortion structure is less susceptible to nonlinear opamp gain [44]. However, the limited resolution of Q<sub>2</sub> and DAC<sub>2</sub> prevents the input signal from being canceled. As a result, Y<sub>1</sub> contains the input signal but the signal power is attenuated as shown in (3.2).

$$Y_1 = (1 - z^{-2})X + z^{-2}N_{Q2} + (1 - z^{-1})^2N_{Q1}$$

(3.2)

Although a 3rd-order modulator is utilized for the actual implementation, the prop-

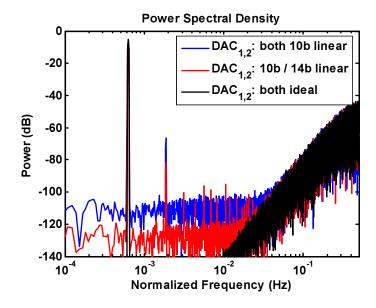

Figure 3.6: Frequency spectra from 3 different types of DACs combinations: (a)  $DAC_{1,2}$  are 10b linear (blue dotted), (b)  $DAC_1$  is 10b linear and  $DAC_2$  is 14b linear (red solid), and (c)  $DAC_{1,2}$  are ideal (black dashed).

erty shown in (3.2) remains unchanged. System-level simulations are performed and Fig. 3.6 shows frequency spectra with different DAC linearity. A 10b linear DAC is typical and can be achieved without much effort. A 14b DAC can be easily obtained from the 10b DAC by applying the DEM. Case (a) shows a high third harmonic due to 10b linearity from DAC<sub>2</sub>. Case (b) has a smaller third harmonic but has multiple high-order harmonics. These high-order harmonics come from the  $Q_2$  since the quantization noise from this quantizer,  $N_{Q2}$ , is not fully randomized.

The fact that random noise only raises the noise floor implies that the nonlinear effect due to random noise can be tolerable, since performance of a  $\Delta\Sigma M$  is often limited by thermal noise and/or DAC clock jitter. Usually SQNR is higher than SNR. The error generated by the nonlinear DAC which processes only quantization noise, affects SNR marginally as long as the increased noise floor is not comparable to thermal noise and/or DAC clock jitter.

Figure 3.7: SNDR variation due to path mismatch between  $DAC_{1,2}$ .

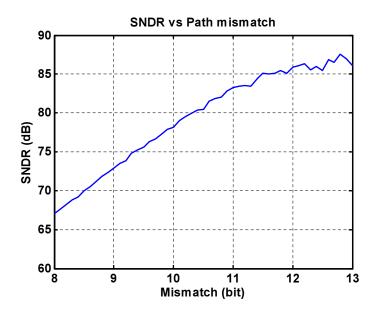

Path mismatch between  $DAC_{1,2}$  degrades modulator performance owing to the leakage from N<sub>Q2</sub>. However, a 9-10b path mismatch is sufficient enough to obtain a 12b ENOB as demonstrated in Fig. 3.7. In this simulation, a -2 dBFS input sinusoidal signal is applied, thus maximum SQNR achievable is 87 dB.

## 3.5 Hybrid Loop Filter Implementation

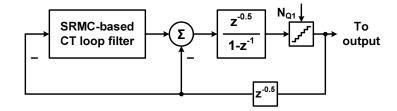

The DT integrator employs a half-delay for the main quantizer,  $Q_1$ , as shown in Fig. 3.8. As a result, the quantizer in the critical path can have relaxed timing (a dedicated half-delay), hence mitigating the excess loop delay problem. The bias current requirement of the integrator is relaxed due to capacitor scaling and linear settling. Furthermore, it eliminates a possible timing problem from the quantizer [24] since the DT integrator output remains constant during latching phase.

Figure 3.8: Hybrid CT/DT loop filter implementation with a dedicated half-delay for the quantizer.

Figure 3.9: SRMC-based CT integrator additional delay absorption.

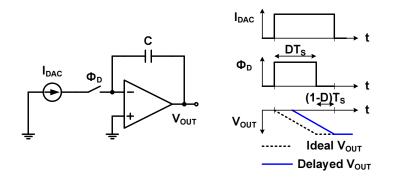

The first two CT integrators are incorporated with the Switched-R-MOSFET-C scheme (SRMC) to tune the RC time constant [45] and to desensitize them from DAC clock jitter [36], since it is the pulse width variation of the tuning clock that alters the output of the integrators. Furthermore, it enables the integrator to absorb the finite opamp delay as illustrated in Fig. 3.9. Note that the delay results from the finite opamp GBW. Although the finite GBW decreases integrator gain, it is not illustrated in the figure. Assume that a clock duty ratio is D, where D<0.9. The rest of clock period,  $(1 - D)T_s$ , can be used to buffer the delay.

Figure 3.10: Quantizer input waveforms when 0 dBFS and +2 dBFS signals are applied to the proposed modulator: (a) Auxiliary quantizer, Q<sub>2</sub>, and (b) Main quantizer, Q<sub>1</sub>.

## 3.6 Over-Full-Scale Input Signal Process

As shown in (3.2), the last integrator mainly processes the quantization errors. This means that the main quantizer,  $Q_1$ , is relatively free from the modulator input amplitude. When the modulator input is equal to or less than  $V_{\text{REF}}$ , shown in Fig. 3.10 (a), the outputs of each integrator are well bounded. This is due to the fact that the auxiliary quantizer,  $Q_2$ , chops off the modulator input signal and the loop filter always sees a smaller signal, red solid line, as illustrated in Fig. 3.10 (b). Now, assume a large signal over the full-scale is applied to the modulator. In Fig. 3.10 (a), a +2 dBFS is applied, blue solid line. As long as each integrator and the main quantizer,  $Q_1$ , can handle increased swing ranges, the modulator is not overloaded [46], [47].

Various system-level simulations show that, without noise transfer function pole optimization, the last integrator swings  $\pm 0.5$  V<sub>REF</sub> when a 0 dBFS input signal applied and that the modulator does not show any overload, which would lead to selecting the 7-level quantizer, corresponding threshold levels from  $V_{TH1,1}$  to  $V_{TH1,6}$ in Fig. 3.10 (b). Noticing that the first two integrators have smaller swing ranges  $(\pm 0.3/0.4 V_{REF})$  than the last one, this margin can be utilized to maximize the modulator power efficiency. Two additional comparators can be used to accommodate an increased swing range for  $Q_1$ , thus the 4b-equivalent 9-level quantizer, corresponding threshold levels from  $V_{TH1,0}$  to  $V_{TH1,7}$ , is selected to convert a +2 dBFS input signal. However, further input amplitude increase may cause a reverse diode turn-on when the input amplitude is larger than power supply rails. In this design, the nominal power supply and reference voltages are 1.2 V and 2 V<sub>PP</sub>, respectively.

#### 3.7 RC Time Constant Tuning Circuit

The time-constant tuning circuitry is an important building block since a CT filter can have a different filter response depending on the time constant. In this design, the SRMC technique is used to tune the time constant [45]. Fig. 3.11 shows a simplified circuit diagram of the tuning circuit. It comprises a master tuning circuit which has a CT/DT integrator, a RC low-pass filter, a voltage-controlled current source (VCCS), and a duty-ratio-controlled pulse generator. The final output,  $\phi_{\text{Duty}}$ , is fed to the master circuit as well as a slave circuit, the SRMC-based CT integrators in the loop filter. Detailed operational principle can be found in [45].

Furthermore, the tuning circuitry desensitizes the modulator from the clock jitter coming from an external clock source [36]. The external clock jitter only shifts the starting instance of  $\phi_{\text{Duty}}$ . The actual pulse width jitter of  $\phi_{\text{Duty}}$  is purely decided by thermal noise and switching noise of the tuning circuitry itself. This can be understood with the help of Fig. 3.12. A solid line represents the

Figure 3.11: RC time constant tuning circuitry.

Figure 3.12: Effect of clock jitter on a SRMC-based integrator: (a) Definition of pulse width and delay, (b) SRMC-based integrator diagram, (c) Integrator output depending on pulse delay jitter, and (d) Integrator output depending on pulse width jitter.

integrator output under ideal case (no jitter) and a dotted line for the jitterinfluenced output. As shown in Fig. 3.12 (c), the pulse delay jitter only changes the starting instance. As a result, the output value remains the same. However, the pulse width jitter affects the output as shown in Fig. 3.12 (d). The pulse width jitter changes the actual integration time, thus preventing the integrator

Figure 3.13: CT integrator modeling: (a) Simulink modeling block and (b) Actual CT integrator modeling block.

from having a correct output.

# 3.8 MATLAB/Simulink Modeling

The properties of the CT and DT integrator have been reviewed in the previous chapter. This section describes how the effects prevalent in the CT integrators can be modeled in MATLAB/Simulink. Modeling method for the DT integrators can be referred to [48]. DAC clock jitter effect is also modeled in this section.

#### CT Integrator

Fig. 3.13 (a) shows a Simulink block diagram which includes the finite GBW and DC gain effects in actual CT integrators. Fig. 3.13 (b) further illustrates how the actual integrator can be modeled. The gain block is for a given sampling frequency (or time constant). The ideal CT integrator block has a clipping ability to mimic an opamp output swing range available. Following mathematic blocks generate the output value depending on the finite GBW and DC gain.

Note that this modeling has limitations since it is based on linear analysis and assumptions. Especially, opamp nonlinearity modeling needs more attention. Although the opamp nonlinearity can be modeled by using either an arctangent function or a high-order polynomial expansion, such as  $x + a_3x^3 + a_5x^5 \cdots$  assuming that x is the opamp output value, the nonlinearity of a transistor-level opamp may be quite different from the modeled nonlinearity.

#### DAC Clock Jitter

Fig. 3.14 (a) shows the actual effect caused by jitter and modeled jitter effect. It is difficult add jitter to the Simuilnk pulse generator block since the pulse width cannot be controlled in random manner. Instead, DAC current has a random variation. As long as  $\frac{\sigma_{\text{Jitter}}}{t_{\text{W}}} = \frac{\Delta I_{\text{DAC}}}{I_{\text{DAC}}}$ , the error charges for both cases equal to each other. Fig. 3.14 (b) demonstrates how the jitter effect is modeled in the block. It receives an ideal DAC value at each sample and the pulse generator creates a fixed pulse width,  $t_{\text{W}}$ , with an amplitude of 1. The DAC value is also multiplied by a random number for each sampling period which is produced by

Figure 3.14: DAC clock jitter modeling: (a) Actual jitter effect (left) and modeled jitter effect (right) and (b) Real DAC modeling block.

the random number generator (RNG) followed by a weight,  $\frac{\sigma_{\text{Jitter}}}{t_{\text{W}}}$ . Two multiplied values are summed together to create a jitter-induced error charge plus the ideal DAC value.

A possible error is integration slope variation. However, this is not problematic since the output of the SRMC-based integrator remains constant once  $\phi_{\text{Duty}}$ is off. In other words, this error is negligible since the output is sampled by the following DT integrator where only the final output affects the loop filter response. Circuit implementation is discussed in this chapter. Simulation results for the building blocks and for the modulator are shown.

# 4.1 Loop Filter Implementation

Fig. 4.1 shows loop filter implementation. The two CT integrators are active RC integrators to ease the design. The DT integrator shares the input sampling capacitor with the DAC capacitor to save power consumption. The noise cancelation filter, K(z), is merged into the DT integrator. The pulse width of  $\Phi_{CT}$  can be arbitrary, but the rising edge of the clock must be synchronized with the rising edge of  $\Phi_1$ . Note that the DEM in the forward path and integrator input common-mode feedback circuits [36] are not shown for simplicity.

To verify the functionality of the proposed modulator, ideal circuit components are used to implement the modulator. Fig. 4.2 shows power spectral density from the *ideal* modulator. SNDR is 86dB when a -3 dBFS sinusoidal signal is applied. Input frequency is 3.125 MHz.

## 4.2 Opamps

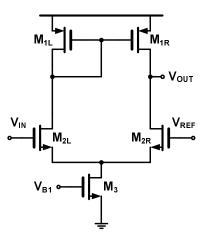

The first opamp requires 30 dB DC gain and 1000 MHz GBW. A single-stage telescopic opamp can be a possible candidate for this purpose since the opamp requires a small signal swing range, moderate DC gain, and large GBW. However,

Figure 4.1: Proposed  $\Delta \Sigma M$  loop filter implementation.

Figure 4.2: Power spectral density using ideal components.