### **Open Access Articles**

## An efficient technique for excess loop delay compensation in continuous-time $\Delta\Sigma$ modulators

| The Faculty of Oregon State University has made this article openly available. |  |

|--------------------------------------------------------------------------------|--|

| Please share how this access benefits you. Your story matters.                 |  |

| Citation     | Zhang, Y., Chen, C. H., & Temes, G. C. (2013). Efficient technique for excess loop delay compensation in continuous-time ΔΣ modulators. Electronics Letters, 49 (24), 1522-1523. doi:10.1049/el.2013.3470 |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DOI          | 10.1049/el.2013.3470                                                                                                                                                                                      |

| Publisher    | The Institution of Engineering and Technology                                                                                                                                                             |

| Version      | Accepted Manuscript                                                                                                                                                                                       |

| Citable Link | http://hdl.handle.net/1957/47384                                                                                                                                                                          |

| Terms of Use | http://cdss.library.oregonstate.edu/sa-termsofuse                                                                                                                                                         |

# An efficient technique for excess loop delay compensation in continuous-time $\Delta \Sigma$ modulators

### Y. Zhang, C.-H. Chen and G.C. Temes

A highly-digital technique is proposed for excess loop delay (ELD) compensation in multi-bit continuous-time  $\Delta\Sigma$  modulators. A digitally controlled reference switching matrix is used to replace the powerhungry signal adder and extra DAC driving the quantizer, which are commonly used in ELD compensation. With the proposed technique, the feedback DAC is embedded in the quantizer and implemented by a few switches. Thus it allows low voltage and low-power operation.

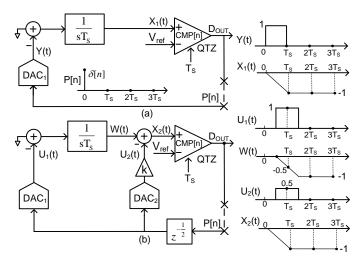

Introduction: Continuous-time (CT)  $\Delta\Sigma$  modulators suffer from excess loop delay (ELD) due to the nonzero delay between the quantizer clock edge and the time when a change in output bit is seen at the feedback node in the modulator [1]. Delay compensation methods described in the literature implement an extra fast direct local feedback path around the quantizer or change the filter coefficients with different feedback DAC pulse shapes [1]-[3]. Figure 1 shows the block diagrams and impulse responses of a first-order loop filter with and without ELD compensation. By introducing an extra direct feedback path around the quantizer, the impulse responses of both loop filters can be matched at the sampling instants as shown in Figs.1(a) and (b).Then,

$$X_{2}(t)\Big|_{t=nTs} = W(t)\Big|_{t=nTs} - U_{2}(t)\Big|_{t=nTs} = X_{1}(t)\Big|_{t=nTs}$$

(1)

This compensation technique makes the allowable quantizer time delay relaxed to half a clock period. Moreover, any signal-dependent quantizer delay is absorbed by the re-timing block in front of DAC<sub>2</sub>. However, this ELD compensation technique requires both an added feedback DAC<sub>2</sub> and a power-hungry signal adder at the input of the quantizer.

*Proposed Reference Switching Technique:* In Fig. 1(b), the output bitstream  $D_{OUT}$  is given by:

$$D_{OUT} = sgn[X_2(t) - V_{ref}] = sgn\{W(t) - [V_{ref} + U_2(t)]\}$$

(2)

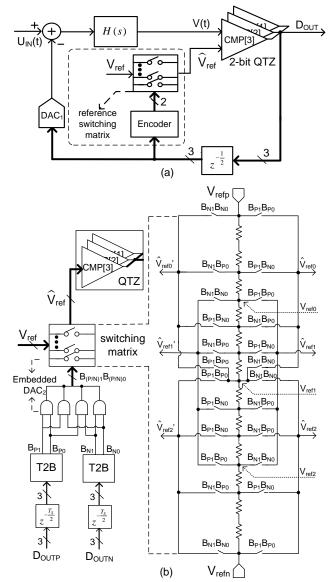

where sgn(·) = 1 when (·) > 0, otherwise sgn(·) = 0. Note that in the term  $V_{ref} + U_2(t)$  in (2),  $V_{ref}$  denotes the fixed reference levels whereas  $U_2(t)$ , the output of DAC<sub>2</sub>, denotes the reference levels controlled by  $D_{OUT}$ . The combination of the two terms is equivalent to generating a group of discrete reference levels modulated by  $D_{OUT}$ . In other words, for each sampling clock cycle, the fixed reference levels in the reference string are shifted by an amount which is determined by the output data  $D_{OUT}$ . This translates into the proposed technique shown in Fig.2(a). A switching matrix, which is digitally controlled by the binary coded output  $D_{OUT}$ , replaces the direct feedback DAC<sub>2</sub> and the signal adder before the quantizer shown in Fig. 1(b). Figure 2(b) shows more details.

In Fig. 2(b), let  $V_{FS} \triangleq V_{refp} - V_{refn}$ , where  $V_{FS}$  is defined as the fullscale range of DAC<sub>2</sub>. Thus the differential full-scale range of DAC<sub>2</sub> is $(-V_{FS}, V_{FS})$ . The resulting 2-bit feedback DAC<sub>2</sub> levels are thus given by  $\left[-V_{FS}, -\frac{V_{FS}}{3}, \frac{V_{FS}}{3}, V_{FS}\right]$ . Therefore the possible values of  $U_2$  in (2), which are the amounts of differential reference shift, are given by:

$$U_{2}(D_{OUT}) = k \cdot \left[-V_{FS}, -\frac{V_{FS}}{3}, \frac{V_{FS}}{3}, V_{FS}\right]$$

$$= \left[-\frac{V_{FS}}{2}, -\frac{V_{FS}}{6}, \frac{V_{FS}}{6}, \frac{V_{FS}}{2}\right]$$

(3)

where k = 0.5 is the feedback coefficient of the DAC<sub>2</sub> in Fig. 1(b). According to (3), the interval between adjacent levels in the reference string is  $\frac{V_{FS}}{12}$  for differential implementation. The fixed  $V_{ref}$  values for the 2-bit quantizer are denoted in Fig. 2(b). The control logic of the

**Fig.1** Impulse response of the first-order loop filter (a) without ELD compensation; (b) with ELD compensation (direct feedback path k=0.5).

**Fig.2** (a) Proposed ELD compensation technique with reference switching matrix (b) Implementation of reference switching matrix with control logic

reference switching matrix is shown in the left side of the Fig. 2(b), in which two thermometer-to-binary blocks and four AND gates are

employed. This whole process is equivalent to introducing an implicit feedback  $DAC_2$  in the reference switching matrix.

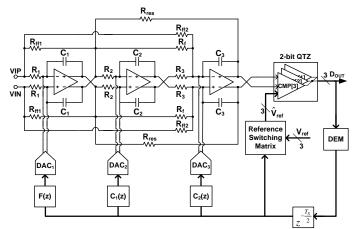

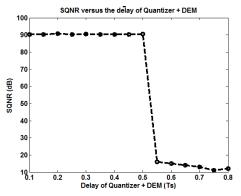

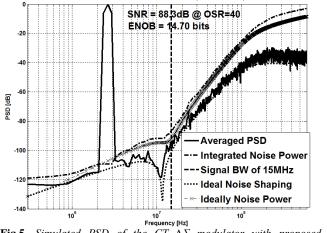

Simulation results: A 3<sup>rd</sup> order CT  $\Delta\Sigma$  modulator in Fig. 3 was fully designed and simulated on the transistor level to verify the proposed ELD compensation technique. It is a combined feed-forward and feedback topology with a non-return-to-zero (NRZ) FIR feedback DAC. The modulator is clocked at 1.2 GHz and the signal bandwidth is 15 MHz. With the proposed ELD compensation, half a clock period is allocated to the delay of quantizer and dynamic element matching (DEM). Figure 4 shows the SQNR as a function of the sum of the quantizer and DEM delays. It indicates that the maxim tolerable delay is around  $\frac{T_S}{2}$ . The simulated PSD is shown in Fig. 5 with a -1.9 dBFS input signal of 2.6 MHz. The achieved SQNR is about 88.3 dB.

**Fig.3.**  $3^{rd}$ -order  $CT \Delta \Sigma$  modulator with proposed ELD compensation

**Fig.4.** SQNR versus sum of the quantizer delay and DEM of the  $CT \Delta \Sigma$  modulator with the proposed ELD compensation

**Fig.5.** Simulated PSD of the CT  $\Delta\Sigma$  modulator with proposed ELD compensation technique

Conclusion: An excess loop delay compensation technique is proposed for multi-bit CT  $\Delta\Sigma$  modulator. A reference switching matrix, together with simple control logic, is used for the ELD compensation. This technique avoids the use of a power-hungry signal adder and an added feedback DAC as commonly used in the conventional ELD compensation scheme. The proposed technique was verified by the simulated example of a 3<sup>rd</sup>-order CT  $\Delta\Sigma$  modulator.

Acknowledgments: This research was supported by Maxim Integrated. The authors would like to acknowledge Geir Ostrem, Nancy Qian, Phillip Elliott and Ed Liu from Maxim Integrated for the useful discussions.

Y. Zhang, C. H. Chen and G. C. Temes (Department of Electrical and Computer Science, Kelley Engineering Centre, Oregon State University, Corvallis, OR 97331-5501, USA))

E-mail: zhangy7@eecs.oregonstate.edu

#### References

- Cherry J.A. and Snelgrove, W.M.: 'Excess loop delay in continuous-time delta-sigma modulators', *IEEE Trans. Circuits* Syst. II, Analog Digit. Signal Process., 1999, 46, (4), pp. 376-389

- Gao W., Shoaei O., and Snelgrove W.: 'Excess loop delay effects in continuous-time delta-sigma modulators and the compensation solution', in *Proc. IEEE Int. Symp. Circuits Syst.*, 1997, vol. 1, pp.65-68

- Singh V., et al.: 'A 16MHz BW 75 dB DR CT ΔΣ ADC compensated for more than one cycle excess loop delay,' *IEEE J. Solid-State Circuits*, Aug. 2012, vol. 47, (8), pp. 1884-1895