#### TRANSISTOR DC AMPLIFIER DESIGN THEORY

by

GERALD FRANK MCGOWAN

A THESIS

submitted to

OREGON STATE COLLEGE

in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE

June 1960

APPROVED:

# Redacted for Privacy

Assistant Professor of Electrical Engineering

Redacted for Privacy

Heed of Electrical Engineering Department

Redacted for Privacy

Chairman of School Graduate Committee

# Redacted for Privacy

Dean of Graduate School

Date Thesis is presented August 4, 1959

Typed by Patricia Malango

#### ACKNOWLEDGMENT

The research which was done in preparation for this paper was accomplished under the direction of Assistant Professor Leonard J. Weber. The author would like to express his sincere appreciation to Professor Weber for his guidance and constructive criticisms.

Since the work presented in this paper is a part of the research sponsored by the Oregon State College Engineering Experiment Station, the author is grateful to Mr. Milosh Popovich, head of the Engineering Experiment Station, and his staff.

Also to be acknowledged are the generous assistance and cooperation of Professor Louis N. Stone, head of the Electrical Engineering Department, other staff members of the Electrical Engineering Department, and the staff of the Oregon State College library.

## TABLE OF CONTENTS

|                                                                                          | Page           |

|------------------------------------------------------------------------------------------|----------------|

| INTRODUCTION                                                                             | 1              |

| DERIVATION OF DC AMPLIFIER REQUIREMENTS                                                  | 3<br>3<br>7    |

| Practical Considerations                                                                 | 8              |

| DISCUSSION OF TRANSISTOR OPERATIONAL CHARACTER -                                         | 11             |

| Physical Characteristics                                                                 | 11             |

| Bias Stabilization                                                                       | 17             |

| ANALYSIS OF DC AMPLIFIER SYSTEMS Direct-Coupled Configurations                           | 22<br>29       |

| Optimum System Analysis                                                                  | 33             |

| CIRCUIT DESIGN ANALYSIS OF THE OPTIMUM SYSTEM  Preliminary Design Layout                 | 36<br>36<br>38 |

| AC Amplifier Design Considerations Demodulator Design Analysis                           | 57<br>60       |

| Output DC Amplifier Design Requirements                                                  | 63             |

| DC Amplifier Results                                                                     | 66<br>66<br>84 |

| CONCLUSIONS                                                                              | 88             |

| General Discussion Possibilities For Future Work                                         | 88<br>91       |

| BIBLIOGRAPHY                                                                             | 93             |

| APPENDIX I. Illustrations of Test Results                                                | 96             |

| APPENDIX II. Derivation of General Operational Amplifier Error Relationship              | 108            |

| APPENDIX III. Derivation of Integrating Operational Amplifier Network Error Relationship | 113            |

| APPENDIX IV. Derivation of Differentiating<br>Operational Amplifier Network Error        |                |

| Relationship                                                                             | 115            |

## LIST OF FIGURES

| Figure |                                                                                                                        | Page |

|--------|------------------------------------------------------------------------------------------------------------------------|------|

| 1.     | An Operational Voltage Amplifier                                                                                       | 3    |

| 2.     | An Operational Current Amplifier                                                                                       | 4    |

| 3.     | A Common-Emitter Single Battery Biasing Circuit                                                                        | 18   |

| 4.     | A Direct-Coupled Single-Sided DC Amplifier                                                                             | 23   |

| 5.     | A Differential DC Amplifier                                                                                            | 27   |

| 6.     | Chopper Stabilized DC Amplifier Systems                                                                                | 30   |

| 7.     | DC Chopper Amplifier Configurations                                                                                    | 31   |

| 8.     | A Specific DC Chopper Amplifier Block Diagram                                                                          | 36   |

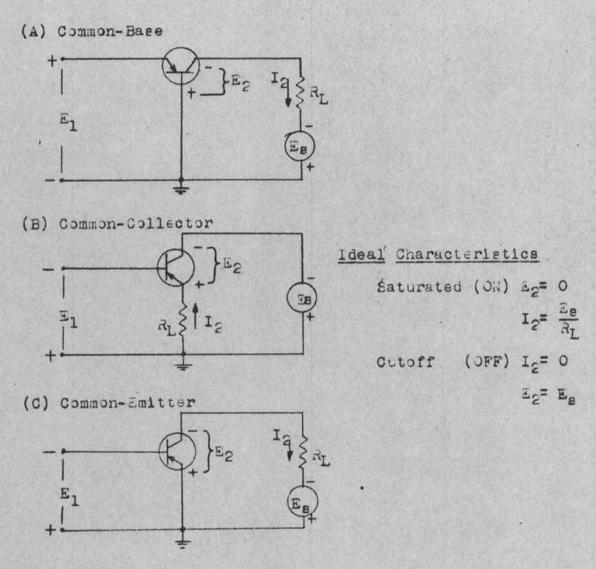

| 9.     | The Basic Switch Configurations                                                                                        | 40   |

| 10.    | Idealized PNP Common-Emitter Character-<br>istic Curves                                                                | 42   |

| 11.    | The Series-Pair Switch                                                                                                 | 44   |

| 12.    | The Shunt Series-Pair Switch, Inverted Connection                                                                      | 46   |

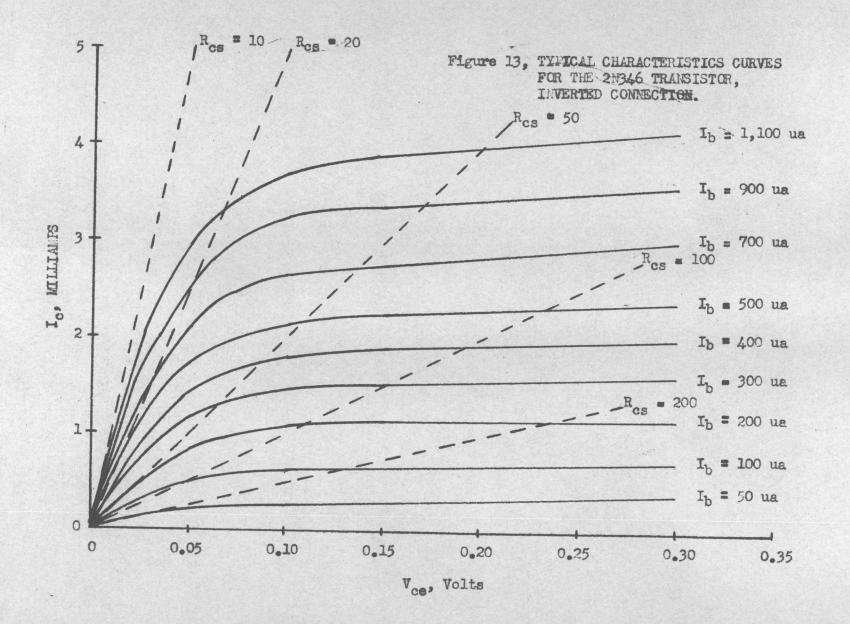

| 13.    | Typical Characteristics Curves for the 2N346 Transistor, Inverted Connection                                           | 49   |

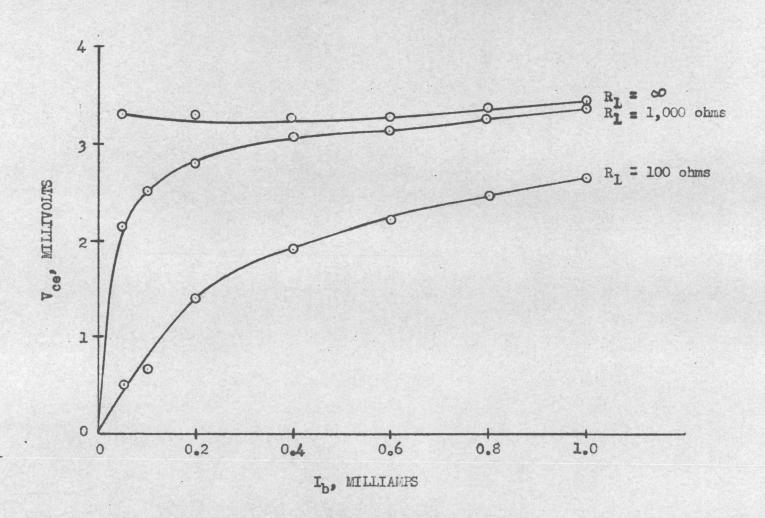

| 14.    | Collector-to-Emitter Saturation Voltages<br>and Base Current for Four Random 2N346<br>Transistors, Inverted Connection | 50   |

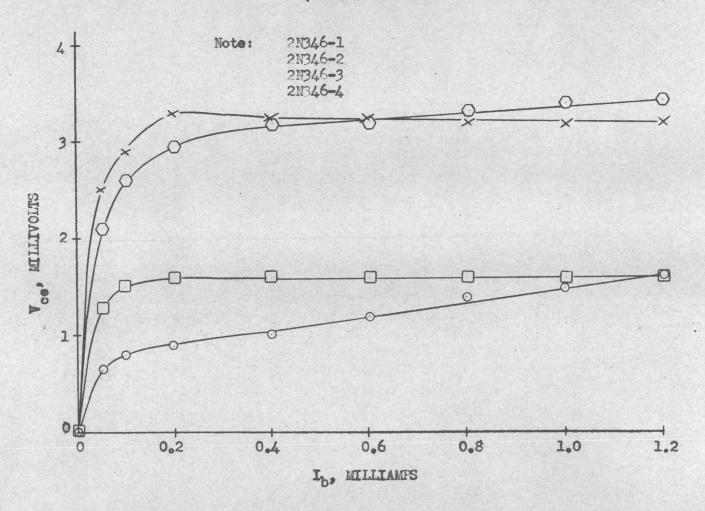

| 15.    | Collector-to-Emitter Saturation Voltage<br>and Base Current for the 2N346 Transistor,                                  | 51   |

| 16.    | Inverted Connection                                                                                                    |      |

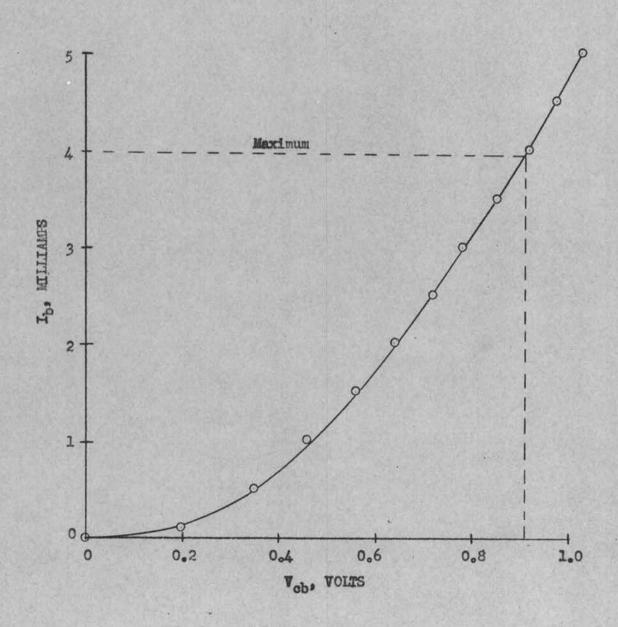

|        | Connection                                                                                                             | 55   |

| 17.    | An Equivalent Demodulator Circuit Diagram.                                                                             | 61   |

| 18.    | Experimental Test Set-up                                                                                               | 66   |

| Figure |                                                                                                       | Page |

|--------|-------------------------------------------------------------------------------------------------------|------|

| 19.    | Output Voltage of the Input Chopper With a Zero Input Signal                                          | 67   |

| 20.    | Output Voltage of the Input Chopper With a -1 Millivolt DC Input Signal                               | 68   |

| 21.    | Output Voltage of the Input Chopper With an AC Input Signal                                           | 69   |

| 22.    | Input and Output Voltage Waveforms of the AC Amplifier With Zero Input Signal                         | 70   |

| 23.    | Input and Output Voltage Waveforms of the AC Amplifier With an Applied Input Signal of -0.8 Millivolt | 71   |

| 24.    | Output Voltage Waveform of the AC Amplifier With an AC External Signal                                | 71   |

| 25.    | Response of the Demodulator Switch to Large Signals                                                   | 72   |

| 26.    | Input and Output Voltage Waveforms of the Demodulator in Response to a DC Input Signal                | 73   |

| 27.    | Input and Output Voltage Waveforms of the Demodulator in Response to an AC Input Signal               | 74   |

| 28.    | Output Voltage Waveform of the Overall DC Amplifier                                                   | 75   |

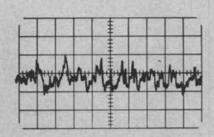

| 29.    | Noise at Output of the Overall DC Amplifier                                                           | 76   |

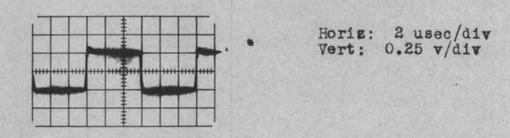

| 30.    | Switching Voltage Waveform                                                                            | 76   |

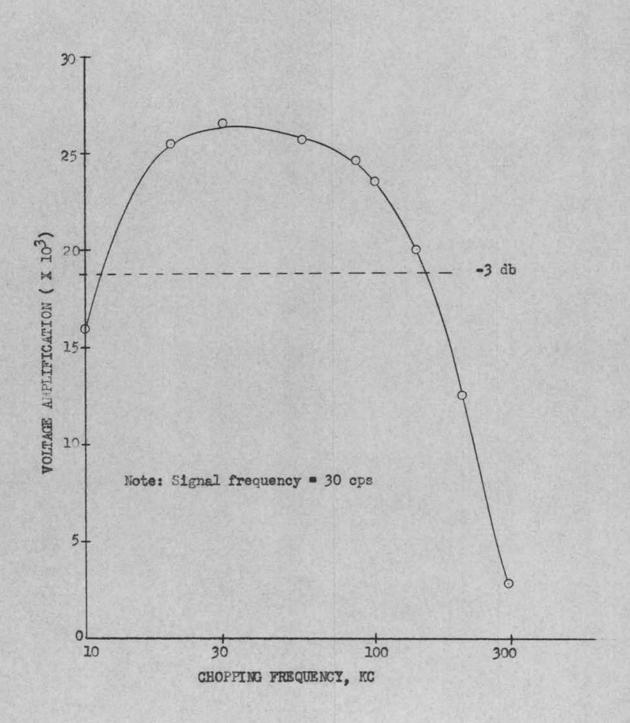

| 31.    | Overall DC Amplification and Chopping Frequency                                                       | 97   |

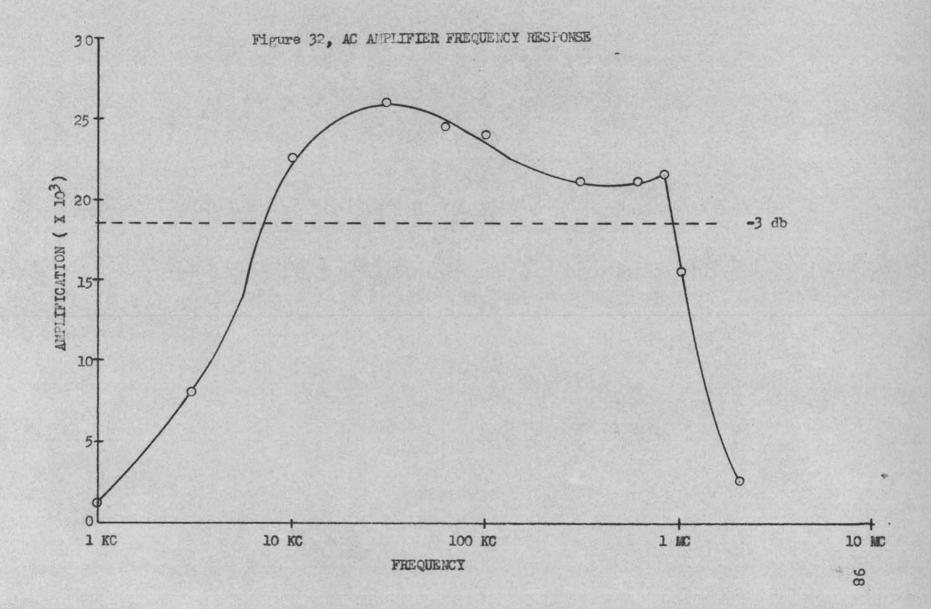

| 32.    | AC Amplifier Frequency Response                                                                       | 98   |

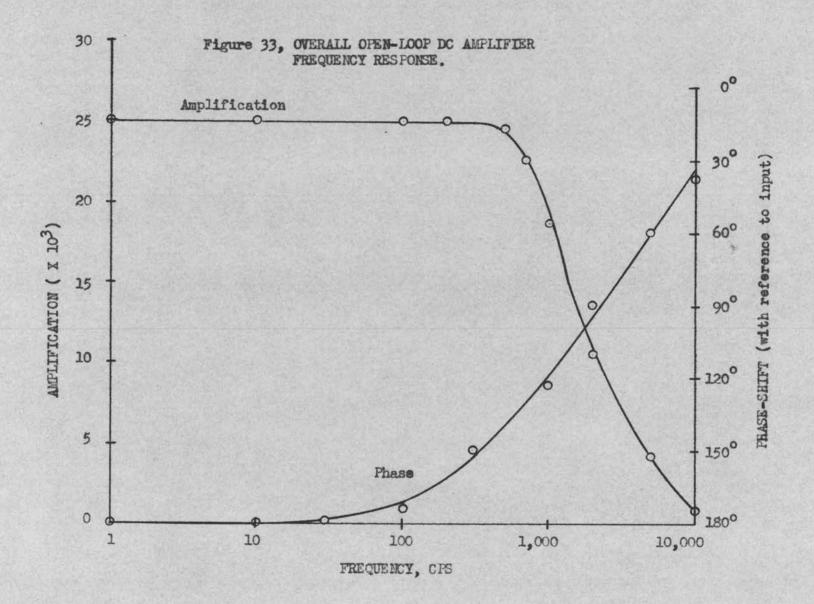

| 33.    | Overall Open-Loop DC Amplifier Frequency Response                                                     | 99   |

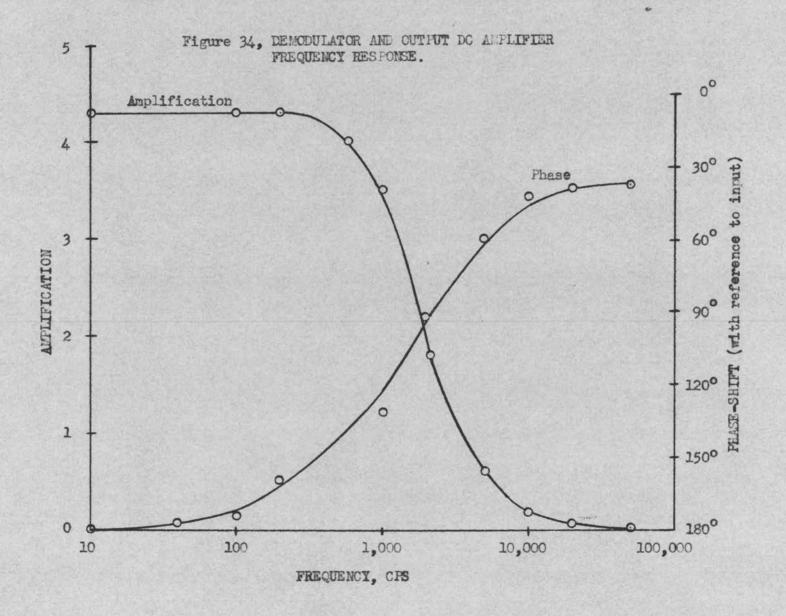

| 34.    | Demodulator and Output DC Amplifier Frequency Response                                                | 100  |

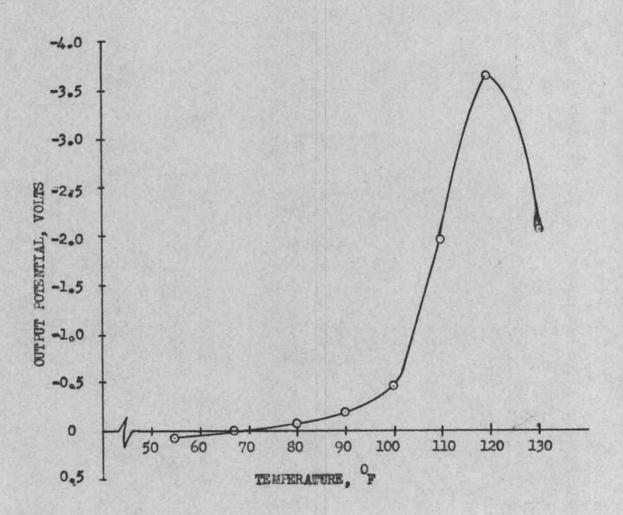

| 35.    | Thermal Drift of Overall Open-Loop DC Amplifier                                                       | 101  |

| Figure | 그리즘 그는 시간 그렇게 보냈다는 사람이 그렇게 되면 했게                                                       | Page |

|--------|----------------------------------------------------------------------------------------|------|

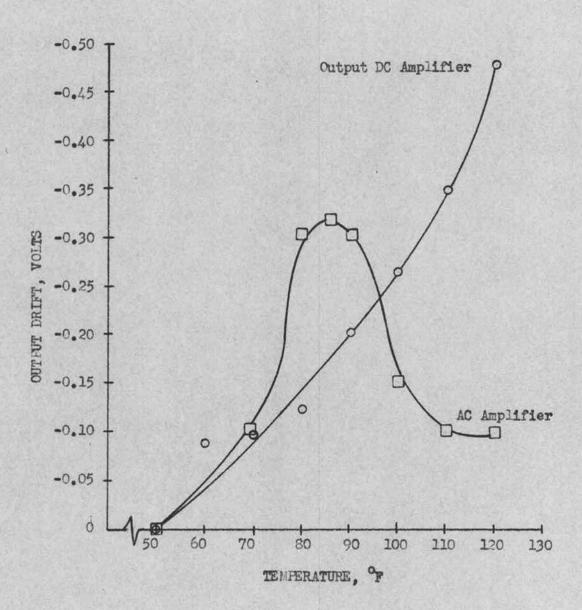

| 36.    | Thermal Drift of AC Amplifier and Output DC Amplifier                                  | 102  |

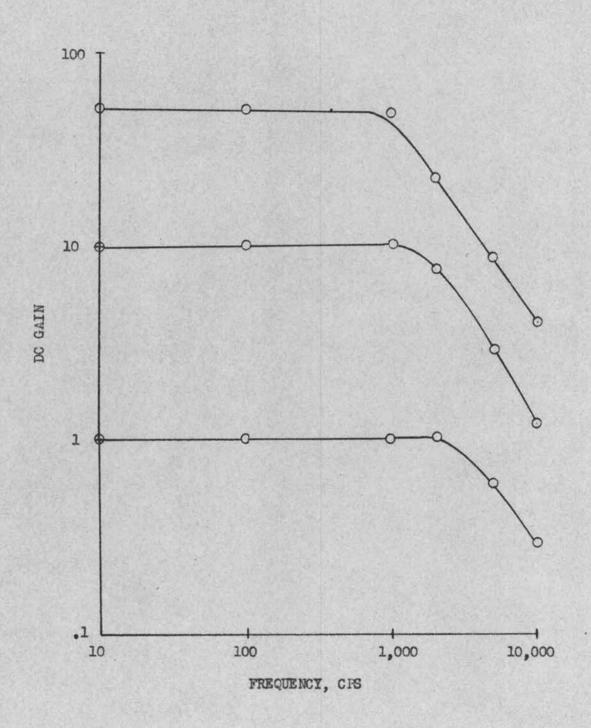

| 37.    | Frequency Responses of Operational Amplifier at Different Values of DC Gain            | 103  |

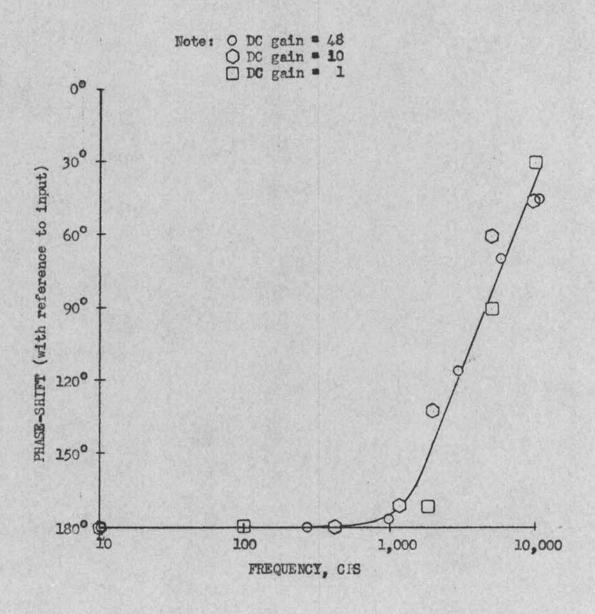

| 38.    | Phase-Shift and Frequency for the Operational Amplifier at Different Values of DC Gain | 104  |

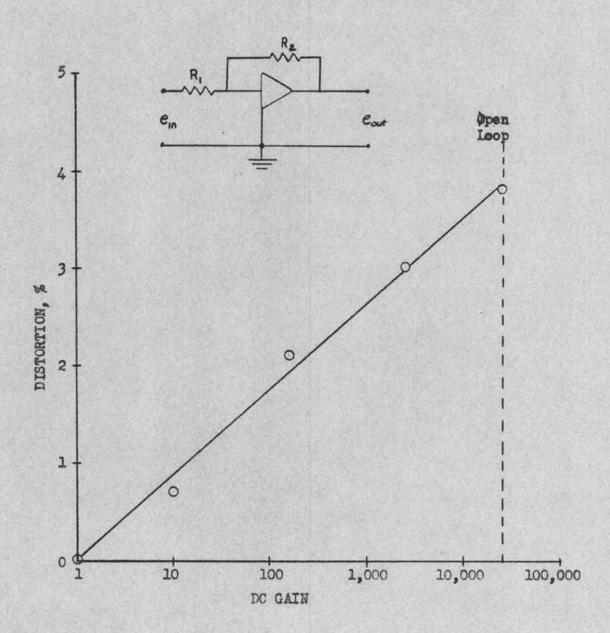

| 39.    | Non-Linear Distortion and DC Gain of the Operational Amplifier                         | 105  |

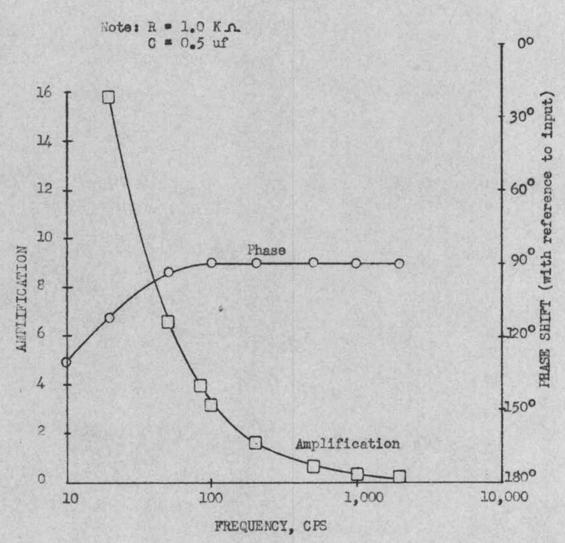

| 40.    | Frequency Response of Operational Ampli-<br>fier Integration Network                   | 106  |

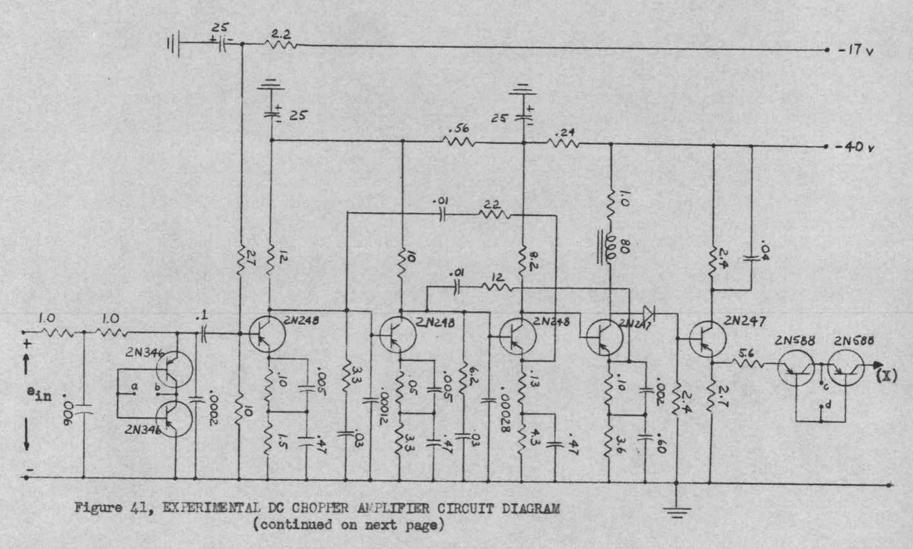

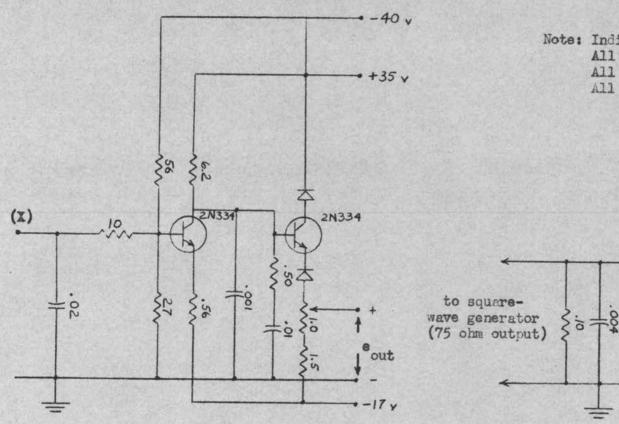

| 41.    | Experimental DC Chopper Amplifier Circuit Diagram                                      | 107  |

| 42.    | Equivalent Circuit of the Non-Ideal DC                                                 | 108  |

| 43.    | A Non-Ideal Operational Amplifier Network                                              | 108  |

| 44.    | Error Limiting Values of Z1 and Z2 for the Non-Ideal Operational Amplifier             | 112  |

| 45.    | A Non-Ideal Operational Amplifier Integrator Network                                   | 113  |

| 46.    | A Non-Ideal Operational Amplifier Differentiator Network                               | 115  |

]

#### ABBREVIATED LIST OF SYMBOLS

- hie Common-emitter input impedance with the output shortcircuited. Also referred to as hile\*

- hre Common-emitter backward voltage transfer ratio with the input open. Also referred to as h12e.

- hfe Common-emitter forward current transfer ratio with the output short-circuited. Also referred to as hale.

- hoe Common-emitter output admittance with the input open. Also referred to as h22e\*

- An Ratio of collector current to emitter current, normal connection.

- (i Ratio of collector current to emitter current, inverted connection (collector and emitter terminals interchanged).

- fx Frequency at which alpha becomes 0.707 of its lowfrequency value, common-base configuration.

- Collector saturation current with the emitter open.

- I Emitter saturation current with the collector open.

- Ie Emitter current.

- Ib Base current.

- Ic Collector current.

- Veb Emitter-to-base voltage.

- Vce Collector-to-emitter voltage.

- Vcb Collector-to-base voltage.

- K Boltzmann's constant, 1.37 X 10 erg/degree.

- T Absolute temperature, OK.

- q Magnitude of charge on an electron, 1.6 X 10-19

- S Algebraically equal to KT/q. or 0.026 volts at 300°K.

- △ Difference operator.

- An amplifier, usually understood to be a dc amplifier unless otherwise indicated.

- Es Signal voltage source.

- u miero,  $10^{-6}$ .

- m milli, 10-3.

- k kilo, 10 3.

#### TRANSISTOR DC AMPLIFIER DESIGN THEORY

#### INTRODUCTION

This paper was prepared to present a practical and realizable solution to the problems of transistor dc amplification. Thus it consists not only of theoretical dc amplifier requirements, problems, and possible solutions for both dc and modulated dc systems, but also the design considerations and experimental results leading to the construction of an acceptable dc amplifier.

Inherent to the subject of general dc amplification is the problem of thermal drift associated with direct-coupled circuitry. In addition, the transistor functions according to well-defined thermal laws thus making temperature considerations even more critical in this application. Offsetting this disadvantage, however, is the tremendous ruggedness, reliability, and low power consumption of the transistor. At the present state of the art, the transistor has been proven to be as reliable as the best vacuum tubes, able to withstand shocks of several thousand g's capable of operating on milliwatts of power at temperatures up to 150°C, and available at about the same cost as a vacuum tube.

From the preceding description it is seen that the transistor is very desirable for many applications. In particular this report emphasizes the application of the dc amplifier to an operational voltage amplifier;

however, most of the information is equally relevant to general dc amplifier applications. Pertinent to all applications are considerations of stability, bandwidth, impedance levels, amplification noise, transistor interchangeability, and cost. These are some of the more general problems treated in this report.

A rather specific analysis is given to the choppertype dc voltage amplifier which was experimentally investigated in detail. This amplifier consisted of a series arrangement of a transistor chopper, ac amplifier, demodulator, and dc amplifier.

#### DERIVATION OF DC AMPLIFIER REQUIREMENTS

Before an intelligent choice of a dc amplification system can be made, the requirements of such a system must be specified. Thus this phase of the report will attempt to develop the theoretical requirements of an operational amplifier\* along with the practical considerations involved in such a project.

### Operational Amplifier Analysis

The operational amplifier is commonly understood to be the basic building block of analog computers. In the intended application to an analog computer, a natural choice exists as to the mode of operation, voltage or current. The network configurations and idealized responses for each mode are indicated below (15, p. 410-13).

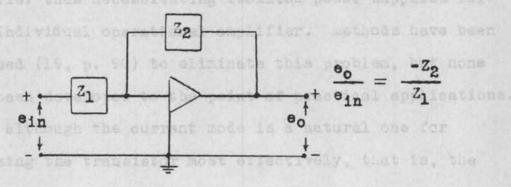

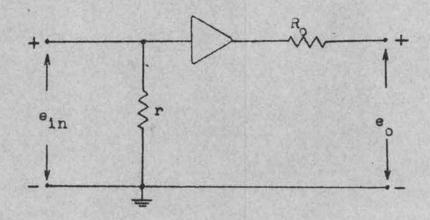

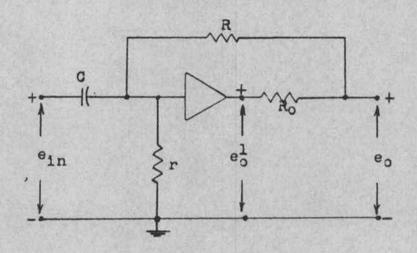

Figure 1. An Operational Voltage Amplifier

<sup>\*</sup> An operational amplifier can be defined as a dc amplifier used with various feedback networks in analog computations.

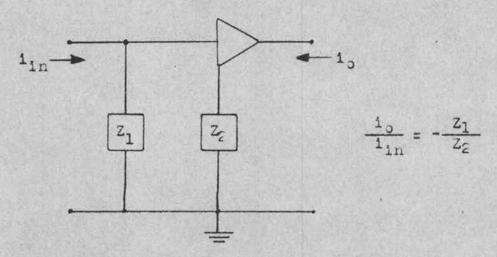

Figure 2. An Operational Current Amplifier

The choice of the operational mode is now seen to be imposed by the proposed application. Since an analog computer requires at least ten operational amplifiers to handle a sufficiently large collection of problems, it is imperative that each amplifier be capable of operating from common power supplies. This condition eliminates the operational current amplifier from further consideration since the feedback impedance, Z2, isolates each amplifier thus necessitating isolated power supplies for each individual operational amplifier. Methods have been proposed (19. p. 90) to eliminate this problem, but none have been developed to the point of practical applications. Thus, although the current mode is a natural one for utilizing the transistor most effectively, that is, the transistor is a current operated device, has low input impedance, and a high output impedance, the prohibitively

large bulk and cost of such an analog computer eliminates this choice.

At this point our problem is now confined to the operational voltage amplifier, figure 1. Since all such amplifiers have a common ground, they may utilize common power supplies and are thus readily adaptable to large analog computer operations.

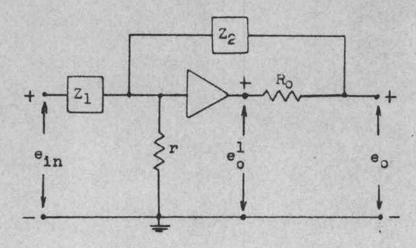

Ideally, a voltage operated device such as an operational amplifier\* has infinite input impedance and zero output impedance. If in addition, the dc amplifier has infinite voltage amplification, an identity is established such that the response of the network shown in figure 1 becomes  $\frac{e_0}{e_{in}} = \frac{-Z_2}{Z_1}$  This equation is the basis for all analog computer operations. Thus the utility of the operational amplifier lies in the accuracy with which this relationship may be obtained and the flexibility of operations which may be performed by choosing different impedances for  $Z_1$  and  $Z_2$ .

Since a transistor dc amplifier will by necessity

have a finite input impedance, finite voltage amplification, and a non-zero output impedance, it is desirable to

know what error is produced by virtue of these non-ideal

conditions. The complete expression for the response of

<sup>\*</sup> Throughout the rest of the report, the term "operational amplifier" will be understood to mean a voltage operated ac amplifier used with various feedback networks in analog computations.

the network shown in figure 1 can be shown (Appendix II) to be:

(1)

$$\frac{e_0}{e_{in}} = -\frac{Z_2}{Z_1} \left[ 1 + \frac{1}{A} \left( 1 + \frac{R_0}{r} + \frac{Z_2}{r} + \frac{R_0}{Z_1} + \frac{Z_2}{Z_1} + \frac{R_0}{Z_2} \right) \right]$$

Where: R<sub>o</sub> = output impedance of dc amplifier

r = input impedance of dc amplifier

A = voltage amplification of dc amplifier

The error term is easily recognized as:

(2) error =

$$6 = \frac{1}{A} \left( 1 + \frac{R_0}{r} + \frac{Z_2}{r} + \frac{R_0}{Z_1} + \frac{Z_3}{Z_1} + \frac{R_0}{Z_2} \right)$$

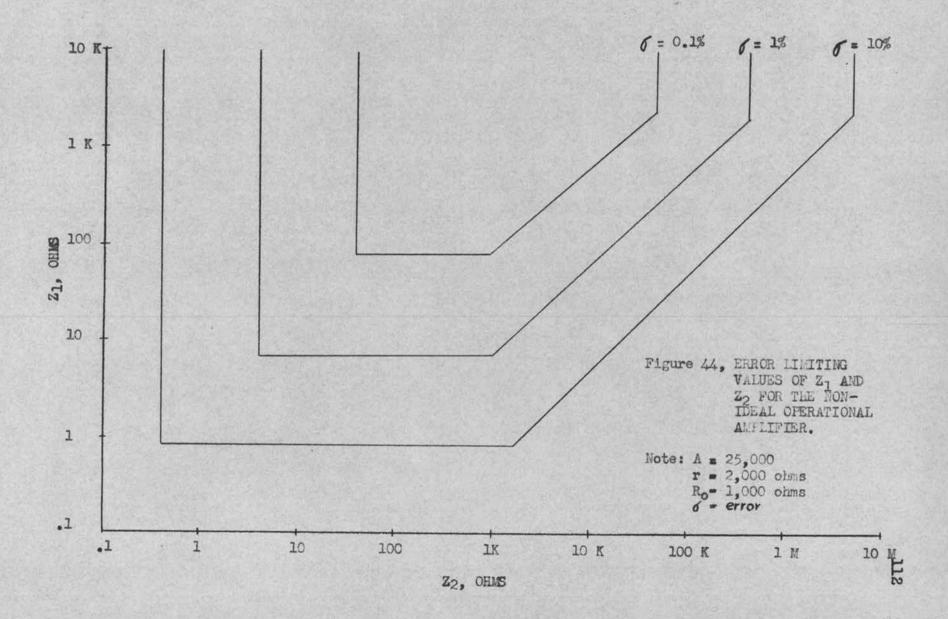

The limiting values of  $Z_1$  and  $Z_2$  for a given magnitude of error are easily found from this expression. For the specific case of A = 25,000,  $R_0$  = 1,000 ohms, and r = 2,000 ohms the limiting values are plotted in figure 44. This figure illustrates the error of the operational amplifier which results from a given choice of  $Z_1$  and  $Z_2$  and an amplifier with the above mentioned specifications.

Certain conclusions are obvious from this analysis. First, it illustrates that an analog computer based on a dc amplifier with A = 25,000,  $R_0$  = 1,000 ohms, and r = 2,000 ohms is not as limited by the choice of  $Z_1$  and  $Z_2$  as is commonly supposed, a maximum dc gain of 200 being possible with an error of only 1%. This indicates

that a transistorized operational amplifier, although restricted, has many applications.

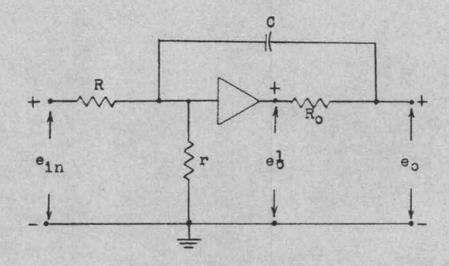

The complete operational amplifier network responses for an integrator and differentiator operation with the non-ideal dc amplifier are developed in Appendix III and IV, respectively.

Equation 1 also implies many more requirements other than amplification,  $\mathbf{Z}_1$ ,  $\mathbf{Z}_2$ , input impedance and output impedance. These are:

- The output drift due to temperature and aging are negligible.

- The amplification A, is large at all frequencies for which the computation accuracy is to be good.

- 3. The amplifier including the feedback loop  $\mathbb{Z}_1$  and  $\mathbb{Z}_2$  is stable.

- 4. The effects of noise and non-linearity are negligible.

These requirements then impose conditions of thermal drift, aging, amplification, bandwidth, stability, phase-shift, noise, and non-linearity upon the operational amplifier.

## Practical Consideration

An inherent implication in any practical project is that it be economically feasible. This provides another requirement which will have to be considered since, practically speaking, it is always desirable to obtain the most acceptable performance for the least cost.

Included indirectly in the cost requirement is the added condition that component tolerance be as large as possible. Thus it is desired to eliminate as many matched or hand-picked components as possible.

Another factor to be considered in a satisfactory de amplifier design is the effects of interchanging transistors. It is desirable to be able to replace transistors of the same type with as little adjustment as possible and still obtain satisfactory results.

A further consideration is the stability of a series of cascaded operational amplifier networks with an overall feedback loop. In this configuration, which is commonly encountered, the phase-shift is additive thus imposing more stringent requirements on the phase-shift per amplifier.

Another requirement is apparent from an investigation of multiple network operations. Namely, that to prevent saturation in succeeding amplifiers each amplifier must be designed so that for the zero input condition, there is also a zero output. This condition is commonly known as an automatic zero-set, AZS arrangement.

## Summary of Compromise Specifications

With all the previously mentioned considerations

in mind, a set of specifications may now be drawn up. It will be noted that the following specifications are quite lenient --the operational amplifier as a whole falling in about the five per-cent error category. Of course, it is desirable to refine the specifications so that the overall error would be less than one per-cent; however, these requirements provide a measure of usefullness as well as a suitable starting point which is practical.

A limitation which has not been mentioned previously is that for the presently available transistors, the maximum output voltage swing is about ± 15 volts. This figure appears below.

From the above conditions the following specifications may be derived for the proposed dc amplifier which is to be used in an operational amplifier network.

- Voltage amplification to be equal to or greater than 20,000.

- Input impedance to be equal to or greater than 2,000 ohms.

- 3. Output impedance to be equal to or less than 1.000 ohms.

- 4. Maximum output voltage swing to be + 15 volts.

- 5. Thermal drift at the output to be equal to or less than 0.25 volt in the temperature range of 70°F ± 15°F.

- 6. Long term output drift to be less than 0.10 volt per hour.

- 7. Bandwidth to be do to 1,000 cps, or greater.

- 8. Phase-shift at output to be less than 100 deviation from the net 1800 phase-shift.

- 9. Noise at output to be less than 0.10 volt peakto-peak.

- 10. Non-linear distortion to be less than 2%.

- Transistors and components to be interchangeable with minimum of custom adjustments or handpicking.

- 12. Cost to be minimum for acceptable performance.

With the desired specifications in mind, the transistor characteristics may now be examined to isolate and analyze the particular aspects which will be important in this application. Consequently, this section of the report is included to provide the background information which is necessary before the significance of particular transistor de amplification systems can be appreciated.

### Physical Characteristics

First to be considered are those characteristics in which the transistor exceeds its vacuum tube counterpart. These qualities are reliability, ruggedness, power dissipation, size, and weight. It is for these reasons that the transistor has been so rapidly developed and applied.

The reliability of transistors is usually considered from the standpoint of short-term and long-term effects. Short-term effects are those contributed by temperature and shock. Electrically the effects of temperature are well known, an increase in the saturation current of reverse-biased junctions being the primary effects of a rise in temperature. Thus it produces no failures in well designed circuits.

As far as mechanical ruggedness is concerned, it has experimentally been found that a shock of 500 g's will

damage less than 1% of the transistors tested. Even at 8,000 g's, a 60% to 75% survival rate was obtained. Vibration and acceleration characteristics are equally impressive, thus making the mechanical ruggedness of the transistor greater than that of many passive circuit elements (20, p. 95-97).

Long term effects generally include the changes produced by continuous operation, namely, aging effects and failure rates. Generally, it has been found that aging produces the same effects as noted from an increase in temperature. These effects are a reduction in the value of current gain and an increase in the collector saturation current, I<sub>co</sub>. Most of the total change occurs in the first few hundred hours; silicon transistors usually showing considerably less change than germanium transistors. These changes are primarily due to changes in the transistor surface conditions (2, p. 376-86).

According to a recent Bell System study, (2, p. 388-91) grown-junction transistors in their P-carrier system exhibited a failure rate of 0.67% per 1,000 hours. In less complex circuitry where transistor requirements were not so stringent, failure rates ranged from 10<sup>-4</sup> % to 0.20% per 1,000 hours. As a basis for comparison, tube failure rates in IBM computer service were found to range from 0.17% to 2.0% per 1,000 hours. In the more

conservatively designed Bell systems the tube failure rate ranges from 0.019% to 0.29% per 1,000 hours. Also it is to be noted that in a submarine cable system, long considered the ultimate in reliability, the required failure rate was just under 0.03% per 1,000 hours. Thus the analysis of transistor failures in field equipment shows failure rates that are comparable with well-designed, conservatively used vacuum tubes. Also, since these results were obtained from transistors of 1956 or earlier vintage, it is probable that presently developed transistors have a higher reliability than these figures indicate.

The other more obvious characteristics which make the transistor a necessity for many applications are its extremely small size, weight and power dissipation.

The above mentioned characteristics are the primary reasons for adapting the transistor to a dc amplifier system.

## Inherent Limitations

Since a transistor exhibits different characteristics in each of its three configurations --common-emitter, common-base, and common-collector, a specific configuration must be specified with any discussion of its particular characteristics. The only configuration which is capable of an iterative voltage gain, however, is the

common-emitter stage (24, p. 73-88); thus this stage is

the only one which deserves much consideration as a voltage

amplifier. The common-base and common-collector stages,

may be very useful as input and output stages where either

a small or large, input or output resistance is desired.

For these reasons the remainder of this discussion will be

primarily directed at the characteristics of the commonemitter configuration.

A fundamental property of any junction transistor is the dependence of the collector saturation current, I<sub>co</sub>, upon the temperature of the device. Since I<sub>co</sub> varies exponentially with temperature, doubling about every 10°C, it is very temperature sensitive and considerable care must be exercised to account for its variation. However, the effects of I<sub>co</sub> are well defined (24, p. 52-54), and consequently there is no mystery involved in designing a suitable temperature stable amplifier. The full significance of this limitation will not be developed until a later section.

Other factors which contribute to the thermal dependence of the transistors are the linear decay of  $V_{be}$  ( $\approx$  2  $\frac{mv}{^{\circ}C}$ ) a slow exponential rise in  $h_{oe}$ , and a small increase in  $h_{fe}$  at lower temperatures and a decrease at the higher temperatures (13, p. 25-30). These changes are, however, of secondary importance and are not usually considered

WAR COURT

directly. In high temperature applications these factors may become appreciable.

Another transistor characteristic which is of paramount importance is the relationship between the magnitude and phase of the common-emitter current amplification, h<sub>fe</sub>, and frequency. A valid expression or experimental result of this relationship is most difficult to obtain since h<sub>fe</sub> is dependent to a great extent on the external circuit and on the extrinsic parameters, besides the intrinsic transistor. For our purposes, however, it is sufficient to note that feedback loops around two common-emitter stages are nearly always stable, while feedback loops around three stages are generally unstable. Also it should be noted that the upper cutoff frequency in the common-emitter configuration is usually slightly less than the quotient of the alpha cutoff frequency in the common-base configuration and the low frequency h<sub>fe</sub>.

Like all other electronic devices the transistor exhibits definite noise properties. Generally the noise encountered in transistors is considered to include three different types; the thermal noise of an ohmic conductor, shot noise, and excess or semiconductor noise. The first two types are white noise while the last type is characterized by a replications it is quite likely that the

semiconductor noise would be most trouble some.

Outside of choosing a low noise-figure transistor to begin with, there are certain general procedures which tend to mimimize the noise tendency. Driving the transistor from a source impedance of about 1,000 ohms seems to reduce the noise (23, p. 14-20) as does reducing the collector-to-emitter voltage and emitter current. Thus the operating point on the critical input stages should be made as low as possible.

Another condition to be considered is the nonlinearity of h<sub>fe</sub>. Generally h<sub>fe</sub>, the small-signal parameter, decreases with increasing collector current. Thus

for large-signal amplification the output will be appreciably distorted. The amount of distortion can be

anticipated from a visual display of the characteristic

curves of the transistor in question. To reduce this nonlinear tendency it is feasible to use as large a load

impedance as possible, and if further improvement is

desired, to apply negative feedback around individual or

multiple stages.

Other important parameters to be considered in a satisfactory design are the maximum collector power dissipation, and the maximum collector-to-emitter voltage.

Needless to say, the ratings of the transistor should never be exceeded. These parameters are usually

determined by the type of transistor and its construction.

ered then some thought must be given to the deviations which are likely to be found in transistors of the same type. Generally the manufacturer will state a maximum, minimum, or average hfe, or a combination of the above. Other parameters are quite likely to vary as much as 100% from average. Thus the design must be able to accomodate very large deviations with a minimum of custom adjustments. Usually one must specify a minimum and maximum hfe to insure that the transistor will be biased in a linear region. The other parameters are generally not so critical.

## Bias Stabilization

The temperature dependence of  $I_{co}$  has been previously mentioned as an inherent limitation of the transistor. In this section we shall discuss the stabilization, with regard to  $I_{co}$ , of the single-stage common-emitter biasing network and its effect on the dc voltage amplification of the stage.

It is easily found that besides providing a suitable biasing arrangement for the transistor, the biasing network determines the sensitivity of the external circuit to temperature. Thus a well-designed biasing network is mandatory. Several suitable biasing schemes exist (24 p. 68-71), however, we shall examine just one of them

which is very general and useful. Other biasing schemes would yield the same general conclusions.

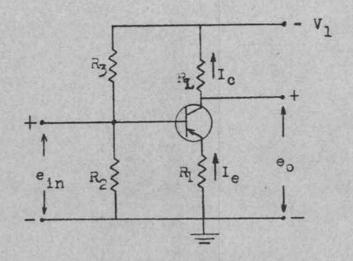

Figure 3. A dommon-Emitter Single Battery Biasing Circuit

Certain stability factors may be derived for this circuit on the basis of the variation of  $I_{\rm CO}$  and its effect on the external circuit. According to Shea's analysis (24, p. 54-71), the current stability factor is defined as the quotient of the change in emitter current and the change in  $I_{\rm CO}$ , or algebraically:

(3)

$$s_{\rm I} = \frac{\Delta I_{\rm e}}{\Delta I_{\rm co}} = \frac{G_{\rm l}}{G_{\rm 2} + G_{\rm 3}}$$

, for average conditions,  $(G_{\rm n} = \frac{1}{R_{\rm n}})$

Likewise, the voltage stability factor is defined as the quotient of the change in collector-to-base voltage and the change in  $I_{co}$ .

(4)

$$S_v = \frac{\Delta V_{cb}}{\Delta I_{co}} = S_I R_1 + (1 + S_I) R_L$$

, for average conditions.

To meet the small thermal drift requirements, therefore, ideally  $S_V$  and  $S_I$  should equal zero. To approach this result, equation 3 states that  $R_l$  should be large and  $R_2$  and  $R_3$  should be small. The voltage stability equation states that the above mentioned conditions should be met plus the condition that  $R_I$  should be small.

One other result is needed to fully appreciate the significance of the above statements. This result is the expression for the input impedance of the transistor.

# (5) Rin = hie + hie Rl. for average conditions.

From these equations the full significance of the gain versus bias stability conflict may be understood. By increasing R<sub>1</sub> and decreasing R<sub>2</sub> and R<sub>3</sub>, thereby increasing the thermal stability, the input impedance of the transistor is raised geometrically while the input impedance of the complete stage is decreased. Thus if this stage is driven by a current source, most of the signal current will be lost through R<sub>2</sub> and R<sub>3</sub> and very little current will enter the transistor. If the stage is driven by a voltage source, the shunting effect of R<sub>2</sub> and R<sub>3</sub> will not be so noticeable; however, the high input impedance of the transistor will definitely limit the current which can enter the transistor. In either case,

the signal current which can enter the transistor is comparitively small. It naturally follows then that the voltage amplification of the stage will be very small since the transistor is a current operated device. Furthermore, the condition that R<sub>L</sub> shall be small for good thermal stability limits the possible voltage amplification even more. For these reasons it is very difficult to achieve appreciable dc voltage amplification per stage with suitable temperature stability.

From the definitions of the voltage and current stability factors, it is apparent that the stability is directly dependent upon  $\Delta I_{\rm co}$ . Thus if  $\Delta I_{\rm co}$  could be decreased for the same change in temperature, the gain versus stability conflict would be alleviated somewhat. This is the reason for the introduction of the silicon transistor. The  $I_{\rm co}$  for both germanium and silicon increase at about the same rate with temperature, however, at room temperature an average silicon transistor has an  $I_{\rm co}$  of the order of  $10^{-8}$  amps while an average germanium transistor has an  $I_{\rm co}$  of the order of  $10^{-6}$  amps. Thus silicon transistors are much better suited to high temperatures applications and dc amplification. It seems that nature always works against the engineer, for accompanying the beneficial temperature characteristics of

silicon is a cost of about ten times that of germanium.

So, a conflict still exists.

#### ANALYSIS OF DC AMPLIFIER SYSTEMS

To obtain the optimum system for a given application, all applicable systems must be evaluated. It is for this reason that a brief analysis must be given to all the systems which could possibly satisfy the previously set forth requirements. From this analysis, then, a system can be chosen which will best satisfy the requirements for the application.

Generally a dc amplifier system will be either a direct-coupled configuration or a modulated dc system.

These are the classifications which will be discussed in this section.

## Direct Coupled Configuration

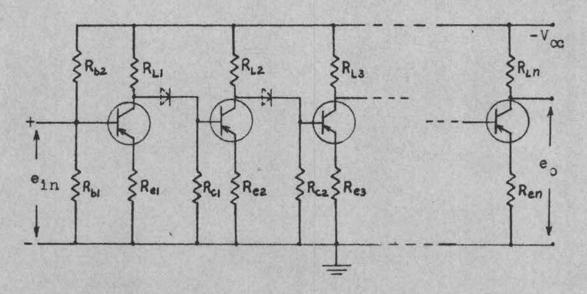

The characteristics of the individual transistor common-emitter stage have already been examined in the previous section. From this discussion a rather obvious possibility is apparent, that of a cascade of several common-emitter stages. A conventional arrangement of such a circuit is illustrated below.

Figure 4. A Direct-Coupled Single-Sided DC Amplifier

Since this type of circuit is merely a series of commonemitter stages, all the limitations of the single stage still apply individually. However, it should be noted that if all stages are identical, each iterative stage has perfect I<sub>CO</sub> stability, and the temperature characteristics of the complete circuit become approximately those of only the first stages. Even with considerable difference between stages, as long as the transistors are all of the same polarity --either PNP or NPN, some cancellation of temperature characteristics from stage to stage will be effected. On the other hand, if the transistors alternate polarity; that is, PNP-NPN-PNP --etc., the temperature characteristics from stage to stage combine additively so that the complete circuit would have very poor thermal stability characteristics. Thus in a real application where it is certainly not desirable to have all stages identical from the standpoint of their quiescent operating points, a certain amount of cancellation of temperature characteristics may be effected from stage to stage by using similar polarity transistors. However, a compromise is still in order between the voltage amplification per stage and thermal stability considerations. This compromise means accepting a low amplification per stage, which indicates a large number of stages, in an attempt to preserve some thermal stability.

This compromise, however, with its large number of stages introduces other problems, namely the voltage accumulation from stage to stage. If a large collector supply voltage is used it further aggravates the gain versus bias stability conflict because of the necessity for larger resistors in the front stages of the circuit. A smaller collector voltage supply may be used if breakdown diodes are used between stages to compensate for the voltage accumulation. If the diodes are used, as indicated in figure 4, the resistors R<sub>cl</sub>, R<sub>c2</sub>, ""R<sub>cn</sub>, are usually necessary to provide sufficient current to fully saturate or break down the diode. Otherwise these resistors may not be necessary. Their insertion provides an additional shunt path thus lowering the amplification.

The breakdown diode in saturation exhibits an

intrinsic incremental resistance of:

(6)

$$R_{lnc} = \frac{\delta}{I}$$

where  $\delta = \frac{KT}{q}$   $\delta = 0.026$  volts at  $300^{\circ}$ K

I = Current through the diode

Additionally, the breakdown diode has a positive temperature coefficient of from 0.001 to 8.0% which must be considered.

The voltage accumulation presents an additional problem in that an output device must be constructed to satisfy the automatic-zero-set requirement.

It is easily recognized that the voltage accumulation problem is eliminated if the transistors are of alternate polarity; however, as previously indicated this combination would exhibit very poor thermal characteristics.

Several non-linear compensating techniques have been developed so that an amplifier may exhibit appreciable gain per stage and yet have satisfactory thermal stability. Among these techniques are the utilization of the positive voltage temperature coefficient of reverse biased diodes, the negative voltage temperature coefficient of forward biased diodes, the negative resistance coefficient of both forward and reverse biased diodes, other temperature sensitive resistors, and extra transistors of the same type

used as compensating current generators (24, p. 20-23).

All these techniques, however, are dependent upon the matching of the temperature characteristics of the compensated and compensating devices. This requires special hand-picked and matched components which are hard to obtain, costly, and definitely undesirable from the stand-point of interchangeability.

From this brief analysis, the single-sided cascaded do amplifier is seen to have definite shortcomings. To achieve appreciable amplification per stage either the temperature stability must be sacrificed, the increased cost of silicon transistors must be absorbed, or the increased cost and complexity of matched compensating devices must be tolerated. Additionally, the voltage accumulation necessitates an output device to provide an AZS arrangement.

A typical figure for the drift of such a dc amplifier is 100 millivolts referred to the input (8, p. 249) for a temperature change of 20°C to 50°C.

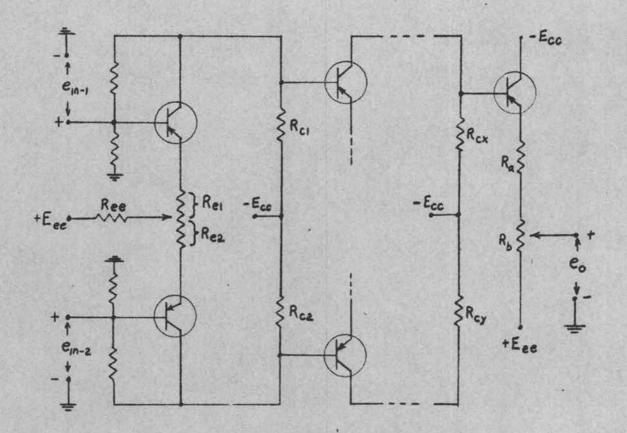

Another direct coupled configuration which has considerable merit as a dc amplifier is the differential amplifier (12, p. 157-60). The differential amplifier is a form of double-sided or double-ended circuit which amplifies the difference between its inputs. A conventional arrangement is shown below:

Figure 5. A Differential DC Amplifier

The principle advantages attributed to this type of circuit (18, p. 194-98) over the single-sided circuit are that the temperature induced variations tend to oppose each other, and that the emitter resistor Ree can be made as large as necessary, thus making the sum of emitter currents as stable as desired, without adversely affecting the gain per stage. Other desirable characteristics are that the gain and input impedance are twice that of its single-sided counterpart. The differential amplifier also has a voltage accumulation from stage to stage which

requires the same consideration as discussed for the singlesided amplifier. An AZS arrangement is also shown in the figure.

The primary problem with this circuit is matching each pair of transistors with respect to temperature induced I<sub>co</sub> variations, emitter current, h<sub>fe</sub>, and base-to-emitter voltage variations with temperature. The degree of matching naturally determines the extent of idealization which may be expected from the amplifier.

A typical figure for the thermal drift of such a dc amplifier in the temperature range of 20°C to 50°C is about 2 millivolts referred to the input (8, p. 249).

Another matter of some practical concern in applying this circuit to an operational amplifier is that a device must be provided to eliminate the dc bias at the input.

From this brief discussion, it is seen that the differential amplifier is much to be preferred over the single-sided amplifier; however, it is still not very desirable for this application because of its necessity for matched transistors.

At this point it is generally concluded that the application of direct-coupled dc amplifier configurations is definitely limited, primarily because of the gain versus bias stability conflict. At best the situation is alleviated somewhat by matched transistors and components,

complex circuitry, and custom adjustments; all being prohibitive from the standpoint of cost, time and interchangeability. The next section deals with a method which practically eliminates the previously noted conflict.

## Modulated DC Systems

According to IRE standards, modulate means to vary some characteristic of one wave in accordance with another wave. In this discussion a modulated dc system refers to a system which utilizes the advantages gained by changing the dc signal to an ac signal in some aspect of its operation, the advantage being that it is much easier to amplify ac signals with acceptable thermal stability than dc signals. This advantage is attributable to the use of reactive bypass and coupling components.

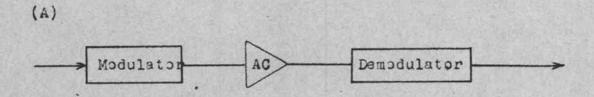

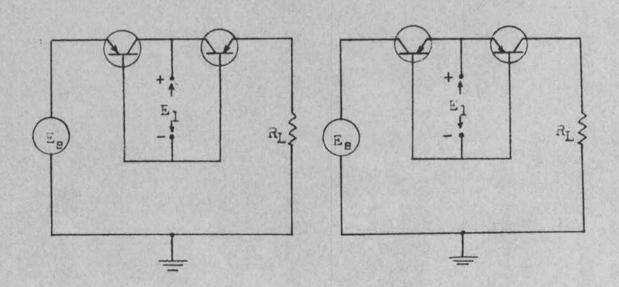

An illustration of possible systems configurations is shown on the following pages. It will be noted that a discrimination is made between dc chopper amplifiers and dc chopper stabilized amplifiers. A chopper amplifier is one in which the chopper and its associated circuitry are the sole mode of amplification; whereas a chopper stabilized amplifier is one in which the chopper amplifier is used in conjunction with another mode of amplification.

Figure 6-A illustrates a rather novel, although conventional, approach to eliminating thermal drift. In this system the output of the conventional dc amplifier is divided by its amplification factor and compared to the input. The

Figure 7, DC Chopper Amplifier Configurations

difference then activates the chopper-amplifier which produces an input to counteract this difference. Thus the drift of the main do amplifier is reduced by the amplification of the chopper amplifier. The basic disadvantage of this system is that it appears to be too complex and refined for this application. Undoubtedly, it could meet the desired requirements. However, a simpler technique is more desirable.

The system shown in figure 6-B provides a different amplifier for the ac and de signal components. Although

this system could provide high gain with a minimum of drift and an extremely large bandwidth, it again suffers because of its complexity.

The system of figure 6-C is merely a simplification of figure 6-B. Instead of providing a separate ac amplifier the high frequency signals are fed directly into the high-level output dc amplifier. Because of this simplification the bandwidth is considerably reduced over that of figure 6-B. The stabilization of this system could logically provide a practical problem, and the system again appears to be too complex for this application.

of all the modulated dc systems, the chopper amplifier shown in figure 7-A is seen to be the ultimate in simplicity. However, since the demodulator is usually simply a low-pass RC filter, the system could be unstable with certain types of feedback encountered in operational amplifier operations (5, p. 10). The system of figure 7-B remedies this situation by isolating the demodulator from the output by a high-level dc amplifier. Thus if the modulating techniques will allow a sufficient bandwidth and the ac and dc amplifiers provide a sufficient voltage amplification, this system appears to be the most desirable.

From this analysis the system shown in figure 7-B was chosen as the one to be experimentally evaluated.

Consequently, most of the rest of this report is an investigation of this system.

## Optimum System Analysis (Figure 7-B)

Theoretically the modulation technique could utilize the phase, frequency, or amplitude of the carrier signal. However, the simplest technique is merely that of chopping the input signal. The chopped signal is then amplified in the ac emplifier, the amplified dc input level is recovered in the demodulator, and the output high-level dc amplifier further amplifies the signal and isolates the output from the demodulator.

By virtue of its simplicity the chopper is a natural choice of the modulation technique. However, here a choice exists as to full-wave or half-wave chopping.

With full-wave chopping there is no inherent phase-shift; however, it requires a double-sided chopper, ac amplifier, and demodulator. This indicates twice as many components as those required for a half-wave chopping system. The half-wave chopping system, though, introduces an effective time lag, or phase shift, when the chopped signal is demodulated, equal to half the period between samples.

Algebraically: (7)  $\phi = \frac{f_s}{f_c}$  180°, where  $f_s = \text{signal frequency}$   $f_c = \text{chopping frequency}$  $\phi = \text{phase-shift}$  Thus to restrict the phase-shift to 100 or less with a maximum frequency of 1,000 cps, the chopping frequency must be at least 18,000 cps. This is perfectly feasible with a transistor chopper.

Additionally, since the chopping technique is merely a form of sampling, the sampling theorems and principles (3, p. 37-41) do apply. The basic information which is to be obtained from this analysis, however, is that the sampled wave must be sampled at a rate at least twice that of the highest significant signal frequency to obtain all of the original information which is contained in the sampled wave. Practically, the sampling rate must be considerably famter than that predicted theoretically. Also, the theoretical considerations show that the demodulator should consist of a low pass filter with a cutoff frequency of one-half the chopping frequency. Under these idealized conditions no information in the sampled wave will be lost.

A practical analysis indicates that other frequency sensitive networks, usually low-pass RC filters, must be used to preserve stability. By necessity these shaping networks must be placed in the dc sections of the amplifier; that is, at the input, after the demodulator, and after or within the dc amplifier (7, p. 10-13).

To minimize the thermal drift it is also seen that the dc amplifier gain should be as low as possible. This necessitates a high gain ac amplifier.

With the desired system and specifications now in mind, the individual components may be developed. An attempt is made to make each component a complete discussion within itself. This development will follow the natural sequential order; that is, chopper, ac amplifier, demodulator, and dc amplifier.

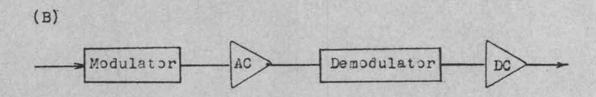

#### Preliminary Design Layout

Before entering into the development of each component, it is advantageous to have a more specific idea of the overall system which is being designed. Consequently, the system block diagram is shown below in order that one may better understand the development to follow. This block or flow diagram is derived in part from the previous discussion and the remainder from the development which follows:

Figure 8. A Specific Chopper-Amplifier Block Diagram

At this point certain conclusions can be drawn from the preliminary layout (17, p. 34-39). First, it is noted that the input filter must have an input resistance of 2,000 ohms to meet the previously set forth requirements. Next, it is apparent that the input chopper must have a very small bias error, or in other words, for a zero input signal it must have a very near zero output since the rest of the circuit dannot tell the difference between a bias error produced by the chopper or an external signal. Thus the chopper must be a very high quality chopper and capable of switching very rapidly. It is obvious that the sensitivity of the chopper determines the sensitivity of the system. Consequently, the success of the system, to a large extent, is determined by the performance of the chopper.

To be discussed in more detail later in the report, are the common-collector output stages on the end of the ac amplifier and dc amplifier. These stages, it will be noted, produce no phase-shift and a low output resistance.

Overall there is seen to be a 180° phase-shift which is necessary in order that the feedback loop and amplifier be stable. Also, the low-pass filters help maintain stability since they are inserted to attenuate the higher frequencies where the total phase-shift may approach 0° and oscillations would otherwise occur.

The single-stage dc amplifier must obviously be quite stable with temperature if the system is to be stable with temperature variations. However, if most of the amplification can be obtained in the ac amplifier, the dc amplifier need not produce very much gain.

At this point it should also be mentioned that a good choice of power supply voltages is best made is one starts at the output which must be at 0 dc level and work back toward the front. Naturally, the transistors and other circuitry must be well in mind before this choice is made.

## Chopper Design Consideration

A search for a suitable chopper or switch to convert do to ac will yield many different methods. Among these are the mechanical chopper, vacuum and gas tube switching circuits, diode switching circuits, cryatron, transistor switches utilizing the Hall effect, and the conventional transistor switching circuits. At this point we shall confine our attention to the latter method --conventional transistor switching circuits. This choice is dictated by the requirements of availability, simplicity, high quality, and high switching frequency.

The basic principle of conventional transistor

switching circuits is suggested by the well-defined dependence of the emitter current, and hence the collector

current, upon the emitter-to-base voltage. Algebraically, the relationship can be shown (18, p. 344) to be:

(8)

$$I_e = I_{eo} \left( \frac{V_{eb}}{S} - 1 \right) - \alpha_i I_c$$

$$\int = \frac{KT}{q}$$

(9)  $I_c = I_{co} \left( \frac{V_{eb}}{S} - 1 \right) - \alpha_n I_e$ , where:  $\alpha_i = I_{nverted}$  alpha  $\alpha_i = N_{ormal}$  alpha

It will be noted that these equations as well as the following discussion apply to polarities associated with a PNP transistor. The same information applies to NPN transistors with polarities reversed.

These equations show that if the emitter junction is made positive with respect to the base, a large emitter current of exponential order will flow. (Since I is normally negative, the two components of I combine additively.) On the other hand, if the emitter is made negative with respect to the base, a very small emitter current will flow. Thus the state of the switch is determined by the polarity of the emitter-to-base voltage.

Extremely different switching characteristics are obtained in each of the different switching configurations. Thus an analysis of each configuration is in order. These configurations are illustrated on the following page.

Figure 9. The Basic Switch Configurations

In the preceding figures it is understood that E<sub>1</sub> is the voltage which determines the state of the switch, and that E<sub>3</sub> is the voltage which is being switched into the load resistance, R<sub>L</sub>. E<sub>2</sub> and I<sub>2</sub> are the quantities which are dependent upon the transistor and determine the quality of the switch.

Under the assumption that these switches are switched

characteristics of each configuration may be obtained (18, p. 339-352). Basically, the common base configuration is undesirable because the saturation voltage, E2, is negative and by no means negligible, being in the order of a tenth of a volt. The common collector switch exhibits a small saturation voltage, but the cut-off current, I2, is negative, which is also undesirable. The common-emitter switch is the best behaved configuration as both the cut-off current, I2, and saturation voltage, E2, are very small and always positive. Thus the common-emitter configuration offers the most ideal characteristics.

Now that the basic configuration has been determined, a more detailed analysis of its operating characteristics should be made in order to find the causes, effects, and solutions of the non-ideal characteristics.

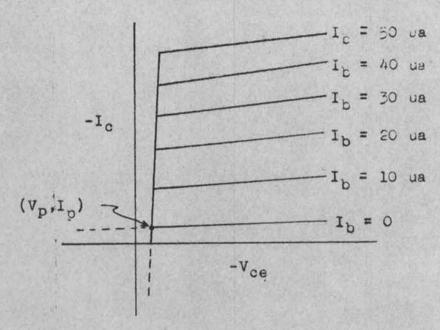

Of primary importance is the magnitude of the saturation voltage and cut-off current. These parameters can easily be recognized from the common-emitter characteristic curves. An idealized and exaggerated set of these curves is illustrated on the following page to emphasize the point.

Figure 10. Idealized PNP Common-Emitter Characteristic Curves

During the saturation the voltage  $V_p$  exists between the collector and emitter thus yielding the saturation voltage, and during cutoff, a cutoff current  $I_p$  flows through the collector leg thus yielding the cutoff current. The above discussion then suggests that the transistor switch can be thought of as an ideal switch shunted by a current source with finite impedance during cutoff, or in series with a voltage source with internal resistance during saturation.

In terms of the transistor parameters, the non-ideal saturation voltage and cutoff current can be expressed as (16, p. 16-21):

(10)

$$I_{p}^{n} = \frac{(1 - \mathcal{A}_{1})}{(1 - \mathcal{A}_{n} \mathcal{A}_{1})} I_{co}$$

$$v_p^n = \frac{KT}{q^0} \ln \frac{1}{q'_1}$$

For ordinary germanium transistors, these parameters usually are in the order of several microamps and several millivolts.

Now if the transistor is inverted; viz, the collector and emitter terminals interchanged, the above parameters are reduced by approximately one order of magnitude (16, p. 16-21).

(12)

$$I_p^i = \frac{(1 - \alpha_n) I_{eo}}{1 - \alpha_n A_i}$$

(13)

$$V_p^i = \frac{KT}{q} l_n \frac{1}{\zeta_n}$$

Where  $l_{eo} \leq n l_{eo} \leq i$

This inversion is possible since both the collector and emitter terminals are of the same polarity, N-type or P-type. Thus either one may act as the emitter or collector. However, in the normal configuration the collector is made larger than the emitter so as to have a high collector efficiency. Thus when these functions are reversed the collector efficiency is considerably reduced. For this reason, generally the  $\swarrow_1$  ranges from 0.3 to 0.9 and  $\swarrow_n$  ranges from 0.9 to 1.0. Accompanying the reduced collector efficiency is also a decrease

in the maximum allowable power dissipation.

A closer examination of the single stage commonemitter switch will also show that it is incapable of turning off appreciable negative signals.

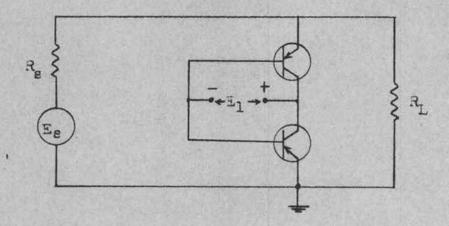

After understanding the characteristics of the singlestage common-emitter switch, we are now ready to procede with the next logical step in a refinement of the transistor switch, namely, the differential type, or seriespair switch.

Figure 11. The Series-Pair Switch

(a) Inverted Connection (b) Normal Connection

A rather obvious advantage of this switch is that at every interval of time, the saturation voltage or cutoff current, depending upon the state of the switch, of the two transistors combine differentially. This greatly improves the quality of the switching characteristics.

In analyzing this and other more complex transistor switches a useful rule to keep in mind is as follows:

The transistor may conduct in either direction if either junction is forward biased, and the transistor will be cutoff only if both junctions are reverse biased. From this information it is seen that with E<sub>1</sub> positive as indicated, both transistors are turned on; and with E<sub>1</sub> negative, one transistor always is turned off regardless of the signal polarity, E<sub>8</sub>. Thus this switch may be used to switch signals of either polarity up to the breakdown voltage of the transistors.

As far as current limitations are concerned, it is advisable to restrict the current through the switch in the inverted connection to about 2/3 of the maximum rated current. This restriction is primarily due to the smaller inverted alpha. In the normal connection, the full rated I<sub>c</sub> may be recognized.

Generally speaking, the normal configuration is preferable in high level applications, while the inverted configuration provides better low level performance. Also, the series switch, meaning that the switch is a series with the load, is usually preferable in low impedance (less than a thousand ohms) circuits; while the shunt switch, meaning that the switch is in parallel with the load, is used more advantageously in the high impedance circuit (11, p. 28-35).

At this point then, we are ready to choose a configuration to be used as the input chopper in the proposed dc chopper amplifier. Since this application requires a high quality low-level switch to be used in a fairly high impedance circuit, the natural choice is the shunt, inverted connection, series-pair configuration.

Figure 12. The Shunt Series-Pair Switch, Inverted Connection

With this configuration in mind, we are now in a position to study the more specific characteristics of the switch in actual operation.

As to the choice of transistors, theoretical considerations indicate that a high  $\alpha_n$ , low  $\alpha_i$ , and low  $\alpha_i$  are desirable. Also to be considered are the

collector saturation resistance, Rcs, and transient switching characteristics.

of the available transistors, the Philco 2N346 surface barrier transistor seemed to be best suited to this application. Only germanium transistors were considered, although silicon transistors are more desirable from the standpoint of their lower I<sub>co</sub>. Also it was found that grown junction transistors are definitely unsuitable for low-level applications because of their large ohmic resistance which makes the collector saturation resistance very large, several hundred ohms.

The 2N346 was found to have an  $\mathcal{L}_n$  of about 0.975,  $\mathcal{L}_1$  of about 0.8 and, an  $I_{co}$  of about 1 to 2 us. Also, its alpha cutoff frequency of 75 Mc was found to be indicative of excellent high speed switching characteristics.

of basic importance in the "on" or conducting state are the collector saturation resistance and collector saturation voltage. The emitter-to-collector saturation resistance, R<sub>cs</sub>, for a transistor in the inverted connection has been shown (5, p. 5) to be:

(14)  $R_{cs} = \frac{kT}{q} \frac{1}{I_b} (1 - \alpha_n \alpha_i) \alpha_i + R_x$  where:  $I_b = Base$  current  $R_x = Ohmic$  resistance

For the specific case of the 2N346, this equation becomes:

(15)

$$R_{cs} = 7.15 \text{ X} \frac{10^{-3}}{I_b} + 10$$

, ohms

(The ohmic resistance of 10 ohms is estimated)

And at Ib = 400 ua, Rcs = 28 ohms\*.

As a verification of this theoretical result, the experimental values of R<sub>cs</sub> were obtained. The experimental value is easily obtained from a visual display of the characteristic curves. A typical set of common-emitter, inverted connection, characteristic curves with saturated resistances indicated are shown on the following page.

It is easily proven that the experimental and theoretical values compare favorably indicating the validity

of the equation. The experimental results also show that

fairly small saturation resistances can be obtained by

driving the transistor with sufficient base current.

The collector saturation voltage is a slightly more complex function since it depends on both the effective load resistance and base current. This relationship is illustrated in figure 14. From this set of curves it is seen that if the effective load resistance as seen by

<sup>\*</sup> Power transistors have much lower Rcs values but are not suited for low-level or high-frequency switching.

Figure 14, COLLECTOR-TO-EMITTER SATURATION VOLTAGE AND BASE CURRENT FOR THE 2N346 TRANSISTOR, INVERTED CONNECTION.

Figure 15, COLLECTOR-TO-EMITTER SATURATION VOLTAGE AND BASE CURRENT FOR THE 2N346 TRANSISTOR, INVERTED CONNECTION. (Characteristics of four random transistors)

the switch is in the vicinity of 1,000 ohms or greater, the saturation voltage is fairly constant. This is indicative of the source resistance, R<sub>cs</sub>, which already has been discussed.

The dependence of the collector saturation voltage upon base current is not very well defined as shown in figure 15. Common to all of these curves, however, is a knee in the vicinity where the acting emitter-base junction becomes saturated. It should also be noted that at zero base-current the collector-to-emitter voltage is not actually zero as indicated by the test instruments. Instead it has a magnitude determined by the relative doping of the P and N regions. This potential, however, cannot be read by a current-drawing device.

The real importance of figure 15, however, lies in the illustration of the difference in the direction of change and rate of change of the saturation voltage with base current. Because none of the transistors tested showed the same rate of change of V<sub>ce</sub> with I<sub>b</sub>, it is relatively easy to get an exact match at some particular value of base current, although not at all values. Thus at some specific value of base current two transistors are easily picked which have the same collector saturation voltage. Consequently, when these transistors are inserted in the circuit of figure 12, and driven with the specified amount

of base current, the overall bias error during saturation is zero. This is a very significant result as will be later seen.

The cutoff characteristics of the 2N346 in this low-level application were found to be very good. Despite a predicted value of the cutoff current source, equation 12, of 0.14 ua, the actual magnitude was so small it was difficult to measure --being in the order of a few hundredths of a microamp. Also it was noted that the transistors were quite uniform in this respect which indicates a very good match in the differential type of circuit. Consequently, the cutoff characteristics could very well be considered ideal, for this application.

It was found that the optimum cutoff voltage, E<sub>1</sub>, was not at all critical—a value anywhere from 0.1 to 1.2 volts being satisfactory. However, for other types of transistors this value may be critical and generally speaking the cutoff voltage should not exceed a few tenths of a volt. It is conventional practice to use diodes as the voltage limiting device for this state.

With the cutoff characteristics being very near ideal, it is now very easy to choose a pair of transistors which are also balanced with respect to their individual saturation voltages. First, a circuit is constructed as shown in figure 12, without the external signal source,

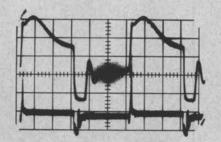

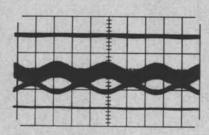

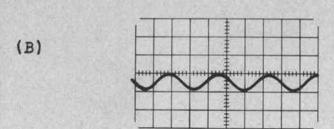

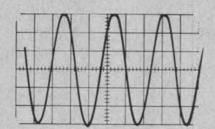

and using a square-wave generator as the switching voltage, E<sub>1</sub>, source. Now by monitoring the output waveform with a high sensitivity, 1 mv/cm, oscilloscope one can insert a pair of transistors, adjust the base current drive from zero through maximum, and note if a balance is obtained. If the balance is obtained the output wave form will appear as shown in figure 19. If not, there will always be an offset in the saturation state, as shown in figure 20. Thus it is not necessary to obtain any point by point plots, as shown in figure 15, to obtain a pair of matched transistors.

As far as the switching source, indicated as E<sub>1</sub>, is concerned, either a voltage or current source may be used. However, as has been shown, it is the base current which drives the transistor into saturation, the on state, and the collector-to-emitter voltage which cuts off the transistor. Furthermore, the switching source must be isolated from ground to obtain the best results. For this purpose a pulse transformer was found to be very good.

In the actual chopper constructed for the dc amplifier, a square-wave voltage generator in conjunction with a pulse-transformer was used as the switching source, E<sub>1</sub>. Under these conditions it is necessary to know what base current is produced by virtue of a given voltage. This information is easily obtained and illustrated in figure 16.

Figure 16, BASE CURRENT AND COLLECTOR-TO-BASE VOLTAGE FOR THE 2NB46 TRANSISTOR, INVERTED CONNECTION.

From this curve, then, a given base current can be imposed by virtue of the applied voltage. The primary reason for obtaining this curve, however, is to find the maximum voltage which can be applied without exceeding the current limitations of the transistor. Since the current is an exponential function of the applied voltage, it is very easy to apply slightly too much voltage, greatly exceed the current rating, and destroy the transistor. This point deserves considerable emphasis.

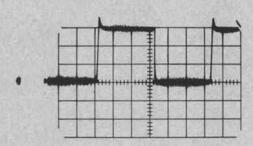

The transient response of this switch can be seen from an analysis of figures 19 and 20. It is fairly obvious that the primary transient occurs as the switch changes states. This is a result of the instantaneous change of the direction of the current in the base region. The resultant spike or transient is of about 25 to 50 millivolts magnitude and has a duration of about 0.4 microsecond. Aside from this transient the switch is very well behaved. No trouble is encountered with delay time or hole-storage time because of the very thin base region of the surface barrier transistor and the very small magnitude of signals, less than one millivolt potential and about a microamp of current, being switched. Along with this discussion it should be mentioned that given equal quality transistors, the NPN transistor will generally exhibit faster transients than the PNP transistor because

of the higher mobility of electrons as compared to holes.

Based upon this discussion an input chopper was constructed as shown in figure 41, for the proposed dc amplifier. The switch itself exhibited a detectable change in output for less than 10 microvolts input and produced no appreciable bias error in either state, conducting or non-conducting.

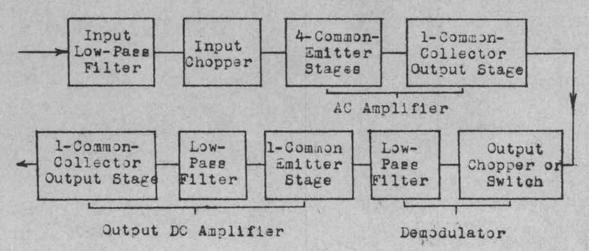

#### AC Amplifier Design Considerations

The design of the ac amplifier is for the most part a straightforward application of the transistor. Since it was desired to be able to utilize chopping frequencies of from 10 kc to 100 kc, it was necessary that the ac amplifier have a bandwidth of from 10 kc to about 1 Mc. The other primary requirement of the ac amplifier was that it have a voltage amplification of about 20,000 or more in the passband with a minimum of noise, distortion, and temperature variations.

The gain versus bias stability conflict which was described previously does not apply to an ac amplifier because of the possible use of reactive bypass elements. In this connection, it should be noted that the emitter leg bypass capacitors should present a 99% bypass in the applicable frequency range to the resistor which they are to bypass. If the conventional 90% bypass elements are

used, it is very likely that undesired degeneration and phase-shift will occur.

The coupling and composition of the ac section was determined primarily by thermal considerations. It has already been shown that the direct-coupled configuration of the same type, PNP or NPN, has the best thermal stability of any other combination. Consequently this scheme was used.

of the available transistors the 2N247 and 2N248, both PNP, seemed well adapted to this application since they have a moderate  $h_{fe}$  of about 40 to 80 and a common base alpha cutoff frequency of 30 and 50 Mc, respectively. The noise figures of the transistors were not available, however, they were judged to be acceptable. Also, the linearity of  $h_{fe}$  was considered acceptable from a brief analysis of their characteristic curves.

one must first make an approximation of the voltage amplification which can be effected per stage. Generally speaking, with some current feedback, an amplification of 20 is easily obtained per stage. With this figure as a base, then, four stages would yield a voltage amplification of 160,000. Thus about 20 db of additional feedback could be applied and still maintain an amplification of 20,000. This would generally be considered enough feedback to make

the amplifier quite stable. Consequently four stages were judged to be adequate.

The quiescent operating points and biasing networks were chosen and constructed by conventional procedures (18, p. 82-101). Of the four stages it was found easiest to accomplish a current gain with the first three stages, and to use the fourth stage as a voltage amplifier.

on the circuit diagram, figure 41. First, current feedback in the form of an unbypassed emitter resistor of from 50 to 200 ohms was used to obtain some degeneration and stabilization. Additionally this type of feedback offers possibilities of extending the frequency response at the higher frequencies by providing a partial capacitive bypass to lower the input impedance of the stage and hence boost the high frequency amplification.

The second type of feedback is a type of dual voltage feedback, in that a voltage is fed back which is proportional to the output current. This type of feedback was applied from the emitter of one stage to the base of the preceding stage. This type of feedback has the normal advantages attributed to loops which enclose two stages rather than a single stage, and also the fact that the feedback is taken from a low-impedance point and applied to a high-impedance point. Thus it does not load down

the stages enclosed in the loop.

Another point to be noted is that because of the high voltage amplification involved and the use of non-ideal power supplies, decoupling was found to be necessary to prevent random oscillations.

Although in a direct-coupled circuit, each stage is somewhat dependent upon the preceeding stage, transistor interchangeability is not adversely affected. To change transistors, generally only a readjustment of the emitter resistor is required to compensate for the variation in transistor parameters which is encountered.

Utilizing the methods outlined above an acceptable ac amplifier was constructed with an amplification of about 22,000 and a bandwidth of 950 kc. For more results see the chapter entitled "Experimental Results".

# Demodulator Design Analysis

At this point in the design, the original dc information has theoretically been chopped and amplified. Now it is desired to recover the amplified information, a process referred to as demodulation.

It should be noted, that by necessity the input circiut must contain a series capacitor between the input

chopper and the ac amplifier to isolate the chopper from

the dc level at the input to the ac amplifier. Since this

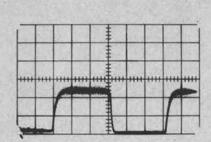

capacitor cannot pass a dc voltage, it distributes the chopped signal about the dc level at the input to the ac amplifier. Thus to recover the chopped and amplified information, only a half of each cycle must be utilized. This is easily accomplished by using a series switch to connect the output of the ac amplifier to a low-pass filter during a half of each chopping cycle.

Since the ac amplifier produces no appreciable phase-shift the positive portion of the chopped wave at the output of the ac amplifier would be in phase with a positive input signal, and the negative portion 180° out of phase with the original signal. Either portion may be recovered depending upon the phase of the recovered signal which is desired. In this specific case the positive in-phase portion was required.

The resultant demodulator then takes the form shown below.

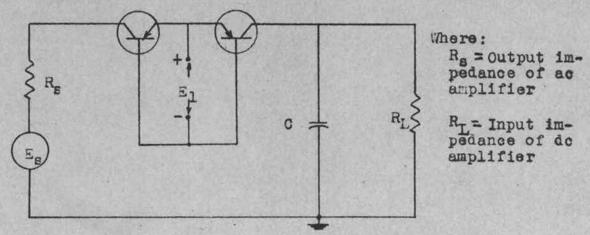

Figure 17. An Equivalent Demodulator Circuit Diagram

For a theoretical minimum noise, the capacitor should charge very fast and discharge very slowly or  $R_{\rm g} \rightarrow 0$ , and  $R_{\rm L} \rightarrow \infty$ . Since the common-emitter stage has an output impedance of several thousand ohms, it was decided to use a common-collector output stage on the ac amplifier to feed the demodulator from a low impedance source, about 1,000 ohms. However, it was later found that a source impedance of several thousand ohms was more desirable since the modulated wave contains several undesirable transients. Thus, by making the charging time-constant longer, the demodulated output of the capacitor could not follow the very brief transients and the noise was considerably reduced. Therefore, the common collector ac output stage is not necessary.

The switch itself is similar to the input chopper discussed previously except that the normal series connection is used. This is a better configuration for the high-level application involved here. Also, the 2N588 transistor was chosen over the 2N346 for this application because of its better high-level characteristics.

The parameters of the equivalent circuit, figure 17, which were obtained in the actual demodulator were approximately  $R_{\rm S}=6,000$  ohms,  $R_{\rm L}=20,000$  ohms, and C=0.02 uf. Thus the charging time-constant was about 0.12 milliseconds and the discharge time-constant about 0.40 milliseconds,

assuming idealized switching conditions. These parameters were found to be about optimum for a shopping frequency of 80 kc, or a chopping period of 12.5 microseconds.

# Output DC Amplifier Design Requirements

After constructing and testing the input circuit, input chopper, ac amplifier and demodulator, it was found that the overall amplification from the input to the output of the demodulator was about 5,000. Thus an amplification of at least 4 is required to boost the total amplification to 20,000 or more.

As previously discussed, it was also required that the input impedance to the high-level dc amplifier be in the order of ten or twenty thousand ohms.

To achieve this minimum gain of 4 along with an input impedance of about 20,000 chms, and acceptable thermal stability, it was decided that silicon transistors would be necessary. This conclusion is apparent after setting up a few theoretical circuits which satisfy the amplification and input impedance requirements, and then calculating the stability factors for the various circuits, allowing a 15°F temperature variation. With germanium transistors it was found that the quiescent collector voltage could easily change a volt or more, while with silicon transistors the change was in the order of

hundredths of a volt.

The NPN type of transistor, in contrast to the PNP transistors used in the ac amplifier, was chosen in order to use the quiescent dc level of -14 volts at the output of the demodulator to the best advantage. In addition to the type, it is easily seen that a moderate h<sub>fe</sub> is desired along with an alpha cutoff frequency of several hundred kilocycles.

One more condition must be imposed before a satisfactory transistor can be chosen. This condition is that the

transistor must have a maximum collector-to-emitter voltage

in the order of 40 volts or more if a + 15 volt output

swing is to be permitted. This is true because the commonemitter amplification stage must produce a plus or minus

17 or 18 volts which is attenuated to 15 volts by the

common-collector output stage and the AZS arrangement.

From these conditions, then, the 2N334 transistor was chosen. Specifically, it is a silicon type NPN transistor with an h<sub>fe</sub> of about 40 and an alpha cutoff frequency of 8 Mc. In addition it has a maximum collector-to-emitter voltage of 45 volts.

The output de amplifier circuit itself is a straightforward conventional type of circuit, which presents no