## AN ABSTRACT OF THE THESIS OF

<u>Triet T. Le</u> for the degree of <u>Doctor of Philosophy</u> in <u>Electrical and Computer Engineering</u> presented on <u>February 19, 2008</u>. Title: <u>Efficient Power Conversion Interface Circuits for Energy Harvesting</u> <u>Applications</u>

Abstract approved:

Terri S. Fiez

Karti Mayaram

Harvesting energy from the environment for powering micro-power devices have been increasing in popularity. These types of devices can be used in embedded applications or in sensor networks where battery replacement is impractical. In this dissertation, different methods of energy harvesting from the environment are explored as alternative sources of energy for devices. Some of the most popular energy extraction used in electronic devices today are radio frequency (RF) and thermal/vibrational energy extraction. This dissertation presents novel power techniques that enable some of the most efficient power conversion circuits published to date.

New power conversion circuits to interface to a piezoelectric micro-power generator that produces electrical energy from temperature differences have been fabricated and tested. Circuit designs and measurement results are presented for a half-wave synchronous rectifier with voltage doubler, a full-wave synchronous rectifier and a passive full-wave rectifier circuit. The active rectifier based on synchronous rectification, fabricated in a 0.25- $\mu$ m CMOS process, is 86% efficient with 22- $\mu$ W peak output power when connected to the piezoelectric micro-power generator. This gives the highest efficiency to date for active rectification circuits at the micro-power level. The passive rectifier circuit is 66% efficient with 16- $\mu$ W peak output power and requires no quiescent current to operate.

RF-powered devices are typically inductively coupled and extract their energy from the near field while operating within a few inches of the radiating source. Longer operating distances, exceeding 10 meters, are desired for a broader set of applications including distributed sensor networks. This dissertation describes an efficient method for far field power extraction from RF energy to enable longdistance passively powered sensor networks.

Passive rectifier circuits are designed in the TSMC 0.25 $\mu$ m mixed-signal CMOS process and antennas for the system are printed on a 4-layer FR4 board. A high-Q resonator is used with a matching network to passively amplify the input voltage to the rectifier. At the circuit level, floating gate transistors are used as rectifying diodes to reduce the diode threshold loss in voltage rectification and therefore increase the rectifier efficiency. A 36-stage rectifier fabricated in a 0.25- $\mu$ m CMOS process attains an efficiency of over 60% in the far field with a received power sensitivity of 5.5 $\mu$ W (-22.6 dBm), corresponding to an operating distance of 44 meters. The effective threshold voltage of the floating-gate diode is reduced to 36 mV. This is the highest performance for far-field RF energy conversion reported to date.

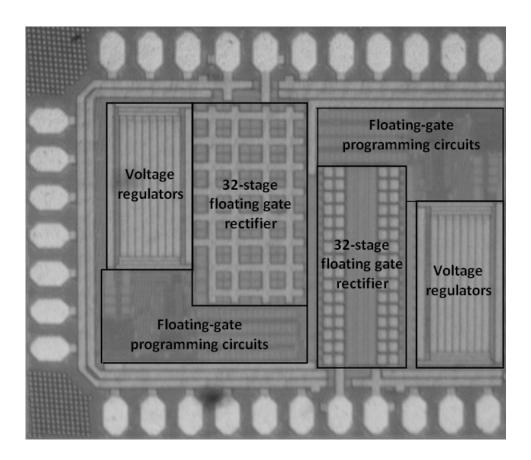

In ultra-low energy system, such as sensor networks, it is essential that power management circuitry are designed to dissipate very low quiescent power. RF energy and power management circuits are designed in a  $0.18\mu$ m CMOS process. Voltage regulators are designed to operate at high input voltage and low power in a standard CMOS process. The voltage regulators can with stand input voltages up to 12 volts and dissipates from 90 nW to 1.4  $\mu\rm W$  of power. A floating-gate programming circuit is designed with a self-wakeup timer that turns itself on about once a month. The floating-gate programming circuits dissipates about 30 nW in sleep mode and 8  $\mu\rm W$  in active mode. ©Copyright by Triet T. Le February 19, 2008 All Rights Reserved Efficient Power Conversion Interface Circuits for Energy Harvesting Applications

by

Triet T. Le

## A THESIS

## submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Presented February 19, 2008 Commencement June 2008 Doctor of Philosophy thesis of <u>Triet T. Le</u> presented on February 19, 2008

APPROVED:

Major Professor, representing Electrical and Computer Engineering

Director of the School of Electrical Engineering and Computer Science

Dean of the Graduate School

I understand that my thesis will become part of the permanent collection of Oregon State University libraries. My signature below authorizes release of my thesis to any reader upon request.

Triet T. Le, Author

#### ACKNOWLEDGMENT

First of all, I express sincere appreciation to my advisor **Dr. Terri Fiez** for giving me the opportunity to do this research. I thank her for making me believe that I can design amazing circuits that are capable of doing great things (i.e. operate at 50 meters distance). Even with her busy schedule as director of the School of EECS, Terri still finds the time to meet with me personally to provide me with guidance and support throughout my years of research at Oregon State University. I thank my co-advisor **Dr. Karti Mayaram** for his valuable insight with my research. Karti always has an eye out for details which really helped keep me on top of everything I've set out to do.

Thanks go to other faculty members, Professor Huaping Liu and Professor Andreas Weisshaar for their valuable suggestions and comments as members of my graduate committee. Special thank to Ravi Naiknaware for his help and suggestions on testing my power harvester when I needed it most. Thanks to Robert Batten for all the help he provided me with when I needed to use the mixed-signal lab, and thanks for cleaning up the mess I made in there. I thank Zhimin Li for his help with the PCB board design. I am grateful to James Ayers for his help with the measurements, for the emotional support he gave at the Power Harvesting Workshop and for making people think my circuits are capable of doing great things (i.e. save the forest, end global warming, and enable graduation). I thank Thomas Brown for the technical assistance and all the helpful resources (i.e. technical references and free beers) he provided over the years. Thanks to Napong Panitantum for all the help setting up Cadence and the emotional support in the lab. Thanks Vikrant Arumugam for his help

and figures that I included in this thesis. Thanks **Hector** and **Farhad** for keeping me in good physical shape and for not letting me take it easy in the gym. To all of my other lab mates in KEC 3040, thanks for all the help you have given, everything you did for me are gratefully appreciated.

I would like to thank all of my friends from my earlier years of graduate school. Thanks all for being my companions throughout my first two years. Together, we survived through all the course work and exams.

In addition, I would like to thank everyone at Living Water Baptist Church for their support in providing me comfort throughout the difficult times in my life.

I would also like to thank everyone in my family for their support throughout my years in college. I thank my aunt and uncle, **Dao Le** and **Hoa Nguyen** as well as my parents, **Hanh** and **Cam Le** for providing me a home on weekends and breaks. I thank them for the sacrifice they made raising me from childbirth to adulthood. I thank all my brothers and sisters for their financial as well as emotional support in my 10-or-so years of college.

A special thanks go to **Hue Le**, my wife for her love and support. For believing in me, caring for me, and for keeping me healthy. Without her I would not be as healthy or motivated as I am today.

And most of all, I thank **GOD**, my Lord and Savior for his guidance in every aspect of my life. I believe "I can do everything through him who gives me strength."

## TABLE OF CONTENTS

# Page

| 1 | INTI | RODUCTION                                               | 1   |

|---|------|---------------------------------------------------------|-----|

|   | 1.1  | Motivation                                              | 1   |

|   | 1.2  | Comparison of Energy Harvesting Methods                 | 3   |

|   |      | 1.2.1 Radio Frequency Energy Harvesting                 | 3   |

|   |      | 1.2.2 Piezoelectric Energy Harvesting                   | 7   |

|   |      | 1.2.3 Solar Energy Harvesting                           | 12  |

|   |      | 1.2.4 Thermo Electric Energy Harvesting                 | 15  |

|   |      | 1.2.5 Vibrational Energy Harvesting                     | 18  |

|   |      | 1.2.6 Electrostatic Energy Harvesting                   | 19  |

|   |      | 1.2.7 Acoustic Energy Harvesting                        | 19  |

|   |      | 1.2.8 Summary of Energy Harvesting Methods              | 20  |

|   | 1.3  | Dissertation Outline                                    | 20  |

| 2 |      | ZOELECTRIC MICRO-POWER GENERATION INTERFACE CIR-        | 0.4 |

|   |      | ΓS                                                      | 24  |

|   | 2.1  | Abstract                                                | 24  |

|   | 2.2  | Introduction                                            | 24  |

|   | 2.3  | Piezoelectric Device Characteristics and Modeling       | 28  |

|   | 2.4  | Half-Wave Rectifier Interface Circuits                  | 31  |

|   |      | 2.4.1 Passive Half-Wave Diode Rectifiers                | 31  |

|   |      | 2.4.2 Synchronous Half-Wave Rectification               | 36  |

|   | 2.5  | Full-Wave Rectifier Circuits                            | 44  |

|   |      | 2.5.1 Passive Full-Wave Rectifier Interface Circuit     | 45  |

|   |      | 2.5.2 Synchronous Full-Wave Rectifier Interface Circuit | 52  |

|   | 2.6  | Conclusion                                              | 60  |

# TABLE OF CONTENTS (Continued)

| 3 |     |        | T FAR-FIELD RADIO FREQUENCY ENERGY HARVEST-<br>PASSIVELY POWERED SENSOR NETWORKS | 61  |

|---|-----|--------|----------------------------------------------------------------------------------|-----|

|   | 3.1 | Abstr  | act                                                                              | 61  |

|   | 3.2 | Intro  | duction                                                                          | 61  |

|   | 3.3 | System | m Overview                                                                       | 64  |

|   |     | 3.3.1  | High-Q Resonator                                                                 | 68  |

|   |     | 3.3.2  | Impedance Matching                                                               | 69  |

|   |     | 3.3.3  | Rectifier Circuit                                                                | 71  |

|   |     | 3.3.4  | Parasitic Components                                                             | 72  |

|   |     | 3.3.5  | Receive Antenna                                                                  | 73  |

|   | 3.4 | Rectif | fier Design                                                                      | 74  |

|   |     | 3.4.1  | Conventional Voltage Doubler Rectifier                                           | 74  |

|   |     | 3.4.2  | Floating-Gate Voltage Doubler Rectifier                                          | 76  |

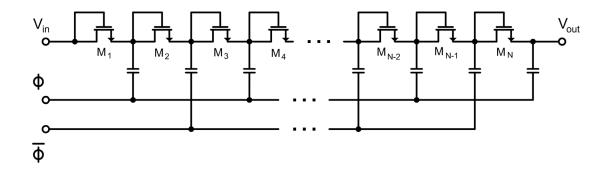

|   |     | 3.4.3  | Multistage Rectifier Circuit                                                     | 81  |

|   |     | 3.4.4  | Rectifier Designs and Optimization                                               | 81  |

|   | 3.5 | Anter  | nna Design                                                                       | 88  |

|   | 3.6 | Expe   | rimental Results                                                                 | 93  |

|   |     | 3.6.1  | RF-DC Rectifier Circuit Performance                                              | 93  |

|   |     | 3.6.2  | RF-DC Power Conversion System Performance                                        | 102 |

|   | 3.7 | Concl  | usion                                                                            | 120 |

| 4 |     |        | T FAR-FIELD RF POWER CONVERSION INTERFACE<br>ER MANAGEMENT CIRCUITS 1            | 121 |

|   | 4.1 | Abstr  | act 1                                                                            | 121 |

|   | 4.2 | Intro  | luction1                                                                         | 121 |

# TABLE OF CONTENTS (Continued)

| 4.3 | Energy Harvesting System Overview122                                         |

|-----|------------------------------------------------------------------------------|

|     | 4.3.1 System Flow Diagram with Floating-gate Programming 123                 |

|     | 4.3.2 Link Budget                                                            |

| 4.4 | Rectifier Design 127                                                         |

|     | 4.4.1 Conventional and Floating-gate Voltage Doubler Rectifier $\ .\ .\ 127$ |

|     | 4.4.2 Multistage Rectifier Circuit                                           |

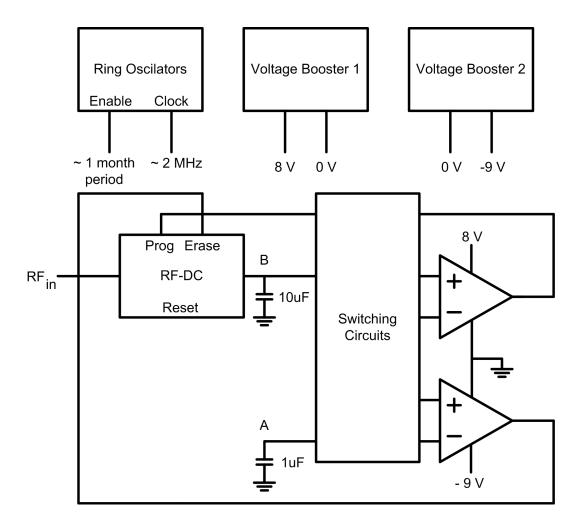

| 4.5 | Floating-Gate Programming Circuits 128                                       |

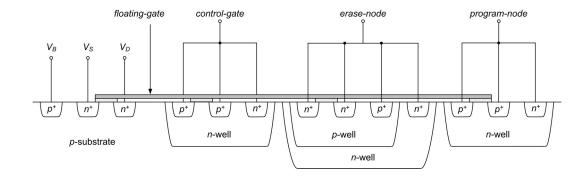

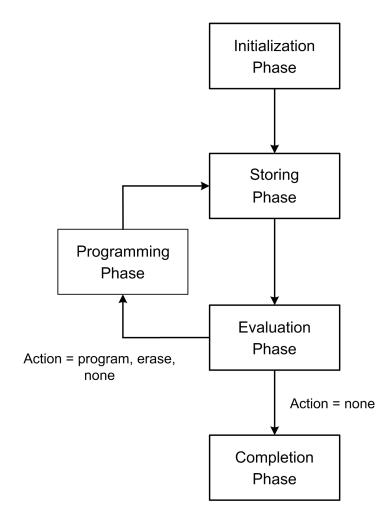

|     | 4.5.1 Floating-Gate Programming Procedures                                   |

|     | 4.5.1.1 Initialization Phase                                                 |

|     | 4.5.1.2 Storing Phase                                                        |

|     | 4.5.1.3 Evaluation Phase                                                     |

|     | 4.5.1.4 Programming Phase 137                                                |

|     | 4.5.1.5 Completion Phase                                                     |

|     | 4.5.2 Ring Oscillator Circuits                                               |

|     | 4.5.3 Voltage Boosters                                                       |

|     | 4.5.4 Low Voltage Regulator                                                  |

| 4.6 | Voltage Regulator Designs141                                                 |

|     | 4.6.1 Adaptive Biasing Circuits                                              |

|     | 4.6.2 Current Reference                                                      |

|     | 4.6.3 Reference Voltage                                                      |

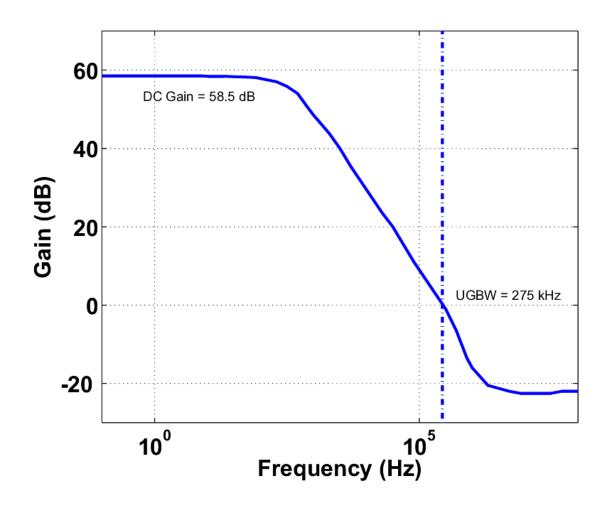

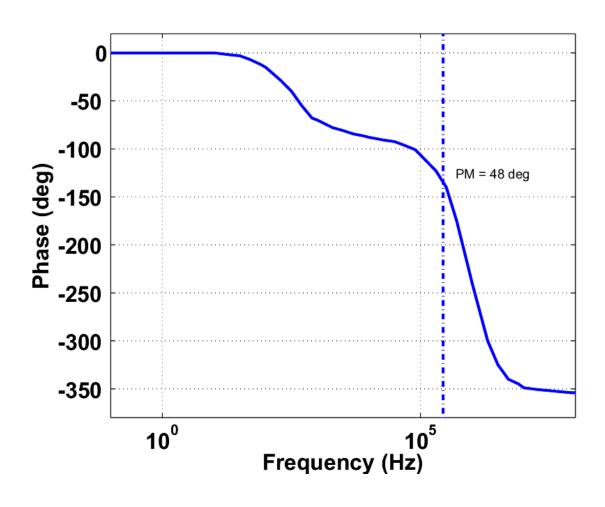

|     | 4.6.4 Opamp Design                                                           |

|     | 4.6.5 Pass Transistors Switches                                              |

|     | 4.6.6 Regulator Performance                                                  |

| 4.7 | Measurement Results                                                          |

# TABLE OF CONTENTS (Continued)

# Page

|    |      | 4.7.1 | Test Setup                                 |

|----|------|-------|--------------------------------------------|

|    |      | 4.7.2 | Floating-gate Rectifier Measured Results   |

|    |      | 4.7.3 | Floating-gate Programming Measured Results |

|    |      | 4.7.4 | Voltage Regulator Measured Results         |

|    |      | 4.7.5 | Power Harvester Performance                |

|    | 4.8  | Concl | usion                                      |

|    |      |       |                                            |

| 5  | CON  | CLUS  | ION                                        |

|    | 5.1  | Concl | usion                                      |

|    | 5.2  | Futur | e Work                                     |

| BI | BLIO | GRAP  | НҮ175                                      |

| AF | PEN  | DICES |                                            |

|    | APP  | ENDI  | X A Voltage Regulator Simulation Results   |

## LIST OF FIGURES

Figure

| 1.1  | General block diagram of an energy harvesting system                                                                                                                                   | 2  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | Path loss of RF signal transmission at UHF                                                                                                                                             | 5  |

| 1.3  | Maximum allowable receive power versus distance according to FCC regulations for RF energy harvesters from a single RF power source.                                                   | 6  |

| 1.4  | Path loss of RF signal transmission in UHF with pathloss model derived from [18, 19]                                                                                                   | 8  |

| 1.5  | Maximum allowed receive power versus distance according to FCC regulations for RF power harvesters from a single RF power source, with pathloss model derived from [18, 19]            | 9  |

| 1.6  | Diagram of piezoelectric power generator [24]                                                                                                                                          | 10 |

| 1.7  | Power density of piezoelectric power generator at different frequency<br>and amplitude of input vibration [24]                                                                         | 11 |

| 1.8  | I-V characteristics of a typical 1-W solar cell for different lighting conditions (at 25°C).                                                                                           | 13 |

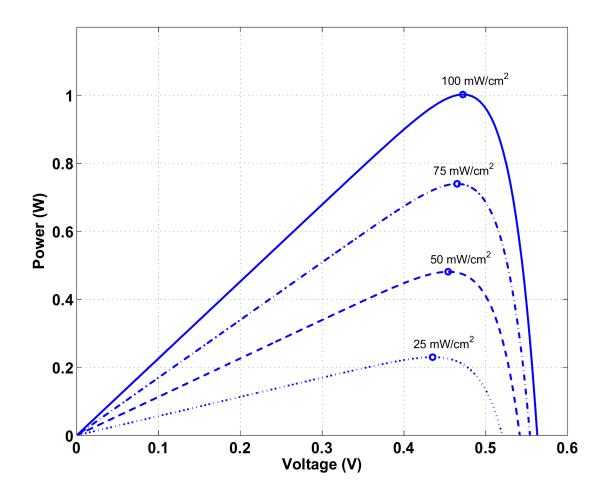

| 1.9  | Output power of a typical 1-W solar cell for different lighting condi-<br>tions (at 25°C).                                                                                             | 14 |

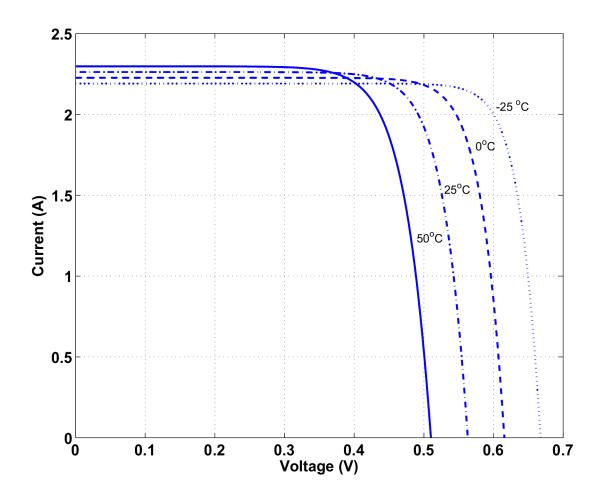

| 1.10 | I-V characteristics of a typical 1-W solar cell at different temperatures (at $100 \text{ mW/cm}^2$ ).                                                                                 | 16 |

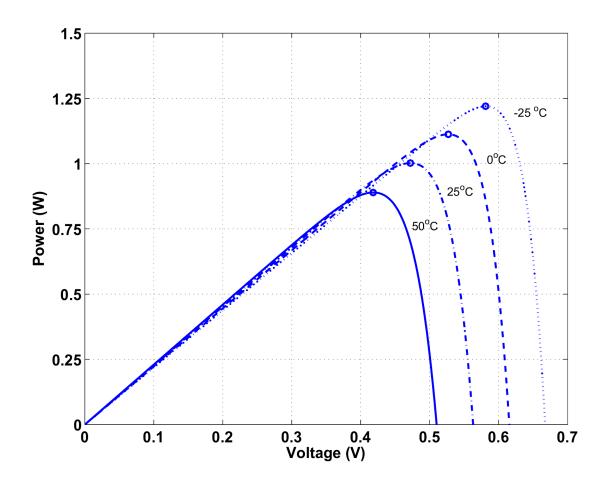

| 1.11 | Output power of a typical 1-W solar cell at different temperatures (at $100 \text{ mW/cm}^2$ )                                                                                         | 17 |

| 2.1  | Schematic of power generation using a piezoelectric laminate                                                                                                                           | 26 |

| 2.2  | Picture of the fabricated PZT                                                                                                                                                          | 27 |

| 2.3  | Measured open circuit output voltage of the 2.45 mm x 2.45 mm piezoelectric membrane.                                                                                                  | 29 |

| 2.4  | Measured peak-to-peak output as a function of input frequency                                                                                                                          | 30 |

| 2.5  | Equivalent circuit of the piezoelectric membrane which models the output voltage waveform as a function of excitation frequency (f) as well as the characteristic output impedance [9] | 32 |

| 2.6  | Half-wave rectifier with diode-tied NMOS                                                                                                                                               | 33 |

| 2.7  | Half-wave rectifier with NMOS and PMOS diodes.                                                                                                                                         | 34 |

# Figure

# Page

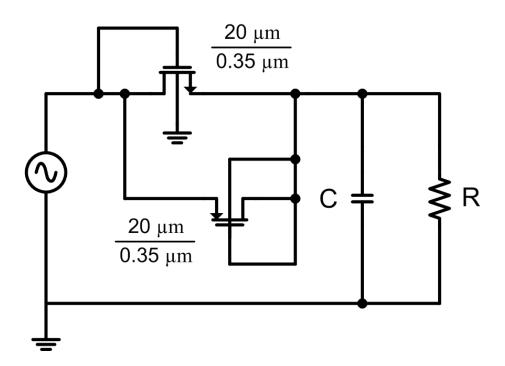

| 2.8  | Simulated power delivery of half-wave rectifier circuits in a $0.35$ - $\mu$ m CMOS process with the PZT input as shown in Fig. 2.3 | 35 |

|------|-------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.9  | Modified synchronous rectifier to generate two-phase clocking for the voltage doubler                                               | 37 |

| 2.10 | Transistor-level schematic of the voltage doubler.                                                                                  | 38 |

| 2.11 | Schematic of the comparator designed and fabricated in the TSMC 0.35- $\mu$ m CMOS process                                          | 41 |

| 2.12 | Simulated efficiency versus output load for the synchronous rectifier designed in the $0.35$ - $\mu$ m CMOS process.                | 42 |

| 2.13 | Die photograph of the synchronous rectifier and voltage doubler de-<br>signed and fabricated in the TSMC 0.35- $\mu$ m CMOS process | 43 |

| 2.14 | Passive full-wave rectifier.                                                                                                        | 45 |

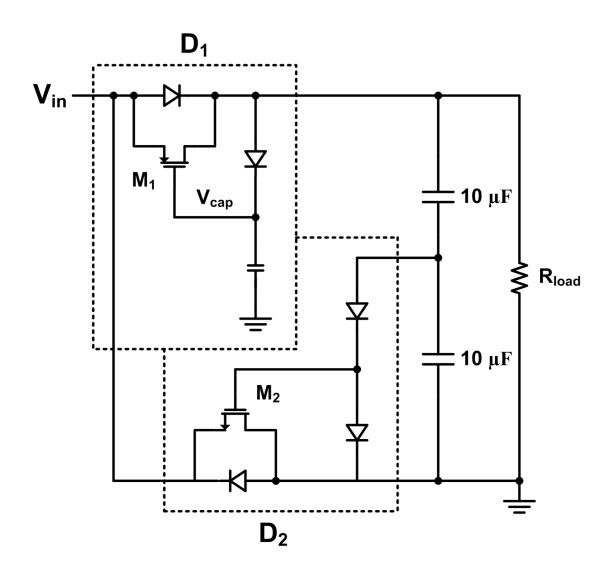

| 2.15 | Reduced diode turn on voltage passive power conversion circuit                                                                      | 46 |

| 2.16 | Die photograph of the passive full-wave rectifier circuit with reduced VT circuitry fabricated in a $0.25$ - $\mu$ m CMOS process   | 48 |

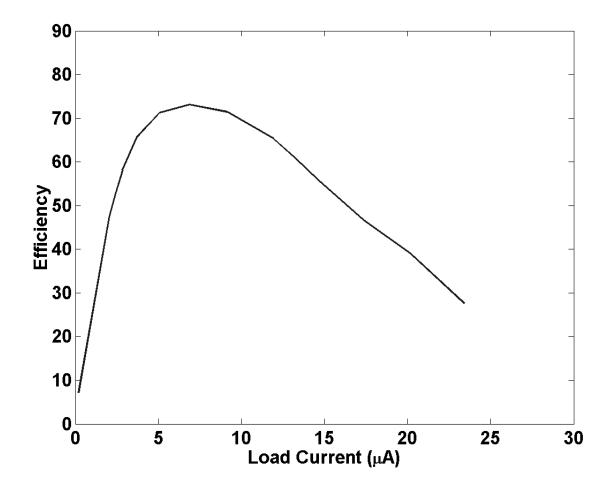

| 2.17 | Power conversion efficiency versus load current of the full-wave passive rectifier circuit with reduced-VT                          | 49 |

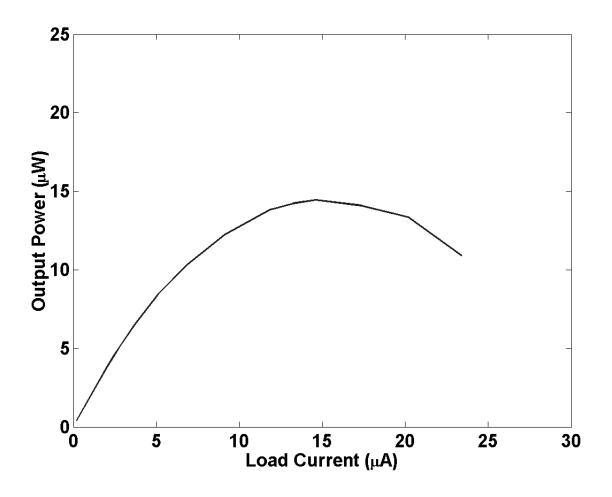

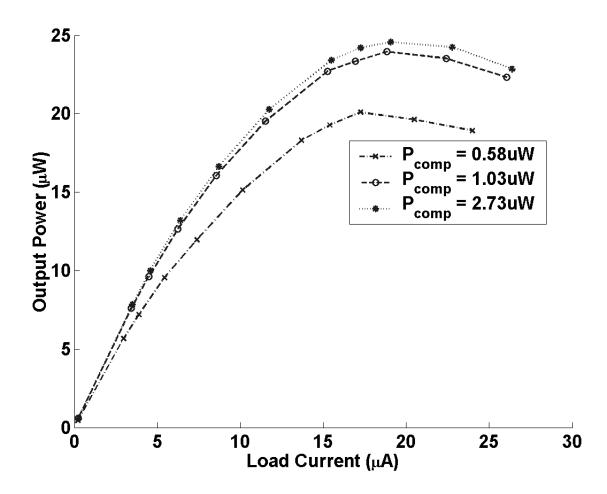

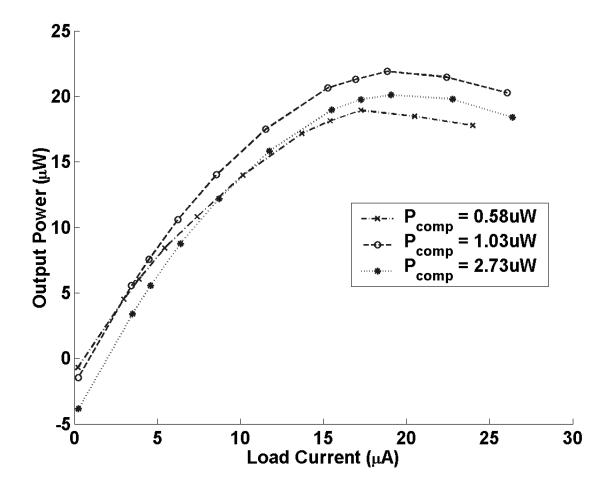

| 2.18 | Output power versus load current of the full-wave passive rectifier circuit with reduced-VT.                                        | 50 |

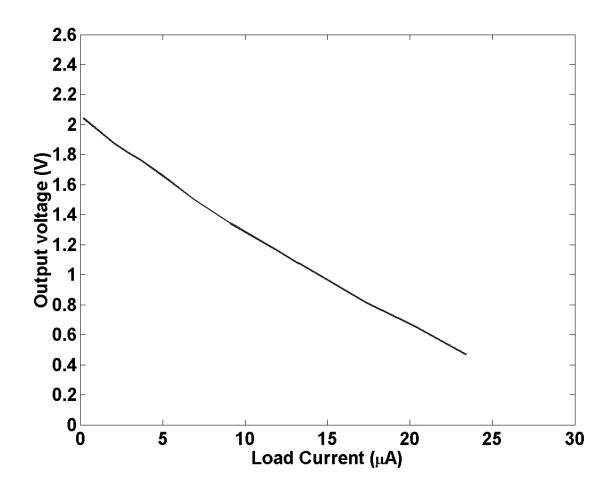

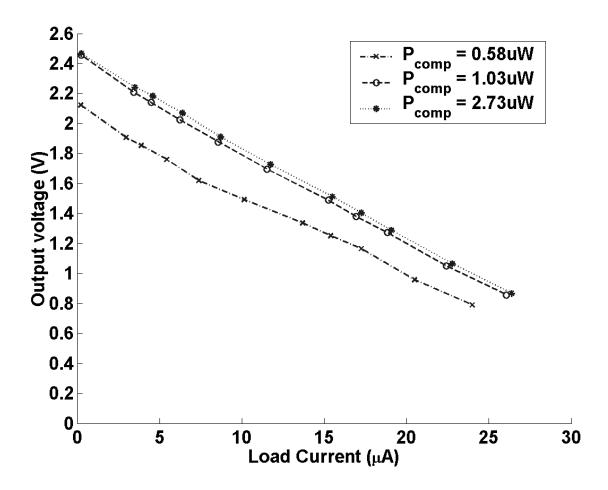

| 2.19 | Output voltage versus load current of the full-wave passive rectifier circuit with reduced- $V_T$ .                                 | 51 |

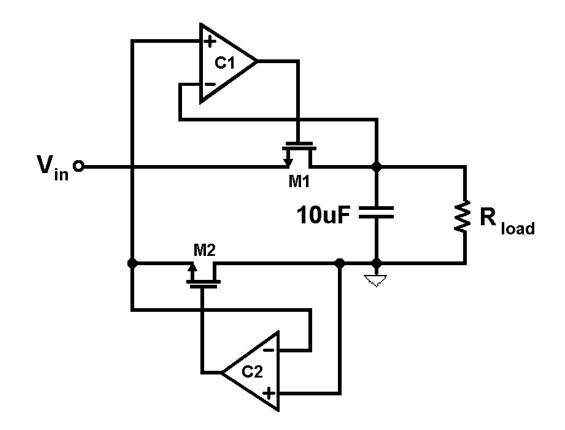

| 2.20 | Synchronous full-wave rectifier.                                                                                                    | 52 |

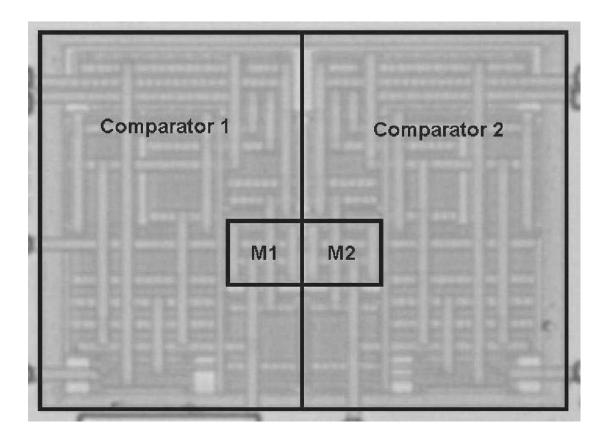

| 2.21 | Die photograph of the full-wave synchronous rectifier circuit fabri-<br>cated in a $0.25\mu$ m CMOS process                         | 54 |

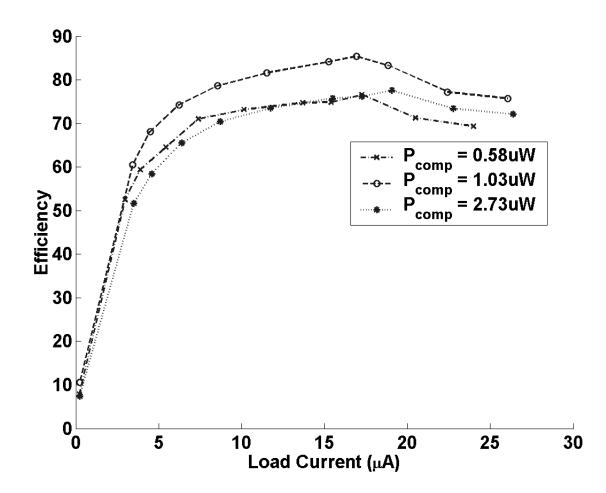

| 2.22 | Measured power conversion efficiency for the synchronous rectifier                                                                  | 55 |

| 2.23 | Measured output power for the synchronous rectifier                                                                                 | 56 |

| 2.24 | Measured effective output power for the synchronous rectifier                                                                       | 58 |

| 2.25 | Measured output voltages for the synchronous rectifier.                                                                             | 59 |

# Figure

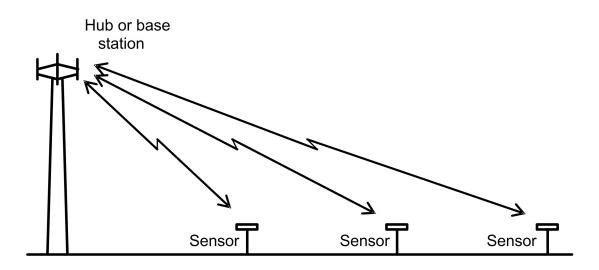

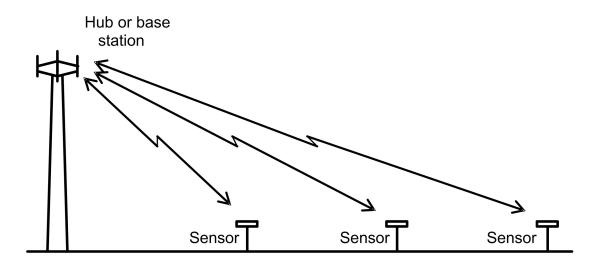

| 3.1  | Illustration of communication links between base station (hub) and sensors in a passively powered sensor network. | 65 |

|------|-------------------------------------------------------------------------------------------------------------------|----|

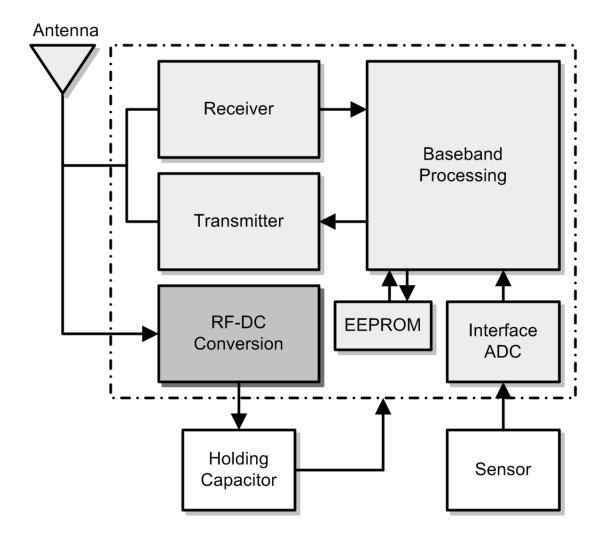

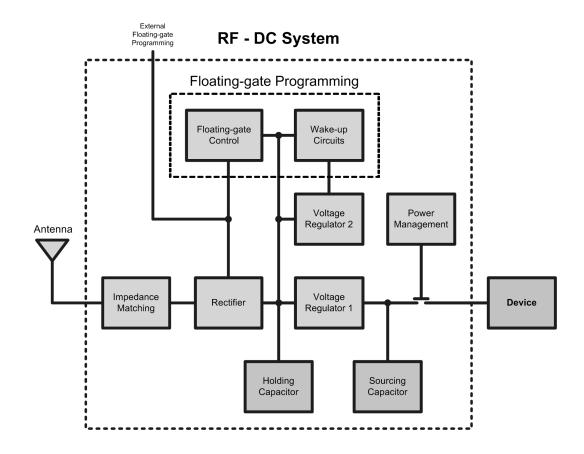

| 3.2  | Block diagram illustrating the RF-DC power conversion system in a passively powered sensor.                       | 66 |

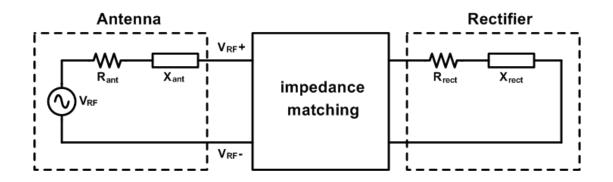

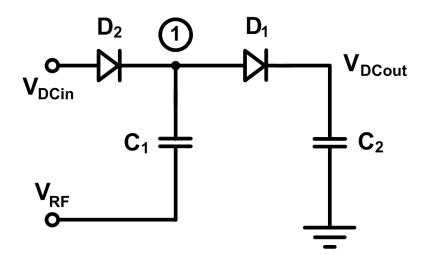

| 3.3  | Passive RF-DC conversion circuit showing the equivalent circuit representation for the antenna and rectifier.     | 67 |

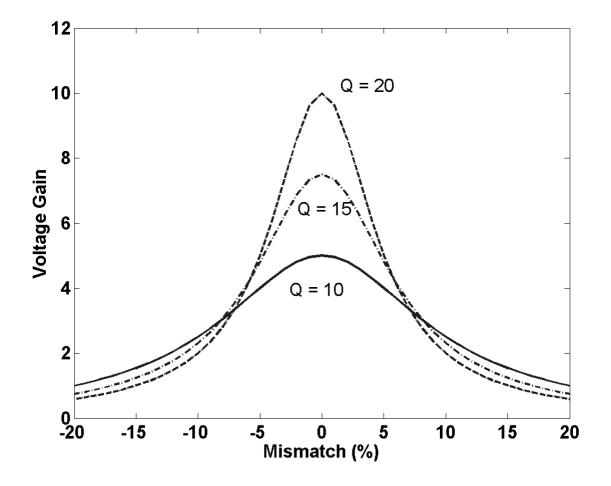

| 3.4  | Effect of impedance mismatch in high Q resonators                                                                 | 70 |

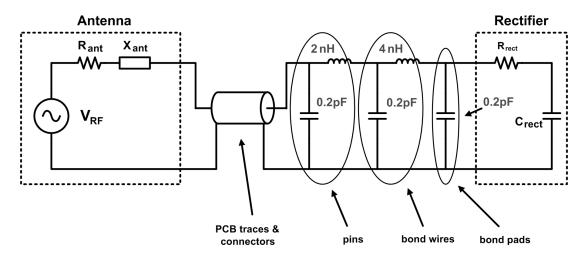

| 3.5  | Parasitic components that affect performance of the RF-DC power conversion circuit.                               | 73 |

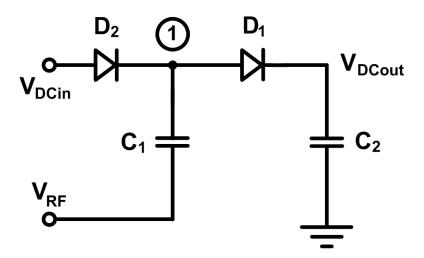

| 3.6  | Conventional voltage doubler rectifier.                                                                           | 74 |

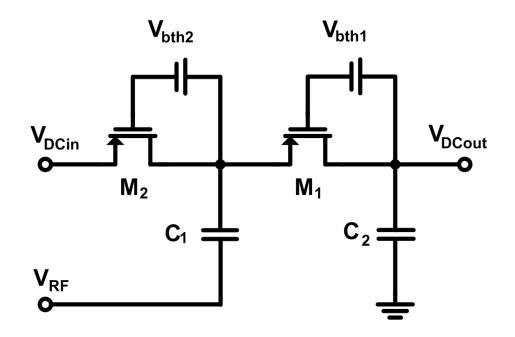

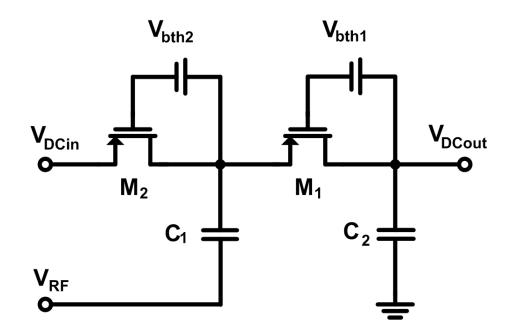

| 3.7  | PMOS floating-gate rectifier.                                                                                     | 75 |

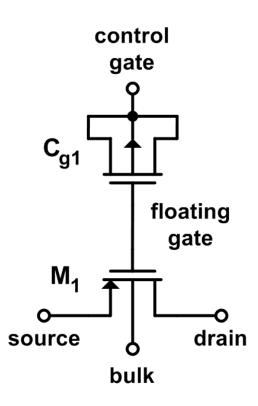

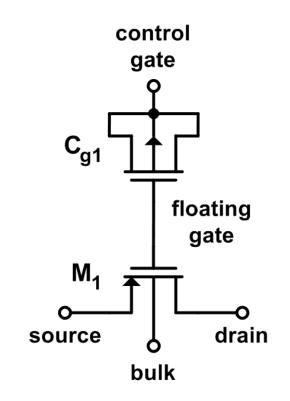

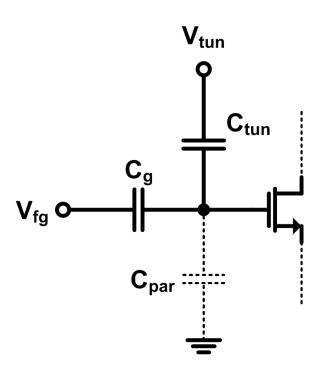

| 3.8  | PMOS implementation of a floating gate transistor.                                                                | 77 |

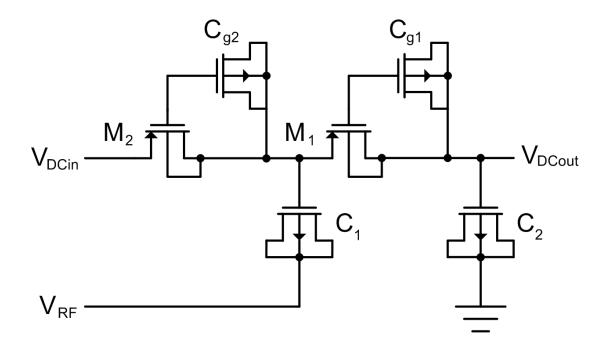

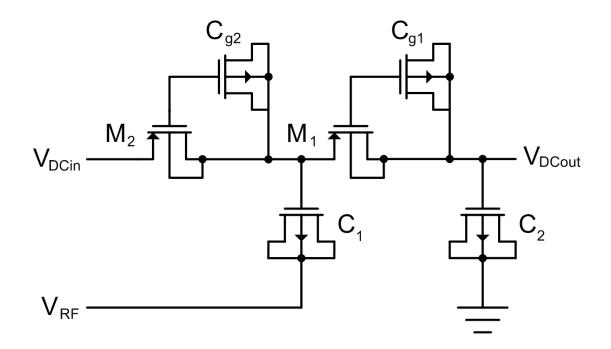

| 3.9  | Transistor level schematic of PMOS floating-gate rectifier.                                                       | 80 |

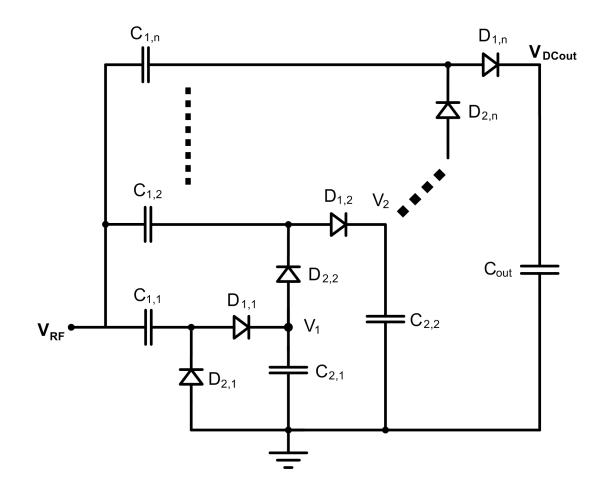

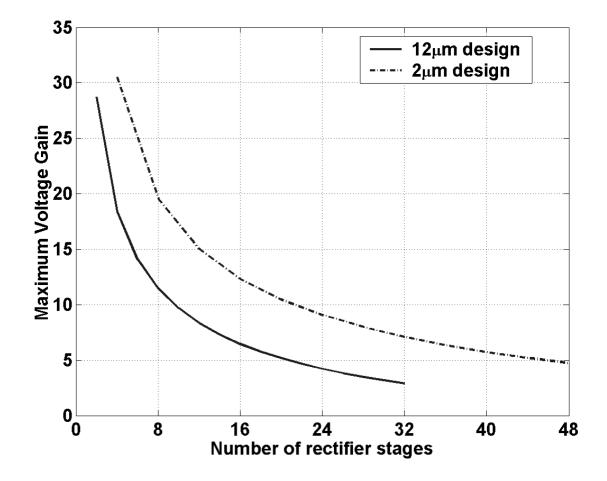

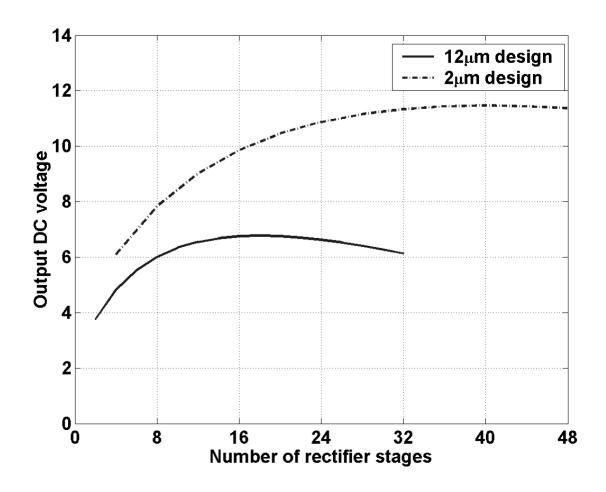

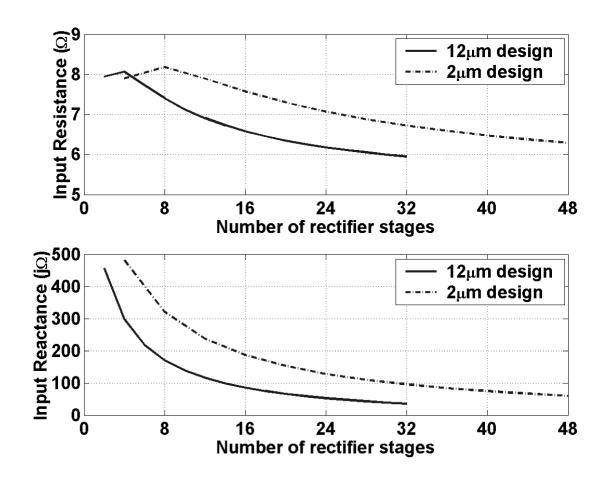

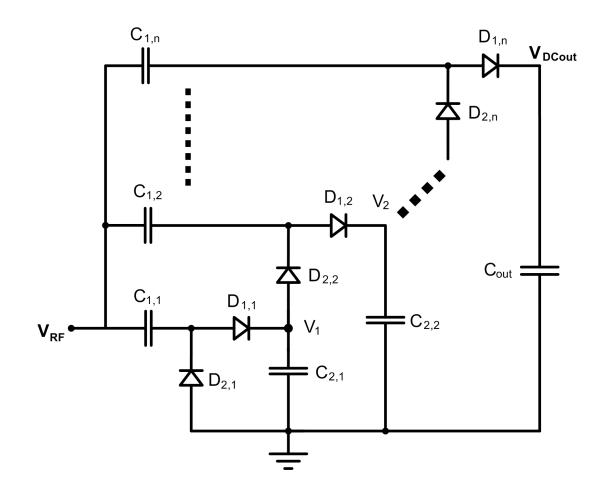

| 3.10 | Voltage doubler rectifier with N-stages in cascade                                                                | 82 |

| 3.11 | Effect of number of rectifier stages on maximum voltage gain                                                      | 84 |

| 3.12 | Effect of number of rectifier stages on output DC voltage                                                         | 85 |

| 3.13 | Effect of number of rectifier stages on input impedance of rectifier                                              | 86 |

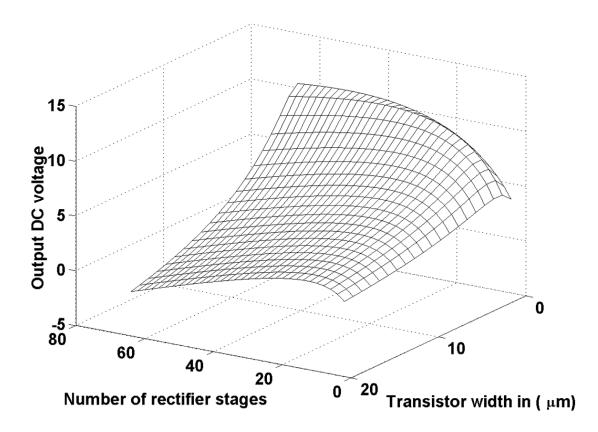

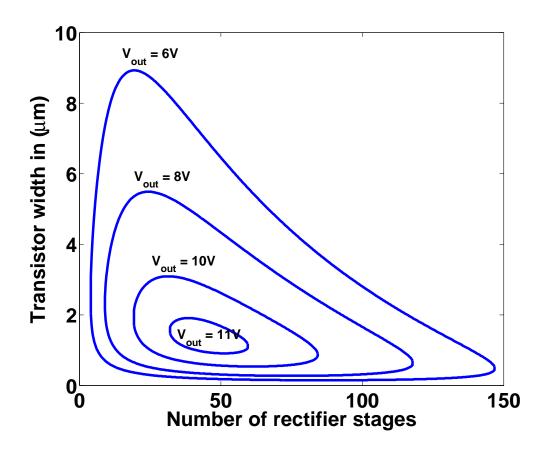

| 3.14 | Output voltage curves as function of the number of rectifier stages<br>and the transistor width                   | 87 |

| 3.15 | Contour plot of constant output voltage                                                                           | 88 |

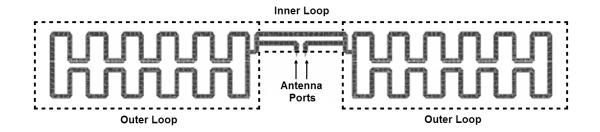

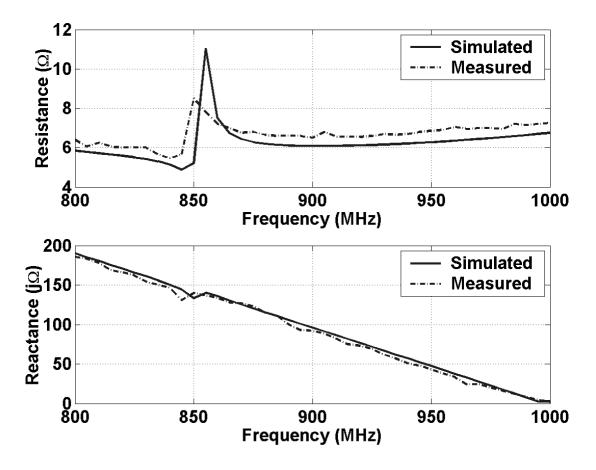

| 3.16 | Antenna design for RF-DC converter.                                                                               | 90 |

| 3.17 | Simulated and measured components of the antenna input impedance.                                                 | 91 |

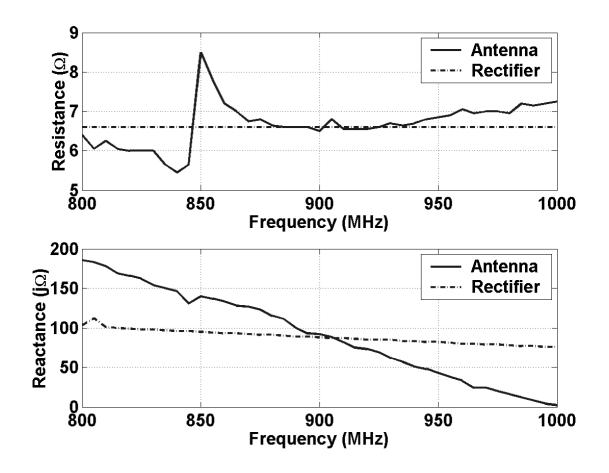

| 3.18 | Measured input impedance of antenna and rectifier circuit                                                         | 92 |

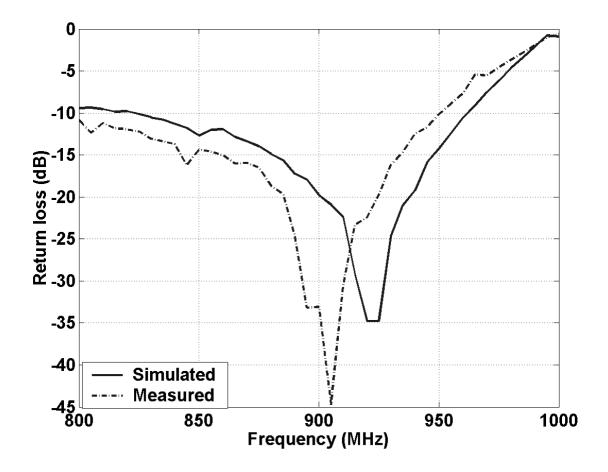

| 3.19 | Measured return loss for 36-stage rectifier design                                                                | 93 |

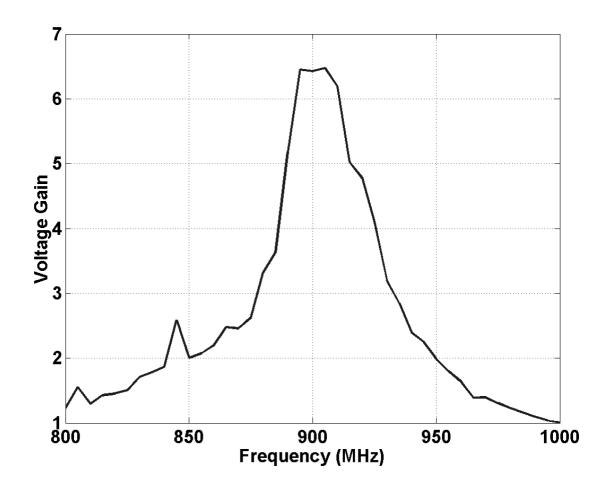

| 3.20 | Voltage gain for 36-stage rectifier design                                                                        | 94 |

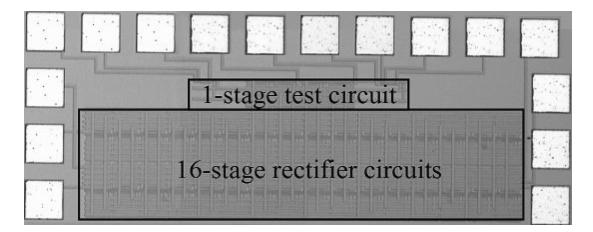

| 3.21 | Die photograph of 16-stage rectifier circuit fabricated in a $0.25\mu m$ CMOS process                             | 95 |

# Figure

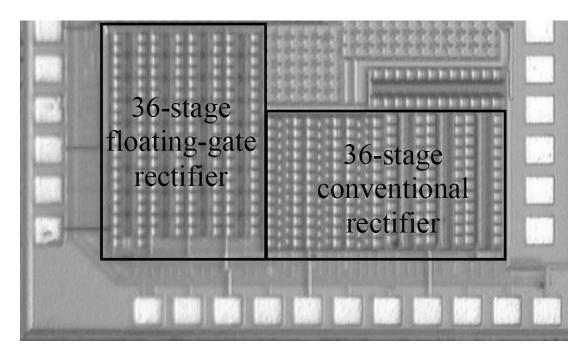

| 3.22 | Die photograph of 36-stage rectifier circuit fabricated in a $0.25\mu m$ CMOS process                            |

|------|------------------------------------------------------------------------------------------------------------------|

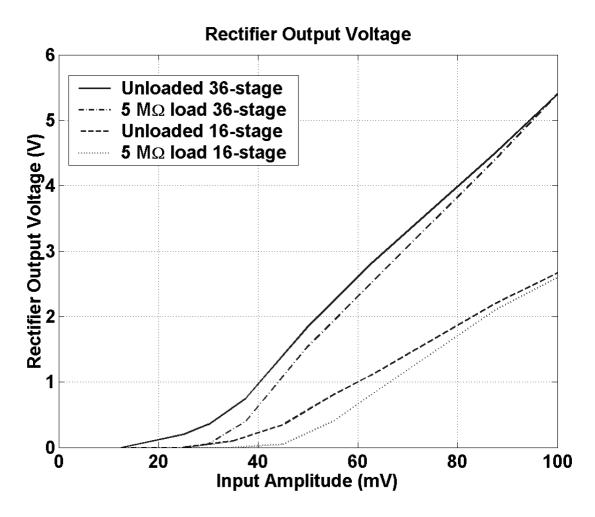

| 3.23 | Measured output DC voltage as a function of the sinusoidal input<br>voltage amplitude                            |

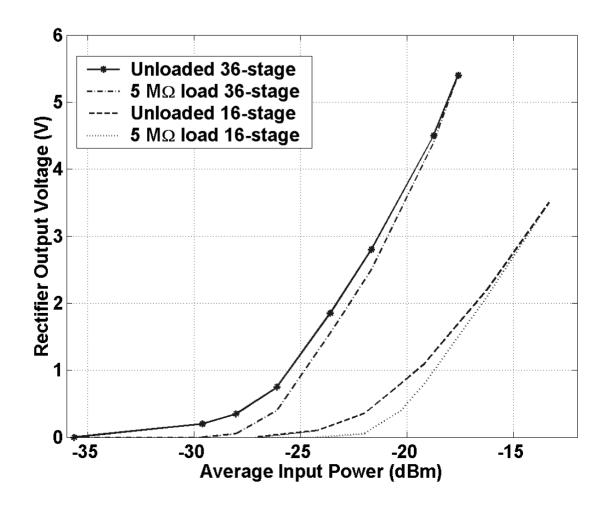

| 3.24 | Measured output DC voltage as function of average input power 100                                                |

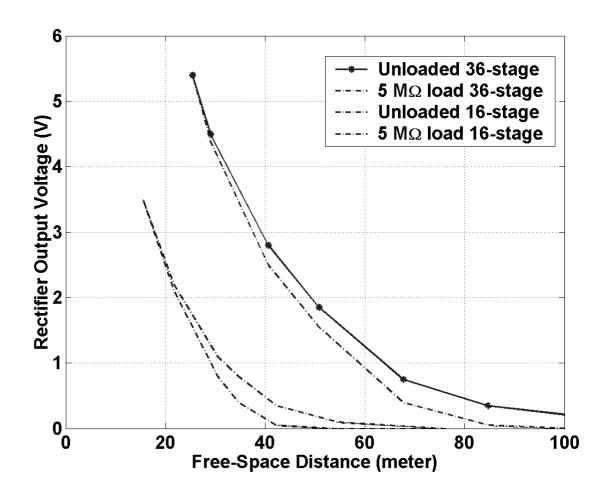

| 3.25 | Measured output DC voltage as function of distance 101                                                           |

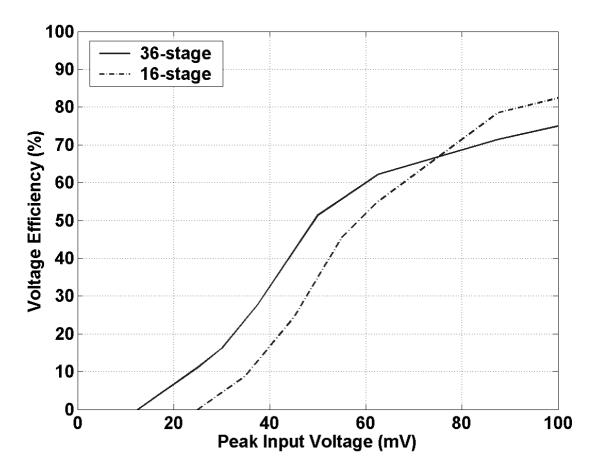

| 3.26 | Measured output DC voltage as function of measured voltage efficiency.<br>103 $$                                 |

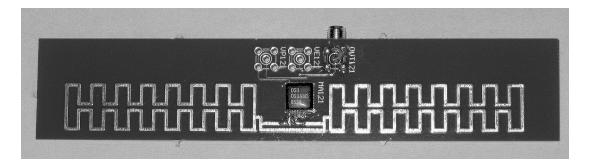

| 3.27 | PCB to test performance of the RF-DC power converter at the system level                                         |

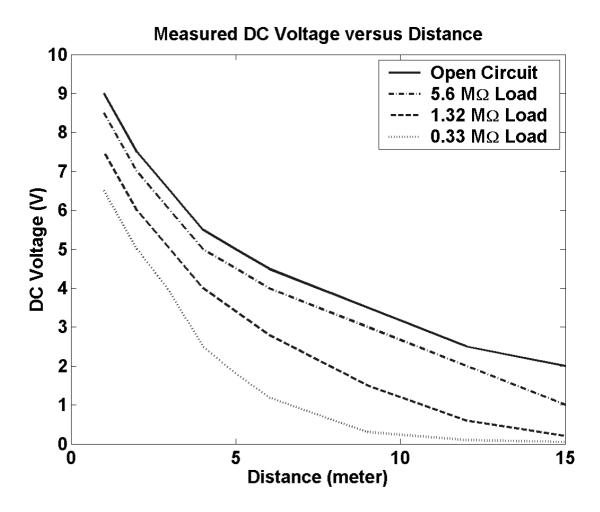

| 3.28 | Measured DC output voltage as function of distance and load for the 36-stage rectifier                           |

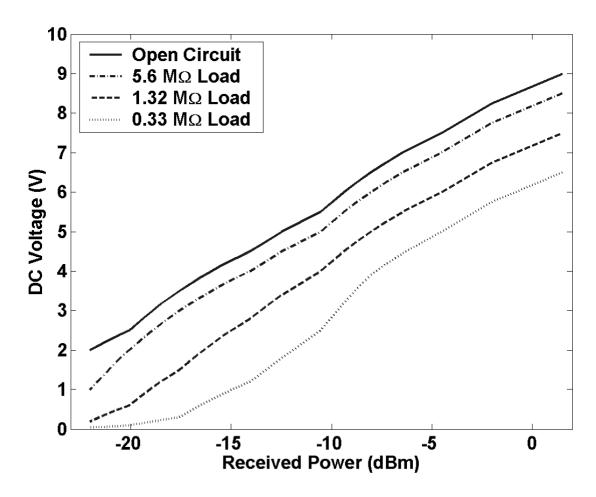

| 3.29 | Measured DC output voltage as function of received power and load<br>for the 36-stage rectifier                  |

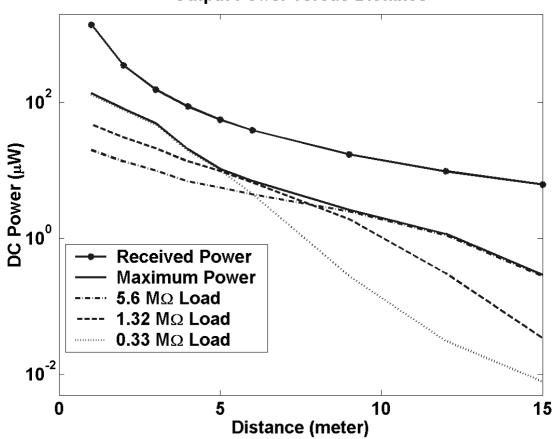

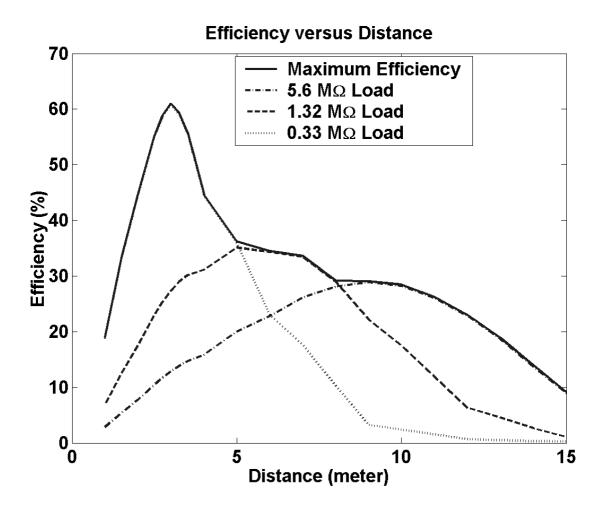

| 3.30 | Measured output power performance as function of distance and load<br>for the 36-stage rectifier                 |

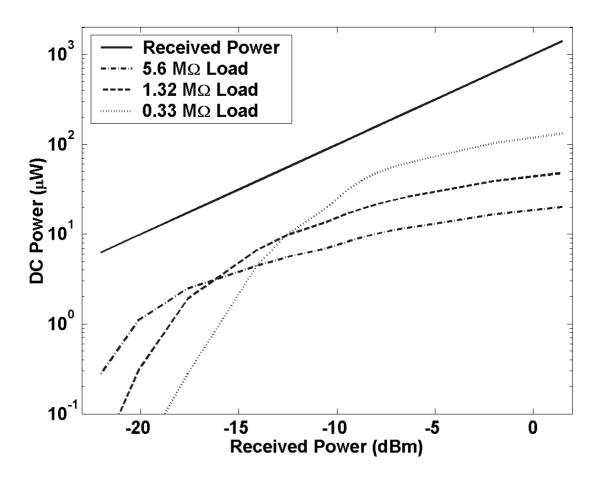

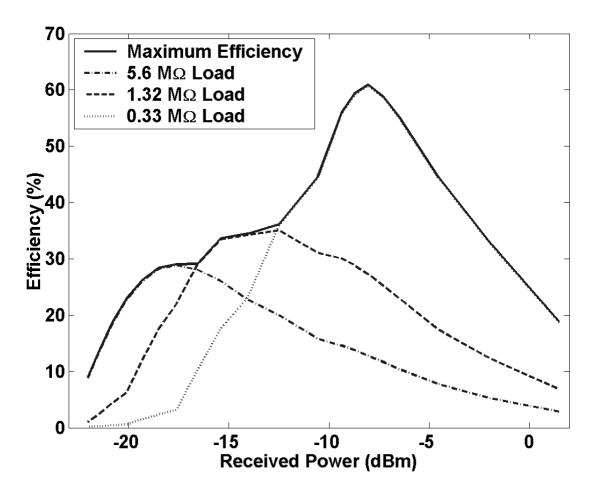

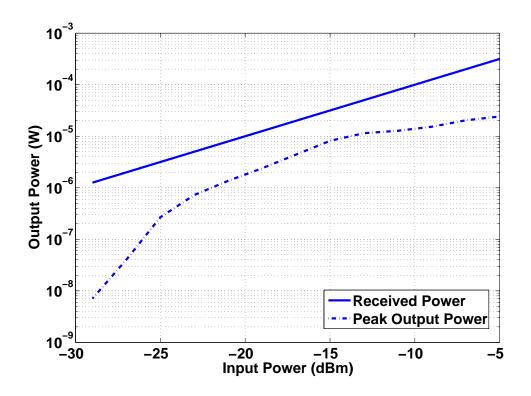

| 3.31 | Measured output power as function of received power for the 36-stage rectifier                                   |

| 3.32 | Measured power conversion efficiency curves as function of distance<br>and load for the 36-stage rectifier       |

| 3.33 | Measured power conversion efficiency curves as function of received<br>power for the 36-stage rectifier          |

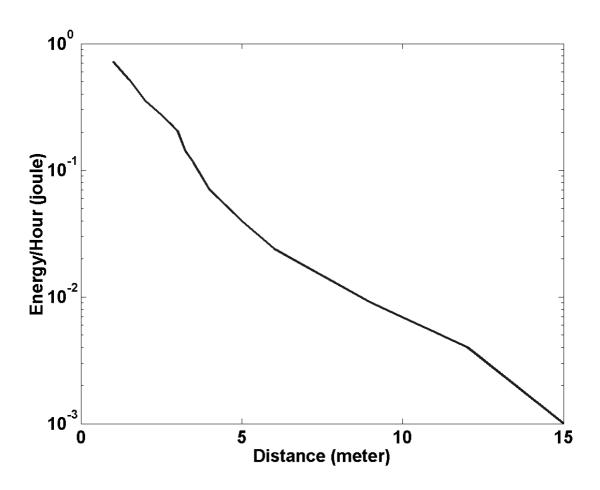

| 3.34 | Measured energy extracted per hour as function of distance for the 36-stage rectifier                            |

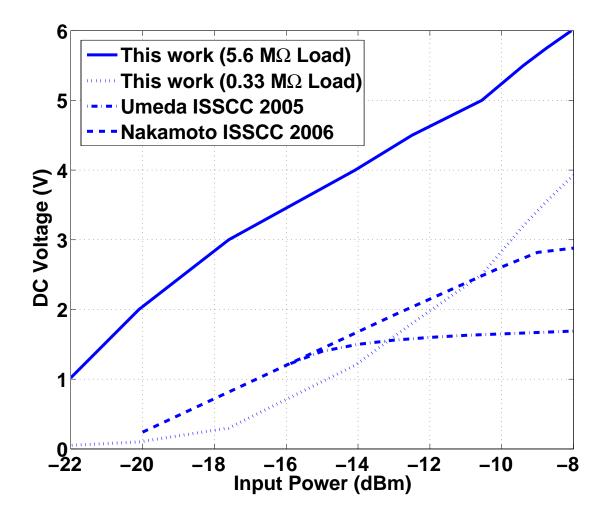

| 3.35 | Output DC voltage as function of the input power 116                                                             |

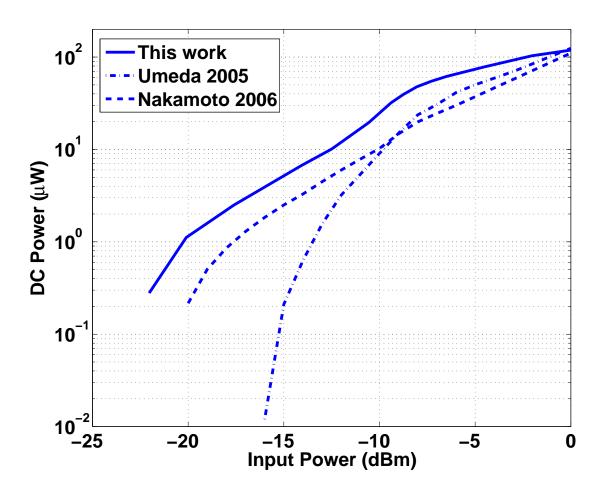

| 3.36 | Output DC power as function of the sinusoidal input 117                                                          |

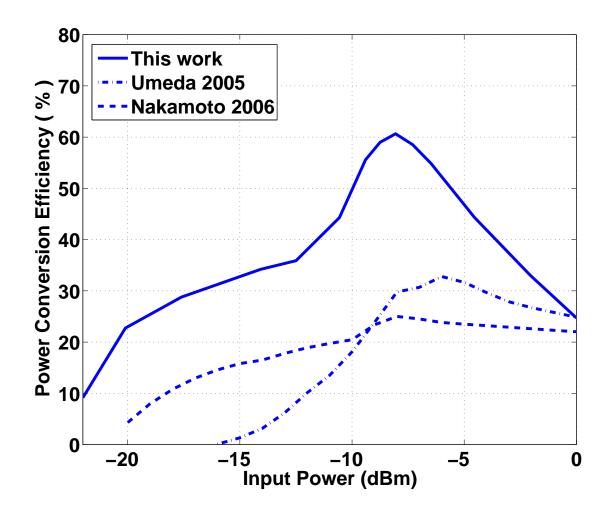

| 3.37 | Power conversion efficiency as function of the sinusoidal input 118                                              |

| 4.1  | Illustration of communication links between base station (hub) and sensors in a passively powered sensor network |

| 4.2  | Block diagram of RF energy harvesting system with floating-gate pro-<br>gramming                                 |

| Figure | <u>Page</u>                                                                                                                                                                  |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

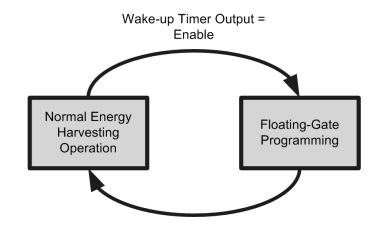

| 4.3    | Flow diagram of the energy harvesting system with floating-gate pro-<br>gramming                                                                                             |

| 4.4    | Conventional voltage doubler rectifier                                                                                                                                       |

| 4.5    | PMOS floating-gate voltage doubler rectifier                                                                                                                                 |

| 4.6    | PMOS implementation of a floating gate transistor                                                                                                                            |

| 4.7    | Transistor level schematic of PMOS floating-gate rectifier 130                                                                                                               |

| 4.8    | Voltage doubler rectifier with N-stages in cascade                                                                                                                           |

| 4.9    | Block diagram of the floating-gate programming circuit                                                                                                                       |

| 4.10   | Structure for programming and deprogramming of floating-gate devices. 133                                                                                                    |

| 4.11   | Cross sectional view of an NMOS floating-gate device with program-<br>ming and deprogramming nodes                                                                           |

| 4.12   | Procedure for floating-gate programming                                                                                                                                      |

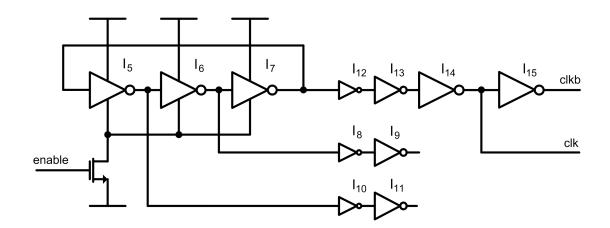

| 4.13   | Low frequency ring oscillator                                                                                                                                                |

| 4.14   | High frequency ring oscillator 140                                                                                                                                           |

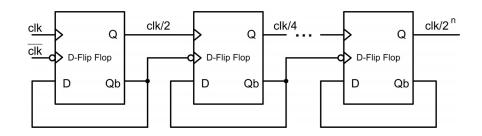

| 4.15   | Frequency divider circuit                                                                                                                                                    |

| 4.16   | Dickson charge pump voltage booster circuit for positive voltage gen-<br>eration                                                                                             |

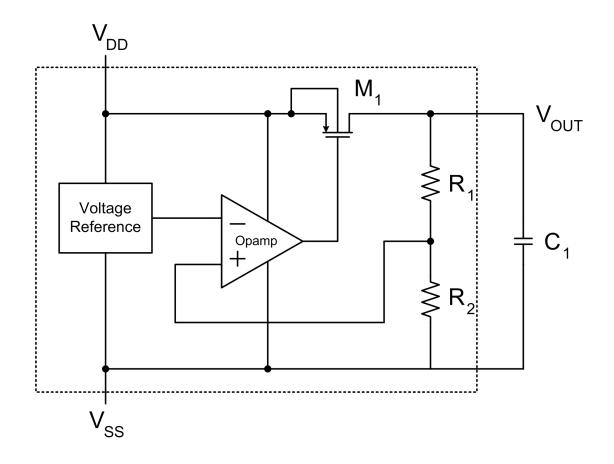

| 4.17   | Linear voltage regulator                                                                                                                                                     |

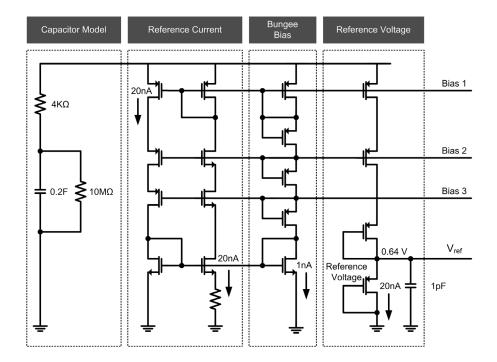

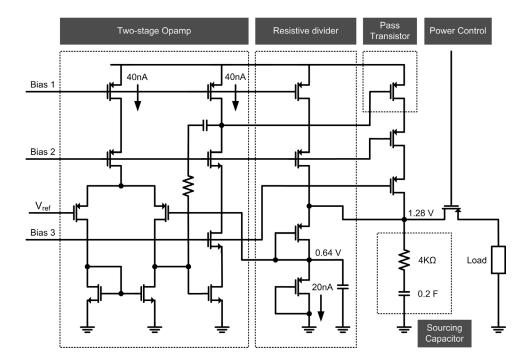

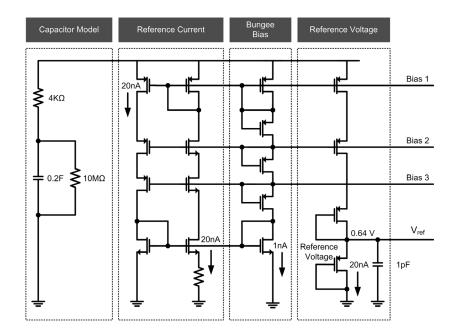

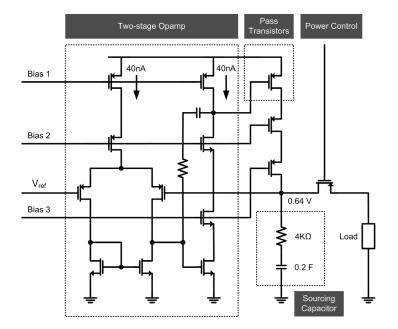

| 4.18   | Transistor level schematic of 1.25 V voltage regulator with adaptive<br>"bungee" biasing circuitry and electric double layer capacitor model<br>for input and output loading |

| 4.19   | Transistor level schematic of 0.625V voltage regulator with adaptive<br>"bungee" biasing circuitry and electric double layer capacitor model<br>for input and output loading |

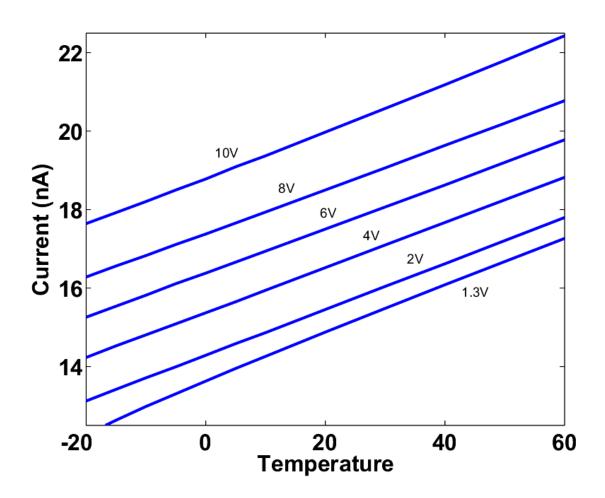

| 4.20   | Linearity of PTAT current reference with bungee bias 150                                                                                                                     |

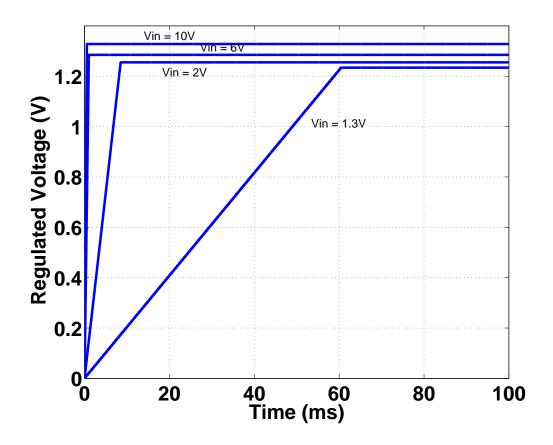

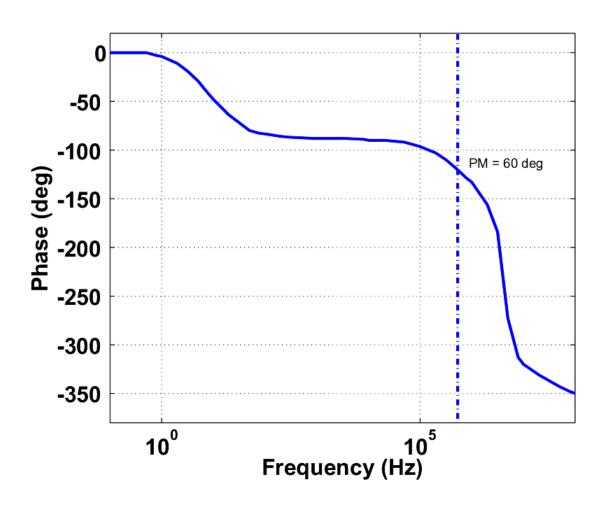

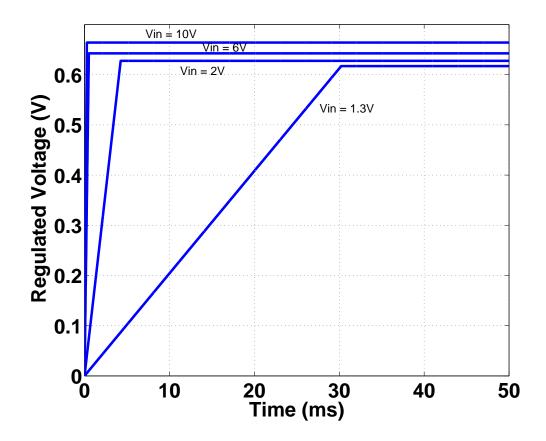

| 4.21   | Transient response of the 1.25 V voltage regulator                                                                                                                           |

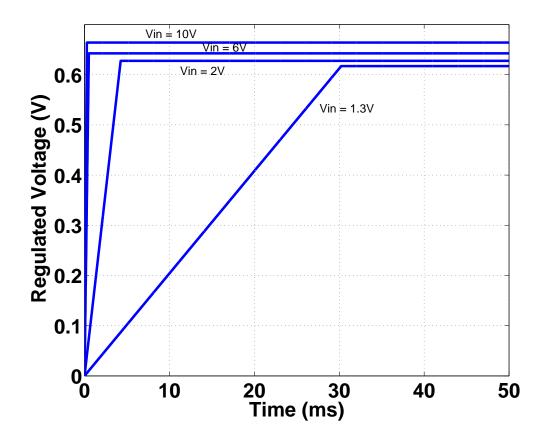

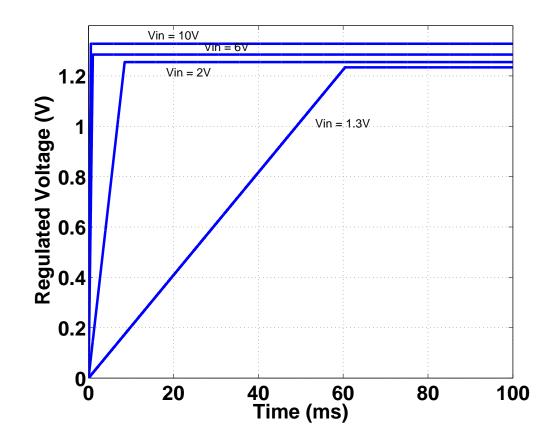

| 4.22   | Transient response of the 0.625 V voltage regulator                                                                                                                          |

| 4.23   | Die photograph of the RF power conversion interface circuits 156                                                                                                             |

## Page

# Figure

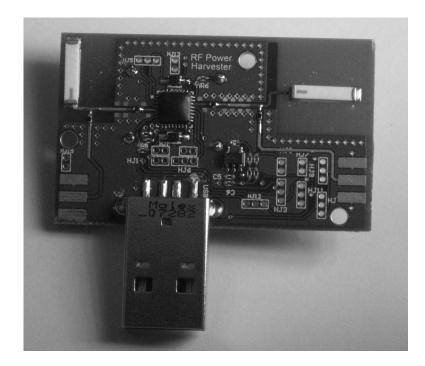

| 4.24 | Photograph of the front-view test printed circuit board (PCB) 157                                          |

|------|------------------------------------------------------------------------------------------------------------|

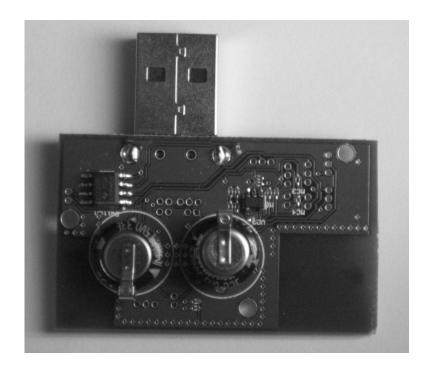

| 4.25 | Photograph of the front-view test printed circuit board (PCB) 158                                          |

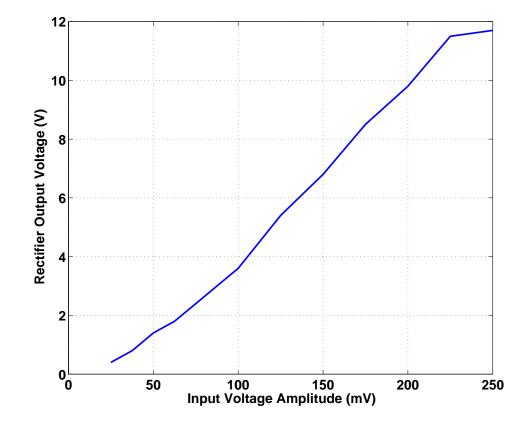

| 4.26 | Measured output voltage performance of the unloaded floating-gate rectifier as a function of input voltage |

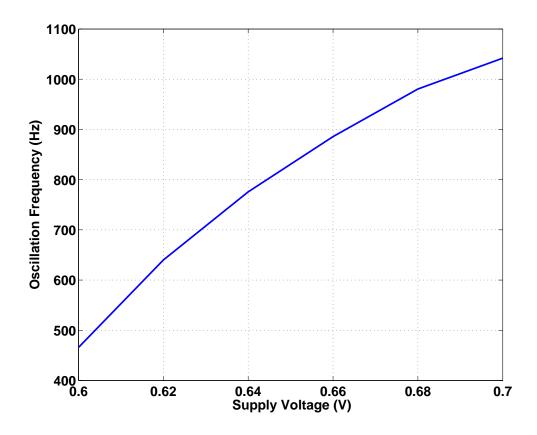

| 4.27 | Measured oscillation frequency as a function of regulated supply voltage.161                               |

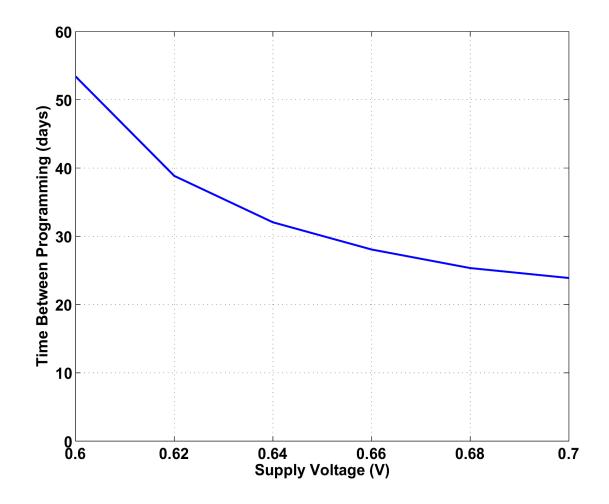

| 4.28 | Time between floating-gate programming intervals                                                           |

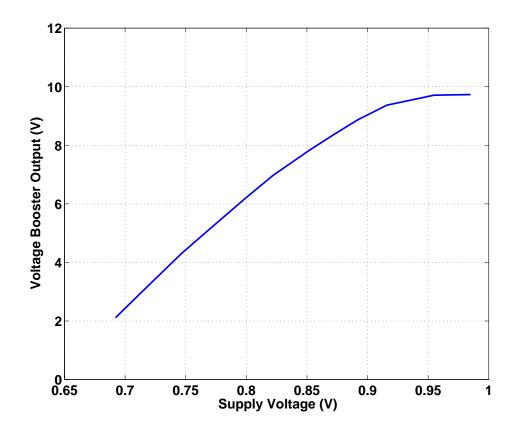

| 4.29 | Measured boosted output voltage as a function of supply voltage 163                                        |

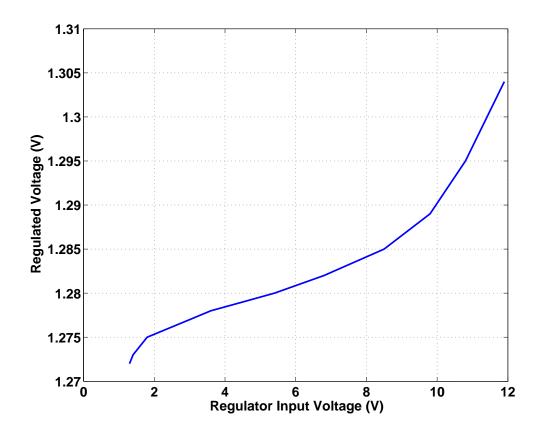

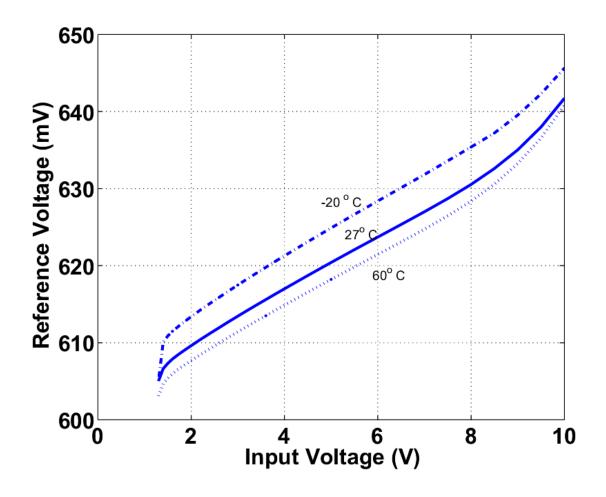

| 4.30 | Measured regulated voltage as a function of the power supply voltage<br>for the 1.25 V voltage regulator   |

| 4.31 | Measured regulated voltage as a function of the power supply voltage<br>for the 0.625 V voltage regulator  |

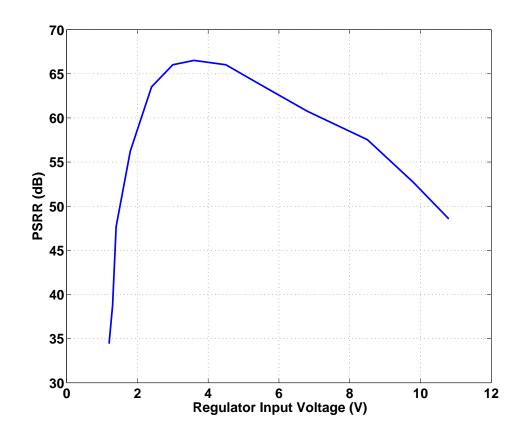

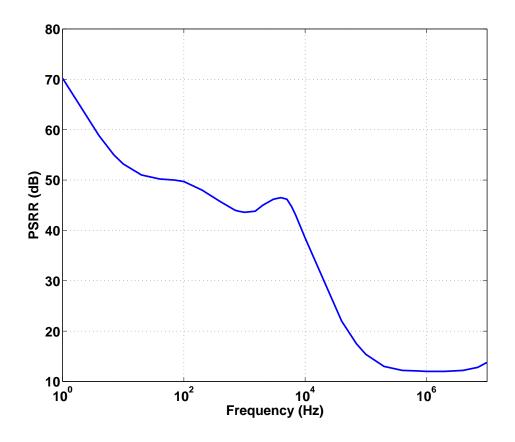

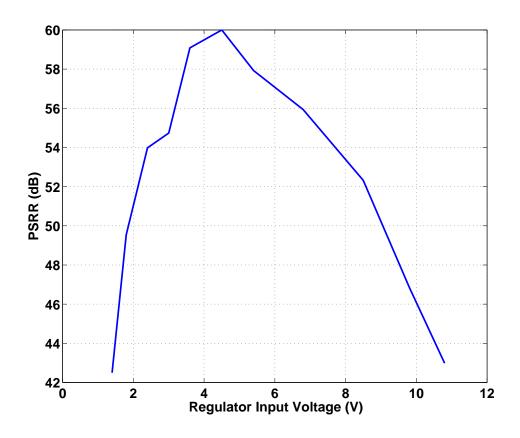

| 4.32 | Measured (DC) power supply rejection ratio (PSRR) of the 0.625 V regulator                                 |

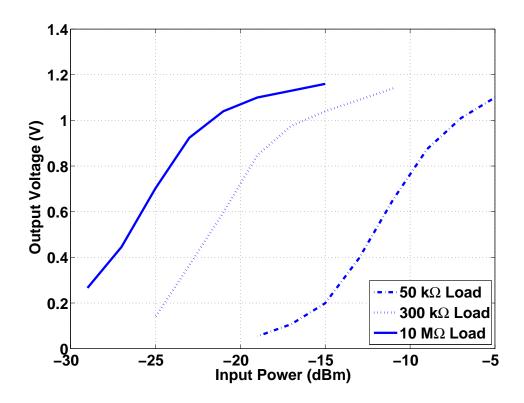

| 4.33 | Measured output voltage performance of RF power harvester 168                                              |

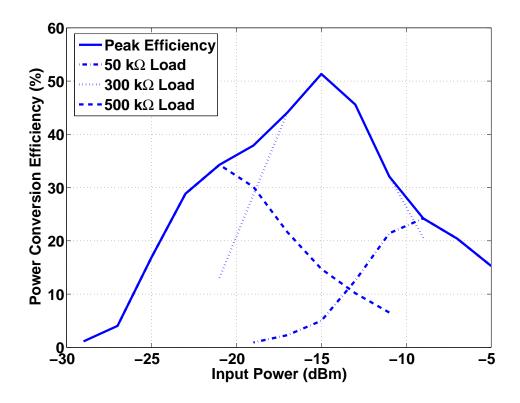

| 4.34 | Measured power conversion efficiency of RF power harvester 169                                             |

| 4.35 | Measured output power performance of RF power harvester 170                                                |

## LIST OF TABLES

<u>Table</u>

| 1.1 | Comparison of energy harvesting methods [5] 21                                                                                             |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------|

| 2.1 | Measured and simulated results for the half-wave synchronous rectifier<br>and voltage doubler connected to the output of the PZT device 44 |

| 3.1 | Transient response time of floating-gate rectifiers                                                                                        |

| 3.2 | Performance summary                                                                                                                        |

| 4.1 | Link budget of energy harvesting system with floating-gate rectifier 126                                                                   |

## Page

## LIST OF APPENDIX FIGURES

# Figure

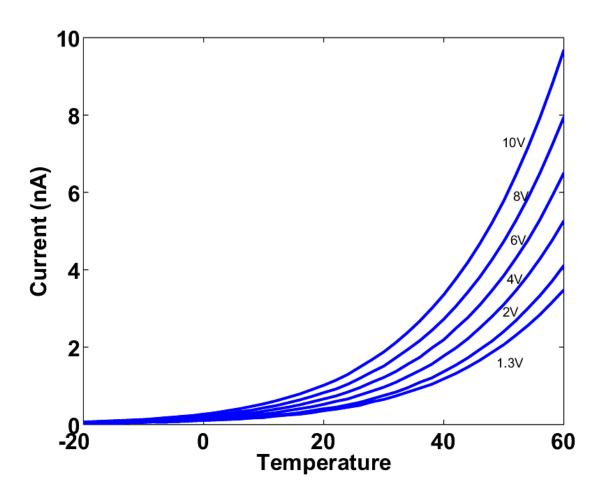

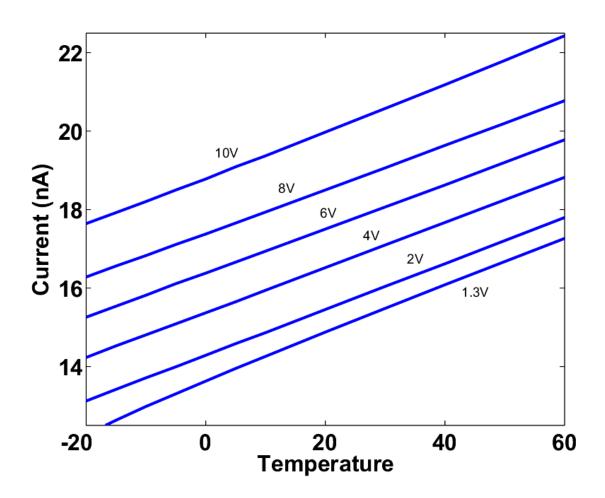

| A-1  | Current through adaptive bungee biasing circuit at various supply voltages and temperature             |

|------|--------------------------------------------------------------------------------------------------------|

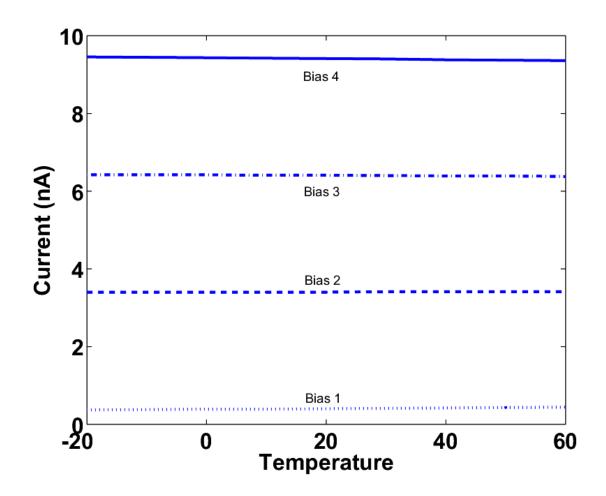

| A-2  | Bungee bias voltages without $V_{TH}$ mismatch effect                                                  |

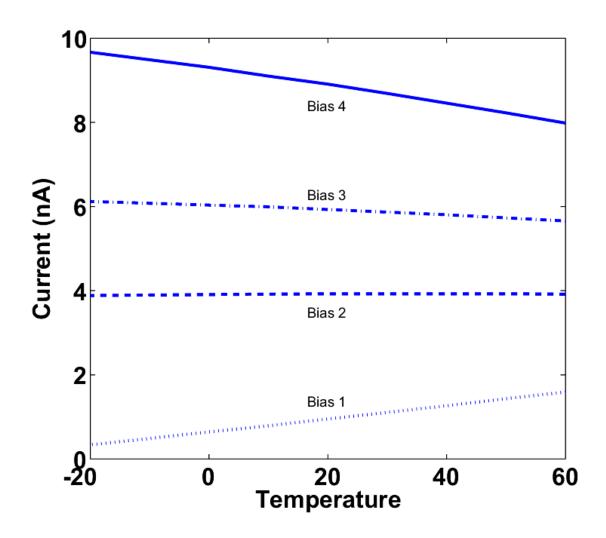

| A-3  | Bungee bias voltages with $V_{TH}$ mismatch of 10mV                                                    |

| A-4  | Linearity of PTAT current reference with bungee bias                                                   |

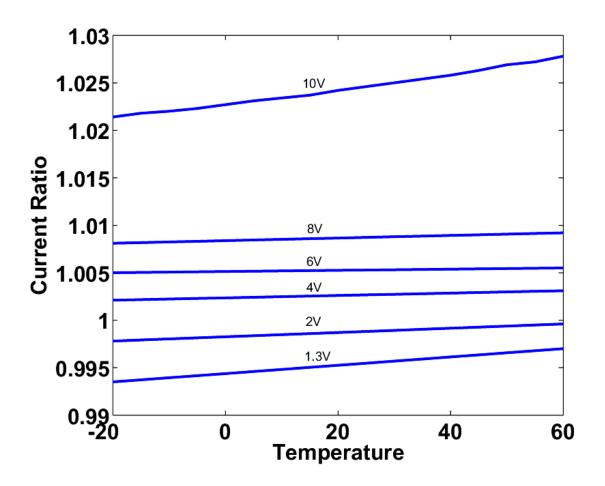

| A-5  | Current ratio of the current mirror                                                                    |

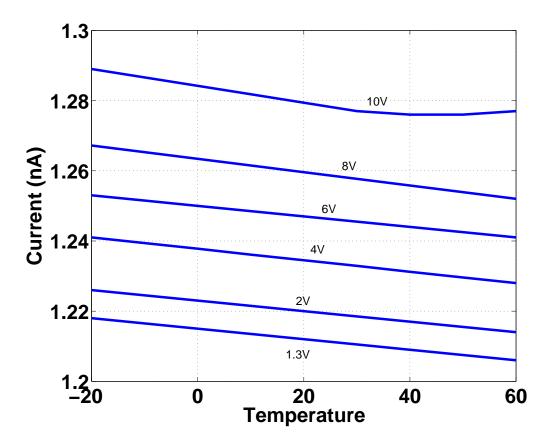

| A-6  | Reference voltage as function of temperature                                                           |

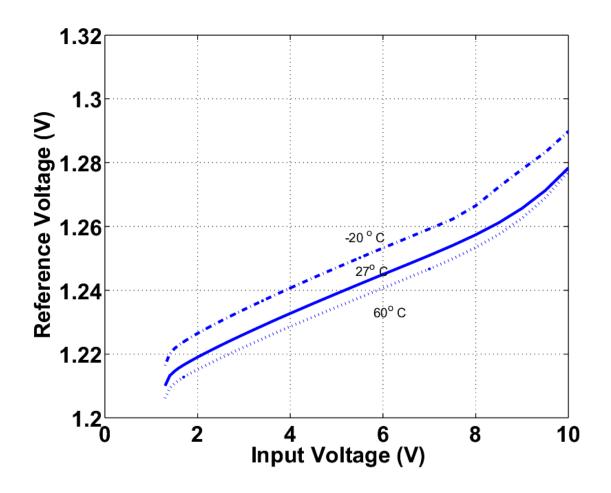

| A-7  | Reference voltage as a function of the power supply voltage 195                                        |

| A-8  | Power supply rejection ratio (PSRR) of the voltage reference circuit<br>as a function of frequency     |

| A-9  | Power supply rejection ratio (PSRR) of the voltage reference circuit<br>as a function of input voltage |

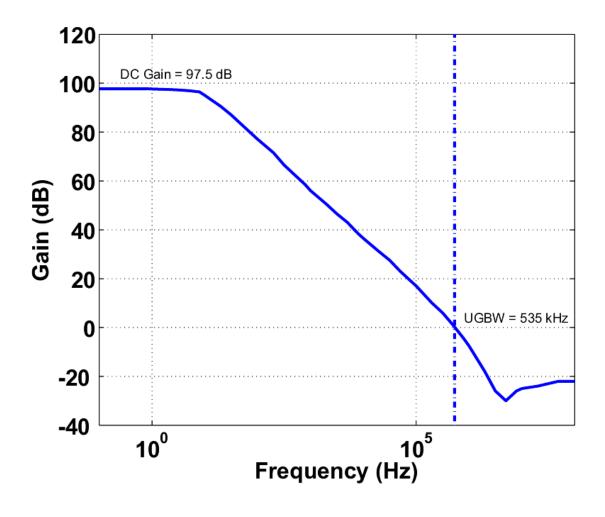

| A-10 | Plot of opamp gain operating at 1.2 V                                                                  |

| A-11 | Plot of opamp phase operating at 1.2 V 198                                                             |

| A-12 | Plot of opamp gain operating at 10 V 199                                                               |

| A-13 | Plot of opamp phase operating at 10 V 200                                                              |

| A-14 | Transient response of voltage regulator                                                                |

| A-15 | Transient response of the low voltage regulator                                                        |

## 1. INTRODUCTION

### 1.1. Motivation

In recent years, there has been an increasing need for power conversion circuits for power and energy harvesting applications. Energy harvesting methods such as RF powered systems [1, 2], solar powered systems [3, 4], wind powered systems, motional energy harvesting systems [5, 6], thermoelectric powered systems [7, 8], and piezoelectric conversion systems [9, 32] can be used to harvest energy from a controlled or ambient environment, to power devices directly or store the energy in capacitors or batteries for later use. These harvesting methods support a wide range of applications and can also be used to increase the lifetime of pre-existing devices. The advantages of energy harvesting applications are that they reduce or eliminate the dependency of devices on batteries and power sources while prolonging their lifetimes or the time between charging of wireless devices. Energy harvesting approaches are mostly used in micro-power applications such as sensor nodes in a distributed sensor network, biomedical implants and radio frequency identification (RFID) [11]. These systems are often very small in size and require little power to operate.

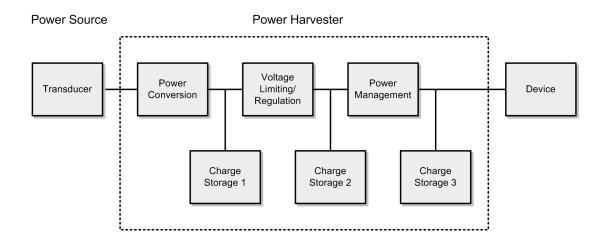

This dissertation covers energy harvesting power interface circuits, used to directly power devices and also charge storage devices such as batteries and capacitors. A general block diagram of a power harvesting system is shown in Figure 1.1.

For a general energy harvesting system, there must be a transducer that harvests energy and converts it into electrical power [12]. The transducer can be

FIGURE 1.1. General block diagram of an energy harvesting system.

an antenna, a piezoelectric device, a solar cell, a fuel cell, a wind turbine, and many other forms. The electrical power available at the output of the transducer can be in the form of direct (DC) or alternating current (AC) and can vary depending on the mode of energy harvesting. A power conversion interface circuit is required to convert the energy to a usable form for storage or it may pass to a voltage regulation circuit.

The power conversion circuit may be in the form of a rectfier or a DC-DC voltage converter. For certain power conversion interface circuits, impedance matching or maximum power tracking is required to ensure maximum power transfer between the power source and power harvester. Charge Storage 1 is the charge storage device to hold the charge harvested through the power conversion interface circuit. The charge storage device in this case can be a capacitor, a battery or any other charge storage element. Depending on the application and voltage available at the power conversion circuit, a buck or boost converter is used to regulate the voltage from the output of the power conversion circuit to a stable DC voltage. In some cases, voltage limiting is done instead of a voltage regulator. Charge Storage 2 stores the charge that is delivered by the output of the voltage regulator or voltage limiter. The power management circuit controls the conduction path between the device and energy harvester. Charge storage 3 is used to stabilize the voltage at the device during operation.

## 1.2. Comparison of Energy Harvesting Methods

The following section presents a summary of different energy harvesting methods comparing the range of harvestable energy under various environmental conditions. Radio frequency, piezoelectric, solar, thermoelectric, vibrational, electrostatic and acoustic energy harvesting methods are studied and compared.

#### 1.2.1. Radio Frequency Energy Harvesting

Other than direct wiring, the most common method of distributing power to embedded electronics is through the use of radio frequency (RF) radiation [1, 5]. RF power harvesting is most often used in RFID or passive RF tags to replace the bar code as a new form of data collection. Passive RFID tags are typically used in a very short range of less than 3 meters. RF powered devices are also used in applications such as structure monitoring where the RF powered devices are embedded into a structure making battery replacement impossible without destroying the structure. Some applications employing RF powered devices require deployment of these devices in very large numbers thus, making individual node battery replacement impractical [13–15]. In RF energy harvesting, the RF harvester can harvest energy from propagating RF waves which can be ambient RF waves generated by nearby electronic components such as cellular phones, or generated from a dedicated RF power source.

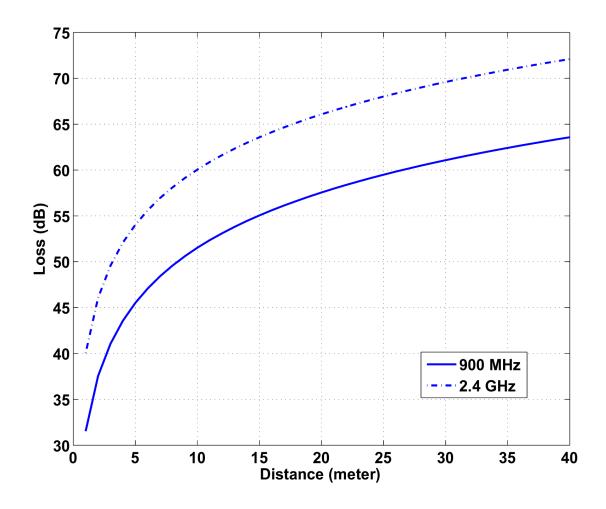

For RF power harvesting, the power that can be transmitted by an RF power source is limited by FCC regulations [16]. The power that can be harvested at the harvester is a strong function of the distance of the harvester from the power source. In free space, the path loss of the RF signal is given by Friis' equation [17] as

$$L_P = \left(\frac{4\pi R}{\lambda}\right)^2 \tag{1.1}$$

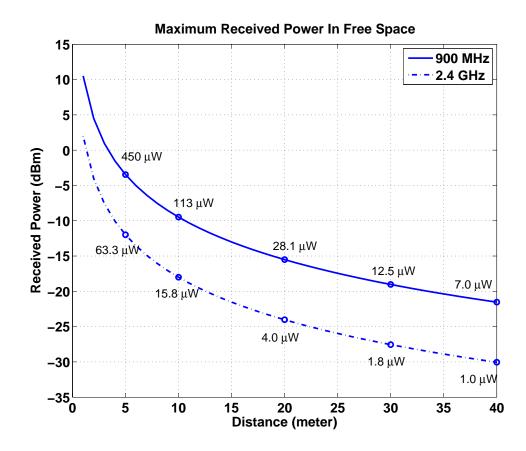

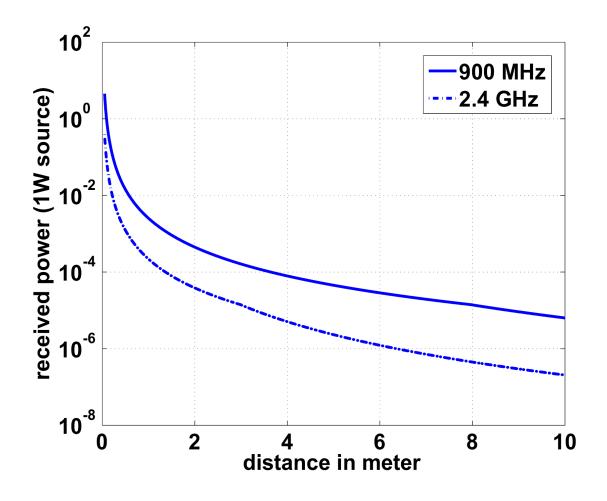

where R is the distance between the power source and power harvester, and  $\lambda$  is the wavelength of the RF signal transmitted from the power source. Figure 1.2 shows the freespace pathloss of RF signal transmission in ultra-high frequencies (UHF). The pathloss for RF signal transmission exceeds 50 dB at a frequency of 900 MHz and 60 dB for 2.4 GHz at a distance of 10 meters. Figure 1.3 shows the maximum power that can be received according to FCC regulations as a function of distance from a single RF power source [16]. For a freespace distance of 40 meters, the maximum theoretical power available power for conversion is 7.0  $\mu$ W and 1.0  $\mu$ W for frequencies of 900 MHz and 2.4 GHz, respectively.

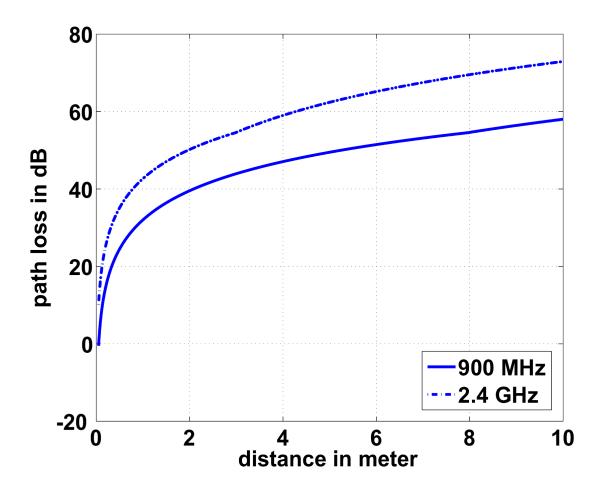

In different environments, the pathloss of the radiated signal behaves differently than it would behave in freespace. With multipath fading and destructive signal collisions, the propagational signal loss from the power source to the harvester increases. Using a simplified pathloss model for a typical office building or a 1-story warehouse [18, 19], the pathloss and received power at the energy har-

FIGURE 1.2. Path loss of RF signal transmission at UHF.

FIGURE 1.3. Maximum allowable receive power versus distance according to FCC regulations for RF energy harvesters from a single RF power source.

vester can be calculated. Figure 1.4 shows the path loss of an RF signal at UHF with the path loss model derived from [19]. The path loss for a 900 MHz signal reaches approximately 60 dB for a distance of 10 meters while exceeding 70 dB for a 2.4 GHz signal at the same distance. Figure 1.5 shows the maximum received power allowed by FCC regulations [16] from a single RF power source at UHF with the pathloss model of an office environment [18, 19]. The received power of 10  $\mu$ W is achievable at 8 meters in an office environment for a transmitted signal at 900 MHz and 3 meters for a transmitted signal at 2.4 GHz. With this high propagational loss, RF power harvesting is best designed for a short range system or a system with highly efficient power conversion and storage.

#### **1.2.2.** Piezoelectric Energy Harvesting

One of the most widely used power harvesting techniques for micro-power operation uses piezoelectric materials to convert mechanical energy from any type of vibration and heat to electrical energy. Also, when an electrical voltage is applied across the piezoelectric materials, the inverse happens and electrical power is converted into mechanical vibration. Due to these bi-directional effects, piezoelectric materials are widely used for making sensors and actuators. Piezoelectric materials are also used to generate electrical power to operate electrical devices from the striking of heels of shoes by walking or running [20, 21].

The piezoelectric effect is one of several ways to convert vibrational energy to electrical power [5]. Piezoelectric power harvesting capitalizes on certain crystal or ceramic materials to generate an electrical potential in response to an applied mechanical stress [22]. One of the most commonly used piezoelectric materials is Lead Zirconate Titanate, more commonly known as PZT. To excite the piezo-

FIGURE 1.4. Path loss of RF signal transmission in UHF with pathloss model derived from [18, 19].

FIGURE 1.5. Maximum allowed receive power versus distance according to FCC regulations for RF power harvesters from a single RF power source, with pathloss model derived from [18, 19].

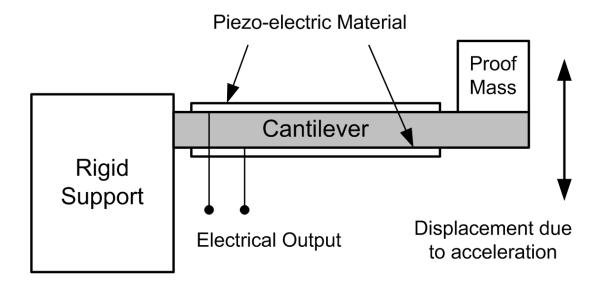

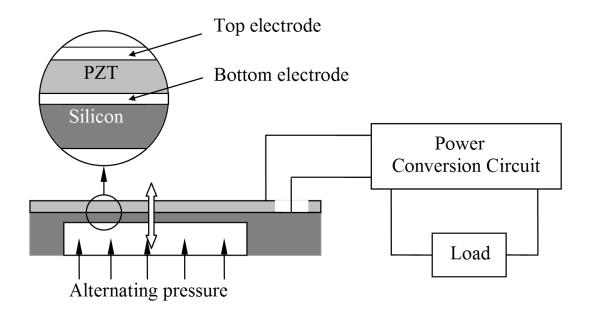

electric membrane, an alternating pressure can be applied or a proof mass can be placed on the end of the cantilever to enhance vibration on the piezeelectric material. Figure 1.6 shows the mechanical setup of a piezoelectric generator with a cantilever and proof mass. The power generated from this system is proportional to the proof mass, to the square of acceleration, and inversely proportional to the resonant and excitation frequency [23].

FIGURE 1.6. Diagram of piezoelectric power generator [24].

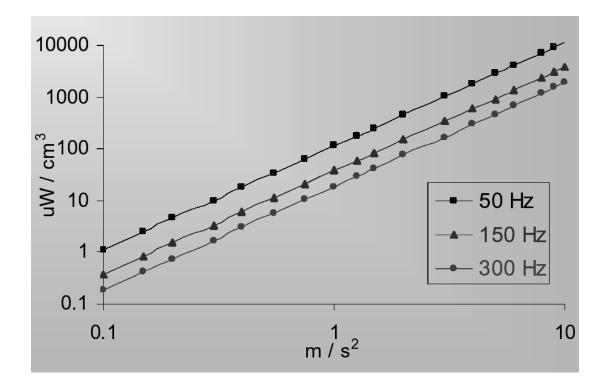

Figure 1.7 shows the power density from vibrational energy at different frequencies and amplitudes of input vibration. A power density of 10 mW/cm<sup>3</sup> is possible at an acceleration of 10 m/s<sup>2</sup> and an excitation frequency of 50 Hz. At a lower excitation frequency and higher acceleration, the power density can be improved significantly. However, in an ambient environment both the amplitude and frequency of vibration is very low, hence typical power that can be extracted from the ambient environment is about 40  $\mu$ W.

FIGURE 1.7. Power density of piezoelectric power generator at different frequency and amplitude of input vibration [24].

#### 1.2.3. Solar Energy Harvesting

Solar energy harvesting is another method to extract power from the environment to power devices. Solar energy is available when there is direct light. Solar powered devices are used in applications where battery replacement is impractical. Solar power harvesters convert sun light to electrical power via the photovoltaic effect or by heating of fluid to create steam that can be converted to electrical power. Defined as full sun light, the solar power density at the equator at noon on the equinox is 1000 W/m<sup>2</sup> or equivalently 100 mW/cm<sup>2</sup> [25]. In the United States, the average solar power density throughout the year is approximately 25 mW/cm<sup>2</sup>. Typical single junction solar cells have an efficiency of 14-19% in production [26] and 30-34% in research. Multi-junction solar cells have achieved an efficiency of over 42% but are relatively more expensive to mass produce [27].

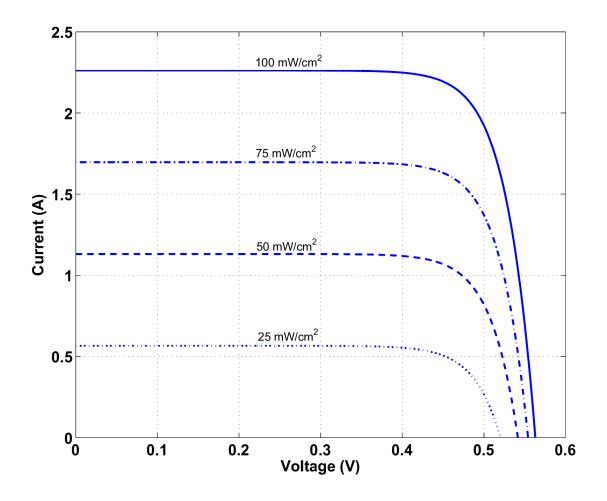

Experimental results shows that the I-V characteristics as well as the maximum power point of solar cells are a function of light intensity and temperature. Figure 1.8 shows the simulated I-V characteristics of a typical 1-W solar cell for different lighting conditions and standard test temperature (25°C). The dimension of the solar cell is about 3 x 3 inches, which translates to a solar cell efficiency of about 17%. From the I-V curves, the short circuit current of the solar cell varies directly with light intensity while the open circuit voltage does not vary greatly with light intensity. In Figure 1.9, the output power curves for the same 1-W solar cell with the maximum power points are shown. From the plot, the maximum power point current varies significantly with light intensity while the maximum power point voltage varies only slightly.

FIGURE 1.8. I-V characteristics of a typical 1-W solar cell for different lighting conditions (at 25°C).

FIGURE 1.9. Output power of a typical 1-W solar cell for different lighting conditions (at  $25^{\circ}$ C).

Figure 1.10 shows the I-V characteristics of a typical 1-W solar cell at different temperatures for standard lighting conditions  $(100 \text{ mW/cm}^2)$ . From the I-V curves, the short circuit current of the solar cell varies only slightly while the open circuit voltage varies greatly. Figure 1.11 shows the output power curves for the same 1-W solar cell with the maximum power point marked. From the plot, both the maximum power point current and voltage vary directly with temperature. From these plots, it can be observed that the short circuit current and maximum power point current of the solar cell is strongly affected by light intensity, while the open circuit voltage and maximum power point voltage is more dependent o the temperature. With these variations in voltage and current from temperature and lighting conditions, the solar power conversion system requires a maximum power tracking circuit to ensure maximum power transfer between the solar cell and the load.

#### 1.2.4. Thermo Electric Energy Harvesting

Energy can be extracted from the thermal temperature difference between two junctions to generate a small amount of electricity [28]. The thermoelectric effect uses the thermal gradient between two dissimilar metal conductors to produce an electrical voltage from diffusion current caused by the heat flow across the dissimilar conductors. The thermoelectric effect is reversable so when an electrical voltage is applied at the conductors, a temperature gradient is created across it. The term thermoelectric effect comprises of the Seebeck effect, the Peltier effect and the Thompson effect of thermoelectricity. Products that utilize thermoelectric energy harvesting includes twist watches that run from the temperature gradient generated between the human body and the ambient environment.

FIGURE 1.10. I-V characteristics of a typical 1-W solar cell at different temperatures (at 100  $\rm mW/cm^2).$

FIGURE 1.11. Output power of a typical 1-W solar cell at different temperatures (at 100  $\rm mW/cm^2).$

Micro-thermoelectric generator have demonstrated the capability of generating a power density of 15  $\mu$ W/cm<sup>3</sup> from a thermal gradient of 10 °C [28]. In recent years, the thin-film thermoelectric technology has improved to enhance the power density of thermoelectric generators. By employing nanoscale thermoelectric materials using superlattices and self-assembled quantum dots, the power density of thermoelectric generators can be increased to over 100  $\mu$ W/cm<sup>3</sup> with an thermal gradient of 1°C [29] once this technology is fully developed. These thermoelectric generators are designed to generate power in the 100 mW range from the heat produced by microprocessors or other integrated circuits that dissipate from 10-20 W of power.

## 1.2.5. Vibrational Energy Harvesting

Other than the piezoelectric effect, other methods to extract power from vibration includes the electrostatic effect (capacitive) or electromagnetic effect (inductive) of vibrational energy conversion. Vibrational energy conversion can be powered from sources such as the human body or powered from machinery. For capacitive vibrational energy harvesting, the capacitance of a varactor are is by the vibration to convert mechanical energy into electrical energy. In inductive vibrational energy harvesting, a coil vibrates through a magnetic field to yield an electrical current.

Typical motional power that can be extracted from human caused vibration is in the microwatt range for very cubic centimeter (cc) while typical harvestable power excited by machinery can be in the hundreds of microwatts for every cubic centimeter. Vibrational energy harvesting is used for applications such as wrist watches and heel strikes for shoes in military applications.

## 1.2.6. Electrostatic Energy Harvesting

In the case for electrostatic energy harvesting, an electrostatic generator or machine is required to produce the static electric effect. Similar to static electricity, the electrostatic generator produces a high voltage and low current by means of inducing friction.

In electrostatic generators, electrical charge can be accumulated by using electrostatic induction or friction. An electrostatic generator can consist of two conductors that generate charge of opposite sign or of moving gears that generate a steady stream of static electricity. Electrostatic machines are often seen in science classrooms to safely demonstrate the effect of electrostatic electricity. The voltage generated from static electricity can reach up to 1,000,000 volts with modern electrostatic generators, however, its current is very low. Another disadvantage of electrostatic power generators is the size of the generator as they are generally much larger than any types of transducer for other modes of energy harvesting.

#### 1.2.7. Acoustic Energy Harvesting

Energy can also be extracted from sound waves as is the case for acoustic energy harvesting. In acoustic energy harvesting, an acoustic transducer or resonator is used to convert acoustic energy to electrical energy. In general, acoustic power can only be harvested in very noisy environments. A study has been conducted using incident sounds as a source of excitation for piezoelectric materials to power an ultra-low power processing circuit and it was found that the system can only operate at very high noise, i.e., 114 dB [30]. In the ambient environment, energy from acoustic noise is very low, hence energy harvesting from sound wave is very inefficient. From theorectical results, acoustic energy harvesting can only yield 0.96  $\mu$ W/cm<sup>3</sup>, much lower than other methods of energy harvesting.

## 1.2.8. Summary of Energy Harvesting Methods

From the summary of different energy harvesting methods, it is clear that energy harvesting by radio frequency and piezoelectric effects are two of the most attractive approaches for low power applications. Table 1.1 shows the power density and energy density of different modes of energy harvesting. The power density for each energy harvesting method is shown for various environmental conditions. The energy density of these methods is also calculated assuming a 10 year lifetime for devices that employ these energy harvesting methods.

The power harvested from the sun has the highest power density in the most ideal situation but drops off as a linear function of light intensity. It can be observed that on a cloudy day or in an office environment, the energy from light is significantly lower compared to other means of energy extraction. Energy harvesting from vibrational, electrostatic and acoustic methods also lacks the power density compared to other methods.

## 1.3. Dissertation Outline

In this dissertation, efficient power conversion interface circuits for piezoelectric and RF power harvesting systems are presented. One of the challenges in designing a power generator is the design and construction of an efficient rectifier circuit to harvest the energy from the PZT membrane. In Chapter 2, a model for a particular piezoelectric membrane is shown and novel power conversion circuits to interface to a piezoelectric micro-power generator have been fabricated

|                  | Power Density          | Energy Density    |                          |  |

|------------------|------------------------|-------------------|--------------------------|--|

|                  | $(\mu {f W}/{f cm^3})$ | $(kJ/cm^3)$       | Source of                |  |

|                  |                        | 10 Year life      | Information              |  |

| RF (900 MHz)     | 450 @ 5m               | 142.0             |                          |  |

|                  | 113 @ 10m              | 71.0              |                          |  |

|                  | 28 @ 20m               | 35.5              |                          |  |

|                  | 7 @ 40m                | 17.7              | Le, et al., 2006 [14]    |  |

| RF (2.4 GHz)     | 63.3 @ 5m              | 20.0              |                          |  |

|                  | 15.8 @ 10m             | 10.0              |                          |  |

|                  | 4.0 @ 20m              | 5.0               |                          |  |

|                  | 1.0 @ 40m              | 2.5               | Le, et al., 2006 [14]    |  |

| Solar (Outdoors) | 15,000 - peak sun      | 4,730 - peak sun  | Commonly                 |  |

|                  | 150 - cloudy day       | 47.3 - cloudy day | Available                |  |

| Solar (Indoors)  | 6 - office desk        | 1.9 - office desk | Roundy 2003 [5]          |  |

| Vibrations       | 200                    | 63.1              | Roundy, et al., 2002 [5] |  |

| Acoutics         | 0.003 @ 75 dB          | 0.0009 @ 75 dB    |                          |  |

|                  | 0.96 @ 100  dB         | 0.30 @ 100  dB    | Theory                   |  |

| Thermo-electric  |                        |                   | Venkasubramanian,        |  |

|                  | 100                    | 31.5              | et al., 2007 [29]        |  |

| Shoe Inserts     |                        |                   | Stamer 1996 [20]         |  |

|                  | 330                    | 104               | Shenck 2001 [21]         |  |

TABLE 1.1. Comparison of energy harvesting methods [5].

and tested. Circuit designs and measurement results are presented for a half-wave synchronous rectifier with a voltage doubler, a full-wave synchronous rectifier and a passive full-wave rectifier circuit connected to the piezoelectric micro-power generator.

In Chapter 3, an RF-DC power conversion system for far-field RF energy extraction is presented. In a far field RF energy harvesting system, RF energy must be extracted from the air at very low power density since the propagation energy drops off rapidly as distance from the source is increased. One of the challenges of designing such a system is the very low available RF power to the receiver in the far-field, and the available voltage for rectification in the RF to DC conversion system falls below the threshold of standard CMOS transistors. Non-conventional rectifier circuits must be designed with threshold reduction techniques to improve the performance of the power conversion system.

The system is designed to efficiently convert far-field RF energy to DC voltages at very low received power and voltages. Passive rectifier circuits are designed in a  $0.25\mu$ m CMOS technology using floating gate transistors as rectifying diodes. Optimized for far field, the high operating voltage range for the rectifier achieved at low load currents make it ideal for use in passively powered sensor networks.

Chapter 4 presents novel voltage regulators and floating-gate programming circuits designed to enhance the power efficiency of RF energy harvesting systems. Operated in weak-inversion, the voltage regulator circuits are designed to operate at sub-microwatt power. The floating-gate programming circuit is designed to replenish charge to the floating-gate of the rectifier circuit for RF power conversion. The programming of the floating-gate is done periodically to prevent charge from leaking off from the floating-gate and also to optimize the performance of the floating gate rectifier over time. Measured results and characterization of the voltage regulators and floating-gate programming circuits are shown.

Chapter 5 concludes the dissertation and identifies key research problems for further investigation.

# 2. PIEZOELECTRIC MICRO-POWER GENERATION INTERFACE CIRCUITS

# 2.1. Abstract

New power conversion circuits to interface to a piezoelectric micro-power generator have been fabricated and tested. Circuit designs and measurement results are presented for a half-wave synchronous rectifier with voltage doubler, a full-wave synchronous rectifier and a passive full-wave rectifier circuit connected to the piezoelectric micro-power generator. The measured power efficiency of the synchronous rectifier and voltage doubler circuit fabricated in a 0.35- $\mu$ m CMOS process is 88% and the output power exceeds 2.5- $\mu$ W with a 100-k $\Omega$ , 100-nF load. The two full-wave rectifiers (passive and synchronous) were fabricated in a 0.25- $\mu$ m CMOS process. The measured peak power efficiency for the passive full-wave rectifier circuit is 66% with a 220-k $\Omega$  load and supplies a peak output power of 16- $\mu$ W with a 68-k $\Omega$  load. Although the active full-wave synchronous rectifier requires quiescent current for operation, it has a higher peak efficiency of 86% with a 82-k $\Omega$  load, and also exhibits a higher peak power of 22- $\mu$ W with a 68-k $\Omega$ load which is 37% higher than the passive full-wave rectifier.

# 2.2. Introduction

With the need for portable and lightweight electronic devices on the rise, highly efficient power generation approaches are a necessity. Novel approaches to obtaining power conversion are being explored including the piezoelectric micro power generator [31], high-voltage solar cell arrays [3] and thermal energy conversion [7]. One that is particularly promising uses a piezoelectric material to convert mechanical energy from heat or vibration into electrical energy. Conversely, applying an electric voltage to this material produces a mechanical strain. Because of these bi-directional effects, piezoelectric materials are widely used for making sensors and actuators.

The use of a thin piezoelectric film/plate for a micro power supply, as shown schematically in Fig. 2.1, is a new and exciting application [31]. In this application, the piezoelectric laminate is mechanically forced to vibrate and thus, it works as a generator to transform the mechanical energy into electrical energy. The piezoelectric material used for this power generation circuit is lead-zirconatetitanate (PZT). The PZT membrane is placed on a silicon substrate between two electrodes. The electrodes are used as conductors to carry the electrical charge from the PZT membrane to the power conversion circuit. The power conversion interface circuit takes the charge across the piezoelectric device and converts this electrical charge into a DC voltage, which can be used to drive a current load. Fig. 2.2 shows the picture of the fabricated PZT with dimension of 2.45 mm x 2.45 mm. The PZT membrane is fabricated on a separate silicon substrate from the power generation interface circuits.

One of the challenges in a power generator of this type is the design and construction of an efficient power conversion circuit to harvest the energy from the PZT membrane. Unlike conventional power supplies and batteries, which typically have very low internal impedance, the piezoelectric generators internal impedance is relatively high. This high internal impedance restricts the amount of output current that can be driven by the PZT source to the micro-amp range. Another unique characteristic of this power source is the relatively low output voltage of the piezoelectric device. This low output voltage makes it challenging

FIGURE 2.1. Schematic of power generation using a piezoelectric laminate.

to develop rectifier circuits that are efficient since many half wave or full wave diode rectifiers require nonzero turn-on voltages to operate.

The above issues are addressed in this paper by presenting several rectifier circuits that are suitable for power conversion with a piezoelectric source. In Section 2.3, typical measured PZT device characteristics are described along with a model that is used for simulation of the power conversion circuits. Section 2.4 presents half-wave rectifier circuits and compares passive and active circuit approaches. Section 2.5 describes the implementation of two full-wave rectifiers that enhance the performance over the half-wave rectifiers. The measured results and comparison of these two implementations are also presented. Section 2.6 concludes the paper.

FIGURE 2.2. Picture of the fabricated PZT.

#### 2.3. Piezoelectric Device Characteristics and Modeling

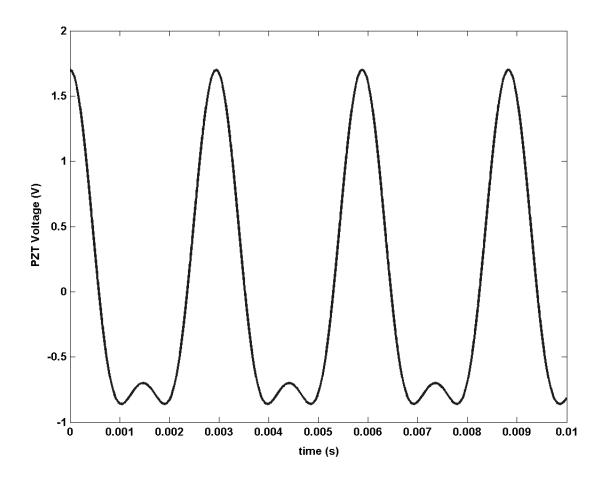

In order to design a power generation interface circuits, a circuit model of the piezoelectric membrane is needed to simulate the interface circuit. When pulses of pressure are applied to a piezoelectric membrane, the amount of charge across the piezoelectric device as well as the output swing varies in amplitude and depends on the membrane characteristics. A typical measurement of the open circuit output voltage is shown in Fig. 2.3 [32, 33]. In this case, the output voltage ranges from -0.85 V to 1.7 V. When experiencing the most change in pressure, the PZT membrane will undergo positive deflections, causing the voltage across the membrane to go to the maximum positive potential. When the change in pressure is zero, the PZT membrane will be at the most negative potential. The smaller increase in the waveform in the negative range is caused by the deflection of the membrane in this direction.

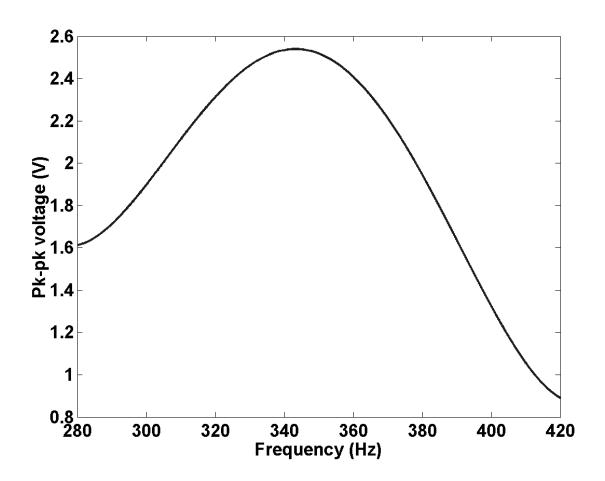

Measurements of the membrane as a function of frequency reveal that the resonant frequency of a 2.45 mm membrane is approximately 340 Hz as shown in Figure 2.4. The peak-to-peak voltage is greatest when the membrane is excited at the resonant frequency. The actual resonant frequency depends on the dimensions of the PZT material.

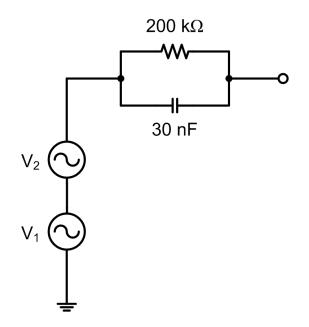

Through measurement results, an equivalent circuit model is developed for the 2.45 mm square PZT membrane as shown in Figure 2.5. Two sinusoidal voltage sources are used to model the voltages at resonance and the second harmonic frequency. The voltage source  $V_1$  represents the fundamental frequency and  $V_2$ represents the second harmonic frequency of the excitation. Although the electrical model for the piezoelectric device can be extended to a higher order (i.e. adding more sinusoidal voltage sources for higher order harmonics), a second or-

FIGURE 2.3. Measured open circuit output voltage of the 2.45 mm x 2.45 mm piezoelectric membrane.

FIGURE 2.4. Measured peak-to-peak output as a function of input frequency.

der model is used because it is simple and provides a good approximation for the output voltage.

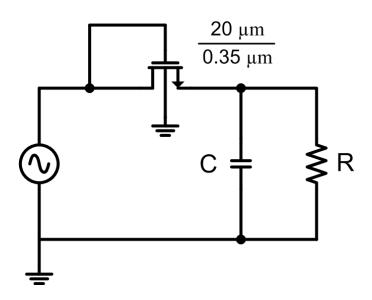

The internal impedance of this particular piezoelectric device is modeled as a 200-k $\Omega$  resistor connected in parallel with a 30-nF capacitor. At DC, the internal impedance is 200 k $\Omega$  and at the resonant frequency, the internal impedance is dominated by the reactive component from the internal capacitance. It is important to note that unlike most power sources, which have low output impedance, the piezoelectric power source is relatively high output impedance. This introduces unique challenges in designing efficient regulation and conversion circuitry.

By curve fitting the peak-to-peak voltage as a function of the input frequency, a fourth-order polynomial was found to most accurately model the changes in the output voltage at different excitation frequencies. Using the coefficients in Fig. 2.5, a particular frequency is chosen for the transient simulation using

$V(t, f) = V_1(f) * \cos(2\pi ft) + V_2(f) * \cos(4\pi ft).$

The response matches particularly well for excitation frequencies in the range of 280-430 Hz which are of highest interest in our application. By fixing the frequency of excitation on the PZT membrane and using this equivalent circuit model, it is possible to simulate and design power conversion circuits for subsequent fabrication.

# 2.4. Half-Wave Rectifier Interface Circuits

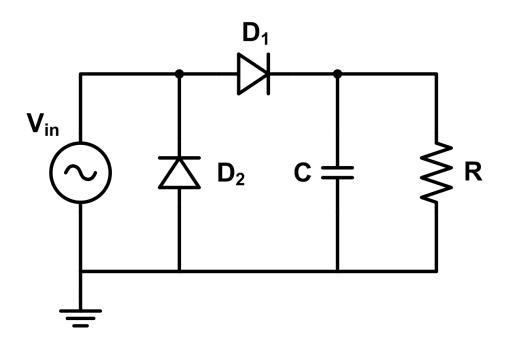

# 2.4.1. Passive Half-Wave Diode Rectifiers

To implement a half-wave diode rectifier in a conventional integrated circuit process, the diodes are constructed from diode-connected transistors. The diode-

$V_{1}(f) = a_{1}*f^{4} + a_{2}*f^{3} + a_{3}*f^{2} + a_{4}*f + a_{5}$  $V_{2}(f) = b_{1}*f^{4} + b_{2}*f^{3} + b_{3}*f^{2} + b_{4}*f + b_{5}$

| a <sub>1</sub> = 2.0409 x 10 <sup>-8</sup>   | $b_1 = 2.0188 \times 10^{-8}$              |

|----------------------------------------------|--------------------------------------------|

| a <sub>2</sub> = - 2.8432 x 10 <sup>-5</sup> | b₂ = - 2.8541 x 10 ⁻⁵                      |

| a <sub>3</sub> = 1.4629 x 10 <sup>-2</sup>   | b <sub>3</sub> = 1.4952 x 10 <sup>-2</sup> |

| a <sub>4</sub> = - 3.2949                    | b <sub>4</sub> = - 3.4392                  |

| a <sub>5</sub> = 2.7515 x 10 <sup>2</sup>    | b <sub>5</sub> = 2.9331 x 10 <sup>2</sup>  |

FIGURE 2.5. Equivalent circuit of the piezoelectric membrane which models the output voltage waveform as a function of excitation frequency (f) as well as the characteristic output impedance [9].

tied NMOS transistor circuit of Fig. 2.6 rectifies the voltage when the input voltage exceeds the threshold voltage of the transistor. With a typical NMOS transistor threshold voltage of 0.5 V, there is a significant reduction in the output voltage of the rectifier and the overall power efficiency. The body effect increases the threshold voltage of the NMOS transistor further, and thus the circuit is improved when a diode-tied PMOS transistor (with the body tied to the source) is connected in parallel with the NMOS transistor, Fig. 2.7.

FIGURE 2.6. Half-wave rectifier with diode-tied NMOS.

To compare these circuits, simulations were performed using the TSMC  $0.35\mu$ m CMOS process models. Figure 2.8 shows the simulated output power versus output current curve for the rectifier structures of Fig. 2.6 and 2.7 using the PZT equivalent circuit. From the output power curves, both half-wave rectifiers are capable of delivering a peak power of less than 2  $\mu$ W.

FIGURE 2.7. Half-wave rectifier with NMOS and PMOS diodes.

FIGURE 2.8. Simulated power delivery of half-wave rectifier circuits in a 0.35- $\mu$ m CMOS process with the PZT input as shown in Fig. 2.3.

#### 2.4.2. Synchronous Half-Wave Rectification

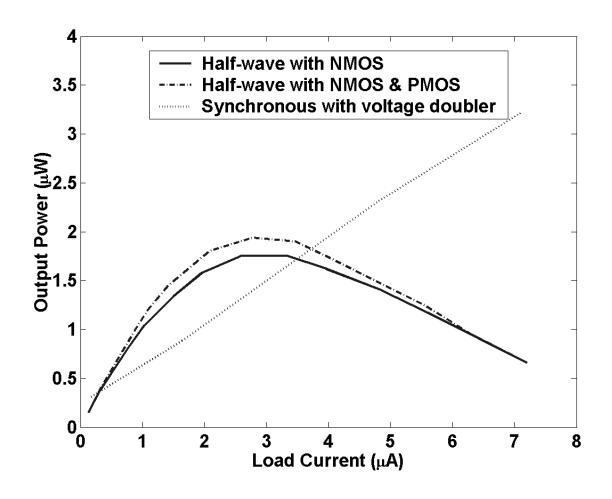

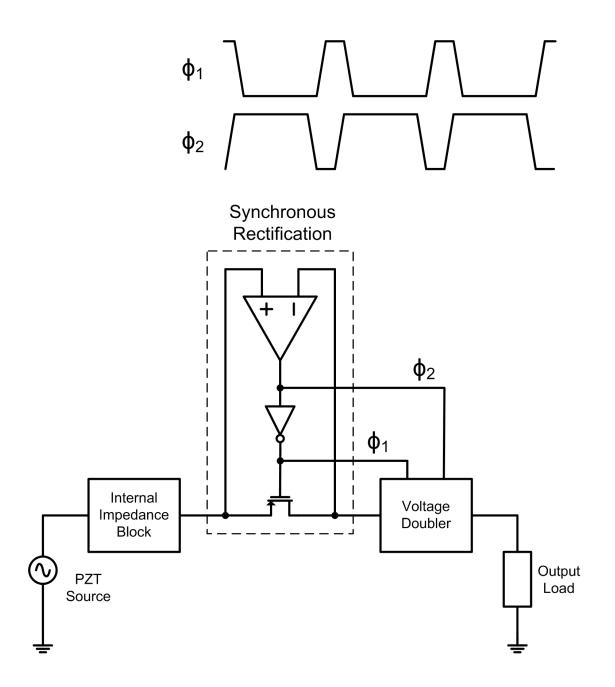

One way to overcome the limitation of the voltage drop is to use a synchronous rectifier circuit (Fig. 2.9). The PZT membrane model is used to simulate the synchronous rectification circuit with the voltage source and impedance block representing the equivalent circuit of the PZT device. The synchronous rectification circuit significantly reduces the equivalent diode voltage drop. However, because active circuits are used to reduce the diode drop, additional static power is required to operate the circuit. If this power is excessive, it can outweigh the benefits of the reduction in diode voltage drop.

In the synchronous rectifier circuit, a MOS transistor is used as a switch to control the conduction in the forward path. When the input to the synchronous rectifier is higher than its output voltage, the comparator output goes to the positive supply rail and turns on the switch to allow the charging of the output load. Conversely, when the input voltage of the synchronous rectifier is lower than the output voltage, the comparator output goes low, the switch is turned off and the forward conduction path is disconnected. The output voltage is very low from this circuit so an additional voltage doubling circuit is added as shown in Fig. 2.10. The voltage doubler is used to double the maximum voltage available from the PZT device.

A PMOS transistor is used as the switch for synchronous rectification because it allows a higher gate voltage drive and reduces the on-resistance of the switch. This allows more current to flow through the forward path and increases the rate at which the output capacitor is charged to its peak value. The size of the PMOS switch and the power supply voltage of the comparator in the synchronous rectifier also control the magnitude of the current and the charging rate through

FIGURE 2.9. Modified synchronous rectifier to generate two-phase clocking for the voltage doubler

FIGURE 2.10. Transistor-level schematic of the voltage doubler.

the synchronous rectifier. Increasing the supply voltage of the comparator reduces the on-resistance of the switch and increases the charging rate but it also increases the power consumption for the comparator. The synchronous rectifier circuit is designed to operate with a supply voltage of 3.3 V. Increasing the size of the PMOS switch increases the charging rate but when the size of the switch gets too large, the gate capacitance seen by the output of the comparator increases thus reducing the slew rate of the comparator.

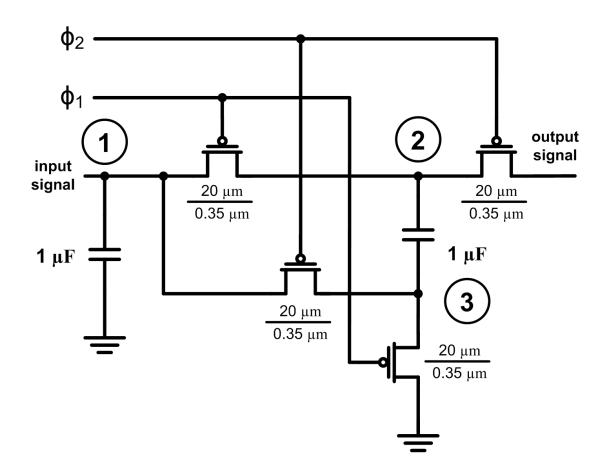

A switched capacitor voltage doubler customized to this application is shown in Figure 2.10 [34]. The two clock phases  $\phi_1$  and  $\phi_2$  are generated from the output of the comparator in the synchronous rectifier. In the voltage doubler, the 1  $\mu$ F capacitor connected to node 1 holds the charge in the forward path. When the synchronous rectifier transistor is turned on,  $\phi_1$  is low and the two PMOS transistors connected to it are turned on. This charges the internal 1- $\mu$ F capacitor connected between nodes 2 and 3. When  $\phi_2$  is low, the two capacitors are stacked to double the voltage at the output.

The design of the comparator is the most critical part in designing an efficient synchronous rectification circuit. The amount of power consumed by the comparator circuit is considered power loss in the synchronous rectification circuit because power must be drawn from other sources to power up the comparator. With the high internal impedance of the PZT device, the amount of power that can be delivered to the load is in the microwatts range. In order to create an efficient power conversion circuit, the comparator must operate with nanowatts of power.

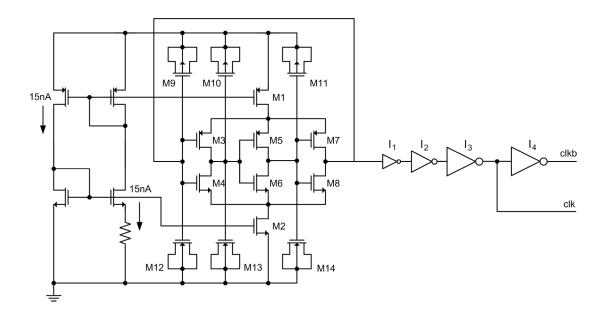

For synchronous rectification of the voltage coming from the PZT membrane, the performance requirements for the comparator are relatively modest. A unity-gain bandwidth in the kiloHertz range and an open loop gain of approximately 40 dB is sufficient. To meet these requirements while achieving very low power, the comparator was designed in the subthreshold region [35, 39, 40]. The operating current is 50 nA and the supply voltage is 3.3 V resulting in a power dissipation of 165 nW.

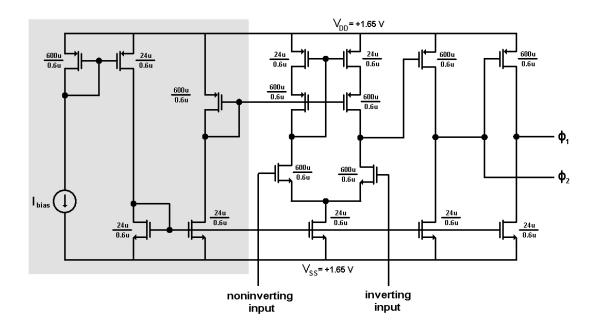

Folded-cascode and telescopic opamp configurations were considered for this comparator. One of the advantages of the folded-cascode configuration is the high gain achieved from the two stages, however, the tradeoff is that it dissipates twice as much power as the telescopic configuration shown in Fig. 2.11. The telescopic configuration is chosen in this case because it burns less static power and more simple to design to fit to the desired specifications. To achieve the 40-dB gain with 50 nA of operating current, the input transistors are sized at 600  $\mu$ m/0.6  $\mu$ m to achieve a  $g_m$  of about 1.4- $\mu$ A/V. The active load of the comparator is cascoded to help achieve the correct output common mode voltage as well as to limit the amount of current available when the output of the comparator goes high.

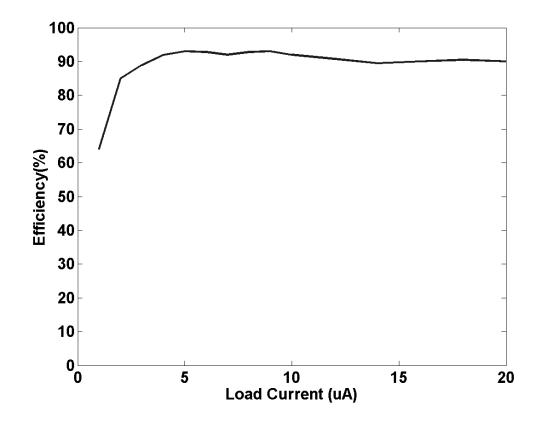

The EKV transistor model was used to design the comparator [35–37] in the subthreshold region. Simulation results of the power conversion circuit efficiency versus output load, is shown in Fig. 2.12, where power conversion efficiency defined as the ratio between the average output power and average input power when the output voltage is charged up to a steady state. The comparator in the measurement was powered by an external power source. For the calculation of power conversion efficiency, the input power is the combination of the average power dissipated by the PZT membrane model and the power dissipated by the comparator. The PZT membrane model was used as the input power source to the power conversion circuit. For output currents greater than 4  $\mu$ A, the efficiency is more than 90%. To compare this rectifier with the passive half-wave rectifier, the

FIGURE 2.11. Schematic of the comparator designed and fabricated in the TSMC 0.35- $\mu$ m CMOS process.

power delivery versus load current is shown in Fig. 2.8. For 6- $\mu$ A load current, the output power is nearly 3  $\mu$ W which is double that of the passive rectifier.

FIGURE 2.12. Simulated efficiency versus output load for the synchronous rectifier designed in the 0.35- $\mu$ m CMOS process.

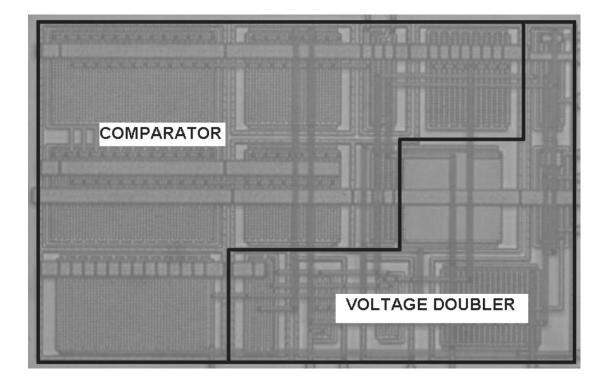

The die photograph for the synchronous rectifier and voltage doubler is shown in Fig. 2.13. The total die area is 160  $\mu$ m x 100  $\mu$ m fabricated in the TSMC 0.35- $\mu$ m CMOS process. All routing and interconnections are as short as possible to reduce junction leakage. When the bias current of the comparator is in the lower nanoamp range, junction leakage can no longer be negligible and may reduce the performance of the comparator. Also, the comparator is shielded with a guard ring to reduce the noise current from the substrate.

FIGURE 2.13. Die photograph of the synchronous rectifier and voltage doubler designed and fabricated in the TSMC 0.35- $\mu$ m CMOS process.

The chip was characterized by connecting the power conversion circuit to the actual piezoelectric membrane. The piezoelectric membrane was excited using a periodic mechanical air pressure device driven by a high voltage AC source. The air pressure is focused on the piezoelectric membrane and periodically alternates at the resonant frequency. Table 2.1 summarizes the simulation versus the measurements of the power conversion circuit.

The measured results are in good agreement with the simulations. The DC output voltage is in the range of 0.6 V for a peak input of approximately 0.6 V. The

|           | R <sub>load</sub>       | $\mathbf{P}_{input}$ | Vout  | $\mathbf{P}_{out}$ | Efficiency     |

|-----------|-------------------------|----------------------|-------|--------------------|----------------|

|           |                         | $(\mu W)$            | (V)   | $(\mu W)$          | (%)            |

| Simulated | $10 \ \mathrm{M}\Omega$ | 0.410                | 0.559 | 0.312              | 67.9~%         |