#### AN ABSTRACT OF THE THESIS OF

<u>Lalit T. Merani</u> for the degree of <u>Master of Science</u> in <u>Electrical and Computer Engineering</u> presented on <u>August 24, 1993.</u> Title: <u>MICRO DATA FLOW (MDF): A Data Flow Approach to Self-timed VLSI</u> <u>System Design for DSP</u>

**Redacted for Privacy**

Abstract approved: \_

Shih-Lien Lu

Synchronization is one of the important issues in digital system design. While other approaches have been intriguing, up until now a globally clocked timing discipline has been the dominant design philosophy. However, we have reached the point, with advances in technology, where other options should be given serious consideration. VLSI promises great processing power at low cost. This increase in computation power has been obtained by scaling the digital IC process. But as this scaling continues, it is doubtful that the advantages of faster devices can be fully exploited. This is because the clock periods are getting much smaller in relation to the interconnect propagation delays, even within a single chip and certainly at the board and backplane level.

In this thesis, some alternative approaches to synchronization in digital system design are described and developed. We owe these techniques to a long history of effort in both digital computational system design as well as digital communication system design. The latter field is relevant because large propagation delays have always been a dominant consideration in its design methods. Asynchronous design gives better performance than comparable synchronous design in situations for which a global synchronization with a high speed clock becomes a constraint for greater system throughput. Asynchronous circuits with unbounded gate delays, or self-timed digital circuit can be designed by employing either of two request-acknowledge protocols - 4-cycle and 2-cycle.

We will also present an alternative approach to the problem of mapping computation algorithms directly into asynchronous circuits. Data flow graph or language is used to describe the computation algorithms. The data flow primitives have been designed using both the 2-cycle and 4-cycle signaling schemes which are compared in terms of performance and transistor count. The 2-cycle implementations prove to be better than their 4-cycle counterparts.

A promising application of self-timed design is in high performance DSP systems. Since there is no global constraint of clock distribution, localized forward-only connection allows computation to be extended and sped up using pipelining. A decimation filter was designed and simulated to check the system level performance of the two protocols. Simulations were carried out using VHDL for high level definition of the design. The simulation results will demonstrate not only the efficacy of our synthesis procedure but also the improved efficiency of the 2-cycle scheme over the 4-cycle scheme.

C Copyright by Lalit T. Merani August 24, 1993

All Rights Reserved

# MICRO DATA FLOW (MDF): A Data Flow Approach to Self-timed VLSI System Design for DSP

by

Lalit T. Merani

# A THESIS

submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of Master of Science

Completed August 24, 1993 Commencement June, 1994 APPROVED:

# **Redacted for Privacy**

Professor of Electrical and Computer Engineering in charge of major

# Redacted for Privacy

Head of the Department of Electrical and Computer Engineering

**Redacted for Privacy**

Dean of Graduate School

Date thesis is presented

August 24, 1993

Typed by researcher for

Lalit T. Merani

# ACKNOWLEDGEMENTS

This report describes research done at the Department of Electrical and Computer Engineering at Oregon State University. Support for the research was provided by the National Science Foundation grant # MIP-9211510. This research has also been helped by *View*logic Inc.

I would like to thank my major professor Dr. Shih-Lien Lu. His contribution to this thesis is irreplaceable (most of the ideas were his) but represents only a small fraction of how he has helped me in the last two years. Shih-Lien's clear and simple expression of his thorough understanding of many fields and his enthusiasm for knowledge makes him one of the best teachers I have ever had.

I would like to acknowledge Prof. Bella Bose's help and inspiration. He has, in his quiet way, influenced my attitude and enthusiasm. He has taught me, in the words of M. A. Biot, "the tradition of clarity, simplicity, intuitive understanding, unpretentious depth, and a shunning of the irrelevant."

I thank Dr. Griffiths and Dr. Shor for having taken time out of their busy schedules to be available for my thesis defense. I would like to thank the following people for invaluable discussions and various other help: Pat Lenders, Jim Herzog, Sayfe Kiaei, Ben Lee, Rita Wells, Tarek Abdelrahman, Suzy Rogers, Chih-Ming Chang. A special mention of thanks to Ravi Ramachandran for his invaluable help in drawing the circuit schematics and through the various draft stages of this report.

Further, I would like to thank my personal friends, Meenu, Shree, Satish, Ashok, Sailesh, Vivek, Manoj, Shashank, Varad, Sunil, Qazi for all the good times that made this stay at OSU easier.

Finally, to my parents, thanks for your love and blessings, without which this would simply have not been possible.

# TABLE OF CONTENTS

| 1. | SYN | ICHRON     | IZATION                                     | 1  |

|----|-----|------------|---------------------------------------------|----|

|    | 1.0 | Introduct  | ion                                         | 1  |

|    | 1.1 | Asynchro   | onous and Synchronous Digital System Design | 2  |

|    | 1.2 | Organiza   | tion of this document                       | 6  |

| 2. | PRO | DTOCOL     | S AND PIPELINES                             | 7  |

|    | 2.0 | Introduct  | ion                                         | 7  |

|    | 2.1 | Pipelining | g                                           | 7  |

|    | 2.2 | The Basic  | c Model                                     | 8  |

|    | 2.3 | The 4-cyc  | cle Request-acknowledge Protocol            | 9  |

|    | 2.4 | The Tran   | sition Signaling Conceptual Framework       | 10 |

|    | 2.5 | Event Log  | gic and Muller-C Elements                   | 11 |

|    |     | 2.5.1      | SR-Latches vs. C-Elements                   | 12 |

|    | 2.6 | A 2-cycle  | FIFO                                        | 13 |

|    | 2.7 | A 4-cycle  | FIFO                                        | 15 |

|    | 2.8 | Some Inte  | eresting Observations                       | 17 |

| 3. | DAI | ra flov    | V PROGRAM GRAPHS FOR DSP                    | 19 |

|    | 3.0 | Introducti | ion                                         | 19 |

|    | 3.1 | The Data   | Flow Concept                                | 20 |

|    | 3.2 | A Data Fl  | low Language                                | 21 |

|    |     | 3.2.1      | Processing elements                         | 22 |

|    |     | 3.2.2      | Information                                 | 23 |

|    |     | 3.2.3      | Arcs                                        | 23 |

|    |     | 3.2.4      | Motivation and advantages                   | 25 |

|                                                   | 3.3  | Schedulin                                   | g of Data Flow Programs for DSP                         | 26 |

|---------------------------------------------------|------|---------------------------------------------|---------------------------------------------------------|----|

|                                                   |      | 3.3.1                                       | Recurrences                                             | 28 |

|                                                   |      | 3.3.2                                       | Conditionals                                            | 29 |

|                                                   |      | 3.3.3                                       | Iterations                                              | 30 |

|                                                   | 3.4  | Some Inte                                   | resting Observations                                    | 33 |

|                                                   | 3.5  | Summary                                     |                                                         | 34 |

| 4.                                                | MO   | DELING                                      | OF DIGITAL CIRCUITS USING VHDL                          | 36 |

|                                                   | 4.0  | Introductio                                 | o <b>n</b>                                              | 36 |

|                                                   | 4.1  | Origins of                                  | VHDL                                                    | 36 |

|                                                   | 4.2  | Describing                                  | g Structure                                             | 37 |

|                                                   | 4.3  | Describing                                  | g Function                                              | 40 |

|                                                   | 4.4  | Discrete E                                  | vent Time Model                                         | 41 |

|                                                   | 4.5  | Summary                                     |                                                         | 44 |

| 5. 2-CYCLE AND 4-CYCLE SELF-TIMED IMPLEMENTATIONS |      |                                             |                                                         |    |

|                                                   | OF 7 | <b>ТНЕ DAT</b>                              | A FLOW ACTORS                                           | 45 |

|                                                   | 5.0  | Introduction                                |                                                         |    |

|                                                   | 5.1  | Design of the Data Path                     |                                                         |    |

|                                                   | 5.2  | Pipeline and Non-pipelined Interconnections |                                                         | 48 |

|                                                   |      | 5.2.1                                       | 2-cycle interconnections                                | 48 |

|                                                   |      | 5.2.2                                       | 4-cycle interconnections                                | 51 |

|                                                   | 5.3  | The Data I                                  | Flow LINKs and Actors                                   | 52 |

|                                                   |      | 5.3.1                                       | Self-timed implementation of the data flow LINK         | 53 |

|                                                   |      | 5.3.2                                       | Self-timed implementation of the data flow PREDICATE    | 56 |

|                                                   |      | 5.3.3                                       | Self-timed implementation of the data flow TRUE actor   | 59 |

|                                                   |      | 5.3.4                                       | Self-timed implementation of the data flow MERGE actor  | 62 |

|                                                   |      | 5.3.5                                       | Self-timed implementation of the data flow SELECT actor | 67 |

|        | 5.3.6          | Self-timed implementation of the data flow MUX actor      | 70         |

|--------|----------------|-----------------------------------------------------------|------------|

|        | 5.3.7          | Self-timed implementation of the data flow INIT actor     | <b>7</b> 0 |

|        | 5.3.8          | Self-timed implementation of the data flow IDENTITY actor | r 75       |

|        | 5.3.9          | Self-timed implementation of the data flow COUNTER actor  | r 75       |

|        | 5.3.10         | Self-timed implementation of the data flow REPEAT actor   | 78         |

| 5.4    | Comparis       | on of the Two Protocols                                   | 81         |

| 5.5    | Summary        |                                                           | 85         |

| 6. SIN | <b>IULATIO</b> | N OF A SELF-TIMED DECIMATION FILTER                       | 86         |

| 6.0    | Introducti     | on                                                        | 86         |

| 6.1    | A Multist      | age Multirate Combs Filter Design Method                  | 86         |

| 6.2    | A Self-tin     | ned Implementation of the Decimation Filter               | 88         |

| 6.3    | Simulatio      | n Results                                                 | 93         |

| 6.4    | Summary        |                                                           | 96         |

| 7. CO  | NCLUSIO        | NS AND FUTURE WORK                                        | 97         |

| 7.0    | Conclusio      | ons                                                       | 97         |

| 7.1    | Future W       | ork                                                       | 97         |

|        | 7.1.1          | DSP applications                                          | 98         |

|        | 7.1.2          | General-purpose computing                                 | 99         |

|        | 7.1.3          | CAD tool design                                           | 99         |

| REFER  | RENCES         |                                                           | 101        |

.

# LIST OF FIGURES

| <u>Figur</u> | <u>e</u>                                                                                                               | <u>Page</u> |

|--------------|------------------------------------------------------------------------------------------------------------------------|-------------|

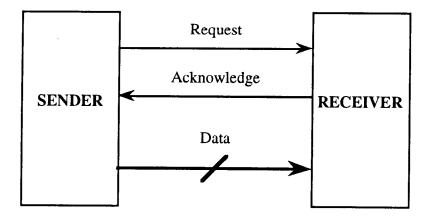

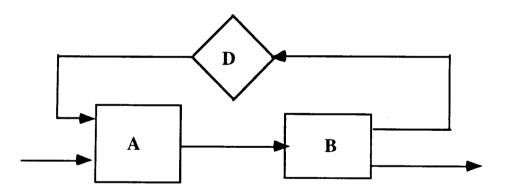

| 1.1          | A block diagram viewpoint of a request-acknowledge handshake scheme.                                                   | 5           |

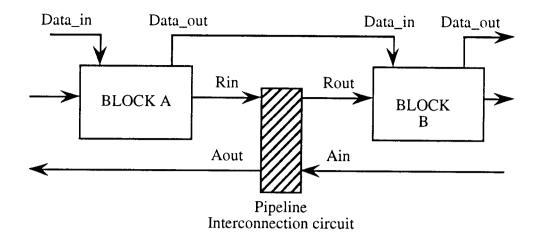

| 2.1          | A simple example of a pipeline interconnection circuit that controls data transfer between blocks A and B.             | 8           |

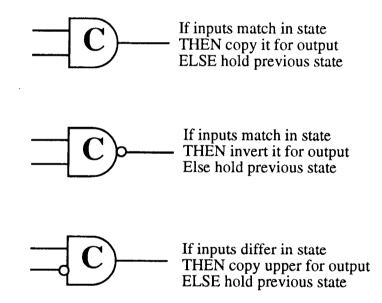

| 2.2          | Muller-C elements for control of events.                                                                               | 11          |

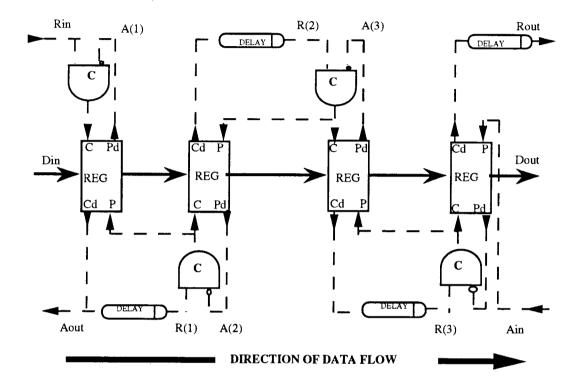

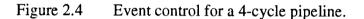

| 2.3          | The Structure of a Micropipeline.                                                                                      | 15          |

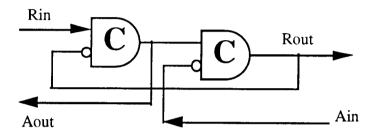

| 2.4          | Event control for a 4-cycle pipeline.                                                                                  | 16          |

| 2.5          | The Structure of a 4-cycle FIFO.                                                                                       | 16          |

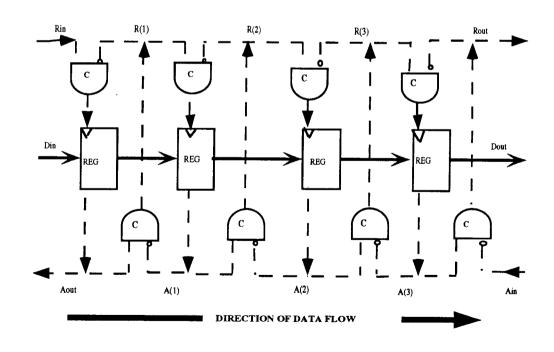

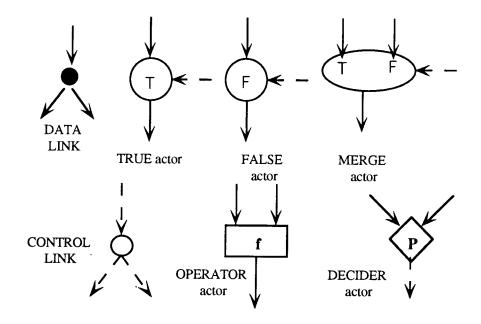

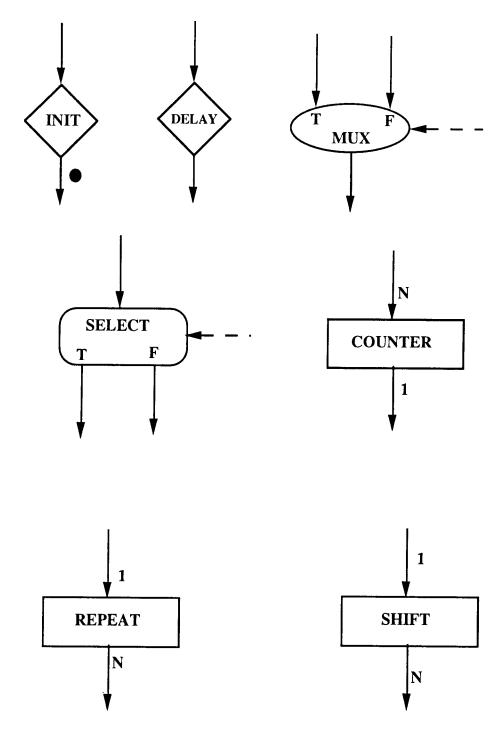

| 3.1          | The Data Flow Links and Actors.                                                                                        | 24          |

| 3.2          | A data flow graph with a recurrence. Recurrences are expressed as directed loops and delays.                           | 28          |

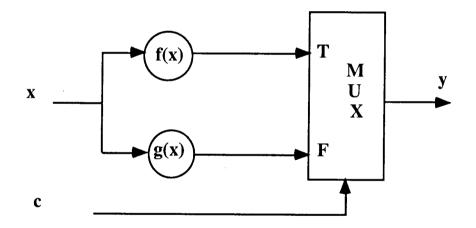

| 3.3          | A data flow graph with conditional assignment. Both $f(x)$ and $g(x)$ are evaluated, and only one of them is selected. | 29          |

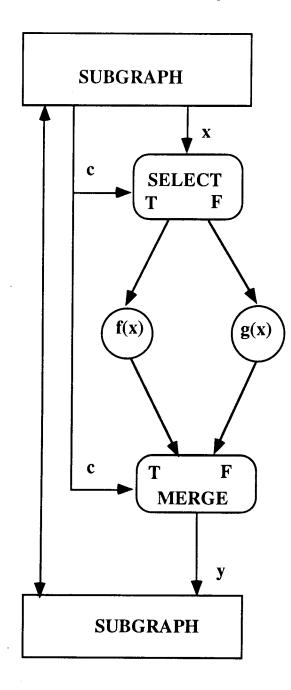

| 3.4          | An alternative data flow graph for the expression<br>y := if(c) then $f(x)$ else $g(x)$ .                              | 31          |

| 3.5          | Data flow graphical representation of 6 additional actors.                                                             | 32          |

| 4.1          | Gate level schematic of a double-edge triggered flip-flop.                                                             | 38          |

| 4.2          | Structural description of a double-edge triggered flip-flop.                                                           | 39          |

| 4.3          | Behavioral description of a double-edge triggered flip-flop.                                                           | 40          |

| 4.4          | A Viewlogic® VHDL Command File.                                                                                        | 42          |

| 4.5          | Waveforms generated by the simulation of a double-edge triggered flip-flop.                                            | 43          |

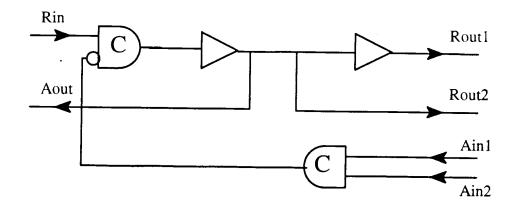

| 5.1          | 4-cycle pipeline interconnection.                                                                                      | 49          |

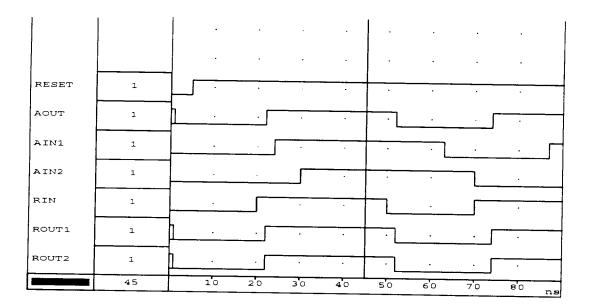

| 5.2          | 4-cycle non-pipeline interconnection.                                                                                  | 49          |

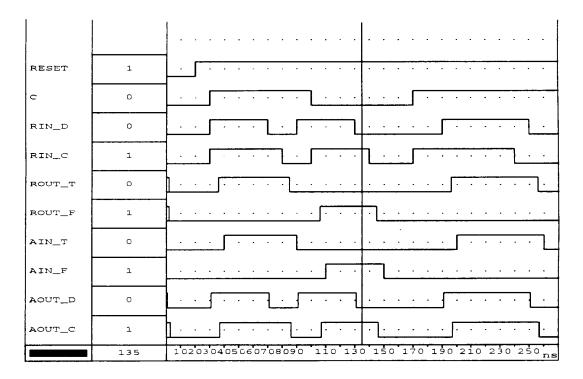

| 5.3          | Simulation result of the 4-cycle pipeline interconnection.                                                             | 50          |

| 5.4  | Simulation result of the 4-cycle non-pipeline interconnection. | <b>5</b> 0 |

|------|----------------------------------------------------------------|------------|

| 5.5  | 2-cycle implementation of a Data Flow LINK.                    | 54         |

| 5.6  | Simulation result of a 2-cycle Data Flow LINK.                 | 54         |

| 5.7  | 4-cycle implementation of a Data Flow LINK.                    | 55         |

| 5.8  | Simulation result of a 4-cycle Data Flow LINK.                 | 55         |

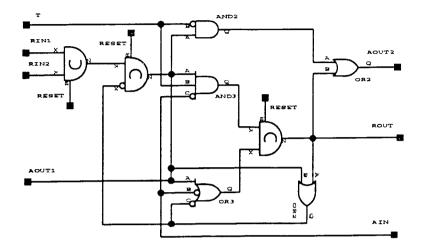

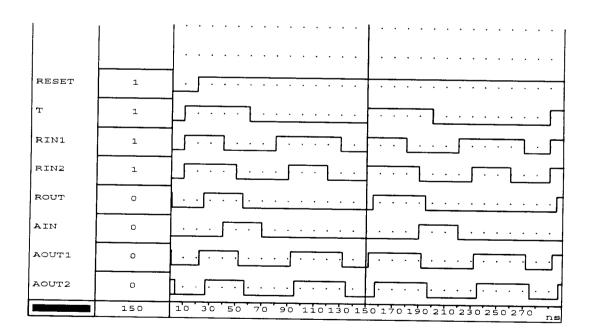

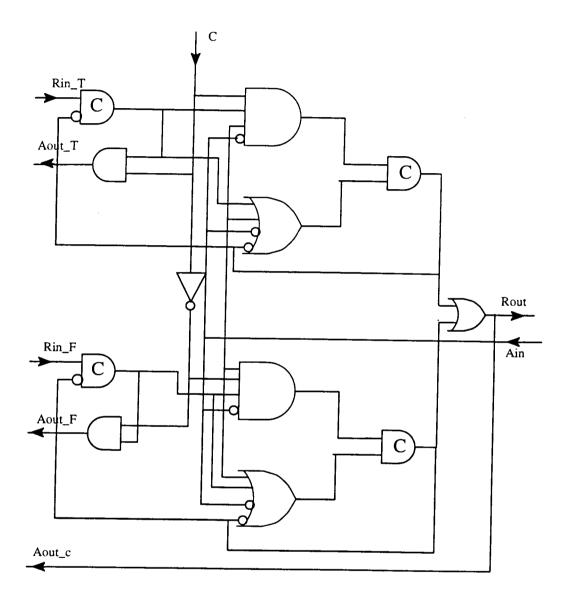

| 5.9  | 2-cycle implementation of a Data Flow PREDICATE.               | 57         |

| 5.10 | Simulation result of a 2-cycle Data Flow PREDICATE.            | 57         |

| 5.11 | 4-cycle implementation of a Data Flow PREDICATE.               | 58         |

| 5.12 | Simulation result of a 4-cycle Data Flow PREDICATE.            | 58         |

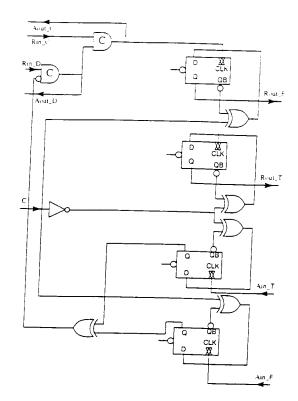

| 5.13 | 2-cycle implementation of a Data Flow TRUE actor.              | 60         |

| 5.14 | Simulation result of a 2-cycle Data Flow TRUE actor.           | 60         |

| 5.15 | 4-cycle implementation of a Data Flow TRUE actor.              | 61         |

| 5.16 | Simulation result of a 4-cycle Data Flow TRUE actor.           | 61         |

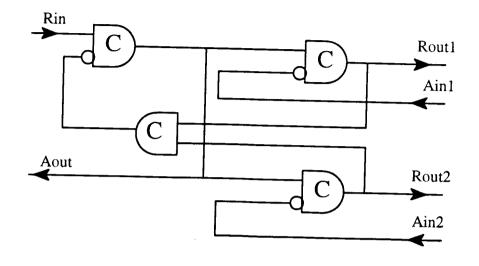

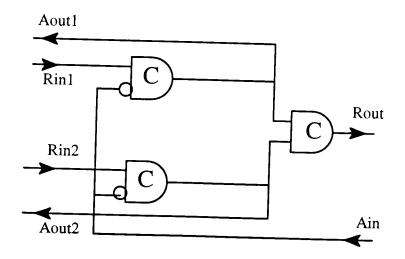

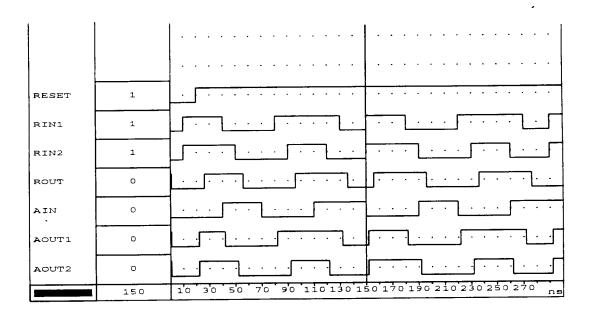

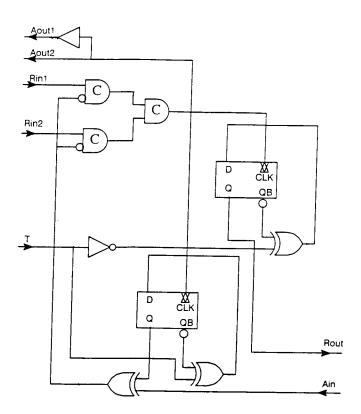

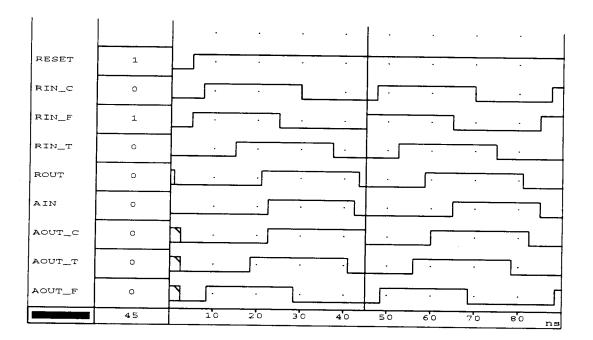

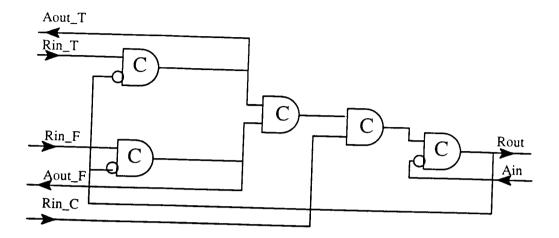

| 5.17 | 2-cycle implementation of a Data Flow MERGE actor.             | 63         |

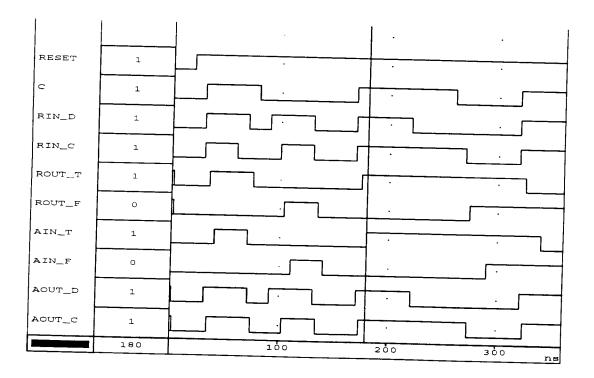

| 5.18 | Simulation result of a 2-cycle Data Flow MERGE actor.          | 64         |

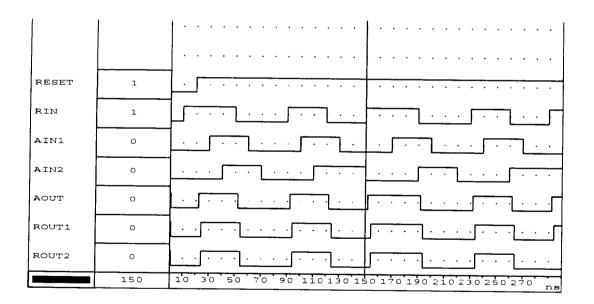

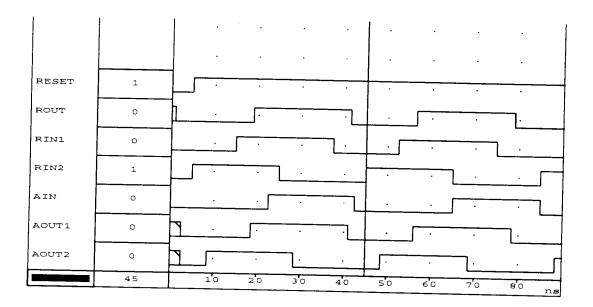

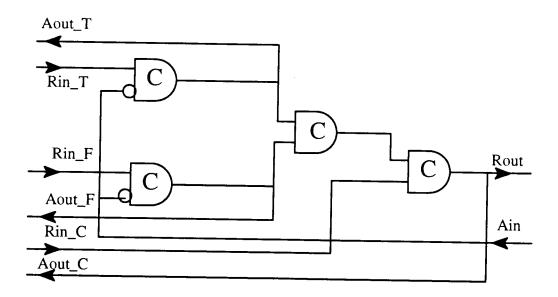

| 5.19 | 4-cycle implementation of a Data Flow MERGE actor.             | 65         |

| 5.20 | Simulation result of a 4-cycle Data Flow MERGE actor.          | 66         |

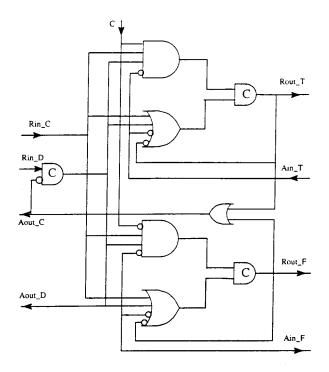

| 5.21 | 2-cycle implementation of a Data Flow SELECT actor.            | 68         |

| 5.22 | Simulation result of a 2-cycle Data Flow SELECT actor.         | 68         |

| 5.23 | 4-cycle implementation of a Data Flow SELECT actor.            | 69         |

| 5.24 | Simulation result of a 4-cycle Data Flow SELECT actor.         | 69         |

| 5.25 | 2-cycle implementation of a Data Flow MUX actor.               | 71         |

| 5.26 | Simulation result of a 2-cycle Data Flow MUX actor.            | 71         |

| 5.27 | 4-cycle implementation of a Data Flow MUX actor.               | 72         |

| 5.28 | Simulation result of a 4-cycle Data Flow MUX actor.            | 72         |

| 5.29 | 2-cycle implementation of a Data Flow INIT actor.              | 73         |

|      |                                                                |            |

| 5.30 | Simulation result of a 2-cycle Data Flow INIT actor.                                         | 73 |

|------|----------------------------------------------------------------------------------------------|----|

| 5.31 | 4-cycle implementation of a Data Flow INIT actor.                                            | 74 |

| 5.32 | Simulation result of a 4-cycle Data Flow INIT actor.                                         | 74 |

| 5.33 | 2-cycle implementation of a Data Flow COUNTER actor.                                         | 76 |

| 5.34 | Simulation result of a 2-cycle Data Flow COUNTER actor.                                      | 76 |

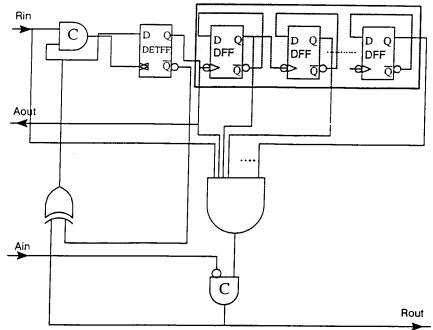

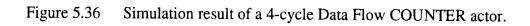

| 5.35 | 4-cycle implementation of a Data Flow COUNTER actor.                                         | 77 |

| 5.36 | Simulation result of a 4-cycle Data Flow COUNTER actor.                                      | 77 |

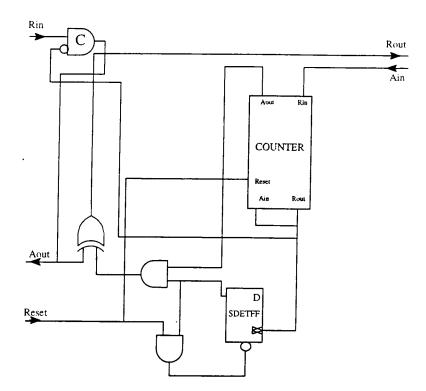

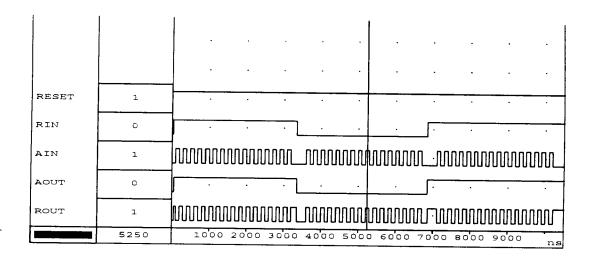

| 5.37 | 2-cycle implementation of a Data Flow REPEAT actor.                                          | 79 |

| 5.38 | Simulation result of a 2-cycle Data Flow REPEAT actor.                                       | 79 |

| 5.39 | 4-cycle implementation of a Data Flow REPEAT actor.                                          | 80 |

| 5.40 | Simulation result of a 4-cycle Data Flow REPEAT actor.                                       | 80 |

| 6.1  | A C program which simulates the operation of the decimator.<br>Courtesy: R. Schreier of OSU. |    |

|      | The original program has been modified by us.                                                | 89 |

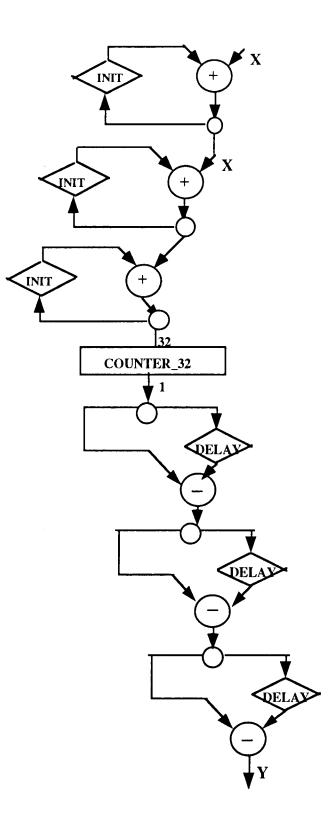

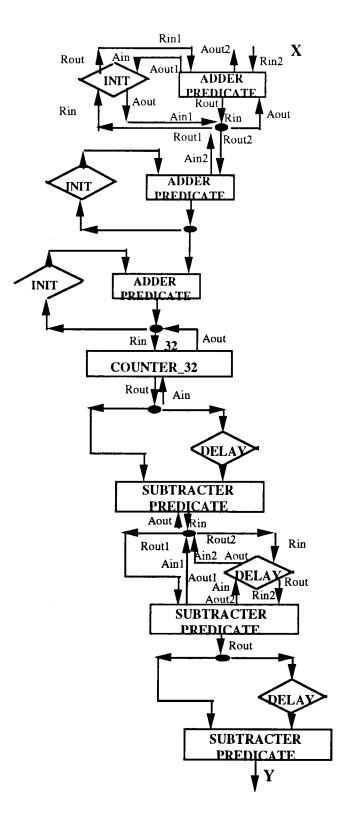

| 6.2  | A Data Flow Graph representation of the C program in Fig. 6.1.                               | 90 |

| 6.3  | A block diagram schematic of the Data Flow program graph.                                    | 91 |

| 6.4  | Behavioral description of a 2-cycle ADDER.                                                   | 92 |

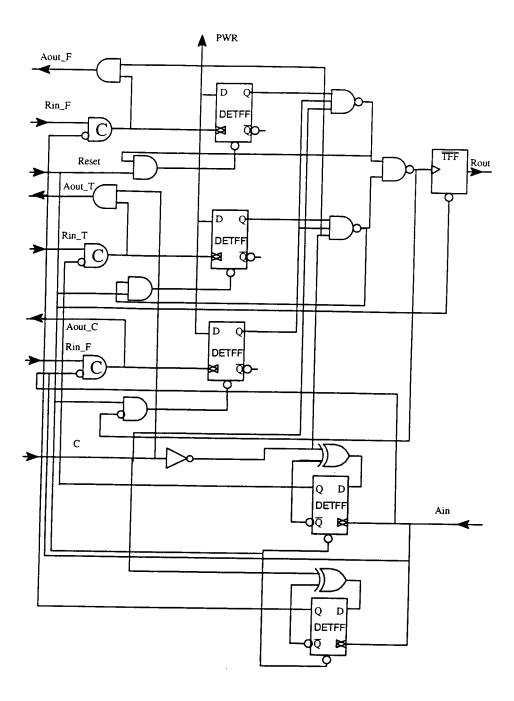

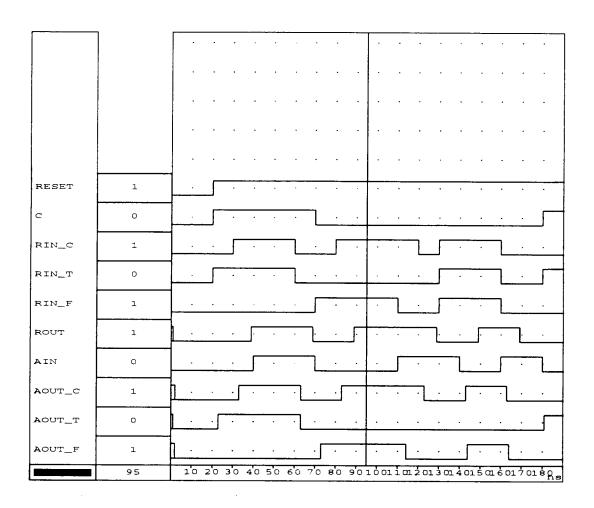

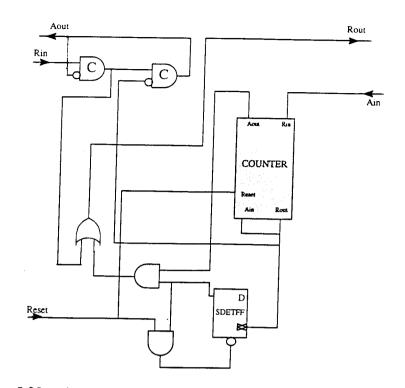

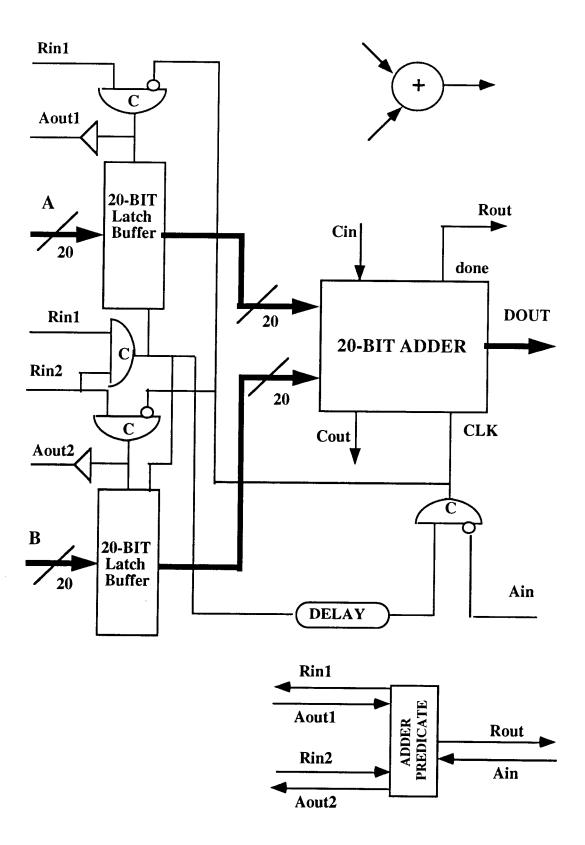

| 6.5  | A Schematic of the 2-cycle ADDER PREDICATE.                                                  | 94 |

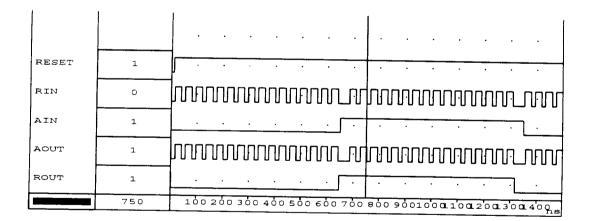

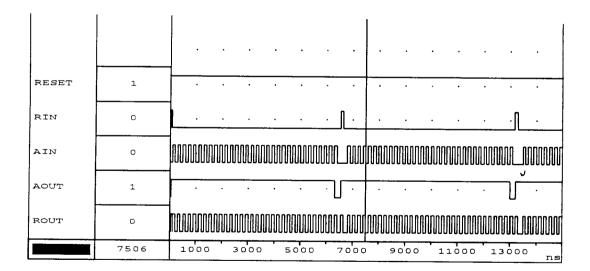

| 6.6  | Simulation results of the 2-cycle Decimation Filter.                                         | 95 |

| 6.7  | Simulation results of the 4-cycle Decimation Filter.                                         | 95 |

|      |                                                                                              |    |

# LIST OF TABLES

| <u>Table</u> |                                                                                                                                                                                                                                                | <u>Page</u> |  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| I            | Transistor count and intrinsic gate delay of the basic logic<br>elements for a static CMOS implementation. Worst case<br>conditions are considered. Note that every additional input to<br>a logic gate adds 2 transistors and 0.5 gate delay. |             |  |

| II           | Comparison of 2-cycle and 4-cycle pipelined implementations<br>of the data flow links and actors. Note that the transistor count,<br>intrinsic delay and performance measure are symbolized                                                    | 82          |  |

|              | as A, T and P, respectively.<br>Comparison of 2-cycle and 4-cycle non-pipelined implementations<br>of the data flow links and actors. Note that the transistor count,<br>intrinsic delay and performance measure are symbolized                | 83          |  |

|              | as A, T and P, respectively.                                                                                                                                                                                                                   | 84          |  |

## MICRO DATA FLOW (MDF):

# A Data Flow Approach to Self-timed VLSI System Design for DSP

#### Chapter 1. SYNCHRONIZATION

# 1.0 Introduction

The last two decades and in essence the '80s have observed the realization of the visions of science fiction writers, considered fanciful at best, even twenty years ago. One of those visions involved the creation of an information society. This required the storage, transformation and communication of information. The main force behind these great technological advances has been the digital model for system design. System here includes both computer systems and communication systems.

In the world of computers and computing, there is always an imbalance between the supply and demand of computing power. Problems which occur in the fields of meteorology, image processing, global models, wind tunnel simulation and simulation of computer systems, among others, are examples of a class of problems which demand very high computing power. Even with the impressive choice of machines that is available to us today, we find ourselves at a great disadvantage when trying to solve such problems.

In recent years, we have seen a veritable explosion of VLSI-based solutions for digital signal and image processing. With the advent of multi-media, the computation and speed requirements of application specific digital systems, which up until now slowly increased, will now steeply rise. Digital cellular telephony, High Definition Television, re-recordable optical memories will all contribute to this rise. Thus, in both the worlds of general-purpose and application specific computing the speed requirements are reaching a stage at which it would be worth evaluating the basic assumptions of current digital system design models.

We are also interested in systems that scale up as the size of the problem increases. This flexibility is going to be very important in the design of future digital systems. We need to look at models that lend themselves very naturally to these requirements of scaling. Linked to these reuiremnets are issues of power consumption, as we become increasingly aware of our environmental responsibilities.

The problem of developing new models is definitely non-trivial. But, where do we begin our re-learning? A basic assumption is that do any effective computing we require a global clock. Like the communications industry, can the computing industry divest itself of this self-imposed restriction of a global clock? In the next section, we discuss the basic issue of synchronization and the effect it has on the way we have designed digital computing systems up until now.

# 1.1 Asynchronous and Synchronous Digital System Design

Synchronization is one of the important issues in digital system design, especially in the effective design of any large computer and communication system. While other approaches have been intriguing, up until now a globally clocked timing discipline has been the dominant design philosophy. Some of the important factors that influenced the methodology of digital system design to take this course were:

• Major components of a computer system, like the memory and the ALU, were built synchronously.

- With global synchronization, the circuit transients do not affect the proper operation of the whole system.

- The step by step nature of synchronous systems made it easy to design and trace the sequence of actions performed by them.

- Synchronous systems were favored because they required fewer gates, which meant a lower cost if the systems were built from gates.

In fact, the reasons that contributed to the control flow, or von Neumann, model of digital computer system design becoming the widely accepted norm in the design of digital computers also contributed to the computer architects at that time favoring global synchronization. But digital communication continued to employ asynchronous design philosophy. The main reason for this was that the clock period was many orders of magnitude smaller than the communication delays.

However, we have reached a point, with advances in VLSI technology, where global synchronization does not suffice. This is because the clock periods are getting much smaller than the interconnect propagation delays within a single chip, not to mention at the board and backplane level. At the same time the theory and methodology of asynchronous computing system design has been maturing. So an intuitive first look suggests that asynchronous computing system design is worth a closer scrutiny.

Besides this, asynchronous computing system design offers other advantages [1]. First of all, asynchronous designs are algorithmic. It is easier to convert an algorithm to a wiring list for asynchronous modules than translating the algorithm into step by step procedures. Secondly, speed independent modules allow the system to perform correctly. There is no need to adjust the pulse width and clock period to fit all modules' timing requirements. It will avoid the clock skewing problem. Third,

the speed of execution is taken to be as fast as the problem or algorithm will allow. Fourth, composition of asynchronous modules in to asynchronous systems is readily simple. Building systems hierarchically is inherent. Building each individual asynchronous module on a single chip enables the testing and verification of each chip to be performed independently. With each module or chip verified to be functionally correct, they can be assembled on a single chip if area permits with no extra timing constraint needing to be satisfied. This ability to verify modules independently is becoming more and more desirable since system testing consumes larger and larger portions of the development cycle with each passing day. Fifth, incremental performance gains are easier to come by. Since there is no global timing requirement, any elements or blocks residing in the critical path may be replaced with faster counterparts without having to readjust the system timing parameters. Sixth, scaling up the system as the problem grows in size is much easier to accomplish. Finally, lower system noise and zero stand-by power consumption add to the many advantages listed before.

To contrast between the synchronous and asynchronous timing disciplines, we present an example which will illustrate the difference [2,3,4]. Pictorially, a synchronous system works like a scheduled train line. At every designated interval, there will be a train taking off from the station whether there is a full load of passengers or none at all. A particular passenger has to synchronize his/her travel itinerary with the schedule of the train. In contrast, an asynchronous system is like traveling in your own car. There is no fear of missing a scheduled departure time. There is no waiting in a depot for a train to arrive. You may visit a new place whenever you have finished visiting an old location.

This potential of asynchronous digital system design has many researchers in academia and some in industry interested. Researchers have a great liking for coining

new terms (as have we, by coining 'micro data flow'). As a result, asynchronous system design has also been called *delay-insensitive* system design. Here the delays of the interconnects within a chip and on the board were not taken into account. Other terms that can be seen in recent literature are *speed-independent* and *self-timed* digital system design. These both essentially mean the same. Both take into account the delays of the interconnects. This is very important as interconnect delays have become a very crucial issue in digital system design [5,6].

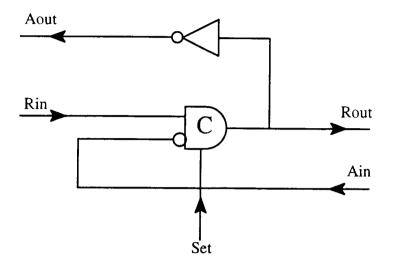

As can be understood from the simple analogy above, we are interested in the sequence of events. We no more allow the different computation blocks to abdicate their synchronization responsibility to a global clock. This requires the development of a protocol strategy, with the help of which we can accomplish synchronization. This protocol governs the proper relationship between events. In digital systems, this is implemented with signaling. We require a strategy based on some form of a request-acknowledge handshaking mechanism. Fig. 1.1 illustrates a block diagram of a request-acknowledge handshake scheme.

Figure 1.1 A block diagram viewpoint of a request-acknowledge handshake scheme.

Though, it is not apparent from the block diagram, it is very important to enforce a simple condition on this handshake scheme. The request needs to be bundled with the data, so that it does not arrive before valid data is ready for the receiver.

# **1.2** Organization of this document

In the next chapter we discuss the two different protocol strategies that are the most commonly used. We will also discuss the effect that pipelining has on digital system throughput. Chapter 3 consists of a discussion of data flow graphs adapted for signal processing functions. It will explain why a data flow graph is a natural method for high-level specification of computing algorithms that need to be mapped onto self-timed digital circuits. Chapter 4 is a brief discussion of how a hardware description language can be effectively used for the synthesis and analysis of self-timed circuits.

Chapter 5 concerns itself with the bulk of the self-timed digital circuits and contains most of the original contribution made by this thesis. In Chapter 6, we will use a decimation filter as an example to illustrate the performance issues involved. We will then conclude and hint at future directions of research in Chapter 7.

# Chapter 2. PROTOCOLS AND PIPELINES

# 2.0 Introduction

To enable effective synchronization and also to make the computation blocks responsible for synchronization, we require a request-acknowledge protocol. We also know that in digital systems such a form of protocol can be implemented using signaling.

Seitz [3] illustrates two main request-acknowledge protocol strategies - a 4cycle protocol (also known as Return-to-Zero protocol, or Muller signaling) and a 2cycle protocol (also known as Non-Return-to-Zero protocol, or transition-signaling). In the case of the former protocol, we accomplish signaling by using pulses of indeterminate lengths. In the second protocol, we use transitions to achieve the same synchronization. In the rest of this thesis, these two strategies have been compared. This thesis should enable us to decide which of these protocols offers greater potential. But before we get to that stage we need to develop an understanding of the protocols and the related issues.

# 2.1 Pipelining

The pipeline is a common paradigm for high-speed computation. The analogy of a pipeline to the assembly line in an automobile factory is apt. The higher speed, or the greater throughput, is due to the fact that the different stages can act concurrently (i.e., after the pipeline has been filled, its latency has been overcome).

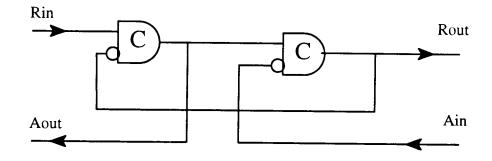

Figure 2.1 A simple example of a pipeline interconnection circuit that controls data transfer between blocks A and B.

Pipelines both store and process data, the storage elements and processing logic alternating along their length. Stripped of all processing logic, any pipeline acts like a series of storage elements through which data can pass. If the parts of the pipeline act in response to a widely distributed, global clock, then the pipeline is said to be clocked. If, on the other hand, the parts of the pipeline act independently as and when local events permit, the pipeline is said to be event-driven. Stripped of any processing logic, a pipeline acts like a First-In First-Out (FIFO) queue. We are interested in an event-driven pipeline with or without internal processing.

# 2.2 The Basic Model

Before we discuss the specifics of the different protocols, we will develop a basic model for a request-acknowledge protocol [7]. The simplest interconnection circuit, a pipelining handshake circuit shown in Fig. 2.1, checks the input request signal  $R_{in}$  (the completion signal of computation block A) to see if the output datum

of block A is valid, and checks the feedback acknowledge  $A_{in}$  to see if block B is ready for a new input. This is important since block A might take longer to finish than block B, which might compute data more than once. This is known as "continual feeding". If the situation reverses, data at the input of block B will be overwritten. Such is a "run-away" condition.  $R_{out}$  controls the request signal to block B, indicating when block B should start evaluation.  $A_{out}$  controls the acknowledge signal to the interconnection block preceding block A, notifying block A when its output datum is transferred to block B.

# 2.3 The 4-cycle Request-acknowledge Protocol

The common four-phase handshake protocol works as follows. Assume that the four signals  $R_{in}$ ,  $R_{out}$ ,  $A_{in}$ , and  $A_{out}$  are initially at logic level 0 ( $R_{in}$ ,  $R_{out}$ ,  $A_{in}$ ,  $A_{out}$ ). When block A finishes its computation, it raises  $R_{in}(R_{in}^{+})$  to request for a data transfer to block B. Since  $A_{in}$ , is initially low, meaning that block B is ready to accept a new input, the handshake circuit raises  $A_{out}(A_{out}^{+})$  to tell block A that its output datum has been accepted.  $R_{in}$  can then be reset ( $R_{in}^{-}$ ). The handshake circuit then raises  $R_{out}(R_{out}^{+})$  to initiate the computation in block B. Eventually block B will complete its task and output a completion signal. This information is fed back through  $A_{in}(A_{in}^{+})$  so that  $R_{out}(R_{out}^{-})$  can be reset which will in turn reset  $A_{in}(A_{in}^{-})$  and complete the four-phase handshake loop. The four-phase handshake protocol always uses the rising transitions to initiate operation and the falling transitions to reset. The four-phase handshake protocol dictates that the sequence of signal transitions on the right hand side of the handshake circuit in Fig. 2.1 is always the iterative  $R_{out}^{+} --> A_{in}^{+} --> R_{out}^{-} --> A_{in}^{-}$  and on the left hand side  $R_{in}^{+} --> A_{out}^{+} -->$  $R_{in}^{-} --> A_{out}^{-}$ .

# 2.4 The Transition Signaling Conceptual Framework

Ivan Sutherland[8] proposed a different timing discipline, namely, the transition-signal conceptual framework for the design of complex computation systems. Sutherland employs the 2-cycle, or non-return-to-zero (NRZ) signaling scheme. This is the most energy efficient and least time consuming signaling scheme. In transition signaling we do not distinguish between rising or falling edge of a signal. This means that, in effect, all responses to transition signals are edge triggered, and are triggered on both rising and falling edges. This results in the fact that the absolute state of control signals have no meaning. They are evaluated with respect to other related signals.

Transition signaling circuits must be symmetric with respect to the high and low states of control signals, since both rising and falling edges have the same meaning. This symmetry of transition signaling is highly desirable because it conforms with the symmetry of CMOS circuits.

If a sender and a receiver communicate using transition signaling, there will be two control wires and many data wires between them. The data wires carry conventional high or low states. The sender places a data value on the data wires *and then* produces a transition (rising or falling, we make no distinction) on the request control line to indicate that valid data are available. The receiver accepts data *and then* produces an acknowledge transition to indicate that the data have been accepted. The three events, data change, request and acknowledge always occur in cyclic order (though the lengths of the different cycles can be different ).

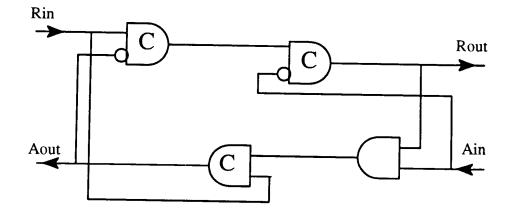

# 2.5 Event Logic and Muller-C Elements

Control circuits for the above request-acknowledge protocols are built out of modules that form various logical combinations of events. The exclusive OR (XOR) circuit acts as the OR element for events. When either input of an XOR circuit changes state, its output also changes state. Thus an event received on either the first input OR the second input of the XOR will produce an output event. For more than two inputs, XOR generalizes to parity; parity circuit acts as a multiple input OR for events.

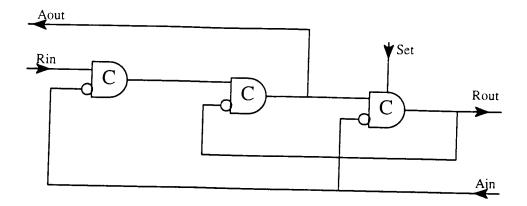

Figure 2.2 Muller-C elements for control of events.

The Muller-C element acts as the AND element for events. A two-input Celement implements the Boolean function C = AB + BC' + AC', where A and B are the two input signals, C' is the previous output signal, and C is the present output signal. The C-element has the property that the output signal will change when both inputs are of the same level; otherwise the output stays unchanged. Thus only after an event takes place on both its inputs does an event occur at a C-element's output. The C-element is one of the basic units in the early approaches to designing speed-independent circuits. The C-element generalizes easily to three or more inputs requiring that all of them reach a new logical state before copying the new state as output. We use the standard AND logic symbol with a large C inside to represent a Muller C-element that implements a logical AND for transition events, as illustrated in Fig. 2.2.

Although the absolute state of a transition signal does not matter, its state relative to other related signals does. Thus it is sometimes important to invert transition signals. We use 'bubbles' on inputs or outputs of logic symbols to represent such inversions, as illustrated in Fig. 2.2. Every loop around which events flow must contain an odd number of inversions. Such loops are, in effect, oscillators whose oscillations are coordinated with those of other loops by the actions of C-elements or other modules at loop junctions.

## 2.5.1 SR-Latches vs. C-Elements

In classical logic design, the Boolean function of an Set/Reset (SR)-latch is written as Q(n) = S + R/Q(n-1). Here S and R are some combinational functions of input signals, Q(n-1) is the previous output signal and / is used to denote active-low signals. Thus S and R cannot be high at the same time, since the condition S = R = 1would set the output Q undefined (a metastable condition) and represent a circuit hazard. This problem is usually circumvented by designing set-dominant (or resetdominant) SR -latches in which the output is set high (or reset low) whenever S (or R) is high. However, because of the assumed unbounded gate delays, there are situations in which the values of S and R cannot be predicted by the Boolean function. Hence the choice of set dominant SR-latch or reset dominant SR-latch becomes a function of gate delays.

Since logic delays are assumed to be finite but unbounded in speedindependent circuits, S and R may both become high with different gate delay assumptions. If we chose to abide by the orthodoxy of a pure speed-independent design, any logic implementation incorporating SR-latches cannot be truly speedindependent, as the mutual exclusion of S and R cannot be guaranteed through unbounded gate delays. C-elements do not have this problem and it has been proposed that speed-independent (and delay insensitive) circuits use only C-elements as memory elements. The functionality of an SR-latch is similar to a C-element with an inverter. Therefore C-elements can be used to replace SR-latches without any functional difference.

# 2.6 A 2-cycle FIFO

In Section 2.1, the basic concept of a event-driven pipeline was presented. Sutherland calls such a pipeline based on the transition-signaling framework - a *micropipeline*. It is from this name that we derive the "micro" part of the acronym MDF. The micro part of the name is appropriate, as a micropipeline consists of very simple circuitry, is useful in short lengths and is very suitable for layout in an integrated circuit. Also note that, when we look at general purpose computing structures, such a pipeline is used to implement the microinstructions as compared to a 'macro' instruction pipelined implementation. Before we look at the actual structure of a micropipeline, let us understand the logic required to control such a pipeline. A string of Muller-C elements interspersed with inverters is the only logic required to control the pipeline. In fact, the third form of Muller-C element shown in Fig. 2.2, is the kind that would be perfect for such a type of control. We can then view this circuit by examining the state of each C-element relative to the states of the predecessor and successor C-elements. Remembering the behavior of the C-elements under discussion, one can see that the control of each stage follows a very simple stage rule:

IF predecessor and successor differ in state THEN copy predecessor's state ELSE hold present state.

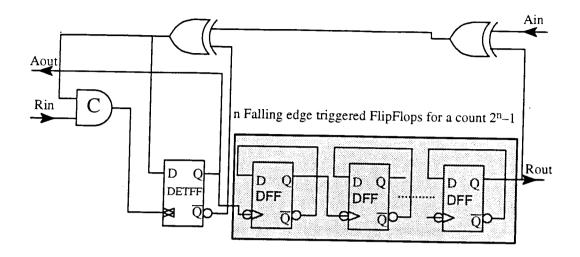

Let us now try to understand how a pipeline without any processing, i.e. a FIFO, could be built with such simple control logic. In Fig. 2.3, we illustrate the basic structure of a micropipeline. A set of event-controlled storage registers in series serves as its data path while a string of Muller C-elements serves as its control. This event controlled storage element is required to respond to both the rising and falling transitions. This can be achieved by using two latches side by side, one controlled by a control wire called "capture", and the other by another wire called "pass", which are activated alternately. In fact, in Chapter 4 we will show that this event-controlled register is in fact modeled as discussed above.

The reason the registers have been arranged to be driven from one end while their control signals are being sensed from the other is because the control signals for the register must be amplified to drive all the switches in the many storage elements involved. Since the wires that carry control signals are long, there is always some delay in controlling the register. The reader must note that, from here on, in all those figures that present both control and data signals, the control signals are denoted by dotted lines and the data path by either a thick line or a thin line.

Figure 2.3 The Structure of a Micropipeline.

# 2.7 A 4-cycle FIFO

In a similar discussion, a 4-cycle FIFO can be developed. But before that we need to understand what kind of control logic would be required. Using the protocol discussed in Section 2.3 and the event logic discussed in Section 2.5, we can obtain a very simple circuit for the event control of a 4-cycle pipeline/FIFO, as shown in Fig. 2.4. This circuit is similar to the one developed by Meng.

With the help of this event control logic and the concepts developed in Section 2.6 on micropipelines, we developed a similar pipeline for a 4-cycle implementation. A significant difference between the storage elements used in the two FIFOs is that the 4-cycle storage elements will respond only on the rising transitions, or if the level of the request input is high. As will be obvious later in this discussion, these storage elements were in fact modeled in a similar fashion as discussed above.

Figure 2.5 The Structure of a 4-cycle FIFO.

# 2.8 Some Interesting Observations

Naturally, data must propagate through an event-controlled pipeline faster than the control events propagate through its control. Sutherland assures this as follows. First the C-elements used in the control circuit are more complex than the storage element used in the data path, and hence inherently slower. Second, since each control stage of the control system must drive the many storage elements that hold a parallel word in each register, the control signals must be amplified to drive multiple loads. The amplification inevitably delays the control signals. Third, the layout of the circuit ensures that the zigzag path of the control signals has longer wires in it than those in the data path. If this can not be guaranteed, the request signal's arrival at the stage must be delayed by the computation time required by the current block.

Other suggestions are having the data path (i.e. the computation block) generate a completion signal. This completion signal can require considerable circuitry to implement. In Chapter 5, we will discuss a new logic family/topology at the transistor level that self-generates a completion signal.

The pipelines developed in the above 2-cycle and 4-cycle frameworks provide for a variety of pipeline processors. In fact, any micropipeline (we will now use it for both types of pipelines without copyright or loss of generality) with processing has combinatorial circuits placed between the storage registers. One can trade off the number of stages and the complexity of the intervening logic to obtain a suitable balance between latency and throughput rate. With less combinatorial logic between stages and more stages of storage, one obtains higher throughput rate at the cost of greater latency. This might entail greater hardware cost. In this discussion, we are going to make an attempt to compare these two protocols and the issues that arise thereof. It is intuitive that there is a possibility of greater performance possible in the 2-cycle framework, but at what cost? But before we can assess the trade-offs therein we need to know what kind of control circuits would be required. We need to develop a higher level abstraction or method for specifying algorithms. This is the topic of discussion in the next chapter.

# Chapter 3. DATA FLOW PROGRAM GRAPHS FOR DSP

## **3.0** Introduction

Digital signal processing (DSP) applications differ from general-purpose computation both in the nature of the algorithms and in the target hardware. The DSP algorithms usually involve a lesser degree of decision making. The target hardware is often dedicated to a particular algorithm, or at the most to a small class of algorithms, rather than being general purpose. They also have stiff cost/performance ratio requirements, especially in the case of real-time DSP. As mainstream computer science techniques can not be effectively employed, the DSP community usually designs its own microprocessors, languages, multiprocessor architectures and software.

DSP designers have been using "block-diagram languages" for high level specification. These languages have been nothing else but variations on the data flow representation of algorithms. Thus, a data-flow representation is very natural for the representation of DSP algorithms. Add to this the additional advantage of built in parallelism and concurrency, and we have a very simple and elegant method for specifying DSP algorithms.

In this chapter, we will try to highlight the major issues of concern. We will begin by explaining the basic concepts of data flow computing without regard to whether the the computation is general purpose, or application specific like DSP. We will then present a brief introduction to data flow program graphs. Finally, the issues concerning scheduling of data flow graphs for DSP will be briefly discussed.

# 3.1 The Data Flow Concept

For decades computers have been designed based on the control flow, more commonly known as the von Neumann model of computing. The corner stones of this philosophy are the program counters that are used to sequence the execution of instructions in a centralized control environment and the fact that data is passed between instructions via references to shared memory. Parallelism was restricted to the switching of a processor among separate processes and programmer-specified decomposition of a program into parallel instruction or data streams, to be processed by separate processors. Although in the last few years some work has been done in the field of parallel compilers to relieve the programmer of the tedium of partitioning the program into parallel processes, there are still many lacunae that need to be explored [10].

A major problem in a traditional multiprocessor system with a shared memory is memory interference. Given that a single processor usually tends to be memory bound, the addition of other processors attached to a shared memory provides only a limited gain (Amdahl's law!!). Local caches may have reduced the problem marginally, but it still remains a prickly problem, especially with the added consideration of memory integrity. Except for the advantages in the area of system availability, multiprocessor systems tend to have poorer cost/performance ratios than their uniprocessor system counterparts.

A second motivation for data flow architectures stems from properties of most current programming languages and the recognition that they mimic the underlying von Neumann computer organization. The organization is one of a passive storage (variable), a processing unit that performs state changes in the storage (assignment), and a control unit that controls the state of the processing unit by sending it sequentially through a stream of instructions (**control flow**) [11,12].

Data flow advocates and programming language theorists argue that these three fundamental ideas are artificial, foreign to the way that programs should be expressed. These ideas contribute to programming complexity. Thus current programming languages were derived not from the outside-in (i.e. from the programmer's viewpoint), but from the inside-out (i.e. heavily influenced by the organization of earlier stored program machines).

The concept of data flow discards these basic principles by eliminating the idea of instruction streams and control flow, eliminating the concept of memory as a passive repository for program variables (an exception being associative memory), and providing a means of taking advantage of opportunities for parallel processing within programs without requiring explicit directions from the programmer.

# 3.2 A Data Flow Language

In a data flow computing environment, instructions are activated by the availability of data tokens (i.e. instructions/statements are data-driven). An instruction (or statement) is considered to be enabled (capable of being executed) when

(1) a datum exists on each of its input ports and

(2) no datum exists on its output port.

When an instruction is executed, the data on its input ports disappear and a result appears on its output port. Programs are represented by connecting instructions in a directed graph (i.e., connecting an instruction's output port to another instruction's

input port ). Thus the order of instruction execution is controlled not by an instruction counter, but by the flow of data among instructions.

Control flow computers have synchronous computations performed using centralized control. Data flow computers are characterized by a passive examine stage. Instructions are examined to reveal the operand availability, upon which they are executed immediately if the functional units are available.

This data driven concept means asynchrony, which means that many instructions can be executed simultaneously and asynchronously. A high degree of implicit parallelism is expected in a data flow computer. Because there is no use of shared memory cells, data flow programs are free from side effects. In other words, a data flow operation is purely functional and produces no side effects such as the changes of a memory word. Operands are directly passed as tokens of values instead of as address variables. Data flow computations have no far-reaching effects. This locality of effect plus asynchrony and functionality makes them suitable for distributed implementation.

The language that will be discussed is basically a two-dimensional graphical language, which suits our purpose very well. The particular language to be examined is one proposed by Dennis [13]. Of course, there do exist data flow languages with the more familiar statement-oriented syntax, but they will not help illustrate the concept that will be discussed. In Dennis's language there are three major concepts:

#### **3.2.1 Processing elements**

A processing element is an operation that is enabled by the arrival of information on its input arcs and the absence of information on its output arc. The two categories of processing elements are *actors* and *links*. An actor is an operation with

one output arc and one or more input arcs. A LINK is an operation with one input arc and multiple output arcs [14].

# 3.2.2 Information

Information exists in the form of tokens (as we will see later, in our case it will be the transitions), which are transmitted over arcs and consumed and created by processing elements. The two basic types of information are *data values* (e.g. numerical values and *control or Boolean values* (e.g. true/false value). Note that at the circuit level the control values are also treated as data.

# 3.2.3 Arcs

An arc is an unidirectional path for information from one processing element to another. An arc can be either empty or contain a single token of information. The arc is the replacement for the traditional concepts of variables and storage. Because of the two classes of information, the arcs are classified as *data arcs* (denoted by solid lines here) and *control arcs* (denoted by dashed lines).

Fig. 3.1 illustrates the processing elements of the language. A LINK (or FORK) operation is enabled when a token appears on its single input arc, and all its output arcs are empty. On firing it distributes the input token to the output arcs. An OPERATOR actor normally has one or two input arcs. It is enabled for execution when data tokens are present on all input arcs (except for the MERGE actor ), and its output arc is empty. It absorbs the input tokens, performs some function across these

values, and places the result data token on its output arc. Typical OPERATOR actors are addition, subtraction, multiplication, negation, square root, and so on.

Figure 3.1 The Data Flow Links and Actors.

The **DECIDER actor (or PREDICATE, or JOIN)** is similar, except that it produces a Boolean or control result. It computes some PREDICATE across the data inputs, which produces a Boolean true or false value as a result. Typical PREDICATEs are equality, inequality, less than, and so on.

The remaining three actors have both data and control inputs. The **TRUE** actor is enabled when it has both a data token and a control token available as its inputs (and, its output arc is empty). Like all other elements, it absorbs its inputs when executed (fired). If the control value is true, the result is placed on the output arc; otherwise, no result is produced. Thus the TRUE actor will either pass its data input to the output arc, or it will simply absorb it. The **FALSE actor** is similar, except that a false control value instead of a true one causes the data to be passed to the output arc.

The **MERGE actor** is an exception in that its execution does not cause all the input tokens to be destroyed, and it does not require all input tokens to be present to become enabled. It is enabled

- when a true control token is present and a data token is present on the data arc labeled T, or

- when a false control token is present and a data token is present on the data arc labeled F.

- In both cases, the output arc must be empty.

If the control input is true then the data token on the T input arc is transmitted to the output arc. These two input tokens are destroyed but the token on the F data input is not destroyed, if present. The opposite is valid if the control input is false.

## 3.2.4 Motivation and advantages

Graphical representations of data flow graphs offer many advantages [15]. Besides, the fact that a mental image of the behavior of a program due to the *data* availability firing rule is much easier to understand, data flow programs are easily composable into larger programs. Also data flow programs prescribe only essential *data dependencies*. It is very easy to attribute a formal meaning to a program by using a graph. This meaning can take the form of an operational definition (i.e. defines a permissible sequence of operations) or a functional one (i.e. describes a single function independent of the execution model).

# 3.3 Scheduling of Data Flow Programs for DSP

As discussed in the introduction to this chapter, we are interested in adapting data flow graphs for DSP. Edward Lee and D. G. Messerchmitt of Berkeley suggest that the data flow techniques of general purpose computing are too expensive for DSP and more powerful than required [16, 17, 18, 19].

In this section, we will deal with the scheduling strategies for data flow graphs. Scheduling is integral to the efficient exploitation of the inherent concurrency of a data flow graph. We will consider only non-preemptive scheduling.

Scheduling involves three basic tasks:

(1) Assigning actors to processors,

(2) Ordering the actors on each processor, and

(3) Specifying their firing time.

Every data flow implementation must have these three components. Implementations may differ by when (compile time or run time) they are implemented. Complexity of scheduling strategy also affects implementation.

Four classes of scheduling can be defined on the basis of which tasks are done when. They are:

(a) *Fully Dynamic* : Actors are scheduled at run time (i.e. they are assigned to a processor only when all the input operands are available).

(b) *Static allocation* : An actor is assigned to a processor at compile time, and a local run time scheduler invokes actors assigned to the processor.

(c) *Self-timed* : The order in which the actors will fire is determined by the compiler. At run time, each processor waits for data to be available for the next actor in its ordered list, and then fires that actor. This is analogous to self-timed circuits.

(d) *Fully Static* : The exact firing time of the actors, and their assignment and ordering information are all determined by the compiler. This is analogous to synchronous circuits.

Note that the boundaries between the different classes are not rigid. But it is interesting to note that as we go from strategy (a) to strategy (d), the degree of data dependency decreases, which means the strategies become less complex and cheaper. as they do not require special hardware support. In the case of self-timed scheduling, some synchronization primitives like simple handshake mechanisms are required. In fact, when extended to multiprocessor systems, the handshaking resembles Hoare's concept of *communicating sequential processes* [20, 21].

But the class of algorithms that can exploit the advantages of strategies (c) and (d) also reduces. Little or no data dependency, as well as comparable execution times of the various actors, are important features of self-timed scheduling and fully static scheduling. Although self-timed scheduling is better than fully static scheduling in tolerating some variations, it is not very good at that. This is not a severe problem in the case of signal processing algorithms and scientific computations [22, 23], like floating point arithmetic [24]. As a result, it can be observed that a self-timed schedule can be a very good option.

The compiler requires more information about the actors in order to construct close-to-optimal schedules. A solution is having the compiler construct a fully static suboptimal schedule and then discard the information that is not required. Static allocation or assignment strategy requires only assignment information, while selftimed scheduling strategy requires both assignment and ordering information.

This gives rise to an important question - how are we to accomplish a fully static schedule for a self-timed scheduling strategy in the case of data dependencies like conditionals, recursion, and data-dependent iteration without losing out on the optimal strategies that would have been otherwise possible?

Considerable work has been done by Lee for synchronous data flow graphs, and by Meng for asynchronous data flow graphs at Berkeley under the guidance of Messerschmitt. For a detailed discussion, see the references in the bibliography. Here, we will present the different problems and discuss some of the suggested solutions and their effects.

#### 3.3.1 Recurrences

Figure 3.2 A data flow graph with a recurrence. Recurrences are expressed as directed loops and delays.

It is important to support recursion, or self-referential function calls. In fact, imperative languages implement recurrences and iteration in some combination. We will avoid the notion of "function calls". We can at least characterize some of the recurrences as feedback paths in data flow program graphs. Data flow models for iteration will be examined in a later section.

A schematic of a data flow graph with a recurrence is shown in Fig. 3.2. This graph is assumed to fire repeatedly. The feedback path has a *delay* represented by a diamond. This can be implemented by an initial token on the arc (in Chapter 4 we will show the design of an actor that we call **INIT actor**). This delay is not a unit time delay but a logical delay or separator. A necessary (but not sufficient) condition for avoiding deadlock is to have at least one delay in a directed graph.

Figure 3.3 A data flow graph with conditional assignment. Both f(x) and g(x) are evaluated, and only one of them is selected.

Conditionals in data flow graphs are harder to describe and schedule statically. Conditionals are constructed within one large grain actor, and concurrency within such actors is difficult to exploit. Hence instead of *conditional evaluation* we use *conditional assignment*. We now require a slight variation on the MERGE actor that we use. We have seen before that after a MERGE actor has fired it will not destroy all its input tokens. If we want to implement the functional expression (see Fig. 3.3)

$$y \le if(c)$$

then  $f(x)$  else  $g(x)$ ,

we need a MERGE in which all the input tokens are destroyed each time the actor fires. Let us call this new kind of MERGE a **MUX actor**. Hence, both f(x) and g(x)are computed each time and only one of the results will be used. This is justifiable only when the functions are simple (deep pipelining), or for hard real-time applications when one of the two subgraphs is simple. Otherwise, the cost of unnecessary computation might be excessive.

An alternative for an if-then-else structure might be the use of a SELECT actor so that a token 'x' can be routed to one of the two functions, depending on the value 'c'. The appropriate function fires, and its value is selected by the MERGE actor. This has been schematically shown in Fig. 3.4.

#### 3.3.3 Iterations

Iterations are of two types - manifest and data-dependent. Manifest iterations are of the type where we know the number of repetitions at compile time, and hence are independent of data. The others, as the name suggests, are data-dependent. They may be known before the iteration begins or after. Though manifest and datadependent iterations pose different problems for the compiler, the resultant additional actors required are the same. They are used in increasingly complex configurations in order to achieve some degree of static scheduling. The study of the problems with iterations required three more actors that were added to the four previously included. This will complete the set of data flow links

Figure 3.4 An alternative data flow graph for the expression y := if(c) then f(x) else g(x).

and actors for DSP applications. One of the actors that Lee suggests is called Last of N. It simply outputs the last of a series of N tokens, where N is a parameter of the

Figure 3.5 Data flow graphical representation of 6 additional actors.

actor. We call this, a little less euphemistically, a **COUNTER actor**. That is what it actually does - it counts N tokens and then lets only the last one through.

Another actor he suggests he calls **REPEAT actor**. It basically takes one input token and repeats it on the output N times. This can be implemented by using a FIFO and a COUNTER actor. A variation on this is required if we need to output the data in a serial fashion. We then require a parallel to serial shift register. We call this actor a **SHIFT actor**.

There are other actors that he suggests, like one that takes in one input token each time it fires, and outputs the last N tokens arrived. This can be built with a COUNTER actor and a N-deep buffer in a self-loop. Since this actor can be built by using other actors, it was not added to the list of links and actors.

Lee also suggest actors that he calls UPSAMPLE and DOWNSAMPLE. Both are variations on the COUNTER and REPEAT actors. Fig. 3.5 shows a graphical symbol for the 6 actors that have been added.

# **3.4** Some Interesting Observations

To the reader it would seem that, since all the additional actors can be constructed using the basic set, these actors are redundant. At this point, we will allude to a recent computer architecture related controversy - Complex Instruction Set Computers (CISC) versus Reduced Instruction Set Computers (RISC). The main motivation for RISC processors was not to minimize the size of the instruction set but to reduce it to the most relevant ones. Hence the authors feel that a more appropriate name would be Relevant Instruction Set Computers.

In the specific case of data flow graphs for DSP algorithms, we added these additional actors because of a high probability of their occurrence in such algorithms.

So, although the basic primitives have been increased the additional primitives are relevant and, hence, not unnecessary.

It is important to note that when we discuss the above actors, we are essentially interested in the control path, or, as we call it, the *distributed control path* (DCP). Although, the data path always exist along with most of the actors, its design is not under discussion here. Simple actors like the DECIDER actor and the OPERATOR have essentially similar control structure to a 'JOIN'. We call this structure a PREDICATE. Similarly, the control LINK and the data LINK, have essentially the same control structure and that of a 'FORK'. We will call this structure as a LINK.

## 3.5 Summary

In concluding the discussion on data flow graphs, we would like to emphasize that work still needs to be accomplished in terms of architectural development, compilers, etc. for self-timed data flow implementations to enable us to engage in fruitful activity as far as the design of programmable DSP processors. But it is definitely an interesting study to find out whether such an effort would pay off against using von Neumann based DSP processors.

A significant body of work has been developed in the last few years related to constructing a strong theoretical framework for the automatic design, development and testing of asynchronous circuits. In [25], A. P. W. Böhm presents a very good monograph on data flow computation. J. C. Ebergen [26] and E. Brunvand et. al. [27] discuss the automatic translation of programs into delay-insensitive circuits. A. J. Martin [28] investigates the compilation of communicating processes into delay-insensitive circuits.

T-A. Chu [29, 30, 31], T. Meng [32], C. J. Tan [33] discuss various methods of synthesizing self-timed circuits. Using trace theory for automatic verification of speed-independent circuits is discussed by D. L. Dill [34]. Dill along with Steven Novick of Stanford [35] discuss the same issue for self-timed circuits in Chapter 7 of Meng's book.

This chapter should enable the reader to understand the different actors required for an effective implementation of DSP algorithms. In the next chapter, we will discuss a hardware description language that allows us to define the functionality of the data path and the structure of the control path. Explicit specification of the data path is not required. Design energy can be concentrated in designing the DCP, and subsequently automating the design of the DCP.

# Chapter 4. MODELING OF DIGITAL CIRCUITS USING VHDL

## 4.0 Introduction

Once we had developed an understanding of the kind of event control circuits that would be required, the task was to design them. But it was important not to get bogged down by details. VHSIC (Very High Speed Integrated Circuit) Hardware Description Language (VHDL) provided a very nice solution to this problem. In this chapter, we will explain how VHDL provides a very good method of describing the structure and function of ICs. Also, looking at the future requirements of this project, it is envisaged that some form of a translator of data flow program graphs into VHDL specifications will be needed. This form of automation would relieve the designer from worrying about all the details (for e.g., the design of the data path), especially in the infancy stage of a new design. These, of course, are the advantages that particularly apply to this project. In the next section, the basic advantages of VHDL will be specified.

This chapter is not intended as a tutorial on the many varied aspects of VHDL. References [36, 37, 38, 39, 40, 41] are provided in the bibliography that will accomplish that. Here we present the reader with some of the basic tenets of this new electronic circuit design philosophy and the approach that was taken by us in this project. This project was developed using View*logic*® VHDL [42].

## 4.1 Origins of VHDL

As has been stated above, VHDL is a language for describing digital electronic systems. It owes its origin to the United States Government's Very High Speed Integrated Circuit (VHSIC) program, initiated in 1980. VHDL has now been adopted by the IEEE as a standard.

VHDL is designed to satisfy a number of needs in the design process. The main among them are:

(1) It allows the description of structure in an hierarchical form.

(2) It allows the specification of the function (or, as is said in VHDL jargon,

behavior) of designs using familiar programming language forms.

(3) It allows a design to be simulated before being manufactured. It allows evaluation of the alternatives without expensive hardware prototyping.

# 4.2 Describing Structure

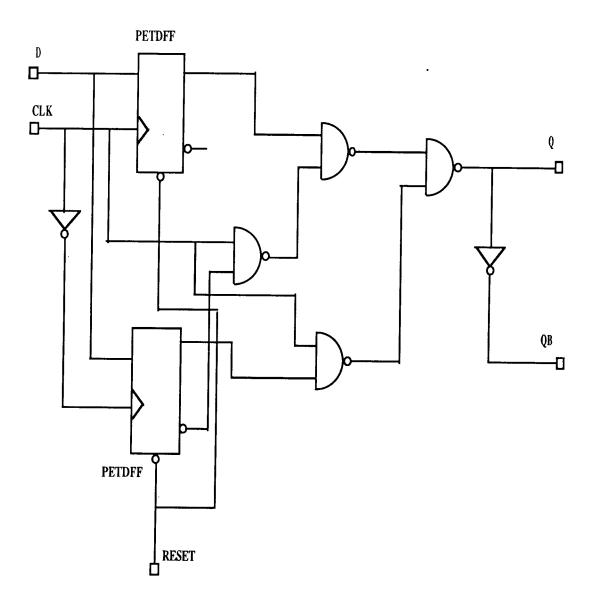

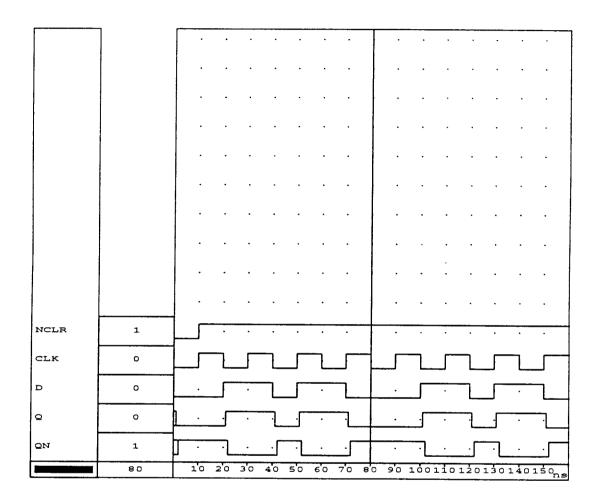

A digital electronic system can be described as a module with inputs and/or outputs. The electrical values on the outputs are some function of the values on the inputs. Fig. 4.1 shows a gate/flip-flop level circuit diagram of a double-edge triggered D flip-flop (DETDFF). Fig 4.2 shows the corresponding VHDL structural description. The module DETDFF has three inputs - D, CLK, RESET - and two outputs - Q, QB. Note that the outputs have been specified also as inputs because of the structure of the flip-flop. Using VHDL terminology, we call the module DETDFF a design **entity**, and the inputs and outputs are called **ports**.

One way of describing the function of a module is to describe how it is composed of sub-modules. Each of the sub-modules is an **instance** of some entity, such as PETDFF (positive-edge triggered flip-flop), NAND2 (2-input NAND gate), etc. The ports of the instances are connected using **signals**. This kind of a description is called a **structural** description. Note that each of the entities might also have a structural description, as can be seen in the next chapter. On the other hand, the entities can all be **behavioral** descriptions (as discussed in the next section). A mix of both types of descriptions is also possible.

Figure 4.1 Gate level schematic of a double-edge triggered flip-flop.

```

-- VHDL structural model for a double-edge triggered D-FF with clear/reset

entity DSTRUCT is

generic (DELAY : time := 5 ns);

port (D, CLK, RESET: in vlbit;

Q, QB: inout vlbit);

end DSTRUCT:

architecture STRUCTURAL of DSTRUCT is

signal Z1, Z2, Z3, Z4, Z5, Z6, Z7, Z8: vlbit; -- internal signals

signal DUMMY: vlbit;

-- component declaration for model NOT1

-- matches NOT1 entity declaration

component NOT1

generic ( TPLH: time := 1 ns;

TPHL: time := 1 ns);

port ( signal QN: out vlbit;

signal A: in vlbit);

end component;

component NAND2

generic (TPLH: time := 1 ns;

TPHL: time := 1 ns);

port (QN: out vlbit;

A, B: in vlbit);

end component;

component PETDFF

generic (DELAY : time := 2 ns);

port (D, CLK, nCLR: in vlbit;

Q, QN: inout vlbit);

end component;

-- 8 component instantiations define the model "structural".

begin

U1: NOT1

port map (Z1, CLK);

U2: PETDFF

port map (D, CLK, RESET, Z2, DUMMY);

U3: PETDFF

port map (D, Z1, RESET, Z3, Z4);

U4: NAND2

port map (Z5, CLK, Z4);

U5: NAND2

port map (Z6, Z2, Z5);

U6: NAND2

port map (Z7, Z3, CLK);

U7: NAND2

port map (Z8, Z6, Z7);

U8: NOT1

port map (QB, Z8);

Q <= Z8;

end STRUCTURAL;

```

Figure 4.2 Structural description of a double-edge triggered flip-flop.

## 4.3 Describing function

In many cases, it is not appropriate to describe a module structurally. One such case is a module that is at the bottom of the hierarchy of some other structural description. For example, if you are designing a system using IC packages bought from a shop, you do not need to specify them structurally. In such cases, a description of the function performed by the module is required, without reference to its actual internal

```

-- VHDL behavioral model for a double-edge triggered D-FF with clear/reset

entity DETDFF is

generic (DELAY : time := 2 ns);

port(D, CLK, nCLR: in vlbit;

Q, QN: out vlbit);

end DETDFF;

architecture BEHAVIOURAL of DETDFF is

begin

P1: process

begin

if nCLR = '0' then

Q <= '0' after 1 ns;

QN \ll '1' after 2 ns;

end if;

wait until pchanging(nCLR) or pchanging(CLK);

if nCLR = '0' then

Q <= '0' after 1 ns;

QN \ll '1' after 2 ns;

else

if nCLR = '1' then

if pchanging(CLK) then

Q <= D after 1 ns;

QN <= not(D) after 2 ns;

end if;

else

Q \leq 'X' after 1 ns;

QN \ll X' after 2 ns;

end if;

end if;

end process;

end BEHAVIOURAL;

```

structure. Such a description is called a **functional** or **behavioral** description. Fig. 4.3 shows such a description of a double-edge triggered flip-flop.