#### AN ABSTRACT OF THE THESIS OF

David Wei Chen for the <u>Master of Science</u> (Degree) in <u>Electrical and Electronics Engineering</u> (Major) presented on <u>J4</u>, 1967 (Date) Title: <u>A MOSFET INTEGRATED CIRCUIT SHIFT REGISTER</u> Redacted for Privacy

Abstract approved: James C. Looney

This paper is concerned with the design of a 21-bit metal-oxide-semiconductor field-effect transistor (MOSFET) integrated circuit static shift register.

This circuit consists of three separate 1, 4, and 16-bit static shift registers constructed on a single monolithic chip, each with independent input and output terminals.

Type D flip-flops are used to implement each bit of delay, enabling data to be stored indefinitely between clock pulses.

This design requires only one power supply and one external clock. Three clocks are generated internally. By appropriate connections, 1 bit, 4 bits, 5 bits, 16 bits, 17 bits, 20 bits and 21 bits may be obtained.

The circuit operates between DC and 800 KHz clock rates. It consists of 162 devices on a chip size of 62 mils x 47 mils.

#### A MOSFET INTEGRATED CIRCUIT SHIFT REGISTER

by

David Wei Chen

A THESIS

submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Master of Science

June 1969

**APPROVED:**

## **Redacted for Privacy**

Associate Professor of Electrical and Electronics Engineering in charge of major

## **Redacted for Privacy**

Head of Department of Electrical and Electronics Engineering

# **Redacted for Privacy**

Dean of Graduate School

Date thesis is presented f/an 24, 1969

Typed by Erma McClanathan for David Wei Chen

#### ACKNOWLEDGMENT

I wish to extend my sincere appreciation to Professor James C. Looney, major professor, and Mr. Steven T. Ou, senior engineer at Texas Instruments, Inc., for their invaluable help and guidance throughout this study.

My appreciation also goes to Dr. Clinton Kuo, senior engineer, Mr. James Doherty and Mr. David Leonard, MOS design engineers at Texas Instruments, Inc., for reviewing the manuscript and for providing many helpful suggestions.

## TABLE OF CONTENTS

| Chapter |                                                    | Page                |

|---------|----------------------------------------------------|---------------------|

| I.      | INTRODUCTION                                       | 1                   |

| II.     | THEORETICAL ANALYSIS                               | 2                   |

|         | <ul> <li>a. MOSFET Characteristics</li></ul>       | 2<br>4<br>7         |

|         | (iii) Capacitance                                  | 8                   |

|         | <ul> <li>b. MOSFET Inverter</li></ul>              | 9<br>13<br>16<br>18 |

|         | <pre>c. Transient Response</pre>                   | 18<br>18<br>22      |

|         | d. Static Shift Register                           | 25                  |

| III.    | DESIGN OF A 21-BIT MOSFET STATIC SHIFT<br>REGISTER | 28                  |

|         | a. Output Buffer and Last Bit                      | 32                  |

|         | b. Next to Last Bit                                | 37                  |

|         | c. Internal Bit and First Bit                      | 39                  |

| ·       | d. Clock Generator                                 | 40                  |

| IV.     | EXPERIMENTAL RESULTS                               | 44                  |

|         | a. Design                                          | 44                  |

|         | b. Electrical Characteristics                      | 57                  |

| ۷.      | CONCLUSIONS                                        | 66                  |

|         | BIBLIOGRAPHY                                       | 67                  |

## LIST OF FIGURES

| Figure |                                                                                                                | Page |

|--------|----------------------------------------------------------------------------------------------------------------|------|

| 1.     | P-channel MOSFET                                                                                               | 3    |

| 2.     | Active Region of Operation for the MOSFET                                                                      | 5    |

| 3.     | A Typical MOSFET Inverter Circuit with a<br>MOSFET as a Load Resistor                                          | 5    |

| 4.     | Drain Characteristics of MOSFET Inverter<br>with Load Line                                                     | 11   |

| 5.     | Transfer Characteristics of MOSFET Inverter<br>with a Load Resistor                                            | 11   |

| 6.     | The Direction of Current Flow in a MOSFET<br>Inverter                                                          | 12   |

| 7.     | The Direction of Current Flow in a MOSFET<br>Load Device                                                       | 12   |

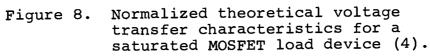

| 8.     | Normalized Theoretical Voltage Transfer<br>Characteristics for a Saturated MOSFET<br>Load Device               | 15   |

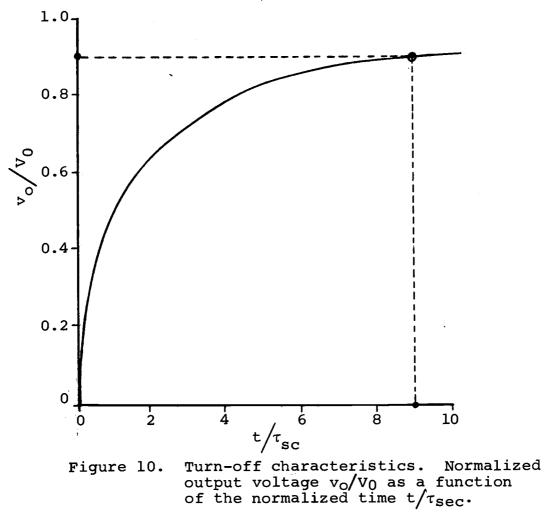

| 9.     | Turn-off Case of a MOSFET Inverter                                                                             | 19   |

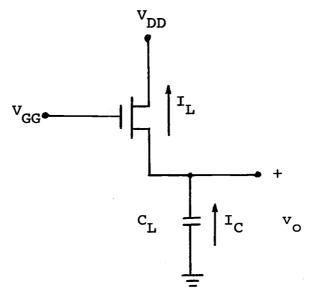

| 10.    | Turn-off Characteristics. Normalized Output Voltage $v_0/V_0$ as a Function of the Normalized Time $t/\tau$ sc | 19   |

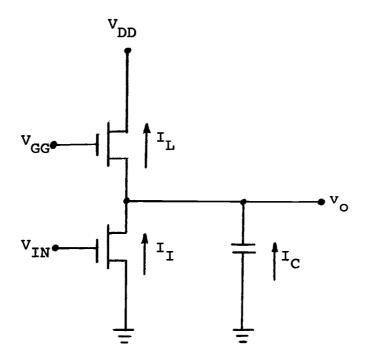

| 11.    | Turn-on Case of a MOSFET Inverter                                                                              | 23   |

| 12.    | Static Shift Register with Clock Waveforms<br>Shown as a Timing Reference                                      | 26   |

| 13.    | Logic Block Diagram of 21-bit Static Shift<br>Register                                                         | 29   |

| 14.    | Circuit Diagram of Output Buffer and Last Bit.                                                                 | 33   |

| 15.    | Circuit Diagram of 21-bit Static Shift<br>Register                                                             | 38   |

| 16.    | Circuit Diagram of Internal Clock Generator<br>with Timing Diagram of the Four Clock Phase                     | 41   |

#### Figure

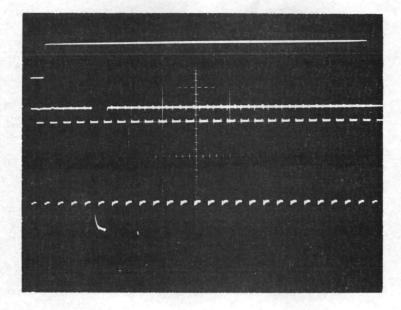

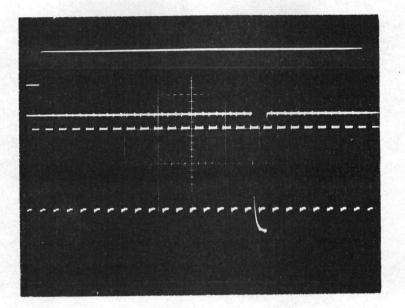

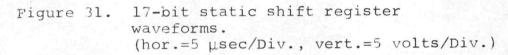

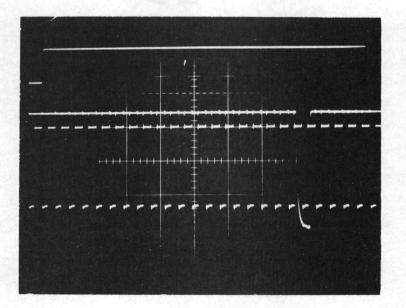

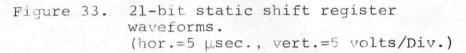

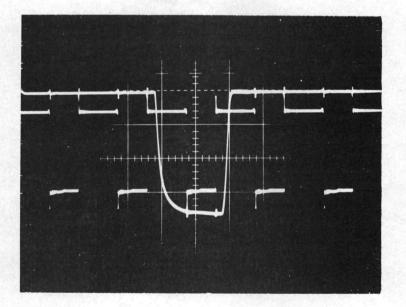

#### Basic Cell of First Bit of 4-bit Static Shift 17. Register and 16-bit Static Shift Register..... 47 Basic Cell of Second Bit of 4-bit Static Shift 18. 48 Register and 16-bit Static Shift Register..... Basic Cell of Next to Last Bit of 4-bit Static 19. Shift Register and 16-bit Static Shift 49 Register..... Basic Cell of Last Bit of 4-bit Static Shift 20. Register and 16-bit Static Shift Register..... 50 Basic Cell of Last Bit of 1-bit Static Shift 21. 51 Register..... Basic Cell of Output Push-pull Buffer..... 52 22. Basic Cell of Clock Generator..... 53 23. Physical Layout of 21-bit Static Shift 24. 54 Register..... Connection Diagram of 21-bit Static Shift 25. 56 Register..... Typical Timing Diagram of 21-bit Static 26. 60 Shift Register..... 1-bit Static Shift Register Waveforms..... 61 27. 4-bit Static Shift Register Waveforms..... 61 28. 62 5-bit Static Shift Register Waveforms..... 29. 62 16-bit Static Shift Register Waveforms..... 30. 17-bit Static Shift Register Waveforms..... 63 31. 63 32. 20-bit Static Shift Register Waveforms..... 21-bit Static Shift Register Waveforms..... 64 33. 34. Rise and Fall Time of the Output Wave 64 with Clock..... Linear Regression Line of Best Fit to the Data 35. for Power Consumption Versus Drain Supply Voltage..... 65

Page

## LIST OF TABLES

| Table |                                            | Page |

|-------|--------------------------------------------|------|

| I.    | Expressions for $I_{sc}$ , m, and $V_0$    | 18   |

| II.   | W/L Ratios of 21-bit Static Shift Register | 45   |

.

#### A MOSFET INTEGRATED CIRCUIT SHIFT REGISTER

#### I. INTRODUCTION

Metal-oxide-semiconductor field-effect transistor (MOSFET) shift registers are at present the most popular MOSFET digital integrated circuit. They offer large bit capacities with attendant advantages of small size, low power consumption, and low cost as compared to other shift register devices. In addition to replacing existing shift registers in many applications they can be used to perform functions that were not practical with conventional components. High capacity digital delay lines and recirculating memories are among the most obvious applications. Industrial uses involving serial data transmission and storage can also benefit from the utilization of MOSFET shift registers.

This paper is intended to present the theoretical analysis, design methods, and results of the design of a 21-bit MOSFET static shift register.

#### **II. THEORETICAL ANALYSIS**

#### a. MOSFET Characteristics

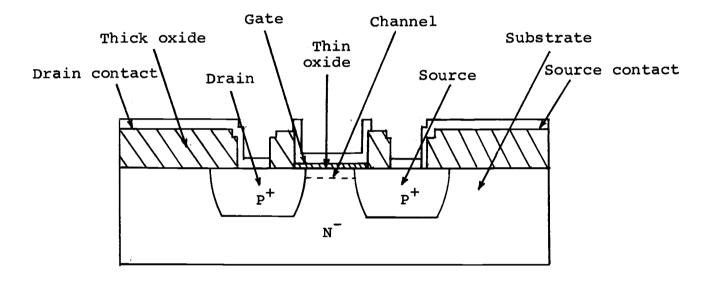

The basic structure of a typical p-channel MOSFET is shown in Figure 1. The substrate is a chip of N-type silicon which serves as the supporting structure for the device. The two p<sup>+</sup> regions, called the source and drain, respectively, are obtained by diffusing two wells of boron impurity into the substrate. In operation, these regions are connected by an induced p region known as the "channel."

The surface of the silicon is covered by a protective layer of silicon oxide formed during the silicon planar process. The gate, which is the control element of the MOSFET, consists of a layer of aluminum covering the surface between the source and drain. It is electrically insulated from the source and drain by the oxide, which is much thinner in this region than elsewhere and is therefore called the "thin-oxide" region to distinguish it from the surrounding "thick-oxide" regions. Aluminum contacts to the source and drain are provided.

If the gate, source, and substrate are grounded and a negative voltage is applied to the drain, no current will flow between source and drain, since the source and drain are isolated from each other by the reverse-biased drainto-substrate p-n junction. If a voltage more negative than a certain threshold value,  $V_{\rm m}$ , is applied to the gate, the

2

Figure 1. P-channel MOSFET.

surface of the N-type silicon "inverts," becoming p-type. This inverted region, called the "channel," connects the source and drain, providing a path for conduction of charge carriers between them.

The type of channel is determined classically by the type of majority carrier in the channel, and the mode of operation is related to the state of the channel at zero gate bias. If the channel must be formed before conduction can occur, it is called "enhancement-mode." A P-channel enhancement-mode MOSFET structure is assumed throughout this paper.

A useful feature of the MOSFET is that the gate-tosource capacitance can be used as a temporary memory storage element. Thus even if the gate supply is temporarily removed, the voltage remains stored on the gate.

#### (i) Drain Current

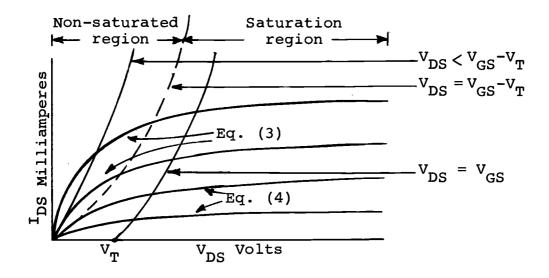

The active region of operation for the MOSFET is divided into two parts shown in Figure 2: the non-saturation region and the saturation region. The theoretical drain current expressions in each of these regions are given as follows (4):

$$\begin{split} \mathbf{I}_{\mathrm{D}} &= \frac{\overline{\mu}_{\mathrm{p}} \varepsilon_{\mathrm{ox}}}{2 t_{\mathrm{ox}}} \frac{W}{\mathrm{L}} \left[ 2 \left( \mathbf{V}_{\mathrm{GS}} - \mathbf{V}_{\mathrm{T}} \right) \mathbf{V}_{\mathrm{DS}} - \mathbf{V}_{\mathrm{DS}}^{2} \right], \\ \left| \mathbf{V}_{\mathrm{GS}} - \mathbf{V}_{\mathrm{T}} \right| &\geq \left| \mathbf{V}_{\mathrm{DS}} \right| \quad (\text{non-saturated region}) \end{split}$$

Figure 2. Active region of operation for the MOSFET.

Figure 3. A typical MOSFET inverter circuit with a MOSFET as a load resistor.

$$\begin{split} \mathbf{I}_{\mathrm{D}} &= \frac{\bar{\mu}_{\mathrm{p}} \in \mathbf{ox}}{2 t_{\mathrm{ox}}} \begin{bmatrix} \mathbf{W} \\ \mathbf{L} & \left( \mathbf{V}_{\mathrm{GS}} - \mathbf{V}_{\mathrm{T}} \right)^{2} \end{bmatrix}, \\ & \left| \mathbf{V}_{\mathrm{GS}} - \mathbf{V}_{\mathrm{T}} \right| \stackrel{\leq}{=} \left| \mathbf{V}_{\mathrm{DS}} \right| \quad (\text{saturated region}) \; . \end{split}$$

Where:

- $\frac{\mu}{p}$  is the average surface mobility of holes in the channel. 185  $\frac{cm^2}{v-sec}$  is typical for (111) material (13).

- $\epsilon_{\text{ox}}$  is the dielectric constant of the oxide layer. 3.38 x  $10^{-13} \frac{\text{farad}}{\text{cm}}$  is the value used here.

- t<sub>ox</sub> is the thickness of the oxide under the gate, typically 1200Å.

- W is the width of the channel.

- L is the length of the channel in the direction of current flow.

- $\boldsymbol{V}_{_{\mathbf{C}}\mathbf{S}}$  is the voltage from gate to source.

- $V_{\boldsymbol{\pi}}$  is the threshold voltage.

- $V_{\rm DS}$  is the voltage from drain to source.

To simplify these equations, it is convenient to define two new parameters, K and K', as follows:

$$K = K' \frac{W}{L}$$

, and (1)

$$\mathbf{K}' = \frac{\bar{\mu}_{\mathbf{p}} \epsilon_{\mathbf{ox}}}{2t_{\mathbf{ox}}} .$$

(2)

The drain current expressions become

$$I_{D} = K \left[ 2 (V_{GS} - V_{T}) V_{DS} - V_{DS}^{2} \right]$$

for  $\left| V_{GS} - V_{T} \right| \geq \left| V_{DS} \right|$ , and

$$I_{D} = K \left[ V_{GS} - V_{T} \right]^{2}$$

for  $\left| V_{GS} - V_{T} \right| \leq \left| V_{DS} \right|$ .

$$(3)$$

The parameter K is fixed by the process; it is not a design variable. The parameter K, on the other hand, is determined by the device topology. A typical value of K' for normal processing is  $2.6 \frac{\mu mhos}{volt}$ .

Theoretical drain characteristics can be determined from the equations. The fact that the characteristics of the device depend upon the ratio W/L is of major importance in the procedures for design of MOSFET circuits.

## (ii) Conductance and Turn-on Resistance

Normally the parameter of transconductance is determined in the active operating region of the device, which is the saturation region. In this region it can be evaluated from the theoretical current expressions:

$$g_{m} = \frac{\partial I_{D}}{\partial V_{G}} \bigg|_{V_{DS}} = 2K \bigg[ V_{GS} - V_{T} \bigg].$$

(5)

The theoretical expression for  $g_m$  shows that this parameter is directly proportional to the ratio of W/L and also to the voltage ( $V_{GS}-V_T$ ).

Another parameter which is of interest in switching

applications is the resistance  $R_{on}$  of the device when it is turned on and operating in the non-saturated region. This is defined as

$$R_{on} = \frac{\partial V_{D}}{\partial I_{D}} \bigg|_{V_{GS}} = \frac{1}{\kappa \left[2 \left(V_{GS} - V_{T}\right) - 2V_{DS}\right]}.$$

Since the current curves are nearly linear over much of the non-saturated region, this value can be approximated by the value at the origin (i.e., as  $V_{\rm DS}$  goes to 0), giving

$$R_{on} \approx \frac{1}{2K(V_{GS} - V_{T})} = \frac{1}{g_{m}} .$$

(6)

#### (iii) Capacitance

There are two kinds of capacitance associated with the MOSFET: intrinsic and parasitic capacitance.

The intrinsic capacitance is due to the charge stored on the gate and in the channel of the device. It is defined as the total value of the gate-oxide-silicon parallel plate capacitance. It depends upon the oxide thickness, and is given by the expression (4):

$$C_{o} = \frac{c_{oxide}}{t_{oxide}}$$

(area of gate). (7)

For an oxide thickness of 1200A

$$C_0 = 0.19 \frac{\text{pf}}{\text{mil}^2}$$

.

The parasitic capacitances fall into two areas: The junction capacitance which is related to the back-bias diffused junctions of the drain and source, and the overlap capacitance due to the gate metal overlapping into the drain and source areas. Junction capacitance is dependent on the amount of reverse bias and is found to be given approximately by the formula

$$C = \frac{0.08}{\sqrt[3]{0.6 + V_R}} \text{ pf/mil}^2 , \qquad (8)$$

where  $V_R$  is the amount of the reverse bias voltage (13). 0.05pf/mil<sup>2</sup> is the average value of parasitic junction capacitance used here. A value of 0.19pf/mil<sup>2</sup> is used here for the parasitic overlap capacitance.

## b. MOSFET Inverter

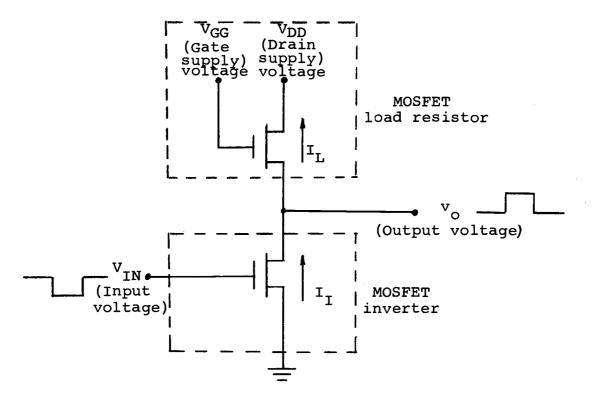

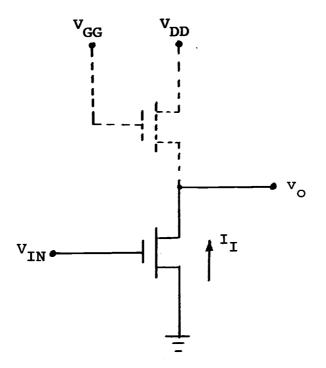

A typical MOSFET inverter circuit with a MOSFET as a load resistor is shown in Figure 3 (page 5). The circuit is normally operated with the drain tied to a negative voltage through the load resistor and the source lead grounded. Application of a negative voltage to the gate in excess of  $V_{\rm T}$  turns the device on and pulls the output voltage from  $V_{\rm DD}$  to ground, thereby causing a simple inversion at the output.

The theoretical expression for the voltage transfer characteristics of a MOSFET inverter device and its associated load will be developed.

The analysis will be done for two different types of loads: (1) a MOSFET device biased in the saturated mode; and (2) a MOSFET device biased in the non-saturated mode. The method is outlined below.

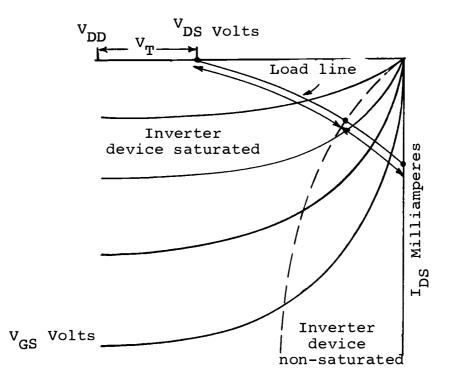

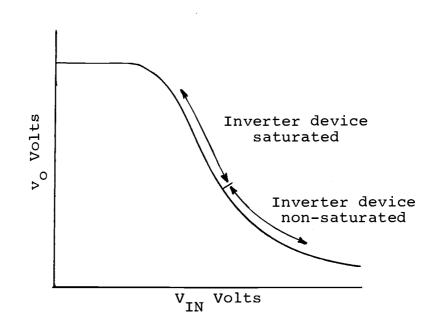

(1) Write the equation for current in the inverter device. Since the inverter device will be in a saturated condition when the input voltage is small, and will enter a non-saturated condition as the input voltage increases, this step will require two equations. As a result, the analysis must be done in two parts to include both inverter conditions. This is illustrated in Figure 4 and Figure 5.

(2) Write the equation for the current in the load.

(3) Equate the current in the inverter device to the current in the load, since the current expressions will be functions only of the device parameters, the bias conditions, the input voltage, and the output voltage; the resulting equation will contain the voltage transfer characteristics.

(4) Normalize the output voltage and input voltage in these equations to the off-level output voltage.

(5) Calculate values and plot the transfer curves.

First consider the inverter shown in Figure 6. From the figure it is clear that

$$V_{GS} = V_{IN}$$

, and (9)

$$V_{\rm DS} = V_{\rm O} \quad . \tag{10}$$

The theoretical expression for the current in the inverter can be found by substituting equations (9) and (10) into equations (3) and (4), as follows:

Figure 4. Drain characteristics of MOSFET inverter with load line.

Figure 5. Transfer characteristic of MOSFET inverter with a load resistor.

Figure 6. The direction of current flow in a MOSFET inverter.

Figure 7. The direction of current flow in a MOSFET load device.

$$I_{I} = K_{I} (V_{in} - V_{T})^{2}$$

(11)

for

$$|V_{in} - V_{T}| \leq |v_{o}|$$

(saturated region), and

$I_{I} = K_{I} \left[ 2(V_{in} - V_{T})v_{o} - v_{o}^{2} \right]$  (12)

for  $|V_{in} - V_{T}| \geq |v_{o}|$  (non-saturated region).

## (i) Saturated MOSFET Load Device

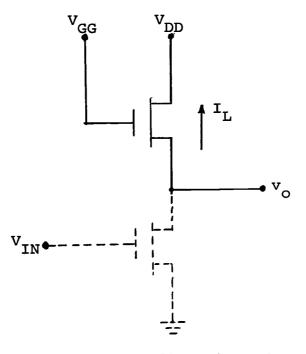

Consider the case where a saturated MOSFET device is used as the load for the MOSFET inverter as shown in Figure 7 (page 12).

In order to insure saturation of the load device, the biasing must satisfy the condition that

$\left| \mathbf{V}_{\rm GG} - \mathbf{V}_{\rm T} \right| \leq \left| \mathbf{V}_{\rm DD} \right|.$ From Figure 7,

$$V_{GS} = V_{GG} - V_{O}, \text{ and}$$

(13)

$$V_{\rm DS} = V_{\rm DD} - V_{\rm O} \qquad (14)$$

The theoretical expression for the current in the saturated device can be found by substituting (13) and (14) into equation (4), then

$$I_{L} = K_{L} \left[ (V_{GG} - V_{O}) - V_{T} \right]^{2} .$$

(15)

Setting  $I_L = I_I$  results in the equations:

$$K_{\rm L} \left[ (V_{\rm GG} - V_{\rm O}) - V_{\rm T} \right]^2 = K_{\rm I} (V_{\rm in} - V_{\rm T})^2$$

(16)

for

$$|v_{in} - v_{T}| \leq |v_{o}|$$

, and

$$K_{L} \left[ (v_{GG} - v_{o}) - v_{T} \right]^{2} = K_{I} \left[ 2 (v_{in} - v_{T}) v_{o} - v_{o}^{2} \right]$$

(17)

for  $|v_{in} - v_{T}| \geq |v_{o}|$ .

If  $v_0$  and  $(v_{in} - v_T)$  are normalized to  $(v_{GG} - v_T)$  and the terms rearranged, equations (16) and (17) become

$$\left(1 - \frac{\mathbf{v}_{O}}{\mathbf{v}_{GG} - \mathbf{v}_{T}}\right)^{2} = \frac{\mathbf{K}_{I}}{\mathbf{K}_{L}} \left(\frac{\mathbf{v}_{in} - \mathbf{v}_{T}}{\mathbf{v}_{GG} - \mathbf{v}_{T}}\right)^{2}$$

(18)

$$\begin{aligned} & \text{for} \left| \left| \frac{\mathbf{v}_{\text{in}} - \mathbf{v}_{\text{T}}}{\mathbf{v}_{\text{GG}} - \mathbf{v}_{\text{T}}} \right| \leq \left| \frac{\mathbf{v}_{\text{O}}}{\mathbf{v}_{\text{GG}} - \mathbf{v}_{\text{T}}} \right|, \text{ and} \\ & \left( 1 - \frac{\mathbf{v}_{\text{O}}}{\mathbf{v}_{\text{GG}} - \mathbf{v}_{\text{T}}} \right)^2 = \frac{\mathbf{K}_{\text{I}}}{\mathbf{K}_{\text{L}}} \left[ 2 \left( \frac{\mathbf{v}_{\text{in}} - \mathbf{v}_{\text{T}}}{\mathbf{v}_{\text{GG}} - \mathbf{v}_{\text{T}}} \right) \left( \frac{\mathbf{v}_{\text{O}}}{\mathbf{v}_{\text{GG}} - \mathbf{v}_{\text{T}}} \right) - \left( \frac{\mathbf{v}_{\text{O}}}{\mathbf{v}_{\text{GG}} - \mathbf{v}_{\text{T}}} \right)^2 \right] \\ & \text{for} \left| \left| \frac{\mathbf{v}_{\text{in}} - \mathbf{v}_{\text{T}}}{\mathbf{v}_{\text{GG}} - \mathbf{v}_{\text{T}}} \right| \geq \left| \frac{\mathbf{v}_{\text{O}}}{\mathbf{v}_{\text{GG}} - \mathbf{v}_{\text{T}}} \right|. \end{aligned}$$

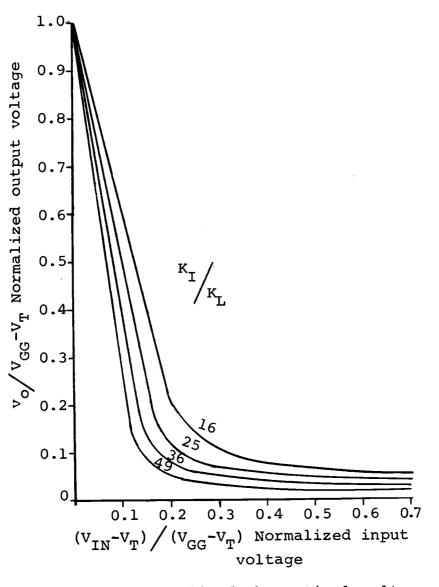

For a given value of the coefficient  $K_{I}/K_{L}$ , the curve of normalized output voltage  $v_{o}/(V_{GG}-V_{T})$  versus normalized input voltage  $(V_{in}-V_{T})/(V_{GG}-V_{T})$  can be calculated using equations (18) and (19). These curves are shown for various values of parameter  $K_{I}/K_{L}$  in Figure 8.

Note that decreasing the W/L ratio of the load increases the value of  $K_{\rm I}/K_{\rm L}$  and that this has the same effect on the transfer characteristics as increasing the load resistance -- a steeper slope and a lower final value. It is also important to realize that the Off-level voltage ( $V_{\rm GG}-V_{\rm T}$ ) is different for different values of  $V_{\rm GG}$ . The only saturated load devices normally used have gate and drain connected together so that  $V_{\rm GG} = V_{\rm DD}$ .

#### (ii) Non-saturated MOSFET Load Device

Consider the case where a non-saturated MOSFET device is used as the load on the MOSFET inverter device. To insure that the load device is not saturated, the biasing must satisfy the condition  $|V_{GG}-V_T| \ge |V_{DD}|$ . The theoretical expression for the current in the non-saturated load device can be found by substituting equations (13) and (14) into equation (3) as follows:

$$I_{L} = K_{L} \left[ 2 (V_{GG} - V_{O} - V_{T}) (V_{DD} - V_{O}) - (V_{DD} - V_{O})^{2} \right].$$

(20)

Equation (20) can be rewritten:

$$\begin{split} \mathbf{I}_{L} &= K_{L} \left( \begin{bmatrix} V_{DD} - v_{o} \end{bmatrix} \begin{bmatrix} 2 & (V_{GG} - V_{T}) - V_{DD} - v_{o} \end{bmatrix} \right) \quad (21) \\ &= K_{L} \begin{bmatrix} 2 & (V_{GG} - V_{T}) - V_{DD} \end{bmatrix} \left( \begin{bmatrix} V_{DD} - v_{o} \end{bmatrix} \begin{bmatrix} 1 - \frac{v_{o}}{2 & (V_{GG} - V_{T}) - V_{DD}} \end{bmatrix} \right) \\ &= K_{L} & V_{DD}^{2} \frac{\left[ 2 & (V_{GG} - V_{T}) - V_{DD} \right]}{V_{DD}} \\ & \left( \begin{bmatrix} 1 & -\frac{v_{o}}{v_{DD}} \end{bmatrix} \begin{bmatrix} 1 & -\frac{v_{DD}}{2 & (V_{GG} - V_{T}) - V_{DD}} & \frac{v_{o}}{v_{DD}} \end{bmatrix} \right) \end{split}$$

To simplify the algebra, it is convenient to introduce into the equation a biasing parameter, m, defined as follows:

$$m = \frac{V_{DD}}{2(V_{GG} - V_{T}) - V_{DD}} .$$

(22)

Equation (21) then becomes:

$$I_{L} = \frac{K_{L}V_{DD}^{2}}{m} \left(1 - \frac{v_{o}}{v_{DD}}\right) \left(1 - \frac{v_{o}}{v_{DD}}\right) .$$

(23)

The biasing parameter m has no real physical meaning. It is merely a convenient parameter to express the biasing conditions. This parameter has meaning only if the load device is non-saturated; the voltage must satisfy the relation  $|V_{GG}-V_{T}| \ge |V_{DD}|$ . The maximum value of m occurs when  $V_{GG}-V_{T} = V_{DD}$  where m =  $V_{DD}/(2V_{DD}-V_{DD}) = 1.0$ .

The value of m decreases as the gate voltage is made more negative and m  $\longrightarrow 0$  as  $V_{GG} \longrightarrow -\infty$ . Setting  $I_T = I_L$  results in the equations

$$\frac{K_{L} V_{DD}^{2}}{m} \left(1 - \frac{v_{o}}{V_{DD}}\right) \left(1 - m_{V_{DD}}^{v_{o}}\right) = K_{I} (V_{in} - V_{T})^{2}$$

$$(24)$$

for  $\left|V_{in} - V_{T}\right| \leq \left|v_{o}\right|, \text{ and}$

$$\frac{K_{L} V_{DD}^{2}}{m} \left(1 - \frac{v_{o}}{V_{DD}}\right) \left(1 - m_{V_{DD}}^{v_{o}}\right) = K_{I} \left[2(V_{in} - V_{T})v_{o} - v_{o}^{2}\right]$$

$$(25)$$

for  $\left|V_{in} - V_{T}\right| \geq \left|v_{o}\right|.$

Note that both types of load can be described by a single general equation

$$I_{L} = I_{sc} \left( 1 - \frac{v_{o}}{V_{0}} \right) \left( 1 - m \frac{v_{o}}{V_{0}} \right) , \qquad (26)$$

where I is the short-circuit current, i.e.,

$I_{sc} = I_L \Big|_{v_0} = 0$ , and  $v_0 = V_0$ , when the inverter is turned off. The value of  $I_{sc}$ , m and  $V_0$  for each case are defined in Table I.

|                              | I <sub>sc</sub>             | m                                                                                                                                     | v <sub>o</sub>                  |

|------------------------------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| Saturated MOSFET load        | $K_{L}(V_{GG}-V_{T})^{2}$   | 1                                                                                                                                     | V <sub>GG</sub> −V <sub>T</sub> |

| Non-saturated<br>MOSFET load | $\frac{K_{L}V_{DD}^{2}}{m}$ | $\frac{\mathrm{V}_{\mathrm{DD}}}{2\left(\mathrm{V}_{\mathrm{GG}}^{-}\mathrm{V}_{\mathrm{T}}^{-}\right)-\mathrm{V}_{\mathrm{DD}}^{-}}$ | V <sub>DD</sub>                 |

Table I. Expressions for  $I_{sc}$ , m, and  $V_0$ .

#### (iii) Power Consumption of MOSFET Inverter

The DC power associated with the current flow in the saturated region is as follows:

$$P = V_{DD} K (V_{GS} - V_T)^2 \text{ watts.}$$

(27)

In the non-saturated region the DC power associated with the current flow is as follows:

$$P = V_{DD} K \left[ 2 (V_{GS} - V_{T}) V_{DS} - V_{DS}^{2} \right].$$

(28)

## c. Transient Response

Theoretical expressions will be obtained for both turn-off and turn-on characteristics of the circuit.

#### (i) Turn-off Time

For the turn-off case shown in Figure 9, the inverter will be assumed to switch from the conducting state to a completely nonconducting state at the beginning of the transient. Thus it is assumed that the input is a step function and that the device itself has no inherent time delay. The currents are  $I_{I_{i}}$ , shown in equation (26) and

Figure 9. Turn-off case of a MOSFET inverter.

$$I_{C} = -C_{L} \frac{dv_{O}}{dt} .$$

(29)

Equating the currents at the output node will give the differential equation describing the transient condition. This gives  $I_L = I_C$ ,

$$I_{sc} \left(1 - \frac{v_o}{v_0}\right) \left(1 - m\frac{v_o}{v_0}\right) = -C_L \left(\frac{dv_o}{dt}\right) .$$

(30)

If the short-circuit resistance is defined as

$$R_{sc} = \frac{-V_0}{I_{sc}} , \qquad (31)$$

equation (30) becomes

$$(1 - \frac{v_0}{V_0}) (1 - m\frac{v_0}{V_0}) = R_{sc} C_L \frac{\frac{dv_0}{V_0}}{dt}.$$

Rearranging and integrating yields

$$\int dt = \int (R_{sc}C_{L}) \frac{d\left(\frac{v_{o}}{v_{0}}\right)}{\left(1 - \frac{v_{o}}{v_{0}}\right)\left(1 - m\frac{v_{o}}{v_{0}}\right)}$$

From a table of integrals,

$$\int \frac{dx}{(1-x)(1-mx)} = \frac{1}{-m+1} \left( l_n(\frac{1-mx}{1-x}) \right)$$

The equation therefore becomes

$$t = R_{sc}C_{L} \left(\frac{1}{1-m}\right) \ell_{n} \left[\frac{1-m\frac{v_{o}}{v_{0}}}{1-\frac{v_{o}}{v_{0}}}\right]$$

Hence,

$$\epsilon^{\left(\frac{1-m}{R_{sc}C_{L}}\right)t} = \frac{1-m\left(\frac{v_{o}}{v_{0}}\right)}{1-\left(\frac{v_{o}}{v_{0}}\right)}$$

Finally, solving for  $v_0/v_0$ :

$$\frac{\mathbf{v}_{o}}{\mathbf{v}_{0}} = \frac{1-\epsilon}{1-\epsilon} \left(\frac{1-m}{R_{sc}C_{L}}\right)^{t}}_{1-m\epsilon} = \frac{1-\epsilon^{-(1-m)t/\tau}sc}{1-m\epsilon^{-(1-m)t/\tau}sc}, \quad (32)$$

where

$$\tau_{sc} = R_{sc}C_{L}$$

(33)

When the load device is saturated, i.e., m = 1, the limit of the above solution may be obtained by using L'Hospital's rule:

$$\frac{\mathbf{v}_{0}}{\mathbf{v}_{0}} \Big|_{m=1} = \lim_{m \to 1} \frac{1 - \epsilon^{-} \left(\frac{1 - m}{\tau_{sc}}\right) t}{1 - m\epsilon^{-} \left(\frac{1 - m}{\tau_{sc}}\right) t}$$

$$= \frac{\frac{t}{\tau_{sc}}}{1 + \frac{t}{\tau_{sc}}} . \tag{34}$$

The curve of  $v_0^{V_0}$  as a function of  $t/\tau_{sc}$  can be calculated and plotted as shown in Figure 10 (page 19). As seen in Figure 10,  $t/\tau_{sc} = 9$  when  $v_0^{V_0} = 90\%$ . Therefore for a saturated device,  $t_{off} = 9R_{sc}C_L$ .

For the saturated device, combining equations (1), (15), (31), (33) and Table I gives

$$\frac{W}{L} = \frac{C_L}{\tau_{sc} (V_{GS} - V_T) K'}$$

(35)

#### (ii) Turn-on Time

For the turn-on case shown in Figure 11, the inverter will be assumed to switch from the nonconducting state to a completely conducting state at the beginning of the transient. Thus it is assumed that the input is a step function and that the device itself has no inherent time delay.

It will be assumed that the MOSFET load device is biased for operation in the non-saturated mode. The solution of the problem for the saturated MOS load device will be obtained as the limiting case of the solution for the non-saturated MOSFET load device. As a result the circuit for t  $\leq$  0 becomes as in Figure 11.

The current equations are given by equations (11), (12), (26), (29) and Table I. Summing currents at the output node will give two differential equations describing the transient condition. This gives  $I_L = I_T + I_C$ ,

$$\frac{K_{L}V_{0}^{2}}{m}\left(1-\frac{v_{0}}{V_{0}}\right)\left(1-\frac{v_{0}}{V_{0}}\right) = K_{I}\left(V_{1n}-V_{T}\right)^{2} - C_{L}\frac{dv_{0}}{dt} \quad (36)$$

for  $\left|v_{0}\right| \geq \left|V_{1n}-V_{T}\right|$ , and

$$\frac{K_{L}V_{0}^{2}}{m}\left(1-\frac{v_{0}}{V_{0}}\right)\left(1-\frac{v_{0}}{V_{0}}\right)$$

$$= K_{I}\left[2\left(V_{1n}-V_{T}\right)-v_{0}-v_{0}^{2}\right] - C_{L}\frac{dv_{0}}{dt} \quad (37)$$

for  $\left|v_{0}\right| \leq \left|\left(V_{1n}-V_{T}\right)\right|$ .

If  $V_{in}-V_T$  is normalized to  $V_0$  and the terms rearranged, equation (36) becomes:

Figure 11. Turn-on case of a MOSFET inverter.

$$\frac{\mathbf{v}_{0}}{\mathbf{v}_{0}} = \frac{1}{2\mathbf{c}_{s}} \left[ -\mathbf{b}_{s} + \sqrt{-\mathbf{q}_{s}} \tanh \left( -\frac{\mathbf{t}}{\mathbf{R}_{sc}\mathbf{C}_{L}} \frac{\sqrt{-\mathbf{q}_{s}}}{2} + \mathbf{K}_{s} \right) \right]$$

(38)

for  $\left| \frac{\mathbf{v}_{0}}{\mathbf{v}_{0}} \right| \ge \left| \frac{\mathbf{v}_{in} - \mathbf{v}_{T}}{\mathbf{v}_{0}} \right|$ .

Where:

$$a_{s} = 1 - m \frac{K_{I}}{K_{L}} \left( \frac{V_{in} - V_{T}}{V_{0}} \right)^{2}$$

$$b_{s} = -(1+m) \cdot c_{s} = m \cdot q_{s}$$

$$q_{s} = 4 a_{s} c_{s} - b_{s}^{2} \cdot K_{s}$$

$$K_{s} = tanh^{-1} \left( \frac{2c_{s} + b_{s}}{\sqrt{-q_{s}}} \right) \cdot K_{s}$$

The output voltage will follow the resulting equation until it has reached the value  $\left|v_{0}/V_{0}\right| = \left|\frac{V_{\text{in}}-V_{\text{T}}}{V_{0}}\right|$ . Then the inverter passes from saturated into unsaturated operation, and the current equation must be changed. The time at which  $\left|v_{0}/V_{0}\right| = \left|\frac{V_{\text{in}}-V_{\text{T}}}{V_{0}}\right|$  will be designated as t'.

Next the solution will be found for  $t \ge t'$  during the time interval when the inverter is non-saturated by rearranging equation (37), and normalizing  $V_{in}-V_T$  to  $V_0$ . This gives

$$\frac{\mathbf{v}_{0}}{\mathbf{v}_{0}} = \frac{1}{2\mathbf{c}_{n}} \left[ -\mathbf{b}_{n} + \sqrt{-\mathbf{q}_{n}} \tanh \left( -\frac{(\mathbf{t}-\mathbf{t}')}{\mathbf{R}_{sc}\mathbf{C}_{L}} \frac{\sqrt{-\mathbf{q}_{n}}}{2} + \mathbf{K'}_{n} \right) \right] \quad (39)$$

for  $\left| \frac{\mathbf{v}_{0}}{\mathbf{v}_{0}} \right| \leq \left| \frac{\mathbf{v}_{in} - \mathbf{v}_{T}}{\mathbf{v}_{0}} \right|.$

Where:

$$a_{n} = 1.$$

$$b_{n} = -\left[1 + m + m \frac{K_{I}}{K_{L}} 2\left(\frac{V_{in} - V_{T}}{V_{0}}\right)\right]$$

$$c_{n} = m \left(1 + \frac{K_{I}}{K_{L}}\right).$$

$$q_{n} = 4 a_{n}c_{n} - b_{n}^{2}.$$

The value of K'<sub>n</sub> can be found from the relation that  $\left| v_{0} / V_{0} \right| = \left| \frac{V_{in} - V_{T}}{V_{0}} \right|$  at (t-t') = 0 where t' is the time at which the inverter enters the non-saturated region of operation.

Solving equations (38) and (39) with

$$V_{in} = -15v,$$

$V_{0} = -21v,$

$V_{T} = -6v,$

$\frac{K_{I}}{K_{L}} = 20,$

$m = 1,$

gives  $t_{on} \approx 0.35 R_{sc} C_L$  which are the values used for the following design for  $v_o/v_0 = 10\%$ . Since the turn-on time is normally much faster than the turn-off time, the turn-on time can usually be neglected.

### d. Static Shift Register

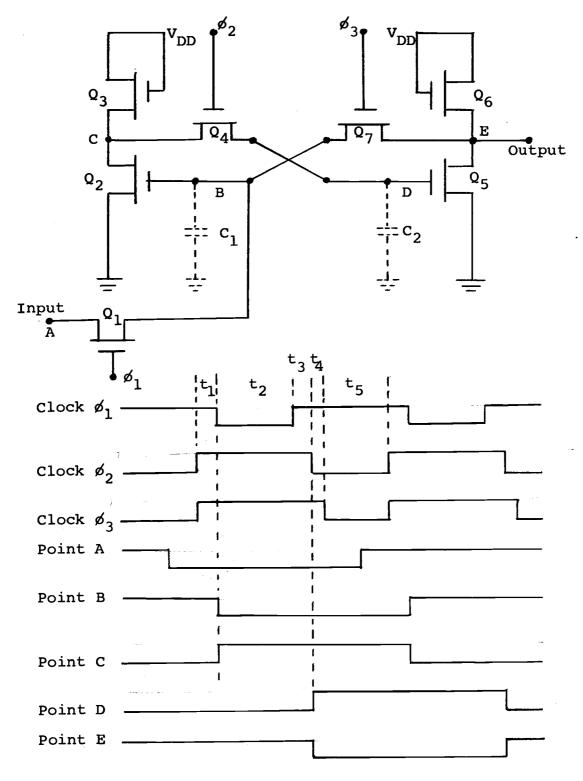

An analysis of static shift register circuit operation follows. A static shift register stage and clock waveforms shown as a timing reference are illustrated in Figure 12.

Figure 12. Static shift register with clock waveforms shown as a timing reference.

A logic "l" input to the register appears as a negative voltage at point A. During t<sub>1</sub> time period,  $\phi_2$  and  $\phi_3$ are at ground. This turns off  $Q_4$  and  $Q_7$ . Information stored on capacitors  $C_1$  and  $C_2$  remains unchanged and the register output appears at point E. During t2, data is transferred to the gate of  $Q_2$  (point B) because of the conduction of  $Q_1$ . As  $C_1$  is charged to the negative input,  $Q_2$ turns on and point C approaches ground potential. As t<sub>3</sub> begins,  $\phi_1$  returns to ground, cutting off  $Q_1$ ; but  $C_1$ remains charged negative holding the drain of  $Q_2$  (point C) near ground. As  $t_4$  begins,  $\phi_2$  goes negative and  $Q_4$  turns on, bringing the gate of  $Q_5$  to the potential of the drain of  $Q_2$  (point C). This turns  $Q_5$  off and point E now rises to within one threshold voltage of  $V_{DD}$ . As t<sub>5</sub> begins,  $\phi_3$ goes negative and  $Q_7$  turns on. Then the voltage from point E is coupled back through  $Q_7$  to the gate of  $Q_2$ , latching  $Q_2$  in the on state. For transferring a logic "O" into the register the sequence is repeated starting with a ground signal at point A.

## III. DESIGN OF A 21-BIT MOSFET STATIC SHIFT REGISTER

A highly versatile 21-bit static shift register was designed by combining three separate 1, 4, and 16-bit MOSFET static shift registers with independent input and output terminals.

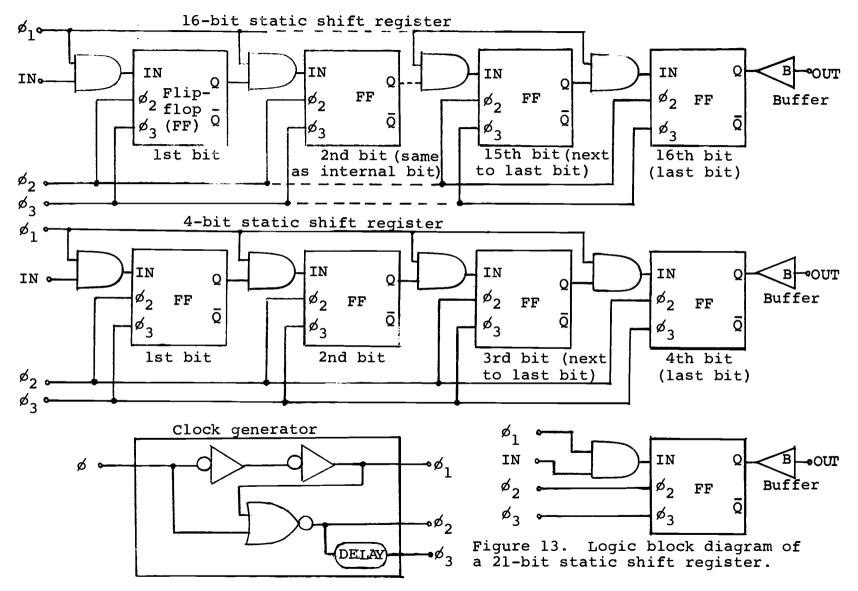

To make it easier to understand, it is shown in logic block diagram form (Figure 13).

The 16-bit static shift register uses 16 single static shift registers and one buffer to get a 16-bit delay. The input and  $\phi_1$  of the first bit go through an AND gate into the first static shift register. The output of the first bit appears at Q, forming the input to the next stage. The output of the last bit goes through a buffer to aid in driving an external load. The function of the 4-bit static shift register and 1-bit static shift register is the same as the 16-bit static shift register.

The clock generator provides the timing signals necessary to operate the static shift registers. One external clock ( $\phi$ ) is required for operation with three clocks ( $\phi_1$ ,  $\phi_2$ , and  $\phi_3$ ) generated internally.  $\phi_1$  is generated in phase with  $\phi$  but is delayed by using two inverters.  $\phi_2$  is generated 180 degrees out of phase with  $\phi$  by a NOR gate, and  $\phi_3$  is produced by delaying  $\phi_2$ slightly.

The design was performed for worst-case conditions.

The following discussion explains the worst conditions of temperature and voltage.

#### High Temperature

Since  $\bar{\mu}_p$  decreases with increasing temperature, I<sub>L</sub> decreases with increasing temperature. A lower charging current results in lower speed.

# Low V<sub>DD</sub>

With a lower  $V_{DD}$ ,  $C_L$  charges to a smaller final voltage and therefore takes longer to reach the voltage defined as a logic "1".

## Low V<sub>GG</sub>

A low  $V_{GG}$  means a higher value of m and therefore slower switching.

## High V<sub>T</sub>

High  $V_T$  means less effective gate drive voltage, and again, less speed. The worst case parameters of this design were assumed as follows:

$V_{DD} = V_{GG} = -27 \text{ volts},$   $V_{o} = -27 \text{ volts},$   $V_{T} = -6 \text{ volts},$   $V_{in} = -11 \text{ volts},$   $V_{0} = -15 \text{ volts},$   $F_{\phi} = 800 \text{ KHz},$   $\phi = -11 \text{ volts},$  P = 260 mw,  $C_{L} = 20 \text{ pF},$   $v_{o}' = -1.5 \text{ volts},$   $^{t}oxide = 1200\text{\AA},$

where:

$V_{DD} = drain supply voltage,$   $V_{GG} = gate supply voltage,$   $V_{o} = buffer supply voltage,$   $V_{T} = threshold voltage,$   $V_{in} = data input voltage,$   $V_{0} = off level data output voltage (final value),$   $F_{\phi} = clock frequency,$   $\phi = clock input voltage,$  P = power consumption,  $C_{L} = load capacitance,$   $v_{o}' = on level .voltage,$   $t_{oxide} = the thickness of oxide under the gate.$

It was assumed that the voltage range for a logic "1" would be from -8v to -15v. Any input voltage within this

range should turn on an inverter. For logic "0" a voltage range from 0v to -4v was assumed. Any input voltage within this range should turn off an inverter.

### a. Output Buffer and Last Bit

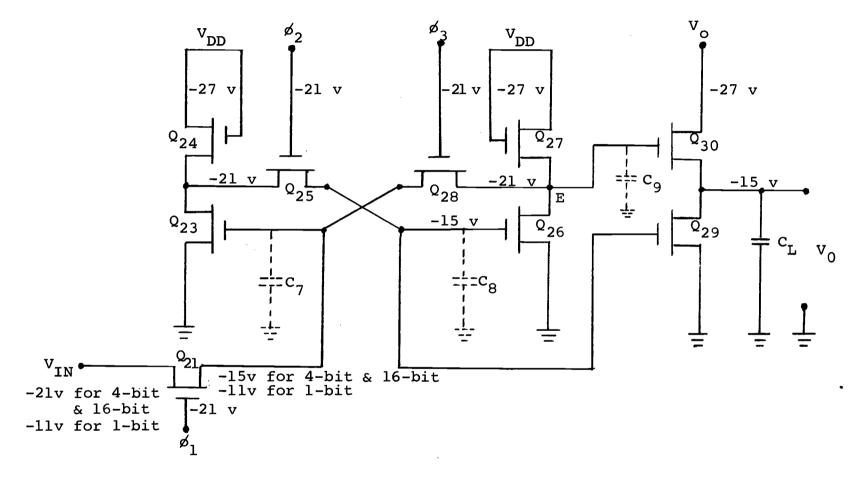

To aid the last bit in driving an external load, a push-pull buffer is used. It is illustrated in Figure 14.

A logic "1" at the point E turns  $Q_{30}$  on and  $Q_{29}$  off, allowing the external capacitor  $C_{\rm L}$  to charge to logic "1". A logic "0" at the point E causes  $Q_{30}$  to turn off and  $Q_{29}$ to turn on, allowing the capacitance to discharge to ground. Since  $Q_{30}$  and  $Q_{29}$  never turn on simultaneously, there is no quiescent power consumption in this stage. With  $Q_{30}$  saturated, equation (35) gives

$$\frac{W}{L} = \frac{C_{L}}{\tau_{sc} (V_{GS} - V_{T}) K'}$$

Assuming  $v_0/V_0 = 90\%$ , Figure 10 or equation (34) gives

$$t_r = 9 \tau_{sc}$$

where  $t_r$  is the time required to charge  $C_L$  to 90% of  $V_0$ and  $v_0$  is the instantaneous value of the output voltage. Equation (35) becomes

$$\frac{W}{L} = \frac{9 C_{L}}{t_{r} (V_{GS} - V_{T}) K'}$$

(40)

The rise time of the circuit is limited by the output buffer and last bit.  $t_r$  should be as small as possible but is limited by the dimensions of  $Q_{30}$ . Taking

Figure 14. Circuit diagram of output buffer and last bit.

ω

this into account, a desired rise time of 80 nsec was selected. The W/L ratio of  $Q_{30}$  is then

$$\left(\frac{W}{L}\right)_{30} = \frac{(9)(20)(10^{-12})}{(80)(10^{-9})(15)(2.6)(10^{-6})} = 60$$

$t_f$  is the time required to discharge  $C_L$  to 10% of  $V_0$ . t' is the time that  $Q_{29}$  changes from saturated into nonsaturated operation. For  $0 \le t \le t'$ ,  $Q_{29}$  is saturated. Combining equations (4) and (29) gives

$$C_{dt}^{dv} = K (V_{GS}^{-}V_{T}^{-})^{2}, \text{ and integrating}$$

(41)

$$\frac{C_{L}}{K(V_{GS}^{-}V_{T}^{-})^{2}} \int_{-15}^{-9} dv_{0}^{-} = \int_{0}^{t} dt .$$

$$t' = \frac{6C}{81K}$$

For t'  $\leq$  t  $\leq$  t<sub>f</sub>, Q<sub>29</sub> is non-saturated. Combining equations (3) and (29):

$$c\frac{dv_{o}}{dt} = K \left[ 2(v_{GS} - v_{T})v_{o} - v_{o}^{2} \right], \text{ and integrating} \quad (42)$$

$$\int_{-9}^{-1.5} \frac{dv_{o}}{-v_{o}^{2} + 2(-9)v_{o}} = \frac{K}{C} \int_{t}^{t} \frac{f}{t} dt, \text{ therefore}$$

$$t_{f} - t' = -\frac{C}{9K} \tanh^{-1} \frac{-v_{o}^{-9}}{9} \Big|_{-9}^{-1.5}$$

$$= -\frac{C}{9K} (-1.2), \text{ and}$$

$$t_{f} = \frac{1.2C}{9K} + \frac{6C}{81K} = \frac{16.8C}{81K} = \frac{16.8C}{81K' \frac{W}{L}} \quad . \quad (43)$$

For the same reason a small value was selected of  $t_f = 55$  nsec. Then the W/L ratio of  $Q_{29}$  is given by equation (43):

$$\left(\frac{W}{L_{29}}\right) = \frac{(16.8)(20)(10^{-12})}{(81)(55)(10^{-9})(2.6)(10^{-6})} = 30$$

For the last bit of this shift register illustrated in Figure 14, one inverter of the pair is always conducting DC. When point E goes to a logical "1", the current from  $Q_{27}$  goes to charge C<sub>9</sub> and  $Q_{27}$  is saturated.

Equation (40) gives

$$\frac{W}{L} = \frac{9 C_9}{t (V_{GS} - V_T) K'}$$

Assuming the duty cycle is 40%, then

$$t = \frac{1}{800 \text{KC}} \times 40\% = 0.5 \ \mu \text{sec.}$$

From equations (7) and (8) the capacitance of  $C_9$ , which is due to the gate area of  $Q_{30}$  and the diffused area which is common to  $Q_{27}$ ,  $Q_{26}$ , and  $Q_{28}$ , is estimated to be 2.1 pf.

Therefore

$$\left(\frac{W}{L}\right)_{27} = \frac{(9)(2.1)(10^{-12})}{(0.5)(10^{-6})(27-6-1.5)(2.6)(10^{-6})} = 0.75$$

When point E goes to a logical "0", current flows through the load  $Q_{27}$  and the inverter  $Q_{26}$ .

From equation (27) the power consumption is

$$P = V_{DD} K (V_{GS} - V_T)^2$$

= (27) (0.75) (2.6) (10<sup>-6</sup>) (27-1.506)<sup>2</sup> = 20 mw.

In order to calculate the W/L of  $Q_{26}$ , the normalized input and output voltages have to be determined.  $Q_{27}$  is saturated and the on-level is assumed to be -1.5 volts, which gives a normalized output voltage of

$$\frac{v'_{O}}{v_{GG}-v_{T}} = \frac{-1.5}{-(27-6)} = \frac{1.5}{21} = 0.0713 .$$

The normalized input voltage is

$$\frac{V_{in} - V_{T}}{V_{GG} - V_{T}} = \frac{-(15 - 6)}{-(27 - 6)} = \frac{9}{21} = 0.428$$

Next, using the above results in equation (19) or Figure 8, we find

$$\frac{K_{I}}{K_{L}} = \frac{\left(\frac{W}{L}\right)_{26}}{\left(\frac{W}{L}\right)_{27}} = 16$$

However, as a margin of safety to insure that  $v'_{o}$  will be somewhat less than 1.5 volts, let

$$\frac{K_{I}}{K_{L}} = \frac{\left(\frac{W}{L}\right)_{26}}{\left(\frac{W}{L}\right)_{27}} = 20 .$$

Therefore,

$$(W/L)_{26} = (20)(0.75) = 15$$

.

The capacitance that  $Q_{24}$  must drive,  $C_8$ , is estimated to be 2.0 pf.

From equation (40),

$(W/L)_{24} = 0.70$ .

For the 4-bit and the 16-bit registers, the input is -15 volts.

From equation (19),

$$K_{I}/K_{L} = 20$$

.

Therefore,

$$(W/L)_{23} = (20) (W/L)_{24} = (20) (0.7) = 14$$

The effect of the resistance of  $Q_{25}$  may be neglected when  $Q_{23}$  turns off if  $(W/L)_{25}/(W/L)_{24} \ge 5$  because the resistance of  $Q_{25}$  will be 1/5 that of  $Q_{24}$ . Choosing  $(W/L)_{25} = 4$ satisfies the above requirement that  $(W/L)_{25}/(W/L)_{24} \ge 5$ . By the same reasoning,

$$(W/L)_{28} = 4$$

,

$(W/L)_{22} \stackrel{>}{=} 5(W/L)_{20}$ .

For the 1-bit register, the input is -11 volts, giving

$$\frac{v_{o}'}{v_{GG} - v_{T}} = 0.0713, \text{ and}$$

$$\frac{v_{in} - v_{T}}{v_{GG} - v_{T}} = \frac{-(11-6)}{-21} = 0.248$$

From equation (19),

$$K_{\rm I}/K_{\rm L} = 34$$

.

Therefore,

$$(W/L)_{23} = 34(W/L)_{24} = (34)(0.7) = 24$$

.

The W/L ratios of the other devices in the 1-bit are identical to the W/L ratios in the 4-bit and the 16-bit.

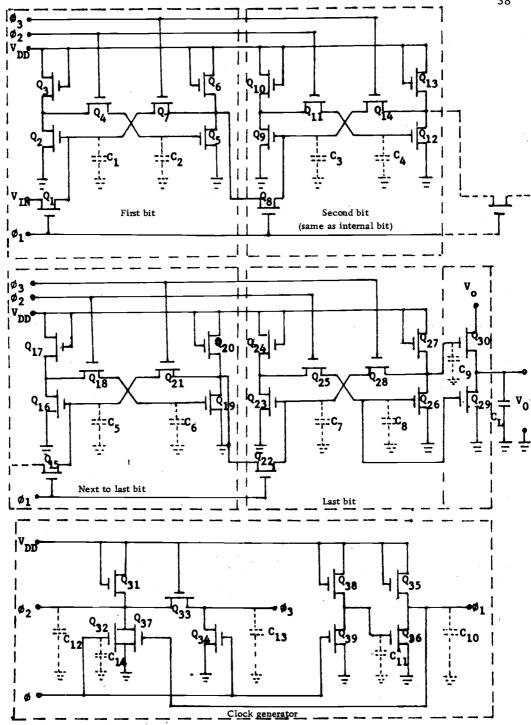

#### b. Next to Last Bit

The next to last bit is shown in Figure 15. The capacitance that  $Q_{20}$  must drive,  $C_7$ , is estimated to be 0.85 pf. Using equations (40), (27), and (19),

Figure 15. Circuit diagram of 21-bit static shift register.

$$(W/L)_{20} = 0.3,$$

P = 5mw, and

$(W/L)_{19} = (20)(0.3) = 6.$

$(W/L)_{22} \ge 5(W/L)_{20} = 2.$

The capacitance that  $Q_{17}$  must drive,  $C_6$ , is estimated to be 0.42 pf. Therefore,

$$(W/L)_{17} = 0.15$$

, and

$(W/L)_{16} = (20)(0.15) = 3$ .

By the same reasoning used for  $Q_{25}$ ,

$$(W/L)_{21} = 2,$$

$(W/L)_{18} = 2,$

$(W/L)_{15} = 1.5.$

c. Internal Bit and First Bit

The first and internal bits are shown in Figure 15. For a typical internal bit, the capacitance is estimated to be 0.3 pf.

Repeating the calculations used above, we get

$$(W/L)_{13} = (W/L)_{10} = 0.1$$

$(W/L)_{12} = (W/L)_9 = 2,$

$(W/L)_{11} = 1.5,$

$(W/L)_{14} = 1.0,$

$(W/L)_8 = 1.5,$

$P = 2.7 \text{ mw}.$

With the exception of  $Q_2$ , the W/L ratios of the devices in the first bit are identical to the W/L ratios in the internal bits. The W/L ratio of  $Q_2$  in the first bit is different because the input voltage is -ll volts.

Using the same calculation as for  $Q_{23}^{}$  of the 1-bit register,

$(W/L)_2 = 4$ .

The total power consumption of 21 bits is (20)(3)+(5)(2)+(2.7)(16) = 113.2 mw.

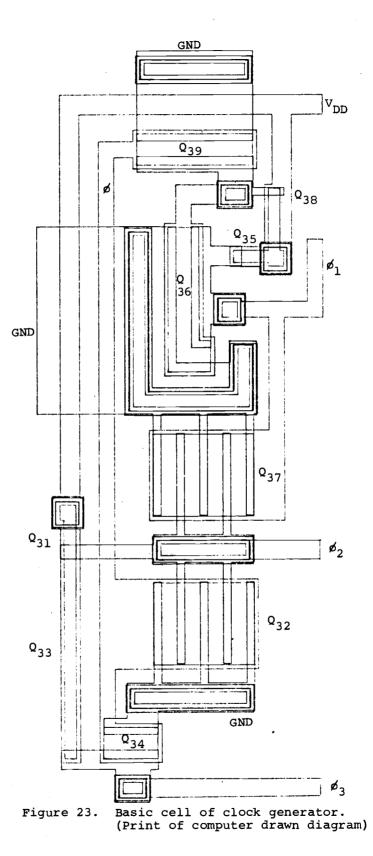

#### d. Clock Generator

For long-term data storage in the register shown in Figure 12 both clocks,  $\phi_2$  and  $\phi_3$ , must be present to lock the flip-flop in a stable state. This requires  $\phi_2$  and  $\phi_3$ to be at a negative level (logic 1) and  $\phi_1$  at zero level (logic 0). However, during the transfer of information into the register,  $\phi_2$  and  $\phi_3$  are required to be at a zero level (logic 0) and  $\phi_1$  at negative level (logic 1).

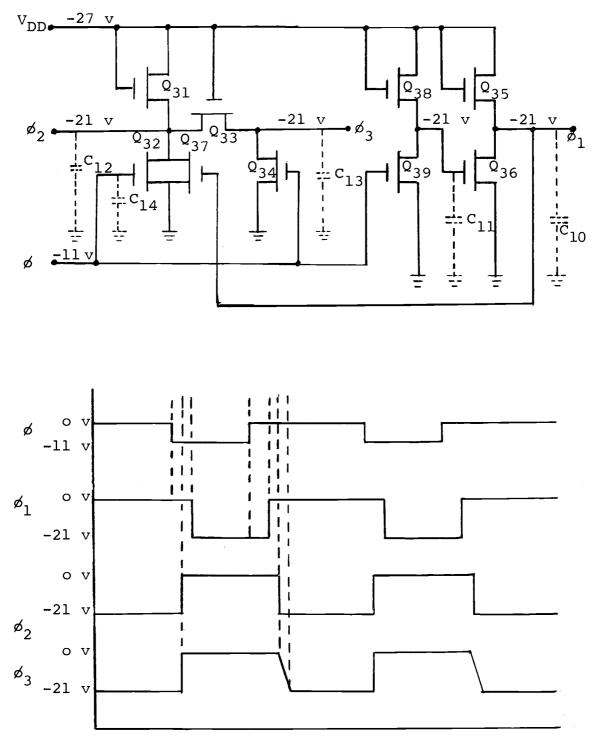

Based on the requirements described above, a generator circuit is shown in Figure 16.

The capacitance that Q<sub>35</sub> must drive, C<sub>10</sub>, is

Figure 16. Circuit diagram of internal clock generation with timing diagram of the four clock phases.

approximately 2.8 pf. Using equations (40) and (27),

$$(W/L)_{35} = 1.0$$

, and

P = 27 mw.

The input voltage is -21 volts. Thus from equation (19),

$$(W/L)_{36} = 20$$

.

The capacitance that  $Q_{38}$  must drive,  $C_{11}$ , is estimated to be 0.9 pf. Therefore,

$$(W/L)_{38} = 0.33$$

, and

P = 9 mw.

The input voltage is -11 volts. Then

$$(W/L)_{39} = 15$$

.

The capacitance that  $Q_{31}$  must drive,  $C_{12}$  and  $C_{13}$ , is estimated to be 3.3 pf. Therefore,

$$(W/L)_{31} = 1.2$$

, and

P = 32 mw.

The input voltage is -11 volts. Then

$(W/L)_{32} = (W/L)_{37} = 42$ .

The power consumption of the generator is

$P_G = 27 + 9 + 32 = 68 \text{ mw}.$

$Q_{31}$  is saturated. From equation (5),

$$(g_m) = 2K(V_{GS} - V_T)$$

= (2)(2.6)(10<sup>-6</sup>)(1.2)(-27+1.5+6)

= 122(10<sup>-6</sup>) mho.

The gates that  $\phi_3$  operate are only effective at frequencies below 10 KHz. They are not needed at the higher frequencies, therefore the charging time of  $\phi_3$  can be much slower than  $\phi_2$ . To insure that  $\phi_3$  is delayed with respect to  $\phi_2$  (assuming that the charging time of  $\phi_2$  is 20 times faster than  $\phi_3$ ), then

20

$$R_{31}C_{12} = (R_{31}+R_{33}) C_{13},$$

(20)  $\left[\frac{C_{12}}{(g_m)_{31}}\right] = \left[\frac{1}{(g_m)_{31}} + \frac{1}{(g_m)_{33}}\right]C_{13},$

where

$$c_{12} = 1.217 \text{ pf},$$

$c_{13} = 1.32 \text{ pf},$

$(g_m)_{33} = 6.9 (10^{-6}) \text{ mho}$

From equation (5):

$$(W/L)_{33} = \frac{(g_m)_{33}}{2K'(V_{GS}-V_T)} = 0.068$$

.

To prevent  $\phi_3$  from turning on  $Q_7$ ,  $Q_{14}$ ,  $Q_{22}$ , and  $Q_{28}$  while  $\phi_1$  is negative (logic 1) the W/L ratio from  $Q_{34}$  is found from equation (19) to be

$$(W/L)_{34} = 7.$$

#### IV. EXPERIMENTAL RESULTS

#### a. Design

The total power consumption of the entire circuit is  $P_m = 113.2 \text{ mw}+68\text{mw} = 181.2 \text{ mw}.$

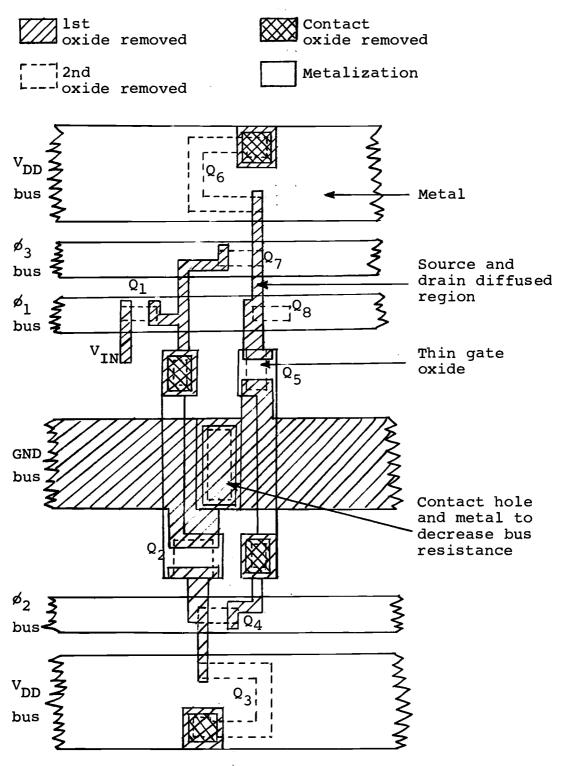

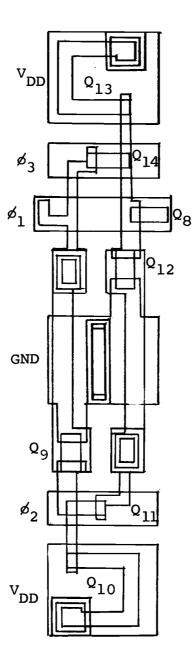

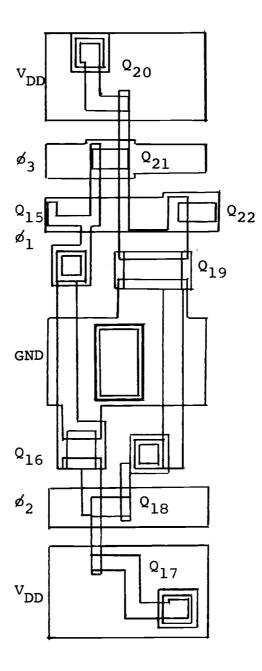

The W/L ratios of the devices of the 21-bit static shift register in this design are shown in Table II. The widths and lengths shown in the table are the dimensions of the first oxidation removal patterns on the fabrication mask. The lateral diffusion of p-regions beyond the oxide edges is approximately 0.1 mil. Consequently, 0.2 mils must be subtracted from the first oxide removal dimensions.

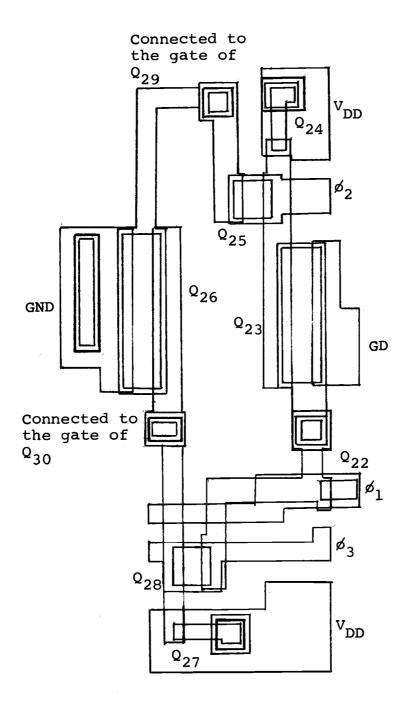

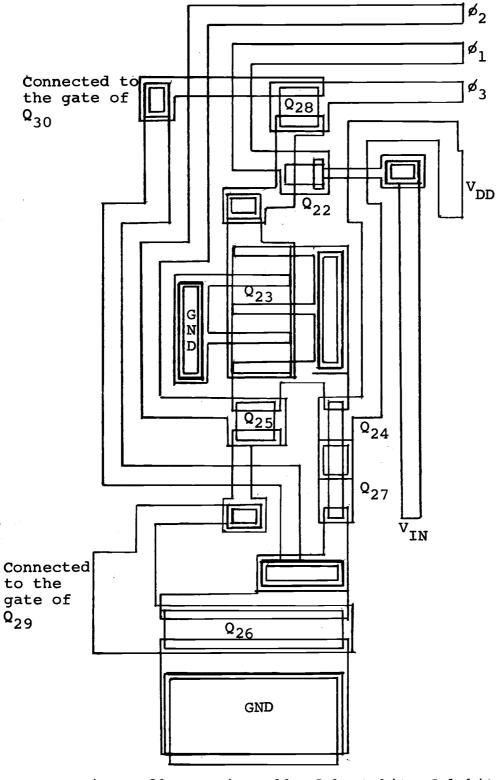

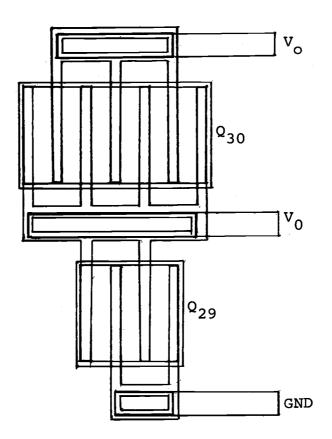

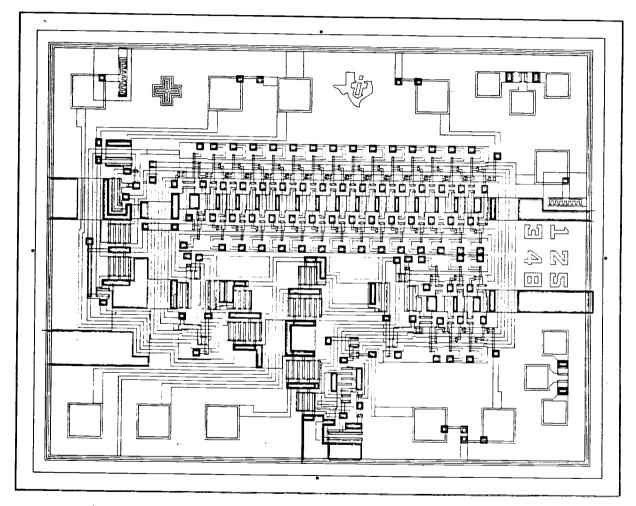

The basic cells were first drawn by hand as shown in Figure 17. Using punch cards, this information was fed into a computer which drew the basic cells shown in Figures 18 to 23. The scale is 500:1 (1 inch = 500 mils). The computer then generated the total physical layout shown in Figure 24 and also cut the Rubylith. Mask making and processing were done by standard Texas Instruments procedures.

#### Table II. W/L Ratios of 21-bit Static Shift Register

Devices

Q8 Q9 Q10

$Q_{11}$

$\begin{array}{c}

\tilde{Q}_{12} \\

Q_{12} \\

Q_{13} \\

Q_{14}

\end{array}$

W/L

1.5

2.0

0.1

1.5

2.0

0.1

1.0

First Bit of 4-bit S.R. and 16-bit S.R.

Second Bit of 4-bit S.R. and 16-bit S.R. (Same as internal bit)

L (lst CR.mils)

0.4

0.4

3.2

0.4

0.4

3.2

0.5

2nd

W\OR.mils/

0.3

0.4

0.3

0.3

0.4

0.3

0.3

|     | (2nd )                                 | (lst )                                                                                                                                                                             |

|-----|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| W/L | W\OR.mils/                             | L\OR.mils/                                                                                                                                                                         |

| 1.5 | 0.3                                    | 0.4                                                                                                                                                                                |

| 4.0 | 0.8                                    | 0.4                                                                                                                                                                                |

| 0.1 | 0.3                                    | 3.2                                                                                                                                                                                |

| 1.5 | 0.3                                    | 0.4                                                                                                                                                                                |

| 2.0 | 0.4                                    | 0.4                                                                                                                                                                                |

| 0.1 | 0.3                                    | 3.2                                                                                                                                                                                |

| 1.0 | 0.3                                    | 0 <b>.</b> 5                                                                                                                                                                       |

|     | 1.5<br>4.0<br>0.1<br>1.5<br>2.0<br>0.1 | W/L         W(OR.mils)           1.5         0.3           4.0         0.8           0.1         0.3           1.5         0.3           2.0         0.4           0.1         0.3 |

# Next to Last Bit of 4-bit S.R. and 16-bit S.R.

Last Bit of 4-bit S.R. and 16-bit S.R.

| Devices | W/L  | $W^{(2nd)}_{OR.mils}$ | $L(\frac{lst}{OR.mils})$ |

|---------|------|-----------------------|--------------------------|

| Q15     | 1.5  | 0.3                   | 0.4                      |

| Q16     | 3.0  | 0.6                   | 0.4                      |

| Q17     | 0.15 | 0.3                   | 2.2                      |

| Q18     | 2.0  | 0.4                   | 0.4                      |

| Q19     | 6.0  | 1.2                   | 0.4                      |

| Q20     | 0.3  | 0.3                   | 1.2                      |

| Q21     | 2.0  | 0.4                   | 0.4                      |

| Devices       | W/L  | W (2nd<br>W (OR.mils) |     |

|---------------|------|-----------------------|-----|

| 900           | 2.0  | 0.4                   | 0.4 |

| Q22<br>Q23    | 14.0 | 2.8                   | 0.4 |

| Q23           | 0.7  | 0.3                   | 0.6 |

| Q24<br>Q25    | 4.0  | 0.8                   | 0.4 |

| $Q_{26}^{25}$ | 15.0 | 3.0                   | 0.4 |

| Q20           | 0.75 | 0.3                   | 0.6 |

| $Q_{28}^{27}$ | 4.0  | 0.8                   | 0.4 |

Table II (Continued).

Last Bit of 1-bit S.R.

| Output | Buffer |

|--------|--------|

|--------|--------|

| Devices               | W/L  | $W^{(2nd)}_{OR.mils}$ | L (lst<br>L (OR.mils) |

|-----------------------|------|-----------------------|-----------------------|

| Q                     | 2.0  | 0.4                   | 0.4                   |

| Q22                   | 24.0 | 4.8                   | 0.4                   |

| $\tilde{Q}_{24}^{23}$ | 0.7  | 0.3                   | 0.6                   |

| ~24<br>Qor            | 4.0  | 0.8                   | 0.4                   |

| Q25                   | 15.0 | 3.0                   | 0.4                   |

| Q26                   | 0.75 | 0.3                   | 0.6                   |

| Q <sub>28</sub>       | 4.0  | 0.8                   | 0.4                   |

| Devices         | W/L  | $W^{(2nd)}_{OR.mils}$ | $\binom{lst}{OR.mils}$ |

|-----------------|------|-----------------------|------------------------|

| Q <sub>29</sub> | 30.0 | 6.0                   | 0.4                    |

| Q <sub>30</sub> | 60.0 | 12.0                  | 0.4                    |

#### Clock Generator

| Devices | W/L                                        | $\binom{2nd}{W(OR.mils)}$ | $L \begin{pmatrix} lst \\ OR.mils \end{pmatrix}$ |

|---------|--------------------------------------------|---------------------------|--------------------------------------------------|

| Q31     | 1.2 42.0 0.068 7.0 1.0 20.0 42.0 0.33 15.0 | 0.3                       | 0.45                                             |

| Q32     |                                            | 8.4                       | 0.4                                              |

| Q33     |                                            | 0.3                       | 4.6                                              |

| Q34     |                                            | 1.4                       | 0.4                                              |

| Q35     |                                            | 0.3                       | 0.50                                             |

| Q36     |                                            | 4.0                       | 0.4                                              |

| Q37     |                                            | 8.4                       | 0.4                                              |

| Q38     |                                            | 0.3                       | 1.2                                              |

| Q39     |                                            | 3.0                       | 0.4                                              |

Figure 17. Basic cell of first bit of 4-bit static shift register and 16-bit static shift register (Scale 500:1).

**....**

•· · ·

Figure 18. Basic cell of second bit of 4-bit static shift register and 16-bit static shift register (Scale 500:1). (Print of computer drawn diagram)

Figure 19. Basic cell of next to last bit of 4-bit static shift register and 16-bit static shift register (Scale 500:1). (Print of computer drawn diagram)

Figure 20. Basic cell of last bit of 4-bit static shift register and 16-bit static shift register (Scale 500:1). (Print of computer drawn diagram)

Figure 21. Basic cell of last bit of 1-bit static shift register (Scale 500:1). (Print of computer drawn diagram)

51

Figure 22. Basic cell of output push-pull buffer (Scale 500:1). (Print of computer drawn diagram)

Figure 24. Physical layout of 21-bit static shift register. (Print of computer drawn diagram)

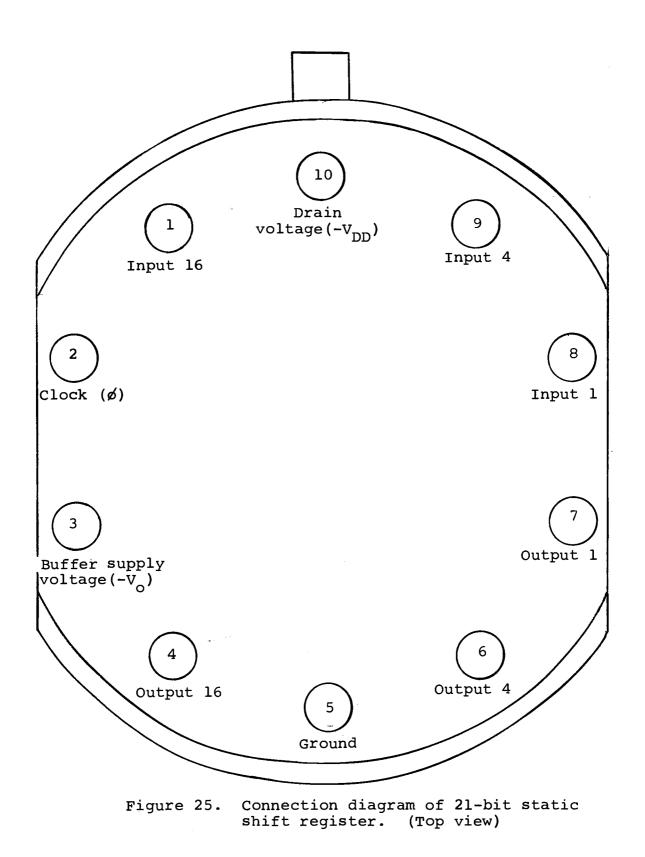

The functions of the terminals shown in Figure 25 are as follows:

| Terminal<br><u>Number</u> | Function                                     |

|---------------------------|----------------------------------------------|

| 1                         | Data input of 16-bit static shift register.  |

| 2                         | Clock input (Ø).                             |

| 3                         | Buffer supply voltage (-V <sub>o</sub> ).    |

| 4                         | Data output of 16-bit static shift register. |

| 5                         | Ground.                                      |

| 6                         | Data output of 4-bit static shift register.  |

| 7                         | Data output of 1-bit static shift register.  |

| 8                         | Data input of 1-bit static shift register.   |

| 9                         | Data input of 4-bit static shift register.   |

| 10                        | Drain voltage (-V <sub>DD</sub> ).           |

Data entered into an n bit static shift register will appear at the output n clock pulses later.

To obtain a 1-bit static shift register use terminals 8 and 7. To obtain a 4-bit static shift register, use terminals 9 and 6. To obtain a 16-bit static shift register, use terminals 1 and 4. To obtain a 5-bit static shift register use terminals 9 and 7, connect terminal 6 to terminal 8. To obtain a 17-bit static shift register use terminals 1 and 7, connect terminal 4 to terminal 8. To obtain a 20-bit static shift register use terminals 1 and 6, connect terminal 4 to terminal 9. And to obtain a 21-bit static shift register use terminals 1 and 7, connect terminal 4 to terminal 9 and terminal 6 to terminal 8.

#### b. Electrical Characteristics

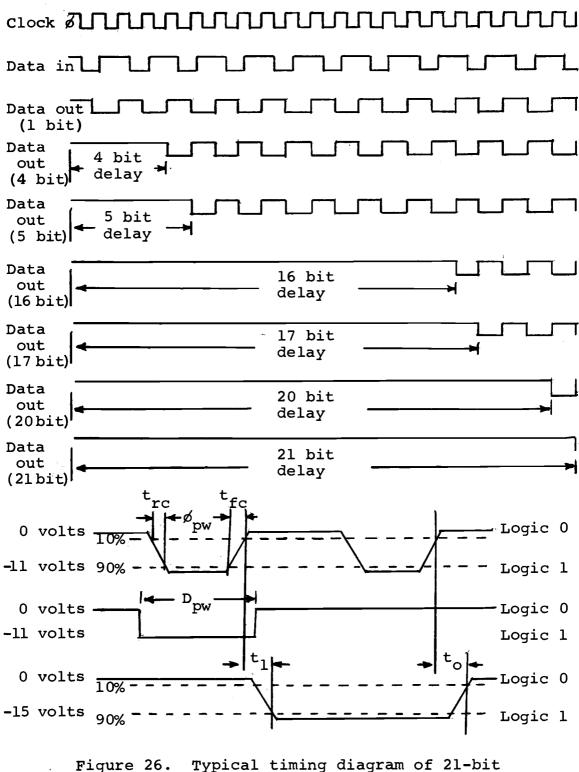

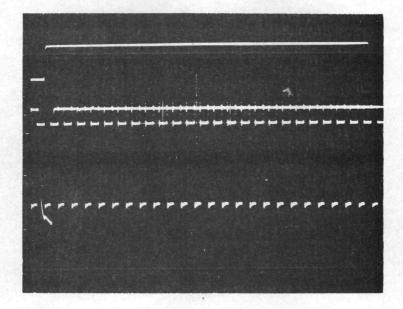

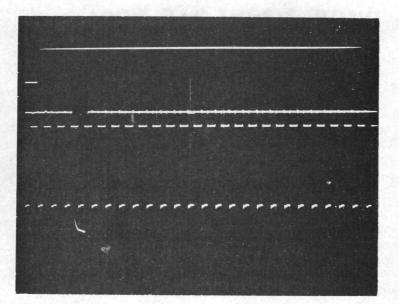

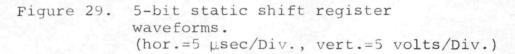

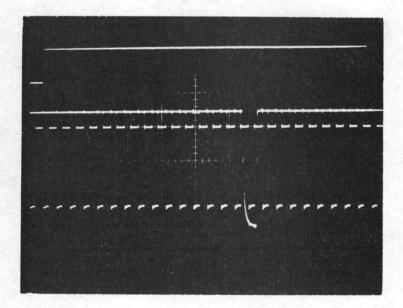

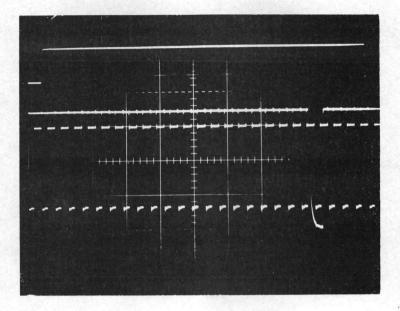

The following is a tabulation of the calculated and experimental electrical characteristics for the 21-bit static shift register. Figure 26 shows the calculated timing diagram, and Figures 27 to 34 show the experimental waveforms. The calculated results agree with those obtained experimentally. The data were obtained from measurements on five circuits with the average values shown.

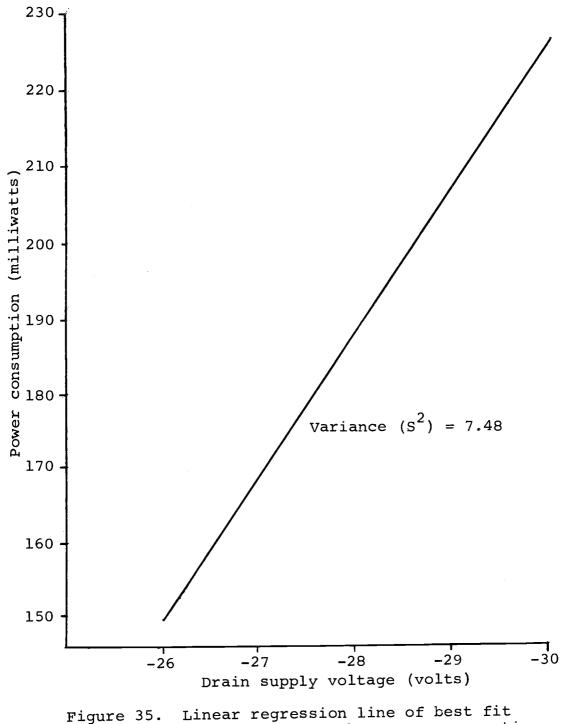

A statistical analysis was used to determine the linear regression line of best fit to the data for power consumption versus drain supply voltage. The regression line is shown in Figure 35. The linear regression was Y = -346.96+19.1X, with variance about regression line  $S^2 = 7.48$ .

#### OPERATING CONDITIONS

| V <sub>DD</sub>                                                             | = -28   | Volts ± 1          | Volt, | $V_{o} = -28$ Vol                  | ts ± 1         | Volt                               |

|-----------------------------------------------------------------------------|---------|--------------------|-------|------------------------------------|----------------|------------------------------------|

| 1                                                                           | Load =  | 10 $M\!\Omega$ and | 10 pf | , $\overline{T}_A = 0^{\circ}C$ to | +85°C          |                                    |

| Characteristics                                                             | Min.    | Typ<br>TA=25°C     | Max.  | Experimental<br>Measurements       | Units          | Conditions                         |

| Clock Repetition Rate                                                       | D.C.    |                    | 0.8   | DC-1.4                             | MHz            |                                    |

| Clock Pulse Widths<br>(ø pw)                                                | 0.8     |                    | 10    | 0.6-12                             | μs             | See Figure 26                      |

| Clock Pulse Rise<br>and Fall Time<br>(t <sub>rc</sub> and t <sub>fc</sub> ) |         |                    | 4     | 4                                  | μs             | See Figure 26                      |

| Clock Pulse Logic<br>Levels (Ø)<br>Logic "O"<br>Logic "l"                   | <br>-10 | 0<br>-11           | -2.0  | 0<br>-11                           | Volts<br>Volts | See Figure 26<br>See Figure 26     |

| Clock Pulse Input<br>Capacitance (Ø)                                        |         | 4.0                | 6.0   | 3.5                                | pF             | ø=0 Volts,<br>T <sub>A</sub> =25°C |

| Clock Input Leakage<br>Current                                              |         |                    | 1.0   | 1x10 <sup>-3</sup>                 | μA             | V <sub>in</sub> = -20 Volts        |

| Data Pulse Width<br>(Dpw)                                                   | 1.0     | -                  |       | 0.8                                | μs             | See Figure 26                      |

Operating Conditions (continued)

| Characteristics                                     | Min.    | тур<br>т <sub>A</sub> =25°С | Max. | Experimental<br>Measurements | Units          | Conditions                       |

|-----------------------------------------------------|---------|-----------------------------|------|------------------------------|----------------|----------------------------------|

| Data Input Logic Levels<br>Logic "0"<br>Logic "1"   | -10     | 0<br>-11                    | -2.0 | 0<br>-11                     | Volts<br>Volts |                                  |

| Data Input Capacitance                              |         | 1.5                         | 2.0  | 1.5                          | pF             | $V_{in}=0$ Volts,<br>$T_A=25$ °C |

| Data Input Leakage<br>Current                       |         |                             | 1.0  | 1x10 <sup>-3</sup>           | μA             | V <sub>in</sub> = -20 Volts      |

| Output Logic Levels<br>Logic "0"<br>Logic "1"       | <br>-11 | 0<br>-15                    | -1.0 | 0<br>-17                     | Volts<br>Volts |                                  |

| Output Logic "l"<br>Response Time (t <sub>l</sub> ) |         |                             | 0.80 | 0.7                          | μs             | See Figure 26                    |

| Output Logic "O"<br>Response Time (t <sub>O</sub> ) |         |                             | 0.45 | 0.4                          | μs             | See Figure 26                    |

| Output Impedance<br>to Ground                       |         | 1.2                         | 3.0  | 1.2                          | <b>K</b> U     | Output Logic "0"                 |

| Output Drive<br>Capability                          | -10     | -11                         |      | -11                          | Volts          | R_=17 K to<br>LGround            |

| Output Drive<br>Capability                          | -5.0    | -8                          |      | -8                           | Volts          | R <sub>L</sub> =4 K to<br>Ground |

| Power Supply Current<br>Drain                       |         | 6.7                         | 9.1  | 6.3                          | mA             | V <sub>DD</sub> = -27 Volts      |

static shift register.

Figure 27. l-bit static shift register

waveforms. Top-input, center output, bottom-clock.

(hor.=5 µsec/Div.,

vert.= 5 volts/Div.)

Figure 28. 4-bit static shift register waveforms. (hor.=5 µsec/Div., vert.=5 volts/Div.)

Figure 30. 16-bit static shift register

waveforms.

(hor.=5 µsec/Div., vert.=5 volts/Div.)

Figure 32. 20-bit static shift register waveforms. (hor.=5 µsec/Div., vert.=5 volts/Div.)

Figure 34. Rise and fall time of the output wave (top) with clock (bottom). (hor.=lusec/Div., vert.= 5 volts/Div.)

Figure 35. Linear regression line of best fit to the data for the power consumption versus drain supply voltage.

#### V. CONCLUSIONS

This design, using a MOSFET static shift register with 162 active devices for multiple-bit serial operation, is a relatively complex circuit put on a single monolithic chip. It requires only one power supply and one external clock. Seven different bit lengths may be obtained by appropriate connections. The circuit performed very well, giving experimental results which agreed with those calculated. The frequency response and output level were actually better since the design was for worst-case conditions.

The use of MOSFET integrated circuits is increasing exponentially, their potential economy is being realized, and new areas of application will inevitably be opened. The economic advantages are due to structural compactness and fabricational simplicity; these factors favor economy through their beneficial effect on yield. The advantages of MOSFET shift registers, both in simplicity and in comparatively good performance, will insure an increasing use in the design of systems in the future.

#### BIBLIOGRAPHY

- Arnell, C. and B. Crawford. Unpublished research on MOS voltage transfer curves. Dallas, Texas Instruments, 1967.

- Bogert, H. Z., Jr. Metal oxide silicon integrated circuits. Semiconductor Products and Solid State Technology 9(3):30-35. 1966.

- 3. Carlyle, J. S. A look at metal-oxide-semiconductor technology. Dallas, Texas Instruments, 1966. 32 p.

- 4. Crawford, R. H. MOSFET in circuit design. New York, McGraw-Hill, 1967. 136 p.

- Delhom, L. Design and application of transistor switching circuit. New York, McGraw-Hill, 1968. 278 p.

- Electronic Design. Planning to use MOS array? (Editorial). Electronic Design 14:42-45. January 1966.

- Farina, D. and D. Trotter. MOS integrated circuits save space and money. Electronics 38(20):84-95. 1965.

- 8. Grove, A. S. Physics and technology of semiconductor device. New York, John Wiley, 1967. 366 p.

- 9. Lohman, R. D. Application of MOSFETs in microelectronics. Semiconductor Products and Solid State Technology 9(3):23-29. 1966.

- Lynn, D. C. and D. Hamilton. Analysis and design of integrated circuits. New York, McGraw-Hill, 1967. 545 p.

- 11. Mahoney, M. V. Logic design. New York, RCA Institutes, 1967. 185 p.

- 12. Millman, J. and H. Taub. Pulse, digital and switching waveforms. New York, McGraw-Hill, 1965. 958 p.

- 13. Redwine, D. Unpublished research on MOS transient calculations. Dallas, Texas Instruments, 1967.

- 14. Sah, C. T. Characteristics of the metal-oxidesemiconductor transistor. IEEE Transactions on Electron Devices ED-11(7):324-345. 1964.

- 15. Seely, J. L. MOS arrays have more on a chip. Electronic Design 14:90-93. January 1966.

- 16. Shopbell, M. Unpublished research on theory and application of MOS design curve. Dallas, Texas Instruments, 1967.

- 17. Warner, R. M. and J. Fordemwalt. Integrated circuits. New York, McGraw-Hill, 1965. 385 p.

- 18. Warner, R. M. A comparison of MOS and bipolar integrated circuits. Dallas, Texas Instruments, 1967. 57 p.

- 19. Wine, R. L. Statistics for scientists and engineers. Englewood Cliffs, Prentice Hall, 1964. 671 p.