#### AN ABSTRACT OF THE THESIS OF

<u>Xiangqing Xu</u> for the degree of <u>Master of Science</u> in <u>Electrical and Computer</u> <u>Engineering</u> presented on <u>May 30, 1995.</u> Title: <u>A Pipelined Baseband Digital</u> <u>Predistortion Architecture for RF Amplifier Linearization</u>

Abstract approved: James H. Herzog

This thesis describes the design of a baseband digital predistortion architecture for radio frequency (RF) amplifier linearization. Existing amplifier linearization techniques are first examined. The nonlinearity of an amplifier can be characterized as amplitude-to-amplitude distortion and amplitude-to-phase distortion. The distortion can be corrected by providing a predistorted driver signal (both in amplitude and phase) to the amplifier. This counteracts the nonlinearity of the amplifier so that the overall system is more linear. A pipelined predistortion architecture is designed to allow fast processing speed, and is capable of providing linearization for a bandwidth of 25 Mhz. The simulation results show significant improvement in amplifier's performance using predistortion technique. The system bandwidth versus cost is examined by using commercially available components.

### A Pipelined Baseband Digital Predistortion Architecture for RF Amplifier Linearization

by

Xiangqing Xu

A THESIS

submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Master of Science

Completed May 30, 1995 Commencement June 1996 Master of Science thesis of Xiangqing Xu presented on May 30, 1995

APPROVED:

Redacted for Privacy

Major Professor, representing Electrical and Computer Engineering

Redacted for Privacy

Chair of Department of Electrical and Computer Engineering

Redacted for Privacy

Dean of Graduate School

I understand that my thesis will become part of the permanent collection of Oregon State University libraries. My signature below authorizes release of my thesis to any reader upon request.

Redacted for Privacy

Xiangqing Xu

2

#### ACKNOWLEDGMENTS

I would like to express my sincere gratitude to professor James Herzog for his understanding, help, patience, advice and encouragement. I am grateful to professor Bella Bose, professor V.K. Trapathi and professor R.J. Schultz for agreeing to be on my graduate committee and taking time out of their busy schedules to be present at my defense.

Special thanks to Mr. Robert S. Larkin, chief engineer (retired) of Celwave for his help, advice and concern on this project. I also thank Mrs. Martina Testa, engineering manager at Celwave for her understanding and support throughout my research. Thanks also to Qiang Wu, Hans-Albert Stumm, David Wills, Phil Mages and all of my colleagues for their friendship and support.

I thank Celwave for their financial support during my study.

I thank Rita Walls, graduate secretary of the Electrical and Computer Engineering department, for her help and support.

Finally, I want to give my deepest gratitude to my husband, Liping and my daughter, Yin. Without their love and encouragement, this would surely not have been possible.

### TABLE OF CONTENTS

| 1. | . Introduction                                                                                  | <u>Page</u><br>1 |

|----|-------------------------------------------------------------------------------------------------|------------------|

|    | 1.1 Radio frequency (RF) amplifiers in Cellular communication syste                             | ems 1            |

|    | 1.2 Frequency spectrum of Cellular telephone system                                             | 2                |

|    | 1.3 RF amplifier nonlinear characteristic                                                       | 3                |

|    | 1.4 Amplifier linearization techniques                                                          | 5                |

|    | 1.4.1 Feed forward<br>1.4.2 Cartesian feedback<br>1.4.3 Predistortion                           | 6<br>7<br>11     |

|    | 1.5 Thesis objectives                                                                           | 11               |

| 2. | . Literature Review on Predistortion                                                            | 12               |

|    | 2.1 Predistortion concept                                                                       | 12               |

|    | 2.2 Analog RF predistorter                                                                      | 12               |

|    | 2.3 Fixed baseband digital predistortion                                                        | 13               |

|    | 2.4 Adaptive baseband predistortion                                                             | 14               |

| 3. | . Architecture Design                                                                           | 19               |

|    | 3.1 The design goal                                                                             | 19               |

|    | 3.2 Architecture design consideration                                                           | 20               |

|    | 3.3 The predistorter unit                                                                       | 25               |

|    | 3.3.1 Block diagram<br>3.3.2 Digital processing architecture<br>3.3.3 Updating the memory table | 25<br>28<br>34   |

# TABLE OF CONTENTS (Continued)

|    | 3.3.4 Micro-operation diagram<br>3.3.5 The controller<br>3.3.6 Interface to host computer                    | <u>Page</u><br>36<br>40<br>43 |

|----|--------------------------------------------------------------------------------------------------------------|-------------------------------|

| 4. | Simulation Performance                                                                                       | 46                            |

|    | 4.1 Simulation model                                                                                         | 46                            |

|    | 4.1.1 Amplifier and predistorter model<br>4.1.2 Predistortion system model                                   | 46<br>49                      |

|    | 4.2. The predistortion tables                                                                                | 53                            |

|    | 4.2.1 AM to AM correction table<br>4.2.2 AM to PM correction table                                           | 53<br>56                      |

|    | 4.3 Single signal test                                                                                       | 57                            |

|    | 4.4 Two tone test                                                                                            | 61                            |

|    | 4.5 Summary                                                                                                  | 65                            |

| 5. | System Bandwidth Versus Cost                                                                                 | 70                            |

|    | 5.1 Bandwidth limiting factor                                                                                | 70                            |

|    | 5.1.1 Analog to digital converter<br>5.1.2 Digital to analog converter<br>5.1.3 Memories<br>5.1.4 Conclusion | 72<br>79<br>80<br>81          |

|    | 5.2 Bandwidth versus cost curve                                                                              | 82                            |

| 6. | Summary and areas of further study                                                                           | . 84                          |

| Bi | bliography                                                                                                   | 86                            |

| Ap | opendices                                                                                                    | 89                            |

.

# **TABLE OF CONTENTS (Continued)**

|                                             | <u>Page</u> |

|---------------------------------------------|-------------|

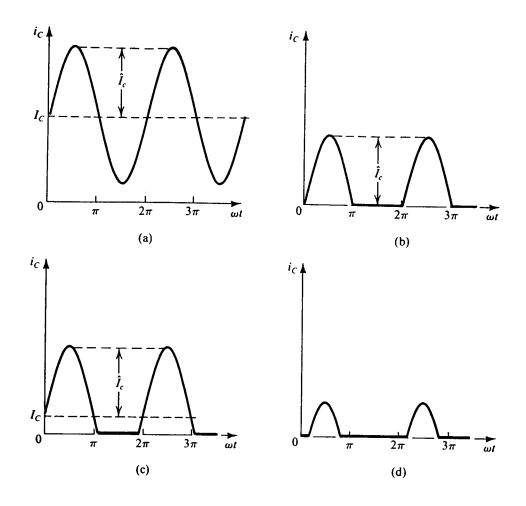

| Appendix A. Classification of Amplifier     | 90          |

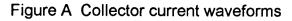

| Appendix B. The third order intercept point | 93          |

| Appendix C. Simulation program              | 97          |

.

### LIST OF FIGURES

| Figure |                                                                        | Page |

|--------|------------------------------------------------------------------------|------|

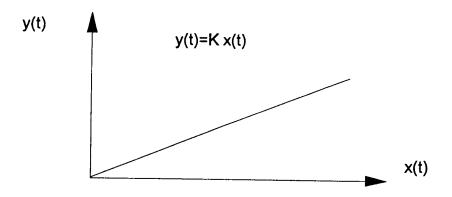

| 1.1    | Transfer characteristic of a linear amplifier (amplitude response)     | 3    |

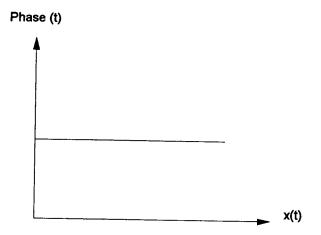

| 1.2    | Transfer characteristic of a linear amplifier (phase response)         | 4    |

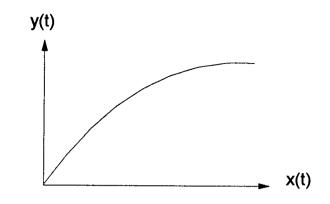

| 1.3    | Transfer characteristic of nonlinear amplifier (amplitude response     | e) 5 |

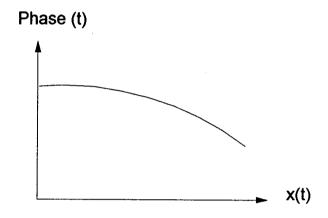

| 1.4    | Transfer characteristic of nonlinear amplifier (phase response)        | 5    |

| 1.5    | Block diagram of a feed forward amplifier                              | 6    |

| 1.6    | I/Q plane                                                              | 8    |

| 1.7    | I/Q modulator and demodulator                                          | 9    |

| 1.8    | Block diagram of a Cartesian feedback amplifier                        | 10   |

| 2.1    | Block diagram of a predistortion amplifier system                      | 12   |

| 2.2    | Block diagram of fixed baseband predistortion system                   | 13   |

| 2.3    | Block diagram of an adaptive predistortion system                      | 14   |

| 2.4    | Nagata's two dimensional look up table                                 | 16   |

| 2.5    | Cavers (1) predistortion system                                        | 17   |

| 3.1    | System block diagram                                                   | 21   |

| 3.2    | Spectrum of demodulation process                                       | 22   |

| 3.3    | Spectrum of shifted frequency band to baseband $\omega_1$ - $\omega_2$ | 23   |

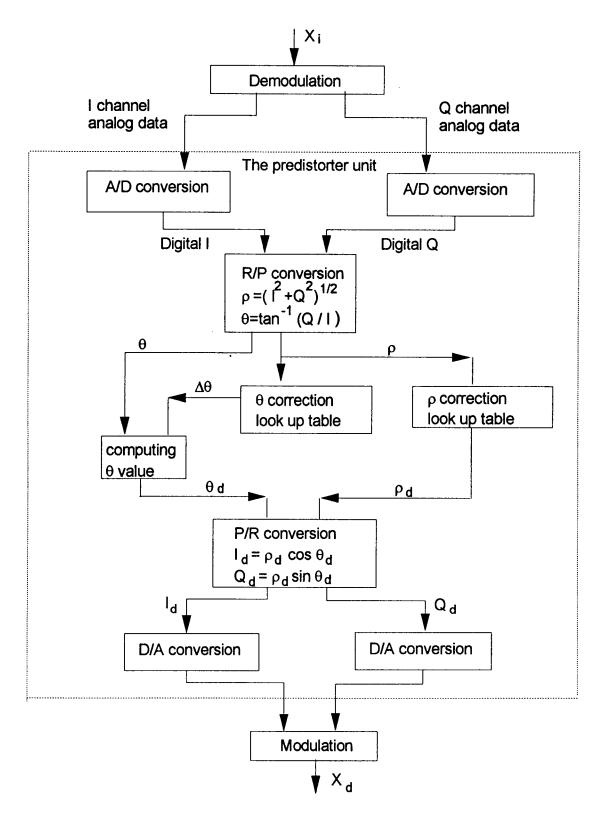

| 3.4    | Block diagram of predistorter unit                                     | 27   |

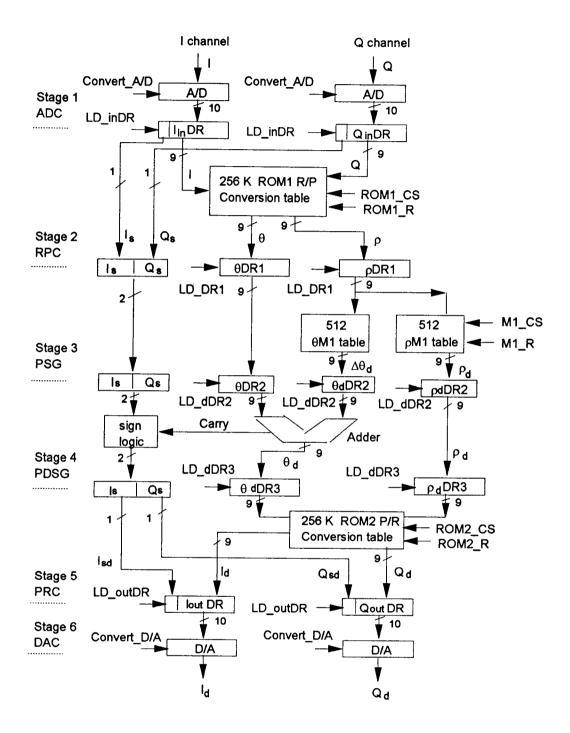

| 3.5    | The predistorter unit                                                  | 29   |

# LIST OF FIGURES (Continued)

| Figur | <u>Figure</u>                                                     |      |

|-------|-------------------------------------------------------------------|------|

| 3.6   | Symmetry of the I/Q plane                                         | 31   |

| 3.7   | Sign generating logic                                             | 33   |

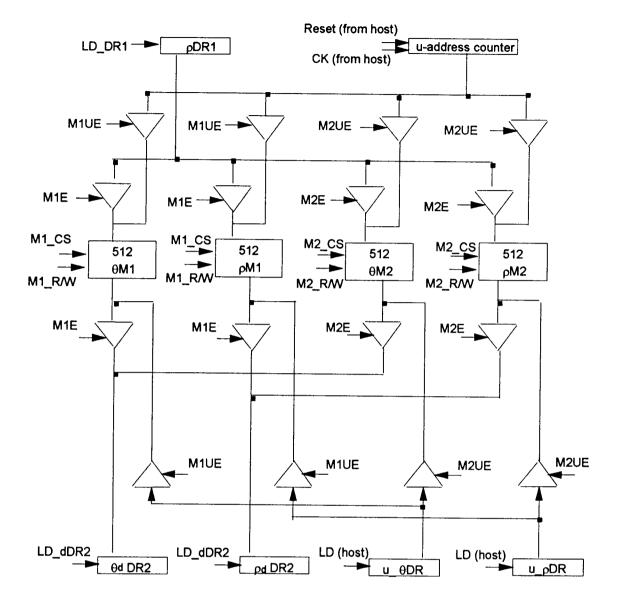

| 3.8   | Memory look up table (Table-set1 and Table-set2)                  | 35   |

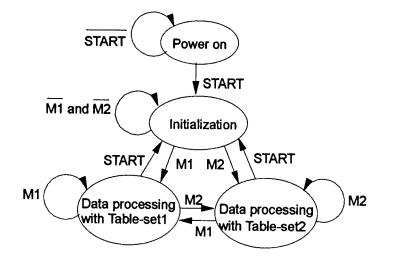

| 3.9   | Interchanges between modes                                        | 38   |

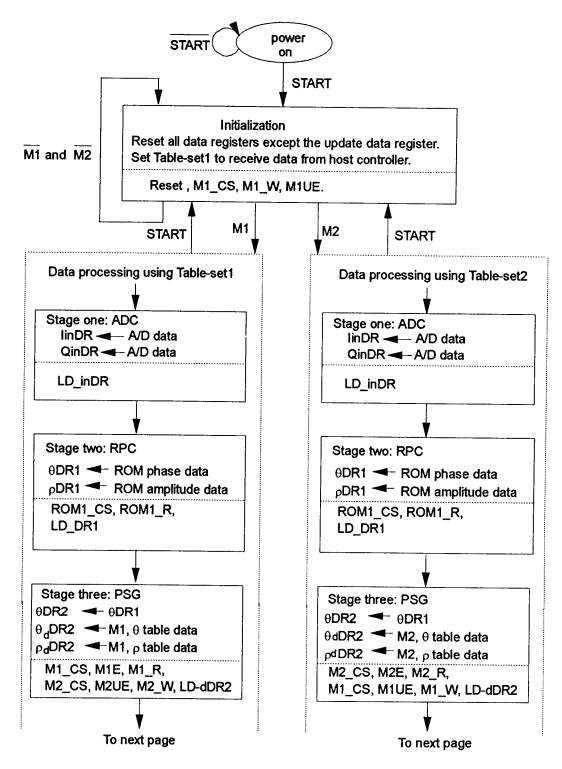

| 3.10  | Micro-operation diagram                                           | 39   |

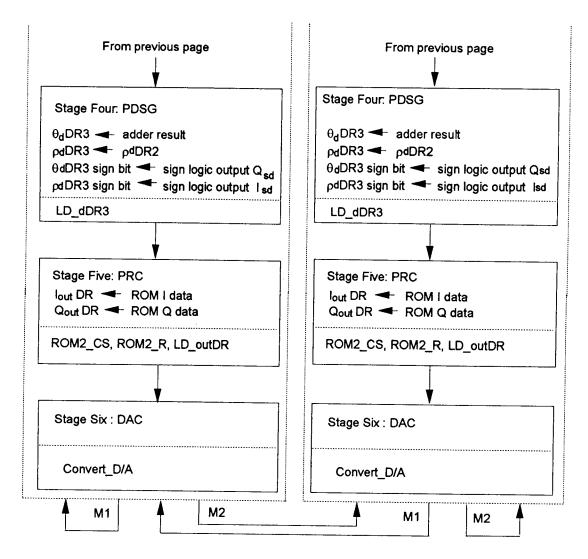

| 3.11  | The controller                                                    | 41   |

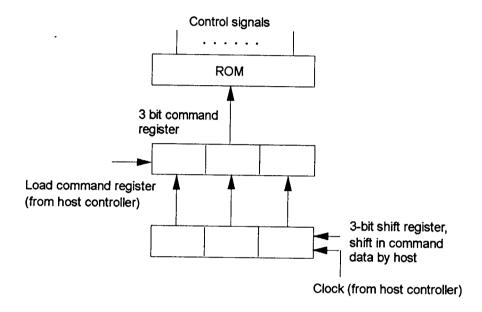

| 3.12  | Interface to host computer                                        | 44   |

| 4.1   | The predistortion system model                                    | 49   |

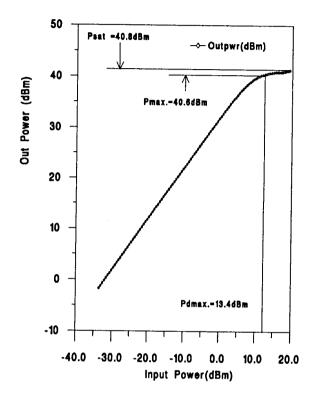

| 4.2   | Amplitude characteristic of PA9340                                | 51   |

| 4.3   | Phase characteristic of PA9340                                    | 52   |

| 4.4   | Maximum In/Out power of PA9340                                    | 54   |

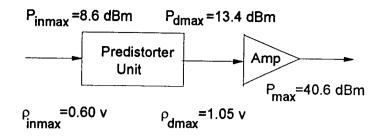

| 4.5   | Illustration of maximum input/output limit                        | 55   |

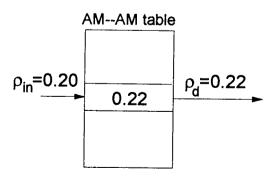

| 4.6   | The relation of $\rho_{in}$ and $\rho_{d}$                        | 55   |

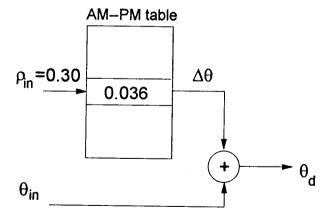

| 4.7   | The relation of $\rho_{in}$ , $\theta_{in}$ , and $\theta_d$      | 56   |

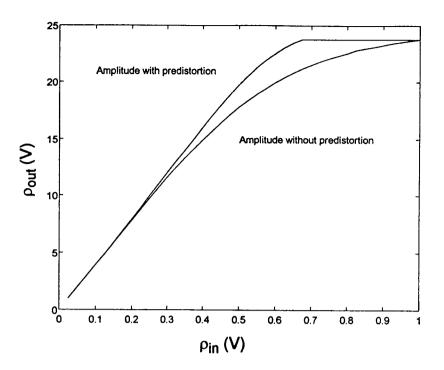

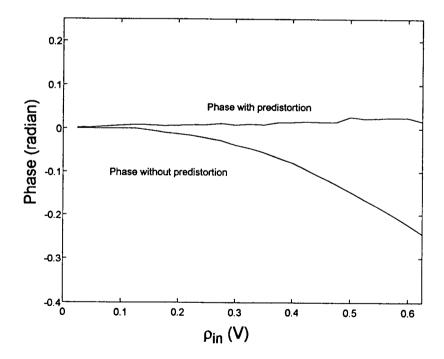

| 4.8   | Amplitude characteristic of the PA9340 with/without predistortion | n 60 |

| 4.9   | Phase characteristic of the PA9340 with/without predistortion     | 60   |

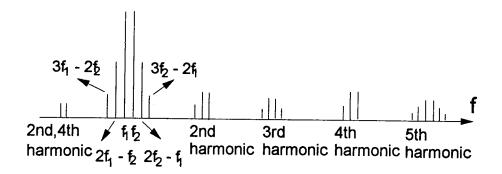

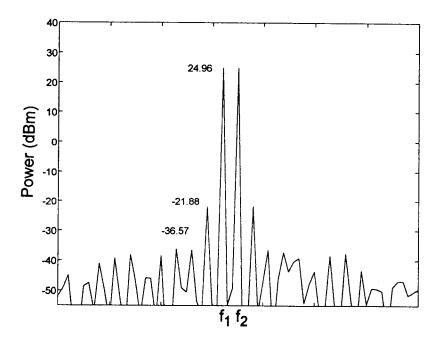

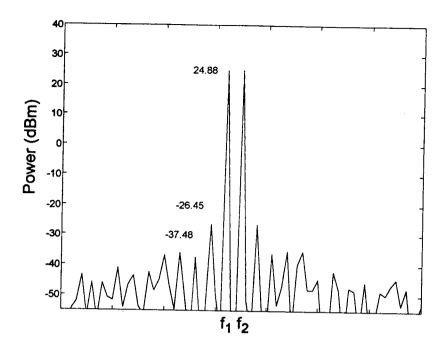

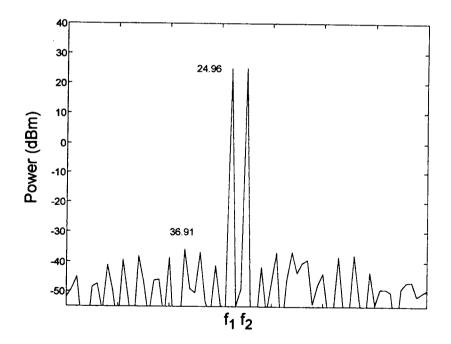

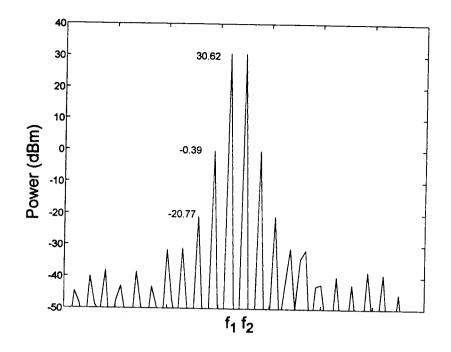

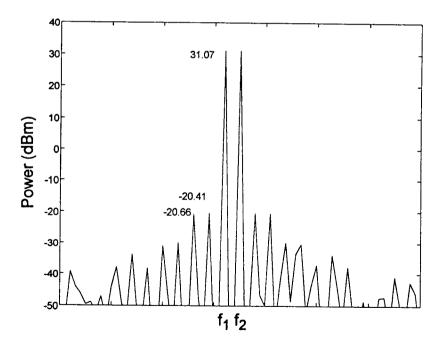

| 4.10  | Two signal intermodulation spectrum                               | 63   |

.

# LIST OF FIGURES (Continued)

| Figure |                                                                              | <u>Page</u> |

|--------|------------------------------------------------------------------------------|-------------|

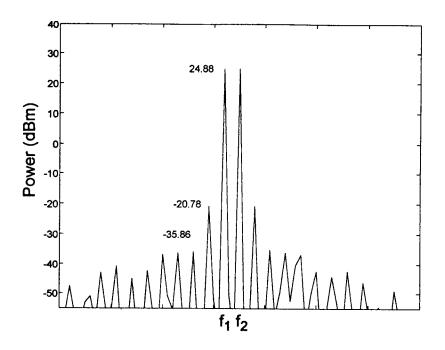

| 4.11   | Two tone test spectrum of the PA9340 without predistortion (-7 dBm input)    | 67          |

| 4.12   | Two tone test spectrum of the PA9340 with AM-AM predistortion (-7 dBm input) | 67          |

| 4.13   | Two tone test spectrum of the PA9340 with AM-PM predistortion (-7 dBm input) | 68          |

| 4.14   | Two tone test spectrum of the PA9340 with full predistortion (-7 dBm input)  | 68          |

| 4.15   | Two tone test spectrum of the PA9340 without predistortion (-1 dBm input)    | 69          |

| 4.16   | Two tone test spectrum of the PA9340 with full predistortion (-1 dBm input)  | 69          |

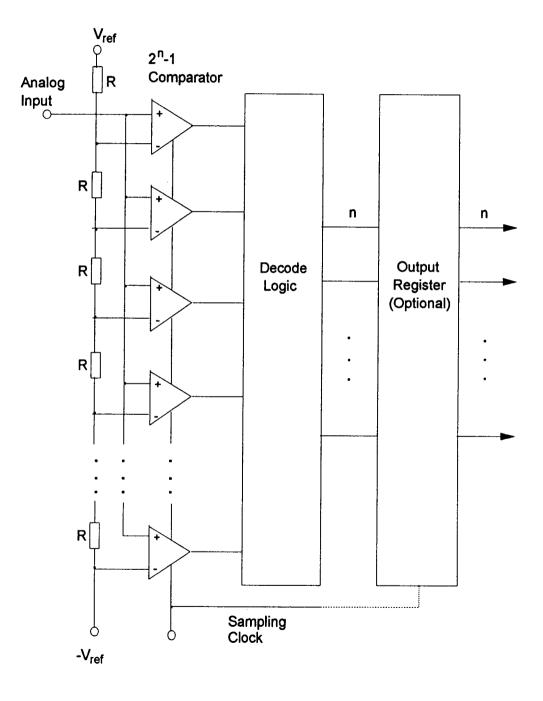

| 5.1    | Block diagram of a flash converter                                           | 73          |

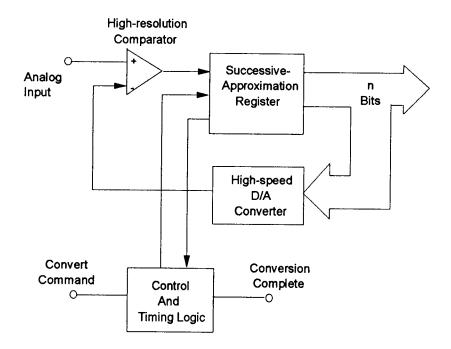

| 5.2    | Block diagram of a successive-approximation converter                        | 74          |

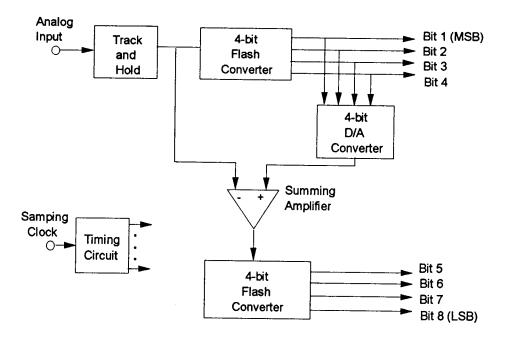

| 5.3    | Block diagram of a two stage subranging converter                            | 76          |

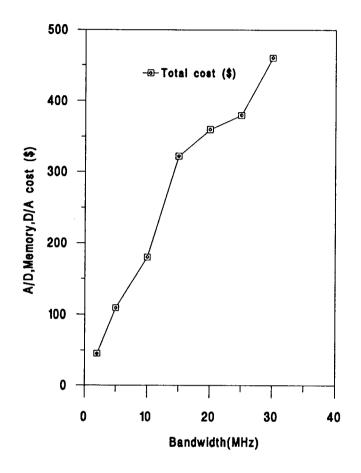

| 5.4    | Bandwidth versus cost                                                        | 83          |

•

## LIST OF TABLES

| Table |                | Page |

|-------|----------------|------|

| 5.1   | A/D converters | 77   |

| 5.2   | D/A converters | 79   |

| 5.3   | Memories       | 80   |

.

•

#### A Pipelined Baseband Digital Predistortion Architecture for RF Amplifier Linearization

#### Chapter 1. Introduction

Cellular telephone communication is becoming increasingly important in the world. Power amplifiers are essential elements in the signal processing path of Cellular system. Nonlinearity of an amplifier creates an interference problem by generating signals at undesired frequencies. The overall goal of this work is to develop a technique to linearize power amplifiers in cellular communication systems.

#### 1.1 Radio frequency (RF) amplifiers in Cellular communication systems

Signal amplification is important in Cellular communication systems. Depending on the application, radio frequency (RF) amplifiers can be classified as low noise and low power receiver amplifiers, or high power transmitter amplifiers.

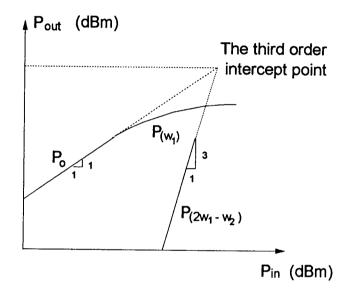

The receiver amplifier emphasizes lower noise figures and is able to handle weak signals. High dynamic range and high sensitivity allow the amplifier to deal with different amplitude signals that are received from the antenna. Receiver amplifiers are normally small signal class A amplifiers (definition of "class" is given in appendix A).

Transmitter amplifiers are normally power amplifiers. The noise figure is of minor interest since the transmitted signal is usually a known signal and the level can be controlled. For most applications, the efficiency is also a concern, especially in portable communication devices. For the purpose of obtaining high power efficiency, power amplifiers are normally class-AB, class-C or Class-A operating near the saturation condition. These types of amplifiers generally experience a degree of nonlinearity in their operating range.

In a multi-channel amplifier, when multiple RF signals are amplified simultaneously, intermodulation distortion is produced in the output due to the nonlinearity of the amplifier. These distortions can interfere with the signal being amplified.

In a single-channel amplifier, when non-constant envelope signals pass through the amplifier, the nonlinear distortion causes emissions and adjacent channel interference. Because of the limited RF spectrum, restrictions on emissions and levels of acceptable adjacent channel interference are stringent. RF linear amplification is required in mobile radio systems.

#### 1.2 Frequency spectrum of Cellular telephone system

In the US, the RF spectrums are set by FCC regulation. In cellular telephone communications, an RF frequency band is split into smaller fixed frequency channels. Multiple signals, each with a different carrier frequency, share the same transmission medium. This is called frequency multiplexing.

In the current US Cellular band, there are two 25 MHz frequency spectrums allocated for cellular phones, the frequency 824 MHz to 849 MHz is for mobile transmit and 869 MHz to 894 MHz is for base station transmit. Each of these 25 MHz band is split into 832 channels which are 30 kHz wide (21).

Amplifiers used in the Cellular system can cover a single channel or the whole band. Depending on the architecture, sometimes an amplifier shifts the

25 MHz spectrum from the high frequency band to the 0-25MHz frequency band. The signal is then processed. This lowest frequency band is often referred to as a baseband. Modulation and demodulation are used to shift signal to different regions of the spectrum.

# 1.3 RF amplifier nonlinear characteristic

In communication systems, an amplifier can be viewed as a two-port network. The output y(t) can be expressed as a function of the input x(t). That is, y(t) = H[x(t)].

If the output y(t) is a scaled version of the input x(t) and superposition applies, then the amplifier is a linear amplifier and the amplification is distortionless amplification. Figure 1.1 and Figure 1.2 show the amplitude and phase response of a linear amplifier. In the real world, there is no amplifier that has this type of ideal transfer characteristic. A typical RF amplifier's amplitude and phase characteristic is shown in Figure 1.3 and Figure 1.4 respectively. The transfer function is nonlinear.

Figure 1.1 Transfer characteristic of a linear amplifier (amplitude response)

Figure 1.2 Transfer characteristic of a linear amplifier (phase response)

Signal distortion resulting from passing a signal through an amplifier with a non-linear transfer characteristic is called "nonlinear distortion". Nonlinear distortion puts limits on the dynamic range of the amplifier. The dynamic range of an amplifier can be defined by its noise figure or its sensitivity as the lower limit and by its acceptable level of signal distortion as its upper limit. Normally, nonlinear distortion occurs when the signal level is high and the amplifier is driven into the saturation region. This type of distortion can be characterized as amplitude to amplitude distortion (AM-AM) and amplitude to phase distortion (AM-PM).

Figure 1.3 Transfer characteristic of nonlinear amplifier (amplitude response)

Figure 1.4 Transfer characteristic of nonlinear amplifier (phase response)

#### **1.4 Amplifier linearization techniques**

The simplest way of achieving linear amplification is to operate a class A amplifier far below saturation. The disadvantage is low power efficiency (Appendix A). In general, if power amplifiers are operated in the linear region of their transfer characteristics, they are power inefficient. If they are power efficient, they are normally not linear. The challenge is to maintain linearity and power efficiency at the same time. This is especially true if the amplifiers are being used in portable communication devices. One of the methods to solve

this problem is by using linearization techniques to make nonlinear power amplifiers more linear.

Many different techniques have been studied or proposed during recent years. Some techniques directly manipulate the high frequency RF carrier signals, such as feed forward correction and RF predistortion. Other techniques work with the baseband signal, then shifting the signal to high frequency RF carrier signal. Cartesian feedback and digital predistortion are examples of such techniques.

#### 1.4.1 Feed forward

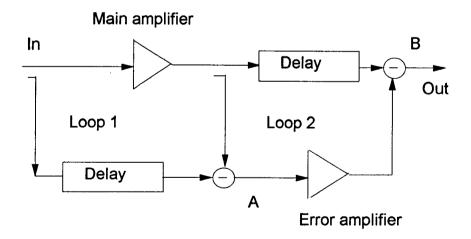

Feed forward amplifiers (11,14,15) apply the nonlinearity cancellation directly to the RF carrier signal. A simplified block diagram of feed forward amplifier is shown in Figure 1.5.

Figure 1.5 Block diagram of a feed forward amplifier

A feed forward amplifier consists of two loops. In loop 1, the input signal feeds into two paths. One goes through the main amplifier and the other to a linear circuit which delays the signal the same amount as the delay through the main amplifier. The original signal is distorted at the output of the main amplifier because of the nonlinearity of the amplifier. Part of the distorted signal is then subtracted from the delayed original signal at point A. These two signals are controlled so that they are of equal amplitude and 180° out of phase. Ideally the resulting error signal only contains the distortion information from the main amplifier to cancel out the distortion in the main path and form a non distorted amplified output signal at point B. Again, as in loop 1, two signals at point B must be equal in amplitude and 180° out of phase in order to cancel out the distortion.

The feed forward process is an open loop process. The bandwidth can be from ten's of MHz to hundred's of MHz (15). Therefore it is suitable for application on a wide-band system. In order to efficiently cancel out the distortion, the amplitude and phase of the signals must closely match in the amplifier and the delay paths. also the error amplifier must not generate any distortion of its own. The balances need to be within a few tenths of a dB and a few degrees to meet required linearity while optimizing maximum available output power.

#### **1.4.2 Cartesian feedback**

The Cartesian feedback method applies linearization techniques to the baseband signal. The baseband signal is transmitted by modulating a carrier

7

signal. Modulation is the process of encoding the low frequency baseband signal onto a carrier signal. The frequency of the carrier is compatible with the transmission medium being used.

The Cartesian feedback technique (3,12) was primarily designed to be applied in transmitter amplifiers where the baseband signal is available. It adjusts the signal according to the feedback from the output of the amplifier in the baseband, then shifts up to the RF carrier frequency for transmission.

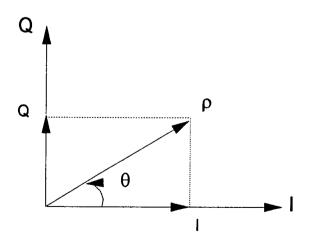

One common method to represent a digital baseband signal in a communication systems is to use a vector in a polar plot (21,23), as shown in Figure 1.6. The length of the vector,  $\rho$ , represents the magnitude of the signal while the angle,  $\theta$ , represents the phase of the signal. This vector can be further decomposed into two rectangular components. The two signals are referred to as the in-phase I and quadrature-phase Q and:

$$\theta = \tan^{-1} Q/I$$

$$\rho = \sqrt{(l^2 + Q^2)}$$

Figure 1.6 I/Q plane

With proper lengths selected for I and Q, any point can be generated in the plane.

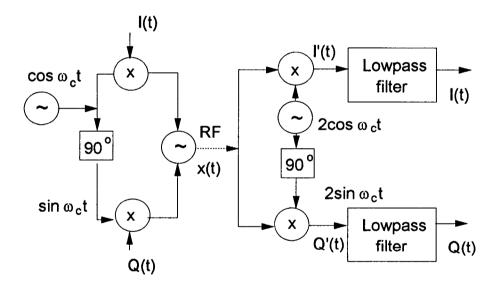

I and Q are modulated onto an RF carrier frequency by an I/Q modulator before final amplification and transmission. An I/Q modulator generates a sine and a cosine channel for I and Q data. Figure 1.7 shows the I/Q modulator and demodulator. The 90° phase shifter is used to generate the sine and cosine channels. Assume the I and Q signals are I(t) and Q(t) respectively, and the carrier signal is  $\cos_{c}t$ , then the modulated RF signal x(t) can be described as:

$x(t) = I(t)\cos\omega_{c}t + Q(t)\sin\omega_{c}t$

Figure 1.7 I/Q modulator and demodulator

The process that removes the carrier and separates the signal into I and Q components is called I/Q demodulation. The I channel signal is obtained by multiplying x(t) with  $2\cos\omega_c t$ . It can be shown that:

$$I'(t) = 2(I(t)\cos\omega_{c}t + Q(t)\sin\omega_{c}t)\cos\omega_{c}t$$

$$= I(t) + I(t)\cos2\omega_{c}t + Q(t)\sin2\omega_{c}t$$

The last two terms are suppressed by the low pass filter, yielding the desired output I(t). Similarly, by multiplying x(t) with  $2\sin\omega_c t$ , yielding:

$Q'(t) = 2(I(t)\cos\omega_c t + Q(t)\sin\omega_c t)\sin\omega_c t$

$= Q(t) + I(t)sin2\omega_{c}t - Q(t)cos2\omega_{c}t$

Q(t) is obtained from the resulting signal through the low pass filter.

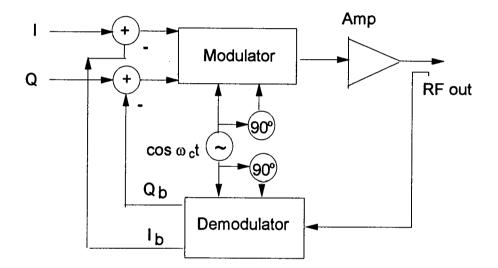

Figure 1.8 shows the block diagram of a Cartesian feedback amplifier.

Figure 1.8 Block diagram of a Cartesian feedback amplifier

The baseband input signal is in quadrature components, I and Q, format. The feedback path takes a portion of the output signal and demodulates it into quadrature components,  $I_b$  and  $Q_b$ , to provide negative feedback. Then  $I_b$  and  $Q_b$  are subtracted from the original I and Q input drive signal to generate a loop error signal. The Cartesian feedback is a closed-loop configuration. The linearizing bandwidth (the bandwidth over which the system is capable of performing linearization) of the Cartesian feedback system is on the order of ten's of kHz. Therefore it is suitable for a narrow-band application. The closed-

loop feature can easily compensate for changes in an amplifier's nonlinearities caused by component aging, temperature drifts or other changes.

#### 1.4.3 Predistortion

The idea of predistortion is to predistort the input signal prior to amplification. This counteracts the nonlinear characteristics of the amplifier and makes the overall system appear linear. A detailed discussion of this technique is given in Chapter Two.

#### **1.5 Thesis objectives**

Because linear amplification is essential and desirable for cellular radio systems, linear amplification techniques have been an important study topic in recent years. Researchers are studying various types of techniques. Each method has its advantages and disadvantages. Some may be better suited for one application than another, but there is no single best solution to the problem. Research is going in many directions. Digital predistortion is one of them.

The purpose of this work is to study various ways of realizing a digital predistortion technique in RF amplifiers. A practical architecture will be presented to implement a digital predistorter and explore the trade-offs between processing speed, circuit complexity, cost and system bandwidth.

#### **Chapter 2. Literature Review on Predistortion**

#### 2.1 Predistortion concept

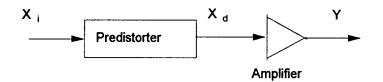

In predistortion amplifier systems, a module called a predistorter is placed between the input signal and the power amplifier. The predistorter is a nonlinear module providing an appropriately distorted signal to the amplifier to compensate for its nonlinearity (Figure 2.1). Like the feed forward system, the correction to the nonlinearity in the predistortion amplifier is an open-loop compensation. There are various ways to implement the predistorter. Most methods can be characterized by two major categories, namely, analog RF predistorters and baseband digital predistorters.

Figure 2.1 Block diagram of a predistortion amplifier system

#### 2.2 Analog RF predistorter

The analog RF predistorter places a network of active and passive components which are designed to compensate for the amplifier characteristics(9) between the signal and the input of the amplifier. Diodes are often used in the network to provide the nonlinear compensation. The correction can be fixed compensation, meaning that once the network is implemented, the correction will not change, or adaptive in which the correction can be continually adjusted with the change of the amplifier characteristics. Because of the open loop feature, RF predistortion is suitable for wide-band application. Due to the difficulty of designing a circuit that can perfectly match the amplifier, the cancellation is not complete.

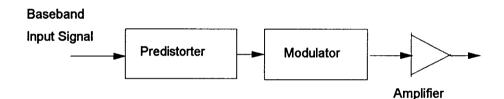

#### 2.3 Fixed baseband digital predistortion

Unlike RF predistortion, the signal predistortion in this technique takes place in the baseband. In fixed baseband digital predistortion, the signal is first predistorted, then modulated onto a carrier RF frequency and fed into the amplifier. Figure 2.2 gives a block diagram.

Figure 2.2 Block diagram of fixed baseband predistortion system

The advantage of predistorting the signal in the baseband is that digital techniques can be applied. Fixed digital predistortion is simple but will not compensate for changes in the amplifier due to aging, temperature or other reasons. For different amplifiers, the signal may need to be predistorted in a different way. This type of predistortion is not used much in practice.

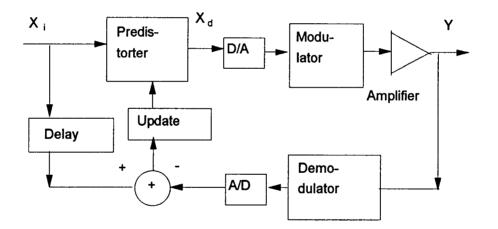

#### 2.4 Adaptive baseband predistortion

This implementation predistorts the baseband signal as in fixed predistortion but the predistortion circuit is adapted by an error signal from the output of the amplifier. The feedback is used only for compensating the drifts of the amplifier as a result of changing temperatures, aging and so on. The feed back is not used for real time modification of predistortion signals. Adaptive baseband predistortion is still an open-loop system in the sense of nonlinearity cancellation. The general block diagram of an adaptive predistortion system is shown in Figure 2.3

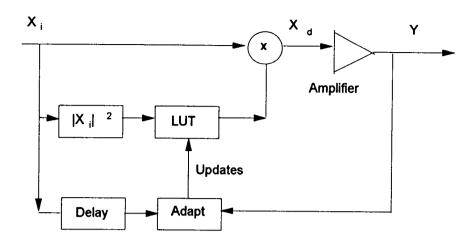

Figure 2.3 Block diagram of an adaptive predistortion system

The baseband digital modulated input signal,  $X_i$ , is predistorted to produce  $X_d$ , converted to analog form through a digital to analog (D/A) converter, then amplified through a power amplifier. The output signal is demodulated and fed back to compare with the appropriately delayed original signal. This generates an error signal to be used for adjusting the predistortion

circuit to adapt to changes in amplifier characteristics. The main problems in an adaptive predistortion system are generating the predistortion signal, monitoring the performance of the system and continuously adapting the predistorter as the characteristics of the amplifier change.

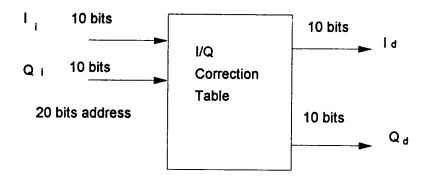

With the development of digital signal processing (DSP) and microcontroller techniques, digital adaptive predistortion has become very popular. Several adaptive predistortion systems that make use of microcontrollers, memory look-up tables(LUT) and DSP techniques have been reported in recent years (8,1,2,5,6). One of the most general and powerful methods was reported by Nagata (8) in 1989. In his implementation, the input signal,  $X_i$ , is represented in quadrature format. The signals, I and Q, are used as addresses of a two-dimensional memory LUT to generate a predistorted signal,  $X_d$ . The output,  $X_d$ , from the LUT is also in quadrature format,  $I_d$  and  $Q_d$ . The mapping of the two is from the I/Q plane to itself. This implementation is not restricted by the type of modulation used. On the other hand, since I and Q carry both amplitude and phase information, the amplifier's amplitude and phase characteristics can be compensated by X<sub>d</sub>. The number of quantization bits plays an important role in the performance of the system. The more bits. the more precisely the signal is represented in the plane. This provides better cancellation of the amplifier nonlinearity. But the more bits, the larger the memory look up table will be. Nagata's study showed that 10 quantization bits were sufficient to achieve reasonable nonlinearity cancellation. The size of the two-dimensional look up table is 20M bits (2^20x20 bit) (Figure 2.4). The table is updated when the nonlinearity is changed. Since the time required to update the LUT is proportional to the size of the memory, each iteration in the adaptive process requires a significant length of time.

Figure 2.4 Nagata's two dimensional look up table

In 1990, Cavers (1) used a one-dimensional table to reduce the memory size. The idea is based on that an amplifier's AM-AM and AM-PM distortion are input signal level dependent (19,1,2). This implies that the magnitude of the input signal can be used to generate correction signals for both amplitude and phase. A complex gain which contains both amplitude and phase information is first defined, the coefficients of this complex gain are stored into a memory look-up table, then the squared magnitude of the input signal is used as a table index to obtain the coefficients. These coefficients are used to calculate predistorted signal X<sub>d</sub> (Figure 2.5). Since calculations are required to obtain X<sub>d</sub>, the table size is reduced in the expense of computation load. Both the squared magnitudes of X<sub>i</sub> and the multiplication of X<sub>i</sub> by the table values have to be performed between data samples.

Figure 2.5 Cavers (1) predistortion system

Based on the same factor that the distortion in the power amplifier is essentially caused by amplitude variations, M. Faulkner (2) used the input amplitude as the index of an amplitude and a phase correction table. The lookup tables are much smaller than Nagata's two-dimensional table and the update to the table is much faster. This approach requires processing time to perform rectangular (I and Q) to polar (magnitude and phase) conversion.

Stapleton and Cavers (5) took another approach to implement the predistorter. They modeled the predistorter and power amplifier output as two truncated complex power series up to the fifth order. The coefficients of the power series are complex so that they can accurately represent the AM-AM and AM-PM distortion in a power amplifier. By properly choosing the coefficients of the predistorter, the distortion of the amplifier can be minimized. The adaptation is accomplished by iterative adjustment of the coefficients of the power series to minimize the distortion in the output of the amplifier. Later, Stapleton and Costesua (6) presented a detailed discussions of how to measure the distortion and use a microcontroller to adjust the coefficients.

Nested multiplication is used to implement the power series polynomial. Clearly the computation load is high in this implementation.

Digital predistortion allows more freedom in handling the cancellation of the nonlinearity since the cancellation is performed through software by using DSP techniques. The restriction is the bandwidth. Because of processing speed limitation, all the systems reported in the literature are limited to narrowband systems. The linearizing bandwidth is similar to that of the Cartesian feedback system which is in the range of 10 to 30 KHz.

#### **Chapter 3. Architecture Design**

#### 3.1 The design goal

The goal of this work is to design a baseband digital predistorter that can be used as a building block in an adaptive predistortion amplifier system. The work is focused on exploring the methods that can be used and the performance that can be achieved rather than meeting some particular specification.

The digital predistortion techniques discussed in Chapter 2 are all implemented in narrow-band systems. Nagata's implementation is simple but requires the use of a large memory table which would require extensive time to update. Caver, Faulkner and Stapleton's implementation require heavy computation to obtain the correction signal. These methods work well for a single channel (a few ten's of kHz) in the mobile communication band. When the bandwidth increases to the order of MHz, these techniques will not work due to the limitation on the processing speed. A new architecture is proposed in this thesis to implement a digital predistorter in wider bandwidth systems.

The predistorter should have the following features:

1. General purpose. The architecture should not be restricted to a particular amplifier or modulation type.

2. Wide bandwidth. In most mobile communication systems, the transmit and receive bands comprise a 20 MHz to 30 MHz frequency spectrum. It is preferable to have an amplifier that can cover the whole frequency band rather than a single channel or a few adjacent channels.

3. Simple interface. The predistorter should have a simple interface and be controlled by a microcontroller or personal computer.

4. Cost effectiveness. The circuit should be simple and realizable by using commercially available components. Eventually the circuit could be integrated into one or more ASICs.

### 3.2 Architecture design consideration

All the baseband predistortion systems reported so far use DSP microprocessors. Because of the limitation in processing speed, it is not possible to implement a predistorter with 20 MHz bandwidth by using the existing DSP implementation methods described in Chapter 2. For example, suppose a DSP processor with a 50 MHz clock rate and 12.5 MHz instruction rate is used. A look-up table structure is utilized in the predistorter. Between two data samples, the DSP processor must read data from the table and process this data (addition, subtraction or multiplication depending on the algorithm). Assuming 10 instructions are required to process a data unit, then the fastest data sample rate is 12.5 MHz/10 = 1.25 MHz. According to the Nyquist sample theorem, the sample rate must be at least twice the maximum frequency component of the real time spectrum in order to avoid aliasing. With a sample rate of 1.25 MHz the actual linearizing bandwidth is limited to 0.625 MHz maximum. That means that a DSP implementation will not be suitable for use in a wide-band predistorter.

To achieve 25 MHz of signal bandwidth, the real time processing speed must not exceed 20 nanoseconds. Direct hardware implementation of the predistorter with a pipeline structure and as little data manipulation as possible seems to be a feasible approach. The requirement for less data manipulation also suggests the use of a look-up table rather than computation to generate predistortion signals.

As discussed in Chapter 2, predistortion correction is an open-loop operation. The correction must be performed in real time. But the adaptation is only for tracking the slow changes in the amplifier characteristic, such as the drifts with temperature and component aging. A general purpose microprocessor or personal computer can be used to handle the adaptation portion of the system.

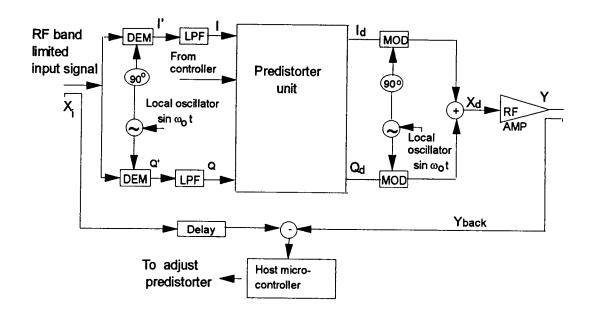

A block diagram of the proposed system is shown in Figure 3.1. The RF band-limited input signal,  $X_i$ , is first demodulated via a quadrature demodulator.

Figure 3.1 System block diagram

The quadrature demodulation process shifts the high frequency input signal to low frequency and represents the signal with two components, in phase component, I' and quadrature component, Q'.

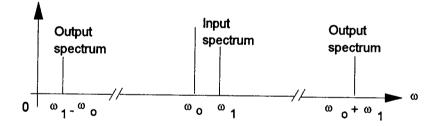

For example, let the input RF signal be  $X_i=Asin\omega_1 t$ , and the local oscillator frequency in the demodulation process be  $\omega_0$ , then the outputs of the quadrature demodulation circuit are:

$$I' = X_i \cos \omega_0 t$$

= A sin  $\omega_1 t \cos \omega_0 t = (A/2) [sin (\omega_1 + \omega_0)t + sin (\omega_1 - \omega_0)t]$

Q' = X<sub>i</sub> sin  $\omega_0 t$

= A sin  $\omega_1 t$  sin  $\omega_0 t$  = (A/2) [ cos ( $\omega_1 + \omega_0$ )t - cos ( $\omega_1 - \omega_0$ )t]

The input and output spectrum are shown in Figure 3.2.

Figure 3.2 Spectrum of demodulation process

The frequency  $\omega_0$  can be selected so that the signal components at frequency ( $\omega_1 - \omega_0$ ) which contains all the information of X<sub>i</sub> are in the desired low frequency region, such as in a baseband. The signal components at frequency ( $\omega_1 + \omega_0$ ) are at approximately twice the frequency of  $\omega_1$  and thus can be suppressed by a low pass filter. The low pass filtered baseband signals, I and Q now are:

$$I = (A/2)\sin(\omega_1 - \omega_0)t$$

$Q = (A/2)\cos(\omega_1 - \omega_0)t$

Since this process shifts the signal from high carrier frequency to the low baseband frequency, it is also referred to as a frequency down-conversion process.

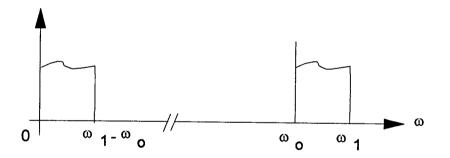

For an amplifier which covers one of the 25 MHz cellular bands, the local oscillator frequency  $\omega_0$  can be selected at the edge of the band, so that the whole band would be folded back into a low frequency region with the same bandwidth. Figure 3.3 shows that  $\omega_0$  is selected at the low edge of the working band, where  $\omega_1$  is the highest frequency in the band and  $\omega_1 - \omega_0$  is the bandwidth.

Figure 3.3 Spectrum of shifted frequency band to baseband  $\omega_1$ -  $\omega_2$

By choosing an I and Q implementation, the system can handle different types of signals because any signal can be represented by its I and Q components. The I and Q channels are symmetrical which simplifies the hardware.

After being demodulated, the I and Q signals are then fed to the digital predistorter unit. The predistorter unit predistorts the signal to  $I_d$  and  $Q_d$  according to the amplifier's nonlinearity. It then brings the signal back to the

RF carrier frequency,  $X_d$ , by a modulation process.  $X_d$  drives the amplifier.  $X_d$  is given as:

$X_d = I_d \cos \omega_0 t + Q_d \sin \omega_0 t$

Notice that the local oscillator frequency  $\omega_0$  here is the same as  $\omega_0$  in the demodulation process. Since the modulation process shifts the signal from baseband frequency to the high carrier frequency, it is also referred to as frequency up-conversion process.

After amplification, part of the output signal,  $Y_{back}$ , is fed back and compared with the delayed input signal to produce an error signal. The microcontroller uses this signal to adjust tables in the predistorter to minimize the error.

The predistorter unit consists of analog-to-digital (A/D) converters, data processing hardware and digital to analog (D/A) converters. According to the Nyquist sample theorem, for a 25 MHz bandwidth signal, the sample rate must be at least 50 MHz. This means that the predistorter unit needs to be able to process each data in a 20 nanosecond (ns) time period. To ensure fast processing speed, a pipeline structure is used in the predistorter unit. Two one-dimensional look-up tables are used in the unit to produce predistorted signals. The unit is controlled by a microcontroller.

A previous study by Nagata (8) has indicated that direct mapping of the predistorted signals,  $I_d$  and  $Q_d$ , from I and Q requires the use of large twodimensional look-up table. This slows down the adaptation processes. Alternatively, the amplitude of the signal can be used to generate correction signals for both amplitude to amplitude (AM-AM) and amplitude to phase (AM-PM) distortions since both distortions are input signal level dependent. This implies that the input signal amplitude can be used as an address in the correction table. A two-dimensional table can be reduced to a one-dimensional table. This is the approach taken in this work.

The correction look-up tables in the predistorter unit are functions of the input amplitude. A rectangular to polar (R/P) conversion is required to convert I and Q format into amplitude( $\rho$ ) and phase( $\theta$ ) format. The simplest and fastest way to perform this conversion is the use of a look-up table. This conversion table is a two-dimensional table and the size may be large. The difference between a conversion table and the correction table is that no update is required in the conversion table. The size of the conversion table does not affect system performance.

#### 3.3 The predistorter unit

#### 3.3.1 Block diagram

Figure 3.4 shows the block diagram of the predistortion unit. The input data of the predistorter unit are the I channel and Q channel analog baseband data. They are provided by the demodulation process. I and Q are converted into digital data by a pair of A/D converters. The outputs of these two A/D converters are used as addresses of a rectangular to polar conversion look-up table. The outputs of the look-up table are amplitude,  $\rho$ , and phase,  $\theta$ , which are the polar format of the input signal.

$$\rho = \sqrt{(l^2 + Q^2)}$$

$\theta = \tan^{-1}(Q/I)$

The amplitude signal,  $\rho$ , is used as an address for the AM-AM and AM-PM correction tables. The output of the amplitude correction table is the predistorted amplitude signal,  $\rho_d$ . This signal is directly used as the amplitude of the drive signal for the amplifier. The phase correction signal,  $\Delta \theta_i$ , which is the output of the AM-PM correction table, is added to the original phase signal to produce a new phase of the drive signal,  $\theta_d$ .  $\rho_d$  and  $\theta_d$  are then converted back to the I and Q format through a polar to rectangular conversion look-up table. The outputs of this table are:

$$I_d = \rho_d \cos\theta_d$$

$Q_d = \rho_d \sin \theta_d$

$I_d$  and  $Q_d$  are then converted back to analog format by a pair of D/A converters and up-converted to the RF carrier frequency to drive the amplifier.

Figure 3.4 Block diagram of predistorter unit

### 3.3.2 Digital processing architecture

As shown in the block diagram, each data sample passes through several steps in the predistorter unit. To achieve fast data processing speed, a six-stage pipeline structure is used. Each stage of the pipeline performs one processing task per clock cycle. After the initial pipeline latency, the unit can accept and output one data value in every clock cycle. In one clock period, a pipeline segment needs to allow time for performing logic functions, register set up and signal propagation. The propagation time for a compact unit is negligible and the set up time for the fast logic register is about 2 ns. The time for performing logic functions must not exceed 18 ns for a 20 ns clock cycle. For a 20 ns clock period, the total latency of the six-stage pipeline is 120 ns. In cellular communications, the information transmitted is mainly voice signals. A time delay of 120 ns has almost no effect on the original signal and is not noticeable in human speech.

A detailed block diagram of the pipelined predistorter is shown in Figure 3.5. The inputs to the unit are I and Q, and outputs are predistorted signals,  $I_d$  and  $Q_d$ . The following section discusses the unit in detail, stage-by-stage along the pipeline. There are data registers for intermediate storage between stages.

Figure 3.5 The predistorter unit

#### **Stage one:** Analog to digital conversion (ADC)

As discussed in Chapter 2, at least 10 quantization bits are required to achieve sufficient system resolution. Increasing the number of quantization bits gives the system more resolution and accuracy but raises the cost. The cost of most components are increased by resolution and speed, especially the A/D converters.

The digital signals generated by the A/D converter are stored in the I channel input data register, I<sub>in</sub>DR, and Q channel input data register Q<sub>in</sub>DR. I<sub>in</sub>DR and Q<sub>in</sub>DR are data sources to the next stage.

The sample rate requirement for A/D is at least 50 MHz for a 25 MHz bandwidth RF signal.

**Stage two:** Rectangular to polar conversion (RPC)

This stage performs a rectangular to polar (R/P) conversion to obtain the amplitude  $\rho$  and phase  $\theta$  from I and Q by using a two-dimensional look-up table.

The input and output relationships of this conversion table are:

$$\rho = \sqrt{(l^2 + Q^2)}$$

$$\theta = \tan^{-1} (Q/l)$$

Where I and Q are the input data, and  $\rho$  and  $\theta$  are the output data from the table.  $\rho$  and  $\theta$  are only dependent on I and Q and independent of other system operation parameters. Since  $\rho$ ,  $\theta$  and I, Q are mathematically defined, the content of the table is fixed. The R/P conversion table can be implemented in ROM memory.

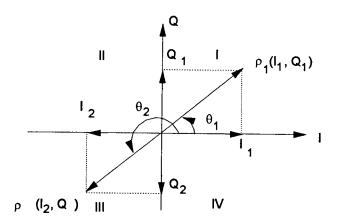

The size of the R/P conversion table is proportional to the number of bits in the I and Q signals. A 10-bit I and 10-bit Q will result in a 20 M-bit table. The table size can be reduced by taking advantage of the symmetry of the I/Q plane, as shown in Figure 3.6. By keeping track of the quadrant the signals are located in, the  $\rho$  and  $\theta$  in any location of the plane can be calculated from the  $\rho$  and  $\theta$  of the first quadrant. This decreases the size of the table by three-fourths. However, some hardware is necessary to keep track of the quadrant.

If the sign-magnitude form is selected as the digital data format, the sign bit can be used to keep track of the phase while the magnitude bits can be used as the address to access the conversion table. The table is pre-computed according to the range of I and Q. The sign bits from the I and Q channels are not used in this stage and are forwarded to the next stage.

Figure 3.6 Symmetry of the I/Q plane

Two data registers,  $\rho DR1$  and  $\theta DR1$ , are used to hold the output data from the conversion table.

Stage three: Predistorted signal generation (PSG)

This stage generates two predistorted signals,  $\rho_d$  and  $\Delta \theta_d$ , using the AM-AM and AM-PM correction tables.

The contents of these two tables are pre-generated according to the amplifier nonlinearity and loaded during initialization. When the amplifier nonlinearity changes, the tables must be updated. These tables are stored in RAM memory. The size of each look-up table is 512 words for a 9 bit address. These two tables are critical to the system.

The phase( $\theta$ ) of the original signal is not modified in stage four, it is passed to the next stage from  $\theta$ DR1 $\rightarrow$  $\theta$ DR2. The sign signals are also directly passed through.

Stage four: Phase predistorted signal generation (PDSG)

An adder is used to combine the predistorted phase signal,  $\Delta \theta_d$ , from the AM-PM table with the original phase,  $\theta$ , and produce a phase offset signal,  $\theta_d$ , for the amplifier. The fast processing time requires the adder be a high performance adder with a carry look ahead circuit.

As described in Stage 2, the phase information in the data register  $\theta$ DR2 only reflects the phase in the first quadrant of the I/Q plane. The real phase can be formed by the sign bits of I and Q. For example, if I and Q are both greater than 0, the signal is located in the first quadrant and no correction is required; if I>0 and Q<0, the signal is located in the fourth quadrant (marked as IV in Figure 3.6) and the real phase is equal to  $2\pi$ -(phase in  $\theta$ DR2).

Actually, there is no need to compute the absolute phase, but only to generate the correct sign bits for the  $I_d$  and  $Q_d$  signals. This can be done by monitoring the carry signal from the adder. If a carry is produced from the adder, which means the predistorted signal is shifted to the next quadrant, then the original signs of  $I_s$  and  $Q_s$  must be corrected. Logic is used to produce the correct signs,  $I_{sd}$  and  $Q_{sd}$ , according to  $I_s$ ,  $Q_d$  and the carry. The relationship is shown in Figure 3.7.

In Figure 3.7,  $I_s$  and  $Q_s$  are the I-channel and Q-channel sign bits respectively. C is a carry produced by the adder.  $I_{sd}$  and  $Q_{sd}$  are predistorted I-channel and Q-channel sign bits respectively.

The output data from this stage are  $\rho_d$  and  $\theta_d$  and they are stored in data registers,  $\rho_d DR3$  and  $\theta_d DR3$ .

| Quadrant         | ls | Qs                                                         | С | l <sub>sd</sub> | Q <sub>sd</sub> |

|------------------|----|------------------------------------------------------------|---|-----------------|-----------------|

| I                | 0  | 0                                                          | 0 | 0               | 0               |

| 11               | 1  | 0                                                          | 0 | 1               | 0               |

|                  | 1  | 1                                                          | 0 | 1               | 1               |

| IV               | 0  | 1                                                          | 0 | 0               | 1               |

| I                | 0  | 0                                                          | 1 | 1               | 0               |

| 11               | 1  | 0                                                          | 1 | 1               | 1               |

| 111              | 1  | 1                                                          | 1 | 0               | 1               |

| IV               | 0  | 1                                                          | 1 | 0               | 0               |

| Logic relations: |    | $I_{sd} = I_s \cdot \overline{C} + C \cdot \overline{Q}_s$ |   |                 |                 |

|                  |    | $Q_{sd} = Q_s \cdot \overline{C} + C \cdot I_s$            |   |                 |                 |

Figure 3.7 Sign generating logic

**Stage 5:** Polar to rectangular conversion (PRC)

A ROM table is used to perform the polar to rectangular conversion. For the same reason as in Stage 2, sign bits are not used in memory access, but appended to the output data. The table is the same size as the table in Stage 2. The outputs of the table are:

$$I_d = \rho \cos\theta$$

$Q_d = \rho \sin\theta$

At this point, the digital predistorted signals,  $I_d$  and  $Q_d$ , have been generated, and they are ready to be converted back to analog signals.

Stage 6: Digital to analog conversion (DAC)

The predistorted digital signals,  $I_d$  and  $Q_d$ , are converted to analog signals by a pair of D/A converters. The analog signals then are up-converted and summed to form an RF drive signal,  $X_d$ , for the amplifier.

# 3.3.3 Updating the memory table

To ensure real time performance and provide adaptability, two sets of the memory tables (Table-set1 and Table-set2) are employed. One set can be used in real time while the other set can be used in the update process.

The interconnection of Table-set1 ( $\theta$ M1,  $\rho$ M1) and Table-set2 ( $\theta$ M2,  $\rho$ M2) is shown in Figure 3.8.

Figure 3.8 Memory look up table (Table-set1 and Table-set2)

Assume that memory Table-set1,  $\theta$ M1 and  $\rho$ M1, is used for the real time processing, and Table-set2,  $\theta$ M2 and  $\rho$ M2, is used for updating. The data paths are created by setting the correct control signals in the tri-state devices. The control signals, M1E (Table-set1 enable), enables the content of  $\rho$ DR1 to provide an address to the  $\theta$ M1 and  $\rho$ M1 tables. It also creates paths for the predistorted signals,  $\rho_d$  and  $\Delta\theta_d$ , (output from the tables), to reach data

registers  $\rho_d DR2$  and  $\theta_d DR2$ . The control signal, M2UE, connects data from the update data register, u- $\rho DR$  and u- $\theta DR$ , to Table-set2. The address to M2 is generated by the update address counter, u-address counter. The update data register, update address counter and update data register are controlled by the host computer.

The host computer updates the table by sending a signal to initialize the address counter. It sends data to the update data registers. It than loads the data to the memory table. The host then advances the counter and sends another data unit. It repeats the steps until all the tables are loaded. The update to the table is sequential from location 0 to 511. When M2 is fully updated, the host computer sends a command to switch the memory units. M2 will now work in real time and M1 is ready to be updated.

With this arrangement, memory update is performed off line and does not affect the processing speed of the system. At the moment the table is switched, new corrections are applied. This results in some data using old corrections and some using new corrections. This is not a problem, because the update is mainly for slow drift of the amplifier's nonlinearity. New correction data are only slight changes of the old ones.

# 3.3.4 Micro-operation diagram

The predistortion unit has three operation modes, an initialization mode and two data processing modes with either Table-set1 or Table-set2 operating in real time.

The host computer sends commands to the unit to trigger changes between modes. The command is stored in a command register to generate control signals for the unit. The control commands are encoded into 3-bit format as follow:

| Command code | Name  | Operation                         |

|--------------|-------|-----------------------------------|

| 100          | START | initialization                    |

| 001          | M1    | begin processing using Table-set1 |

| 010          | M2    | begin processing using Table-set2 |

The diagram of the interchanges between modes is shown in Figure 3.9.

When power on, the unit waits for the START command from the host computer. When START is received, the unit enters the initialization mode.

In the initialization mode, the unit resets all the data registers except the update data register. It then puts memory Table-set1 into the ready-to-receive (RTR) data state. The unit then waits until the host computer finishes loading the table into Table-set1.

After loading the table, the host computer sends a command to start data processing.

In the data processing modes, the unit receives one data unit from the A/D converter in each clock cycle. Also in each clock cycle, a data unit is processed by one pipeline stage. The first data requires 6 clock cycles to process. After that, there will be one processed data unit output per cycle. The unit either uses Table-set1 as the real time working table and Table-set2 as the update table or vice versa.

Figure 3.9 Interchanges between modes

The micro-operation diagram is shown in Figure 3.10. Each of the rectangular boxes indicates the action in each clock cycle. The upper half of the box shows the register to register transfer action and the lower half of the box indicates the required control signal to carry out the action. The control commands to switch modes are also shown.

Figure 3.10 Micro-operation diagram

Figure 3.10 Micro-operation diagram (Continued)

# 3.3.5 The controller

The controller generates control signals for the predistorter unit. Since only a few operations are carried out by the unit, the controller is relatively simple. It consists of a 3-bit command register and a ROM. The control command from the host computer is stored in the command register. The output of this register provides addresses to a ROM which produces the control signals for the unit. There are a total of 20 control signals. A ROM of at least  $8 \times 20$  bits is enough to provide control signals. By using the ROM, the controller is much more flexible than a controller designed with hardwired logic. The content of the ROM can easily be modified to fit any design changes.

The block diagram is shown in Figure 3.11.

Figure 3.11 The controller

The communication between host and the unit is in serial format (this will be explained in next section). A command issued by the host computer is first shifted into a 3-bit shift register then loaded to the command register. The control signals associated with this command are then generated from the ROM. Refer to Figure 3.10, the Micro-operation diagram, for the use of the control signals.

The control signals are as follows:

signal name Function

1 Convert\_A/D Start A/D data conversion

| 2  | LD_inDR     | load input data registers, I <sub>in</sub> DR and Q <sub>in</sub> DR    |

|----|-------------|-------------------------------------------------------------------------|

| 3  | ROM1_CS     | Rectangular to polar conversion ROM1 chip select                        |

| 4  | ROM1_R      | ROM1 read                                                               |

| 5  | LD_DR1      | Load data registers, $\rho DR1$ and $\theta DR1$                        |

| 6  | M1_CS       | Look-up table memory Table-set1 chip select                             |

| 7  | M1_R/W      | M1 read/write                                                           |

| 8  | M2_CS       | Look-up table memory Table-set2 chip select                             |

| 9  | M2_R/W      | M2 read/write                                                           |

| 10 | M1E         | Enable Table-set1 as real time look-up table                            |

| 11 | M1UE        | Enable Table-set1 as update table                                       |

| 12 | M2E         | Enable Table-set2 as real time look-up table                            |

| 13 | M2UE        | Enable Table-set2 as update table                                       |

| 14 | LD_dDR2     | Load predistorted data registers, $\rho_{d} DR2$ and $\theta_{d} DR2$   |

| 15 | LD_dDR3     | Load predistorted data registers, $\rho_{d} DR3$ and $\theta_{d} DR3$   |

| 16 | ROM2_CS     | Polar to rectangular conversion ROM2 chip select                        |

| 17 | ROM2_R      | ROM2 read                                                               |

| 18 | LD_outDR    | Load output data registers, I <sub>out</sub> DR and Q <sub>out</sub> DR |

| 19 | Convert_D/A | Start D/A data conversion.                                              |

| ~~ | <b>D</b> (  |                                                                         |

20 Reset Reset all data registers except the update register

During the data processing operation, the control signals for each stage are issued in every clock cycle because of the pipeline structure. Therefore, some of the control signals can be shared. For example, all the register loading signals, LD\_inDR, LD\_DR1, LD\_dDR2, LD\_dDR3, and LD\_outDR can be reduced to a single load signal. Similarly, memory chip select signals, A/D and D/A convert signals can be reduced. The total number of the control signals are reduced to 11. The reduced control signals are as follows:

| New signal | Replaced old signals                        |

|------------|---------------------------------------------|

| Convert    | Convert_A/D, Convert_D/A                    |

| LD_REG     | LD_inDR, LD_DR1, LD_dDR2, LD_dDR3, LD_outDR |

| MEM_CS     | ROM1_CS, ROM2_CS, M1_CS, M2_CS              |

| ROM_R      | ROM1_R, ROM2_R                              |

Actually, because of the pipeline structure, control signals are issued at each cycle. Only three different control signals, each associates with an operation mode, are required. For the purpose of clarity, the name of the control signals remain unchanged.

# 3.3.6 Interface to host computer

The unit is designed to interface with a general purpose microcontroller or a personal computer. The host uses an 8-bit parallel port to control the unit. Since speed is not a concern, data from the host computer to the unit are in a serial format. Data transmission is controlled by the host using a bit-bashing technique. The function of each interface bit is defined as follows:

| bit number | function                                 |

|------------|------------------------------------------|

| 1          | command data bit                         |

| 2          | command shift register clock bit         |

| 3          | load command register                    |

| 4          | reset address generate counter           |

| 5          | address counter increment                |

| 6          | memory table data bit                    |

| 7          | memory table shift register clock        |

| 8          | load memory data to update data register |

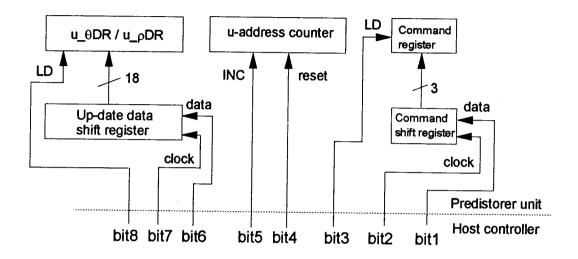

There are four registers and one address counter in the unit that can be controlled by the host. Figure 3.12 shows the interface to the host.

Figure 3.12 Interface to host computer

The 3-bit command shift register receives serial data from host. It loads the data to the command register in parallel. Three interface bits are required, bit1 carries data, bit2 is a shift clock and bit3 is a load signal. Similarly, bit6, bit7 and bit8 are for loading the update data registers. As indicated in Figure 3.7, a u-address counter is used to provide address for update the LUT. The update is performed in sequential order from lower address to higher address. Bit4 and bit5 are for resetting and incrementing the u-address counter respectively.

The data transfer to the idle memory table is controlled by the host controller while the unit is working at its own real-time speed with the active memory table.

When the system starts to run, the host computer first sends a start command to initialize the predistorter unit. The unit executes this command, resets all data registers and sets the memory Table-set1 ready for receiving data from the host. Next, the host asserts bit4 to reset the address counter. It then sends a bit-string of one data word to the update data shift register. This word is then transferred in parallel to the u\_0DR and u\_0DR and loaded to Table-set1. This completes one data word update cycle. The host computer then advances the memory address by asserting the counter INC bit, bit5 and starts next data word update cycle until all data are loaded into Table-set1. When Table-set1 is fully loaded, the host sends a command, M1, to start data processing mode.

The host computer monitors the output of the amplifier, generates a modified table and loads the new table to Table-set2 while the unit is working with the LUT in Table-set1. When Table-set2 is updated, the host sends a command to switch from Table-set1 to Table-set2. The host computer continuously monitors the performance of the amplifier and makes adjustments to the LUT. The LUT is updated without interrupting the real-time operation. The rate at which the table needs to be updated depends on the optimization algorithm and components drift. This needs further study. Since the adjustment is mainly for drift of the amplifier's nonlinearity, the update speed should be on the order of minutes.

## **Chapter 4. Simulation Performance**

#### 4.1 Simulation model

The predistortion amplifier system can be modeled as two cascaded blocks, the predistorter block and the amplifier block.

The quadrature demodulation and modulation in the system do not participate in the amplifier nonlinearity cancellation process. These functions are used to down-convert the RF signal to the baseband and up-convert the predistorted signal back to RF. They are assumed to be ideal linear functional blocks when the nonlinearity cancellation of the amplifier is discussed.

### 4.1.1 Amplifier and predistorter model

A commonly used model for an amplifier with a weak nonlinearity is the power series (16). The instantaneous output,  $e_0$ , of the amplifier with input,  $e_i$ , is given as:

$$e_0 = a_1 e_i + a_2 e_i^2 + a_3 e_i^3 + \dots = \sum_{k=1}^{\infty} a_k e_i^k$$

Where the  $a_k$ 's are device-dependent coefficients.

For most nonlinear cellular amplifiers the coefficients  $a_k$  decrease with k. Thus, the contribution of  $a_k e_i^k$  to the energy of  $e_0$  from higher order terms (k>1) is small compared to the linear term (k=1). Coefficients of the higher order terms are usually rather small compared with those first few terms. Therefore, the first few terms are normally sufficient to describe the amplifier (19). Using more terms gives more accuracy but adds computation complexity. A power series up to the fifth order gives a reasonable compromise between accuracy and complexity, and is the model used here. Higher order terms are assumed to be negligible.

Consider the amplifier input,  $x_d = A\cos\omega t$ , then y can be written as:  $y = a_1A\cos\omega t + a_2A^2\cos^2\omega t + a_3A^3\cos^3\omega t + a_4A^4\cos^4\omega t + a_5A^5\cos^5\omega t$   $= [(1/2)a_2A^2 + (3/8)a_4A^4] + [a_1A + (3/4)a_3A^3 + (5/8)a_5A^5]\cos\omega t$   $+ [(1/2)a_2A^2 + (1/2)a_4A^4]\cos^2\omega t + [(1/4)a_3A^3 + (5/16)a_5A^5]\cos^3\omega t$  $+ [(1/8)a_4A^4]\cos^4\omega t + [(1/16)a_5A^5]\cos^5\omega t$

The output signal consists of a component at the fundamental frequency,  $\omega$ , and spurious signals at the dc, the second, third, fourth and fifth harmonic frequencies,  $2\omega$ ,  $3\omega$ ,  $4\omega$ , and  $5\omega$ . The second and higher harmonic components in y are normally not of interest for cellular RF amplifier since they are outside the working frequency band and can be eliminated by a band pass filter.

The fundamental component of y has an amplitude of  $(a_1A + 3/4 a_3A^3 + 5/8 a_5A^5)$ . The gain of the amplifier at the fundamental frequency is given as:

$$= a_1 + 3/4 a_3 A^2 + 5/8 a_5 A^4$$

g is usually expressed in dB. This is:

$$G = 20log(g)$$

The linear gain of the amplifier is defined as:

$G_1 = 20log(a_1A/A) = 20log(a_1)$

If  $a_3$  and  $a_5$  are negative, the resulting amplitude of the fundamental component is smaller than the linear amplitude,  $a_1A$ , of the amplifier, especially at high input level. This property is called gain compression. Most RF amplifiers are compressive. Gain compression generates AM-AM distortion.

When the input signal amplitude is small, the terms,  $3/4 a_3A^3$  and  $5/8 a_5A^5$  are negligible.  $a_1A$  is a dominant term to the fundamental component and the amplifier behaves linearly. With increases in the input amplitude, the higher order terms play a more important role, and gain compression becomes more significant. When the input amplitude reaches a certain level, the output will not increase further. The amplifier is said to be saturated. The output power of an amplifier is usually defined as the output power at which the gain drops by 1 dB compared to the small input signal gain. This point is referred as the 1 dB gain compression point.

Notice, only the  $a_k$ 's of the odd order terms in the power series generate the gain compression. Even order terms have no effect on the amplitude of the fundamental component. For this reason, the amplifier is modeled as:

$y = a_1 x_d + a_3 x_d^3 + a_5 x_d^5$

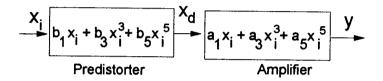

Where y and  $x_d$  are the output and input, and  $a_1$ ,  $a_3$ , and  $a_5$  are the coefficients of the amplifier model.

Now consider the predistorter. Let the input to the predistorter be  $x_i$ , then the output,  $x_d$ , can be represented in power series as:

$x_d = b_1 x_i + b_2 x_i^2 + b_3 x_i^3 + b_4 x_i^4 + b_5 x_i^5 + \dots$

where b's are the coefficients which are chosen to cancel the nonlinearity of the amplifier. Since only the odd order terms generate gain compression, there is no need for compensation by the even predistortion terms. So all  $b_i$ 's for which i = 2, 4, 6, ... can be set to zero. For the same consideration as in the amplifier, the predistorted power series is truncated to the fifth order as:

$$x_d = b_1 x_i + b_3 x_i^3 + b_5 x_i^5$$

# 4.1.2 Predistortion system model

As shown in Figure 4.1, two truncated power series are used to represent the predistorter block and the amplifier block in the system. They are:

$x_d = b_1 x_i + b_3 x_i^3 + b_5 x_i^5$  $y = a_1 x_d + a_3 x_d^3 + a_5 x_d^5$

Figure 4.1 The predistortion system model

In practice the amplifier model is obtained from measured characteristic. A least square error fitting algorithm is used to generate  $a_1$ ,  $a_3$ , and  $a_5$ . This analytical function is then used to determine the initial coefficients of the predistorter.

Assuming perfect up and down conversion, then the overall system input and output can be represented as:

$$y = a_{1}(b_{1}x_{i} + b_{3}x_{i}^{3} + b_{5}x_{i}^{5}) + a_{3}(b_{1}x_{i} + b_{3}x_{i}^{3} + b_{5}x_{i}^{5})^{3}$$

+  $a_{5}(b_{1}x_{i} + b_{3}x_{i}^{3} + b_{5}x_{i}^{5})^{5}$

=  $C_{1}x_{i} + C_{3}x_{i}^{3} + C_{5}x_{i}^{5} + C_{7}x_{i}^{7}$  + higher order terms

where the overall system power series coefficients are:

$$C_1 = a_1b_1$$

$C_3 = a_1b_3 + a_3b_1^3$

$C_5 = a_1b_5 + a_5b_1^5 + 3a_3b_1^2b_3$

...

By properly selecting the coefficients of the predistorter  $b_i$ 's, the third and the fifth order terms in the overall system can be canceled out or reduced. Perfect cancellation of the nonlinearity requires the use of an infinite number of power series terms. This is not feasible. In most RF amplifiers, the higher order terms are small and can be omitted. Based on this assumption, only the third and fifth orders are considered here.

The cancellation conditions for the third and fifth order are given as:

$a_1b_3 + a_3b_1^3 = 0$   $a_1b_5 + a_5b_1^5 + 3a_3b_1^2b_3 = 0$ Choosing  $C_1 = a_1$ , then  $b_1 = 1$ , and  $b_3$  and  $b_5$  are given as:  $b_3 = -a_3 / a_1$  $b_5 = (-a_5 - 3a_3b_3) / a_1$

These conditions are used as the initial start up amplitude to amplitude (AM-AM) correction in the predistorter. They are adjusted by an adaptive process to optimize the correction.

Since the amplifier also has amplitude to phase (AM-PM) distortion, a correction on AM-PM is also required in the predistorter. The measured AM-PM characteristic,  $\theta = a'_1 x_d + a'_3 x_d^3 + a'_5 x_d^5$ , of the amplifier is used to determine the initial AM-PM compensation in the predistorter.

The predistorter uses two look-up tables to produce the AM-AM and AM-PM correction signals, as described in Chapter 3.

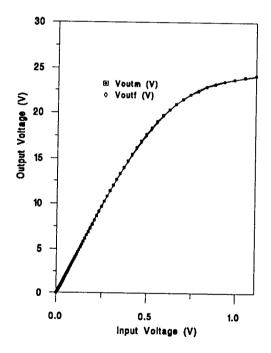

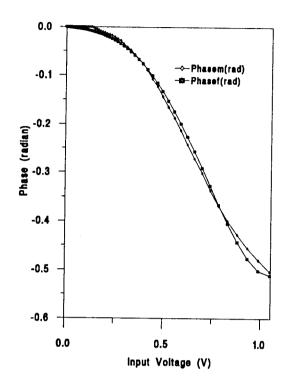

The amplifier used in this study is a three-stage class A power amplifier, Celwave model PA9340 used in Cellular base stations. Its linear gain is 32 dB and designed output power is 6 Watt. The amplifier is operated from 869 MHz to 894 MHz with  $50\Omega$  resistive source and load impedance. The output power at the 1 dB compression point of PA9340 is measured as 38.29 dBm at 880 MHz, the saturated power is 40.8 dBm.

The measured amplitude and phase characteristics of the PA9340 with the fifth order least squared fitting curves are shown in Figure 4.2 and Figure 4.3 respectively. The characteristics are measured with an HP model 8753A network analyzer. The fitting curves are generated by a minimum mean squared error fitting algorithm.

Figure 4.2 Amplitude characteristic of PA9340

Figure 4.3 Phase characteristic of PA9340

In Figure 4.2, Voutm (V) is the measurement amplitude characteristic. Voutf (V) is the fifth order least squared fit curve. The coefficients of the AM-AM function are:  $a_1$ =40.61,  $a_3$ =-23.21,  $a_5$ = 6.38.

In Figure 4.3, Phasem(rad) is the measurement phase characteristic. Phasef(rad) is the fifth order least squared fit curve. The coefficients of the AM-PM function are:  $a'_1$ =-0.049,  $a'_3$ =-1.038,  $a'_5$ = 0.581.

## 4.2. The predistortion tables

## 4.2.1 AM to AM correction table

The following considerations are used to determine the input range on the amplifier for proper operation of the predistortion.

From Figure 4.2, it can be seen that the non-linearity increases drastically near the saturated output power region. It is difficult to try to linearize an amplifier up to that area. Cavers (1) pointed out that in practice the amplifier could be linearized up to 95 % - 98 % of its saturated power.

Let the maximum output power,  $P_{max}$ , at which the system tries to linearize be 95% of the saturated power,  $P_{sat}$ , of the PA9340.  $P_{max}$  in dBm is given by:

$P_{max} = P_{sat} + 10 \log (0.95)$ =  $P_{sat} - 0.22 dBm$ = 40.8 - 0.22 dBm = 40.58 dBm

The  $P_{max}$  limits the input power,  $P_d$ , of the amplifier to  $P_{dmax}$ . Since  $P_d$  is from the output of the predistorter,  $P_{dmax}$  sets the output limit of the predistorter.

From the measurement data, shown in Figure 4.4,  $P_{dmax}$  is equal to 13.4 dBm with  $P_{max}$  at 40.58 dBm. In a 50  $\Omega$  system, the power is equivalent to the voltage amplitude of:

$\rho_{\text{dmax}}(\text{rms}) = \sqrt{(10^{(13.4/10)} \times 0.001 \times 50)} = 1.05 \text{ V}$ because: P(in dBm) = 10log(1000\*V<sup>2</sup>/R)

Figure 4.4 Maximum In/Out power of PA9340

The maximum input power,  $P_{inmax}$ , with respect to  $P_{max}$  of the system is set by the linear gain and the  $P_{max}$  of the amplifier as:

$P_{inmax} = P_{max}$  - linear gain (in dBm)

In practice, the linear gain is measured with a low level input, since at low signal levels the amplifier behaves linearly. With the linear gain of 32 dB,  $P_{inmax}$  is 8.6 dBm. This is equivalent to  $\rho_{inmax} = 0.60$  V. Figure 4.5 illustrates the maximum input and output limits.

Figure 4.5 Illustration of maximum input/output limit

$\rho_{inmax}$  and  $\rho_{dmax}$  are the maximum input voltage and output voltage of the amplitude correction table respectively. Let the input and output of the table be  $\rho_{in}$  and  $\rho_{out}$  respectively, then the input and output relation of the table is given as:

$\rho_{d} = b_{1}\rho_{in} + b_{3}\rho_{in}^{3} + b_{5}\rho_{in}^{5}$

where  $\rho_{in}$  and  $\rho_{out}$  are bound by  $\rho_{inmax}$  and  $\rho_{dmax}$  respectively. The b<sub>i</sub>s are coefficients of the predistorter which can be adjusted by the adaptive process to optimize the nonlinearity cancellation. The initial value of b<sub>i</sub>s are: b<sub>1</sub>=1, b<sub>3</sub>=0.5715, b<sub>5</sub>=0.823.

For example, if  $\rho_{in}$  = 0.20 V,  $\rho_d$  will be 0.22V. This 0.22 is stored in AM-AM table at the location corresponding to  $\rho_{in}$  = 0.20V, as shown in Figure 4.6.

Figure 4.6 The relation of  $\rho_{in}$  and  $\rho_{d}$

### 4.2.2 AM to PM correction table

As shown in Figure 4.3, the phase drops with an increase in the signal level. To keep the input phase and output phase equal, a phase shift,  $\Delta\theta$ , is added to the input phase of the signal for each input level.  $\Delta\theta$  is stored in the AM-PM correction table and added to the original phase,  $\theta_{in}$ , to generate the phase offset signal,  $\theta_d$ , for the amplifier.

Let the input and output of the table be  $\rho_{in}$  and  $\Delta\theta$  respectively, then the input and output relation of the table is given as:

$\Delta \theta = b'_{1}\rho_{in} + b'_{3}\rho_{in}^{3} + b'_{5}\rho_{in}^{5}$

The b'<sub>i</sub>s are determined initially by the AM-PM relation of the amplifier. They can be adjusted by the adaptive process later. The initial value of b'<sub>i</sub>s are: b'<sub>1</sub>=0.049, b'<sub>3</sub>=1.038, b<sub>5</sub>=-0.581.