#### AN ABSTRACT OF THE THESIS OF

<u>Jacob W. Zechmann</u> for the degree of <u>Master of Science</u> in <u>Electrical and Computer Engineering</u> presented on <u>June 30, 2005</u>.

Title: Investigation of a Noise-Shaping Accelerometer Interface Circuit for Two-Chip

Implementation.

Redacted for privacy

Abstract approved: \_\_\_\_\_\_Un-Ku Moon

The world market for sensors is several hundred million dollars growing at an annual rate of 20 percent with accelerometers comprising 19 percent of the market. With an increasing market, a wide range of applications with varying degrees of resolution are in demand. Therefore, there is sufficient motivation for developing new architectures that are more accurate, reliable, less costly, and easy to implement in any given application. This research investigates a new proposed architecture intended to improve each of the mentioned motivations.

Capacitive sensors and their electrical interfaces measure the displacement of a suspended beam mass in response to an input acceleration. The studied architecture is a two-chip solution with the capacitive sensor and electrical interface fabricated independently. This two-chip approach has several advantages. The micro-machining process for capacitive sensors is difficult with lower yields than most VLSI technologies. By fabricating the electrical interface in a different process with higher yields and smaller geometries, the cost of the architecture is reduced. As micro-machining yields improve, this advantage will diminish in favor of single-chip integration of the sensor and interface. If the production volumes are high and a single-chip solution is best suited for a particular application, this architecture can be easily integrated on one chip. Another advantage of a two-chip solution is the ease of implementation. The sensor is able to be placed at the point of interest while the electrical interface can be placed in a more convenient location. Also, several sensors can be multiplexed to one electrical interface. Sensors can be replaced while keeping the interface circuitry intact. This lowers cost and increases reliability of the system. Given its flexibility, the architecture is easy to implement and maintain in most applications.

Over-sampling techniques through delta sigma modulation are used extensively in implementations of analog interfaces on VLSI technologies. The electrical interface to a capacitive sensor is no exception. There are several architectures available that measure capacitive displacement. Two popular approaches for the electrical interface are a demodulator and delta-sigma modulator architecture. The demodulator architecture is commercially used by Analog Devices Inc. in their ADXL50 and ADXL05 products. To further improve the accuracy of available sensors, the delta-sigma architecture is used in this investigation. There are techniques used in this research that improve the resolution of current delta-sigma interface architectures. The architecture is a third order delta-sigma modulator. With a higher order modulator, the quantization noise is further suppressed in the signal band increasing the accuracy. The integrator implements correlated double sampling (CDS) in order to suppress the negative affects of input offset due to mismatch and flicker (1/f) noise on dynamic range and SNDR. With the use of force-feedback and a digital differentiator, a third order system is realized. The force-feedback has three levels which can result in linearity degradation. To improve the linearity, a mismatch shaping scheme was implemented. The interface circuit was implemented in a 1.6-um, 5-volt, CMOS process.

The initial fabricated design experienced instability and functional problems. This research involved improving analog blocks in the electrical interface and implementing test structures and methods to determine the root cause of the original design performance. Through this research it is shown that the combination of using a surface-machined capacitive senor and the parasitic capacitance associated with a two-chip implementation has a detrimental effect on the integrator of the electrical interface.

©Copyright by Jacob W. Zechmann

June 30, 2005

All Rights Reserved

# Investigation of a Noise-Shaping Accelerometer Interface Circuit for Two-Chip Implementation

by

Jacob W. Zechmann

#### A THESIS

submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Master of Science

Presented June 30, 2005 Commencement June 2006 APPROVED:

# Redacted for privacy

Major Professor, representing Electrical and Computer Engineering

# Redacted for privacy

Director of the School of Electrical Engineering and Computer Science

# Redacted for privacy

Dean of the Graduate School

I understand that my thesis will become part of the permanent collection of Oregon State University libraries. My signature below authorizes release of my thesis to any reader upon request.

# Redacted for privacy

Jacob W. Zechmann, Author

### **ACKNOWLEDGMENTS**

Earning my master of science at Oregon State University has been a very rewarding experience. As with any challenge, it begins eagerly with an opportunity and ends successfully with determination and perseverance, learning and training, support from mentors, colleagues, and friends, and a certain amount of luck.

With gratitude, I thank Professor Moon and Professor Temes for offering me the opportunity to study within their research group. I have benefited from their guidance, support, and technical expertise. Professor Temes has been a great influence in laying my Data Converter foundation through discussion, studies, and course work.

There are several companies, organizations, and individuals that have supported this research project. The financial support from the Catalyst Foundation and Yamatake Corporation is gratefully acknowledged. I wish to thank Tetsuya Kajita for providing the groundwork, technical discussions, thesis notes, and friendship. Appreciation to Paul Ferguson and Steve Lewis of Analog Devices Inc. for their initial investigation and supplying the capacitive sensors is acknowledged. I appreciate MOSIS for their understanding and support over the digital pad dilemma and for the fabrication of the experimental circuits.

I am especially grateful to the members of MSW of Texas Instruments Inc. for lab support in order to test my design and for their understanding of time needed to finish this document and defense. I am indebted to Francisco Ledesma. Without his support, it would be another three years until my test board is completed.

Jose' Siva and Robert Batten deserve a special acknowledgment from the Electrical and Computer Engineering Department. I would like to give a special thanks to Jose' for his support with Cadence, Simulink, delta-sigma design, instrumentation, and discussions. I thank Robert for his Mentor Graphics support and keeping the Owen 405 lab in functional order. Without the contributions of these two gentlemen, my progress would have been less enjoyable.

I acknowledge the following colleagues for their technical discussions and friendship. Arun, without your advice, I would not have pursued my masters. Pavan and Jose' your intelligence and humility make you both very special people. David, I appreciated your humor and company at the gym. Don't forget to take your protein. Brandon's determination and dedication is an inspiration. Nathan thanks for your advice and friendship. I thank Dong-Yong

for the intense golf matches at the Trysting Tree. Rather he should thank me for the ten-stroke handicap. To the rest of the inhabitance of Owen 245, thank you for making my stay meaningful.

I discovered a love for singing and music and a number of friendships during my vocal study at Oregon State University. To the members of the OSU Meistersingers Men's Chorus, you sound great. Professor Zielke, you are a talented conductor. I would like to thank Richard Wagner, my individual vocal instructor, for developing my voice and giving me my only C in college. It was actually a C+.

I thank my parents for their support and motivation to finish my master degree. Yes mother, I have finished my thesis.

## TABLE OF CONTENTS

|   |     |                                                        | Page |

|---|-----|--------------------------------------------------------|------|

| 1 |     | Introduction                                           | 1    |

|   | 1.1 | Organization                                           | 2    |

|   | 1.2 | Simulation Details                                     | 3    |

| 2 |     | Capacitive Sensors                                     | 4    |

|   | 2.1 | Bulk vs. Surface Micro-Machined Sensors                | 4    |

|   | 2.2 | Damped Mass-Spring Behavior                            | 5    |

|   | 2.3 | Sense Capacitance                                      | 7    |

|   | 2.4 | Brownian Noise                                         | 7    |

| 3 |     | System Architecture                                    | 9    |

|   | 3.1 | $k_0$ : Conversion from $\alpha_{EXT}$ to $F_{EXT}$    | 10   |

|   | 3.2 | k <sub>2</sub> : Conversion from Force to Acceleration | 10   |

|   | 3.3 | Accelerometer Transfer Function                        | 10   |

|   | 3.4 | Integrated Voltage from Displacement                   | 12   |

|   | 3.5 | Integrator Transfer Function                           | 15   |

|   | 3.6 | Dither                                                 | 18   |

|   | 3.7 | kq: 1-Bit Quantizer                                    | 20   |

|   | 3.8 | k4: Feedback DAC                                       | 21   |

# TABLE OF CONTENTS (Continued)

|   |      |                                        | Page |

|---|------|----------------------------------------|------|

|   | 3.9  | H <sub>C</sub> (z) Digital Compensator | 23   |

|   | 3.10 | Three-Level Force-Feedback             | 24   |

|   | 3.11 | Five Phase Integration Cycle           | 26   |

|   | 3.12 | System Simulations                     | 27   |

| 4 |      | Interface Implementation               | 30   |

|   | 4.1  | Process and Simulation Corners         | 30   |

|   | 4.2  | Amplifier Bandwidth Challenges         | 30   |

|   | 4.3  | Amplifier Design                       | 34   |

|   | 4.4  | Amplifier Common Mode Feedback         | 40   |

|   | 4.5  | Integrator Switch Design Implications  | 41   |

|   | 4.6  | Correlated Double Sampling             | 44   |

|   | 4.7  | Interface Integrator Gain Error        | 48   |

|   | 4.8  | KT/C and Thermal Noise                 | 49   |

| 5 |      | Test Structures and Methodology        | 53   |

|   | 5.1  | Interface On-Chip Test Structures      | 53   |

|   | 5.2  | First Order Integrator Test Method     | 54   |

| 6 |      | Experimental Results                   | 56   |

|   | 6.1  | Initial Design IO Pad Problem          | 56   |

# TABLE OF CONTENTS (Continued)

|     |                                        | Page |

|-----|----------------------------------------|------|

| 6.2 | Reference Feedback DAC and Input VCM   | 56   |

| 6.3 | First Order Test Structure Performance | 59   |

|     | Conclusion                             | 65   |

|     | Bibliography                           | 67   |

## LIST OF FIGURES

| <u>Figure</u> |                                                                           | Page |

|---------------|---------------------------------------------------------------------------|------|

| 2.1           | Capacitive Sensor shown with mass-spring modeling                         | 5    |

| 2.2           | Structural diagram of ADI's capacitive sensor                             | 7    |

| 3.1           | Block diagram of the system architecture                                  | 9    |

| 3.2           | Sensor capacitance changes as a function of acceleration                  | 12   |

| 3.3           | Simplified version of the interface integrator without CDS                | 13   |

| 3.4           | Single-ended version of the integrator without CDS                        | 15   |

| 3.5           | Block diagram of the integrator's z-transfer function                     | 17   |

| 3.6           | Implemented SC Dither Structure                                           | 18   |

| 3.7           | Single-bit pseudo RNG used for dither                                     | 19   |

| 3.8           | Implemented RNG simulation results                                        | 20   |

| 3.9           | Comparator schematic implementing the single-bit quantizer                | 21   |

| 3.10          | DAC schematic implementing the k4 feedback                                | 23   |

| 3.11          | Force-Feedback schematic showing the capacitors, switches, and references | 24   |

| 3.12          | Implemented (a) positive and (b) negative force-feedback                  | 26   |

| 3.13          | System simulation Simulink schematic                                      | 27   |

| 3.14          | System simulation results                                                 | 28   |

| 3.15          | System simulation Simulink schematic with amplifier thermal noise         | 28   |

| 3.16          | System simulation results with amplifier thermal noise                    | 29   |

# LIST OF FIGURES (Continued)

| <u>Figure</u> |                                                                                      | Page |

|---------------|--------------------------------------------------------------------------------------|------|

| 4.1           | Integrator schematic showing the sampling, integrating, and parasitic capacitance    | 31   |

| 4.2           | Open loop frequency response simulated for the initial interface amplifier           | 32   |

| 4.3           | Closed loop frequency response simulated for the initial interface amplifier         | 33   |

| 4.4           | Amplifier schematic was implemented in the second design revision                    | 34   |

| 4.5           | Open loop frequency response simulated for the re-designed interface amplifier       | 37   |

| 4.6           | Closed loop frequency response simulated for the re-designed interface amplifier     | 38   |

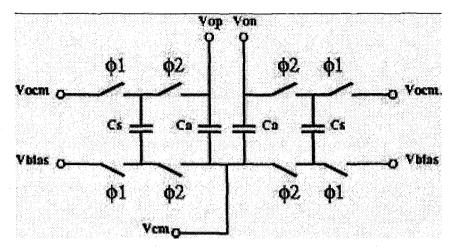

| 4.7           | Amplifier common mode feedback structure                                             | 41   |

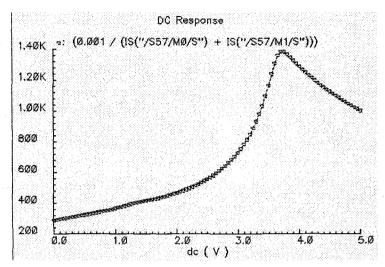

| 4.8           | DC sweep resistance simulated for the CMOS initial design switch                     | 42   |

| 4.9           | DC sweep resistance simulated for the NMOS initial design switch                     | 42   |

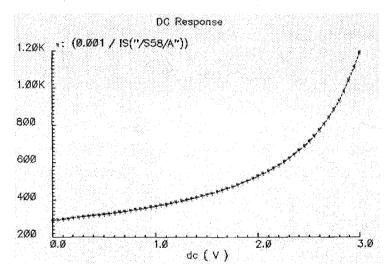

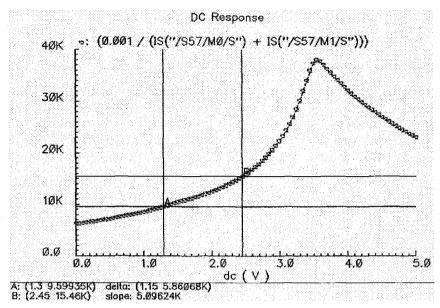

| 4.10          | DC sweep resistance simulated for the CMOS re-design switch                          | 43   |

| 4.11          | DC sweep resistance simulated for the NOS re-design switch                           | 43   |

| 4.12          | Schematic of the switch capacitor, CDS network                                       | 45   |

| 4.13          | Integrator block diagram for noise analysis                                          | 50   |

| 4.14          | Modified integrator block diagram for noise analysis                                 | 51   |

| 4.15          | Amplifier input fluctuations due to voltage pulses on the sensor beam                | 52   |

| 5.1           | Parasitic capacitance matching test structure                                        | 53   |

| 5.2           | Capacitive Sensor model on the interface chip to simulate a constant DC acceleration | 54   |

# LIST OF FIGURES (Continued)

| Figure |                                                                                      | Page |

|--------|--------------------------------------------------------------------------------------|------|

| 6.1    | Schematic of the switch capacitor, CDS network                                       | 57   |

| 6.2    | DAC schematic implementing the k4 feedback                                           | 58   |

| 6.3    | Baseline configuration test structure measure                                        | 60   |

| 6.4    | Test structure with parasitic matching measurement                                   | 61   |

| 6.5    | Test structure with parasitic matching verse baseline configuration measurement      | 62   |

| 6.6    | Test structure with parasitic matching, floating beam, and dither measurement        | 63   |

| 6.7    | Test structure with parasitic matching verse floating beam configuration measurement | 64   |

# LIST OF TABLES

| <u>Table</u> |                                                                    | Page |

|--------------|--------------------------------------------------------------------|------|

| 3.1          | Implemented digital compensator output and force-feedback polarity | 24   |

| 6.1          | Input CM voltages for various sample frequencies                   | 58   |

| 6.2          | Input CM voltages with capacitor matching                          | 61   |

| 6.3          | Input CM voltages with capacitor matching and floating beam        | 63   |

# Investigation of a Noise-Shaping Accelerometer Interface Circuit for Two-Chip Implementation

### Chapter 1.

#### INTRODUCTION

Worldwide revenues for micro-electromechanical systems (MEMS) will grow from \$3.9 billion in 2001 to \$9.6 billion in 2006 as predicted by In-Stat/MDR [1]. MEMS such as, accelerometers are capable of sensing changes in movements relative to a particular reference point. The low-G, high-resolution, accelerometer market in particular is experiencing rapid growth. These sensors are needed for gaming devices, touch pads, and crash detection systems. Some other accelerometer applications include: computer hard-drive protection, personal navigation systems, physical therapy and rehabilitation equipment, seismic detectors, and industrial vibration measurement [1]. Original equipment manufacturers are using low-G accelerometers to differentiate their products with safety, security and convenience features. Hence, there is significant motivation for improving sensitivity, cost, reliability, and convenience.

One architecture implementation decision that affects the cost and convenience is whether to integrate the capacitive sensor and electrical interface on the same substrate. Factors that would influence this decision are production volume and application. For example, industrial vibration measurement applications benefit from a two-chip solution where the sensor is placed on the industrial machinery. If the volumes are sufficiently large, fabrication of a single-chip may have a lower cost than fabricating the electrical interface separately with a cost effective VLSI technology. However, there is a tradeoff in design difficulty between the single and two-chip implementations. The large and often mismatched parasitic capacitance found between the sensor and interface of a two-chip implementation reduces sensitivity and dynamic range of an accelerometer.

Delta-sigma modulation is a stable implementation of high-resolution, analog-to-digital converters in a VLSI technology. It is an excellent approach for accelerometers, given their low-G sensing demand. With delta-sigma modulation, over-sampling and feedback techniques can be used to shape the electrical noise out of the signal band thereby increasing the resolution.

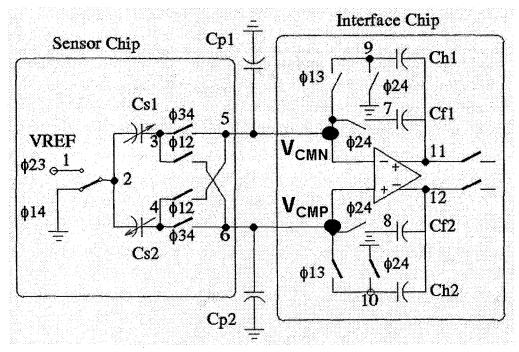

This research investigates the design of an over-sampled, third order, delta-sigma modulator that consists of a two-chip implementation. The interface design consists of a correlated double sampling CDS integrator, inter-loop feedback DAC, force-feedback and mismatch shaping logic, switches, and clock generation. The sample capacitors of the integrator, force-feedback capacitors, and associated switches are found on the sensor chip. The system design contains a number of techniques that are useful for lowering the signal band noise, improving linearity, and maximizing dynamic range. The goal is to demonstrate that a two-chip implementation of a third order delta-sigma modulator is stable and has a high dynamic range and SNDR over a 200 Hz signal bandwidth. The initial fabricated design experienced instability and functional problems. This research involved improving analog blocks in the electrical interface and implementing test structures and methods to determine the root cause of the original design performance. Through this research it is shown that the combination of a surface-machined, capacitive senor and the parasitic capacitance associated with a two-chip implementation has a detrimental effect on the integrator performance of the electrical interface.

The electrical interface circuitry is fabricated in a standard, 5-volt, 1.6-um, CMOS technology. Analog Devices Inc. fabricated the capacitive sensor through their surface micromachining technology.

### 1.1 Organization

Chapter 2 discusses two differences in capacitive sensor fabrication. This chapter describes the fundamental behavior of a capacitive sensor, such as, displacement of a suspended beam mass through acceleration stimulus. The design principles of capacitive sensors will be discussed including the mechanical modeling of the physical device and its electrical behavior. Noise poses a threat to the resolution of any data converter. The noise associated with capacitive sensors will be briefly stated.

Chapter 3 discusses the system level design. The objective of this chapter is to theoretically describe each block of the third order delta-sigma modulator. The integrator and mismatch shaping are discussed. Building on the modeling of capacitive sensors, the integrator function, feedback, and the performance of the system is presented.

Chapter 4 addresses the interface design. Discussions include the integrator amplifier, common mode feedback, switch capacitor architecture, and switch design. The important parameters of gain, unity gain bandwidth, slew rate, and noise are derived. The new design discussed provides a combination of derivations and transistor level simulations. Given the noise sources of each block, complete noise contributions of the integrator are determined. As well as noise, gain error is an important design consideration for the interface implementation.

Chapter 5 is focused on testing the interface design. The test structures implemented on the interface chip are presented. Due to the stability and functional problems of the initial design, a first order test methodology is discussed in this chapter. This methodology is used to simplify the system in order to debug selected blocks.

Experimental results are presented in chapter 6. This chapter begins with the pad problems of the initial fabrication. In Chapter 6, two major testing results are presented. The first is the implementation effects on the input common mode voltage of the amplifier. Finally, the measurement results of the first order test structure are shown.

The conclusion summarizes the investigation of this research, and is found in Chapter 7. Possible future work and focus with this interface design is discussed.

#### 1.2 Simulation Details

The results included in this research were generated from behavioral and transistor level simulations. Matlab's Simulink performed the over all system performance and stability simulations. Spectra density estimation was determined through a fast Fourier transform (FFT) with Hamming window. FFT's are performed on the digital modulator's output, 1 to -1. No decimation filtering was implemented in the system or on silicon, nor in simulations or measurements. Spectre was used to simulate the transistor level block implementation and system performance.

#### **CAPACITIVE SENSORS**

#### 2.1 Bulk vs. Surface Micro-Machined Sensors

A detailed discussion of micromachining is beyond the scope of this research. However, it is informative to describe the main two types of displacement accelerometers relevant to this research. These types of accelerometers, capacitive sensors, are capacitive position sensing. Capacitive sensors measure the displacement of a proof mass, the beam, in response to an external force or acceleration. Capacitive sensors are used in high resolution applications. Other advantages include their low intrinsic temperature coefficient and ease of integration with CMOS fabrication [2]. The system performance is sensitive to the presence of parasitic capacitance at the amplifier input to the interface circuit. This sensitivity is an important consideration that sets design parameters and limits achievable results.

This sensitivity varies between the bulk and surface micro-machined capacitive sensors. Interconnect capacitance can degrade the sensitivity of capacitive sensors significantly by several orders of magnitude. In cases such as two-chip solutions where a large interconnect parasitic capacitance is present between the sensor and the electrical interface circuit, bulk micro-machined sensors are preferred [2]. Bulk sensors have large sense capacitance with similar magnitude as the parasitic capacitance, making it suitable for two-chip solutions.

Surface micro-machining is a more sophisticated technique than bulk. The surface, micromachining process creates much smaller and more intricate, precisely, patterned structures [3]. Surface-machined devices are around 1 to 2µm similar to the dimensions of electronic CMOS circuitry. Therefore, surface-machined devices are about 20 times smaller than bulk-machined devices, and their sense capacitors are much smaller and more sensitive to parasitic capacitance than bulk-machined. The bulk-machined process can not be integrated with electronic CMOS technology, making it non-ideal in certain applications [3].

### 2.2 Damped Mass-Spring Behavior

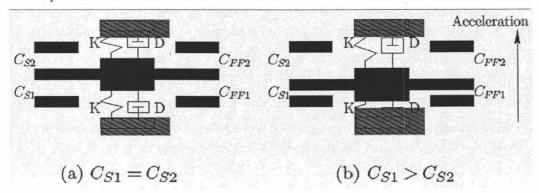

Capacitive sensors behave as damped mass-springs. A beam is suspended above the substrate by compliant springs. The two sense capacitors are formed between the beam and a corresponding stationary plate as shown in Figure 2.1. The figure shows the capacitive sensor with and without applied acceleration [4]. Under applied acceleration, the beam will displace from its nominal position. The displacement of the beam is reflected in a change in the sense capacitors,  $C_{S1}$  and  $C_{S2}$ . As the figure shows, the change in distance between the plates, displacement, of the sense capacitors will change equally but in the opposite direction for each sense capacitor.

Figure 2.1 Capacitive Sensor shown with mass-spring modeling.

From the figure, K is the spring constant and D is the damping factor for the beam. There are three forces that influence the beam expressed in Equation 2.1 under steady state conditions. The differential equation is presented in Equation 2.2 where M is the mass of the beam, and X is the displacement of the beam.

$$0 = Mass \cdot Acceleration + D \cdot Velocity + K \cdot displacement$$

(2.1)

$$0 = M \cdot \frac{d^2 X}{dt^2} + D \cdot \frac{dX}{dt} + K \cdot X \tag{2.2}$$

These forces are the acceleration on the beam's mass with the spring constant and damping factor apposing the beam's acceleration. When an external force,  $F_{EXT}$ , is applied to the beam, the forces are related in Equation 2.3.

$$F_{EXT} = M \cdot \frac{d^2 X}{dt^2} + D \cdot \frac{dX}{dt} + K \cdot X \tag{2.3}$$

For simplicity, assume the external force is sinusoidal and the solution for X is  $X=xe^{(jwt)}$ . Where x is a complex number indicating the maximum displacement and phase with respect to the external force. Therefore, Equation 2.3 can be transformed from the time domain to the frequency domain [5].

$$F_{EXT} \cdot e^{(jwt)} = M \cdot \frac{d^2 x e^{(jwt)}}{dt^2} + D \cdot \frac{dx e^{(jwt)}}{dt} + K \cdot x e^{(jwt)}$$

(2.4)

$$F_{EXT} = -M\omega^2 x + D\omega xj + Kx \tag{2.5}$$

The frequency the mass-spring would oscillate without mechanical damping is called the natural frequency,  $\omega_0$ .

$$\omega_0 = \sqrt{\frac{K}{M}} \tag{2.6}$$

The quality factor, Q, is the efficiency at natural frequency.

$$Q = \frac{\sqrt{MK}}{D} \tag{2.7}$$

Using Equations 2.5 through 2.7, the following continuous time transfer function from acceleration to displacement is derived.

$$H(s) = \frac{X(s)}{\alpha(s)} = \frac{1}{s^2 + \frac{\omega_0}{O}s + \omega_0^2}$$

(2.8)

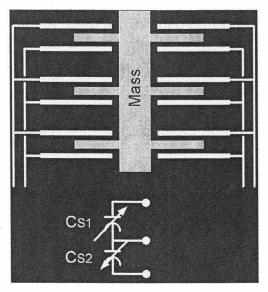

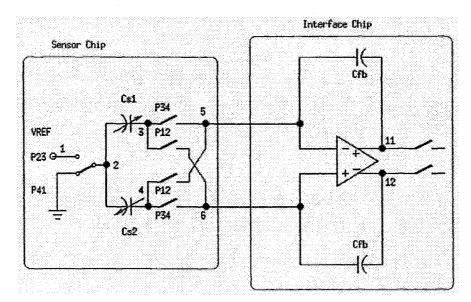

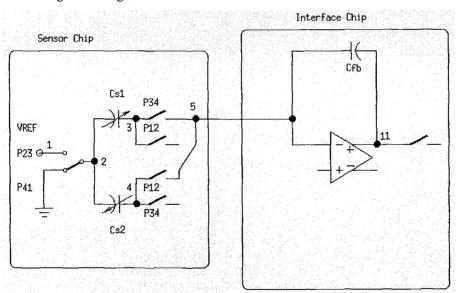

A surface-machined sensor was fabricated for the purpose of initial research which I am investigating. Analog Devices Inc. (ADI) provided the sensor using their surface micromachining process. Figure 2.2 shows the structural diagram of ADI's capacitive senor. The nominal value for the sense capacitors,  $C_{S1}$  and  $C_{S2}$ , are 100fF. The beam has a mass of 0.1 $\mu$ g. The quality factor, Q, and natural frequency,  $\omega_0$ , are 4 and  $2\pi(25e3)$  respectively. The nominal distance between the beam and the stationary plate of each sense capacitor,  $d_1$  and  $d_2$ , is  $1\mu$ m [6].

Figure 2.2 Structural diagram of ADI's capacitive sensor.

### 2.3 Sense Capacitance

As previously discussed, the beam mass behaves mechanically and is modeled as a damped mass-spring. Electrically, the sensor behaves as a variable capacitor subject to external force. The value of each sense capacitor changes according to the displacement of the beam as shown in Equation 2.9.

$$C_{S1} = \frac{\varepsilon A}{d_1 + X} = \frac{C_0 \cdot d_1}{d_1 + X}, C_{S2} = \frac{\varepsilon A}{d_2 - X} = \frac{C_0 \cdot d_2}{d_2 - X}$$

(2.9)

This equation illustrates beam displacement will increase one sense capacitance and decrease the other. The permittivity of the sensor capacitor is  $\varepsilon$ . A is the total surface area of overlap between the stationary sense and beam plates. The nominal distance for  $d_1$  and  $d_2$  is  $d_0 = 1 \mu m$ . X is the displacement of the beam under applied external force.

#### 2.4 Brownian Noise

One source of noise at the accelerometer output is due to the suspended beam mass. The beam is subject to viscous damping by air molecules causing noticeable energy dissipation and creating what is called Brownian noise. Mechanical damping is caused from both gas and structural losses. Given that structural losses are a few orders of magnitude lower than gas-damping effects, they may be ignored. A few methods available for lowering Brownian noise

includes reducing the air damping and increasing the sense-element mass. In order to reduce the air damping, vacuum packaging is needed [2].

The sensor provided for this research did not include special micromachining procedures to increase the beam mass or vacuum packaging. These considerations are out of the scope of this research.

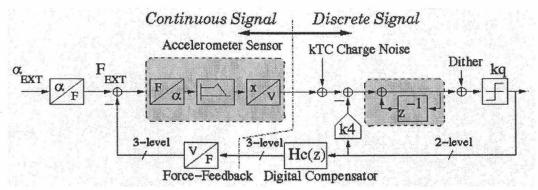

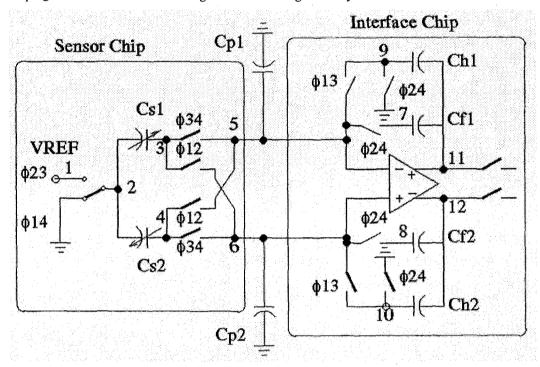

### SYSTEM ARCHITECTURE

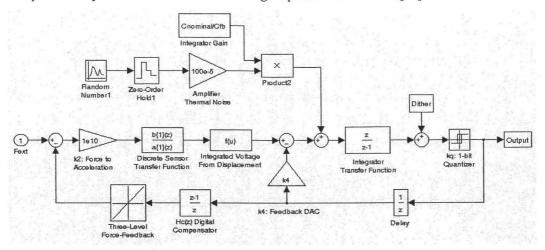

A block diagram of the two-chip system architecture investigated is shown in Figure 3.1 [4]. The dashed line through the center of the diagram divides the continuous-time world of the accelerometer and the discrete-time implementation of the interface circuit. Following the flow of the block diagram, the external acceleration is applied to the accelerometer. The force resulting from this acceleration is added to the negative force-feedback. This final force is applied to the accelerometer and results in displacement of the beam changing the sense capacitance. A difference in capacitance between sense capacitors produces an integrated differential voltage. The charge sampled by the sensor capacitors is added to the negative feedback through  $k_4$ . A digital compensator or differentiator,  $H_C$ , is needed to match the order of the system at the input of the sensor.

The following sub chapters will discuss the modeling of each block in the system and the implementation of blocks in the interface circuit.

Figure 3.1 Block diagram of the system architecture.

#### 3.1 $k_0$ : Conversion from $\alpha_{EXT}$ to $F_{EXT}$

The external acceleration,  $\alpha_{EXT}$ , is expressed in gravity, G. One G is equal to 9.83 m/s<sup>2</sup>. The accelerometer's beam has a mass of 0.1µg. Given that force equals mass multiplied by acceleration,  $k_0$  is derived as shown in Equation 3.1. Constant  $k_0$  is used to convert the external acceleration to force by multiplying this constant by the number of Gs applied to sensor.

$$k_0 = \frac{F_{EXT}}{\alpha_{EXT}} = M \cdot 9.83 \left( \frac{m}{s^2} \right) = 0.1e - 9(kg) \cdot 9.83 \left( \frac{m}{s^2} \right) = 9.83e - 10 \left( \frac{kg \cdot m}{s^2} \right) (3.1)$$

### 3.2 k<sub>2</sub>: Conversion from Force to Acceleration

In order to convert the external force summed with the force-feedback to acceleration,  $k_2$  is modeled. Using the relationship that force equals mass multiplied by acceleration, the acceleration can be determined by dividing the force by the mass of the beam. This is shown in Equation 3.2.

$$k_2 = \frac{\alpha}{F} = \frac{1}{M} = \frac{1}{0.1e - 9(kg)} = 1e10 \binom{1}{kg}$$

(3.2)

#### 3.3 Accelerometer Transfer Function

The discrete-time function is derived from the continuous-time damped mass-spring function previously reviewed. This transfer function determines the beam displacement from the applied acceleration. The continuous-time transfer function is shown in Equation 3.3.

$$H(s) = \frac{X(s)}{\alpha(s)} = \frac{1}{s^2 + \frac{\omega_0}{Q}s + \omega_0^2}$$

(3.3)

This architecture was modeled and simulated in discrete-time. The continuous-time transfer function presented above was converted to discrete-time using MATLAB's c2d function [4]. Equation 3.4 shows the second order discrete-time representation of the sensor transfer function.

$$H(z) = \frac{B(z)}{A(z)} = \frac{b_0 + b_1 z^{-1} + b_2 z^{-2}}{a_0 + a_1 z^{-1} + a_2 z^{-2}}$$

(3.4)

Substituting the quality factor and natural frequency provided by ADI into Equation 3.3 and applying the c2d function the following discrete time function is used to mode the sensor in the system.

$$H(z) = \frac{B(z)}{A(z)} = \frac{1.495e - 11z + 1.381e - 11}{z^2 - 1.084z + 0.7937}$$

(3.5)

From Equation 3.3, the DC gain of the accelerometer is computed in Equation 3.6.

$$A_{DC} = \frac{X}{\alpha_{gravity}} = \frac{1}{\omega_0^2} = \frac{1}{(2\pi \cdot 25e3)^2} = 4.0528e - 11$$

(3.6)

This gain is needed to determine the amount of displacement for a given acceleration and the corresponding sensor capacitor values. Given the modeling constants derived, the beam displacement can be determined for any acceleration input in terms of G's. For a one G input, the beam displacement is 0.3984nm as shown in Equation 3.7.

$$X = 1 \cdot k_0 \cdot k_1 \cdot A_{DC} = 1 \cdot 9.83e - 10 \cdot 1e10 \cdot \frac{1}{(2\pi \cdot 25e3)^2} = 3.984e - 10(m) \quad (3.7)$$

From Equation 2.9, the corresponding sensor capacitor value due to a 0.3984nm displacement is determined in Equations 3.8 and 3.9.

$$C_{S1} = \frac{C_0 \cdot d_1}{d_1 + X} = \frac{100e - 15 \cdot 1e - 6}{1e - 6 + 3.984e - 10} = 99.96018 fF$$

(3.8)

$$C_{S2} = \frac{C_0 \cdot d_2}{d_2 - X} = \frac{100e - 15 \cdot 1e - 6}{1e - 6 - 3.984e - 10} = 100.03982 \, fF \tag{3.9}$$

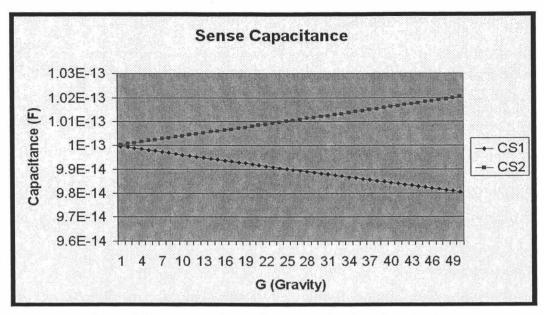

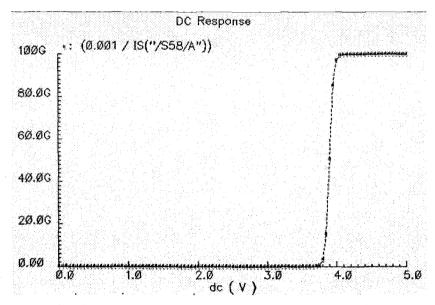

Therefore, one G of acceleration results in about 40aF of increase and decrease sense capacitance. This is an extremely small capacitance to detect. The next sub chapter will determine the resulting integrated voltage from 40aF of sense capacitance. Figure 3.2 is a plot of the sensor capacitance verses the input acceleration in G's. From the chart, 50G of acceleration is equivalent to a 2fF change in sense capacitance. For this type of capacitive sensor, 50G is the maximum input specification from the ADI ADXL50 catalog accelerometer.

Figure 3.2 Sensor capacitance changes as a function of acceleration.

### 3.4 Integrated Voltage from Displacement

The sensor beam displacement needs to be converted to voltage. The gain of the interface integrator is derived in the following discussion. The previous Equations 3.8 and 3.9 show the sensor capacitor value in terms of displacement. These equations will be substituted into the integrator gain equation. The final result will be integrated voltage as a function of beam displacement.

To simplify the integrator gain analysis, the switch capacitor, feedback network implementing correlated double sampling will be replaced with a single non-switched feedback capacitor,  $C_{fb}$ . Another simplification is to ignore the transition from phase  $\Phi 4$  to  $\Phi 1$  and  $\Phi 2$  to  $\Phi 3$ . These phases are used to cross couple the sense and parasitic capacitor mismatch in order to remove DC offset due to mismatch in sense and interconnect parasitic capacitance. Figure 3.3 is the switch capacitor, integrator circuit used in this analysis.

Transitioning from  $\Phi 1$  to  $\Phi 2$ , Equations 3.10 and 3.11 show the delta gain of the plus and minus output terminals of the integrator. During  $\Phi 1$ , node 2 is switched to ground. Therefore, the integrated output voltage is the ratio of  $C_{S2}/C_{fb}$  multiplied by VREF [7], 0V. For  $\Phi 2$ , VREF is switched to node 2 and the integrated output voltage is  $C_{S2}/C_{fb}$  multiplied by VREF. The integrated voltage from  $\Phi 1$  to  $\Phi 2$  is derived in Equations 3.10 and 3.11, and the differential, integrated voltage is derived in Equation 3.12.

Figure 3.3 Simplified version of the interface integrator without CDS.

$$\Delta Voutp_{12} = -\frac{C_{S2}}{C_{fb}} \cdot V_{REF} - \left(-\frac{C_{S2}}{C_{fb}} \cdot 0\right) = -\frac{C_{S2}}{C_{fb}} \cdot V_{REF}$$

(3.10)

$$\Delta Voutm_{12} = -\frac{C_{S1}}{C_{fb}} \cdot V_{REF} - \left(-\frac{C_{S1}}{C_{fb}} \cdot 0\right) = -\frac{C_{S1}}{C_{fb}} \cdot V_{REF}$$

(3.11)

$$\Delta Voutdiff_{12} = V_{REF} \cdot \left( -\frac{C_{S2}}{C_{fb}} - \left( -\frac{C_{S1}}{C_{fb}} \right) \right) = \frac{V_{REF}}{C_{fb}} \cdot \left( C_{S1} - C_{S2} \right)$$

(3.12)

Transitioning from  $\Phi$ 3 to  $\Phi$ 4, Equations 3.13 and 3.14 show the delta gain of the plus and minus output terminals of the integrator. The same approach is taken in determining the differential integrated voltage from  $\Phi$ 3 to  $\Phi$ 4 resulting in Equation 3.15.

$$\Delta Voutp_{34} = -\frac{C_{S1}}{C_{fb}} \cdot 0 - \left( -\frac{C_{S1}}{C_{fb}} \cdot V_{REF} \right) = \frac{C_{S1}}{C_{fb}} \cdot V_{REF}$$

(3.13)

$$\Delta Vout m_{34} = -\frac{C_{S2}}{C_{fb}} \cdot 0 - \left(-\frac{C_{S2}}{C_{fb}} \cdot V_{REF}\right) = \frac{C_{S2}}{C_{fb}} \cdot V_{REF}$$

(3.14)

$$\Delta Voutdiff_{34} = V_{REF} \cdot \left( \frac{C_{S1}}{C_{fb}} - \frac{C_{S2}}{C_{fb}} \right) = \frac{V_{REF}}{C_{fb}} \cdot \left( C_{S1} - C_{S2} \right)$$

(3.15)

The total integrated voltage after the four phases of each integration cycle is determined by summing the differential integrated voltages form  $\Phi$ 34 and  $\Phi$ 12 as shown in Equation 3.16.

$$Voutdiff = \Delta Voutdiff_{34} + \Delta Voutdiff_{12} = \frac{2 \cdot V_{REF}}{C_{fb}} \cdot (C_{S1} - C_{S2})$$

(3.16)

With a small change in sensor capacitance, the integrated voltage will be small as well. To increase the output voltage, the input sampling sensor capacitors are cross coupled between  $\Phi$ 12 and  $\Phi$ 34. Equation 3.16 shows a gain factor of two as a result of double sampling the cross coupled connection. The integrated voltage in terms of displacement is derived by substituting the sense capacitance from Equation 2.9 into Equation 3.16. The resulting expression is provided in Equation 3.17.

$$Voutdiff = \frac{2 \cdot V_{REF}}{C_{fb}} \cdot \left(C_{S1} - C_{S2}\right) = \frac{2 \cdot V_{REF}}{C_{fb}} \cdot \left(\frac{\varepsilon A}{d_1 + X} - \frac{\varepsilon A}{d_2 - X}\right)$$

(3.17)

Making the following assumptions that the beam displacement is much smaller than the nominal distance between sense capacitor plates and that the actual  $C_{S1}$  and  $C_{S2}$  distances are equal, the following equation is valid.

$$Voutdiff = \frac{2 \cdot \varepsilon A \cdot V_{REF}}{C_{fb}} \cdot \left( \frac{1}{d_0 \cdot \left(1 + \frac{X}{d_0}\right)} - \frac{1}{d_0 \cdot \left(1 - \frac{X}{d_0}\right)} \right)$$

(3.18)

Re-arranging Equation 3.18 provides a relationship between the beam displacement and integrated voltage.

$$Voutdiff \cong \frac{2 \cdot V_{REF}}{C_{fb}} \cdot \frac{\mathcal{E}A}{d_0} \cdot \left( \left( 1 - \frac{X}{d_0} \right) - \left( 1 + \frac{X}{d_0} \right) \right) = -\frac{2 \cdot V_{REF} \cdot C_0}{C_{fb}} \cdot \frac{2 \cdot X}{d_0}$$

(3.19)

$$Voutdiff \cong -\frac{4 \cdot V_{REF} \cdot C_0 \cdot X}{C_{fb} \cdot d_0}$$

(3.20)

Using the ADI's surface-machined capacitive sensor parameters, a VREF equal to 5V, and an integrator feedback capacitor equal to 200fF, the numerical constant is determined in Equation 3.21.

$$k_{2} = \frac{Vout}{X} = \frac{4 \cdot V_{REF} \cdot C_{0}}{C_{fb} \cdot d_{0}} = \frac{4 \cdot 5V \cdot 100 \, fF}{200 \, fF \cdot 1 \, \mu m} = 1e7 \left(\frac{V}{m}\right)$$

(3.21)

A more sophisticated model for system simulations is to use the expression in Equation 3.18.

### 3.5 Integrator Transfer Function

The next block modeled in the system is the integrator's discrete-time transfer function. The gain which determines the sampled integrated voltage is added to the negative feedback of the inner loop, k<sub>4</sub>. This voltage will be integrated as determined from the following analysis.

A straight forward derivation of the transfer function is possible if we simplify the integrator as shown in Figure 3.4. As in the gain derivation, the CDS has been removed. Another simplification in Figure 3.4 is the single-ended representation of the differential integrator. Observing the charge equations from phase  $\Phi 1$  to  $\Phi 2$  is all that is necessary to determine the z-transfer function of the integrator. Despite the implemented integrator taking four phases to obtain the final integrated voltage per cycle, it is still only considered one clock cycle in system simulations through modeling.

Figure 3.4 Single-ended version of the integrator without CDS.

The charge equations for  $C_{S2}$  and  $C_{fb}$  in phase  $\Phi 1$  are provided in Equations 3.22 and 3.23. Charge equations are simply the voltage across the capacitor multiplied by the capacitance of the capacitor.

$$QC_{S2} = (V_5 - 0)C_{S2} (3.22)$$

The voltage across  $C_{fb}$  in phase  $\Phi 1$  is  $V_5$  and  $V_{OUTP}$ . Node voltage  $V_5$  is associated with the node numbered 5 in Figure 3.4. Node voltage  $V_{OUTP}$  is the positive output shown on the differential amplifier in Figure 3.4 also labeled node 11. Node 5 is assumed to not vary over time, a constant, since it is held by the gain of the amplifier. However,  $V_{OUTP}$  is time-varying or signal dependent, and the time  $V_{OUTP}$  is considered must be noted [7] as shown in Equation 3.23.

$$QC_{fb} = (V_5 - V_{OUTP}(nT - \frac{T}{2}))C_{fb}$$

(3.23)

The charge equations for  $C_{S2}$  and  $C_{fb}$  in phase  $\Phi 2$  are provided in Equations 3.24 and 3.25.

$$QC_{S2} = (V_5 - V_{REF})C_{S2} (3.24)$$

$$QC_{fb} = (V_5 - V_{OUTP}(nT))C_{fb}$$

(3.25)

The next step in the switch capacitor analysis is to determine the change in charge across each capacitor transitioning from phase  $\Phi 1$  to  $\Phi 2$ .

$$\Delta QC_{S2} = -V_{REF}C_{S2} \tag{3.26}$$

$$\Delta QC_{fb} = (-V_{OUTP}(nT) + V_{OUTP}(nT - \frac{T}{2}))C_{fb}$$

(3.27)

Due to charge conservation, summing the delta charge across  $C_{S2}$  and  $C_{fb}$  will result in zero excess charge. However, this equation should reflect whether the integrator is inverting or non-inverting.

$$\Delta QC_{S2} + \Delta QC_{fb} = 0 \tag{3.28}$$

Equation 3.29 shows the delta charges equations for C<sub>S2</sub> and C<sub>fb</sub> substituted into Equation 3.28.

$$-V_{REF}C_{S2} + (-V_{OUTP}(nT) + V_{OUTP}(nT - \frac{T}{2}))C_{fb} = 0$$

(3.29)

Note that the integrator output is only valid after phase  $\Phi 2$  in this analysis representing the completion of the implemented integration cycle. Therefore, the voltage at  $V_{OUTP}$  at the end of  $\Phi 1$  is the same as the last valid integrated voltage in the previous  $\Phi 2$  phase. Under this condition Equation 3.30 is correct and Equation 3.29 can be rewritten into Equation 3.31.

$$V_{OUTP}(n\frac{T}{2} - \frac{T}{2}) = V_{OUTP}(nT - T)$$

(3.30)

$$\frac{-V_{REF}C_{S2}}{C_{fb}} = V_{OUTP}(nT) - V_{OUTP}(nT - T)$$

(3.31)

Taking the z-transform of Equation 3.31, the charge equation is transformed into the discrete z-domain in Equation 3.32.

$$\frac{-V_{REF}C_{S2}}{C_{fb}} = V_{OUTP}(z)(1-z^{-1})$$

(3.32)

Re-arranging the previous equation, leads to Equation 3.33. This transfer function indicates that the integrator is inverting and non-delaying. Since the sampling capacitor is always connected to the input of the amplifier, both the sampling and integration occur in the same phase. In this situation, the integrator is non-delaying as reflected in Equation 3.35.

$$V_{OUTP}(z) = \frac{-V_{REF}C_{S2}}{C_{fb}} \cdot \frac{1}{(1-z^{-1})}$$

(3.33)

The input voltage of the integrator is the step voltage sampled, V<sub>REF</sub>.

$$\frac{\Delta Voutdiff}{\Delta Vindiff} = \frac{\Delta Voutdiff}{V_{REF} - 0} = \frac{\Delta Voutdiff}{V_{REF}}$$

(3.34)

In order to complete the integrator's transfer function, multiply the integrator gain derived in the last chapter by the z-domain transfer function presented in Equation 3.35.

$$\frac{\Delta Voutdiff}{V_{REF}} = \frac{2}{C_{fb}} \cdot \left(C_{S1} - C_{S2}\right) \cdot \frac{1}{\left(1 - z^{-1}\right)}$$

(3.35)

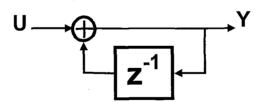

The system block diagram illustrated in Figure 3.1 contains the block diagram representation for the integrator show in Figure 3.5. The transfer function is verified through the following three equations. The transfer function presented in Equation 3.38 matches the z-domain transfer function presented in Equation 3.35.

Figure 3.5 Block diagram of the integrator's z-transfer function.

$$Y = U + Yz^{-1} (3.36)$$

$$Y(1-z^{-1}) = U (3.37)$$

$$\frac{Y}{U} = \frac{1}{(1 - z^{-1})} \tag{3.38}$$

### 3.6 Dither

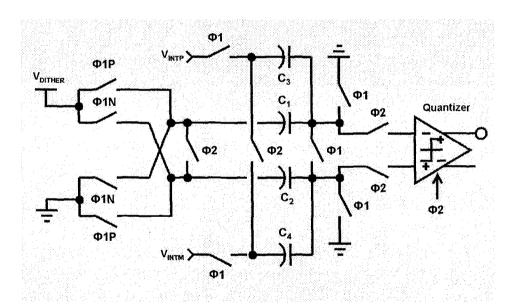

It is well known that first order modulators produce tones. Dither is used to reduce the amount of idle tones [8]. There are two concerns when using dither. Dither must have a white-noise type spectrum and must not saturate the quantizer. Dither is added prior to the quantizer. Therefore, the dither noise can be noise shaped along with the quantization noise [7]. Injecting dither into the integrator output is done with the structure shown in Figure 3.6 [4]. One important point to make about this structure is the division of the difference between  $V_{INTP}$  or  $V_{INTM}$  and signal ground by two due to charge sharing when C1, C2, C3, and C4 are equal. However, the gain of the single bit quantizer will adjust as needed for the required loop gain. The disadvantage is the reduction in differential integrator output voltage to be quantized. Switch control signals  $\Phi$ 1P and  $\Phi$ 1N are driven from a Random Number Generator (RNG) shown in Figure 3.7. This pseudo RNG gives the dither a white-noise property.

Figure 3.6 Implemented SC Dither Structure.

With an on-chip RNG, dither can be provided reducing test board area and complexity. This is a major concern when using a shaker table for testing and in application. The dither circuit needs two phases in order to perform the dithering.

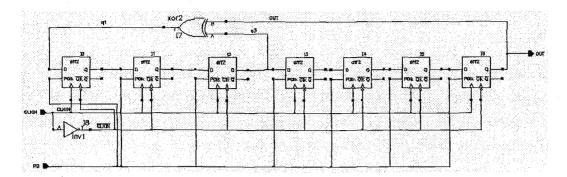

Figure 3.7 Single-bit pseudo RNG used for dither.

The single-bit, pseudo random number generator was implemented using a Linear Feedback Shift Register (LFSR). The generated pattern will repeat every predetermined clock cycles according to the number of flip flops, m, in the architecture [9]. This is known as the period of the generator. Equation 3.39 relates the number of flip flops in the RNG to its period.

$$period = 2^m - 1 \tag{3.39}$$

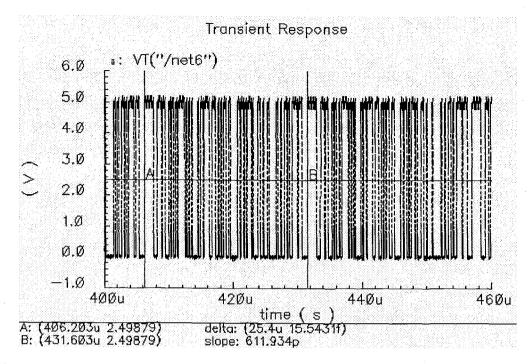

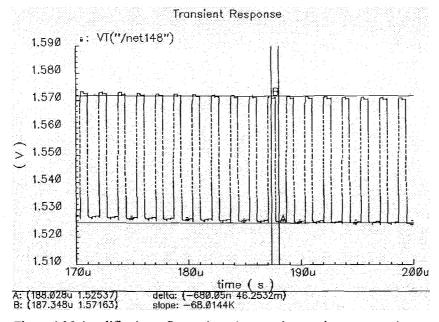

For both test chips, seven D-type Flip Flops (DFFs) were used to implement the RNG. From this implementation, the pattern will repeat every 127 cycles. A 3MHz master clock corresponds to a 600 kHz system frequency when you consider there are 5 phases or master clock cycles per integration cycle. The RNG period is 127 cycles multiplied by the period of one integration cycle, 1.667us. This equates to a 211.667µs period corresponding to a frequency of 4.724 kHz. This repetition at 4.724 kHz will be seen in the spectrum of the system when the dither is activated. The signal power will depend on the dither voltage applied. Therefore, to avoid SNDR degradation, this frequency should not fall in the signal band of interest. For this architecture, the signal band is DC to 200Hz. The simulation result showing that the RNG pattern repeats every 127 cycles is provided in Figure 3.8. From a clock period of 200ns, the simulation verifies the expected RNG period of 25.4µs.

Figure 3.8 Implemented RNG simulation results.

### 3.7 kg: 1-Bit Quantizer

The quantizer of a delta sigma system is the Analog to Digital Converter (ADC). The differential outputs of the integrator are compared resulting in digital output bit stream that modulates. The gain of a 1-bit quantizer is linear and self adjusting within the loop of the delta sigma system. This is an advantage of two-level ADC's. For multi-level quantizers the gain must be determined according to system stability requirements and implemented with adequate linearity.

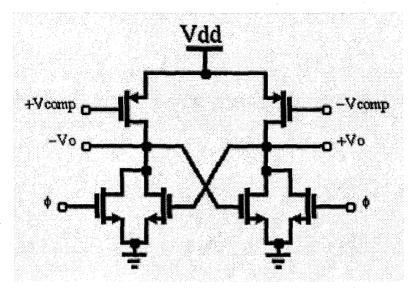

A different comparator shown in Figure 3.9 was implemented in the second revision that has a symmetric error bounded by +(1/2) and -(1/2). The advantage of symmetric quantization error is maximum dynamic range. Another advantage of this comparator is that it consumes less die area.

Figure 3.9 Comparator schematic implementing the single-bit quantizer.

Prior to making a comparison, +Vcomp and -Vcomp shown in the figure are charged to the integrator output Common Mode (CM) voltage. The  $\Phi$  signal is high and creating a current path form Vdd to ground thereby grounding outputs, +Vo and -Vo, and resetting the comparator. If power consumption is a concern, this comparator design is not optimum. When grounding the outputs of the comparator, a constant current consumption is present. When making a comparison, +Vcomp and -Vcomp are valid integrator outputs. The comparator reset signal,  $\Phi$ , is released allowing the cross coupled, positive feedback to drive +Vo and -Vo to opposite rails depending on the value of +Vcomp and -Vcomp. If +Vcomp is greater than -Vcomp, +Vo is pulled to Vdd and -Vo is pulled low.

#### 3.8 k4: Feedback DAC

The constant, k4 feedback is determined by multiplying the differential reference voltage by the DAC integrator gain. Equation 3.40 represents the differential value for k4. The polarity of the feedback depends on the quantizer output.

$$|k4| = (V_{REF} - V_{REF}) \cdot \frac{C_{REF}}{C_{fb}} = 2 \cdot V_{REF} \cdot \frac{100 \, fF}{200 \, fF} = V_{REF}$$

(3.40)

The magnitude of the k4 determines the full scale voltage of the interface integrator, and is adjusted by varying  $V_{REF}$ . Depending on the input signal level, k4 is adjusted accordingly not to saturate the integrator or cause distortion.

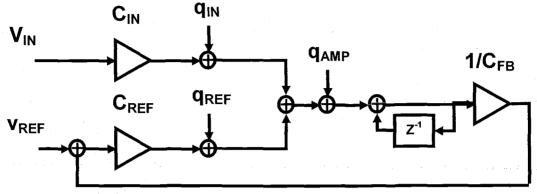

The initial design of the inner-loop feedback DAC changes between a non-inverting and an inverting switch capacitor (SC) structure. The reference voltage,  $V_{REF}$ , is integrated either positively or negatively depending on the control of the switches. This DAC architecture is not ideal. Given that each terminal of the differential feedback has a different SC network while integrating, creates a potential for offset due to mismatch and a reduction in dynamic range due to gain error.

The DAC could have been implemented by using the same SC network, but reversing the polarity of the reference voltage. For example the positive reference voltage would be  $V_{REF}$  to ground, and the negative reference would be ground to  $V_{REF}$ . This architecture has the advantage of limiting the need for extra reference voltages and logic for controlling the switches.

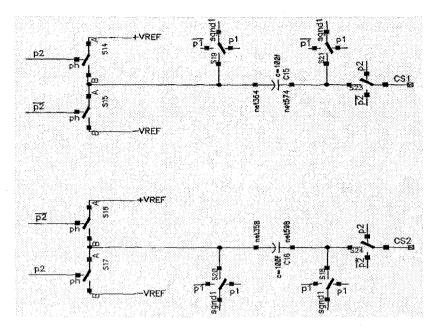

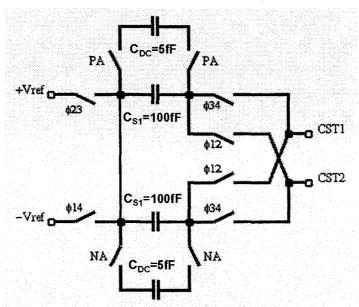

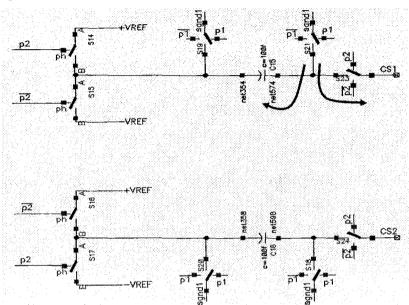

A third solution shown in Figure 3.10 was implemented in the second design revision. This structure uses the same two inverting feedback structures for each differential input. Nodes CS1 and CS2 are the differential inputs to the amplifier of the integrator. During  $\Phi$ 1, the reference capacitors are reset, and during  $\Phi$ 2 the reference voltage is sampled and integrated creating an inverting SC structure. For this implementation a second reference,  $-V_{REF}$ , is needed which could be set to ground. Considering the common mode and stability problems of the initial design, it was preferred to balance the DAC as much as possible. Using the same inverting switch capacitor structure, the  $+V_{REF}$  and  $-V_{REF}$  reference voltages are switched before the DAC. The reference voltage switch polarity is determined by the quantizer output.

Figure 3.10 DAC schematic implementing the k4 feedback.

## 3.9 H<sub>C</sub>(z) Digital Compensator

The accelerometer is a second order system as described in the mass-spring discussion. The sense capacitors are the sampling capacitors of the integrator. This provides the interface between the accelerometer and integrator. An integrator is a first order system. Therefore, the output of the quantizer is a third order response. A compensator or differentiator is needed to reduce the order of the quantized output, so that a required second order signal is feedback to the accelerometer.

The two different approaches to implementing the compensator block are analog or digital. The investigated architecture used a digital compensator [4]. The advantage of a digital compensator is its simplicity. The transfer function of the digital differentiator is provided in Equation 3.41.

$$H_C(z) = 1 - z^{-1} (3.41)$$

The output of the quantizer or input to the compensator is +1 and -1. After passing through the digital compensator's transfer function, the output is +2, 0, and -2. The fact that the output is multi-level having three possible values is one disadvantage of a digital compensator. Adequate linearity of the multi-level force-feedback is necessary in order to minimize system distortion. The inner loop DAC feedback,  $k_4$ , is inherently linear since only a straight line exists between two

possible outputs from the quantizer. The linearity of the three-level force-feedback is improved with a new proposed mismatch shaping scheme [10]. The force-feedback mismatch shaping scheme is presented in Table 3.1. Using the compensator output, the polarity of the force-feedback and the applied phase can be determined.

| Digital Compensator | Mismatch Shaping | Force-Feedback    | Force-Feedback    |

|---------------------|------------------|-------------------|-------------------|

| Output              | Control          | Ф5                | Φ6                |

| 2                   | Ун               | F <sub>FB+</sub>  | F <sub>FB+</sub>  |

| 0                   | Y <sub>M</sub>   | $F_{FB+}$         | F <sub>FB-</sub>  |

|                     | (Alternate)      | F <sub>FB</sub> . | F <sub>FB+</sub>  |

| -2                  | Y <sub>L</sub>   | $F_{FB}$          | F <sub>FB</sub> - |

Table 3.1 Implemented digital compensator output and force-feedback polarity.

### 3.10 Three-Level Force-Feedback

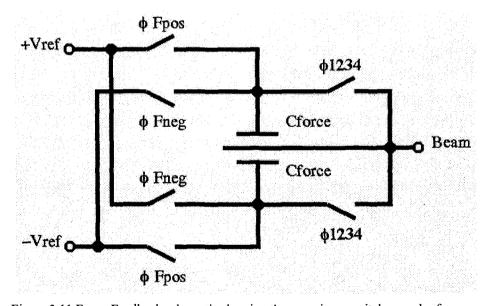

The external force applied to the capacitive sensor is subtracted by the force-feedback of the system's outer loop. The schematic shown in Figure 3.11 is the implementation of the force-feedback.

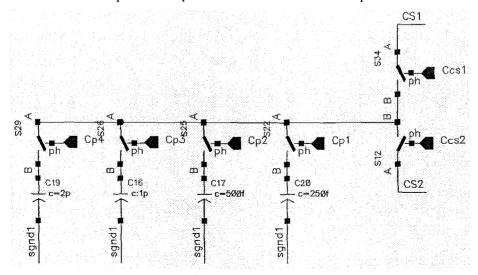

Figure 3.11 Force-Feedback schematic showing the capacitors, switches, and references.

The sense capacitors,  $C_{S1}$  and  $C_{S2}$ , change in value as the beam is displaced due to an external force. However, during force-feedback a charge is placed across the C<sub>FORCE</sub> capacitors in order to electrically force a beam displacement. The C<sub>FORCE</sub> capacitors are additional capacitors identical to the sense capacitors, C<sub>S1</sub> and C<sub>S2</sub>, but with a nominal capacitance of 10fF as compared to 100fF of sense capacitance. In the initial design while the integrator is sampling the acceleration of the sensor, the force-feedback terminals of the sensor are floating. Therefore, an uncontrolled potential of the two force-feedback capacitors could inadvertently create an unwanted electrostatic force. During phase  $\Phi 1$  through  $\Phi 4$ , the interface circuit is completing one cycle of integration. During this period, the CFORCE capacitors should not have an affect on the displacement of the beam while the effects of the external force are being sampled. Therefore, the beam and stationary plate of the CFORCE capacitors are connected together resulting in zero charge across the capacitors. The accompanying positive and negative reference voltages and switches are used to place different charges on the CFORCE capacitors in order to create an electro-static force that displaces the beam. The switches are driven in  $\Phi$ 5. After the four phases needed for integration, the fifth and final phase of the system is use to apply the force feedback. The polarity of the force-feedback switches are determined by the digital compensator and mismatch shaping scheme.

The following discussion will derive the electro-static force equations necessary for modeling the system force-feedback. The energy stored on a capacitor is expressed in Equation 3.42.

$$Energy = \frac{1}{2}Q \cdot V_{TOP} - \frac{1}{2}Q \cdot V_{BOTTOM} = \frac{1}{2}Q \cdot V_{ACROSS} = \frac{1}{2}C_0 \cdot V \cdot V$$

(3.42)

By taking the derivative of the previous equation with respect to the distance between the two plates of the  $C_{FORCE}$  capacitor, d, the electro-static force is determined as shown in Equation 3.43.

Force =

$$\frac{\partial Energy}{\partial d} = \frac{V^2}{2} \cdot \frac{\partial C}{\partial d} = \frac{V^2}{2} \cdot \frac{\partial \left(\frac{\varepsilon A}{d}\right)}{\partial d} = -\frac{\varepsilon A \cdot V^2}{2d^2}$$

(3.43)

In terms of C<sub>FORCE</sub>, the electrostatic force becomes:

$$Force = -\frac{\varepsilon A \cdot V^2}{2d^2} = -\frac{C_{FORCE}}{2d}V^2$$

(3.44)

It is standard practice to use linearity enhancements for multi-level feedback DACs or in this case digital to force converters (DFC). Several algorithms schemes exist to implement dynamic element matching [11]. The only elements available are the two force-feedback

capacitors. The electrostatic force equations for the implemented mismatch shaping scheme are presented below. The 0 output of the digital differentiator corresponds to the  $y_M$  of the mismatch shaping scheme. In order to maintain adequate linearity due to mismatch in the distances between the  $C_{FORCE}$  and sense capacitor, stationary plates and the beam, force-feedback is time averaged [10]. To implement the time averaging the force-feedback is alternated between  $F_{FB+}$  in  $\Phi 5$  with  $F_{FB-}$  in  $\Phi 6$  and  $F_{FB-}$  in  $\Phi 5$  with  $F_{FB+}$  in  $\Phi 6$  as shown in Table 3.1. The mismatch or difference between  $d_1$  and  $d_2$  is averaged to zero over time for the middle level of the DFC by alternating the sequence of applied positive and negative electro-static forces.

$$y_H = 1, F_{FB+} = -\frac{\varepsilon A}{2} \cdot \left[ \left( \frac{V_1 - V_{BEAM}}{d_1 + x} \right)^2 - \left( \frac{V_{BEAM} - V_2}{d_2 - x} \right)^2 \right]$$

(3.45)

$$y_L = 1, F_{FB-} = -\frac{\varepsilon A}{2} \cdot \left[ \left( \frac{V_{BEAM} - V_2}{d_1 + x} \right)^2 - \left( \frac{V_1 - V_{BEAM}}{d_2 - x} \right)^2 \right]$$

(3.46)

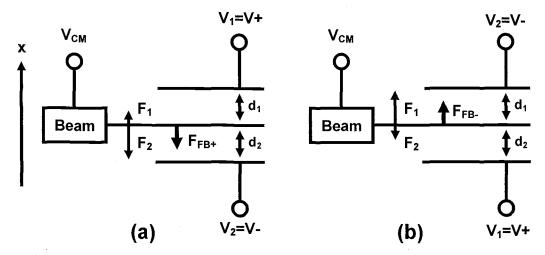

Figure 3.12 illustrates the positive and negative force-feedback Equations 3.45 and 3.46.

Figure 3.12 Implemented (a) positive and (b) negative force-feedback.

## 3.11 Five Phase Integration Cycle

The cycle time of the DS modulator was reduced from six master clock cycles to five. Currently, the fifth and sixth phase used to perform the multi-level force-feedback will now be completed in only the fifth phase of the master clock. The two functions needed to be completed are now finished in two phases of the master clock and not two master clock cycles. The amount

of time used to apply the force-feedback is independent of the first four phases used by the CDS circuit. Reducing the time force-feedback is applied, will increase the DS sampling rate and improve the SNR. An implication due to the fifth phase of this system architecture clocking, is that the sampling of the integrator is non-uniform. The sense capacitors are sampled and integrated in phases two and four. Phase  $\Phi 4$ ,  $\Phi 5$  and  $\Phi 1$  need to be finished before the next sample and integration. Through system simulations this non-uniformity does not have a significant affect on performance.

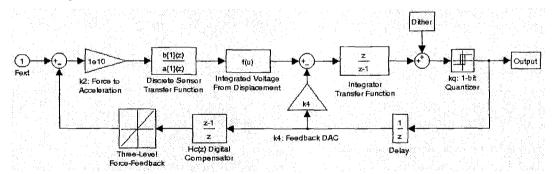

### 3.12 System Simulations

System stability and performance was analyzed and determined through MATLAB Simulink simulation. Each block in the architecture was modeled according to the previous discussions. Figure 3.13 shows the block diagram of the simulation schematic used in Simulink. The advantages of modeling simulations are speed and ease of use. Sensitivity analysis was performed by degrading the linearity of the force-feedback, finite amplifier gain, and mismatch in sense capacitance and distance between beam and stationary plates. Other analog non-idealities, such as amplifier thermal noise and KT/C noise were included in some Simulink simulations.

Figure 3.13 System simulation Simulink schematic.

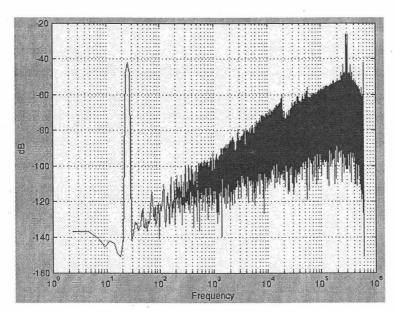

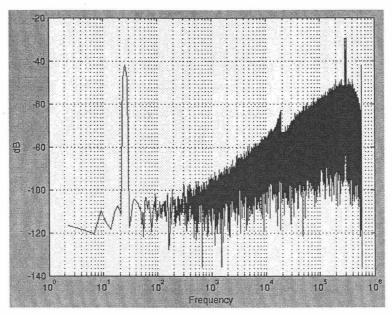

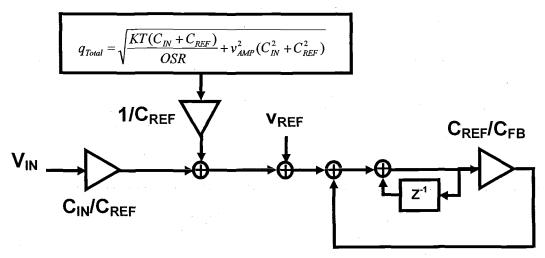

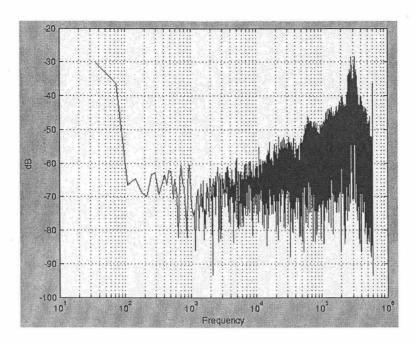

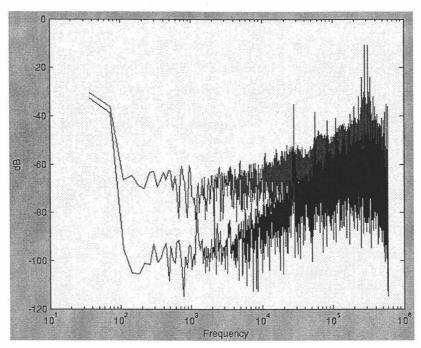

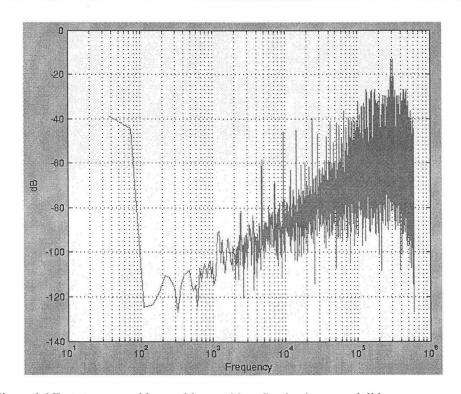

An FFT of the system performance under ideal conditions is presented in Figure 3.14. The force-feedback is linear, sense capacitance and distances  $d_1$  and  $d_2$  are nominal, and the feedback DAC,  $k_4$ , was 0.25V differential. The noise is shaped 20dB per decade or first order shaping due to the interface integrator. This noise shaping would not be present if an amplifier was implemented instead of an integrator. Given a one G input and a sample rate of 600 kHz, the simulated Signal to Noise Ratio (SNR) is 57.5dB for a signal bandwidth of 200 Hz.

Figure 3.14 System simulation results.

Figure 3.15 shows the block diagram of the Simulink schematic with the amplifier thermal noise injected in the summing node of the integrator. This Simulink simulation technique was presented by Franco Maloberti for modeling amplifier non-idealities [12].

Figure 3.15 System simulation Simulink schematic with amplifier thermal noise.

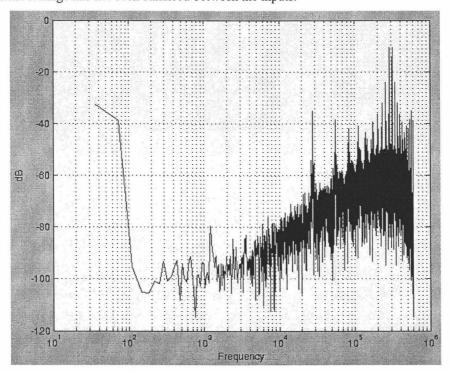

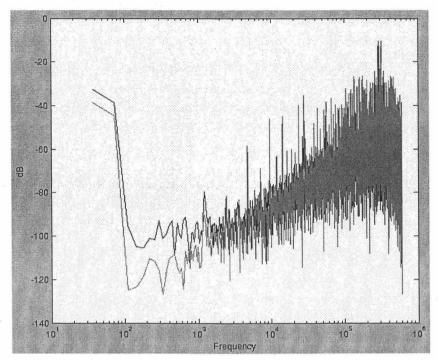

The FFT provided in Figure 3.16 shows that the noise floor has increased from an ideal system of -140dB to a system with amplifier thermal noise of -110dB. The thermal noise injected into the system was 100e-5Vrms. Even though the noise floor was increased due to the included

amplifier thermal noise, a good portion of this noise was shape. Since the noise floor did not significantly increase, due to the large root mean squared (RMS) noise voltage injected in the system.

Figure 3.16 System simulation results with amplifier thermal noise.

#### INTERFACE IMPLEMENTATION

#### 4.1 Process and Simulation Corners

Fabrication of the electrical interface chip was done by American Microsystems Inc. (AMI). AMI is vendor for MOSIS, a low-cost prototyping and small-volume production service for IC development. The interface design was fabricated in a 1.6μm, the minimum MOSFET gate length process.

The Spectre simulator through Cadence was used to simulate the analog blocks of the interface design. The Spectre models available through MOSIS are BSIM3. The models include only the nominal process at room temperature, 27 degrees Celsius, for the NMOS and PMOS devices. No other device process models are present including capacitors and resistors. Noise parameters were not available within the provided models in order to simulate the amplifier thermal and flicker (1/f) noise.

# 4.2 Amplifier Bandwidth Challenges

The amplifier bandwidth requirement depends on the distortion performance needed. A 90dB distortion requirement equates to 31.6228µVrms voltage error as shown in Equation 4.1.

$$error = 1e^{\frac{-Ts}{\tau}} = 90dB = 31.6228\mu V$$

(4.1)

The required unity gain bandwidth is derived from Equation 4.2 resulting in Equation 4.3. Solving  $\tau$ , the settling time constant, from Equation 4.1 and the feedback factor,  $\beta$ , of the amplifier from Equation 4.5 are used to determine  $\omega_{uebw}$ .

$$\tau = \frac{1}{\beta w_{ugbw}} \tag{4.2}$$

$$w_{ugbw} = \frac{1}{\tau \cdot \beta} \tag{4.3}$$

Equation 4.1 is re-arranged in Equation 4.4 to solve for  $\tau$ . Ts represents the time period available for the voltage to settle. This period is the clock period of the switch capacitor sampling clock, Fs. There are four phase in each integration cycle of the integrator. During each phase the node voltages must settle within the determined error voltage of the desired value. With a sampling clock frequency of 3MHz, the corresponding  $\tau$  is equal to 32.17ns.

$$-Ts = \tau \ln(error) \Rightarrow \tau = \frac{-Ts}{\ln(error)} = 32.17ns \tag{4.4}$$

Figure 4.1 Integrator schematic showing the sampling, integrating, and parasitic capacitance.

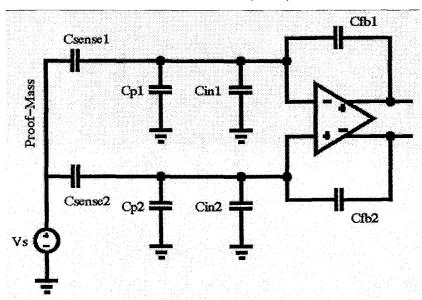

In order to determine the feedback factor, the capacitive network of the integrator is analyzed in Figure 4.1.  $C_{\text{sense}}$  is the sense capacitor of the sensor and sampling capacitor of the interface integrator.  $C_p$  is the sum of the interconnect capacitances associated with this two-chip implementation. The input parasitic capacitance of the amplifier is represented by  $C_{in}$ . The integrating feedback capacitor is  $C_{fb}$ . From the integrator output back to the amplifier input is a capacitive divider representing the closed loop feedback factor of the amplifier as expressed in Equation 4.5.

$$\beta = \frac{C_{fb1}}{C_{fb1} + C_{sense1} + C_{p1} + C_{in1}}$$

(4.5)

The following two equations assume the parasitic capacitance  $C_{pl}$  of 5pF and 20pF. The other capacitances  $C_{fb1}$ ,  $C_{sense1}$ , and  $C_{in1}$  are 200fF, 100fF, and 3pF respectively.

$$f_{ugbw} = \frac{1}{2\pi \cdot \tau \cdot \beta} = \frac{1}{2\pi \cdot 32.17 ns \cdot 0.0240964} = 205.3 MHz \tag{4.6}$$

$$f_{ugbw} = \frac{1}{2\pi \cdot \tau \cdot \beta} = \frac{1}{2\pi \cdot 32.17 ns \cdot 0.0085837} = 576.4 MHz \tag{4.7}$$

The required amplifier bandwidths are extremely fast and difficult to meet with the AMI  $1.6\mu m$  process. The feedback factor,  $\beta$ , is extremely small in this application. From Equation 4.5, the effects of large interconnect parasitic capacitances experienced in this two-chip application can easily be seen on  $\beta$ . There are two negative effects on the amplifier requirements due to small feedback factors. The unity gain frequency bandwidth has been identified. The second is the closed loop gain of the amplifier is greatly reduced. A reduction in loop gain has a detrimental effect of the amplifier's distortion and noise in the integrator.

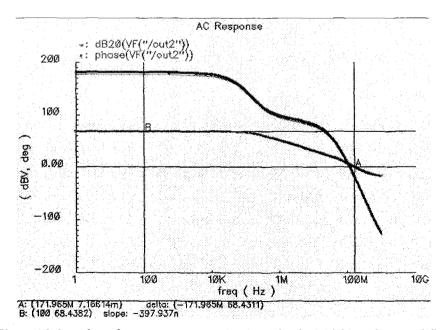

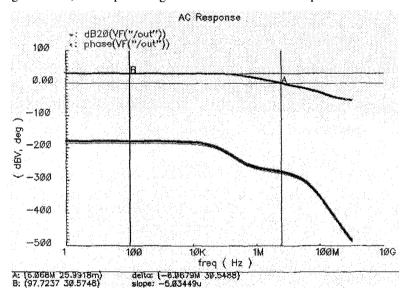

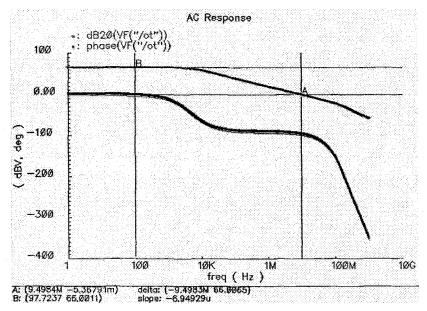

The initial interface amplifier's open and closed loop gain and phase responses are provided in Figures 4.2 and 4.3.

Figure 4.2 Open loop frequency response simulated for the initial interface amplifier.

From the open loop frequency response we can see that the DC gain is 68dB and the unity gain bandwidth is 172MHz with negative phase margin. Negative phase margin in any system will not be stable. However, these simulation results are from an open loop configuration. When determining the stability of a system, the closed loop which includes the feedback factor should be analyzed. Given that the feedback factor in this application is small, the closed loop frequency response is stable. The closed loop gain response is the open loop gain response multiplied by  $\beta$ . Since  $\beta$  is small, the open loop gain is shifted down lowering the gain and bandwidth but increasing the phase margin. This effect can be seen in Figure 4.3 showing the closed loop response.

From the closed loop frequency response we can see that the DC gain has reduced to 30.6dB and the unity gain bandwidth is 6MHz with plenty of positive phase margin. In the second interface design revision, the amplifier's gain and bandwidth were improved.

Figure 4.3 Closed loop frequency response simulated for the initial interface amplifier.

## 4.3 Amplifier Design

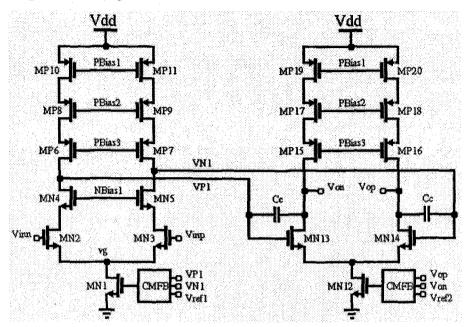

Figure 4.4 Amplifier schematic was implemented in the second design revision.

The integrator amplifier was redesigned in the second interface design as shown in figure 4.4. The two main parameters that needed to be met were the DC gain and unity gain bandwidth. Both of these parameters relate to the distortion and stability performance of the system. Other important amplifier parameters are thermal noise and slew rate. In order to achieve a high DC gain, a large amount of current was needed to increase the input transistor's gm. As a result, the thermal noise is lowered, and the slewing capability of the amplifier is increased with the increase in needed current.

The amplifier has two stages. The first stage is a telescopic amplifier with double cascode PMOS loads. The second stage is a standard differential amplifier with double cascode PMOS loads. A Miller compensation capacitor is present between the two stages for stability.

The gain of a multistage amplifier is the gain of each stage multiplied together. The telescopic stage's gain is expressed in Equation 4.8, and the second stage's gain is provided in Equation 4.9 [13].

$$-gm_{MN2}[(gm_{MN4}ro_{MN4}ro_{MN2})//(gm_{MP6}ro_{MP6}gm_{MP8}ro_{MP8}ro_{MP10})]$$

(4.8)

$$-gm_{MN13}[(ro_{MN13})//(gm_{MP15}ro_{MP15}gm_{MP17}ro_{MP17}ro_{MP19})]$$

(4.9)

Using the AMI 1.6 $\mu$ m process parameters, the gain can be calculated. The following three equations are used to determine the gain. The transconductance, gm, is determined in Equation 4.10 were  $\beta$  is derived from Equation 4.11. The output resistances, ro, are computed using Equation 4.12. The DC current,  $I_D$ , is the nominal bias current. For the second revision design the bias current for each amplifier is 1mA. Lambda,  $\lambda$ , is assumed to be 0.1. This is a reasonable assumption since the process is older with large, channel lengths.

$$gm = \sqrt{2\beta I_D} \tag{4.10}$$

$$\beta = KP \cdot \left( \frac{W}{L} \right) \tag{4.11}$$

$$r_0 = \frac{1}{\lambda \cdot I_D} \tag{4.12}$$

The NMOS and PMOS KP parameters are presented in Equations 4.13 and 4.14 respectively.

$$KP_{NMOS} = 35.9 \,\mu A / V^2 \tag{4.13}$$

$$KP_{PMOS} = 12.1\mu A/V^2$$

(4.14)

NMOS devices 2, 4, and 13 for simplicity are assumed to have the same gm. The amplifier's MOSFETs are sized such that aside from the tail currents all of the NMOS devices have the same W/L, and all of the PMOS devices have the same W/L. This is a reasonable assumption since the devices have the same dimension and  $I_D$  current.

$$gm_{MN13} = gm_{MN2} = gm_{MN4} = \sqrt{2 \cdot 35.9 \binom{\mu A}{V^2} \cdot \binom{1120 \, \mu m}{1.6 \, \mu m} \cdot 1mA}$$

(4.15)

Therefore, the NMOS transconductance,  $gm_N$ , is computed and presented in then following equation.

$$gm_N = 7.0894e - 3 \binom{A_V}{V}$$

(4.16)

The same argument holds for the PMOS transconductance. The  $gm_P$  is computed in the next two equations.

$$gm_{MP15} = gm_{MP17} = gm_{MP6} = gm_{MP8} = \sqrt{2 \cdot 12 \cdot 1 \binom{\mu A}{V^2} \cdot \binom{1472 \, \mu m}{1.6 \, \mu m} \cdot 1 mA} \quad (4.17)$$

$$gm_P = 4.7185e - 3 \left( \frac{A}{V} \right)$$

(4.18)

The output transistor resistances for both NMOS and PMOS devices are approximately  $10k\Omega$ .

$$ro_N = ro_P = \frac{1}{0.1 \cdot 1mA} = 10k\Omega \tag{4.19}$$

Using the previous relationships, the open loop gain of the amplifier is 110.76dB. The actual simulated open loop DC gain was 101.3dB indicating that the approximations and hand calculations are reasonable.

The Unity Gain Bandwidth (UGBW) for a two stage amplifier with a compensation capacitor can be approximated as shown in the following discussion [7]. The equivalent compensation capacitor as seen by the first stage is the following equivalent capacitance using Miller's Theorem derived in Equation 4.20.

$$C_{EQ} = C_C (1 + A_{2ndStage}) \cong C_C \cdot A_{2ndStage}$$

(4.20)

The gain of the first stage is the gm of MN2 and the output impedance of the first stage. The output impedance is the output resistance in parallel with the equivalent capacitance as presented below.

$$A_{1stStage} = -gm_{MN2} \cdot Z_{OUT1} = -gm_{MN2} \cdot \left( R_{OUT1} // \frac{1}{sC_{EO}} \right)$$

(4.21)

For mid-band frequencies, the equivalent capacitance will dominate the output impedance as shown in Equation 4.22. The equation also shows the equivalent capacitance in terms of the compensation capacitor and the second stage gain.

$$A_{1stStage} \cong -gm_{MN2} \cdot \frac{1}{sC_{EO}} = -gm_{MN2} \cdot \frac{1}{sC_{C}A_{2ndStage}}$$

(4.22)

The total gain of the amplifier is the first and second cascaded stages multiplied together. The resulting amplifier gain is shown in Equation 4.23.

$$A(s) = A_{1stStage} \cdot A_{2ndStage} = gm_{MN2} \cdot \frac{1}{sC_C A_{2ndStage}} \cdot A_{2ndStage} = \frac{gm_{MN2}}{sC_C} \quad (4.23)$$

In order to determine the unity gain bandwidth, the magnitude of the amplifier gain is set to one.

$$|A(jw)| = 1(UGBW) \tag{4.24}$$

From this relationship, the UGBW frequency is 564.2MHz.

$$\therefore f_{UGBW} = \frac{gm_{MN2}}{2\pi \cdot C_C} = \frac{7.0894e - 3}{2\pi \cdot 2pF} = 564.16MHz \tag{4.25}$$

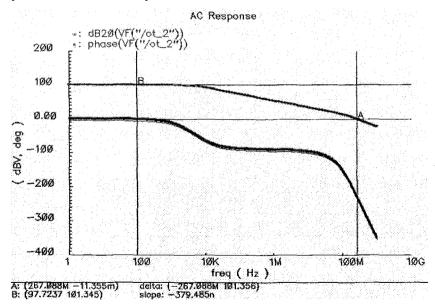

The simulation results for the gain and phase responses are shown in the next figures. The open loop, simulation results provided in Figure 4.5 confirm that the second revision amplifier has improved the DC gain and the UGBW. As expected, the open loop phase margin is negative. Figure 4.6 shows that the closed loop phase margin of the amplifier when applied in the system is positive and stable. The DC gain and unity bandwidth of this op-amp has been significantly increased over the initial fabricated design.

Due to the design requirements of the integrator, the amplifier has several layers of cascode. There is a need for the bias circuit to bias each device of the cascode without significantly degrading the output swing of the amplifier. A negative effects of interconnect parasitic capacitance is an increase in gain error. The extra voltage integrated due to gain error demands as large an output swing as possible. A wide-swing current mirror was implemented for this reason.

In any system, trying to achieve high accuracy noise is important. In switch capacitor networks, the thermal noise of the amplifier is sampled on the sampling and reference capacitors. The thermal noise of the amplifier is also sampled on interconnect parasitic capacitance. This is contrary to the initial design understanding and will be discussed later in this chapter and shown through experimental results in Chapter 6.

Figure 4.5 Open loop frequency response simulated for the re-designed interface amplifier.

Figure 4.6 Closed loop frequency response simulated for the re-designed interface amplifier.

For this research, hand calculations of the amplifier thermal noise were relied upon. The Spectre models provided by AMI did not include noise model parameters for simulation. The flicker noise is not computed since the integrator implementation reduces flicker noise through correlated double sampling (CDS).

There are several devices in an amplifier design, and only the devices in the signal path are important for noise analysis. For example, bias circuitry is not significant and should not be considered as noise sources. The noise in the second stage of a two-stage amplifier, as in this design, is not a significant noise source. When the noise generated in the second stage is referred to the input, it is divided by the square of the first stage gain. The noise from the tail current device, MN1, can be canceled with proper, layout techniques through symmetry and matching. Therefore, the noise sources to be considered are MN2-MN5 and MP6-MP11 of the telescopic, first stage amplifier.

$$\overline{i_{ON}^2} = g m_{N2}^2 \cdot \overline{v_{N2}^2} + g m_{N3}^2 \cdot \overline{v_{N3}^2} + g m_{N4}^2 \cdot \overline{v_{N4}^2} + g m_{N5}^2 \cdot \overline{v_{N5}^2}$$

(4.26)

$$\overline{i_{OP}^2} = gm_{P6}^2 \cdot \overline{v_{P6}^2} + gm_{P7}^2 \cdot \overline{v_{P7}^2} + gm_{P8}^2 \cdot \overline{v_{P8}^2} + gm_{P9}^2 \cdot \overline{v_{P9}^2} + gm_{P10}^2 \cdot \overline{v_{P10}^2} + gm_{P11}^2 \cdot \overline{v_{P11}^2}$$

(4.27)

$$\overline{i_O^2} = \overline{i_{ON}^2 + i_{OP}^2} \tag{4.28}$$

Through layout techniques of symmetry and matching, Equations 4.26 and 4.27 can be simplified.

$$\overline{i_O^2} = 2gm_{N3}^2 \cdot \overline{v_{N3}^2} + 2gm_{N5}^2 \cdot \overline{v_{N5}^2} + 2gm_{P7}^2 \cdot \overline{v_{P7}^2} + 2gm_{P9}^2 \cdot \overline{v_{P9}^2} + 2gm_{P11}^2 \cdot \overline{v_{P11}^2}$$

(4.29)

Equation 4.29 is output referred noise in terms of drain current. The input referred thermal noise is represented in Equation 4.30.

$$\overline{v_{NIN}^2} = \frac{\overline{i_O^2}}{gm_{N3}} = 2\left[\overline{v_{N3}^2} + \frac{gm_{N5}^2}{gm_{N3}^2} \cdot \overline{v_{N5}^2} + \frac{gm_{P7}^2}{gm_{N3}^2} \cdot \overline{v_{P7}^2} + \frac{gm_{P9}^2}{gm_{N3}^2} \cdot \overline{v_{P9}^2} + \frac{gm_{P11}^2}{gm_{N3}^2} \cdot \overline{v_{P11}^2}\right] (4.30)$$

The input referred noise voltage for a transistor in saturation is show in Equation 4.31. If the bulk and source do not have the same potential, then Equation 4.32 applies. The temperature, T, is in Kelvins and typically 300 degrees. K is the Boltzmann constant equal to  $1.38 \times 10^{-23}$  (J/K), and  $f_{SBW}$  is the signal band of interest.

$$\overline{v_{NT}^2} = 4KT \frac{2}{3} gm \cdot f_{SBW} \tag{4.31}$$