#### AN ABSTRACT OF THE THESIS OF

<u>David Arnett</u> for the degree of <u>Master of Science</u> in <u>Electrical and Computer Engineering</u> presented on <u>18 June 1998</u>. Title: <u>Digital Clocks Based upon Dual Side Band Suppressed</u>

<u>Carrier Modulation</u>.

| Abstract approved: | R  | ec | dacted | d for | Privacy |

|--------------------|----|----|--------|-------|---------|

| Vijai K. Tripat    | hi |    | •      |       |         |

A method and apparatus are presented for generating suppressed carrier digital clock signals. These clock signals have the advantage of being broad band in nature and thus exhibiting lower power spectral density. Structures or systems utilizing such clock signals would be less likely to create electromagnetic noise of sufficient intensity to interfere with radio frequency systems and services.

The apparatus requires only digital logic devices, rather than the analog devices required for frequency- or phase-modulated spread spectrum clock generators. The method provides the opportunity to synchronously demodulate the clock, thus restoring the original narrow band clock signal where required.

The apparatus was implemented in a programmable gate array using 20 MHz and 33.33 MHz fundamental clocks. Measurements of the resulting electronic spectra and clock jitter are reported.

© Copyright by David Arnett 18 June 1998 All Rights Reserved

# Digital Clocks Based upon Dual Side Band Suppressed Carrier Modulation

by

David Arnett

### A THESIS

submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Master of Science

Presented 18 June 1998 Commencement June 1999

| Master of Science thesis of David Arnett presented on 18 June 1998 |  |

|--------------------------------------------------------------------|--|

|                                                                    |  |

APPROVED:

# Redacted for Privacy

Major Professor, representing Electrical and Computer Engineering

Redacted for Privacy

Head or Chair of Department of Electrical and Computer Engineering

# Redacted for Privacy

Dean of Graduate School

I understand that my thesis will become part of the permanent collection of Oregon State University libraries. My signature below authorizes release of my thesis to any reader upon request.

Redacted for Privacy

David Arnett, Author

#### ACKNOWLEDGMENT

I have appreciated the ideas and support of many instructors, friends, and colleagues who have encouraged and supported me during the pursuit of this degree and preparation of this thesis. Some deserve a special measure of appreciation, including Dr. Vijai Tripathi, Dr. Bill Warnes, Bob Puckette, Larry Arnett, Mark Smith, and Russ Carlson.

There is one whose support has been most noteworthy and constant: my dear wife, Stacya. It is a fortunate man who marries so well.

## TABLE OF CONTENTS

| 1. INTRODUCTION                | 1  |

|--------------------------------|----|

| 2. TECHNOLOGY OVERVIEW         | 9  |

| 3. THEORY AND ANALYSIS         | 10 |

| 4. CIRCUIT IMPLEMENTATION      | 24 |

| 5. MEASUREMENT CONFIGURATIONS  | 39 |

| 6. EXPERIMENTAL RESULTS        | 42 |

| 7. DESIGN SCENARIOS            | 67 |

| 8. CONCLUSIONS                 | 73 |

| 9. SUMMARY                     | 75 |

| BIBLIOGRAPHY                   | 76 |

| APPENDICES                     | 77 |

| APPENDIX A. ANALYSIS PROGRAMS  | 78 |

| APPENDIX B. TERMS AND ACRONYMS | 81 |

| APPENDIX C. CONTROL SWITCHES   | 87 |

### LIST OF FIGURES

| <u>Fig</u> | <u>ure</u>                                                                    | Page     |

|------------|-------------------------------------------------------------------------------|----------|

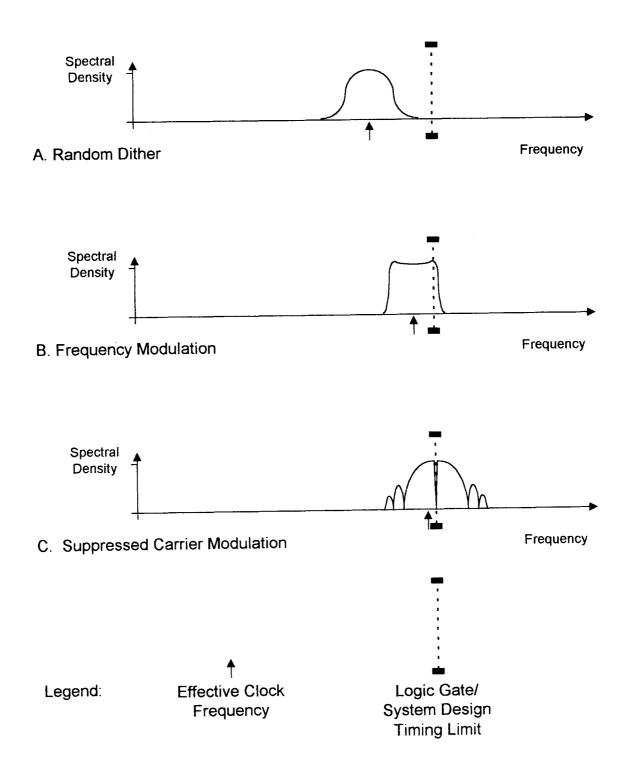

| 1.1        | Spread Spectrum Technology Comparisons                                        | 7        |

| 3.1        | Spectral analysis of pure square waves by graphic and numeric processes.      | 11       |

| 3.2        | Spectral analysis of modulated square waves by graphic and numeric production | cesses13 |

| 4.1        | A simple modulator-demodulator pair.                                          | 25       |

| 4.2        | A buffered modulator-demodulator pair.                                        | 27       |

| 4.3        | Timing Diagram                                                                | 28       |

| 4.4        | A stand-alone buffered modulator.                                             | 31       |

| 4.5        | Top side of circuit board                                                     | 33       |

| 4.6        | Bottom side of circuit board.                                                 | 34       |

| 4.7        | External view of test assembly                                                | 35       |

| 4.8        | Circuit board with redesigned transmission lines.                             | 37       |

| 6.1        | 20 MHz Baseline                                                               | 43       |

| 6.2        | 33.33 MHz Baseline                                                            | 43       |

| 6.3        | Null Experiment                                                               | 45       |

| 6.4        | 20 MHz Clock with 2.5 MHz Square Wave Modulation                              | 47       |

| 6.5        | 33.33 MHz Clock with 2.083 MHz Square Wave Modulation                         | 48       |

| 6.6        | 20 MHz Clock with 2.5 MHz Square Wave Modulation and Marks                    | 49       |

| 6.7        | 33.33 MHz Clock with 4 <sup>th</sup> Order Pseudo-Random Modulation           | 52       |

| 6.8        | 33.33 MHz Clock with 2.1 MHz Square Wave Modulation                           | 56       |

### LIST OF FIGURES, cont'd.

| <u>Page</u>                                             | Figu |

|---------------------------------------------------------|------|

| 3.33 MHz Clock with 4.2 MHz Square Wave Modulation57    | 6.9  |

| 3.33 MHz Clock with 8.3 MHz Square Wave Modulation      | 6.10 |

| Modulated 33.33 MHz Clock Without Source Termination    | 6.11 |

| Modulated 33.33 MHz Clock With Source Termination Added | 6.12 |

| extreme Side Band Asymmetry of Modulated 20 MHz Clock65 | 6.13 |

| 3.33 MHz Design Baseline. 68                            | 7.1  |

| Design Scenario #168                                    | 7.2  |

| Design Scenario #270                                    | 7.3  |

### LIST OF TABLES

| Table | <u>Pag</u>                                                                                                                                            | <u>ge</u> |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| 3.1   | Binary Patterns and Logical Patterns                                                                                                                  | .5        |

| 6.1   | 20 MHz Baseline Data.                                                                                                                                 | 14        |

| 6.2   | 33.33 MHz Baseline Data                                                                                                                               | 14        |

| 6.3   | 2.5 MHz Modulation Spectrum                                                                                                                           | 50        |

| 6.4   | 20 MHz Clock with 2.5 MHz Square Wave Modulation                                                                                                      | 51        |

| 6.5   | 4 <sup>th</sup> Order 2.222 MHz Pseudo-Random Modulation                                                                                              | 51        |

| 6.6   | 33.33 MHz Clock with 4 <sup>th</sup> Order 2.222 MHz Pseudo-Random Modulation                                                                         | 53        |

| 6.7   | Measured Effective Frequencies                                                                                                                        | 54        |

| 6.8   | Side Band Amplitudes with Various Narrow Band Modulation Profiles                                                                                     | 55        |

| 6.9   | Side Band Amplitudes with Various Broadband Modulation Profiles                                                                                       | 59        |

| 6.10  | Amplitude Reductions in the Spectra of 33.33 MHz Clocks with Square-Wave at Pseudo-Random Modulation Signals having Comparable Effective Frequencies. | nd<br>60  |

| 7.1   | Amplitude Reductions due to the Design Scenario #1 Modulation Profile                                                                                 | 69        |

| 7.2   | Amplitude Reductions Measured on the Modulated Clock Signal due to the Desi<br>Scenario #2 Modulation Profile                                         | ign<br>71 |

| 7.3   | Amplitude Reductions Measured on the Modulation Signal due to the Design                                                                              | .71       |

# Digital Clocks Based upon Dual Side Band Suppressed Carrier Modulation

#### 1. Introduction

Electronic devices become more reliable and efficient as engineers design them to operate within an appropriate set of environmental conditions. Electromagnetic noise is a significant environmental constraint for many products and systems, and could cause many devices to malfunction unless the levels of man-made electromagnetic noise were controlled. Stray noise can impact communications, navigation, and other critical radio services. Fortunately, there are technologies and standards that enable engineers to reduce the electromagnetic noise generated by their designs. The work described in this thesis is an additional technology - a tool - for controlling the emissions from digital systems into the electromagnetic environment.

#### 1.1 Electromagnetic Interference

Electromagnetic interference (EMI) occurs when radio noise from one electronic system disrupts the function of another system. Many countries have enacted laws that limit the strength of radio emissions from various classes of products. Some companies and military organizations have additional standards. These standards are all directed to achieving the objective defined in the European EMC Directive (European Council, 1989):

The apparatus ... shall be so constructed that:

- a. the electromagnetic disturbance it generates does not exceed a level allowing radio and telecommunications equipment and other apparatus to operate as intended;

- b. the apparatus has an adequate level of intrinsic immunity to electromagnetic disturbance to enable it to operate as intended.

Interference requires three components: a noise source, a noise receptor, and a coupling path (Ott, 1988). A noise source can be any device that creates electromagnetic fields. A noise receptor is a device that responds to those fields in an unintended manner. The coupling path comes in many forms, and may include signal cables, power cables, or free space. The coupling path determines how much radio power from the noise source will impinge upon the receptor. By eliminating or modifying any of these three components, one can prevent troublesome interference effects. The condition in which interference effects are sufficiently controlled is called Electromagnetic Compatibility, or EMC.

#### 1.2 Radio Systems

Many cases of electromagnetic interference involve radio systems. Radio transmitters intentionally create strong electromagnetic fields, thereby acting as the noise source. A well-known example is the HERO problem, which deals with the Hazards of Electromagnetic Radiation to Ordnance. It is a standard practice on many military ships to keep missiles and explosives away from radar dishes, because the strong radio pulses from such dishes can overload the propellant igniters or explosive initiators.

Radio receivers also are involved in many cases of interference, because they are intentionally designed to respond to radio waves. They can act as noise receptors. A well-publicized example of this arises from the use of personal electronic devices aboard airplanes. Many airlines restrict the types of electronic devices that passengers can use in flight, especially during the approach and departure phases of flight. These restrictions were established because cell phones, electronic toys, and other devices that seem safe can actually interfere with navigational radio systems.

Radio receivers typically contain very selective narrow band filters. For interference to occur, a noise source must emit significant radio power within the input band of the tuned receiver or its intermediate tuner stages.

#### 1.3 High Speed Digital Systems

High speed digital systems are a very common source of electromagnetic noise, and often cause interference to other devices and systems. This happens mainly due to system clocks that are repetitive square wave signals. Interference may also occur on occasion as a result of data interactions, which are synchronous to the system clocks. The characteristics of these clock and data signals that allow them to cause interference are their high frequencies, their high harmonic content, and their narrow bandwidths which may be only a few hundred Hertz wide or less. The high frequency has functional value in that it permits faster data manipulation. The high harmonic content is necessary to provide clean signal edges. The narrow bandwidth is not always necessary, it is present as a result of the crystal oscillators used to generate reliable high frequency timing.

# 1.4 Spread Spectrum Clocks within Digital Systems

The manner in which a clock signal is used in high speed digital systems can generally be grouped into one of three categories: for direct drive of digital systems, as a frequency reference for phase locked loop (PLL) frequency synthesis; and as a timing reference for PLL synchronized data interchange. Each usage category responds differently to broad band clocks.

A fast digital clock is commonly used to indicate when data is valid on a bus, but sometimes data is simply synchronized to phase-locked loops at the data source and destination. The PLLs are synchronized using a slower clock or intermittent strobe.

Narrow band clocks are critical for PLL synchronized data interchange. Systems that use this method include x86-class microprocessors, and the low-voltage differential signaling system (LVDS) used on many flat panel displays. Even the analog color system used in color television relies on PLL synchronized data interchange. Variations in the clock

operation, in the form of cycle-to-cycle jitter or frequency hopping, can cause data loss in such systems.

A clock used as a reference frequency for PLL synthesis can accommodate more jitter and frequency drift, though there are limits at which the synthesis becomes unstable (Hardin et al., 1997). PLL synthesis is used in many microprocessor systems, as well as digitally tuned radio and television sets, to generate a stable, digitally-selectable high frequency signal from a low frequency oscillator.

In the end, almost every digital clock is used to drive logic gates, such as NAND gates, latches and flip-flops. Clocks used to drive circuitry directly can withstand jitter and frequency variation without any difficulty, so long as the design meets the minimum values for clock period, data setup time, and data hold time. These minimum timing values are violated when the high period or the low period of the clock is shortened beyond an acceptable limit.

Spread spectrum clocks reduce interference to radio systems by spreading the electromagnetic emissions across a wider band of frequencies. Narrow bandwidth radio tuners are less likely to experience interference from digital systems using broad band clocks, because their own receiver filters tend to reject most of the noise power. Exchanging a narrow band clock for a spread spectrum clock will not generally decrease the power in an emission; rather, it decreases the power spectral density. This modification to the noise source can resolve many interference problems.

The application of a spread spectrum clock to a circuit or system must be done with an understanding of how that system uses the clock: for direct drive, synthesis, or synchronization. The cycle-to-cycle jitter and frequency drift characteristics of the spread spectrum clock must meet the requirements of the system.

#### 1.5 Existing Spread Spectrum Technologies

Spread spectrum methods are increasingly popular in radio communications.

These include methods of digitally double-modulating a radio carrier to improve efficient use of the communication channels. The second digital modulation is done with an encryption key, and several transmitters broadcast into overlapping frequency channels. The various keys used in a channel are mathematically orthogonal so the individual information streams in the channel can be recovered and discriminated.

Digital systems that use spread spectrum clocks for control of electromagnetic interference are not nearly so elegant. There are two basic methods in use: random phase or frequency variations, or controlled frequency modulation (FM).

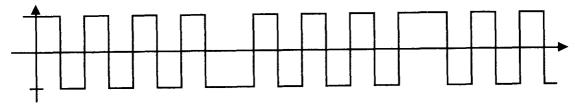

The random methods are quick, cheap, and dirty: a disturbance signal is injected somewhere within the clock generation circuit. This disturbance signal causes the phase or frequency to shift from the oscillator's steady state conditions. The clock circuit recovers and establishes a new steady state condition. The disturbance signal changes again and again, forcing more recovery processes and steady state conditions. The resulting clock signal has spread spectrum characteristics. A clock with these random variations is called a dithered clock. The signal may also include significant levels of jitter or frequency drift, making these generally useful only for direct drive circuitry. Due to the random nature of these dithering methods, the clock period may be lengthened or shortened while trying to restore steady state conditions. This can impact the timing margin in the digital design, and so the designer must take this effect into account. The effective clock rate or effective frequency of a signal is the number of low-to-high transitions per second. A circuit designer who uses random dithering must make the effective clock rate low enough so that the minimum timing requirements of the logic gates are not violated during the system's randomized timing variations, as shown in the

upper graph of Figure 1.1. The random variation method is not useful in circuits involving phase locked loops, or in high performance systems where the effective clock frequency must be near the minimum cycle time limit, defined by either the logic gate technology or the overall system design.

The FM method of spread spectrum clock generation is best described in work done by engineers at Lexmark, Inc. Their method uses a narrow band reference clock to create a frequency modulated output clock. The modulation is performed with a patented modulation wave, optimized to result in a flat frequency spectrum over the modulation band (Hardin et al., 1994). The frequency deviation of the fundamental may be set to provide the desired power spectral density. The deviation is multiplied for harmonics, such that higher harmonics have a wider spectral spread.

This FM method tends to work quite well in direct drive systems. With appropriate modulation rates, it works well in frequency synthesis systems, though the PLL loop filter within the synthesis circuit may alter the flatness of the emission spectrum. It is less useful in synchronization applications, though it can provide acceptable results. The major drawback of this method is that it requires phase locked loops, or similar analog devices, to establish low-jitter clocking. This makes the technique difficult to implement on a silicon process which is optimized for high speed digital operation. The effective clock rate depends on the modulation wave shape. Generally, the effective clock rate is set below the maximum permissible clock rate by the amount of the FM deviation, as shown in the middle graph of Figure 1.1.

# 1.6 A Dual Side Band Supressed Carrier Spread Spectrum Clock

This work presents a different method and system for generating a spread spectrum digital clock based upon dual side band suppressed carrier amplitude modulation, which is useful for most digital clock applications. The system is entirely digital, and is compatible with existing digital technology. The method does not create

Figure 1.1: Spread Spectrum Technology Comparisons.

random short pulses that might violate minimum timing specifications, but allows the designer to achieve an effective clock rate that is closer to the maximal clock rate of the circuit, as suggested in the lower graph of Figure 1.1.

#### 2. Technology Overview

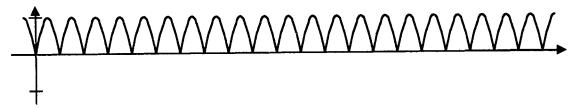

Existing spread spectrum technologies modulate the phase or frequency of a wave to achieve broadband signal characteristics. The method described here uses amplitude modulation to create a broadband signal. A dual side band suppressed carrier clock can replace the narrow band square wave clock used in digital electronics.

A square wave clock changes between a logical 1 and a logical 0 at regular intervals. One could look at it as a bit pattern: 10101010101010101010101010. In the new scheme, transitions will be omitted from time to time, to make a bit pattern more like this: 1010110101010101010101. This modification to the pattern could be viewed as a phase delay; however, it is more useful to think in terms of repeatedly changing the polarity of the signal.

By changing the polarity of the signal, bits tend to cancel each other in the frequency domain. In fact, the signal energy moves into the side bands commonly discussed in AM modulation theory. The end result is that the modulation pattern - the template which determines how often the bit polarity will be inverted - will completely determine the shape of the side bands. Spectral reductions of greater than 20 decibels are noted in this thesis.

Many digital devices can use this clock as their timing reference. Others can use this clock only when distributing signals across cables or between chassis. This method has the capability of demodulating the signal so that the original square wave clock is recovered at the receiving circuit.

The proposed method uses only logic gates. It does not require the use of analog devices -such as phase locked loops - in digital designs.

#### 3. Theory and Analysis

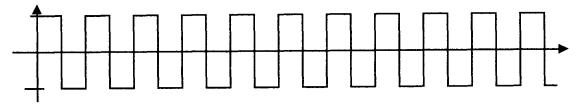

## 3.1 Phase Inversion and Spectral Cancellation

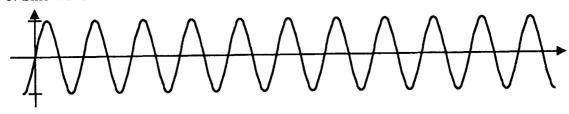

Consider the waves shown in Figure 3.1. The first wave, (a), represents a standard square wave moving between the binary values +1 and -1. The second, (b), is a sinusoidal wave with the same fundamental frequency as the square wave. Fourier analysis of the square wave would show a peak in the frequency spectrum at the frequency of the sinusoidal wave.

The Fourier transformation,  $G(\omega)$ , of a function, g(t), is generated by comparing g(t) with a sinusoidal wave (or,  $e^{-j\omega t}$  in general) at every frequency,  $\omega$ . The function g(t) and the sinusoidal wave are compared by multiplying them together, and their product is integrated over a time period, such as  $-\infty$  to  $\infty$ . For any value of  $\omega$ , the transformed function,  $G(\omega)$ , will have some value corresponding to the power spectral density of the original function, g(t), at frequency  $\omega$ .

If the first two functions of Figure 3.1 were multiplied, as shown in part (c), the resulting function would always be positive: when the sine wave is positive, the square wave is positive, yielding a positive product; when the square wave is negative, the sine wave is negative, and the result is again positive. Since wave (c) is always positive, its average value of is also positive. The Fourier transform of the square wave has a peak at the frequency of the sinusoidal wave, indicating that the wave has power at the frequency of the sine wave. This power implies a possibility of interfering with a radio receiver tuned to the frequency of the sine wave.

Figure 3.1 includes an ordered set of numbers, (d), representing the square wave as a binary pattern of +1 and -1 values. Figure 3.1 also includes (e), a Fast Fourier Transform of that digital pattern. Only the integer part of the magnitude of the Fast

a. Square wave

b. Sine wave

c. Product function

d. Numeric pattern representing the square wave

e. Fast Fourier Transform of the numeric square wave pattern

Figure 3.1: Spectral analysis of pure square waves by graphic and numeric processes. Parts a, b, and c demonstrate the graphic process; parts d and e represent the numeric process.

Fourier results will be shown, though the values are often complex numbers. The Fast Fourier Transform identifies repetitions in a signal, and each entry in the transformed number set corresponds to a different repetition rate or frequency. The peak value of 16 located at position 9 in the transformed pattern corresponds to the fundamental frequency of the square wave.

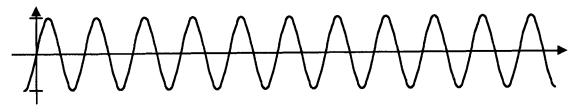

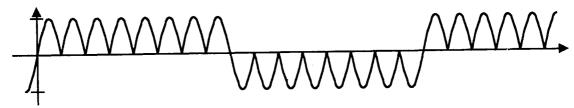

Compare these results to those in Figure 3.2. The first wave, (a), is like the square wave in Figure 3.1, except that the magnitude is inverted every four cycles. This is a suppressed carrier modulated square wave, and its spectral properties form the basis of this work. When the modulated wave, (a), and the sine wave, (b), are multiplied, their product function, (c), is sometimes positive and sometimes negative. The average value of this product function is exactly zero. A Fourier analysis would show no energy peak at the frequency of the sine wave. A radio receiver tuned to the frequency of the sine wave would not experience interference from this square wave.

Figure 3.2 also includes a binary representation of the wave with inversion, (d), and a Fast Fourier Transform of that binary pattern, (e). This transform shows two immediately significant properties. The first is that element 9, corresponding to the frequency of the sine wave, is zero. Note that other elements in the transformed pattern are nonzero, suggesting that the energy in such a wave would be distributed across many frequencies. The second significant property is that the highest value in Figure 3.1(e) was 16, but the peak lowered to a value of 10 in Figure 3.2(e).

## 3.2 Suppressed Carrier Modulation

Suppressed carrier modulation can be considered mathematically from several different viewpoints. Starting with a binary pattern C which represents a clock or square wave, and a binary modulation pattern M, the modulated binary pattern S can be generated in either of two equivalent processes.

a. Modulated square wave

b. Sine wave

c. Product function

d. Numeric pattern representing the modulated square wave

e. Fast Fourier Transform of the numeric modulated square wave pattern

Figure 3.2: Spectral analysis of modulated square waves by graphic and numeric processes. Parts a, b, and c demonstrate the graphic process; parts d and e represent the numeric process.

The first process is an element-by-element multiplication process:

$$\mathbf{S}_{j} = \mathbf{A} \ \mathbf{C}_{j} \ \mathbf{M}_{j} + \mathbf{B}$$

for  $j = 1$  to n Eq. 3.1

$$\mathbf{C}_{j} \in \{ -1 + 1 \}$$

$$\mathbf{M}_{i} \in \{ -1 + 1 \}$$

Where C, M and S are binary patterns of length n. The scalar constants A and B are selected so that  $S_j$  maps into the same binary space as  $C_j$  and  $M_j$ . For binary values in the set  $\{-1+1\}$ ,  $A=\pm 1$  and B=0.

Equation 3.1 defines an amplitude modulation process. Standard amplitude modulation is based upon the equation

$$f(t) = A \sin(2\pi f_c t) [1 + m(t)]$$

Eq. 3.2

where f(t) is the modulated signal,  $f_c$  is the carrier frequency, and m(t) is the modulation signal. Since the quantity [1 + m(t)] is assured to be positive, there is always some spectral energy at the frequency  $f_c$ .

Suppressed carrier amplitude modulation, by contrast, has little or no energy at the carrier frequency  $f_{\rm c}$ . It is based upon the equation

$$f(t) = A \sin(2\pi f_c t) m(t)$$

Eq. 3.3

This modulation is similar to that described in Equation 3.1. The relationship exists more clearly between Equation 3.1 and Equation 3.3 when: C is the binary pattern of a square wave with a fundamental frequency fc; the variable A in Equation 3.3 takes the value one, with A and B in equation 3.1 set to +1 and 0 respectively; and M is a binary-valued substitute for m(t).

The second equivalent process for generating the modulated pattern S from C and M is to represent the patterns as logical values and perform a bit-by-bit exclusive-OR operation. The mapping of the logical space  $(0\ 1)$  into the binary space  $\{-1\ +1\}$  is not unique. For mathematical purposes in this chapter, the logical state 0 will map to the

binary value +1, and the logical state 1 will map to the binary value -1. The mapping will be different in later chapters of this thesis, to better suit the mappings commonly used in electrical engineering. Once a mapping relationship is established, any binary-valued pattern  $\mathbf{P}$  will uniquely map to a logical pattern  $\mathbf{P}$ , and vice versa.

Let the binary patterns S, C, and M map into the logical patterns S, C, and M. The process of Equation 3.1 may be equivalently written as

$$S_i = C_i \oplus M_i$$

for  $j = 1$  to n Eq. 3.4

Table 3.1 demonstrates how  $\mathbb{C}$ ,  $\mathbb{M}$ ,  $\mathbb{S}$ ,  $\mathbb{C}$ ,  $\mathbb{M}$ , and  $\mathbb{S}$  relate under these mappings and modulation processes. Suppressed carrier modulation can be implemented in a binary system by using Equation 3.1, or in a logical system by using Equation 3.4. Binary patterns in brackets [], and logical patterns in braces  $\{\}$  will be used interchangeably in the remainder of this text.

Table 3.1: Binary Patterns and Logical Patterns.

| Binary Patterns |                     | Logical Patterns             |               |  |

|-----------------|---------------------|------------------------------|---------------|--|

| С               | [-1 +1 -1 +1 -1 +1] | С                            | {101010}      |  |

| M               | [-1 -1 +1 +1 -1 +1] | M                            | {1 1 0 0 1 0} |  |

| $S_i = C_i M_i$ | [+1 -1 -1 +1 +1 +1] | $S_{i} = C_{i} \oplus M_{i}$ | {0 1 1 0 0 0} |  |

## 3.3 Side Bands from Narrow Band Suppressed Carrier Modulation

Analog communication theory predicts that an amplitude modulation process will produce side bands equally spaced above and below the carrier frequency. The side bands are related in frequency and amplitude to the carrier frequency and the spectral content of the modulation signal. The Fast Fourier Transform pattern of Figure 3.2e showed spectral content equally spaced above and below position 9 in the pattern, where position 9 corresponded to the carrier frequency before modulation. This suggests that the side bands predicted in analog communication theory also appear as a result of the digital processes detailed above in Section 3.2.

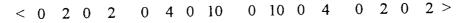

#### 3.4 Simulation and Analysis of Side Bands

This prediction is tested by analysis of several 32-element modulation patterns. In all cases, the carrier C is composed of alternating logic states  $\{0\ 1\ 0\ 1\ 0\ 1\ \dots\ 0\ 1\ 0\ 1\}$ . The Fast Fourier Transform of the binary modulation signal M is shown as Fm, and that of the binary modulated signal S is shown as Fs. As before, the Fast Fourier results will be shown in angled brackets >, and only the integer portion of the magnitude will be shown. The transformations will be performed on binary patterns, as before, though logical patterns will be shown. This work was carried out using the Fast Fourier Transform, vector, and list manipulation functions of the HP48G calculator. The Reverse Polish LISP programs and algorithms are detailed in Appendix A.

For reference, the first system analyzed will be an unmodulated signal.

| $M = \{0\ 0\ 0\ 0\ 0\ 0\ 0\ 0\ 0\ 0\ 0\ 0\ 0\ 0$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Eq. 3.5a |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| $Fm = \langle 32\ 0\ 0\ 0\ 0\ 0\ 0\ 0\ 0\ 0\ 0\ 0\ 0\ 0\$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Eq. 3.5b |

| $S = \{0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\$ | Eq. 3.5c |

| $F_{s} = \langle 0.000.000.000.000.000.32000.000.000.000.$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Eq. 3.5d |

The initial value of 32 in Fm indicates that the average value of  $\mathbf{M}$  is not zero. The reader will recall that each binary value  $\mathbf{M}_j$  is +1 for all j, because of the mapping between logic and binary spaces defined previously. Thus, Equation 3.5b is not the Fast Fourrier Transform of Equation 3.5a. Logical M is converted to binary  $\mathbf{M}$ , and then transformed, and then magnitudes of the transformed values are rounded to the nearest integer for simpler presentation. Fs shows that the peak of 32 occurs at position 17, corresponding to the fundamental frequency of the carrier  $\mathbf{C}$ .

The second system to be considered uses a square wave modulation signal of onesixteenth the carrier frequency:

The first half of Fm shows a peak value in position 2, with decreasing values in evennumbered positions. This corresponds to a low frequency square wave and its decreasing spectral content at even-multiple harmonics. The second half of Fm is a reversal of the first half. This is a spectral wrap-around effect of the Fast Fourier Transform.

The first half of Fs is a reverse image of the first half of Fm, and the second half of Fs is a copy of the first half of Fm. These are the upper and lower side bands expected from modulation theory. As expected, the value at position 17 of Fs is zero. This indicates a suppressed carrier modulated square wave.

The next system to be analyzed uses a square wave modulation signal at onequarter of the carrier frequency:

As in Equation 3.6, Fm shows harmonics of a square wave in the first half of the spectrum, which are repeated as upper and lower side bands in Fs.

It is useful to note the locations of the side bands between Fs in Equation 3.6 and Fs in Equation 3.7. In Equation 3.6, the largest elements are in positions 16 and 18. In Equation 3.7, the magnitudes of these largest elements have changed little, but they have been relocated to positions 13 and 21. A slower modulation signal can compact the side bands more closely together without necessarily changing the side band magnitude.

Another feature to note at this point is the total number of 0 to 1 or 1 to 0 transitions in S, compared to those in M and C. The effective clock rate or effective

frequency of a signal is the number of low-to-high transitions per second. Careful comparison will show that the number of transitions in S plus the number in M will equal the number in C. This arises because each transition in the modulation signal creates a phase inversion at the same time the carrier phase was expected to change. Therefore S has fewer transitions than C, and the difference is directly attributed to M. For application of this technique to the clocks of digital systems, that trade-off between the number of edges in the modulation signal and the resulting effective clock rate (as measured by the number of transitions in S) will become a major design consideration.

The next few systems will have random modulation signals.

$$M = \{1\ 0\ 0\ 1\ 1\ 1\ 0\ 0\ 0\ 0\ 1\ 1\ 1\ 0\ 1\ 0\ 1\ 1\ 1\ 1\ 0\ 0\ 0\ 0\ 0\ 1\ 1\ 1\ 1\ 0\}\}$$

Eq. 3.8a

$F_m = <0\ 1\ 8\ 4\ 11\ 3\ 4\ 6\ 2\ 2\ 6\ 2\ 8\ 4\ 6\ 3\ .\ 4\ 3\ 6\ 4\ 8\ 2\ 6\ 2\ 2\ 6\ 4\ 3\ 11\ 4\ 8\ 1>$  Eq. 3.8b

$S = \{1\ 1\ 0\ 0\ 1\ 0\ 0\ 1\ 0\ 1\ 1\ 0\ 1\ 0\ 0\ 1\ 1\ 1\ 1\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 1\}\}$  Eq. 3.8c

$F_S = <4\ 3\ 6\ 4\ 8\ 2\ 6\ 2\ 2\ 6\ 4\ 3\ 11\ 4\ 8\ 1\ .\ 0\ 1\ 8\ 4\ 11\ 3\ 4\ 6\ 2\ 2\ 6\ 2\ 8\ 4\ 6\ 3>$  Eq. 3.8d

Again, the number pattern in the first half of Fm is repeated as side bands in Fs. The peaks in Fm, and therefore in Fs, were lower with this randomly generated modulation signal. However, the number of transitions in M was large, resulting in a lower effective clock rate in S.

Equations 3.9 and 3.10 will examine the effect of doubling each entry in the previous random modulating signal, M. The first half of M from Equation 3.8 will be used in Equation 3.9, and the second half will be used in Equation 3.10.

$M = \{1\ 1\ 0\ 0\ 0\ 0\ 1\ 1\ 1\ 1\ 1\ 1\ 0\ 0\ 0\ 0\ 0\ 0\ 1\ 1\ 1\ 1\ 1\ 0\ 0\}\}$  Eq. 3.9a  $F_m = <0\ 4\ 11\ 10\ 0\ 9\ 9\ 3\ 0\ 3\ 6\ 5\ 0\ 3\ 2\ 0\ .\ 0\ 0\ 2\ 3\ 0\ 5\ 6\ 3\ 0\ 3\ 9\ 9\ 0\ 10\ 11\ 4>$  Eq. 3.9b  $S = \{1\ 0\ 0\ 1\ 0\ 1\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 1\ 0\ 1\ 0\ 1\}$  Eq. 3.9c  $F_s = <0\ 0\ 2\ 3\ 0\ 5\ 6\ 3\ 0\ 3\ 9\ 9\ 0\ 10\ 11\ 4\ .\ 0\ 4\ 11\ 10\ 0\ 9\ 9\ 3\ 0\ 3\ 6\ 5\ 0\ 3\ 2\ 0>$  Eq. 3.9d  $M = \{1\ 1\ 0\ 0\ 1\ 1\ 1\ 1\ 1\ 1\ 0\ 0\ 0\ 0\ 0\ 0\ 0\ 0\ 0\ 0\ 0\ 1\ 1\ 1\ 1\ 1\ 1\ 1\ 1\ 0\ 0\}\}$  Eq. 3.10a  $Fm = <0\ 12\ 13\ 5\ 5\ 2\ 4\ 7\ 6\ 6\ 3\ 1\ 2\ 2\ 2\ 1\ .\ 0\ 1\ 2\ 2\ 2\ 1\ 3\ 6\ 6\ 7\ 4\ 2\ 5\ 5\ 13\ 12>$  Eq. 3.10b  $S = \{1\ 0\ 0\ 1\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\}$  Eq. 3.10c  $Fs = <0\ 1\ 2\ 2\ 2\ 1\ 3\ 6\ 6\ 7\ 4\ 2\ 5\ 5\ 13\ 12\ .\ 0\ 12\ 13\ 5\ 5\ 2\ 4\ 7\ 6\ 6\ 3\ 1\ 2\ 2\ 2\ 1>$  Eq. 3.10d

The peak in Equation 3.8 was a value of 11. The peaks in Equations 3.9 and 3.10 were 11 and 13 respectively. The effective clock rate improved from a value of 9 cycles in Equation 3.8 to values of 12 cycles and 13 cycles in the later equations. In some cases, the effective clock rate can be increased without a significant impact on peak noise levels.

By comparison, the peak values found using square wave modulation in Equations 3.6 and 3.7 were relatively constant, with values of 20 and 21. The effective clock rates were quite different, with rates of 15 cycles in Equation 3.6 and 12 cycles in Equation 3.7. Again, effective clock rate and peak emission levels can be somewhat independent. However, the randomly modulated signals seem to have much lower peak spectral values that the square-wave modulated signals.

# 3.5 Prediction of Side Band Peak Frequencies and Intensities

The foregoing analysis suggests that the side band characteristics predicted by AM modulation theory will apply directly in the analysis of the spectra that result when two digital waves are modulated through an exclusive-OR operation. The basic analysis for side band peak locations arises by replacing m(t) in Equation 3.3 with a sine wave:

$$f(t) = A \sin(2\pi f_c t) \sin(2\pi f_m t)$$

$$f(t) = 0.5 A \{ \sin[2\pi (f_c + f_m) t] + \sin[2\pi (f_c - f_m) t] \}$$

Eq. 3.11

Two peaks of equal amplitude result, located at frequencies that are the sum and difference of the initial frequencies. A few clarifications are necessary when predicting the digital suppressed carrier modulation results, to account for the fact that the modulation occurs in logic space.

If the modulating signal is not a sine wave, it will be composed of a spectrum of frequencies. When the sine wave of Equation 3.11 is replaced with a series expansion of m(t), the spectrally-rich nature of side bands becomes apparent:

$$m(t) = \Sigma_j B_j \sin(2\pi f_j t + \phi_j)$$

Eq. 3.13

$$f(t) = A \sin(2\pi f_c t) \sum_i B_i \sin(2\pi f_i t + \phi_i)$$

Eq. 3.14

$$f(t) = 0.5 A \Sigma_{j} B_{j} \{ sin[2\pi (f_{c} + f_{j})t + \phi_{j}] + sin[2\pi (f_{c} - f_{j})t - \phi_{j}] \} Eq. 3.15$$

where  $\Sigma_j$  denotes summation over j,  $B_j$  and  $\phi_j$  are constants, and the  $f_j$  are the constituent frequencies which make up m(t).

In the present case, the carrier wave is not a sine wave, either. It is a square wave, c(t), which is composed of a harmonic spectrum of signals. The modulation process and harmonic products are defined by the following equations.

$$f(t) = c(t) m(t)$$

Eq. 3.16

$$c(t) = \sum_{k} A_{k} \sin(2\pi k f_{c} t)$$

Eq. 3.17

$$f(t) = \sum_{k} A_{k} \sin(2\pi k f_{c} t) \sum_{j} B_{j} \sin(2\pi f_{j} t + \phi_{j})$$

Eq. 3.18

$$f(t) = 0.5 \sum_{k} \sum_{j} A_{k} B_{j} \{$$

sin  $[2\pi (k f_{c} + f_{j}) t + \phi_{j}] + \sin [2\pi (k f_{c} - f_{j}) t - \phi_{j}] \}$  Eq. 3.19

This is a long way of saying that the shape of the side bands will match the shape of the modulating signal in relative frequency and relative amplitude. However, the shape of the side band becomes more complicated as the side bands of adjacent harmonics begin to overlap.

When predicting the actual spectral content at a given frequency, one must account for the possibility that two modulation products may contribute to a single peak, and that contribution may be constructive or destructive based upon phase angle. For example, a first signal with spectral content at 20 kHz and 40 kHz is modulated with a second signal having spectral content at 5 kHz and 15 kHz. The spectral content at 25 kHz would include the modulation contribution from (20 kHz + 5 kHz) and the contribution from (40

kHz - 15 kHz). Similarly, the spectral content at 35 kHz would include content from the (20 kHz + 15 kHz) and (40 kHz - 5 kHz) modulation products.

#### 3.6 Demodulation

When demodulation is discussed in the realm of communication theory, it is presented with the goal of recovering the modulation signal. Synchronous demodulation of an analog suppressed carrier signal is accomplished through a process of: (1) replicating or retrieving the original carrier signal; (2) modulating the suppressed carrier signal, f(t), with the replicated carrier, to produce g(t); and (3) passing g(t) through a low-pass filter to recover m(t), the modulation signal. Mathematically,

$$g(t) = D \sin(2\pi f_c t) f(t)$$

Eq. 3.20

Recalling Equation 3.3 which generated the modulated signal,

$$f(t) = A \sin(2\pi f_c t) m(t)$$

(Eq. 3.3)

it is clear from Equation 3.20 that

$$g(t) = A D \sin(2\pi f_c t) \sin(2\pi f_c t) m(t)$$

Eq. 3.21

$$g(t) = 0.5 \text{ A D } [m(t) - \cos(4\pi f_c t) m(t)]$$

Eq. 3.22

from which m(t) can be retrieved using a low-pass filter. These equations assume there is no phase error introduced, or that the replicated carrier is phase locked to the original carrier. If there is time or phase delay introduced in the transmission of the suppressed carrier signal from modulator to demodulator, the same delays must be present in the replicated carrier.

In the present context where the carrier or clock is the significant signal and the modulation is of little functional value, there is great value in demodulating the suppressed carrier signal to retrieve the clock. This could be accomplished using a second exclusive OR gate and an exact copy of the logical modulation pattern M. Recalling Equation 3.4,

$$S_j = C_j \oplus M_j$$

for  $j = 1$  to n (Eq. 3.4)

this demodulation would create a pattern T, such that

$$T_{j} = S_{j} \oplus M_{j}$$

=  $C_{j} \oplus M_{j} \oplus M_{j}$

=  $C_{j}$  for  $j = 1$  to n Eq. 3.23

In this manner, demodulation recovers the original clock signal. As with analog synchronous demodulation of suppressed carrier signals, the time delays introduced in transmission from the modulator to the demodulator must be present in the modulated signal and the modulating signal equally.

#### 3.7 Application and Summary

The objective of a spread spectrum technology is to reduce the electromagnetic interference attributable to high speed electronic systems while creating minimal degradation to the performance of the systems. This chapter proposes and predicts that the peak spectral density in a clock signal can be reduced through use of suppressed carrier amplitude modulation. Significant points from this analysis include:

- A. This modulation may be achieved in a logic system using the XOR logic gate function.

- B. The original clock may be recovered by routing the modulating signal and the modulated signal to an XOR gate demodulator.

- C. The side bands of the modulated wave will take the spectral shape of the modulation signal.

- D. The effective clock rate after modulation will decrease as the edge rate of the modulating signal increases.

- E. Decreasing the modulation wave frequency has the effect of compacting the side bands of the modulated signal. This compaction can improve the effective clock rate of the modulated signal with only a small impact upon peak spectral density.

- F. Modulation with complex or random waves will produce lower peaks in the modulated signal spectrum.

There are practical limits to how compact the modulation spectrum can be. Power spectral density is measured with a device having a finite input bandwidth. Most devices that are susceptible to electromagnetic interference are susceptible over a small bandwidth. Any adjacent peaks in the modulation signal will be added together if they are separated by less than the critical input bandwidth of the measuring equipment or the susceptible device. International standards require the electromagnetic radiation from digital devices at frequencies below 1 GHz to be measured with a 120 kHz input bandwidth (IEC, 1993).

Assuming that adjacent peaks do not fall within the critical bandwidth, discrete spectral analysis predicts that a narrow band modulation signal applied to a square wave voltage clock could reduce the emissions from a relative linear level of 32 to a level of 20. A broad band modulation signal could decrease the emissions further – to a level of 11, for example.

#### 4. Circuit Implementation

### 4.1 A Simple Modulator - Demodulator Pair

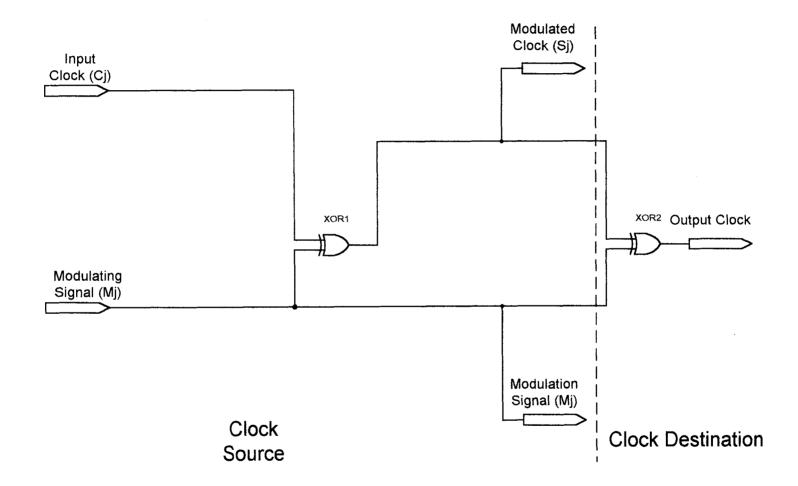

Figure 4.1 shows a simple modulator and synchronous demodulator, as suggested by the discussion of the previous chapter:

$$S_j = C_j \oplus M_j$$

for  $j = 1$  to n (Eq. 3.4)

The modulator would be located at a source circuit or system, and the demodulator would be located at the destination circuit. The traces or cables that connect the two circuits would not carry any narrow band signals. This feature tends to reduce the peak spectral emissions from the circuit or cable that would otherwise carry a narrow band clock.

In practice, this circuit would not perform well in a high speed digital system. The first problem lies in the nature of the exclusive-OR gate. If the Input Clock changes its logical state when the Modulating Signal changes state, the Modulated Clock may glitch. The glitch is a normal result when both inputs change at the same time, or at nearly the same time. In transition between input values of 11 and 00, the output should remain 0. In practice, the logic may attempt to output a transient value of 1, which is the proper result of a 01 or 10 input pattern. Thus the output of the XOR gate would start at  $1\oplus 1=0$ , begin a transition to an intermediate state such as  $1\oplus 0=1$ , and then revert to the desired  $0\oplus 0=0$  condition. A similar glitch could occur in the Output Clock signal if the Input Clock is stable when the Modulating Signal changes state. The Modulated Clock would change logical states, but its change would involve a time delay relative to the Modulation Signal. The Output Clock would change state in response to the Modulation Signal, and then change back due to the delayed transition of the Modulated Clock.

Figure 4.1: A simple modulator-demodulator pair.

To avoid such glitches, the circuitry surrounding an XOR gate should be arranged such that either (1) only one input switches at a time, or (2) glitches in the output are functionally acceptable.

A second problem with the simple circuit of Figure 4.1 is that the Input Clock and Modulating Signal are not necessarily synchronous. Their timing transitions could be separated by arbitrarily short intervals, leading to a condition where the Modulated Clock could have pulses of very short duration. These pulses would probably violate the minimum low or high periods of logic gates attached to the Modulated Clock line, including XOR2.

## 4.2 A Better Modulator - Demodulator Pair

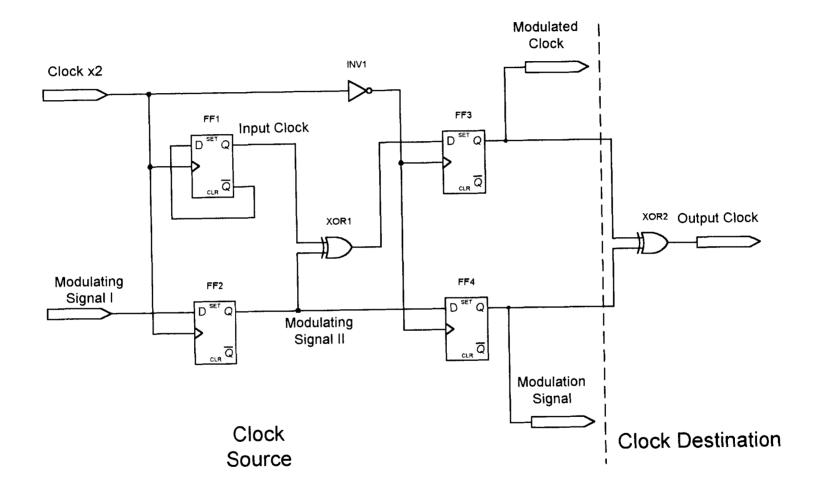

These issues are addressed by the circuit design of Figure 4.2. Within the system architecture, the final XOR gate would be located at the destination circuit, and the remainder of the circuit elements would be located at the source circuit.

This design requires a reference clock (Clock x2) operating at twice the desired output clock frequency. Flip-flop 1 is arranged as a divide-by-two counter, to create the Input Clock for the modulator. This Input Clock changes state on the rising edge of Clock x2. Modulating Signal I is latched by a flip-flop to create Modulating Signal II, which also changes state on the rising edge of Clock x2. The XOR1 gate receives these two signals as input, and so the output of XOR1 will have glitches only at the rising edge of Clock x2.

A second stage of latches is clocked on the falling edge of Clock x2. At the falling edge of Clock x2, Modulating Signal II and the output of the first XOR gate are both stable. The Modulated Clock and Modulation Signal will both transition in sync with the falling edge of Clock x2.

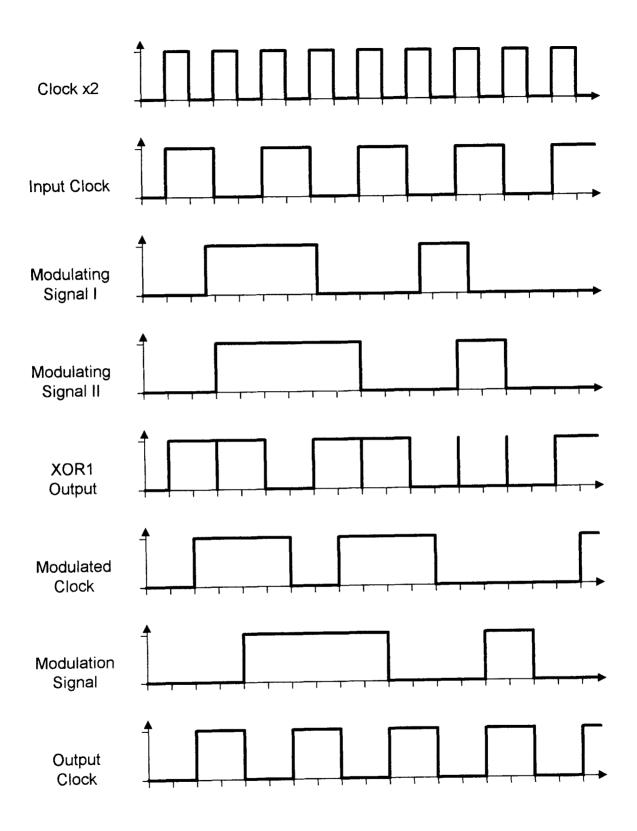

Figure 4.3 is a timing diagram of the circuit in Figure 4.2. As this figure shows, either the Modulated Clock or the Modulation Signal will change on every falling edge

Figure 4.2: A buffered modulator-demodulator pair.

Figure 4.3: Timing Diagram.

of Clock x2, but never will both change at the same time. The Output Clock will not suffer from glitches. Note that the Output Clock is synchronous with the falling edge of Clock x2, not the Input Clock. This is an important design consideration.

## 4.3 Backward Compatibility

The modulator and the demodulator would typically be included in separate integrated circuits or system modules. The question arises how this method might be used on a standardized or generic device when other parts of the system may not be fully designed for suppressed carrier modulation.

If the modulator circuit or module were to drive a destination circuit incapable of utilizing a modulated clock, the Modulating Signal I input would simply be grounded.

The output of the modulator will be a stable, unmodulated clock.

Suppose the destination system is built to accommodate a modulated clock, but a source module is chosen that does not include the modulator. Simply ground the Modulation Signal input at the destination circuit. In this way, the unmodulated clock will be received and utilized appropriately.

With these options in mind, the modulator and demodulator could be implemented in existing systems for use when connected to an appropriate mating circuit. Systems with these circuits added are backward compatible with narrow band systems.

#### 4.4 A Stand-Alone Modulator

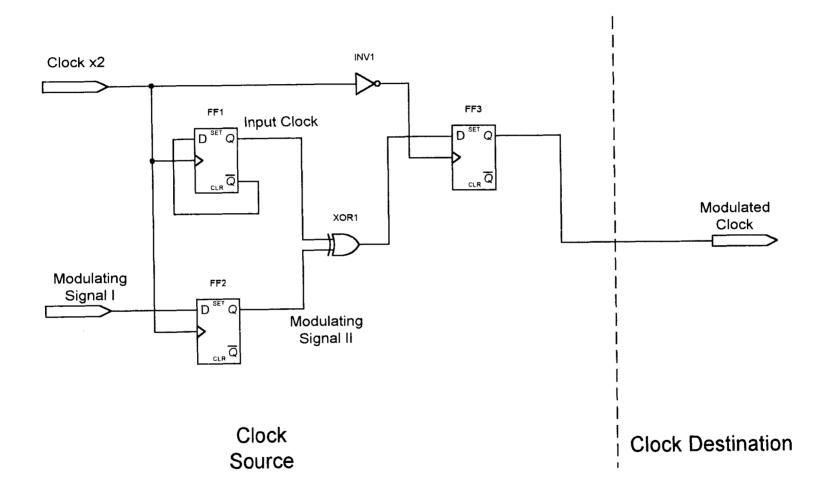

The circuit design of Figure 4.2 is sufficient to transmit a narrow band clock from one circuit or system to another without routing any narrow band signals across circuit boards or through cables. However, there are many direct-drive circuits that will operate effectively from a broad band clock having the characteristics described in Chapter 1. Specifically, the clock must meet the minimal high, low, setup, and hold requirements specified for logic gates. A state machine is an example of a direct drive circuit that can

operate on a clock that occasionally provides a longer clock phase than typical. A modulated clock can be used to drive such circuits without providing a demodulator.

The circuit of Figure 4.4 is appropriate for such a direct-drive circuit. The only changes are removal of the demodulating XOR gate, and the flip-flop used to create the Modulation Signal.

### **4.5 Modulation Sources**

The design of broad-spectrum noise sources is related to, but distinct from, the present subject matter. The theory of suppressed carrier clock modulation predicts that the measured emission levels from a device using suppressed carrier clocks will depend heavily upon the modulating spectrum. The implication is that a spectrally broad modulation source may be desirable.

Every real suppressed carrier clock modulator must have such a noise source, including those that are to be used in the next chapter of this work, and so the topic will be discussed briefly at this point.

The simplest modulation waveform is a square wave with a frequency set below the input clock frequency, perhaps using a divide-by-n counter from the input clock. Such waveforms were used in the previous chapter (refer to Equation 3.7). A more complex waveform would be a random signal approximating white noise.

Another useful waveform is the pseudo-random pattern. It has good spectral smoothness, yet the hardware implementation of the pattern generator is simple and straightforward. The details of this pattern generator will not be covered in this present text. In future chapters, references to the pseudo-random signal will mention an order number (defining the size of the state machine used to generate the signal) and the effective clock rate (which is the average number of low-to-high transitions per second).

Figure 4.4: A stand-alone buffered modulator.

### **4.6 Construction**

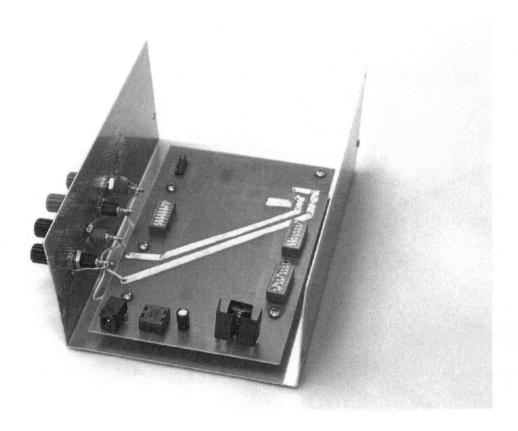

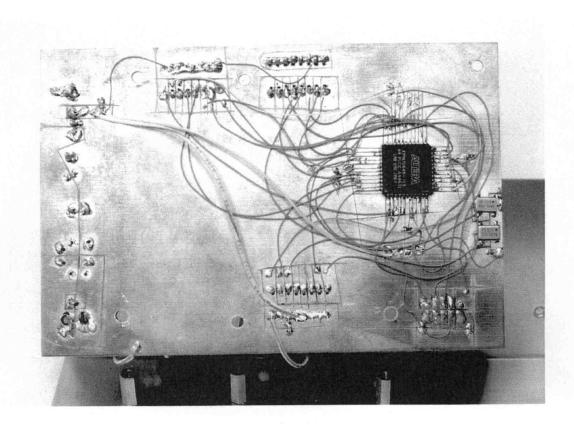

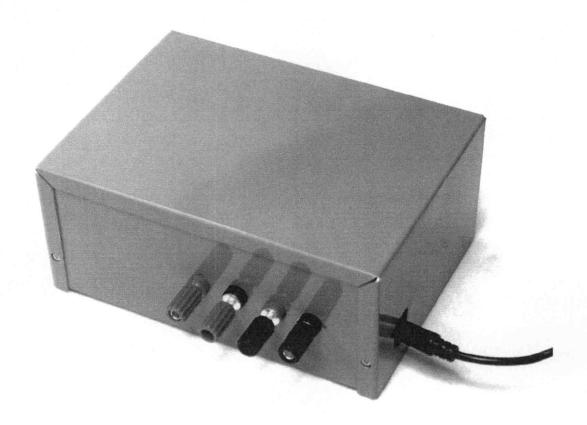

The suppressed carrier clock generator was assembled using a piece of 1.5 mm thick fiberglass circuit board plated on one side with copper, as shown in Figures 4.5 and 4.6. Traces and land patterns in the copper were created by carving out unwanted metal with a hobby knife, due to budget and schedule. Most interconnections are made with narrow gauge wire. The circuit includes a 5V power supply, a number of single-pole single-throw switches in Dual Inline Package (DIP) arrays, a connector for the serial programming interface, and a programmable gate array containing all the logic circuits. The circuit board was mounted inside a sheet metal box on half-inch standoffs. Four terminals are provided on the side of the box for accessing 5V power and ground rails, plus the two output signals (Modulated Clock and Modulation Signal). A hole in the end of the box permits insertion of the 12 V power input, as shown in Figure 4.7.

The gate array used is an Altera EPM7064S-7ES, which contains 64 macrocells, and has a maximum operational speed well above 140 MHz. A gate array macrocell can be thought of as a flip-flop with support gates. The output of each macrocell can be connected to the input nodes of other macrocells. This gate array can be reprogrammed in place using a serial interface from a computer. The array is in a 44-pin J-lead package.

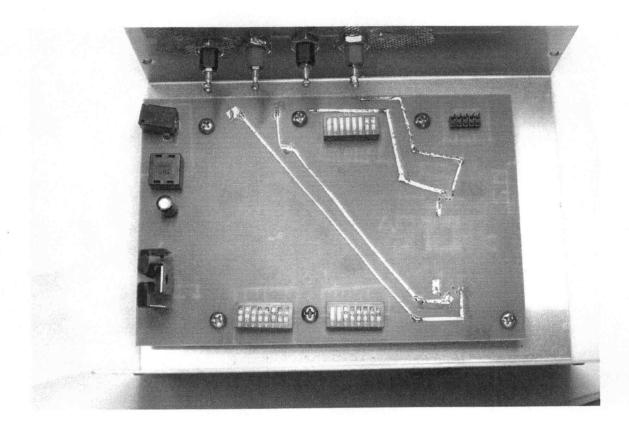

The design has only five high-speed signals external to the gate array: 66.66 MHz and 40.00 MHz primary clocks, a Modulated Clock output, a Modulation Signal output, and a demodulated clock output. The primary clocks originate from crystal oscillators soldered on the circuit board, and attached to the gate array using narrow gauge wire. The outputs are routed on the non-plated side of the board using copper tape with an adhesive backing.

Figure 4.5: Top side of circuit board.

Figure 4.6: Bottom side of circuit board.

Figure 4.7: External view of test assembly.

The characteristic impedance of a microstrip structure can be approximated using Equations 4.1 and 4.2 (Pozar, 1990). The fiberglass thickness, d, is 1.5 mm. Its relative permittivity,  $\varepsilon_r$ , is 4.

$$\varepsilon_{e} = (\varepsilon_{r} + 1)/2 + [(\varepsilon_{r} - 1)/2\sqrt{(1 + 12d/W)}]$$

Eq. 4.1

$$Z_0 = 120\pi / \sqrt{(\epsilon_e)} [W/d + 1.393 + 0.667 ln(W/d + 1.444)]$$

Eq. 4.2

In the original arrangement this tape width, W, was approximately 4 mm, and contained no filter or termination elements. This would make the trace characteristic impedance about  $45\Omega$ . At a later stage of the measurement process, the trace width was narrowed to about 0.75 mm, as shown in Figure 4.8. This change produced a characteristic impedance near  $100\Omega$ .

There are, in fact, two demodulators in the system. The first demodulator receives the Modulated Clock and Modulation Signal before they exit the gate array. Its output is provided as a means of verifying that the system is running correctly. This demodulator was present throughout testing, and was referred to as Demod. At a later stage of the experimental work, when the trace impedances were increased to  $100\Omega$ , additional circuitry was provided to return the signals to gate array inputs and then demodulate the signals, resulting in the Xclk signal.

The Modulated Clock and Modulation Signals ran from the gate array outputs through  $100\Omega$  microstrip transmission lines to the terminal posts. The power and ground connections previously provided at these posts were removed. The signals were connected to a five-inch length of  $300\Omega$  television antenna twin-lead. After the twin-lead, the signals were routed back across the circuit board to the gate array, at the inputs of the second demodulator. The output of this second demodulator is called Xclk, because it demodulates signals that have been routed external to the gate array and circuit board. Measurements on Xclk permitted evaluation of the effects of signal filtering.

Figure 4.8: Circuit board with redesigned transmission lines.

Signal flow within the gate array is controlled using a number of digital inputs, set using the DIP switches. These are DC signals, and are routed with narrow gauge wire.

The function of each switch is discussed in further detail in Appendix C.

The serial programming interface is also attached in one corner of the board.

During normal circuit operation, these programming signals are idle.

The power supply is designed for quick assembly and quiet operation, rather than efficiency. The AC to DC converter is an HP F1044B AC adapter which converts power from the building mains to regulated 12V DC. This DC current enters the circuit board through a mating connector, and passes through a common mode choke to a 47  $\mu$ F filter capacitor. The 12V power is converted to 5V using a 7805 voltage regulator chip set in an appropriate heat sink. This 5V power is supplied to the various elements of the system, with 0.1  $\mu$ F decoupling capacitors added at the power input terminals of most devices on the board, and to the power terminal on the side of the box.

### 5. Measurement Configurations

Before providing the experimental data, it may be useful to describe the equipment used for various measurements.

### 5.1 Bench Top Spectral Measurements

The spectral content of a signal is linearly related to the far-field radio measurement used in most EMC testing, but predicting the scaling factor is a difficult task. That factor includes the effects of the spatial relationship between the measurement antenna and the electronics device creating the radio emissions. The measured strength of a radio emission will also depend upon the radiation efficiency of the mechanical structures that make up the source device. Measurement of the relative amplitudes in a signal spectrum on a laboratory bench is a convenient technique for evaluating variations in signal content, which will have a direct effect on far-field radio emissions.

During spectral measurements made on the laboratory bench, the clock generator is assembled as described in Chapter 4, except that the cover of the metal box is removed to permit frequency measurements. Spectral measurements are made at the terminal lugs outside the box, unless stated otherwise.

Measurement equipment includes an HP8594EM Spectrum Analyzer, an HP85024A High Frequency Probe with an HP11881A 10:1 Divider tip in place, and an XY Plotter controlled by the Spectrum Analyzer through an HPIB channel.

Spectrum analyzer measurements are made using a 120 kHz IF Bandwidth, as is typically used in regulatory emissions testing. Where possible, this bandwidth is also used when measuring spectra at frequencies below the lower regulatory limit of 30 MHz. The

analyzer readings are presented in  $dB\mu V$  without any additional calibration factors included to account for the response of the high frequency probe.

The frequency response of the probe and tip are assumed to be fairly flat over the measurement range. Most of the comparisons in the data analysis will involve comparing data at a single frequency or nearby frequencies from two different experiments.

Therefore, the relative magnitudes of the various signals can be compared, and probe calibration effects will cancel out in the comparison. These probe calibration effects, if any, are small compared to the larger issues of antenna orientation and the radiating structure efficiency which must be considered in relating bench top tests to radiated field measurements.

The original measurements contain data measured with the peak detector and with the quasi-peak detector of the spectrum analyzer. For stable, narrow band spectral peaks, the two detectors will produce the same value. When measuring signals in which the inband power level varies faster than 10 kHz, the Quasi-Peak detector will register more like an Average detector. Unless stated otherwise, spectral measurements discussed in this thesis are peak detector values and are equivalent to quasi-peak readings within 0.3 dB.

## 5.2 Effective Frequency Measurements

The effective clock rate or effective frequency of a signal is the number of low-to-high transitions per second. This parameter is important in understanding how a modulation technique will affect the operational throughput of a digital system that is directly driven by a modulated clock. This parameter is irrelevant in discussing the operation of systems using demodulated clocks.

The equipment set used to determine the effective clock edge rates of digital signals includes a Universal Counter, and a 10:1 voltage probe. The universal counter, often called a frequency counter, is adjusted to read a stable value of the effective frequency.

# 5.3 Clock Parameter Measurements

Hewlett-Packard makes a Time Interval Analyzer, the HP E1725A. This device makes very fast measurements of timing signals, and will report various characteristics of a clock signal, such a cycle-to-cycle jitter, or minimum and maximum pulse widths. The test device uses standard 1 M $\Omega$  10:1 voltage probes as would be used on an oscilloscope. It has a graphic interface, based upon a windowed operating system, for control of the high-speed instrument. This instrument was used to measure jitter.

### 6. Experimental Results

#### 6.1 Experimental Approach

The objectives of these experiments are: (1) to verify that the spectra generated by the modulator fit the theory presented in Chapter 3, especially the specific points detailed in Section 3.7; (2) to measure the timing parameters of digital clocks generated or distributed by the techniques described herein; and (3) to note, investigate, and characterize anomalous or unexpected results.

#### 6.2 Baseline Clock Spectra

Before attempting to measure or discuss the complex spectra of modulated clocks, it is reasonable to present and discuss a few baseline spectra. The baseline spectra are an unmodulated 20 MHz clock, and unmodulated 33.33 MHz clock, and a signal held at the low logic level. The measurements of the unmodulated clocks will serve as a standard of comparison for determining how much noise reduction can be achieved with modulation. The data from the signal held low will indicate the noise levels measured by the test setup that come from sources other than the signals under study.

These initial measurements are made from 0 Hz to 100 MHz. This range is deemed sufficient to capture the expected effects without losing detail.

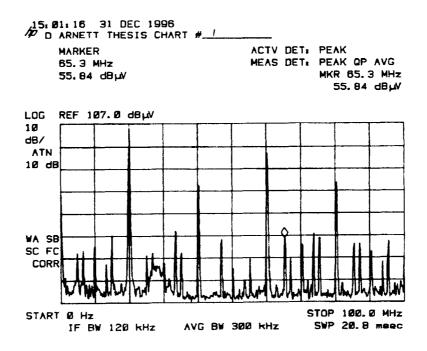

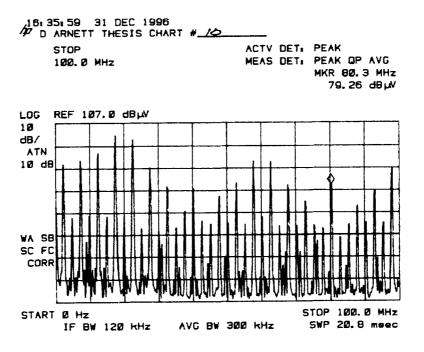

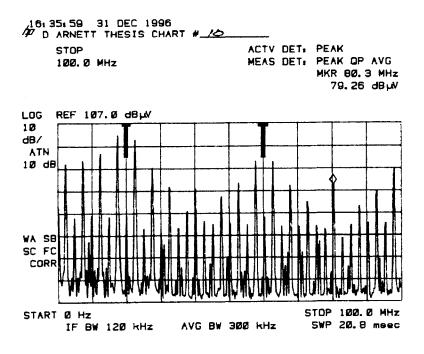

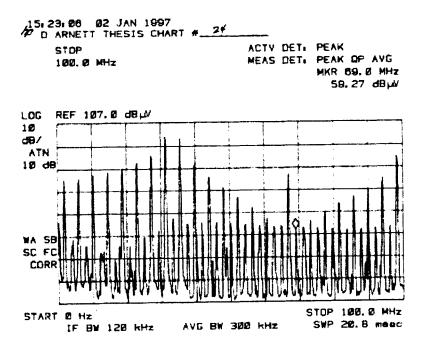

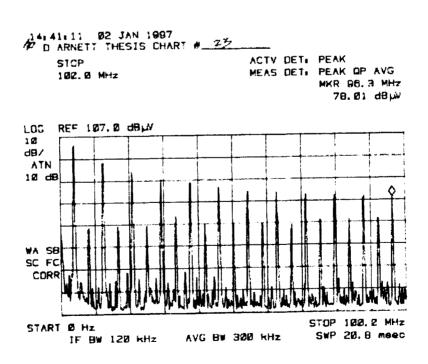

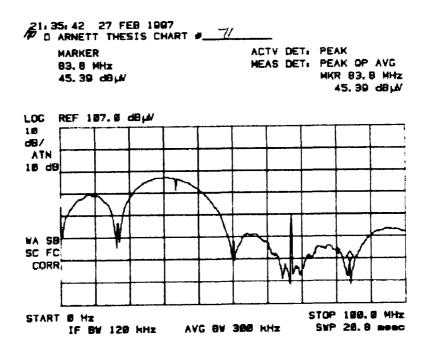

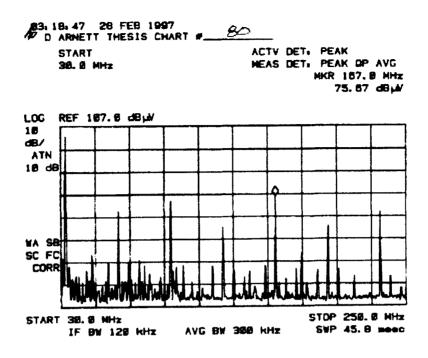

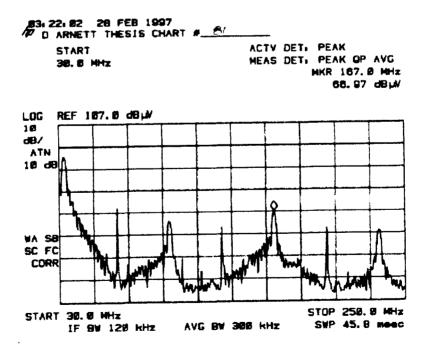

The 20 MHz clock is shown in Figure 6.1. This figure shows the electrical power present in the signal measured, as a function of frequency. The horizontal scale is the frequency axis. In this case, the frequency runs from 0 Hz (DC) to 100 MHz. The vertical scale is signal amplitude, measured on a logarithmic scale. The top line is 107 dB $\mu$ V, and each division is a 10 dB separation. Four harmonics peaks were measured. The readings appear in Table 6.1.

Figure 6.1: 20 MHz Baseline.

Figure 6.2: 33.33 MHz Baseline.

Table 6.1: 20 MHz Baseline Data.

| Frequency<br>MHz | Signal Level<br>dBμV |

|------------------|----------------------|

| 20.0             | 105.1                |

| 40.0             | 79.8                 |

| 60.0             | 94.2                 |

| 80.0             | 81.2                 |

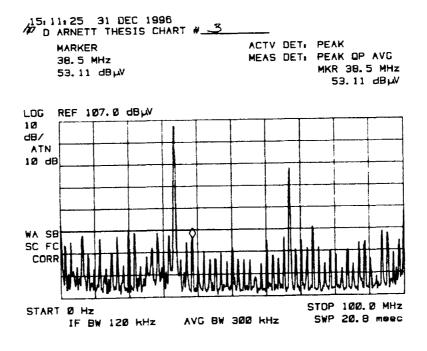

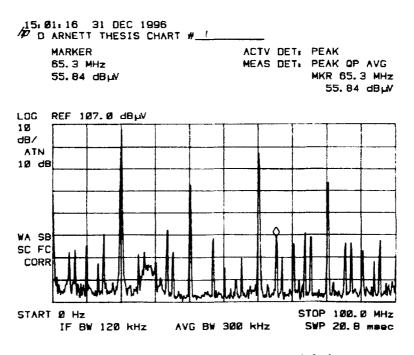

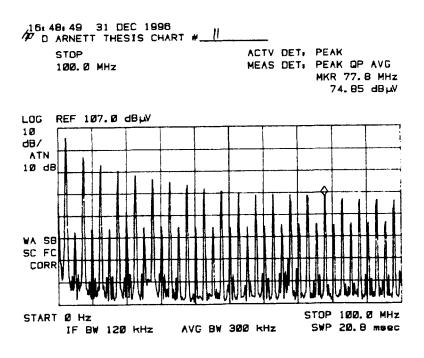

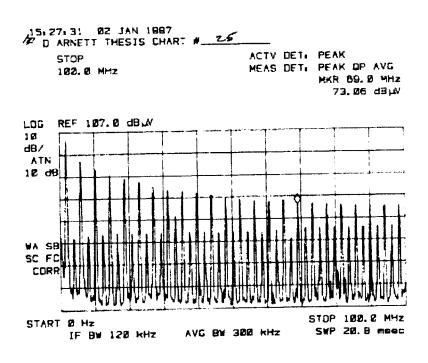

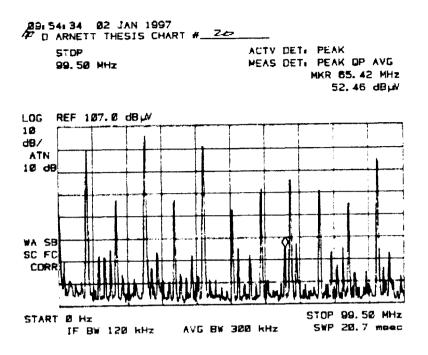

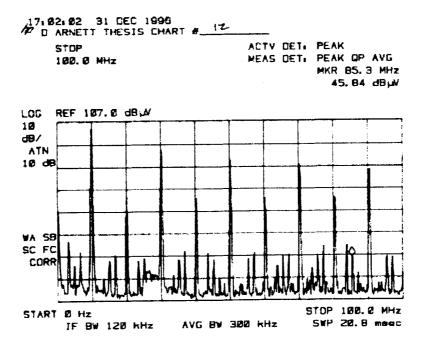

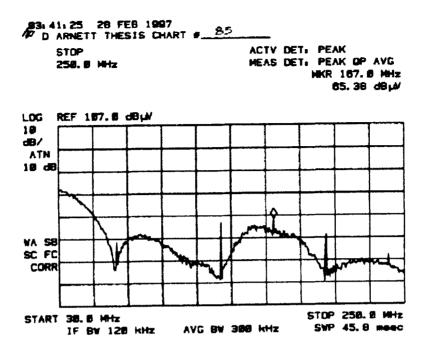

The 33.33 MHz clock is shown in Figure 6.2. Two harmonic peaks were measured, and those readings appear in Table 6.2.

Table 6 2: 33.33 MHz Baseline Data.

| Frequency<br>MHz | Signal Level<br>dBµV |

|------------------|----------------------|

| 33.3             | 104.7                |

| 66.6             | 85.0                 |

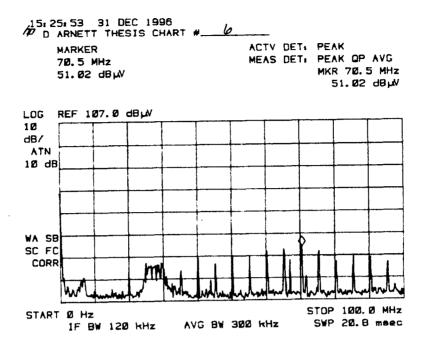

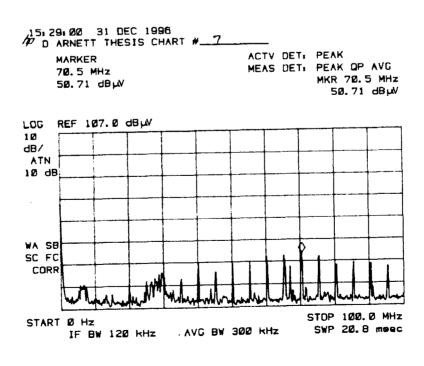

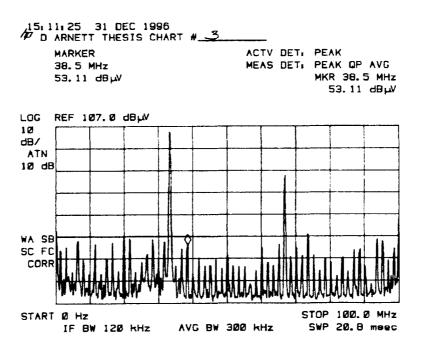

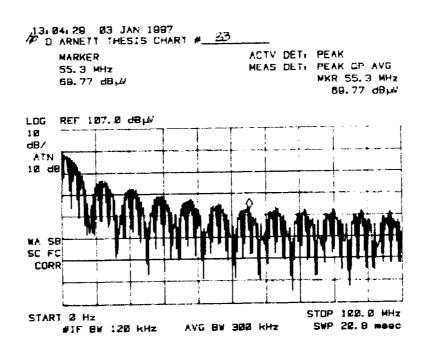

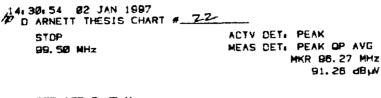

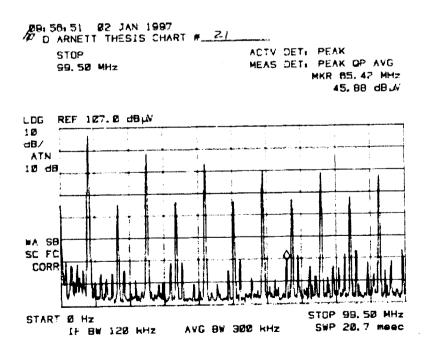

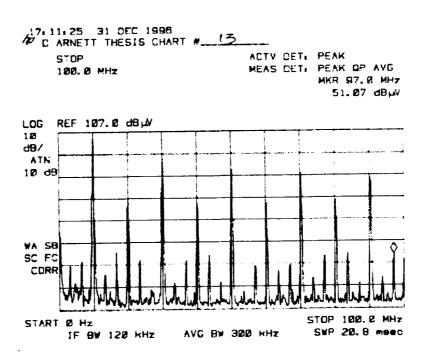

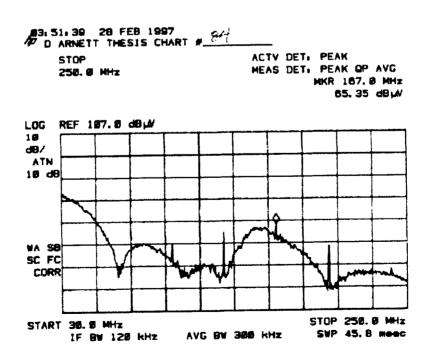

The null experiment data is shown in Figure 6.3. The diamond-shaped marker is placed on the highest data point in the spectrum. The notation in the upper right corner of the data plot indicates that the marker is at 70.5 MHz, and the signal amplitude at that frequency is  $51.02~dB\mu V$  on the Modulated Clock line and  $50.71~dB\mu V$  on the Modulation Signal line. This suggests that data above  $60~dB\mu V$  is related to intentional signals rather than extraneous noise.

The signal readings reported, as with the 20 MHz and 33 MHz baseline data shown above, are made using a measure-at-maximum function of the HP8594EM Spectrum Analyzer. This function will repeatedly narrow the measurement range about a spectral peak, to find the local maximum very precisely. The function then makes Peak, Quasi-Peak, and Average detector measurements. The data measured in this way reflects the signal amplitude with better accuracy than the marker function.

Figure 6.3: Null Experiment. Above, Modulated Clock. Below, Modulation Signal.

# 6.3 Does an Exclusive-OR Modulator Generate a Suppressed Carrier Signal?

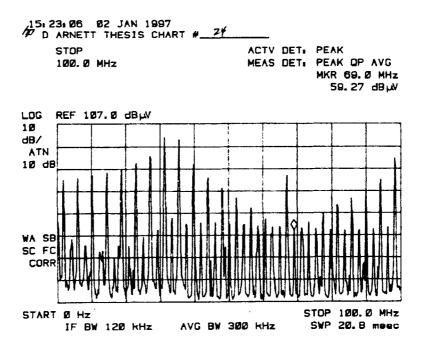

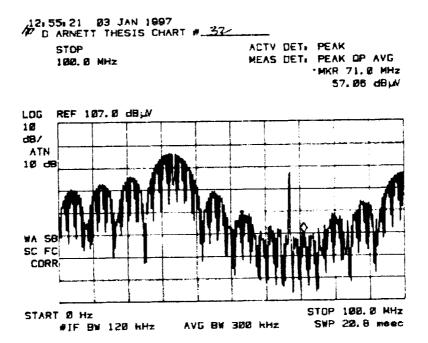

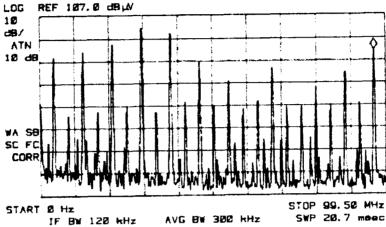

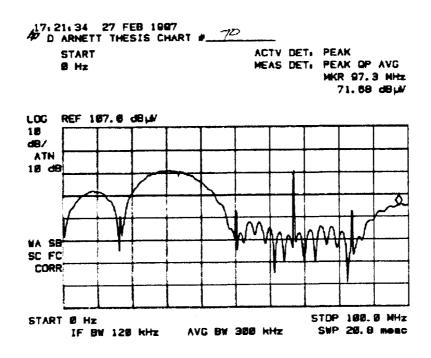

The data in Figure 6.4 shows the spectrum measured when a 20 MHz clock is modulated with a 2.5 MHz square wave. The unmodulated clock spectrum is also shown for comparison. The signal amplitude at 20 MHz is above the 60 dBµV background noise level, and so there is true spectral content measured there. However, 20 MHz has clearly been suppressed, and the energy has moved to other frequencies in the spectrum.

The clock harmonic at 60 MHz also is suppressed. However, the harmonics at 40 MHz and 80 MHz are not suppressed. This is an unexpected result, and will be discussed further in Section 6.9.

Similarly, Figure 6.5 shows the spectrum observed when a 33.33 MHz clock is modulated with a 2.083 MHz square wave. The signal at 33.33 MHz is suppressed; the signal at 66.67 MHz is not suppressed.

The buffered exclusive-OR modulator does create a suppressed-carrier signal. However, this suppression does not appear to benefit even-multiple harmonics.

# 6.4 Can Synchronous Demodulation Recover the Original Clock?

In each of the dozens of modulation profiles tested, the Demod signal was measured using the Universal Counter. Without fail, it reported the correct frequency. The signal timing was also quite good, as will be discussed in Section 6.10. Synchronous demodulation appears to function as expected.

# 6.5 Does the shape of the side band match the modulation spectrum?

To address this, we return to the measurements of the 20 MHz clock that has been modulated by a 2.5 MHz square wave. Figure 6.6 shows the spectrum observed at the

Figure 6.4: 20 MHz Clock with 2.5 MHz Square Wave Modulation. Above, Modulated Clock. Below, Narrow Band Clock.

Figure 6.5: 33.33 MHz Clock with 2.083 MHz Square Wave Modulation. Above, Modulated Clock. Below, Narrow Band Clock.

Figure 6.6: 20 MHz Clock with 2.5 MHz Square Wave Modulation and Marks. Above, Modulated Clock. Below, Modulation Signal.