#### AN ABSTRACT OF THE THESIS OF

DAVID MING-SHIH TAO for the DOCTOR OF PHILOSOPHY (Name) (Degree)

Electrical and in Electronics Engineering presented on Nov. 8, 1972 (Major) (Date)

Title: A COMPLEMENTARY MOS RANDOM-ACCESS-MEMORY CELL

WITH DOUBLE-DIFFUSED MOS TRANSISTORS

Redacted for privacy

Abstract approved:

James C. Looney

The use of double-diffused n-type MOS transistor

(DN-MOS) in a complementary MOS random-access-memory (CMOS RAM) cell is the main objective of this investigation.

DN-MOS transistors and conventional p-channel MOS transistors on the same chip have been successfully fabricated. Process sequence effects on device threshold voltage and channel length are discussed. The CMOS RAM cell operating characteristics were studied as related to the characteristics of devices in the cell. Both hybrid and monolithic CMOS RAM cells with DN-MOS transistors were realized. The theoretical predictions of cell switching characteristics are experimentally justified.

The advantage of using DN-MOS transistors in a CMOS RAM cell is found to be that a faster switching cell can be built using the same area of silicon as compared to a regular complementary structure.

# A COMPLEMENTARY MOS RANDOM-ACCESS-MEMORY CELL WITH DOUBLE-DIFFUSED MOS TRANSISTORS

by

David Ming-Shih Tao

A THESIS

submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

June 1973

# Redacted for privacy

Associate Professor of Electrical and Electronics Engineering in charge of major

# Redacted for privacy

Head of Department of Electrical and Electronics Engineering

Redacted for privacy

Dean of Graduate School

Date thesis is presented Nov 8 1972

Typed by Erma McClanathan for David Ming-Shih Tao

#### ACKNOWLEDGMENT

The author wishes to express his deep appreciation to Professor James C. Looney for his continued guidance and helpful assistance throughout the course of this study.

The Department of Electrical and Electronics Engineering has provided financial aid in the form of graduate assistantship which made this investigation possible.

Finally the author wishes to dedicate this thesis to his wife, Susan, for her patience and encouragement. Special thanks should go to Mrs. McClanathan for carefully preparing this final copy.

### TABLE OF CONTENTS

| I.   | I. Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                |  |  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|--|--|

| II.  | Double-Diffused and Conventional MOS Transistors                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3                                                              |  |  |

|      | A. Device Structure B. Device Operation C. Processes and Considerations 1. Process Steps 2. Experimental Results 3. Threshold Voltage Considerations a. Net Channel Doping Effect on Threshold Voltage b. Impurity Profile Calculations c. Impurity Profile Control on DN-MOS Transistor Threshold Voltage d. Silicon Orientation Effect on Threshold Voltage 4. DN-MOS Transistor Channel Length Considerations Punch Through 5. Diffusion Schedule Considerations 6. Other Considerations | 36<br>61<br>12<br>13<br>15<br>22<br>27<br>30<br>38<br>46<br>48 |  |  |

| III. | The Complementary MOS Random-Access-Memory Cell  A. The CMOS RAM Cell Circuit  B. Cell D.C. Operation  C. Cell Dynamic Operation  1. Cell Step Response  2. Cell Pulsed Response  D. Cell Power Dissipation                                                                                                                                                                                                                                                                                 | 50<br>52<br>54<br>64<br>65<br>69<br>72                         |  |  |

| IV.  | DN-MOS in CMOS RAM Cell  A. Monolithic Structural Cross-Section  B. Advantages of DN-MOS Transistor in  CMOS RAM Cell  C. Hybrid Realization  D. Monolithic Realization                                                                                                                                                                                                                                                                                                                     | 74<br>74<br>76<br>77<br>84                                     |  |  |

| V.   | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 87                                                             |  |  |

|      | Bibliography                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 89                                                             |  |  |

|      | Appendix I. Description of Process Steps  a. Field Oxidation b. P-MOS Source and Drain Diffusion                                                                                                                                                                                                                                                                                                                                                                                            | 91<br>92<br>94                                                 |  |  |

| Fo            | J-MOS Opening, p-Di                                      | sion                                                    | 95  |

|---------------|----------------------------------------------------------|---------------------------------------------------------|-----|

|               | te Opening Followed<br>Ridation                          | d by Gate                                               | 96  |

| M∈            | pen Contacts to Sour<br>etalization and Exce<br>emoval   | rce and Drain,<br>ess Aluminum                          | 97  |

| Appendix II.  | Numerical Data of I<br>for P-MOS Transisto<br>Transistor | I <sub>ds</sub> versus V <sub>qs</sub><br>or and DN-MOS | 98  |

| Table A.      | Ids versus Vgs for                                       | P-MOS Transistor                                        | 99  |

| Table B.      | I <sub>ds</sub> versus V <sub>gs</sub> for Transistor    |                                                         | 99  |

| Appendix III. | DN-MOS Transistor<br>Profile Numerical                   | Impurity<br>Values                                      | 100 |

| Table C.      | Numerical Values for DN-MOS P-Region Imp                 |                                                         | 101 |

| Table D.      | Numerical Values for DN-MOS n+-Region II                 |                                                         | 102 |

| Table E.      | DN-MOS Transistor   Profile Numerical                    |                                                         | 103 |

|               |                                                          |                                                         |     |

|               |                                                          |                                                         |     |

|               |                                                          |                                                         |     |

# LIST OF FIGURES

| Figur | e                                                                                           | Page       |

|-------|---------------------------------------------------------------------------------------------|------------|

| 1.    | Cross-Section of DN-MOS                                                                     | 4          |

| 2.    | Impurity Profile of DN-MOS Structure                                                        | 4          |

| 3.    | Cross-Section of Conventional P-MOS                                                         | 5          |

| 4.    | Enhancement MOS Transistors in Operation                                                    | s <b>8</b> |

| 5.    | $V_{th}$ of Both P-Channel and N-Channel MOS Transistors versus $N_A - N_D$ and $N_{ss}$    | 11         |

| 6.    | Major Steps of Device Fabrication Process                                                   | 13         |

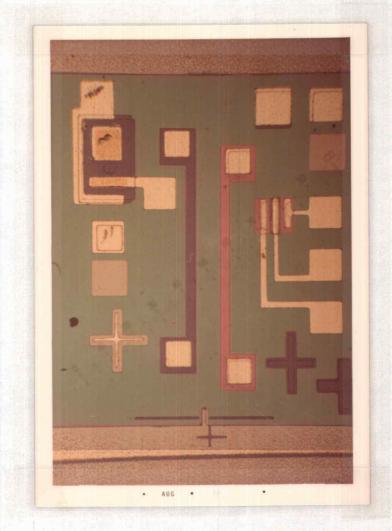

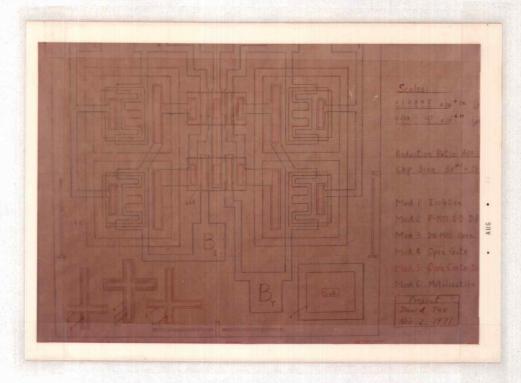

| 7.    | Device Composite Layout                                                                     | 15         |

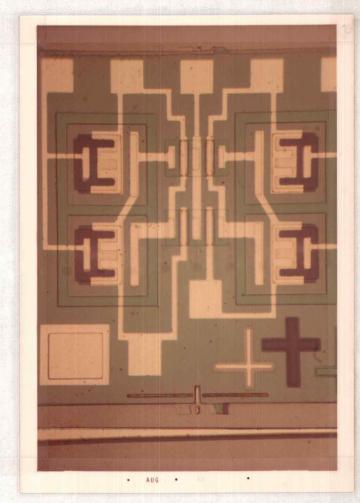

| 8.    | Photomicrograph of Devices                                                                  | 16         |

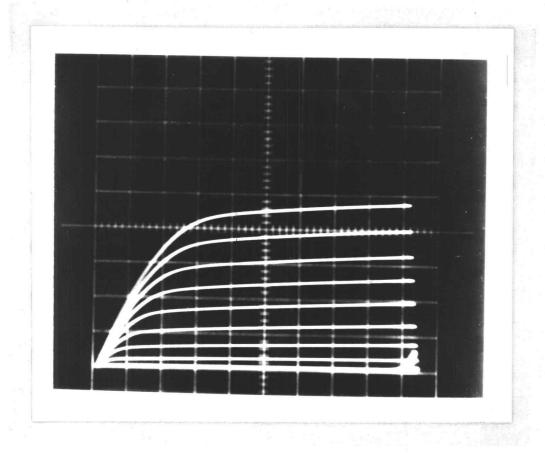

| 9.    | P-MOS Transistor Characteristics                                                            | 17         |

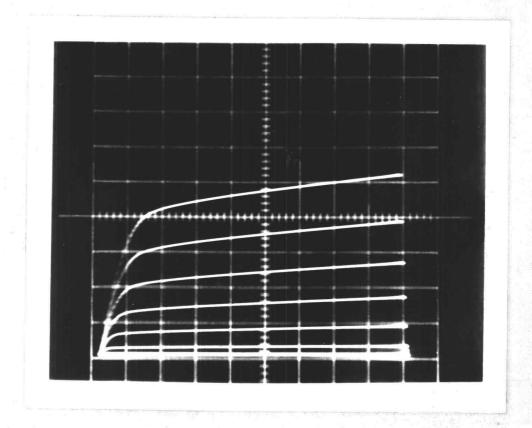

| 10.   | DN-MOS Transistor Characteristics                                                           | 19         |

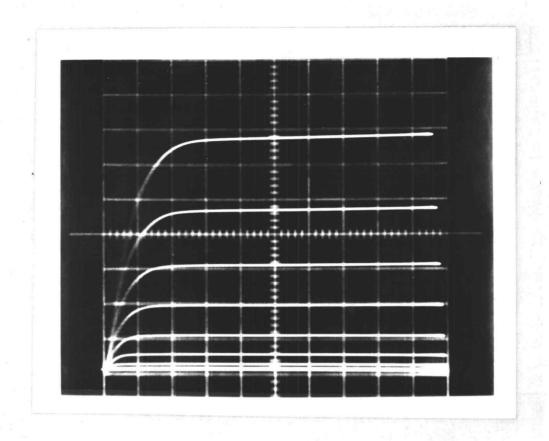

| 11.   | P-MOS Transistor Ids versus -Vgs                                                            | 23         |

| 12.   | DN-MOS Transistor V <sub>qs</sub> versus V <sub>qs</sub>                                    | 24         |

| 13.   | DN-MOS Threshold Voltage ( $V_{tn}$ ) versus Net Channel Doping $N_A - N_D$ Near Source End | 26         |

| 14.   | DN-MOS Transistor Impurity Profiles                                                         | 31         |

| 15.   | DN-MOS Net Impurity Profile                                                                 | 32         |

| 16.   | R <sub>S</sub> Effect on DN-MOS P-Region Impurity Profile                                   | 34         |

| 17.   | Drive-In Time Effect on DN-MOS P-Region Impurity Profile                                    | 36         |

| 18.   | Enlarged Cross-Section of DN-MOS Transistor with Defining Quantities                        | 40         |

| 19.   | Depletion Region Width Variation Effect on<br>Channel Length of DN-MOS Transistor           | 45         |

| 20.   | The Random-Access-Memory System Block Diagram                                               | 51         |

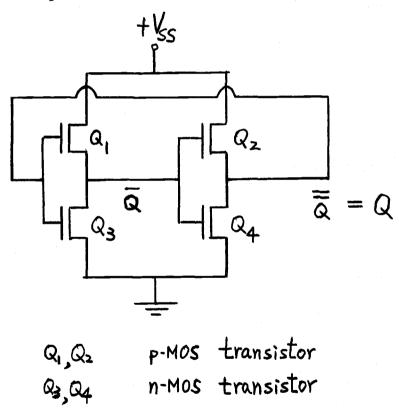

| 21.   | CMOS RAM Cell Circuit                                                                       | 52         |

| Figure | <b>e</b>                                                                                                       | Page |

|--------|----------------------------------------------------------------------------------------------------------------|------|

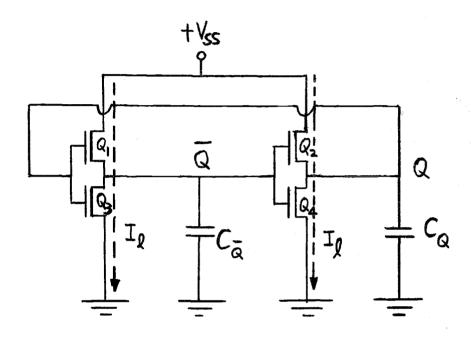

| 22.    | CMOS Storage Cell                                                                                              | 54   |

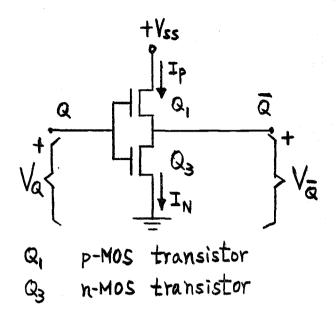

| 23.    | CMOS Inverter                                                                                                  | 56   |

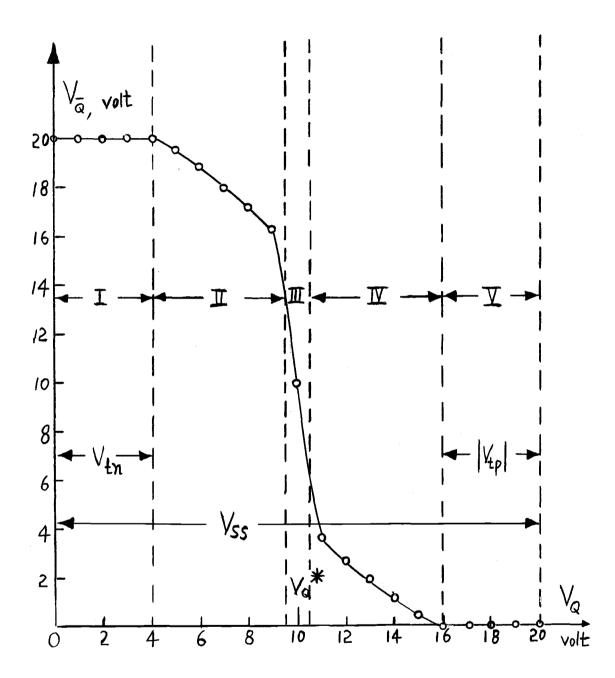

| 24.    | Inverter Operating Point Locus                                                                                 | 57   |

| 25.    | Inverter Voltage Transfer Curve. Input Voltage $(V_{\overline{Q}})$ versus Output Voltage $(V_{\overline{Q}})$ | 60   |

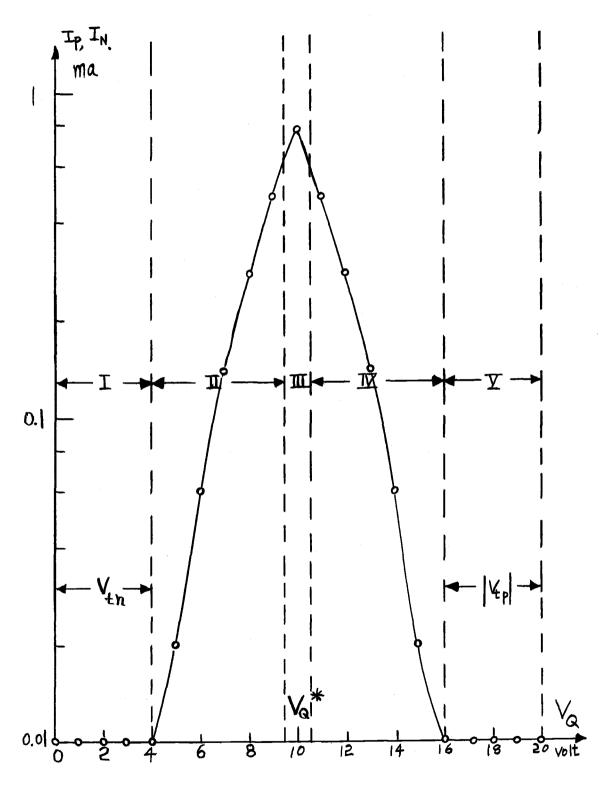

| 26.    | Inverter Current $(I_p, I_N)$ versus Input Voltage $(V_Q)$                                                     | 61   |

| 27.    | Inverter with Step Input                                                                                       | 65   |

| 28.    | Simplified Inverter Step Response                                                                              | 66   |

| 29.    | Step Response of Cell                                                                                          | 69   |

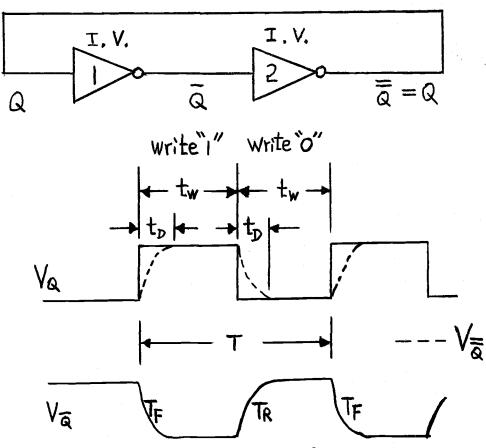

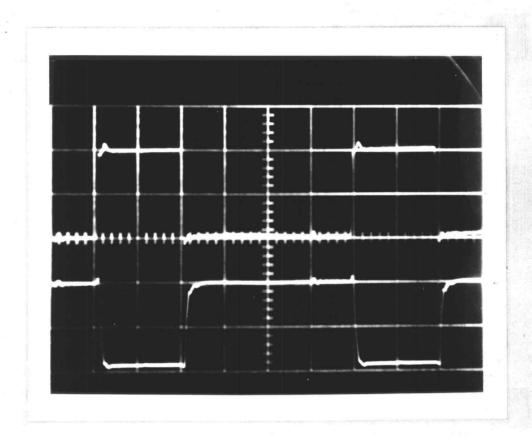

| 30.    | Cell Pulsed Response                                                                                           | 70   |

| 31.    | CMOS Storage Cell with Nodal Capacitors                                                                        | 72   |

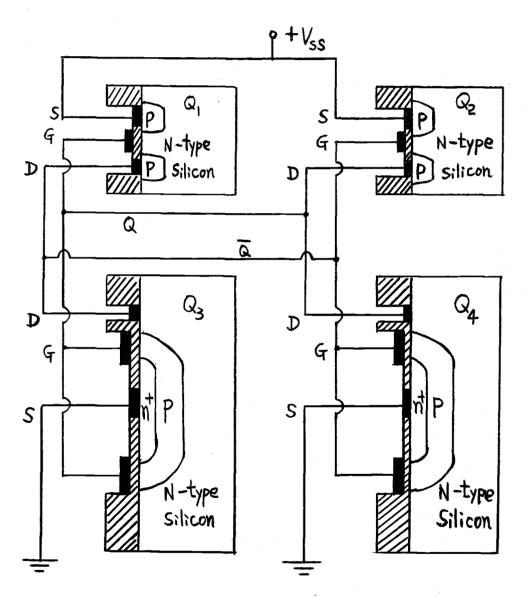

| 32.    | Monolithic Storage Cell                                                                                        | 74   |

| 33.    | Hybrid Cell                                                                                                    | 77   |

| 34.    | Cell Switching Test Schematic                                                                                  | 78   |

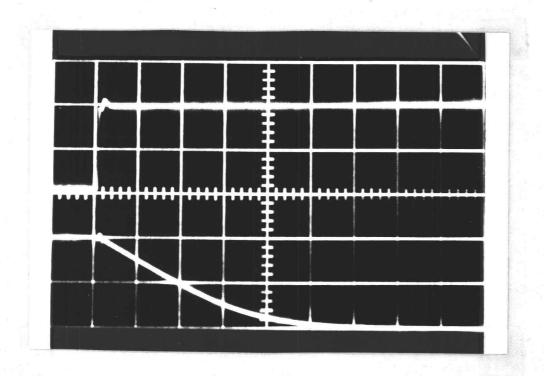

| 35.    | Cell Switching                                                                                                 | 79   |

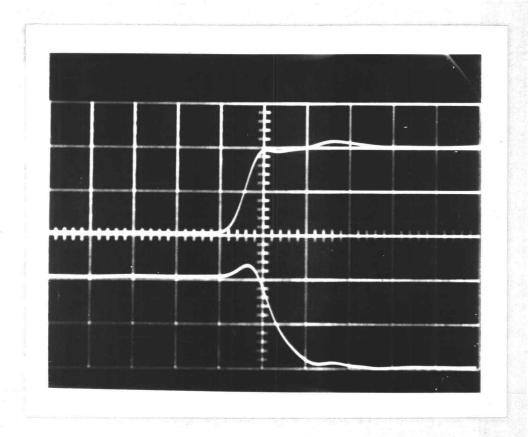

| 36.    | Enlarged Cell Switching                                                                                        | 80   |

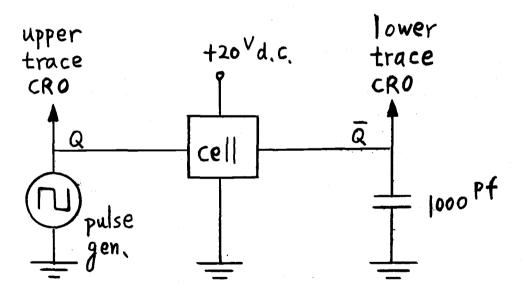

| 37.    | T <sub>F</sub> Testing Circuit                                                                                 | 81   |

| 38.    | Fall Time Response                                                                                             | 82   |

| 39.    | CMOS RAM Cell Composite                                                                                        | 84   |

| 40.    | Monolithic CMOS RAM Cell Photomicrograph                                                                       | 85   |

|        | LIST OF APPENDIX FIGURES                                                                                       |      |

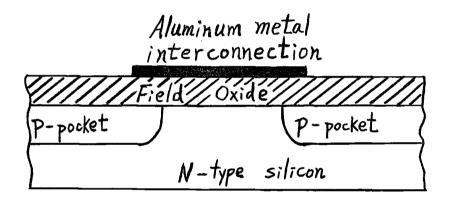

| A.     | Accidental MOS Structure Between Two Diffused Pockets                                                          | 93   |

### LIST OF TABLES

| Table |                                                                            | Page |

|-------|----------------------------------------------------------------------------|------|

| 1.    | V <sub>tn</sub> for Various N <sub>A</sub> - N <sub>D</sub>                | 25   |

| 2.    | Numerical Values of Depletion Region Width and Effective Channel Length    | 44   |

| 3.    | Diffusion Schedules                                                        | 47   |

| 4.    | Static Cell States                                                         | 55   |

| 5.    | Transistor Operating Condition versus Input Voltage $(V_Q)$ of an Inverter | 58   |

|       | LIST OF APPENDIX TABLES                                                    |      |

| Α.,   | Ids versus Vgs for P-MOS Transistor                                        | 99   |

| В. И  | Ids versus V <sub>gs</sub> for DN-MOS Transistor                           | 99   |

| С.    | Numerical Values for the Plot of DN-MOS<br>P-Region Impurity Profile       | 101  |

| D.    | Numerical Values for the Plot of DN-MOS n+-Region Impurity Profile         | 102  |

| E.    | DN-MOS Transistor Net Impurity Profile                                     | 1.03 |

# A COMPLEMENTARY MOS RANDOM-ACCESS-MEMORY CELL WITH DOUBLE-DIFFUSED MOS TRANSISTORS

#### I. INTRODUCTION

There are four MOS transistors in a complementary MOS random-access-memory storage cell. This study investigates the use of a special kind of MOS transistor called "double-diffused MOS transistor" as two of the required four MOS transistors in implementing the cell. It is found that incorporating double-diffused MOS transistors into the complementary MOS random-access-memory cell will improve the switching speed and/or cell size without causing monolithic fabrication complexity, yet preserving the power saving nature which is inherent to the complementary structure.

The fabrication processes and the performance of this particular cell are the focal points of interest. Cell operation, power dissipation, switching speed, cell size and fabrication complexity are discussed in detail.

Experiments started with developing a process so that both conventional p-channel and double-diffused n-channel MOS transistors could exist on a single chip in enhancement mode. A hybrid prototype cell was then built by using the two types of MOS transistors mentioned. Finally a monolithic design was realized. Test results of both the individual devices involved and the cell are presented.

Semiconductor integrated circuit memory has just now

been widely used by industry to store data in a computing system. There are two categories of semiconductor integrated circuit memory: the bipolar memory and the MOS memory; this investigation belongs to the MOS memory category. Both p-channel type and n-channel type MOS transistors are employed in implementing the memory cell which is different from the regular configuration using only one type of MOS transistor; the word "complementary" is added to tell the difference.

Random-access-memory (RAM) is the structure where information can be written into the cell at random and stored, then read out later on. There is another name for it called "read-write memory" to distinguish it from the read-only memory (ROM) structure.

# II. DOUBLE-DIFFUSED AND CONVENTIONAL MOS TRANSISTORS

The double-diffused n-type channel MOS transistor and conventional p-type channel MOS transistor are discussed alongside each other throughout this chapter. Investigation of the double-diffused MOS transistor as a discrete microwave device has been done by Hans J. Sigg et al. (19), while here the main objective is to explore this device as used together with conventional MOS transistors in monolithic complementary structure and the effect on circuit operating speed. Device characteristics related to circuit performance is emphasized in this chapter.

#### A. DEVICE STRUCTURE

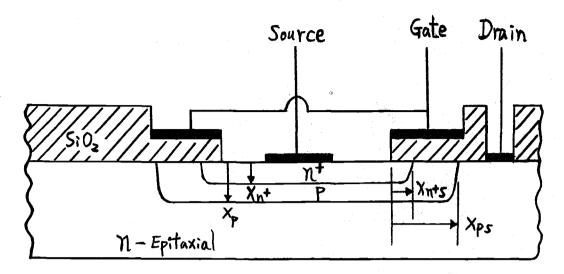

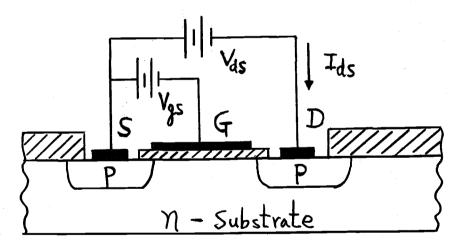

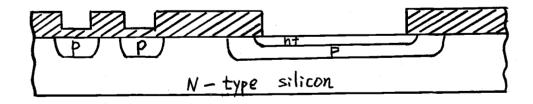

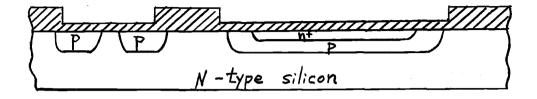

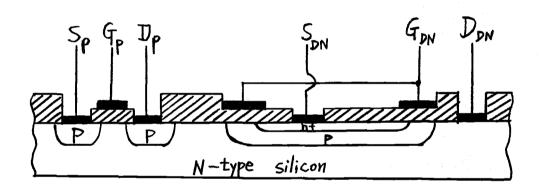

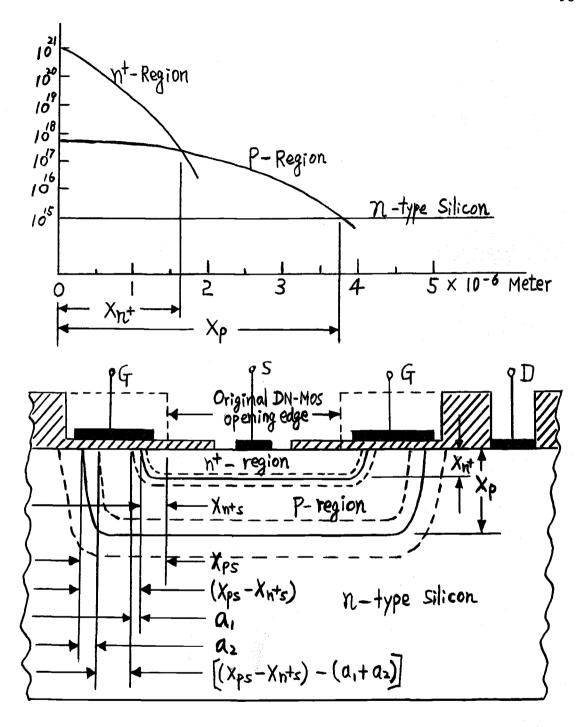

Figure 1 shows the cross-section of a double-diffused n-type channel MOS transistor (DN-MOS). The channel of the DN-MOS transistor is laterally diffused through an oxide window opening and bounded by  $n^+$  - p junction and p-n epitaxial junction. The p-diffusion into the n-epitaxial layer is followed by a  $n^+$  - diffusion through the same oxide window.

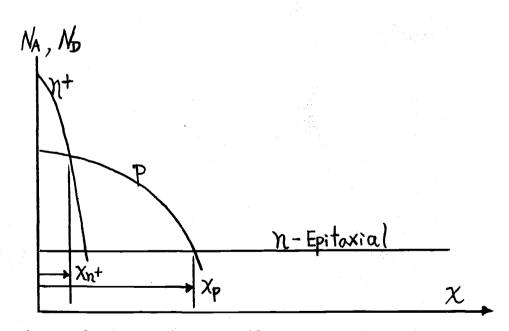

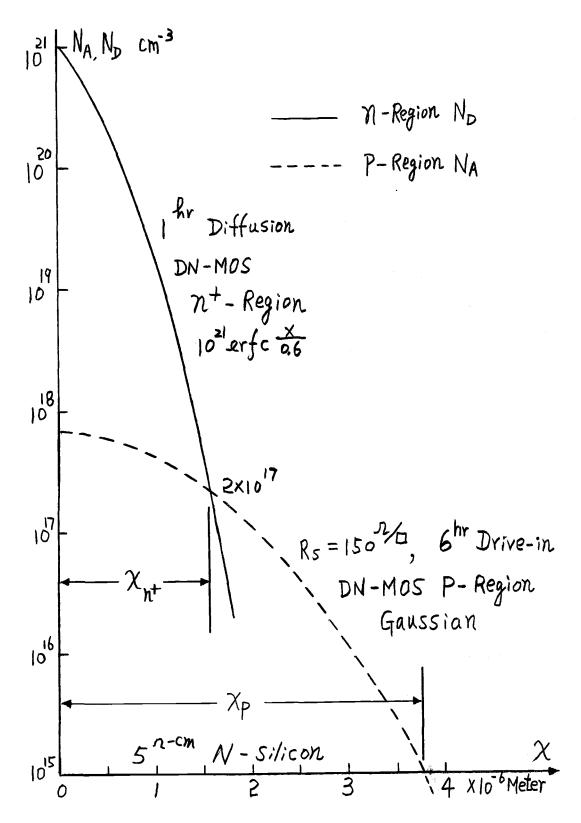

The impurity profile of this structure is shown in Figure 2. The surface concentrations of  $n^+$  and p impurity layer and their distribution shape are controlled by the fabrication process, which will be discussed later. Once  $X_{n+}$  and  $X_p$  are known then  $X_{n+s}$  and  $X_{ps}$  in Figure 1 can be

Figure 1. Cross-section of DN-MOS.

Figure 2. Impurity profile of DN-MOS structure.

found through the calculated results by D. P. Kennedy and R. R. O'Brien (13); the metallurgical channel length is  $X_{\rm ps}-X_{\rm n+s}$ . This is shown in a later section, II C 4, in detail. By using the double diffused technique channel length close to 1  $\mu$ M (10<sup>-6</sup> meter) can be realized while the conventional photolithography technique can only yield channel length of 5  $\mu$ M at best.

Contacts to n<sup>+</sup> layer and n-epitaxial layer are provided to be source and drain contact respectively as in Figure 1. Gate thin oxides are grown after gate opening. Aluminum metal gate is evaporated on the thin oxide as shown in Figure 1.

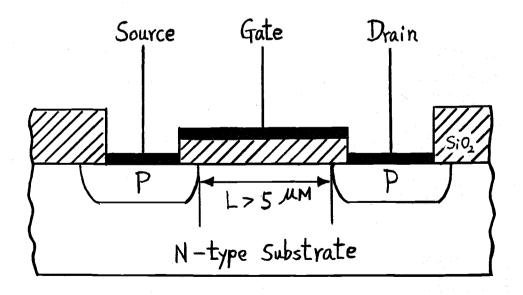

Figure 3 gives the cross-section of a conventional p-type channel MOS transistor (p- MOS). The p-type source

Figure 3. Cross-section of conventional p-MOS.

and drain region are diffused into uniformly doped n-type substrate, separated by at least 5  $\mu M$  (5 x 10<sup>-6</sup> meter) due to regular photolithography limit. Aluminum metal contacts are provided to source, drain and gate.

#### B. DEVICE OPERATION

The double-diffused MOS transistor differs from the conventional one in the channel doping; the former has a gradually decreasing channel doping level from source to drain as can be seen in Figures 1 and 2, while the latter has uniformly doped channel from source to drain as shown in Figure 3. The effect of this non-uniform channel doping on device threshold voltage has been studied by Chou (2), and it was found that the heavy impurity concentration near the source end of the channel determines the device threshold voltage. We assume the first order theory of conventional MOS equations (5) still holds for double-diffused MOS transistors (19); namely they are:

$$I_{ds} = \frac{\mu \epsilon_{ox}^{W}}{2t_{ox}^{L}} \left[ 2(v_{gs} - v_{th}) v_{ds} - v_{ds}^{2} \right]$$

for  $v_{ds} < v_{gs} - v_{th}$  (non-saturation region)

$$I_{ds} = \frac{\mu \epsilon_{ox}^{W}}{2t_{ox}^{L}} (v_{gs} - v_{th})^{2}$$

for  $v_{ds} \geqslant v_{gs} - v_{th}$  (saturation region)

$$I_{ds} = 0$$

(3)

for  $V_{qs} < V_{th}$  (off region)

where:

Ids = current from drain to source

μ = effective electron mobility for n-type MOS

transistor; effective hole mobility for p-type

MOS transistor

$\epsilon_{\text{OX}}$  = permittivity of silicon dioxide 1/3 pf/cm

tox = gate silicon dioxide thickness

W = MOS transistor channel width

L = MOS transistor channel length

V<sub>gs</sub> = voltage drop from gate to source

$V_{th}$  = MOS transistor threshold voltage

V<sub>ds</sub> = voltage drop from drain to source

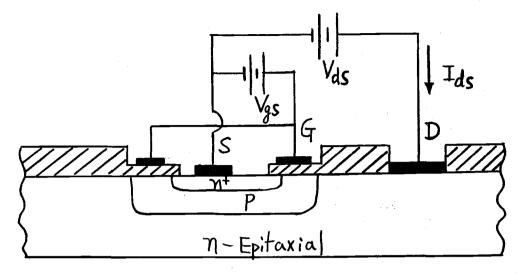

The above equations and definitions are for n-type channel MOS transistors. For p-type channel MOS transistor in enhancement mode quantities  $I_{\rm ds}$ ,  $V_{\rm gs}$ ,  $V_{\rm th}$  and  $V_{\rm ds}$  will all be negative, if their corresponding absolute values are used, equations (1), (2) and (3) still hold. Figure 4 gives a clear picture of the above statements, where two enhancement MOS transistors are used as examples.

Enhancement mode MOS transistor means it takes a positive  $V_{\rm gs}$  to have  $I_{\rm ds}$  flow for n-type channel MOS transistor, while it takes a negative  $V_{\rm gs}$  to have  $I_{\rm ds}$  flow for p-type channel MOS transistor. Some n-type channel MOS transistors will have  $I_{\rm ds}$  flow even at zero  $V_{\rm gs}$  or

(a) Enhancement DN-MOS transistor,  $I_{ds}$ ,  $V_{gs}$ ,  $V_{th}$ , and  $V_{ds}$  all positive.

(b) Enhancement conventional p-type channel MOS transistor, I<sub>ds</sub>, V<sub>gs</sub>, V<sub>th</sub>, and V<sub>ds</sub> all negative.

Figure 4. Enhancement MOS transistors in operation.

negative  $V_{gs}$ ; they belong to depletion mode. All these will be obvious when threshold of device is discussed.

The threshold voltage  $(V_{th})$  of the MOS transistor has been given by the following expression (12):

$$V_{th} = 2\phi_{F} + \phi_{ms} - \frac{qN_{ss}}{C_{o}} + \frac{Q_{B}}{C_{o}}$$

$$= V_{tn} \quad \text{(for n-type channel)}$$

(4)

$$V_{th} = 2\phi_{F} + \phi_{ms} - \frac{qN_{ss}}{C_{o}} - \frac{Q_{B}}{C_{o}}$$

$$= V_{tp} \text{ (for p-type channel)}$$

(5)

where:

$\phi_{ms}$  = work function difference between gate metal aluminum and silicon bulk

$q = electronic charge 1.6 x <math>10^{-19}$  coulomb

$N_{ss} = surface states per cm<sup>2</sup>$

$C_0$  = gate oxide capacitance per unit area  $= \epsilon_{0x}/t_{0x}$

Q = charge density per unit area within the surface depletion region in equilibrium

$$= \sqrt{2\epsilon_{\text{si}}q \mid N_{\text{A}} - N_{\text{D}} \mid 2\phi_{\text{F}} \mid}$$

$\epsilon_{

m si}$  = permittivity of silicon, 1.0632 pf/cm  $\left| {\rm N_A - N_D} \right|$  = net channel impurity level at heavily doped source end for DN-MOS just N<sub>D</sub> for conventional p-MOS

The value of  $\phi_{\mathbf{F}}$  is given as (16):

$$\Phi_{\mathbf{F}} = \frac{\mathbf{KT}}{\mathbf{q}} \ln \frac{\mathbf{N_A} - \mathbf{N_D}}{\mathbf{n_i}} \tag{6}$$

where:

K = Boltzmann's constant, 8.62 x 10<sup>-5</sup> ev/Kelvin

degree

T = temperature in Kelvin degree

$n_i$  = intrinsic silicon carrier concentration, 1.6 x 10<sup>10</sup> per cm<sup>3</sup> at room temperature

The numerical values of  $\phi_{ms}$  given by Deal <u>et al</u>. (7) range from -0.4 volt to -0.1 volt for n-type silicon, and -0.8 volt to -1.1 volt for p-type silicon. The exact value of  $\phi_{ms}$  depends on  $|N_A - N_D|$  which runs from  $10^{14}$  to  $10^{18}$  per cm<sup>3</sup>.

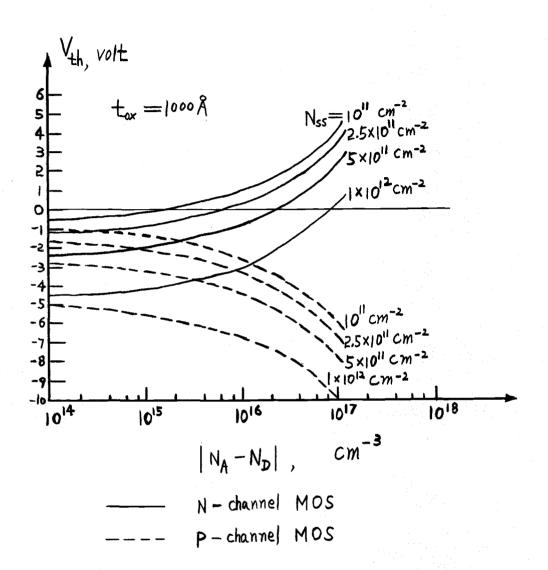

Assuming  $\phi_{ms} = 0$  for n-type silicon, -0.7 volt for p-type silicon, and  $t_{ox} = 1000 \text{ Å} = 10^{-7}$  meter, equations (4) and (5) are plotted by Lin <u>et al</u>. (15) which is transferred as Figure 5 for reference.

The threshold  $V_{\rm th}$  of an n-type channel MOS transistor can be either positive or negative depending on both  $|N_{\rm A}-N_{\rm D}|$  and  $N_{\rm ss}$  as shown in Figure 5. If  $V_{\rm th}$  is positive for an n-type channel MOS transistor it is enhancement mode; it takes a more positive  $V_{\rm gs}$  to have  $I_{\rm ds}$  flow (see equations 1, 2, and 3). If  $V_{\rm th}$  is negative for an n-type channel MOS transistor, it is depletion mode; a positive  $V_{\rm gs}$  or less negative  $V_{\rm gs}$  or zero  $V_{\rm gs}$  will give  $I_{\rm ds}$  flow

Figure 5.  $V_{th}$  of both p-channel and N-channel MOS transistors versus  $|N_A - N_D|$  and  $N_{ss}$ . (Ref. 15)

(see equations 1, 2, and 3). The statement made earlier on pages 7 and 9 is justified.

The threshold voltage of most practical p-type channel MOS transistors is negative as can be seen in Figure 5; a negative threshold voltage for the p-type channel MOS transistor means enhancement mode. The reason for this is that the only positive term in equation (5),  $2\phi_{\rm F}$ , is usually small as compared to the sum of the other three negative terms.

#### C. PROCESSES AND CONSIDERATIONS

The objective of this section is devoted to the fabrication considerations of both double-diffused n-type channel MOS transistor (DN-MOS) and conventional p-type channel MOS transistor (p-MOS) monolithically on a chip. The complementary memory cell configuration requires both DN-MOS and p-MOS operating in enhancement mode. A lower threshold voltage ( $V_{\rm th}$ ) and shorter channel length will result in faster switching of the complementary memory cell. The circuit performance requirements will be clear when cell operation is discussed later; however, the requirements must be considered in process planning and fulfilled during processing.

#### 1. Process Steps

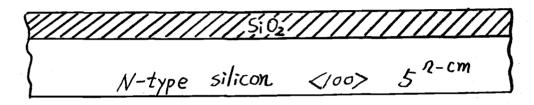

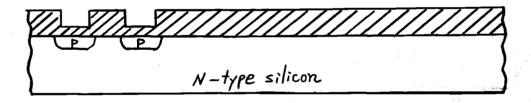

The fabrication sequence of the monolithic chip containing both DN-MOS and p-MOS is illustrated in Figure 6 below. Each step in Figure 6 is accompanied by the description in Appendix I.

a. Field oxidation,

b. p-Mos source and drain diffusion.

c. DN-Mos opening, p-diffusion followed by n+-diffusion.

Figure 6a. Major steps of device fabrication process.

d. Gate opening, followed by gate oxidation.

e. Open Contacts to source and drain, metalization and excess aluminum removal.

Figure 6b. Major steps of device fabrication process.

## 2. Experimental Results

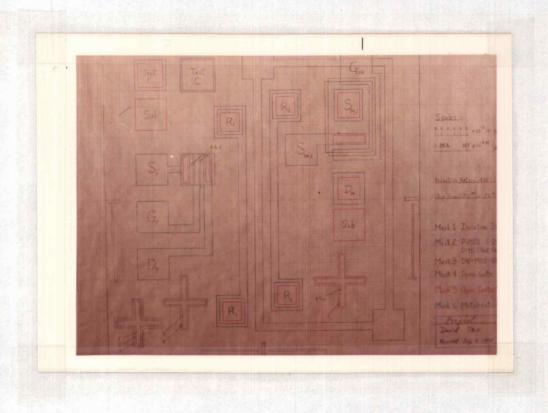

A composite layout was designed, as shown in Figure 7. It consists of a conventional p-MOS transistor, a DN-MOS transistor, two diffused resistors, and a testing MOS capacitor. The purpose of this part is to ensure that the process sequence stated in previous sections will yield good p-MOS and DN-MOS transistors.

Figure 7. Device composite layout.

A set of masks are generated. Samples are processed as stated in section II C 1. Typical finished sample under the microscope looks like that shown in Figure 8.

Figure 8. Photomicrograph of devices.

An individual chip is cut from the wafer, using a diamond scriber. A TO-5 header is used to encase the chip. Bonding is done by a Sonoweld ultrasonic bonder with  $1 \times 10^{-3}$  inch diameter aluminum wire.

Both p-MOS transistor and DN-MOS transistor characteristics are tested through the transistor curve tracer.

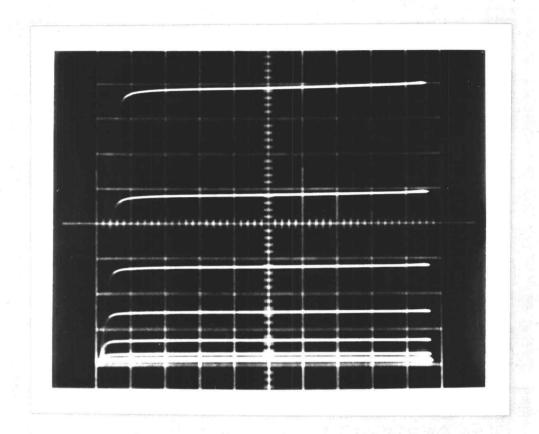

Typical results are shown in Figures 9 and 10. Two pictures are shown for each type of transistor; gate bias

Vertical -  $I_{ds}$ : 2 milli-ampere per major division Horizontal -  $V_{ds}$ : 5 volts per major division Gate bias: 2 volts per step. Top curve  $V_{gs}$  = - 20 volts

Figure 9a. P-MOS transistor characteristics.

Vertical -  $I_{ds}$ : 500 micro-ampere per major division Horizontal -  $V_{ds}$ : 5 volts per major division Gate bias: 1 volt per step. Top curve  $V_{gs}$  = - 10 volts

Figure 9b. P-MOS transistor characteristics.

Vertical  $I_{ds}$ : 2 milli-ampere per major division Horizontal  $V_{ds}$ : 5 volts per major division Gate bias: 2 volts per step. Top curve  $V_{gs}$  = 20 volts

Figure 10a. DN-MOS transistor characteristics.

Vertical  $I_{ds}$ : 100 micro-ampere per major division Horizontal  $V_{ds}$ : 5 volts per major division Gate bias: 1 volt per step. Top curve  $V_{gs}$  = 10 volts

Figure 10b. DN-MOS transistor characteristics.

as high as 20 volts is shown. Drain voltage can reach beyond 40 volts without causing the junction between drain region and channel bulk to breakdown. Twenty volts is the highest voltage in the complementary memory cell configuration to be realized later by employing both p-MOS transistor and DN-MOS transistor, so it is safe as far as the voltage rating is concerned. However, if the n<sup>+</sup>-region of the DN-MOS transistor were used as drain and n-type silicon as source (refer to Figure 4a), then the breakdown voltage of the n<sup>+</sup>-p junction would limit the voltage within the cell to less than ten volts, which may not be practical if the device threshold voltage is close to four volts because the biasing condition will cause very slow switching of the cell.

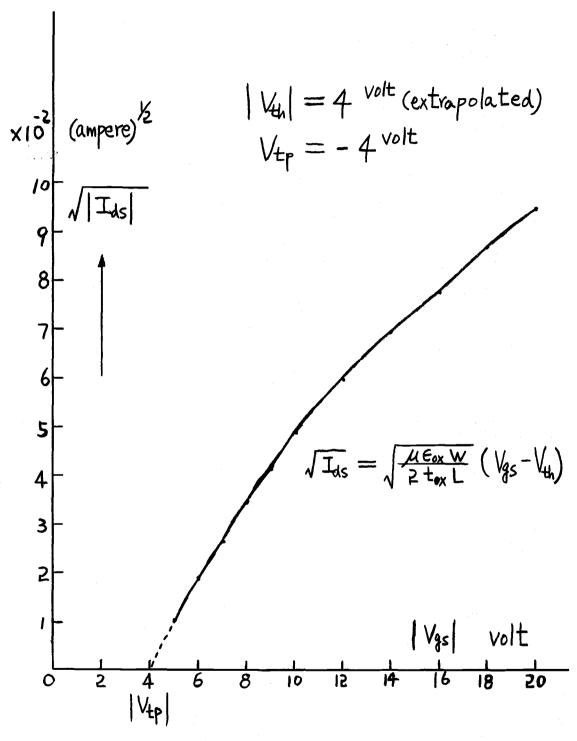

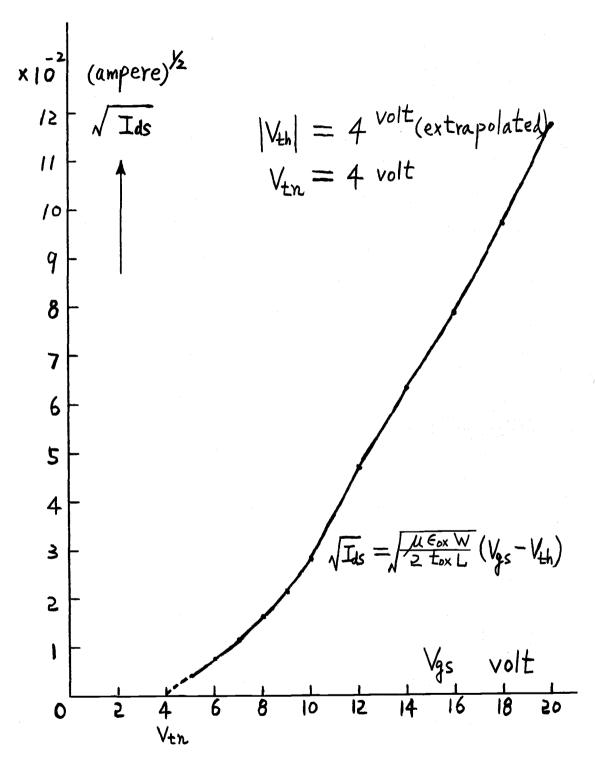

From equation (2) it has

$$\sqrt{I_{ds}} = \sqrt{\frac{\mu \epsilon_{ox} W}{2t_{ox} L}} \quad (v_{gs} - v_{th})$$

for  $v_{ds} \geqslant v_{gs} - v_{th}$  (saturation region)

In the linear plot of  $\sqrt{I_{\rm ds}}$  versus  $V_{\rm gs}$ ,  $V_{\rm th}$  can be found from the point when  $\sqrt{I_{\rm ds}}$  is zero.

$I_{\rm ds}$  and corresponding  $V_{\rm gs}$  values read from Figures 9 and 10 are tabulated in Tables A and B in Appendix II.  $\sqrt{I_{\rm ds}}$  is also listed for convenience.  $I_{\rm ds}$  values are read when  $-V_{\rm ds}=25$  volts for the p-MOS transistor and  $V_{\rm ds}=25$  volts for the DN-MOS transistor; it is the point when the transistors are in saturation.

Linear plots of  $\sqrt{I_{\rm ds}}$  versus  $V_{\rm gs}$  for both p-MOS and DN-MOS transistors are shown in Figures 11 and 12. The extrapolated curve shows threshold voltage for p-MOS transistor  $V_{\rm tp}$  = -4 volts and threshold voltage for DN-MOS transistor  $V_{\rm tn}$  = 4 volts.

## 3. Threshold Voltage Consideration

The threshold voltage of both p-MOS transistor and DN-MOS transistor is an important factor affecting the performance of the complementary MOS memory cell. Reference to equations (4), (5), and (6) shows that net channel doping  $|N_A - N_D|$  determines values of  $\phi_F$ ,  $\phi_{ms}$ , and  $Q_B$ . Its effect on  $V_{th}$  is observed first, and the calculation and control of  $|N_A - N_D|$  is then discussed.

# a. Net Channel Doping NA - ND Effect on Threshold Voltage

For the p-MOS transistor, the channel is uniformly doped.  $N_A - N_D$  is simply the doping level of the starting n-type silicon, 5 ohm-cm resistivity corresponding to a doping level  $N_D$  of  $10^{15}$  per cm<sup>3</sup>; hence the threshold voltage of p-MOS transistor  $V_{\rm tp}$  can be calculated using equations (5) and (6) to be - 3.2 volts, assuming a surface state of 5 x  $10^{11}$  per cm<sup>2</sup> and gate oxide thickness of 1200 Å (1.2 x  $10^{-7}$  meter). An error of 0.8 volt is found between the calculated value and the experimental

Figure 11. P-MOS transistor  $\sqrt{|I_{ds}|}$  versus  $|-V_{gs}|$ .

Figure 12. DN-MOS transistor  $\sqrt{I_{ds}}$  versus  $V_{gs}$ .

extrapolated value in Figure 11. Error source could very well come from the estimation of  $|N_A - N_D|$ . The lot of silicon wafers used has a specified resistivity of 1 to 5 ohm-cm, which means  $|N_A - N_D|$  has a range between 5 x  $10^{15}$  to  $10^{15}$  per cm<sup>3</sup> respectively. If  $|N_A - N_D|$  is 5 x  $10^{15}$  per cm<sup>3</sup>, then the calculated  $V_{tp}$  would be - 4 volts.

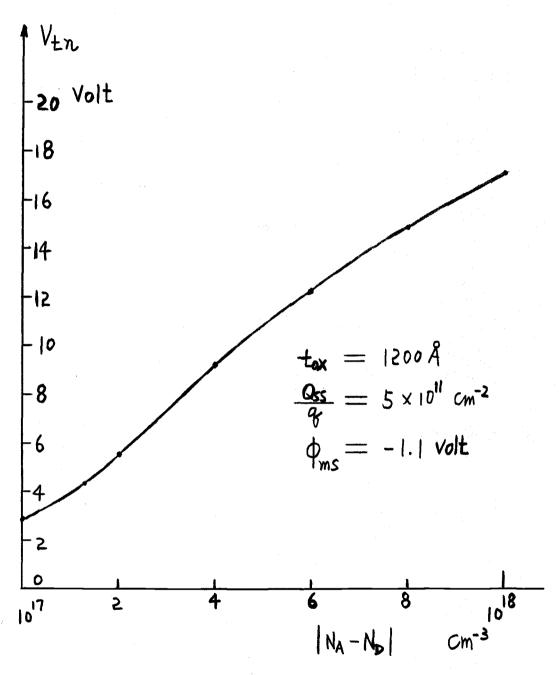

For the DN-MOS transistor, the heavy net channel doping near the source end determines threshold voltage  $V_{tn}$  (2). Figure 5 shows  $\left| N_A - N_D \right|$  up to  $10^{17}$  per cm<sup>3</sup> only, while the range of interest to the particular process sequence stated in Appendix I is between  $10^{17}$  and  $10^{18}$  per cm<sup>3</sup>.  $V_{tn}$  for various  $\left| N_A - N_D \right|$  between  $10^{17}$  and  $10^{18}$  per cm<sup>3</sup> is calculated using equations (4) and (6), assuming  $5 \times 10^{11}$  per cm<sup>2</sup> surface states and 1200 Å (1.2  $\times 10^{-7}$  meter) gate oxide thickness.  $\Phi_{ms}$  used is -1.1 volt from reference (7). The results are listed in Table 1 below and plotted in Figure 13.

| Table 1. V <sub>tn</sub> for Various N <sub>A</sub> - N <sub>D</sub> |                  |                    |                    |                    |                    |                  |

|----------------------------------------------------------------------|------------------|--------------------|--------------------|--------------------|--------------------|------------------|

| $\begin{bmatrix} N_A - N_D \\ (cm^{-3}) \end{bmatrix}$               | 10 <sup>17</sup> | 2x10 <sup>17</sup> | 4×10 <sup>17</sup> | 6x10 <sup>17</sup> | 8x10 <sup>17</sup> | 10 <sup>18</sup> |

| V <sub>tn</sub> (volt)                                               |                  |                    | 9.30               |                    |                    |                  |

| (volt)                                                               |                  |                    |                    |                    |                    |                  |

It can be seen in Figure 13 that  $V_{\text{tn}}$  goes from 2.88 volts to 17.15 volts as net channel doping varies. The control

Figure 13. DN-MOS threshold voltage ( $V_{tn}$ ) versus net channel doping  $N_A - N_D$  near source end.

of  ${\rm V}_{\rm tn}$  is therefore dependent on the impurity profile of the DN-MOS transistor.

### b. Impurity Profile Calculations

There are two kinds of impurity profile distribution involved in the processing sequence stated in section II C 1. A predeposition giving a sheet resistance followed by a long drive-in period results in Gaussian distribution, which has a limited-source boundary condition. The p-MOS transistor source and drain region and the DN-MOS transistor p-region belong to the Gaussian distribution. In a later section when the memory cell is realized, the isolation diffusion belongs to this kind also. The DN-MOS transistor n+-region is fabricated by one step diffusion as stated in Appendix I C, which has a constant-source boundary condition. The impurity distribution profile is a complementary error function (erfc); this is the second kind.

For p-type Gaussian distribution, it has (22):

$$N_{A}(x) = \sqrt{\frac{Q}{\pi D_{p}t}} \quad e^{-x^{2}/4D_{p}t}$$

(8)

$$Q = \frac{1}{R_{s}q\mu}$$

(9)

where:

$^{N}A$  = acceptor impurity atoms per unit volume,  $cm^{-3}$ .

Q = impurity concentration in atoms per unit  $area, cm^{-2}$ .

$D_{\rm p}$  = diffusion coefficient, or diffusivity, for boron in silicon at 1100°C.  $D_{\rm p}$  is 0.09  $(\mu M)^2$  per hour or 0.09 x  $10^{-8}$  cm<sup>2</sup> per hour (12).

t = drive-in diffusion time in hour.

X = depth into the surface of silicon in micrometer  $\mu M$ .

$R_s$  = sheet resistance of silicon surface after predeposition, in ohms per square.

$q = electronic charge, 1.6 \times 10^{-19} coulomb$ .

$\mu$  = mobility of holes, 480 cm<sup>2</sup> per volt-sec.

For n-type complementary error function distribution (erfc) it has (22):

$$N_{D}(X) = N_{O} \text{ erfc } \frac{X}{2\sqrt{D_{p}t}}$$

(10)

where:

$N_D = \text{donor impurity atoms per unit volume, cm}^{-3}$ .

$N_{O}$  = surface concentration in atoms per cm<sup>3</sup>, independent of diffusion time.  $10^{21}$  per cm<sup>3</sup> for phosphorus in silicon at  $1000^{\circ}$ C, determined by solid solubility (22).

$D_n$  = diffusion coefficient of phosphorus into silicon, 0.09  $(\mu M)^2$  per hour at 1000°C (12).

Consider the DN-MOS transistor p-region first. It has a sheet resistance of 150 ohms per square, and an

over-all effective drive-in time of six hours (refer to Appendix I c). Equation (9) gives:

$$Q = \frac{1}{(150)(1.6 \times 10^{-19})(480)}$$

and

$$Q = 8.7 \times 10^{13} \text{ cm}^{-2} \tag{11}$$

Substituting equation (11) into equation (8) yields:

$$N_{A}(X) = \frac{8.7 \times 10^{13}}{\sqrt{(3.14)(0.09 \times 10^{-8}) 6}} e^{\frac{-X^{2}}{4(0.09) 6}}$$

and

$$N_{A}(X) = 6.7 \times 10^{17} e^{\frac{-X^{2}}{2.16}}$$

(12)

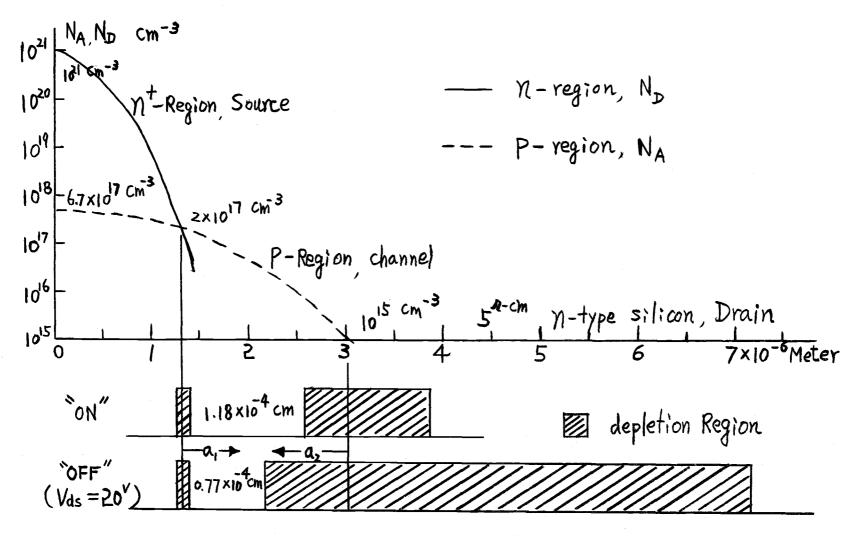

The plot of equation (12) is the dotted line in Figure 14, based on numerical values listed in Table C, Appendix III.

The value of  $X_p$  can be calculated by solving  $N_A(X_p) = 10^{15}$  from equation (12) as follows:

$$\frac{-x_p^2}{2.16}$$

$$10^{15} = 6.7 \times 10^{17} \text{ e} \tag{13}$$

then

$$x_p^2 = 2.16 \ln 670 = 2.16 \left( \ln 6.7 + 2 \ln 10 \right)$$

and

$$x_p = 3.74 \mu M = 3.74 \times 10^{-6} \text{ meter}$$

For the  $n^+$ -region of DN-MOS transistor, it has a complementary error function distribution, the phosphorus diffusion is done at 1000°C for one hour. Thus

equation (10) gives:

$$N_D(X) = 10^{21} \text{ erfc } \frac{X}{2\sqrt{(0.09)(1)}}$$

=  $10^{21} \text{ erfc } \frac{X}{0.6}$  (14)

The plot of equation (14), also shown in Figure 14, is based on the numerical values listed in Table D, Appendix III. Error function values are obtained from a reference table (18). The value of  $X_{n+}$  is read from Figure 14 to be 1.55 x  $10^{-6}$  meter. This graphical solution is much easier than setting equation (12) equal to equation (14) and trying to solve for  $X_{n+}$  analytically.

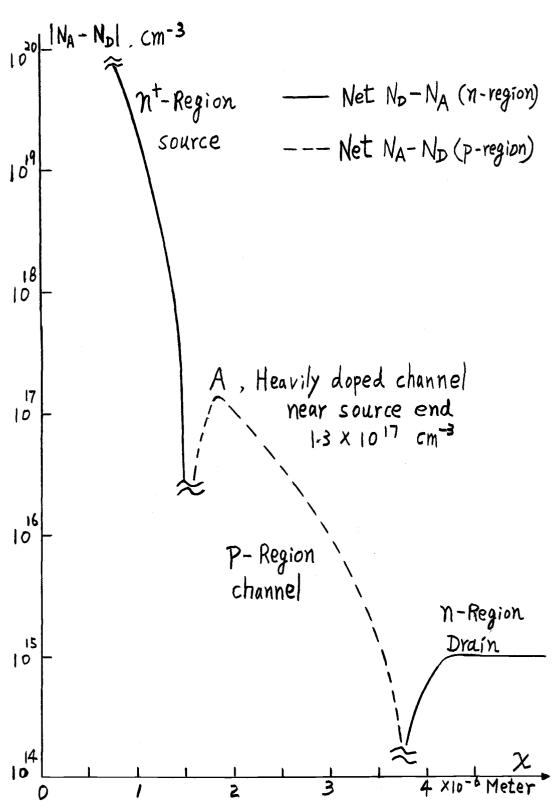

Net impurity doping profile for the DN-MOS transistor is plotted in Figure 15 based on numerical values listed in Table E, Appendix III. The channel has the heaviest doping at point A in Figure 15 near the source end. The value of this high doping level is found to be  $1.3 \times 10^{17}$  atoms per cm<sup>3</sup> from Table E, Appendix III.

Based on the value of 1.3 x  $10^{17}$  cm<sup>-3</sup> as  $|N_A - N_D|$  and from Figure 13, the value of  $V_{\rm tn}$  should be 4.4 volts, which is very close to the experimental extrapolated result of four volts in Figure 12.

# c. Impurity Profile Control on DN-MOS Transistor Threshold Voltage

The threshold voltage of DN-MOS transistor  $v_{\rm tn}$  is dependent on the impurity profile of the p-region near the

Figure 14. DN-MOS transistor impurity profiles.

Figure 15. DN-MOS net impurity profile.

n<sup>+</sup>-p junction as point A in Figure 15.

Referring to equations (8) and (9), both sheet resistance  $R_S$  and drive-in time t are the two parameters which can be adjusted to fit a designer's need. The boron diffusivity  $D_p$  can be varied depending on the drive-in temperature (practical value is from 1000°C to 1200°C). The effect of varying  $D_p$  on  $N_A$  (X) is the same as that of varying t on  $N_A$  (X); this can be seen from equation (8). In the diffusion practice it is desirable to plan on varying t rather than changing diffusion furnace temperature.

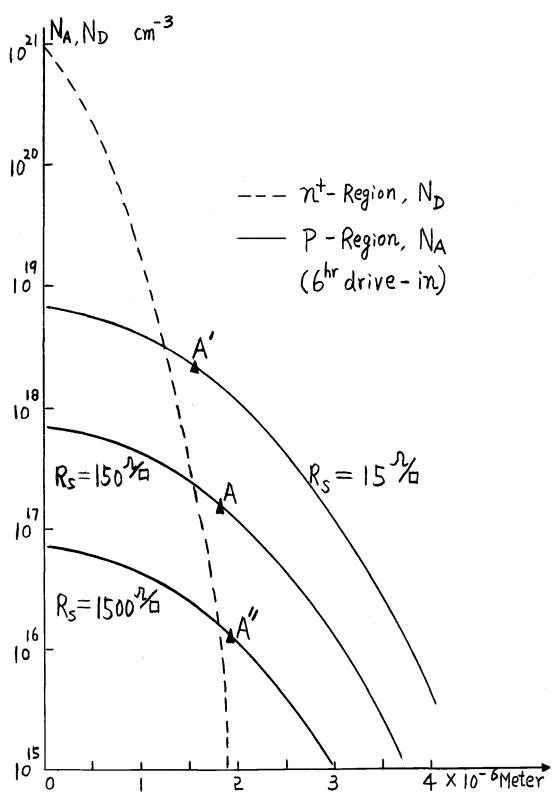

The effect of changing sheet resistance  $R_{c}$  after predeposition on p-region profile is shown in Figure 16, where three different  $R_{_{\mathbf{S}}}$  values are shown assuming same six hours drive-in at 1100°C.  $N_{A}$  (X) is linearly proportional to the reciprocal of  $\mathbf{R}_{_{\mathbf{S}}}\text{, as can be seen from equations (8) and$ (9). Figure 16 shows this effect clearly. If the same n<sup>+</sup>-region diffusion is used, then the dotted line in Figure 16 represents the n<sup>+</sup>-region impurity profile. The point A with the highest net channel doping would move up approximately to A' or down to A'' in Figure 16, depending on sheet resistance. A' has a  $|N_A - N_D|$  larger than  $10^{18}$  per  $cm^3$ , which gives a  $V_{tn}$  larger than 17 volts (see Figure 13). Point A' has a  $|N_A - N_D|$  close to  $10^{16}$  per cm<sup>3</sup>, which may make the DN-MOS operating in depletion mode with a negative  $V_{tn}$  (refer to Figure 5). As  $R_s$  goes from 15 ohms per square to 1500 ohms per square,  $V_{\text{tn}}$  goes from above 17

Figure 16.  $R_S$  effect on DN-MOS p-region impurity profile.

volts to a negative value. It is then concluded that  $\mathbf{R}_{\mathbf{S}}$  affects  $\mathbf{V}_{\mathbf{t}\,\mathbf{n}}$  drastically.

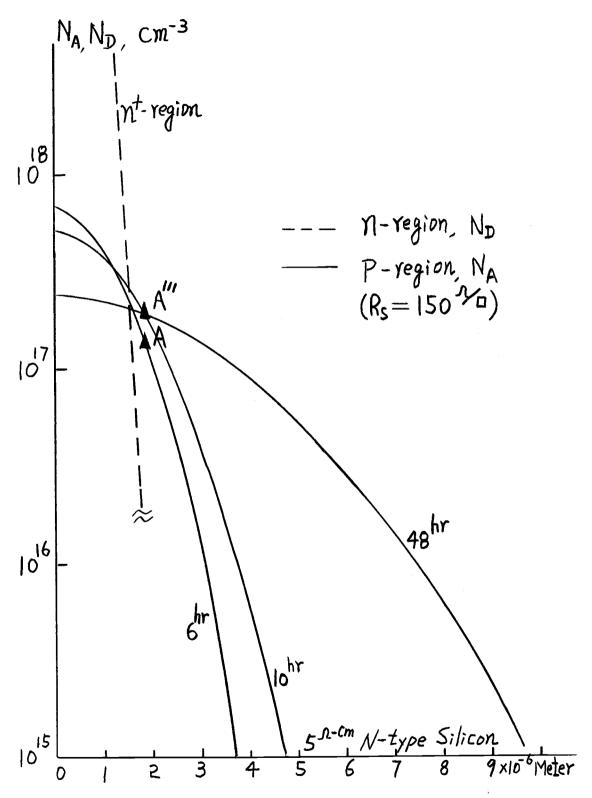

The other diffusion parameter is the drive-in time t. From equations (8) and (9), assuming  $R_{\rm S}=150$  ohms per square constant and t = six hours, ten hours or 48 hours respectively, a family of curves is plotted in Figure 17 according to the following equations\*:

$$N_{A}(X) = 6.7 \times 10^{17} \text{ e}$$

(15)

(for t = 6 hours)

$$N_{A}(X) = 5.19 \times 10^{17} e$$

(16)

(for t = 10 hours)

$$N_{A}(x) = 2.37 \times 10^{17} e$$

(for t = 48 hours)

(17)

Also in Figure 17 the n+-region impurity profile is shown in dotted line assuming the same n+ diffusion as before. It can be seen that  $N_D$  of the n+-region is a very steep function with respect to X within the vicinity where point A locates. As the drive-in time of the DN-MOS p-region changes from six hours to ten hours or to 48 hours, the point A where net channel doping  $N_A - N_D$  is highest

<sup>\*</sup>Equation (15) is the same as equation (12), copied for convenience.

Figure 17. Drive-in time effect on DN-MOS p-region impurity profile.

moves approximately to point A''' for both ten hour and 48 hour cases, as shown in Figure 17. Corresponding new  $\left| N_{A} - N_{D} \right|$  is then 2 x  $10^{17}$  per cm<sup>3</sup>; it does not deviate much from the 1.3 x  $10^{17}$  per cm<sup>3</sup> for point A before. Of course  $V_{tn}$  still changes to 5.5 volts as listed in Table 1 as compared to 4.4 volts for point A before. A change of 1.1 volt in  $V_{tn}$  results from drastically changing p-region drive-in time from six hours to ten hours or even to 48 hours.

Because of the insensitive nature of the Gaussian (p-region) distribution with respect to t near the small X end, and the sensitive nature of the complementary error function (n+-region) distribution with respect to X near the tailing end, it is concluded that varying t will not change  $|N_A - N_D|$  and thence  $V_{\rm tn}$ .

From Figure 17 it is seen that the junction depth of p-region varies drastically as the drive-in time increases. Ten hours drive-in gives a junction depth of  $4.7 \times 10^{-6}$  meter, which is the p-MOS transistor source and drain region. Forty-eight hours drive-in gives a junction depth of  $9.7 \times 10^{-6}$  meter, which can be used for isolation diffusion when a memory cell is realized on an  $8 \times 10^{-6}$  meter thick n-type epitaxial layer on p-type substrate. These junction depths can be calculated using equations (16) and (17) in the same manner as  $X_p$  was calculated in equation (13).

#### d. Silicon Orientation Effect on Threshold Voltage

The surface state charge density  $N_{SS}$  (refer to equations 4 and 5) of thermally oxidized gate silicon has a smaller value for  $(100)^*$  oriented silicon than  $(111)^*$  oriented silicon (6).

For a p-MOS transistor this means (100) oriented silicon will yield a smaller threshold voltage  $|V_{\rm tp}|$  than (111) oriented silicon. This is because the third term in equation (5) will have a smaller absolute value for (100) silicon and usually the third term is a major contributing term for  $V_{\rm tp}$ . The dotted lines in Figure 5 also illustrate this phenomenon.

For a DN-MOS transistor, less  $N_{SS}$  means equation (4) will have a better chance to yield a positive  $V_{tn}$ . In other words, a DN-MOS transistor is likely to operate in enhancement mode. This is because the third term in equation (4) is a major negative term. The solid lines in Figure 5 demonstrate this fact clearly.

Since the DN-MOS transistor must operate in enhancement mode in the complementary memory cell discussed later, and it is desirable to have low absolute value  $V_{tp}$  for p-MOS transistors used in the complementary memory cell, (100) orientation is therefore much preferred over (111) orientation.

<sup>\*</sup>Miller indices for crystal orientation.

# 4. DN-MOS Transistor Channel Length Consideration -- Punch Through

An enlarged cross-section view of the DN-MOS transistor with definition of quantities used in channel length calculation is shown in Figure 18. Figure 14 is also inserted to indicate the correlation of quantities in the impurity profile diagram. Quantities in Figure 18 have the following definitions:

$X_{n+}$  = junction depth of the  $n^+$ -p junction between  $n^+$ -region and p-region

X<sub>p</sub> = junction depth of the p-n junction between

p-region and n-type silicon

$x_{n+s} = lateral$  junction depth of the  $n^+$ -p junction

$X_{ps}$  = lateral junction depth of the p-n junction

a = depletion width in the p-region side of the

n +-p junction

a<sub>2</sub> = depletion width in the p-region side of the p-n junction

The values of  $X_p$  and  $X_{n+}$  were found in section II C 3b to be 3.74 x  $10^{-6}$  meter and 1.55 x  $10^{-6}$  meter respectively.

In order to find  $X_{ps}$ , the p-region impurity distribution function in equation (12) is considered again. The surface impurity level is found by setting X = 0:

$$N_{A}(0) = 6.7 \times 10^{17} \text{ cm}^{-3}$$

(18)

The background to be diffused in has an impurity level

Figure 18. Enlarged cross-section of DN-MOS transistor with defining quantities.

of  $10^{15}$  per cm<sup>3</sup>. Considering the concentration ratio

$$\frac{10^{15}}{6.7 \times 10^{17}} = 0.00149 \tag{19}$$

as a parameter, from the Gaussian distribution contours calculated by Kennedy et al. (13), it is found that:

$$\frac{X_{ps}}{X_{p}} = \frac{2.1}{2.6} \tag{20}$$

Equation (20) gives  $X_{ps}$  as

$$X_{ps} = (3.74)(\frac{2.1}{2.6}) \times 10^{-6}$$

= 3.02 x 10<sup>-6</sup> meter (21)

For the value of  $X_{n+s}$ , the surface concentration of  $n^+$ -region is found from equation (14) by setting X=0

$$N_D(0) = 10^{21} \text{ erfc } 0$$

=  $10^{21} \text{ cm}^{-3}$  (22)

The p-region background to be diffused in has a doping level of 2 x  $10^{17}$  per cm<sup>3</sup> (refer to Figure 14). Considering the concentration ratio

$$\frac{2 \times 10^{17}}{10^{21}} = 0.0002 \tag{23}$$

as a parameter, from the complementary error function distribution contours calculated by Kennedy et al. (13), it is found that

$$\frac{X_{n+s}}{X_{n+}} = \frac{2.3}{2.7} \tag{24}$$

Equation (24) gives  $X_{n+s}$  as

$$X_{n+s} = (1.55)(\frac{2.3}{2.7}) \times 10^{-6}$$

= 1.32 x 10<sup>-6</sup> meter (25)

The metallurgical channel length should be (X  $_{\rm ps}$  - X  $_{\rm n+s}$  ), which is 1.7 x 10  $^{-6}$  meter.

The values of depletion widths  $a_1$  and  $a_2$  depend on the biasing condition of the DN-MOS transistor and the impurity distribution near  $n^+$ -p junction and p-n junction. If  $(X_{ps} - X_{n+s})$  is equal to or smaller than  $(a_1 + a_2)$ , then the depletion regions occupy the metallurgical channel, the DN-MOS transistor is accidentally "on" all the time. There will be no "off" state, which is called "punch through." Frohman-Bentchkowsky <u>et al</u>. (11) reported this phenomenon for a lightly doped short channel device.

The worst case to consider possible punch through is when the transistor is supposed to be in "off" state, while no drain current is drawn, and the large drain voltage  $V_{\rm ds}$  is reverse biasing the drain p-n junction giving a large  $a_2$ .

Assume  $\rm V_{ds}$  is 20 volts, which is the highest d.c. voltage in the memory cell to be discussed later. Consider the following parameters

$$\frac{\text{(junction bias)}}{\text{(background doping)}} = \frac{20^{\text{V}}}{10^{15} \text{ cm}^{-3}}$$

$$= 2 \times 10^{-14} \text{ V} - \text{cm}^{3}$$

(26)

$$\frac{\text{(background doping)}}{\text{(surface doping)}} = \frac{10^{15}}{6.7 \times 10^{17}}$$

$$= 1.49 \times 10^{-3} \tag{27}$$

and a Gaussian junction depth of  $3.74 \times 10^{-4}$  cm, the total depletion width and a<sub>2</sub> can be found from the calculated results by Lawrence and Warner (14) to be:

(drain junction total depletion width)

$$= 5 \times 10^{-4} \text{ cm}$$

=  $5 \times 10^{-6} \text{ meter}$

and

$$a_2 = (0.17)(5 \times 10^{-4}) = 8.5 \times 10^{-5} \text{ cm}$$

= 0.85 x 10<sup>-6</sup> meter

A similar approach is used to find  $a_1$ . Consider 0.7 volt  $n^+$ -p junction built-in voltage as junction bias,  $2 \times 10^{17}$  per cm<sup>3</sup> as background doping,  $10^{21}$  per cm<sup>3</sup> as surface doping, and a complementary error function junction depth of  $1.55 \times 10^{-4}$  cm. These new parameters yield:

(source junction total depletion width)  $= 0.14 \times 10^{-6} \text{ meter}$

and

$$a_1 = 0.08 \times 10^{-6} \text{ meter}$$

Then  $(a_1 + a_2)$  gives  $0.93 \times 10^{-6}$  meter which is smaller than  $(X_{\rm ps} - X_{\rm n+s}) = 1.7 \times 10^{-6}$  meter. The DN-MOS transistor will not punch through under 20 volts bias; an effective channel length of  $0.77 \times 10^{-6}$  meter still exists.

The numerical values involved so far are summarized in Table 2. The depletion widths and effective channel length, when the DN-MOS transistor is in "on" state, are also listed in Table 2. During the calculation built-in voltages are considered as the junction bias for both source and drain junctions.

Table 2. Numerical Values of Depletion Region Width and Effective Channel Length

| DN-MOS                                                             | State                     | OFF<br>V <sub>ds</sub> = 20 <sup>V</sup> | on<br>v <sub>ds</sub> = o <sup>v</sup> |

|--------------------------------------------------------------------|---------------------------|------------------------------------------|----------------------------------------|

| source n <sup>+</sup> -p<br>junction                               | total depletion width, cm | 0.14x10 <sup>-4</sup>                    | 0.14x10 <sup>-4</sup>                  |

|                                                                    | a <sub>l</sub> , cm       | 0.08x10 <sup>-4</sup>                    | 0.08x10 <sup>-4</sup>                  |

| drain p-n<br>junction                                              | total depletion width, cm | 5x10 <sup>-4</sup>                       | 1.3x10 <sup>-4</sup>                   |

|                                                                    | a <sub>2</sub> , cm       | 0.85x10 <sup>-4</sup>                    | $0.44 \times 10^{-4}$                  |

| effective channel length $(X_{ps}^{-X}_{n+s}) - (a_1^{+a}_2)^{cm}$ |                           | 0.77×10 <sup>-4</sup>                    | 1.18x10 <sup>-4</sup>                  |

The depletion region width variation effect on DN-MOS transistor effective channel length is shown in Figure 19 with the numerical values in Table 2 as reference. Two approximations are made during the calculation process: the first one is that the p-region impurity doping level is a constant of 2 x  $10^{17}$  per cm<sup>3</sup> near ( $\pm$  0.1 x  $10^{-6}$  meter, where depletion region extends) the source n<sup>+</sup>-p junction; the second one is that the depletion width does not change

Figure 19. Depletion region width variation effect on channel length of DN-MOS transistor.

in lateral cases.

Figure 19 indicates that effective channel length varies from  $0.77 \times 10^{-6}$  meter to  $1.18 \times 10^{-6}$  meter as the DN-MOS transistor switches from "off" state to "on" state.

It has been shown that the channel length of the DN-MOS transistor depends on biasing condition and impurity profile distribution. Section II C 3c shows that the impurity profile also controls the threshold voltage of the DN-MOS transistor. It is then concluded that the impurity profile determines both threshold voltage and channel length of the DN-MOS transistor.

### 5. Diffusion Schedule Considerations

There are three diffused regions under consideration:

p-MOS transistor source and drain region, DN-MOS transistor

p-region, and DN-MOS transistor n+-region. Because diffusions are performed consecutively, the heat cycle experienced must be accumulatively considered for each region.

Table 3 shows the schedule summarized from Appendix I.

In planning this schedule, several conditions must be met. The first condition is that the total time experienced by DN-MOS p-region and DN-MOS n+-region affect their impurity profiles, which in turn control the channel length and the threshold voltage of the DN-MOS transistor. They must be properly arranged to avoid punch through and/or too high a threshold voltage.

| diffused<br>region                 | p-MOS source<br>and drain | DN-MOS<br>p-region | DN-MOS<br>n+-region |

|------------------------------------|---------------------------|--------------------|---------------------|

| section<br>describing<br>diffusion | II C lb                   | II C lc            | II C lc             |

| diffusion<br>type                  | Gaussian                  | Gaussian           | erfc                |

| diffusion<br>time                  | 4 hr                      | 5 hr               | 1 hr                |

| total time<br>experienced          | 10 hr                     | 6 hr               | 1 hr                |

Table 3. Diffusion Schedules

In the determination of DN-MOS n+-region diffusion time, it is assumed that the DN-MOS p-region has been chosen (within limits stated later in section II C 6) as the dotted line in Figure 14, and the n+-p source junction occurs at X = 1.55 x  $10^{-6}$  meter N (X) = 2 x  $10^{17}$  per cm<sup>3</sup> point. This choice determines both the threshold voltage and channel length of the DN-MOS transistor. Set N<sub>D</sub> (X) in equation (10) equals to 2 x  $10^{17}$  per cm<sup>3</sup>, and X equals to 1.55 x  $10^{-6}$  meter to solve for t; t is found to be one hour for DN-MOS n+-region diffusion.

Every planned schedule must be checked according to the same approach as in sections II C 4 and II C 3c, for punch through and threshold voltage.

The second condition is that since different regions are diffused consecutively, there must be an appreciable difference between the total time experienced by each

region, so that it is possible to schedule diffusion time for each step.

The third condition is that the drive-in time for  $p ext{-MOS}$  source and drain region must be long enough (four hours in Table 3) so that thick enough oxide can be grown during drive-in to protect the region against the following p and p diffusions for the DN-MOS transistor.

Too long a drive-in time for p-MOS source and drain region will give too deep a junction depth (refer to Figure 17). The lateral diffused source and drain region will decrease the channel length as seen from the diffusion mask, causing large Miller's capacitance between gate and source (or drain).

When isolation diffusion is needed, a total drive-in time of 48 hours will safely isolate a 5 ohm-cm resistivity and 8.5 to 9  $\times$  10<sup>-6</sup> meter thick n-type silicon layer (refer to Figure 17). This isolation could be done before p-MoS source and drain region which has a ten hour total drive-in time.

### 6. Other Considerations

During the drive-in diffusion of the DN-MOS p-region the atmosphere must be in inert gas as described in Appendix I c. Nitrogen is used to prevent any oxidation so that the original DN-MOS opening edge (see dotted line in Figure 18) can be preserved as mask for the following

n+ diffusion.

The doping level of point A in Figure 15 has an upper limit of  $4.5 \times 10^{17}$  per cm<sup>3</sup> if threshold voltage of the DN-MOS transistor,  $V_{\rm tn}$ , is limited to a maximum value of ten volts (see Figure 13). There is a lower limit for the doping level of point A to be  $4.5 \times 10^{16}$  per cm<sup>3</sup> so that  $V_{\rm tn}$  can be positive, then the DN-MOS transistor operates in enhancement mode. The impurity level corresponding to point A in Figure 15 is determined mostly by the p-region impurity profile. The above mentioned limits serve as limits for the DN-MOS p-region impurity level near n+-p junction as well.

The 5 ohm-cm starting material affects the threshold voltage of p-MOS transistor  $V_{\rm tp}$  (see Figure 5). It also affects the DN-MOS transistor drain p-n junction breakdown voltage; for n-type silicon having 1 to 25 ohm-cm resistivity (5 x  $10^{15}$  to 2 x  $10^{14}$  per cm<sup>3</sup>) 3.74 x  $10^{-6}$  meter Gaussian junction depth, the breakdown voltage is well above 20 volts (reference 20), so that the d.c. bias in the memory cell circuit discussed later can operate safely on the DN-MOS transistor.

## III. THE COMPLEMENTARY MOS RANDOM ACCESS MEMORY CELL

The complementary MOS random access memory (CMOS RAM) cell to be discussed can operate from static (d.c.) to high speed (a few megahertz). The cell offers a non-destructive read out process; reading need not be followed by a write operation to restore memory contents. Each cell is directly addressed within the memory matrix of cells through its associated selecting MOS transistors. The addressing process is random, because each cell has its own combination of "on" selecting transistors.

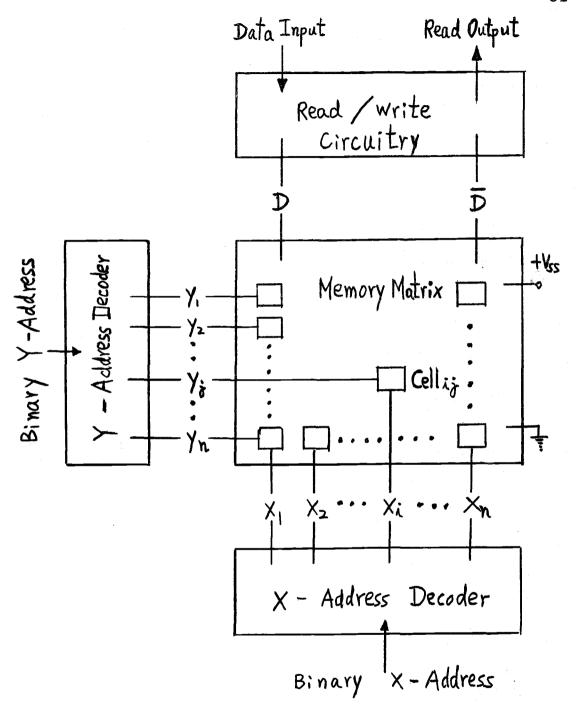

Figure 20 shows the functional blocks of the memory system. Binary addressing signals are decoded through x or y decoder circuitry to select an x and a y line; the selected x and y lines determine the particular cell in the memory matrix where data can be written in or read out through the read/write circuitry. For an n x n memory matrix, there are n x-lines and n y-lines, while binary input to both x and y decoder should have log<sub>2</sub> n lines.

Cells within the memory matrix are all identical. A typical  $cell_{ij}$  is investigated in the following sections.

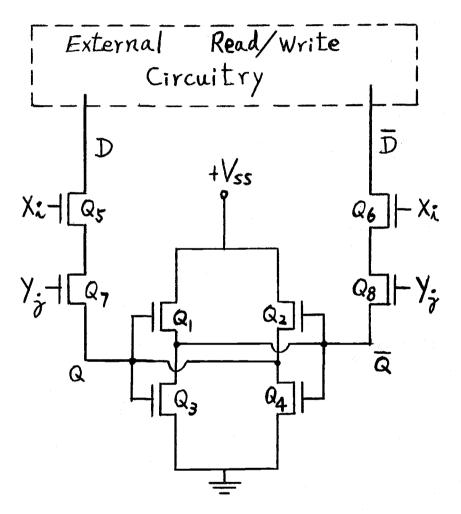

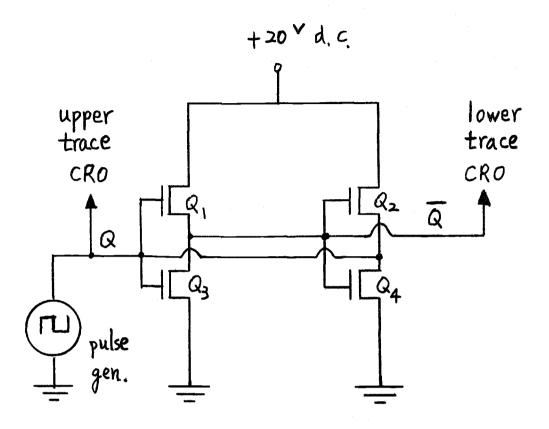

As shown in Figure 21, the cell consists of eight MOS transistors; four ( $Q_5$   $Q_6$   $Q_7$   $Q_8$ ) are selecting transistors, and the other four ( $Q_1$   $Q_2$   $Q_3$   $Q_4$ ) form a bistable storage flip-flop. Only  $Q_3$  and  $Q_4$  are n-type channel MOS

Figure 20. The random-access-memory system block diagram.

#### A. THE CMOS RAM CELL CIRCUIT

$\mathbf{Q}_5$   $\mathbf{Q}_7$   $\mathbf{Q}_1$   $\mathbf{Q}_2$   $\mathbf{Q}_8$   $\mathbf{Q}_6$  p-MOS transistors  $\mathbf{Q}_3$   $\mathbf{Q}_4$  n-MOS transistors  $\mathbf{Q}_5$   $\mathbf{Q}_6$   $\mathbf{Q}_7$   $\mathbf{Q}_8$  selecting transistors  $\mathbf{Q}_1$   $\mathbf{Q}_2$   $\mathbf{Q}_3$   $\mathbf{Q}_4$  storage flip-flop

Figure 21. CMOS RAM cell circuit.

transistors; the remaining six are p-type channel MOS transistors.

Two possible circuit configurations for external read/ write circuit can be found in a Texas Instrument application report (17).

The selecting process is accomplished by negative going voltage step from  $V_{ss}$  to 0 reaching node  $x_i$  and  $y_i$ in Figure 21. If writing of "l" is performed at this moment, the external read/write circuit will provide + V<sub>ss</sub> at node D, which pulls node Q to  $V_{ss}$  through  $Q_{5}$  and  $Q_{7}$ ; the writing of "0" is done the same way only through  $\bar{D}$   $\bar{Q}$ branch instead. Once the information is written in the storage flip-flop  $(Q_1 \ Q_2 \ Q_3 \ Q_4)$ , it will be memorized by the bistable nature of the flip-flop in terms of nodal voltage at Q and  $\bar{Q}$ . If reading of "l" in the cell is performed, the high voltage at node Q ( $V_{O} = V_{ss}$ ) will cause a current flow in branch Q D, which will then be detected by a sense amplifier in the read/write circuitry in Figure 21. The reading of "0" is done the same way through current flow in  $\overline{Q}$   $\overline{D}$  branch, but the sense amplifier will have a different response due to its input voltage polarity. Both node  $x_i$  and  $y_i$  must be at zero ground potential (cell; being selected from the matrix) when writing or reading is taking place. During stand-by situation, at least one of  $x_i$  or  $y_i$  must be at  $V_{ss}$  turning off the corresponding selecting transistor isolating the storage

flip-flop from external read/write circuit. The coincident select method is the same as that used by Friedrich (10).

#### B. CELL D.C. OPERATION

$Q_5$  and  $Q_7$  or  $Q_6$  and  $Q_8$  in Figure 21 only provide the necessary path to the read/write circuitry when needed. The storage of information is essentially performed by  $Q_1$ ,  $Q_2$ ,  $Q_3$ ,  $Q_4$  in Figure 21. The  $Q_1$ ,  $Q_2$ ,  $Q_3$  and  $Q_4$  portion is redrawn in Figure 22 below.

Figure 22. CMOS storage cell.

The d.c. operation of the CMOS storage cell can be best stated in a tabled form:

| cell state | Q <sub>1</sub> | Q <sub>2</sub> | Q <sub>3</sub> | Q <sub>4</sub> | v <sub>Q</sub>   | v <sub>Q</sub>   |

|------------|----------------|----------------|----------------|----------------|------------------|------------------|

| "1"        | OFF            | ON             | ON             | OFF            | +V <sub>ss</sub> | 0                |

| "0"        | ON             | OFF            | OFF            | ON             | 0                | <sup>+V</sup> ss |

Table 4. Static Cell States

It is noted that in either state "1" or "0", no current flows (except leakage current of the "off" device) between the d.c. power supply +  $V_{SS}$  and ground, which is the power saving nature of complementary MOS memory.

Close examination of the configuration in Figure 22 reveals that the cell is two inverters in cascade with the output of the second inverter fed back to the input of the first inverter to ensure bistable of the cell when input is removed. It is now imperative to study the static operation of the complementary MOS inverter so that how the cell changes state can be understood. Figure 23 shows the first inverter which is composed of  $Q_1$  and  $Q_3$ .

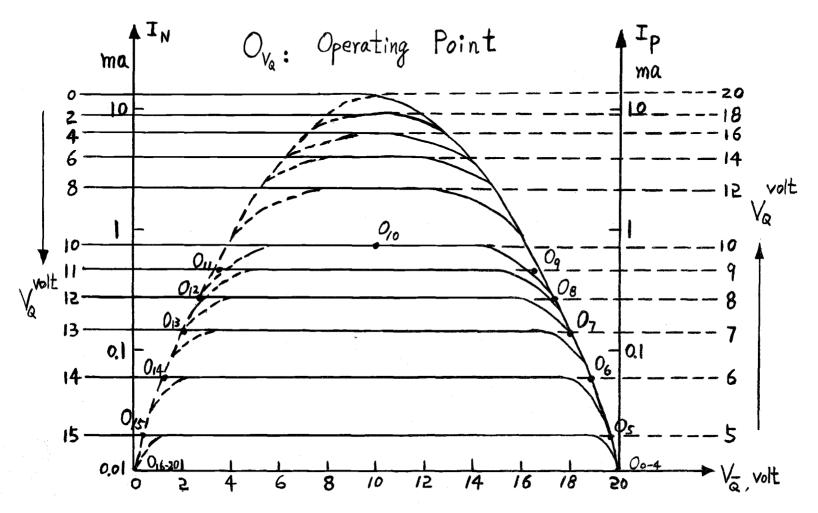

The p-MOS transistor  $Q_1$  can be thought as load to the n-MOS transistor  $Q_3$ . As  $V_Q$  increases from zero to +  $V_{ss}$ ,  $V_{\overline{Q}}$  decreases from +  $V_{ss}$  to zero. The operating point corresponding to different  $V_Q$  value  $(0_{VQ})$  is shown in Figure 24. Transistor drain characteristics are, from Figure 10, dotted line for n-MOS transistor  $Q_3$  and solid line for load p-MOS transistor  $Q_1$ .  $V_{ss}$  is assumed to be 20 volts. It is noted that  $Q_3$  goes from off to

Figure 23. CMOS inverter.

saturation then to non-saturation, and  $Q_1$  goes from non-saturation to saturation then to off as  $V_Q$  increases. Based on these different operating conditions of  $Q_1$  and  $Q_3$ , five different regions are listed in Table 5. The governing inequalities in Table 5 are based on the conditions given in equations (1), (2), and (3), with the understanding that for  $Q_1 \mid V_{gs} \mid = V_{ss} - V_Q$  and  $\mid V_{ds} \mid = V_{ss} - V_{\overline{Q}}$  while for  $Q_3 \mid V_{gs} \mid = V_Q$  and  $\mid V_{ds} \mid = V_{\overline{Q}}$ . The boundary between regions is determined from two relating inequalities; for instance, in region I ( $V_Q < V_{th}$ ) while in region II ( $V_Q > V_{th}$ ) the boundary dividing regions I and II must be at ( $V_Q = V_{th}$ ) etc. Results are shown in the scale below Table 5.

The inverter voltage transfer curve is shown in

Figure 24. Inverter operating point locus.

Table 5. Transistor Operating Condition versus Input Voltage ( $V_Q$ ) of an Inverter

| Region<br>Transistor | I                | II                                    | III                              | IV                                   | - L V .                            |           |

|----------------------|------------------|---------------------------------------|----------------------------------|--------------------------------------|------------------------------------|-----------|

|                      | (OFF)            | (ON)                                  |                                  |                                      |                                    |           |

| N-MOS                | $(v_Q < v_{tn})$ | $(v_Q > v_{tn})$                      |                                  |                                      |                                    |           |

| (Q <sub>3</sub> )    |                  | (Saturated)                           |                                  | (Nonsa                               | aturated)                          |           |

|                      |                  | $(V_{\bar{Q}} > V_{Q} - V_{tn})$      |                                  | (V <sub>Q</sub> < )                  | $v_{Q} - v_{tn}$ )                 |           |

|                      |                  | $(v_{Q} < v_{\overline{Q}} + v_{tn})$ |                                  | $(V_Q > 1)$                          | v <sub>Q</sub> + v <sub>tn</sub> ) |           |

|                      |                  | (0)                                   | N)                               |                                      | (OFF)                              |           |

|                      |                  | $(v_{ss}-v_{Q})$                      | $(v_{ss}-v_{Q}) v_{tp} $         |                                      | $v_{ss}-v_{Q} < v_{tp}$            |           |

| P-MOS                |                  | $(v_Q < v_{ss} -  v_{tp} )$           |                                  |                                      | $(V_Q > V_{ss} -  V_{tp} )$        |           |

| (Q <sub>1</sub> )    |                  |                                       |                                  | rated)                               |                                    |           |

|                      |                  |                                       |                                  | $v_{ss} - v_{Q} -  v_{tp} $          |                                    |           |

|                      |                  | /Q -  V <sub>tp</sub>  )              |                                  | v <sub>Q</sub> -  v <sub>tp</sub>  ) |                                    |           |

|                      | I                | II                                    | III                              | īv                                   | V                                  | VQ        |

|                      | 0 7              | v <sub>tn</sub> v <sub>Q</sub> -      | V <sub>tp</sub> V <sub>Q</sub> + | V <sub>tn</sub> V <sub>ss</sub>      | - V <sub>tp</sub> V <sub>ss</sub>  | <b></b> - |

Figure 25, and the inverter current versus input voltage curve is shown in Figure 26. All data are taken from Figure 24.

From Figure 25, the slope  $(dV_{\overline{Q}}/dV_{\overline{Q}})$  is zero in region I and V, while in region III it has a very large negative value. This means the inverter has a high gain region in the center separating two regions with zero gain, which is an ideal characteristic based on input voltage  $V_{\overline{Q}}$  noise consideration.

The value of input voltage  $V_Q^*$  when the inverter operates in high gain region III is called the transition voltage. For better noise immunity,  $V_Q^*$  is designed to be  $1/2~V_{SS}$  (see Figure 25). A condition relating device constant and biasing voltage can be found according to this design criteria.

First, the set of MOS equations for both p-channel  $Q_1$  and n-channel  $Q_3$  are rewritten below, referring back to equations (1), (2), (3) and Figure 23 for convenience. For p-channel  $Q_1$  we have:

$$I_{p} = |I_{ds}| \qquad (28)$$

$$= K_{p} \left[ 2(|V_{Q}-V_{ss}| - |V_{tp}|)(|V_{\overline{Q}}-V_{ss}|) - (|V_{\overline{Q}}-V_{ss}|)^{2} \right]$$

$$= K_{p} \left[ V_{\overline{Q}}-V_{ss}| - |V_{tp}| + N_{p} \right] \qquad (29)$$

$$= K_{p} \left( |V_{Q}-V_{ss}| - |V_{tp}| \right)^{2} \qquad (29)$$

$$= K_{p} \left( |V_{\overline{Q}}-V_{ss}| - |V_{tp}| \right)^{2} \qquad (29)$$

$$= K_{p} \left( |V_{\overline{Q}}-V_{ss}| - |V_{tp}| \right)^{2} \qquad (29)$$

.2

Figure 25. Inverter voltage transfer curve. Input voltage ( ${\rm V_Q}$ ) versus output voltage ( ${\rm V_{\overline Q}}$ ).

Figure 26. Inverter current  $(I_p,I_N)$  versus input voltage  $(V_Q)$ .

$$I_{p} = 0$$

(30) for  $|V_{Q}-V_{ss}| < |V_{tp}|$ , off region

For n-channel  $Q_3$  we have:

$$I_{N} = I_{ds}$$

$$= K_{N} \left( 2 (V_{Q} - V_{tn}) V_{\overline{Q}} - V_{\overline{Q}}^{2} \right)$$

(31)

for  $V_{\bar{Q}} \leftarrow V_{Q}^{-}V_{tn}^{}$ , non-saturation region

$$I_{N} = K_{N} (V_{O} - V_{tn})^{2}$$

(32)

for  $V_{\overline{O}} \geqslant V_{O}^{-}V_{tn}^{}$ , saturation region

$$I_{\overline{N}} = 0 \tag{33}$$

for  $V_0 < V_{tn}$ , off region

where:

$$K_{p} = \frac{\overline{\mu}_{h} \in_{OX} W_{p}}{2 t_{OX} L_{p}}$$

(34)

$$K_{N} = \frac{\overline{\mu}_{e} \in_{OX} W_{N}}{2 t_{OX} L_{N}}$$

(35)

$\mathbf{K}_{\mathbf{D}}$  and  $\mathbf{K}_{\mathbf{N}}$  are the MOS transistor conduction constants.

In region III, both  $Q_1$  and  $Q_3$  are in saturation (see Table 5). Equations (29) and (32) yield:

$$I_{ds} = K_p (|V_Q^* - V_{ss}| - |V_{tp}|)^2 = K_N (V_Q^* - V_{tn})^2$$

namely

$$\left(\frac{K_{p}}{K_{N}}\right)\left(\left|\frac{V_{Q}^{*}}{V_{ss}}-1\right|-\frac{|V_{tp}|}{|V_{ss}|}\right)^{2}=\left(\frac{V_{Q}^{*}}{|V_{ss}|}-\frac{|V_{tn}|}{|V_{ss}|}\right)^{2} \tag{36}$$

Define:

$$\beta = \frac{K_p}{K_N} \tag{37}$$

$$\alpha_{n} = \frac{V_{th}}{V_{ss}} \tag{38}$$

$$\alpha_{p} = \frac{|V_{tp}|}{|V_{ss}|} \tag{39}$$

Equation (36) becomes:

$$\sqrt{\beta}(0.5 - \alpha_{p}) = (0.5 - \alpha_{n})$$

(40)

where  $V_Q^* = \frac{1}{2} V_{ss}$  was assumed.

Equation (40) represents a family of straight lines in the  $\alpha_n$ ,  $\alpha_p$  plane with slope  $\sqrt{\beta}$  as parameters. Rapp (21) and Cobbold (3) gave the curve in their works. An easy way to satisfy equation (40) is when  $V_{tn} = V_{tp}$  and  $K_p = K_N$ . An interesting condition is that if  $\alpha_p = \alpha_n = 0.5$  equation (40) will always hold independent of  $\beta$  value, but this will give a relatively slow dynamic time response as stated by Burns (1).

So far, node voltage  $V_Q$  is considered to be the input to the inverter composed of  $Q_1$  and  $Q_3$ .  $V_{\overline{Q}}$  is considered to be the response, which is exactly the case when writing of "1" is implemented by the cell. The writing of "0" can be analyzed by considering  $V_{\overline{Q}}$  as input to inverter  $Q_2$ ,  $Q_4$  (see Figure 22) and  $V_Q$  as output response, which leads to the same analysis.

During the "read" operation, no change of state is happening in the cell  $(Q_1, Q_2, Q_3, Q_4 \text{ remain in their original state})$ . Only the side of the cell with high

voltage (+  $V_{SS}$ ) will cause current flow in either digit line D or  $\bar{D}$  depending on the state of the cell. If the state is "1",  $V_Q = V_{SS}$  produces current in digit line D, otherwise digit line  $\bar{D}$  will have current flow (see Table 4 and Figure 21).

#### C. CELL DYNAMIC OPERATION

Two different cases will be considered when the cell is in dynamic operation.

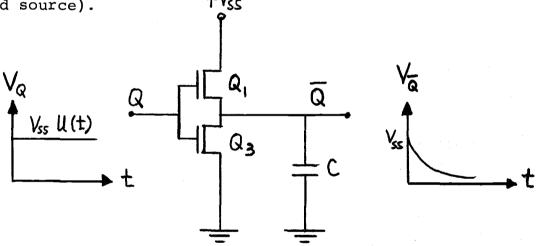

The first case is when a step voltage  $(v_{ss}, u(t))$  is reaching one side (either node Q or node  $\bar{Q}$  in Figure 22) of the cell, the other side is having a voltage change (from  $v_{ss}$  to zero) as a response. This is the situation when writing of either "1" or "0" is taking place in the cell. How long it takes for the response to change from 0.9  $v_{ss}$  to 0.1  $v_{ss}$  is calculated in detail. This amount of time is the minimum time required for a "write" operation. If the input voltage is a time-dependent function, then an analytical closed form solution for the response voltage is quite difficult. Feller (9) used a lumped model to simulate the response through computer analysis, which is a practical way of predicting the response. However, the step response analysis will yield some insight of the factors affecting the write time.

The second case considers the pulsed response of the cell. The maximum switching rate of the cell is determined

from the inverter pair delay time.

## 1. Cell Step Response

In Figure 22 assume  $V_Q(t) = V_{ss}u(t)$ , and  $V_{\overline{Q}}(0) = V_{ss}$ . The inverter in Figure 23 is redrawn in Figure 27 with nodal capacitor between node  $\overline{Q}$  and ground shown. In the actual physical structure the nodal capacitor is the output capacitor of  $Q_1$  and  $Q_3$  (between their source and drain) plus the input capacitance of  $Q_2$  and  $Q_4$  (between their gate and source).

Q<sub>1</sub> p-mos transistor Q<sub>3</sub> n-mos transistor

Figure 27. Inverter with step input

The step voltage will turn off  $Q_1$ , leaving  $Q_3$  on as the only discharging path for capacitor C. The situation is further simplified as shown in Figure 28.

Figure 28. Simplified inverter step response.

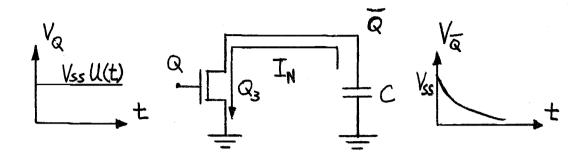

As the discharge process continues,  $V_{\overline{Q}}$  is decreasing from  $V_{ss}$  towards zero.  $Q_3$  operates from saturation  $(V_{\overline{Q}} \geq V_{ss} - V_{tn})$  to non-saturation  $(V_{\overline{Q}} < V_{ss} - V_{tn})$ . Due to changing biasing condition,  $Q_3$  acts like a current valve regulating the discharge current  $I_N$ .

For saturation region, it has:

$$-C\frac{dV_{\overline{Q}}}{dt} = K_{N} \left(V_{ss} - V_{tn}\right)^{2} \tag{41}$$

where equation (32) was referred to. Solving equation (41) for  $V_{\bar{Q}}(t)$  and employing initial condition  $V_{\bar{Q}}(0) = V_{ss}$  yields:

$$V_{\bar{Q}}(t) = V_{ss} - \frac{K_{N}(V_{ss}-V_{tn})^{2}}{C} t$$

(42)

for  $(V_{\bar{Q}} \geqslant V_{ss} - V_{tn})$

Equation (42) indicates a linear decay of  $V_{\overline{Q}}(t)$  before  $t_{0}$ ,

where

$$V_{\overline{Q}}(t_{o}) = V_{ss} - V_{tn}$$

$$= V_{ss} - \frac{K_{N}(V_{ss} - V_{tn})^{2}}{C} t_{o}$$

(43)

hence

$$t_{o} = \frac{c V_{tn}}{K_{N}(V_{ss}-V_{tn})} 2$$

(44)

From  $t_{\Omega}$  and on the binding equation becomes:

$$-C \frac{dV_{\overline{Q}}}{dt'} = K_{\overline{N}} \left( 2(V_{ss} - V_{tn}) V_{\overline{Q}} - V_{\overline{Q}}^{2} \right)$$

$$for (V_{\overline{Q}} < V_{ss} - V_{tn}) and t' = (t - t_{o}) \geqslant 0$$

(45)

Solving equation (45) for  $V_{\overline{Q}}(t')$  is quite difficult; however, the time for  $V_{\overline{Q}}$  decreases to v, namely t'(v) can be solved from equation (45) as:

$$t'(v) = -\int_{V_{ss}-V_{tn}}^{V} \frac{C \, d \, V_{\overline{Q}}}{K_{N} \left( 2(V_{ss}-V_{tn})V_{\overline{Q}}-V_{\overline{Q}}^{2} \right)}$$

$$= (\frac{C}{K_{N}}) \left( \frac{1}{V_{ss}-V_{tn}} \right) \int_{0}^{V_{ss}-V_{tn}-V} \frac{(V_{ss}-V_{tn})d(V_{ss}-V_{tn}-V_{\overline{Q}})}{(V_{ss}-V_{tn})^{2}-(V_{ss}-V_{tn}-V_{\overline{Q}})^{2}}$$

$$= \frac{C}{K_{N}(V_{ss}-V_{tn})} \quad \tanh^{-1} \frac{V_{ss}-V_{tn}-V_{tn}}{V_{ss}-V_{tn}}$$

(46)

where Dwight's integration table (8) was used. Equation (46) is rearranged to be:

$$v(t') = (v_{ss} - v_{tn}) \left[1 - \tanh \frac{K_N(v_{ss} - v_{tn}) t'}{C}\right]$$

(47)

hence

$$V_{\overline{Q}}(t) = (V_{ss} - V_{tn}) \left(1 - \tanh \frac{K_{N}(V_{ss} - V_{tn})(t - t_{o})}{C}\right)$$

for  $t \ge t_{o}$  (48)

Equations (42) and (48) can be written as (refer to equation 38)

$$\frac{V_{\overline{Q}}(t)}{V_{ss}} = 1 - \frac{(1-\alpha_n)^2}{T_N} t$$

for  $t < t_0$  (49)

and

$$\frac{V_{\overline{Q}}(t)}{V_{ss}} = (1-\alpha_n) \left(1-\tanh \frac{(1-\alpha_n)(t-t_0)}{T_N}\right)$$

for  $t \geqslant t_0$  (50)

where defining:

$$T_{N} = \frac{C}{K_{N} V_{SS}}$$

(51)

Let equation (49) equal to 0.9 solve for  $t_{0.9}$  and equation (50) equal to 0.1 solve for  $t_{0.1}$ ; the fall time of  $V_{\overline{Q}}$  can be expressed as:

$$T_{F} = t_{0.1} - t_{0.9}$$