#### AN ABSTRACT OF THE THESIS OF

<u>Jenna Y. Gorecki</u> for the degree of <u>Master of Science</u> in <u>Chemical Engineering</u> presented on <u>June 1, 2016.</u>

Title: <u>Low-temperature</u>, <u>Inkjet-printed p-Type Copper(I) Iodide-based Thin-Film Transistors.</u>

| Abstract approved: |                 |  |

|--------------------|-----------------|--|

|                    | Chih-Hung Chang |  |

Inkjet-printed p-type copper(I) iodide-based TFTs were successfully fabricated. As-printed copper(I) halide semiconductor films, such as CuI, CuBrI, and CuCII, were used as p-type active channel layers for TFTs. The entire process of the TFTs fabrication was maintained under 150 °C, which is compatible with flexible plastic substrates and transparent glass substrate. Various printing temperatures, drop spacing, W/L ratios, and TFT structures were tested in order to find the optimum device properties for p-type copper(I) iodide-based TFT. In addition, inkjet-printed CuI, CuBrI, and CuCII films were characterized to study optical, electrical, and morphological properties. Furthermore, device performance of printed copper(I) iodide-based p-type TFTs was also investigated. Among them, CuI TFTs with SU-8 encapsulation exhibited outstanding p-type transistor behaviours with field-effect mobility as high as 4.36 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and I<sub>on</sub>/I<sub>off</sub> ratio of 10<sup>3.24</sup> on the silicon substrate. Also, CuBrI TFTs resulted in successful p-type transistor behaviours with average

field-effect mobility of  $2.4~\text{cm}^2~\text{V}^{-1}~\text{s}^{-1}$  and  $I_{on}/I_{off}$  ratio of  $10^{1.9}$  on the glass substrates when the molar ratio of CuBr:CuI was 1:1. In addition, CuCII TFTs were successfully fabricated with field-effect mobility as high as  $1.02~\text{cm}^2~\text{V}^{-1}~\text{s}^{-1}$  and  $I_{on}/I_{off}$  ratio of  $10^{0.73}$  on the silicon substrates when the molar ratio of CuCl:CuI was 1:9. The device performances were comparable to reported p-type metal oxide TFTs. This study suggests promising candidates of low-temperature printed p-type TFTs that can be used for complementary inorganic circuits.

©Copyright by Jenna Y. Gorecki June 1, 2016 All Rights Reserved

# Low-temperature, Inkjet-printed p-Type Copper(I) Iodide-based Thin-Film Transistors

by Jenna Y. Gorecki

## A THESIS

submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Master of Science

Presented June 1, 2016 Commencement June 2016

| Master of Science thesis of Jenna Y. Gorecki presented on June 1, 2016                                                                                                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                               |

|                                                                                                                                                                                               |

| APPROVED:                                                                                                                                                                                     |

|                                                                                                                                                                                               |

|                                                                                                                                                                                               |

| Major Professor, representing Chemical Engineering                                                                                                                                            |

|                                                                                                                                                                                               |

|                                                                                                                                                                                               |

| Head of the School of Chemical, Biological, and Environmental Engineering                                                                                                                     |

|                                                                                                                                                                                               |

|                                                                                                                                                                                               |

| Dean of the Graduate School                                                                                                                                                                   |

|                                                                                                                                                                                               |

|                                                                                                                                                                                               |

|                                                                                                                                                                                               |

|                                                                                                                                                                                               |

|                                                                                                                                                                                               |

| I understand that my thesis will become part of the permanent collection of Oregon State University libraries. My signature below authorizes release of my thesis to any reader upon request. |

|                                                                                                                                                                                               |

| Jenna Y. Gorecki, Author                                                                                                                                                                      |

#### ACKNOWLEDGEMENTS

First and foremost, I would like to express my sincere gratitude to my advisor, Prof. Chih-Hung Chang for his support of my M.S. research with patience and enthusiasm. He gave me a lot of insightful advice which always helped me to be motivated and focus on the research. I have been really fortunate to have him as an advisor and it was an amazing experience to work with him.

I am deeply grateful to Dr. Chang-ho Choi, who gave me a lot of advice which helped me tremendously throughout my research. I have been amazingly fortunate to have him as a mentor, and I have learned a lot from him. I deeply appreciate his guidance.

My sincere thanks also goes to Dr. Ki-joong Kim for his advice and comments on my thesis and defense which were really helpful. I really appreciate his enthusiasm and detailed guidance.

I would also like to express my thanks to all of my group members. I am really grateful to have met Michele David who has helped me to get through a lot of difficult times and has always been on my side as an amazing friend. In addition, I deeply appreciate Zhen Fang for his help on instrumental operation training. He helped me a lot to when I first started the research, and I really appreciate all of his effort and patience for me. Also, I really appreciate Yujing Zhang for her help on AFM operations. She spent a great deal of time on my samples which was amazingly generous and helpful. I would like to thank to Yujuan He, Han Mei, Zhongwei Gao,

Dick Chiu, Changqing Pan, Qun Jing, Guoheng Ma and Shujie Li for their support and help.

Most importantly, none of this would have been possible without the love and patience of my family. I deeply appreciate to the love of my life, my husband, Ryan Gorecki for his continuous love and support.

Finally, I appreciate the financial support from AU Optronics that funded the research discussed in this thesis.

# TABLE OF CONTENTS

|    | <u>I</u>                                           | Page |

|----|----------------------------------------------------|------|

| 1. | Introduction                                       | 1    |

|    | 1.1 Metal Oxide Thin-Film Transistors              | 1    |

|    | 1.2 Solution-processed p-Type TFTs                 | 2    |

|    | 1.3 Solution-processed Copper(I) Iodide-based TFTs | 3    |

| 2. | Literature Review                                  | 5    |

|    | 2.1 Vacuum-processed p-type TFTs                   | 5    |

|    | 2.1.1 SnO TFTs                                     | 5    |

|    | 2.1.2 Cu <sub>2</sub> O TFTs                       | 7    |

|    | 2.2 Solution-processed p-type TFTs                 | 9    |

|    | 2.2.1 Cu <sub>2</sub> O TFTs                       | 9    |

|    | 2.2.2 CuO TFTs                                     | . 10 |

|    | 2.2.3 SnO TFTs                                     | . 11 |

|    | 2.2.4 PbS TFTs                                     | . 11 |

| 3. | Materials and Method                               | . 12 |

|    | 3.1 Materials                                      | . 12 |

|    | 3.2 Film Fabrication by Inkjet Printer             | . 12 |

|    | 3.3 Characterization                               | . 14 |

| 4. | Results and Discussion: Copper(I) Iodide TFTs      | . 15 |

|    | 4.1 Characterization of CuI film                   | . 15 |

|    | 4.1.1 Morphology of CuI film                       | . 15 |

|    | 4.1.2 Optical property of CuI film                 | . 18 |

|    | 4.1.3 Crystal structure of CuI film                | . 19 |

|    | 4.1.4 XPS of CuI film                              | . 20 |

|    | 4.1.5 Electrical properties of CuI film            | . 21 |

|    | 4.2 Device performance of CuI TFTs                 | . 21 |

|    | 4.2.1 Effect of printing temperature (RT – 60 °C)  |      |

|    | 4.2.2 Effect of Drop spacing (10 – 40 μm)          | . 24 |

# TABLE OF CONTENTS (continued)

|                                                         | <u>Page</u> |

|---------------------------------------------------------|-------------|

| 4.2.3 Effect of W/L ratios (W/L = 1.4 – 5)              | 26          |

| 4.2.4 Effect of TFT structures (BGTC, BGBC)             | 28          |

| 5. Results and Discussion: Copper (I) Iodide-based TFTs | 29          |

| 5.1 Characterization of CuBrI film                      | 29          |

| 5.1.1 Morphology of CuBrI film                          | 29          |

| 5.1.2 Optical property of CuBrI film                    | 30          |

| 5.1.3 Crystal structure of CuBrI film                   | 31          |

| 5.2 Device Performance of CuBrI TFTs                    | 32          |

| 5.2.1. CuBrI TFTs printed at RT                         | 32          |

| 5.2.2. Effect of molar ratio of CuBrI TFTs              | 33          |

| 5.3 Device Performance of CuCII TFTs                    | 34          |

| 6. Conclusion                                           | 36          |

| Bibliography                                            | 37          |

# LIST OF FIGURES

| <u>Figure</u> <u>Page</u>                                                                                                                                                                                                                                                                                                                                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

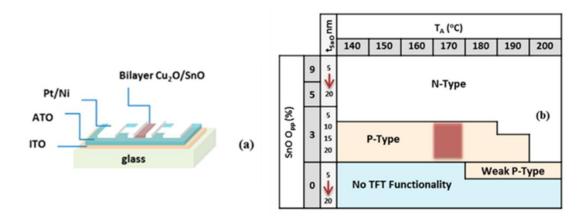

| Figure 1. (a) Schematic diagram of Cu2O/SnO bilayer TFT and (b) the TFT polarity obtained under different oxygen partial pressures (Opp) and annealing temperatures. (Reproduced from [12])                                                                                                                                                                      |

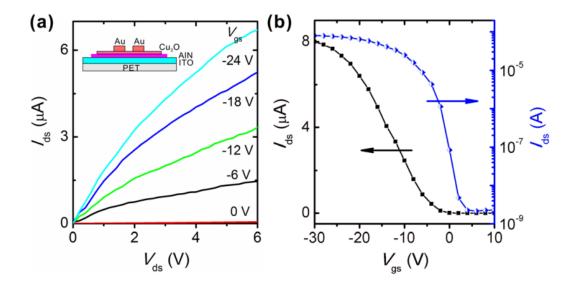

| Figure 2. (a) Drain current-drain voltage (Ids-Vds) characteristics of p-type Cu2O TFT grown on PET. (b) Ids-Vgs plots of the same device at a fixed Vds of þ5 V. Inset in (a) shows the schematic device structure of the Cu2O TFTs. (Adapted from [11]) 8                                                                                                      |

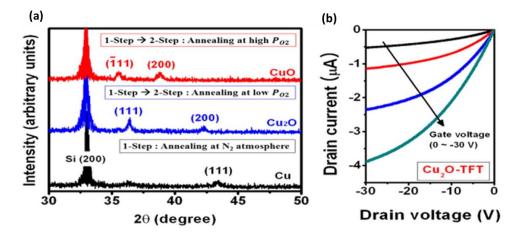

| Figure 3. (a) XRD spectra of copper oxide films as-annealed in N2 atmosphere and two-step annealed under high and low oxygen partial pressures. (b) Output characteristics of copper oxide TFTs annealed at Opp of 0.04 Torr (Adapted from [8])                                                                                                                  |

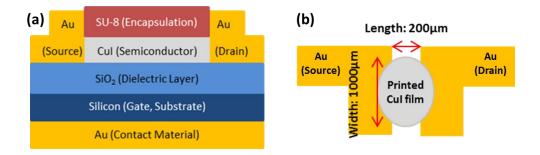

| Figure 4. (a) The schematic diagram of CuI TFT on the SiO2/Si substrate, (b) The scaled schematic diagram of printed CuI film with gold source/drain conductors. The width and length of channel layer of CuI TFT are $1000~\mu m$ and $200~\mu m$ , respectively                                                                                                |

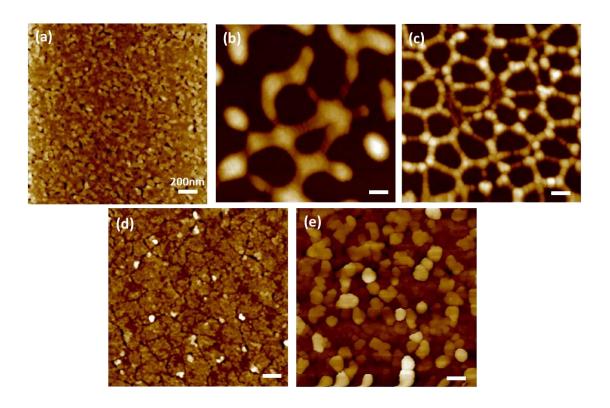

| Figure 5. AFM images of the printed CuI films on SiO <sub>2</sub> /Si substrate printed at (a) RT, (b) 30 °C (c) 40 °C, (d) 50 °C, and (e) 60 °C                                                                                                                                                                                                                 |

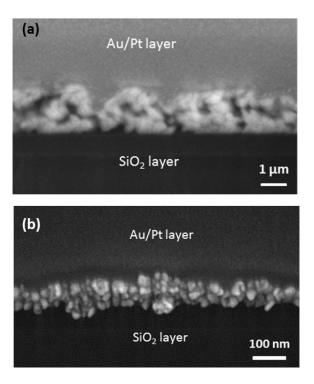

| Figure 6. Cross-sectional SEM images of CuI film printed on SiO <sub>2</sub> /Si substrate (a) at RT and (b) at 60 °C                                                                                                                                                                                                                                            |

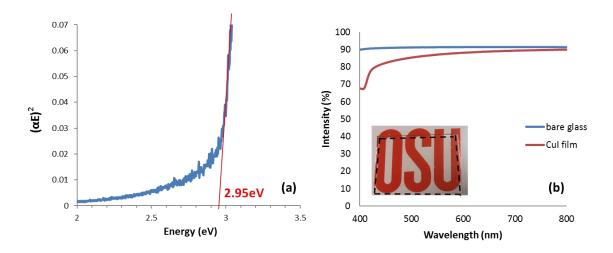

| Figure 7. (a) Calculated band gap and (b) transmittance spectrum of spin-coated CuI film at RT                                                                                                                                                                                                                                                                   |

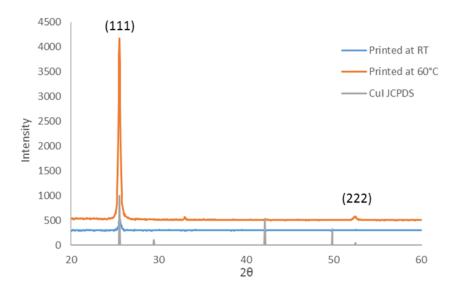

| Figure 8. XRD patterns of CuI films printed at RT and 60 °C. The printed CuI films were dried at 120 °C for 30min after printing                                                                                                                                                                                                                                 |

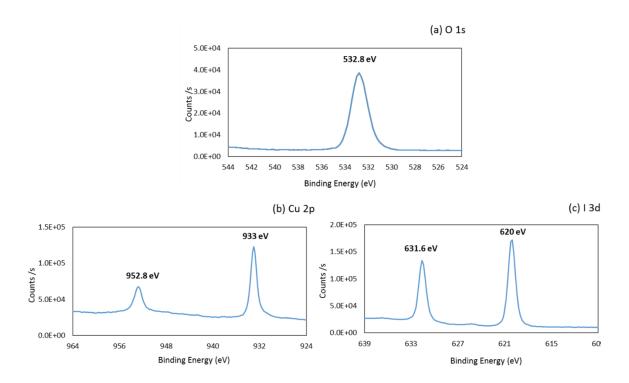

| Figure 9. (a) O 1s, (b) Cu 2p, and (c) I 3d XPS spectra of printed CuI film at RT. The film was dried at 120 °C for 30 min after printing                                                                                                                                                                                                                        |

| Figure 10. (a) The drain current-drain voltage (ID-VD) output characteristics (b) drain current-gate voltage (ID-VG) transfer characteristics (ID plotted logarithmically) at VDS = -40 V of RT printed CuI TFT on the SiO2/Si substrate. (c) ID-VD output characteristics (d) ID-VG transfer characteristics of 60 °C printed CuI TFT on the SiO2/Si substrate. |

| Figure 11. (a) Average field effect mobility and (b) average Log(on/off ratio) data of CuI TFTs printed at various substrate temperature from RT to 60 °C (with standard deviation error bars)                                                                                                                                                                   |

# LIST OF FIGURES (continued)

| <u>ragure</u>                                                                                                                                                                                                                                                                                                              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

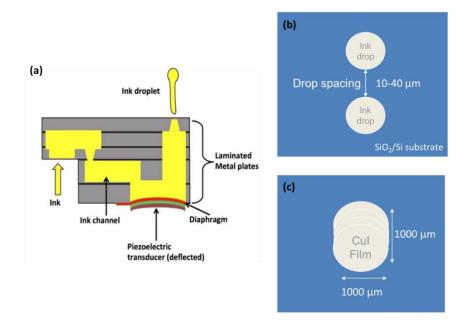

| Figure 12. Schematic diagram of (a) piezoelectic inkjet printer (adapted from [6]), (b) exaggerated illustration of drop spacing, the distance between printed droplets, and (c) realistic illustration of printed CuI film with the overlapped printed droplets of which drop-spacing is in the range from 10 μm to 40 μm |

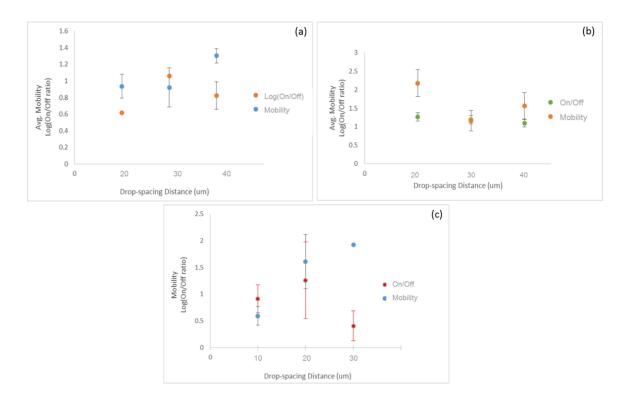

| Figure 13. Effect of drop spacing in piezoelectric inkjet printer on mobility and $log(I_{on}/I_{off})$ of p-type CuI TFTs printed at (a) 30 °C, (b) 50 °C, and (c) 60 °C 25                                                                                                                                               |

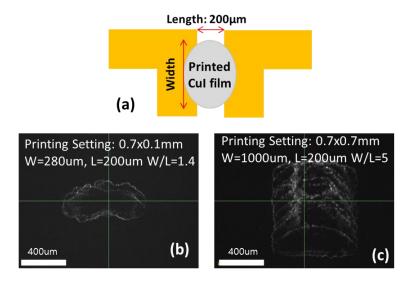

| Figure 14. (a) Schematic diagram of printed CuI channel layer and deposited gold as a source and drain with defined channel width and length (b) optical top-view of printed CuI film at 60 °C with W=280 $\mu$ m, L=200 $\mu$ m, and (c) with W=1000 $\mu$ m, L=200 $\mu$ m.                                              |

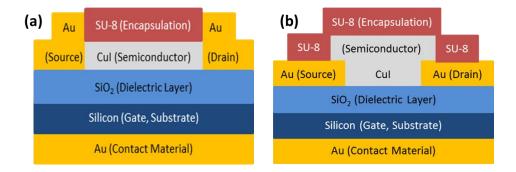

| Figure 15. P-type CuI TFT with (a) Bottom-Gate Top-Contact (BGTC) structure, and (b) Bottom-Gate Bottom-Contact (BGBC) structure                                                                                                                                                                                           |

| Figure 16. AFM images of CuBrI film printed at RT of (a) $2x2~\mu m$ , (b) $10x10~\mu m$ on PECVD-SiO <sub>2</sub> /Si substrates; (c) $2x2~\mu m$ , (d) $10x10~\mu m$ on thermally-grown SiO <sub>2</sub> /Si substrate.                                                                                                  |

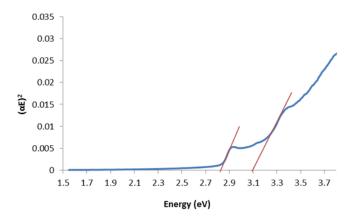

| Figure 17. Estimated bandgap of spin-coated CuBrI film on soda lime glass at RT. The spin-coated film was dried at 120 °C for 30 min before measurement                                                                                                                                                                    |

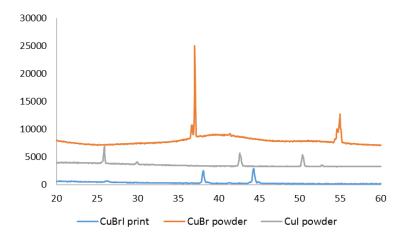

| Figure 18. XRD patterns of CuBrI film printed at RT, CuBr powder, and CuI powder. The printed CuBrI films were dried at 120 °C for 30min after printing                                                                                                                                                                    |

| Figure 19. (a) The drain current-drain voltage $(I_D-V_D)$ output characteristics (b) drain current-gate voltage $(I_D-V_G)$ transfer characteristics $(I_D$ plotted logarithmically) at $V_D = -40$ V of CuBrI TFT printed at RT on the PECVD- SiO <sub>2</sub> /glass substrate                                          |

| Figure 20. (a) The drain current-drain voltage (ID-VD) output characteristics (b) drain current-gate voltage (ID-VG) transfer characteristics (ID plotted logarithmically) at VDS = -40 V of CuClI TFT printed at 60 °C on the TG- SiO2/glass substrate, when CuCl:CuI ratio was 1:9.                                      |

|                                                                                                                                                                                                                                                                                                                            |

# LIST OF TABLES

| <u>Table</u>                                                                                                                         | <u>Page</u>          |

|--------------------------------------------------------------------------------------------------------------------------------------|----------------------|

|                                                                                                                                      |                      |

| Table 1. Electrical properties of printed CuI film at RT on soda li                                                                  | · ·                  |

| Table 2. Average mobility and on/off ratio data of p-type CuI TF which were fabricated with various drop spacing (10 - 30 μm) an 5). | d W/L ratios (1.4 -  |

| Table 3. Device performance of CuBrI TFTs for various molar ra<br>PECVD-SiO2/glass and TG-SiO2/Si substrate printed at RT and        | 60 °C, respectively. |

# 1. Introduction

#### 1.1 Metal Oxide Thin-Film Transistors

In recent years, metal based oxide thin-film transistors (TFTs) have attracted increasing attention as a promising candidate to replace the conventional amorphous hydrogenated silicon (a-Si:H) TFTs due to their superior properties such as higher mobility and lower off-state current. [1], [2] Although low electronic properties of a-Si:H semiconductor (carrier mobility < 1 cm<sup>2</sup>/Vs) were sufficient for Liquid Crystal Displays application, the switching elements for Active-Matrix Organic Light-Emitting Diode (AMOLED) require higher electronic properties, which a-Si:H semiconductor cannot achieve. Metal oxide semiconductors and low-temperature polycrystalline Si (poly-Si) have been extensively studied recently in order to replace a-Si:H for AMOLED display application. Although poly-Si TFTs can achieve high mobility and on/off ratio, they have device uniformity issues due to the grain boundaries in the film. Amorphous metal oxide semiconductors have novel and uniform device performances (carrier mobility ~ 1-100 cm<sup>2</sup>/Vs) due to the lack of grain boundaries, unlike in the poly-Si TFTs. [1] Various oxide semiconducting materials from binary (ZnO, In<sub>2</sub>O<sub>3</sub>, SnO<sub>2</sub>) to quaternary (IGZO, IZTO) oxide compounds have been researched for the TFTs application. [3]-[5] However, most of the reported oxide TFTs have been mainly focused on n-type semiconductors and only a few studies have been reported about p-type oxide semiconductors TFTs. Since all-oxide electronics will enable high charge carrier mobility with low-cost and scalable processes, developing p-type oxide semiconductors is still necessary. Therefore, finding the p-type semiconductor candidates, which have high electronic

properties comparable to n-type counterparts, would be a crucial step for entering the next generation of electronics applications.

# 1.2 Solution-processed p-Type TFTs

Recently, solution-processed fabrication of TFTs, which enables a simple and low-cost fabrication, has extensively been introduced as a promising alternating method to conventional vacuum processes. Printing technology is one of the most promising solution-based techniques that facilitates a direct writing of materials, reduction of chemical waste, and good reproducibility with a high-resolution scale.[6] Since Lee et al. [7] reported the low-cost and general way of fabricating solutionprocessed metal oxide semiconductors, extensive research has been conducted on manufacturing solution-processed metal oxide TFTs. In addition, developing solution-fabricated p-type semiconductors that have comparable properties as their ntype counterparts will enable the development of complementary metal-oxidesemiconductor circuits as well as p-n diodes via flexible and controllable solutionbased manufacturing processes. [8]–[10] P-type organic semiconducting materials have been studied for a long time but they have limitations due to low mobility and their instability in ambient air.[10] Also, SnO and Cu<sub>2</sub>O have been studied extensively as p-type channel layers of TFTs mainly by vacuum-processed fabrications. Yao et al. [11] reported p-type Cu<sub>2</sub>O TFTs on flexible polyethylene terephthalate substrate with field effect mobility of ~2.40 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and on/off ratio of  $\sim 3.96 \times 10^4$  by magnetron sputtering at room temperature. Al-Jawhari et al. [12] reported Cu<sub>2</sub>O/SnO bilayer p-type TFTs. The SnO film was sputtered as an active

channel layer and the  $Cu_2O$  film was sputtered as a capping layer onto the tin oxide layer. The optimum bilayer TFT was fabricated with 10 nm of  $Cu_2O$  and 15 nm of SnO with the field effect mobility of  $\sim 0.66$  cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and on/off ratio of  $\sim 1.5 \times 10^2$ . In addition, solution-processed p-type metal oxide TFTs have also been reported several times. Kim et al. [8] reported sol-gel spin coated cuprous oxide ( $Cu_2O$ ) TFTs with field effect mobility of 0.16 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and on/off ratio of  $\sim 10^2$ . Also, Pattanasattayavong et al. [9] reported spray pyrolysis fabricated  $Cu_2O$  TFTs with field effect mobility of  $10^{-4}$  -  $10^{-2}$  cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and on/off ratio of  $4 \times 10^3$ . Despite the recent extensive research on p-type oxide TFTs, the field-effect mobility is still not satisfactory.

# 1.3 Solution-processed Copper(I) Iodide-based TFTs

Copper(I) halides (CuI, CuBr, and CuCl) have been studied as good candidates for p-type semiconductors especially in solar cell applications. [13] While CuI, CuBr, and CuCl have three different crystalline phases,  $\alpha$ ,  $\beta$ , and  $\gamma$ ,  $\gamma$ -copper(I) halides semiconductor exhibit p-type characteristics. The copper halide film has several advantages as an active channel layer for p-type TFTs, such as high transparency in the visible wavelengths (Eg  $\sim 2.9-3.4$  eV) and a simple film preparation method.[13] Also, due to their intrinsic p-type semiconductor properties, copper(I) iodide-based TFTs do not require an oxidation step, which means no annealing step is needed. Therefore, fabricating TFTs with copper(I) halide channel layer enables the overall process temperature to be reduced significantly; the entire process of the TFTs fabrication is maintained under 150 °C in this research. Considering low-temperature

low-cost solution-processes have the potential to be a mainstream fabricating method which will replace conventional high-cost vacuum processes, Copper(I) halides are the ideal p-type semiconductor candidates for future electronics applications. In this work, we demonstrate solution-processed Copper(I) Iodide-based p-type TFTs for the first time.

#### 2. Literature Review

# 2.1 Vacuum-processed p-type TFTs

Most of reported p-type oxide TFTs were mainly fabricated by vacuum-based techniques, such as radio-frequency (RF) magnetron sputtering and pulsed laser deposition. [14], [15] While most of reported  $Cu_2O$  TFTs deposited by vacuum-processed techniques showed low hole mobility ( $< 1 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ ) and on/off ratio, most of vacuum-processed SnO TFTs showed closer or above  $1 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ , which indicated that SnO could be more promising than  $Cu_2O$  for p-type TFT application. [16]

#### 2.1.1 SnO TFTs

There has been a lot of efforts to control the stoichiometry of metal to oxide ratio for metal oxide semiconductor. Several studies reported that optimizing the annealing conditions, such as oxygen partial pressure or annealing time, was crucial to deposit continuous and pure p-type SnO semiconductor layer.

Fortunato et al. [17] showed the effect of oxygen partial pressure ( $O_{pp}$ ) during annealing on forming p-type SnO film. It was found that metallic  $\beta$ -Sn was the dominate phase at  $O_{pp}$  < 5%, and p-type polycrystalline film with  $\alpha$ -SnO $_x$  and  $\beta$ -Sn were formed when 5% <  $O_{pp}$  < 15%. Also, n-type SnO $_2$  film was formed when  $O_{pp}$  > 15%. They successfully fabricated SnO $_x$  (x<2) TFTs with the field-effect mobility ( $\mu_{FE}$ ) of 1.1-1.2 cm $^2$  V $^{-1}$  s $^{-1}$  and on/off ratio ( $I_{on}/I_{off}$ ) of 10 $^3$ . The film was deposited by RF magnetron sputtering at room temperature (RT) and annealed at 200 °C for 1 hr with 0.2 Pa of Ar and O $_2$ .

Zhong et al. [18] investigated the crystalline structure and composition of the channel layer film while varying oxygen annealing time in order to find an optimized annealing condition. The channel layer was deposited by sputtering at RT and post-annealed at 300 °C with oxygen pressure of 0.3 Torr. While as-deposited film showed n-type Sn-dominated film with high electron concentration, the 30 min annealed film showed p-type characteristics, and the drain current was further improved for 45 min annealed film. Also, they found that the amorphous as-deposited film changed to polycrystalline film after annealing for 30 min. They fabricated p-type SnO TFTs with the  $\mu_{FE}$  of 3.24 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and  $I_{on}/I_{off}$  larger than  $I_{on}$ .

In addition, Cu<sub>2</sub>O/SnO bilayer p-type TFTs was reported by Al-Jawhari et al.[12]. SnO film was sputtered as an active channel layer, and Cu<sub>2</sub>O film was sputtered as a capping layer onto the tin oxide layer. It was suggested that the Cu<sub>2</sub>O capping layer improved the electrical properties of the TFT by reducing the surface leakage current as well as enhancing the oxidation of SnO layer. While the oxygen partial pressure (O<sub>pp</sub>) during deposition of Cu<sub>2</sub>O kept as 10 %, the O<sub>pp</sub> of SnO deposition varied to find the optimum condition for TFT application. As shown in Figure 3, the bilayer device exhibited n-type at high O<sub>pp</sub> of SnO, when O<sub>pp</sub> was 5 % and 9 %, since the extra oxygen from Cu<sub>2</sub>O layer influenced the transformation of SnO to Sn<sub>2</sub>O. In addition, 3% of O<sub>pp</sub> of SnO was required to achieve p-type transistor behaviour. Also, TFT device with 0% of O<sub>pp</sub> of SnO was found to have no TFT functionality, since the oxygen delivered from Cu<sub>2</sub>O capping layer was not enough to convert Sn to SnO film. The optimum bilayer TFT was fabricated with 10 nm of

$Cu_2O~(10\%~O_{pp})~and~15~nm~of~SnO~(3~\%~O_{pp})~with~the~\mu_{FE}~of~\sim\!\!0.66~cm^2~V^{-1}~s^{-1}~and$   $I_{op}/I_{off}~of~\sim\!\!1.5\times10^2.$

Figure 1. (a) Schematic diagram of Cu2O/SnO bilayer TFT and (b) the TFT polarity obtained under different oxygen partial pressures (Opp) and annealing temperatures. (Reproduced from [12]).

#### 2.1.2 Cu<sub>2</sub>O TFTs

Yao et al. [11] demonstrated that the growth temperature affected the microstructure and electrical transport properties of Cu<sub>2</sub>O films by changing the sputtering temperature from RT to 500 °C. They found that the Cu<sub>2</sub>O film that was sputtered at RT had good electrical performance. They achieved superior transfer performance of p-type Cu<sub>2</sub>O TFTs on flexible polyethylene terephthalate (PET) substrate with  $\mu_{FE}$  of ~2.40 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and  $I_{on}/I_{off}$  of ~3.96 × 10<sup>4</sup> by magnetron sputtering at RT without post-annealing.

Figure 2. (a) Drain current-drain voltage (Ids-Vds) characteristics of p-type Cu2O TFT grown on PET. (b) Ids-Vgs plots of the same device at a fixed Vds of p5 V. Inset in (a) shows the schematic device structure of the Cu2O TFTs. (Adapted from [11])

Figueiredo et al.[19] investigated the impact of sputtering  $O_{pp}$  on forming  $Cu_xO$  film. They deposited  $Cu_xO$  film by RF magnetron sputtering, while varying the  $O_{pp}$  from 0% to 100%. They showed that a metallic Cu film was formed at  $O_{pp}$  was 0%, and was transformed to  $Cu_2O$  phase when  $O_{pp}$  was 9%. Also, CuO phase was formed when  $O_{pp}$  was 25% and 50%. They fabricated p-type TFT with  $Cu_xO$  film, deposited when  $O_{pp}$  was 9%, had  $\mu_{FE}$  of  $7x10^{-3}$  cm<sup>2</sup>  $V^{-1}$  s<sup>-1</sup> and  $I_{on}/I_{off}$  of  $10^3$ .

Nam et al. [20] demonstrated that the device performance of Cu<sub>2</sub>O TFTs was substantially affected by the active layer thickness. They varied the film thickness from 15nm to 155 nm in order to investigate optical, structural, and electrical properties of the TFTs. They concluded that 45 nm was optimum film thickness since the device exhibited the cleanest transfer function with small subthreshold slope.

### 2.2 Solution-processed p-type TFTs

Significant progress of device performance of solution-based p-type oxide TFTs has been made recently, some of which are comparable with the vacuum-based p-type oxide TFTs performance. The solution-processed technique enables simple and low cost fabrication and it has a potential to replace the conventional vacuum-processed fabrication.

#### 2.2.1 Cu<sub>2</sub>O TFTs

Kim et al. [8] successfully fabricated sol-gel spin coated cuprous oxide (Cu<sub>2</sub>O) TFTs with Cu(II) acetate as a metal cation precursor. As-coated film went through two-step annealing process, first  $N_2$  annealing at 400 °C for 30 minutes and then  $O_2$  annealing at 700 °C for 30 minutes, in order to improve the morphology of the film.  $N_2$  annealing before the oxidation step helped to improve the uniformity and continuity of the film, which is favourable as a channel layer of TFT application. Also, they showed that the TFT performance was also affected by the oxygen partial pressure ( $O_{pp}$ ) in the second step of annealing. While uniform Cu<sub>2</sub>O thin film was formed under low oxygen partial pressure ( $O_{pp}$  = 0.04 - 0.2 Torr), CuO as well as Cu<sub>2</sub>O were formed as a rough film with many voids at higher oxygen partial pressure ( $O_{pp}$  = 0.9 Torr). They fabricated p-type Cu<sub>2</sub>O TFT with  $\mu_{FE}$  of 0.16 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and  $I_{on}/I_{off}$  of ~10<sup>2</sup> of which annealed at  $O_{pp}$  of 0.04.

Figure 3. (a) XRD spectra of copper oxide films as-annealed in N2 atmosphere and two-step annealed under high and low oxygen partial pressures. (b) Output characteristics of copper oxide TFTs annealed at Opp of 0.04 Torr (Adapted from [8]).

Yu et al. [21] fabricated spin-coated Cu<sub>2</sub>O TFTs with one-step vacuum annealing, in order to effectively transform CuO into Cu<sub>2</sub>O. They tested different annealing temperature from 400 °C to 700 °C. It was found that the grain size and surface roughness of the films increased as annealing temperature increased. They found that 600 °C is the optimum annealing temperature for TFT application. They reported the device performance of the spin-coated Cu<sub>2</sub>O TFTs as  $\mu_{FE}$  of 0.29 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and  $I_{on}/I_{off}$  of  $1.6 \times 10^4$ .

#### 2.2.2 CuO TFTs

Jang et al. [22] fabricated solution-processed p-type CuO TFTs as well as Cu2O TFTs using a sol-gel route. They deposited copper (II) acetate precursor by sol-gel route and sintered at various temperature from 200-500 °C. It was found that Cu was formed when sintered at 200 and 300 °C, while mixture of Cu, Cu<sub>2</sub>O, and CuO were

formed at 400 °C. Pure CuO film was formed when sintered at 500 °C for more than 30 minutes. The author successfully fabricated p-type Cu2O TFTs, after sintering at 200 C for 4hr, as well as p-type CuO TFTs, sintering at 400C for 1hr. The resulting p-type CuO and Cu<sub>2</sub>O TFTs exhibited  $\mu_{FE}$  of 0.01 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and 2x10<sup>-3</sup> cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> respectively, and  $I_{on}/I_{off}$  of ~10<sup>3</sup>.

#### 2.2.3 SnO TFTs

Okamura et al. [23] fabricated spin-coated SnO TFTs which achieved  $\mu_{FE}$  of 0.13 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and  $I_{on}/I_{off}$  of  $10^{1.9}$ . They tested various precursor (SnCl<sub>2</sub>·2H<sub>2</sub>O in methanol) concentration from 0.05-0.5 M and various post-annealing conditions from 200-600 °C in order to find the optimum condition. It was found that SnO crystallites monotonically grew in the temperature range of 300-450 °C, while SnO began to decompose into Sn and SnO<sub>2</sub> at 500 °C, and completely decomposed at 600 °C. It was found that precursor concentration of 0.1 M and post-annealing temperature of 450 °C were the optimum condition for fabricating transistors that demonstrated superior performance.

#### 2.2.4 PbS TFTs

Carrillo-Castillo et al. [24] fabricated PbS TFTs by chemical bath deposition. While as-deposited TFT showed channel mobility of ~0.09 cm<sup>2</sup>/Vs, the mobility for devices annealed at 150 °C increased to ~0.14 cm<sup>2</sup>/Vs.

# 3. Materials and Method

#### 3.1 Materials

SiO<sub>2</sub>/Si substrates were used to fabricate Copper(I) Iodide-based TFTs. The substrate has a gold (Au) layer of 100 nm thickness as a contact layer sputtered on silicon substrate. SiO<sub>2</sub> layer of 100nm thickness was thermally grown on the other side of silicon substrate as a dielectric layer. All of the substrates were treated using oxygen plasma cleaning prior to the deposition. Copper(I) iodide (γ-CuI, anhydrous, 99.995%), copper(I) bromide (99.999%, Metal basis), and copper(I) chloride (>=99.995%) were purchased from Sigma-Aldrich. A solvent of acetonitrile (HPLC>99.9%) was purchased from Fisher Scientific. Also, SU-8 was purchased from Micro Chem. 0.05 M CuI, 0.05M Cu(Br, I) (with various molar ratio of CuBr: CuI), and 0.05M Cu(Cl, I) (with various molar ratio of CuCl: CuI) solutions were sonicated for 30 min and filtered with syringe filter (Nonsterile, PTFE 25mm x 0.20um) purchased from VWR. The resulting precursor solution served as a printing ink without any additives. As-printed CuI, Cu(Br, I), and Cu(Cl, I) films were dried at 120 °C for 30 minutes and SU-8 was applied on it in order to prevent moisture from reacting with the channel layer.

## 3.2 Film Fabrication by Inkjet Printer

Piezoelectric inkjet printer (Dimatix DMP-2831, Fujifilm) was used to manufacture the CuI, Cu(Br, I), and Cu(Cl, I) films. The dimension of the printed film was controlled by software installed in the printer. The CuI, Cu(Br, I), and Cu(Cl, I) films were printed on SiO<sub>2</sub>/Si substrates, which was oxygen plasma treated

enabling the surface to be hydrophilic. The temperature of substrates while printing varied from RT, 30 °C, 40 °C, 50 °C, to 60 °C in order to investigate the optimized condition. As-printed film was placed on a hot plate set to 120 °C for 30 minutes, allowing solvent to evaporate. The as-printed films were able to be converted into dense and uniform films after simply drying at 120 °C. A gold layer of 50 nm thickness then was deposited as source and drain by thermal evaporator using a shadow mask for patterning. The active channel layer was defined as 1000 µm and 200 µm for width and length, respectively (Figure 4b). All investigated TFTs are fabricated in the described bottom gate bottom contact structure (Figure 4a). After depositing source and drain, the device was placed on a hot plate at 150 °C for 30 minutes in order to get rid of moisture that might have remained in the CuI, Cu(Br, I), and Cu(Cl, I) films. Then, SU-8 was applied on the printed CuI, Cu(Br, I), and Cu(Cl, I) area as an encapsulation layer in order to prevent moisture and impurities from contacting the channel layer, which helps to improves device performance.

Figure 4. (a) The schematic diagram of Cul TFT on the SiO2/Si substrate, (b) The scaled schematic diagram of printed Cul film with gold source/drain conductors. The width and length of channel layer of Cul TFT are 1000 μm and 200 μm, respectively.

#### 3.3 Characterization

Optical, electrical, and morphological properties of CuI films were investigated. The cross-sectional morphology of the CuI films was characterized by scanning electron microscopy (SEM, FEI Helios 650). Atomic force microscope (AFM, Veeco Nanoscope digital instruments) was employed to analyze the surface morphology and roughness of the films. The films were characterized by X-ray diffraction (XRD, Bruker D8 discover) to investigate the crystalline structure. The optical properties of the films were studied using UV-vis spectroscopy (Jasco, V-670 Spectrophotometer). For the transmittance measurement, CuI film was deposited on bare soda lime glass substrate. Device properties of TFTs, such as output characteristics (I<sub>D</sub>-V<sub>D</sub>), mobility, and transfer characteristics (I<sub>D</sub>-V<sub>G</sub>, on/off ratios), of encapsulated CuI TFTs were measured using an Agilent Technologies E5270B Semiconductor Parameter Analyzer under ambient conditions.

# 4. Results and Discussion: Copper(I) Iodide TFTs

#### 4.1 Characterization of CuI film

Inkjet-printed CuI film on SiO<sub>2</sub>/Si substrate was characterized by AFM, SEM, and XRD (Figures 5, 6, and 8). Electrical properties of the films were studied by using Hall Effect measurement (Table 1). CuI solution was also spin-coated on a soda lime glass substrate for analyzing band gap (Figure 7).

#### 4.1.1 Morphology of CuI film

CuI film was printed on a SiO<sub>2</sub>/Si at RT (~21°C), 30 °C, 40 °C, 50 °C, and 60 °C; while the temperature of the CuI ink in the cartridge was kept at RT. The AFM images (Figure 5) showed different CuI forming at various temperatures of substrates.

Printed CuI film at RT showed uniformly distributed small grains of ~20 nm with nano-holes, which traps charge carriers resulting degrading the performance of transistors when applied as a channel layer (Figure 5a). In order to reduce the voids in the film, various printing temperatures were tested. When the film printed at 30 °C, partial coffee-ring pattern was formed while increasing the size of voids drastically, leading to form discontinuous film (Figure 5b). As the printing temperature increased to 40 °C, the size of the voids decreased, and the film became more continuous while forming the network of coffee-ring pattern (Figure 5c). It was inferred that Marangoni flow, which moved the interior particles toward to edge of the film, induced to form coffee ring pattern when the printing temperature was between RT and 40 °C. As printing temperature increased to 50 °C, the film became denser with a few cracks and voids (Figure 5d). Finally, the CuI film that was deposited at 60 °C had the densest and most continuous film without any voids (Figure 5e). It was inferred that

when the printing temperature was higher than 50 °C, the fast evaporation helped to form crystallization faster while overcoming Marangoni flow effect. It was found that dense and continuous film with larger grains were formed at printing temperature between 50 °C and 60 °C. The printing temperature higher than 60 °C were not tested due to the limitation of the printer capacity; however, the thicker film is expected to be form at higher temperature which is not desirable for TFT application.

Figure 5. AFM images of the printed CuI films on SiO $_2$ /Si substrate printed at (a) RT, (b) 30 °C (c) 40 °C, (d) 50 °C, and (e) 60 °C.

Cross-sectional SEM image of printed CuI films was investigated by Helios SEM using a milling technique with a Focused Ion Beam (FIB). Figure 6 shows the cross-sectional SEM images of CuI films printed at RT and 60 °C. As-printed CuI films were annealed at 120 °C for 30 minutes in ambient air and coated with a gold/platinum protective layer. The CuI films were milled with an FIB for cross-sectional morphology investigation. Printed CuI film at RT had a highly porous film with thickness of ~1500 nm. Printed CuI film at 60 °C formed a free-void densely packed film with thickness of ~150 nm. It was inferred that the higher temperature formed more uniform and continuous film while suppressing creating voids. This result indicates that at printing temperature as high as 60 °C, the fast evaporation helped me form crystalline faster resulting in continuous and dense film, which is good agreement with AFM results.

Figure 6. Cross-sectional SEM images of Cul film printed on SiO<sub>2</sub>/Si substrate (a) at RT and (b) at 60 °C.

## 4.1.2 Optical property of CuI film

The optical properties of spin-coated CuI film was investigated by UV-Vis spectroscopy. CuI film was spin-coated at RT on soda lime glass and was dried at 120 °C for 30 minutes before measuring the optical properties. The bandgap was expected to be ~2.95 eV, indicating the transparency in the visible wavelengths (Figure 7a). The expected bandgap of CuI film was smaller than the widely known value (~3.1 eV) [13]. Similar band gap value was reported for a spray-coated CuI film (~2.97 eV) [25]. Also, the film had 70~90% transmittance in the visible range (Figure 7b), which also elucidated the transparency of CuI film.

Figure 7. (a) Calculated band gap and (b) transmittance spectrum of spin-coated Cul film at RT.

# 4.1.3 Crystal structure of CuI film

CuI film printed on SiO<sub>2</sub>/Si substrates at RT and 60 °C were used for XRD analysis. It was found that the film formed preferably with (111) crystal plane (Figure 8), which match with the reported results for spray-coated CuI film [25] and spin-coated CuI film [26]. The increased intensity of the peak for the CuI film printed at 60 °C, compared to the peak for the CuI film printed at RT, indicates that the crystallinity was enhanced at higher printing temperature.

Figure 8. XRD patterns of CuI films printed at RT and 60 °C. The printed CuI films were dried at 120 °C for 30min after printing.

#### 4.1.4 XPS of CuI film

X-ray photoelectron spectroscopy of CuI film was measure in order to confirm the oxidation state of the film (Figure 9). O 1s spectra had a peak at 532.8 eV which showed that all oxygen can be accounted for by bonds with Si and/or Carbon; in other words, there is no evidence for oxidized Cu species on the film. While I 3d spectra showed two peaks at 620eV and 631.6 eV, Cu 2p spectra showed two peaks at 933 eV and 952.8 eV. The asymmetry on the low binding energy side of the Cu 2p<sub>3/2</sub> peak was due to the overlapping I 3p<sub>1/2</sub> signal [27].

Figure 9. (a) O 1s, (b) Cu 2p, and (c) I 3d XPS spectra of printed Cul film at RT. The film was dried at 120 °C for 30 min after printing.

#### 4.1.5 Electrical properties of CuI film

Table 1. Electrical properties of printed CuI film at RT on soda lime glass substrate.

| Electrical properties | Resistivity [Ω cm] | Conductivity $[\Omega \text{ cm}]^{-1}$ | Avg. Hall Coeff. | Hall mobility [cm²/Vs] |

|-----------------------|--------------------|-----------------------------------------|------------------|------------------------|

| Results               | 0.12               | 8.99                                    | 1.22 (p-type)    | 11.2                   |

Table 1 shows electrical properties of printed CuI film at RT on soda lime glass substrates. The result demonstrates that the printed CuI film possesses the p-type nature with average Hall coefficient of 1.22. These results showing consistent electrical properties clearly indicate that the continuous and dense CuI film was successfully fabricated via inkjet printing technique.

## 4.2 Device performance of Cul TFTs

# 4.2.1 Effect of printing temperature (RT – 60 °C)

Inkjet-printed CuI film was used as an active channel layer for fabricating TFT devices. The Bottom-Gate Top-Contact (BGTC) TFT structure was fabricated. Device performances of the CuI TFT improved dramatically after the SU-8 encapsulation, showing an excellent gate modulation, saturated drain current at high drain voltage, and less off-state current.

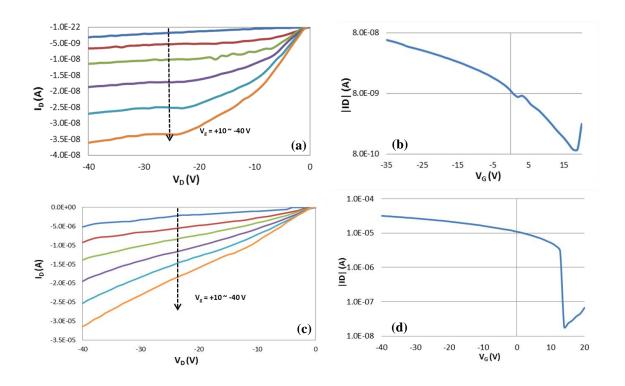

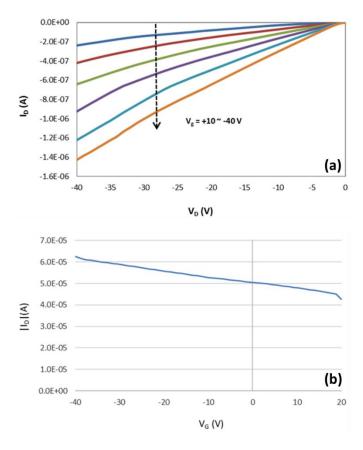

Figure 10. (a) The drain current-drain voltage (ID-VD) output characteristics (b) drain current-gate voltage (ID-VG) transfer characteristics (ID plotted logarithmically) at VDS = - 40 V of RT printed Cul TFT on the SiO2/Si substrate.

(c) ID-VD output characteristics (d) ID-VG transfer characteristics of 60 °C printed Cul TFT on the SiO2/Si substrate.

Figure 10 shows the drain current-drain voltage ( $I_D$ - $V_D$ ) output characteristics and the drain current-gate voltage ( $I_D$ - $V_G$ ) transfer characteristics of CuI TFTs printed at RT and 60 °C, respectively. Both transistors that were fabricated at RT and 60 °C exhibited great gate-modulated behavior with drain-current saturation (soft-saturation for the device printed at 60 °C). The average field-effect mobility ( $\mu_{FE}$ ) and on/off ratio ( $I_{on}/I_{off}$ ) of CuI TFTs printed at RT were 0.11 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and 10<sup>1.7</sup>, respectively. The highest  $\mu_{FE}$  and  $I_{on}/I_{off}$  of CuI TFTs printed at 60 °C were 4.4 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and 10<sup>3.2</sup>, respectively. The mobility was determined from the transconductance of the device at  $V_{DS}$  = -1 V and the  $I_{on}/I_{off}$  was determined at  $V_{DS}$  = -40 V.

Device performances of CuI TFTs were measured at ambient conditions. Figure 11 shows the  $\mu_{FE}$  and  $I_{On}/I_{Off}$  data for CuI TFT devices as a function of the printing temperature from RT to 60 °C. The AFM and SEM data (Figure 5, 6) suggested that printing temperature affected crystallinity and continuity of the printed CuI film; while CuI film printed at RT had a porous structure, the film printed at 60 °C formed dense and continuous film. It is preferred for the channel layer of TFT device to have dense and continuous film without voids, which trap charge carriers, in order to have superior TFT device properties. Also, the grain size of printed CuI film increased when printed at 60 °C which resulting reduction in grain boundaries at the semiconductor and dielectric interface resulting in less carrier scattering [24]. Therefore, the p-type CuI TFT printed at 60 °C showed the maximum  $\mu_{FE}$  and  $I_{On}/I_{Off}$ .

The variation of mobility and on/off data for the same printing temperature might be due to the dissimilarity among ejected CuI ink droplets. Even with the same printing setting, the ejected CuI ink droplet varies every time when printing which affects the uniformity when forming the films.

Figure 11. (a) Average field effect mobility and (b) average Log(on/off ratio) data of Cul TFTs printed at various substrate temperature from RT to 60  $^{\circ}$ C (with standard deviation error bars).

# 4.2.2 Effect of Drop spacing ( $10 - 40 \mu m$ )

In this study, CuI film was deposited on SiO<sub>2</sub>/Si substrate by piezoelectric inkjet printer, where piezoelectric materials were controlled by high electric field and the deformation of the materials ejecting the ink towards the substrate (Figure 12 a) [6]. In the meantime, the film deposition can be varied by changing the drop spacing, which is the distance between the printed droplets on the substrate (Figure 12 b, c). Drop spacing of the printed CuI film was in the range from  $10 \, \mu m$  to  $40 \, \mu m$ .

Figure 12. Schematic diagram of (a) piezoelectic inkjet printer (adapted from [6]), (b) exaggerated illustration of drop spacing, the distance between printed droplets, and (c) realistic illustration of printed CuI film with the overlapped printed droplets of which drop-spacing is in the range from 10  $\mu$ m to 40  $\mu$ m.

Figure 13. Effect of drop spacing in piezoelectric inkjet printer on mobility and  $log(I_{on}/I_{off})$  of p-type Cul TFTs printed at (a) 30 °C, (b) 50 °C, and (c) 60 °C.

The various drop spacing distances were tested for printing CuI films at different printing temperatures in order to optimize the device properties of CuI TFT. Figure 13 shows the mobility and log(on/off ratio) data with various drop spacing distances from 10  $\mu$ m to 40  $\mu$ m when CuI film was printed on the substrate of 30 °C (Figure 13 a), 50 °C (Figure 13 b), and 60 °C (Figure 13 c). It was concluded that 30  $\mu$ m is the optimum drop-spacing for 30 °C printing setting and 20  $\mu$ m for 50 °C and 60 °C printing settings.

## 4.2.3 Effect of W/L ratios (W/L = 1.4 - 5)

Channel layer width (W) and length (L) were varied to optimize the device performance of p-type CuI TFT. While fixing the length of the channel layer as 200  $\mu$ m, the width of the channel layer was varied from 280  $\mu$ m to 1000  $\mu$ m (Figure 14). While the printed CuI film had less overlapped area and formed almost single layer at W/L=1.4, there were multiple overlapped area in the CuI film when W/L=5. The  $\mu_{FE}$  was as high as 6.54 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and  $I_{on}/I_{off}$  ratios of  $I_{on}$  for CuI TFT printed at 60 °C when W/L=1.4. It was expected that the overlapped area of CuI film helped to reduce the off-current state. Therefore, the p-type CuI TFTs were fabricated with W/L=5 channel layer. It was inferred that the overlapped area might influence the variation of device performance as shown in the error bars for the TFTs in Figure 7.

Figure 14. (a) Schematic diagram of printed CuI channel layer and deposited gold as a source and drain with defined channel width and length (b) optical top-view of printed CuI film at 60 °C with W=280  $\mu$ m, L=200  $\mu$ m, and (c) with W=1000  $\mu$ m, L=200  $\mu$ m.

Table 2 shows summarized results of device performance of p-type CuI TFTs with various drop spacing and W/L ratios. The CuI films of the devices were printed at 60 °C. It turned out that the device performance of CuI TFT was optimized when W/L = 5 and drop spacing was 20  $\mu$ m.

Table 2. Average mobility and on/off ratio data of p-type Cul TFTs printed at 60 °C which were fabricated with various drop spacing (10 - 30  $\mu$ m) and W/L ratios (1.4 - 5).

| Printed<br>at 60 °C | L=200 μm, W varied |                                        |               |                                        |               |                                        |  |  |  |

|---------------------|--------------------|----------------------------------------|---------------|----------------------------------------|---------------|----------------------------------------|--|--|--|

|                     | W/L=5              |                                        | W/L=2.5       |                                        | W/L=1.4       |                                        |  |  |  |

| drop spacing        | Avg. Mobility      | Avg. I <sub>on</sub> /I <sub>off</sub> | Avg. Mobility | Avg. I <sub>on</sub> /I <sub>off</sub> | Avg. Mobility | Avg. I <sub>on</sub> /I <sub>off</sub> |  |  |  |

| 10 μm               | 0.99               | 10 <sup>0.59</sup>                     | -             | -                                      | -             | -                                      |  |  |  |

| 20 μm               | 2.20               | 10 <sup>1.28</sup>                     | 1.75          | 10 <sup>0.69</sup>                     | 3.09          | 10 <sup>0.48</sup>                     |  |  |  |

| 30 μm               | 0.53               | 10 <sup>1.68</sup>                     | -             | -                                      | -             | -                                      |  |  |  |

### 4.2.4 Effect of TFT structures (BGTC, BGBC)

Different TFT structures were applied for fabricating p-type CuI TFTs in order to find the best performing device structure. Bottom-Gate Top-Contact (BGTC) and Bottom-Gate Bottom-Contact (BGBC) were applied when fabricating CuI TFTs (Figure 15). The active channel layers which were printed at 60 °C, 20  $\mu$ m drop-spacing, and W/L=5 were used to fabricate CuI TFT for each structure. While the BGTC CuI TFT had the highest  $\mu_{FE}$  as 4.4 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and and  $I_{on}/I_{off}$  ratios of  $10^{3.2}$  with great gate-modulation and drain-current saturation, the BGBC CuI TFT had the highest  $\mu_{FE}$  as 1.83 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and  $I_{on}/I_{off}$  ratio of  $10^{0.4}$  with less gate-modulation and lack of drain-current saturation. The inferior device properties of the BGBC structure were expected to be due to lack of uniformity of the channel layer. It was inferred that since gold was deposited as a source and drain first and then the channel layer was printed for the BGBC structure, the CuI film at the edge of the source/drain interacted with the gold layer surface. This deposition process made CuI film form a meniscus shape, instead of a uniform horizontally parallel film.

Figure 15. P-type Cul TFT with (a) Bottom-Gate Top-Contact (BGTC) structure, and (b) Bottom-Gate Bottom-Contact (BGBC) structure.

# 5. Results and Discussion: Copper (I) Iodide-based TFTs

In order to improve device performance, different copper(I) halides (CuX, X=Br, Cl) were implemented for fabricating copper(I) iodide-based TFTs. It was expected that implementing different halide materials would reduce the carrier concentration which could lead to less conductivity and better saturation for resulting transistor devices. While CuI was used as a base material, CuBr and CuCl were added in precursor solutions which resulted in CuBrI and CuClI ink. Since the crystalline structure of CuX is the same as CuI, the powder form of them was simply mixed with CuI powder in solvent when preparing the precursor ink. Various molar ratios were tested in order to find optimum conditions for CuBrI and CuClI solution for TFT application.

#### 5.1 Characterization of CuBrI film

Inkjet-printed CuBrI film on PECVD-SiO<sub>2</sub>/glass substrate was characterized by AFM and XRD (Figures 16, 17). CuBrI solution was also spin-coated on a soda lime glass substrate for analyzing band gap.

### 5.1.1 Morphology of CuBrI film

CuBrI film was printed at RT on PECVD-SiO<sub>2</sub>/glass and thermally-grown-SiO<sub>2</sub>/Si (TG-SiO<sub>2</sub>/Si) substrates. The AFM images (Figure 16) showed different CuBrI forming with respect to different substrates. It was found that the nature of substrate affected forming CuBrI films, in terms of reaction kinetics and the adhesion of the deposited film [28]. While only islands were formed, which resulted in

discontinuous film on TG-SiO<sub>2</sub>/Si substrate, more continuous film was formed on PEVCD- SiO<sub>2</sub>/glass substrate.

Figure 16. AFM images of CuBrI film printed at RT of (a)  $2x2 \mu m$ , (b)  $10x10 \mu m$  on PECVD-SiO<sub>2</sub>/Si substrates; (c)  $2x2 \mu m$ , (d)  $10x10 \mu m$  on thermally-grown SiO<sub>2</sub>/Si substrate.

# 5.1.2 Optical property of CuBrI film

The optical properties of spin-coated CuBrI film was investigated by UV-Vis spectroscopy. CuBrI film was spin-coated at RT on a soda lime glass and was dried at 120 °C for 30 minutes before measuring the optical properties. The bandgap was expected to be ~2.85 eV and ~3.1 eV, which agreed to the reported values [13], indicating CuI and CuBr crystalline were formed separately (Figure 17). The

estimated bandgap indicated the transparency of printed CuBrI film in the visible wavelengths.

Figure 17. Estimated bandgap of spin-coated CuBrl film on soda lime glass at RT. The spin-coated film was dried at  $120\,^{\circ}\mathrm{C}$  for 30 min before measurement.

# 5.1.3 Crystal structure of CuBrI film

The CuBrI film printed at RT, CuBr powder, and CuI powder were used for XRD analysis. It was found that the film formed preferably with (2 2 0) crystal plane (Figure 18) which agreed with reported data [13].

Figure 18. XRD patterns of CuBrI film printed at RT, CuBr powder, and CuI powder. The printed CuBrI films were dried at 120 °C for 30min after printing.

### 5.2 Device Performance of CuBrI TFTs

### 5.2.1. CuBrI TFTs printed at RT

Inkjet-printed CuBrI film was used as an active channel layer for fabricating TFT device on PECVD-SiO<sub>2</sub>/glass substrate without SU-8 encapsulation. The Bottom-Gate Top-Contact (BGTC) TFT structure was fabricated. It was found that the transistors exhibited good gate-modulated behavior with drain-current saturation without SU-8 encapsulation, unlike CuI TFTs. It was inferred that CuBr helped the film to be more compatible for TFT application in terms of durability and moisture sensitivity. While the CuBrI film printed at RT on TG-SiO<sub>2</sub>/Si substrate was not applicable as a TFT device, the film printed at RT on PECVD-SiO<sub>2</sub>/glass substrate was successfully implemented into a TFT device. It was inferred that the film morphology affected the feasibility of TFT application; the CuBrI film printed on TG-SiO<sub>2</sub>/Si formed mostly islands, while the film printed on PECVD-SiO<sub>2</sub>/glass substrate was more continuous film (Figure 16).

Figure 19 shows the drain current-drain voltage ( $I_D$ - $V_D$ ) output characteristics and the drain current-gate voltage ( $I_D$ - $V_G$ ) transfer characteristics of CuBrI TFTs printed at RT. The average field-effect mobility ( $\mu_{FE}$ ) and on/off ratio ( $I_{on}/I_{off}$ ) of CuBrI TFTs printed at RT were 2.39 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and 10<sup>1.9</sup>. The mobility was determined from the transconductance of the device at  $V_{DS}$  = - 1 V and the  $I_{on}/I_{off}$  was determined at  $V_{DS}$  = - 40 V.

Figure 19. (a) The drain current-drain voltage ( $I_D$ - $V_D$ ) output characteristics (b) drain current-gate voltage ( $I_D$ - $V_G$ ) transfer characteristics ( $I_D$  plotted logarithmically) at  $V_{DS}$  = - 40 V of CuBrI TFT printed at RT on the PECVD-SiO<sub>2</sub>/glass substrate.

#### 5.2.2. Effect of molar ratio of CuBrI TFTs

Various molar ratios of CuBr: CuI were tested in order to find the optimized condition for CuBrI TFT application (Table 2). P-type CuBrI TFTs for 1:1, 3:7, and 7:3 molar ratio of CuBr: CuI were successfully realized on PECVD-SiO2/glass substrate. 1:1 molar ratio was found to be the optimum condition for CuBrI transistor printed at RT on PECVD-SiO2/glass substrate. In addition, the films printed on TG-SiO2/Si substrate were also tested for 1:1, 3:7, and 1:9 molar ratios for printing temperature of RT and 60 °C. The film printed at RT on TG-SiO2/Si substrate was not feasible for TFT application, while the CuBrI film of which 3:7 and 1:9 molar

ratios of CuBr : CuI printed at 60 °C were successfully implemented into TFTs on TG-SiO<sub>2</sub>/Si substrates.

Table 3. Device performance of CuBrI TFTs for various molar ratios of CuBr:CuI on PECVD-SiO2/glass and TG-SiO2/Si substrate printed at RT and 60 °C, respectively.

| PECVD-SiO2/Glass                        |                   |                    |                    | Thermally-Grown-SiO2/Si                 |     |                    |                    |  |

|-----------------------------------------|-------------------|--------------------|--------------------|-----------------------------------------|-----|--------------------|--------------------|--|

| RT                                      | 1:1               | 3:7                | 7:3                | 60 °C                                   | 1:1 | 3:7                | 1:9                |  |

| $\mu_{FE}$ (cm2/Vs)                     | 2.38              | 0.033              | 0.013              | μ <sub>FE</sub> (cm2/Vs)                | -   | 0.78               | 0.95               |  |

| I <sub>on</sub> /I <sub>off</sub> ratio | 10 <sup>1.9</sup> | 10 <sup>0.16</sup> | 10 <sup>1.39</sup> | I <sub>on</sub> /I <sub>off</sub> ratio | -   | 10 <sup>0.48</sup> | 10 <sup>0.54</sup> |  |

## 5.3 Device Performance of CuClI TFTs

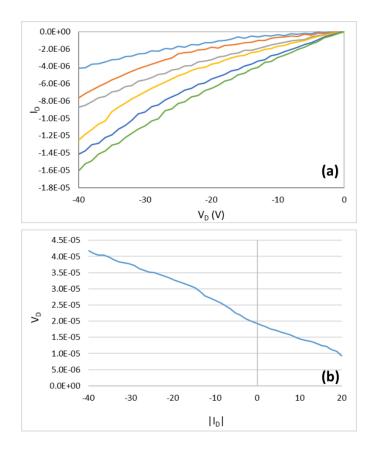

The CuClI film inkjet-printed at 60 °C was used as an active channel layer for fabricating TFT devices on TG-SiO<sub>2</sub>/Si substrate. The Bottom-Gate Top-Contact (BGTC) TFT structure was fabricated. It was found that the transistors exhibited good gate-modulated behavior, but conductive compared to CuI and CuBrI TFTs. Also, SU-8 encapsulation was needed in order to have a better gate-modulation, like in CuI TFTs. Various molar ratios of CuCl: CuI were tested in order to find the optimized condition. It was found that only the film with 1:9 ration of CuCl: CuI was working as channel layer of p-type TFT device.

Figure 20 shows the drain current-drain voltage ( $I_D$ - $V_D$ ) output characteristics and the drain current-gate voltage ( $I_D$ - $V_G$ ) transfer characteristics of CuClI TFTs printed at RT. The highest  $\mu_{FE}$  and  $I_{on}/I_{off}$  of CuClI TFTs printed at 60 °C were 1.02 cm<sup>2</sup>  $V^{-1}$  s<sup>-1</sup> and 10<sup>0.73</sup>. The mobility was determined from the transconductance of the device at  $V_{DS}$  = - 1 V and the  $I_{on}/I_{off}$  was determined at  $V_{DS}$  = - 40 V.

Figure 20. (a) The drain current-drain voltage (ID-VD) output characteristics (b) drain current-gate voltage (ID-VG) transfer characteristics (ID plotted logarithmically) at VDS = - 40 V of CuClI TFT printed at 60 °C on the TG-SiO2/glass substrate, when CuCl:CuI ratio was 1:9.

# 6. Conclusion

Inkjet-printed Copper(I) Iodide-based p-type TFTs were fabricated for the first time. CuI, CuBrI, and CuCII films were printed at room temperature. As-printed copper(I) halides films were used as p-type active channel layers for TFTs after drying at 120 °C. The entire process of fabricating TFTs was kept under 150 °C, which is compatible with flexible plastic substrates and transparent glass substrate. Various different printing temperatures, drop spacing, W/L ratios, and TFT structures were tested in order to find the optimum device properties for p-type copper(I) iodide-based TFT. It was found that the BGBC CuI TFTs with 60 °C printed channel layer which has 20 µm drop-spacing and W/L ratio as 5 have the most superior device properties. CuI TFTs with SU-8 encapsulation exhibited outstanding p-type transistor behaviors with field-effect mobility as high as 4.36 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and and I<sub>on</sub>/I<sub>off</sub> ratios of 10<sup>3.24</sup> for CuI films that were printed at 60°C on the silicon substrates. Also, CuBrI TFTs resulted in successful p-type transistor behaviours with average field-effect mobility of 2.4 cm $^2$  V $^{-1}$  s $^{-1}$  and I<sub>on</sub>/I<sub>off</sub> ratio of 10 $^{1.9}$  on the glass substrates when the molar ratio of CuBr:CuI was 1:1. In addition, CuCII TFTs were successfully fabricated with field-effect mobility as high as 1.02 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and I<sub>on</sub>/I<sub>off</sub> ratio of  $10^{0.73}$  on the silicon substrates when the molar ratio of CuCl:CuI was 1:9. The device performance were comparable to reported p-type metal oxide TFTs. This study suggests that copper(I) iodide-based semiconductors could be promising lowtemperature inkjet-printed p-type semiconductor candidates for TFT application.

# Bibliography

- [1] E. Fortunato, P. Barquinha, and R. Martins, "Oxide Semiconductor Thin-Film Transistors: A Review of Recent Advances," *Adv. Mater.*, vol. 24, pp. 2945–2986, 2012.

- [2] J. S. Park, W.-J. Maeng, H.-S. Kim, and J.-S. Park, "Review of recent developments in amorphous oxide semiconductor thin-film transistor devices," *Thin Solid Films*. 2012.

- [3] S. Y. Han, C. H. Chang, D. H. Lee, and G. S. Herman, "Inkjet-printed high mobility transparent-oxide semiconductors," *IEEE/OSA J. Disp. Technol.*, 2009.

- [4] C.-H. Choi, S.-Y. Han, Y.-W. Su, Z. Fang, L.-Y. Lin, C.-C. Cheng, and C. Chang, "Fabrication of high-performance, low-temperature solution processed amorphous indium oxide thin-film transistors using a volatile nitrate precursor," *J. Mater. Chem. C*, 2015.

- [5] S. Y. Han, G. S. Herman, and C. H. Chang, "Low-temperature, high-performance, solution-processed indium oxide thin-film transistors," *J. Am. Chem. Soc.*, 2011.

- [6] C.-H. Choi, L.-Y. Lin, C.-C. Cheng, and C. -h. Chang, "Printed Oxide Thin Film Transistors: A Mini Review," *ECS J. Solid State Sci. Technol.*, vol. 4, no. 4, pp. 3044–3051, 2015.

- [7] D.-H. Lee, Y.-J. Chang, G. S. Herman, and C. Chang, "A General Route to Printable High-Mobility Transparent Amorphous Oxide Semiconductors," *Adv. Mater.*, vol. 19, no. 6, pp. 843–847, 2007.

- [8] S. Y. Kim, C. H. Ahn, J. H. Lee, Y. H. Kwon, S. Hwang, J. Y. Lee, and H. K. Cho, "p-Channel Oxide Thin Film Transistors Using Solution-Processed Copper Oxide," *ACS Appl. Mater. Interfaces*, vol. 5, no. 7, p. 2417–2421, 2013.

- [9] P. Pattanasattayavong, S. Thomas, G. Adamopoulos, M. a. McLachlan, and T. D. Anthopoulos, "P-channel thin-film transistors based on spray-coated Cu2O films," *Appl. Phys. Lett.*, vol. 102, no. 16, 2013.

- [10] M. A. Q.-L. A. Carrillo-Castilloa, A. Salas-Villasenora, I. Mejiaa, S. Aguirre-Tostadob, B.E. Gnadea, "P-type thin films transistors with solution-deposited lead sulfide films as semiconductor," *Thin Solid Films*, vol. 520, no. 7, pp. 3107–3110, 2012.

- [11] Z. Q. Yao, S. L. Liu, L. Zhang, B. He, A. Kumar, X. Jiang, W. J. Zhang, and G. Shao, "Room temperature fabrication of p-channel Cu2O thin-film transistors on flexible polyethylene terephthalate substrates," *Appl. Phys. Lett.*, vol. 101, 2012.

- [12] H. A. Al-Jawhari, J. A. Caraveo-Frescas, M. N. Hedhili, and H. N. Alshareef, "P-Type Cu2O/SnO Bilayer Thin Film Transistors Processed at Low Temperatures," *ACS Appl. Mater. Interfaces*, vol. 5, p. 9615–9619, 2013.

- [13] M. Grundmann, F. L. Schein, M. Lorenz, T. Böntgen, J. Lenzner, and H. Von Wenckstern, "Cuprous iodide a p-type transparent semiconductor: history and novel applications," *Physica Status Solidi (A) Applications and Materials Science*. 2013.

- [14] S.-Y. Sung, S.-Y. Kim, K.-M. Jo, J.-H. Lee, J.-J. Kim, S.-G. Kim, K.-H. Chai, S. J. Pearton, D. P. Norton, and Y.-W. Heo, "Fabrication of p-channel thin-film transistors using CuO active layers deposited at low temperature," *Appl. Phys. Lett. Appl. Phys. Lett.*, vol. 97, no. 96, pp. 222109–192102, 2010.

- [15] K. Matsuzaki, K. Nomura, H. Yanagi, T. Kamiya, M. Hirano, and H. Hosono, "Epitaxial growth of high mobility Cu2O thin films and application to p-channel thin film transistor," *Appl. Phys. Lett.*, vol. 93, no. 20, 2008.

- [16] S. R. Thomas, P. Pattanasattayavong, and T. D. Anthopoulos, "Solution-processable metal oxide semiconductors for thin-film transistor applications.," *Chem. Soc. Rev.*, 2013.

- [17] E. Fortunato, R. Barros, P. Barquinha, V. Figueiredo, S.-H. K. Park, C.-S. Hwang, and R. Martins, "Transparent p-type SnOx thin film transistors produced by reactive rf magnetron sputeering followed by low temperatrue annealing," *Appl. Phys. Lett.*, vol. 97, 2010.

- [18] C.-W. Zhong, H.-C. Lin, K.-C. Liu, and T.-Y. Huang, "Impact of thermal oxygen annealing on the properties of tin oxide films and characteristics of ptype thin-film transistors," *Jpn. J. Appl. Phys.*, vol. 55, 2016.

- [19] V. Figueiredo, E. Elangovan, R. Barros, J. V. Pinto, T. Busani, R. Martins, and E. Fortunato, "p-Type CuxO Films Deposited at Room Temperature for Thin-Film Transistors," *J. Disp. Technol.*, vol. 8, no. 1, 2012.

- [20] D.-W. Nam, I.-T. Cho, J.-H. Lee, E.-S. Cho, J. Sohn, S.-H. Song, and H.-I. Kwon, "Active layer thickness effects on the structural and electrical properties of p-type Cu<sub>2</sub>O thin-film transistors," *J. Vac. Sci. Technol. B*, 2012.

- [21] J. Yu, G. Liu, A. Liu, Y. Meng, B. Shin, and F. Shan, "Solution-processed ptype copper oxide thin film transistors fabricated by using a one-step vacuum annealing technique," *J. Mater. Chem. C*, vol. 3, 2015.

- [22] J. Jang, S. Chung, H. Kang, and V. Subramanian, "P-type CuO and Cu2O transistors derived from a sol-gel copper (II) acetate monohydrate precursor," *Thin Solid Films*, 2016.

- [23] K. Okamura, B. Nasr, R. A. Brand, and H. Hahn, "Solution-processed oxide semiconductor SnO in p-channel thin-film transistors," *J. Mater. Chem.*, vol. 22, 2012.

- [24] A. Carrillo-Castillo, A. Salas-Villasenor, I. Mejia, S. Aguirre-Tostado, B. E. Gnade, and M. A. Quevedo-L??pez, "P-type thin films transistors with solution-deposited lead sulfide films as semiconductor," *Thin Solid Films*, 2012.

- [25] Y. Youhua, Z. Shaoxiong, L. Zhichao, and L. Zhengbang, "Microstructure and optical properties of sprayed γ-CuI thin films for CuInS 2 solar cells," *RARE Met.*, vol. 30, no. 1, 2011.

- [26] S. Inudo, M. Miyake, and T. Hirato, "Electrical properties of CuI films prepared by spin coating," *Phys. Status Solidi Appl. Mater. Sci.*, vol. 210, no. 11, pp. 2395–2398, 2013.

- [27] R. P. Vasquez, "CuI by XPS Spectra," Surf. Sci. Spectra, vol. 2, no. 149, 1993.

- [28] P. Vas-Umnuay, "Growth, Characterizations and Applications of Copper Sulfide Thin Films by Solution-Based Processes," Oregon State University, 2013.