#### AN ABSTRACT OF THE THESIS OF

|        | Sung Chiao Hu      | for the Do        | ctor of Philosophy |

|--------|--------------------|-------------------|--------------------|

|        | (Name)             |                   | (Degree)           |

| Ele    | ctrical and        |                   |                    |

| in Ele | ctronics Engineeri | ng presented on   |                    |

|        | (Major)            |                   | (Date)             |

| Title: | CELLULAR SYNT      | HESIS OF SYNCHRON | OUS SEQUENTIAL     |

|        | MACHINES           |                   |                    |

| Abstra | .ct approved:      | Redacted for      | r Privacy          |

|        |                    | Robert A          | . Short            |

With the advancing solid-state technology, it is necessary to develop new techniques for synthesizing digital networks. The regular pattern of cellular circuits seems to be the best fitted for the new LSI technology. Recently, cellular implementations of combinational circuits have received considerable attention but very little attention has been given to sequential circuits. In this paper, we present two new methods for realizing sequential machines, both using cellular circuits. These new techniques will also enable us to do away with the time-consuming and difficult problem of state assignment. State-assigned (Moore) machines are assumed throughout.

The first method converts sequential functions into combinational like equations. In order to do so, the machine must be either definite or finite input and feedback memory (FIFM). If the machine is neither definite nor FIFM, it is made FIFM by constructing a proper feedback

function. These combinational like equations can easily be implemented by conventional combinational cellular circuits, such as the cutpoint cellular arrays, together with delay elements.

The second method utilizes matrix methods. It is noted that when a machine is in a certain state and is subject to an input, it does two things: it makes a state transition and it produces outputs. If the diagonal elements of an nxn array of cells are thought as representing n states, the transition of states can be accomplished by first moving horizontally and then vertically and the output can be collected by an added bottom collection row.

In both cases, bounds on the number of cells are established and minimal realizations are studied. Methods for starting these cellular machines are also investigated. In order to make the machine more flexible, techniques are devised to initialize the machine into any state desired.

It is safe to predict that future computing systems will continue to increase the demands on several sophisticated design areas. They will need to be more readily expandable and modifiable. Automatic error detection and correction will also play a more significant role. Therefore, besides modularity, reliability and programmability are also important aspects of any new design techniques. Both synthesis methods presented in this paper can easily be modified to include these features.

# Cellular Synthesis of Synchronous Sequential Machines

by

Sung Chiao Hu

#### A THESIS

submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

June 1970

APPROVED:

# Redacted for Privacy

Professor of Electrical and Electronics Engineering

in charge of major

# Redacted for Privacy

Head of Department of Electrical and Electronics Engineering

# Redacted for Privacy

Dean of Graduate School

Date thesis is presented May 1,1970

Typed by Barbara Eby for Sung Chiao Hu

#### **ACKNOWLEDGEMENTS**

The author acknowledges with sincere thanks the interest and guidance offered by Dr. R. A. Short; the willingness of Drs. F. Young, J. Herzog, D. Pierce and M. Cropsey to serve on the author's graduate committee; the help offered by Mr. W. Chiu in the final stages of the thesis preparation; and the patience and understanding of my loving wife, Lily.

# TABLE OF CONTENTS

| I.   | INTROI | DUCTION                                | 1   |

|------|--------|----------------------------------------|-----|

|      | 1.1    | Problems, Objectives, and Results      | 1   |

|      | 1.2    | Definition of Terms                    | 3   |

|      | 1.3    | Historical Backgrounds                 | 6   |

| II.  | SM SYN | THESIS USING FIFM PROPERTY             | 10  |

|      | 2.1    | Introduction                           | 10  |

|      | 2.2    | Tests for FIFM                         | 11  |

|      |        | 2.2.1 Definiteness Tests               | 11  |

|      |        | 2.2.2 Finiteness Tests                 | 15  |

|      | 2.3    | Converting Non-FIFM Machines to FIFM   |     |

|      |        | Machines - Construction of Feedback    |     |

|      |        | Functions                              | 19  |

|      | 2.4    | Determination of K                     | 23  |

|      | 2.5    | Characterization of FIFM Machines      | 25  |

|      |        | 2.5.1 Difference Equations             | 25  |

|      |        | 2.5.2 Predecessor Trees                | 31  |

|      | 2.6    | Cellular Synthesis                     | 35  |

|      |        | 2.6.1 Linear Cascade                   | 36  |

|      |        | 2.6.2 Array                            | 39  |

|      |        | 2.6.3 Tree                             | 40  |

|      | 2.7    | Minimal Realizations and Bounds        | 43  |

|      | 2.8    | Summary                                | 45  |

| III. | SM SYN | THESIS BY MATRIX                       | 48  |

|      | 3.1    | Introduction                           | 48  |

|      | 3.2    | Matrices                               | 48  |

|      | 3.3    | Cellular Synthesis                     | 50  |

|      | 3.4    | Minimal Realizations and Bounds        | 53  |

|      | 3.5    | Summary                                | 56  |

| IV.  | INITIA | LIZATION PROBLEM                       | 5 7 |

|      | 4. l   | Introduction                           | 5 7 |

|      | 4.2    | Recoverable Machines                   | 58  |

|      | 4.3    | Input Approach                         | 60  |

|      | 4.4    | Implementation of Recoverable Machines | 65  |

|      | 4.5    | Initialization Sequence                | 66  |

|      | 4.6    | Summary                                | 67  |

| v.  | RELIA      | BILITY AND PROGRAMMABILITY         | 69         |

|-----|------------|------------------------------------|------------|

|     | 5.1        | Introduction                       | 69         |

|     | 5.2        | Reliability Improvements           | 71         |

|     |            | 5.2.1 Static Redundancy            | 71         |

|     |            | 5.2.2 Dynamic Redundancy           | 73         |

|     | 5.3        | Programmability                    | 76         |

|     |            | 5.3.1 Minterm Select               | 76         |

|     |            | 5.3.2 Coincidence or Linear Select | 77         |

|     | 5.4        | Summary                            | <b>7</b> 9 |

|     |            |                                    | 0.1        |

| VI. |            | ARY AND CONCLUSIONS                | 81         |

|     |            | Summary                            | 81         |

|     | 6.2        | Problems for Further Research      | 83         |

|     | 6.3        | Conclusions                        | 84         |

|     | BIBLIC     | OGRAPHY                            | 131        |

|     | APPENDIX I |                                    | 134        |

|     | APPEN      | IDIX II                            | 136        |

|     |            |                                    |            |

# LIST OF FIGURES

| Figure |                                                                                                                                                               | Page           |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 1      | Time unit of a synchronous sequential machine.                                                                                                                | 86             |

| 2      | Flow table representation of a Moore machine, Ml.                                                                                                             | 86             |

| 3      | <ul><li>(a) Flow table of M2</li><li>(b) State graph of M2</li></ul>                                                                                          | 87<br>87       |

| 4      | D-successor tree test of Ml.                                                                                                                                  | 87             |

| 5      | D-pair table test of M1.                                                                                                                                      | 88             |

| 6      | F-successor tree test of Ml.                                                                                                                                  | 88             |

| 7      | F-pair table test of Ml.                                                                                                                                      | 89             |

| 8      | <ul> <li>(a) Flow table of M3.</li> <li>(b) D-pair table test of M3.</li> <li>(c) F-pair table test of M3.</li> <li>(d) D-implication graph of M3.</li> </ul> | 89<br>89<br>89 |

| 9      | <ul><li>(a) Flow table of M3' - M3 with an added output, F.</li><li>(b) F-pair table test of M3'.</li></ul>                                                   | 90<br>90       |

| 10     | D-pair trees of M3.                                                                                                                                           | 90-93          |

| 11     | <ul><li>(a) Flow table of M2 using X as the input variable.</li><li>(b) D-pair table test of M2.</li></ul>                                                    | 93<br>93       |

| 12     | <ul><li>(a) Flow table of Ml using X as the input variable.</li><li>(b) Expanded flow table of Ml to include the feed-</li></ul>                              | 94             |

|        | back input.                                                                                                                                                   | 94             |

| 13     | <ul><li>(a) Flow table of M3'.</li><li>(b) Expanded flow table of M3' to indicate the feed-</li></ul>                                                         | 94             |

|        | (b) Expanded flow table of M3' to indicate the feed-back input.                                                                                               | 94             |

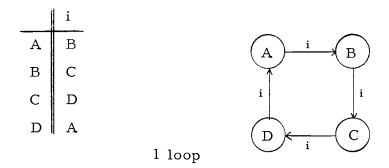

| 14     | <ul><li>(a) Flow table of M2.</li><li>(b) Predecessor tree of M2.</li></ul>                                                                                   | 95<br>95       |

| 15     | (a) Expanded flow table of M1. (b) Predecessor tree of (a).                                                                                                   | 96<br>96       |

| Figure |                                                                                                                                    | Page           |

|--------|------------------------------------------------------------------------------------------------------------------------------------|----------------|

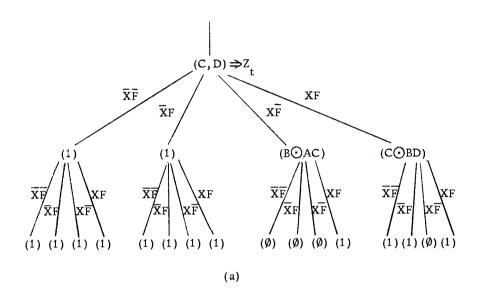

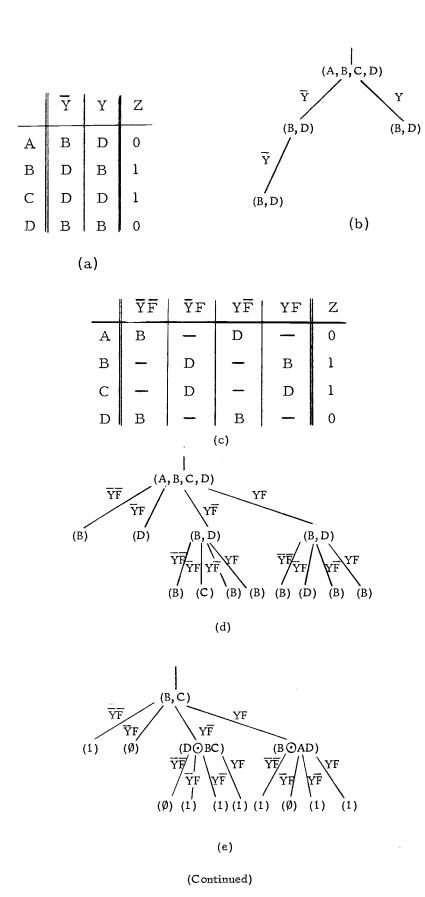

| 16     | <ul> <li>(a) Expanded flow table of M3.</li> <li>(b) Z-predecessor tree of (a).</li> <li>(c) F-predecessor tree of (a).</li> </ul> | 97<br>97<br>97 |

| 17     | Maitra cascade.                                                                                                                    | 98             |

| 18     | <ul><li>(a) The difference equation for the output of M2.</li><li>(b) Two-rail cascade realization of (a).</li></ul>               | 98<br>98       |

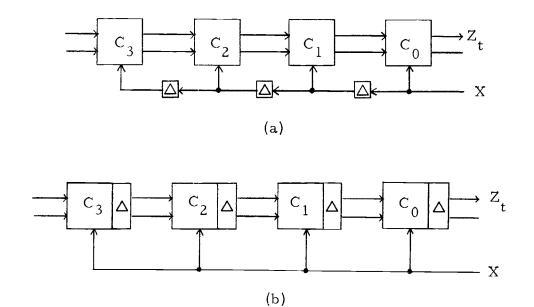

| 19     | Two-rail cascade realization with (a) delayed input, and (b) delayed logic.                                                        | 99<br>99       |

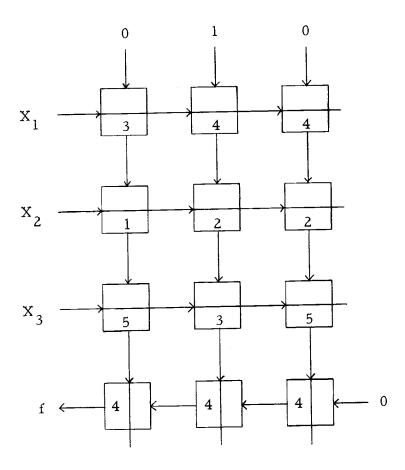

| 20     | Cellular array synthesis of Equation 2.12 using Spandorfer's technique.                                                            | 99             |

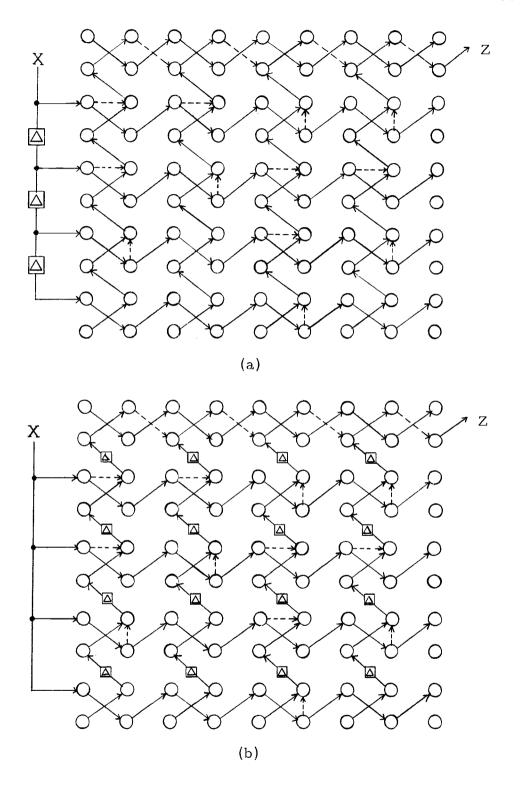

| 21     | Array realization of M2 using (a) delayed input, and (b) delayed logic.                                                            | 100<br>100     |

| 22     | <ul><li>(a) Difference equations characterizing M3.</li><li>(b) Array realization of M3 using delayed input.</li></ul>             | 101<br>101     |

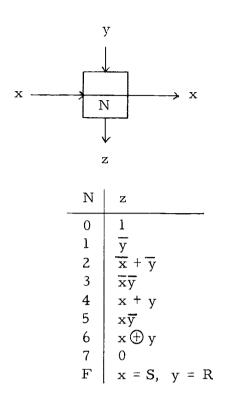

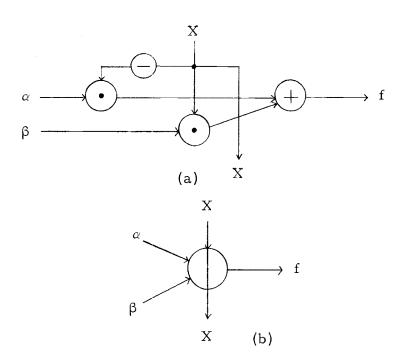

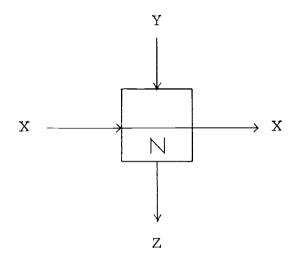

| 23     | Functional description of a cutpoint cell                                                                                          | 102            |

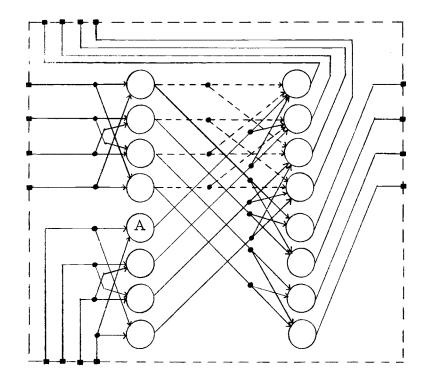

| 24     | Cutpoint cellular array synthesis of M2.                                                                                           | 102            |

| 25     | Cutpoint cellular array synthesis of Ml.                                                                                           | 103            |

| 26     | <ul><li>(a) Tree realization of Equation 2.14.</li><li>(b) Another way of tree realization of Equation 2.14.</li></ul>             | 1 04<br>1 04   |

| 27     | Two ways of realizing Equation 2.14 using gate circuits.                                                                           | 1 05           |

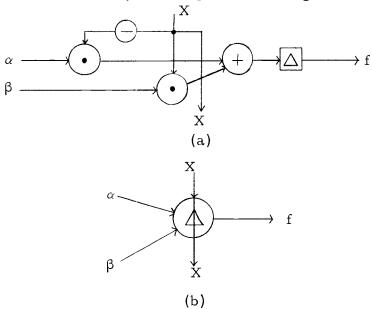

| 28     | <ul><li>(a) Detailed gate circuit of a cell in a delayed input tree structure.</li><li>(b) The symbol represents (a).</li></ul>    | 106<br>106     |

| 29     | <ul><li>(a) Detailed gate circuit of a cell in a delayed logic tree structure.</li><li>(b) The symbol represents (a).</li></ul>    | 106<br>106     |

| Figure |                                                                                                                       | Page |

|--------|-----------------------------------------------------------------------------------------------------------------------|------|

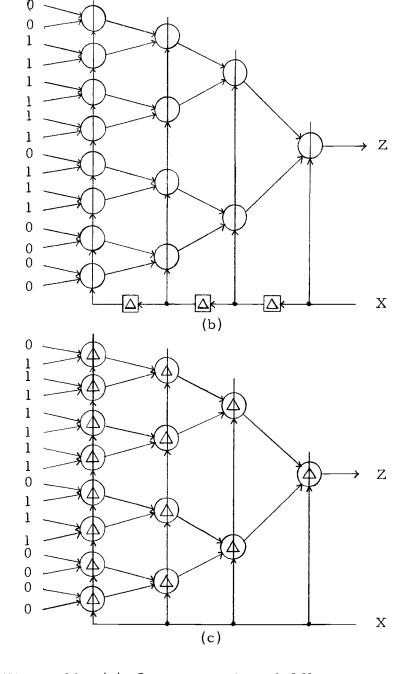

| 30     | (a) Output equations of M2.                                                                                           | 107  |

|        | (b) Delayed input tree realization of M2.                                                                             | 107  |

|        | (c) Delayed logic tree realization of M2.                                                                             | 107  |

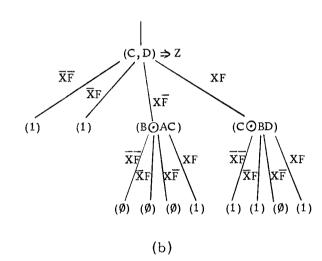

| 31     | (a) Predecessor tree for Z of M3.                                                                                     | 108  |

|        | (b) Predecessor tree for F of M3.                                                                                     | 108  |

|        | (c) Delayed input tree realization of M3.                                                                             | 109  |

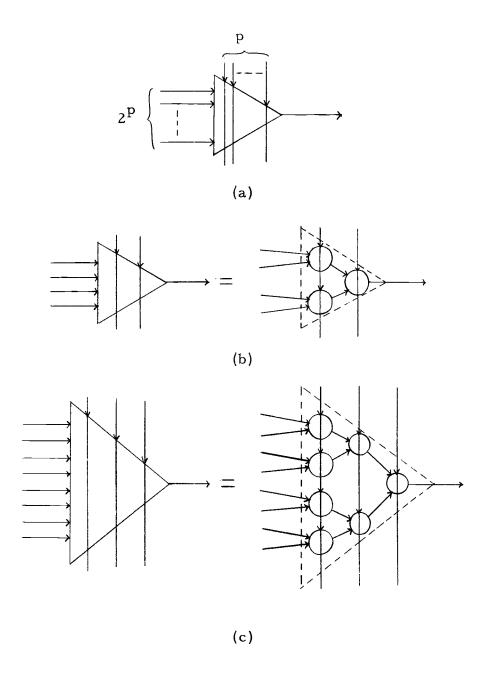

| 32     | (a) Symbol for a super cell                                                                                           | 110  |

|        | (b) Gate structure of a 2-input super cell.                                                                           | 110  |

|        | (c) Gate structure of a 3-input super cell.                                                                           | 110  |

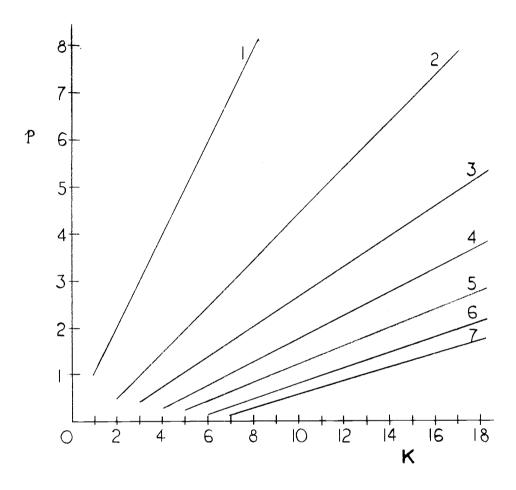

| 33     | Tradeoff graph.                                                                                                       | 111  |

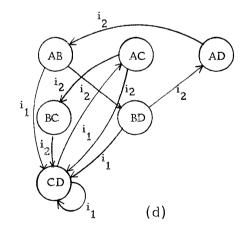

| 34     | (a) Flow table of M4.                                                                                                 | 112  |

|        | (b) Transition matrix of M4.                                                                                          | 112  |

|        | (c) i <sub>1</sub> -transition matrix of M4.                                                                          | 112  |

|        | (d) i <sub>2</sub> -transition matrix of M4.                                                                          | 112  |

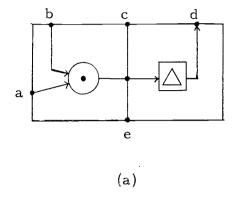

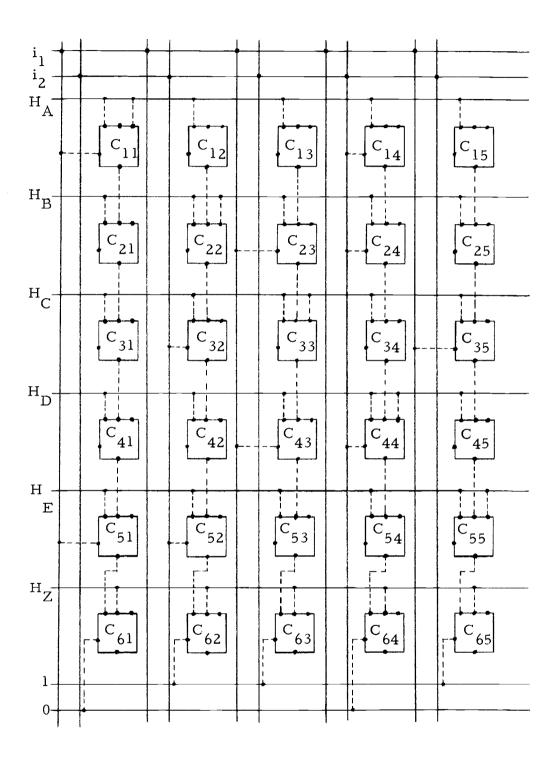

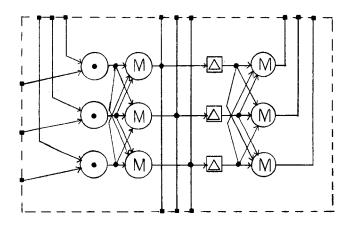

| 35     | (a) Cell structure used in matrix synthesis.                                                                          | 113  |

|        | (b) Matrix synthesis of M4.                                                                                           | 113  |

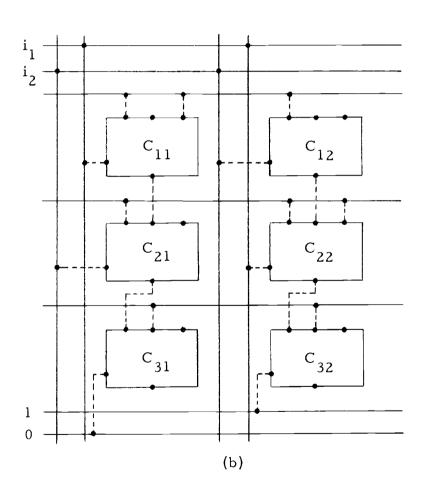

| 36     | Matrix synthesis of M2.                                                                                               | 114  |

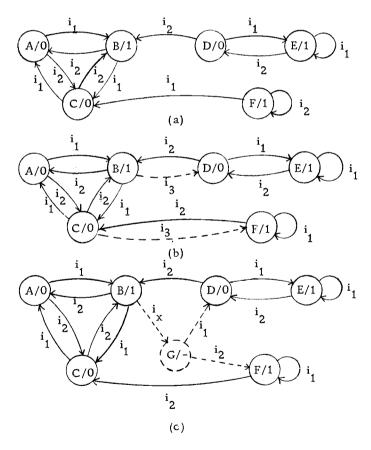

| 37     | A machine whose behavior depends on its starting state.                                                               | 115  |

| 38     | <ul> <li>(a) State diagram of M given in Figure 37.</li> <li>(b) Added input i makes transient state D, E,</li> </ul> | 115  |

|        | and F recoverable.                                                                                                    | 115  |

|        | (c) Added state G makes transient states D, E, and F recoverable.                                                     | 115  |

| 39     | (a) Flow table of M5.                                                                                                 | 116  |

|        | (b) Recoverable version of M5.                                                                                        | 116  |

| 40     | A machine with a permutation column but not a complete permutation column.                                            | 116  |

|        |                                                                                                                       |      |

| 41     | A machine with a complete permutation column.                                                                         | 117  |

| 42     | (a) An example machine M.                                                                                             | 117  |

|        | (b) Recoverable version of (a).                                                                                       | 117  |

|        |                                                                                                                       |      |

| Figure |                                                                                                                                                                                                                                                                                           | Page                                                 |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

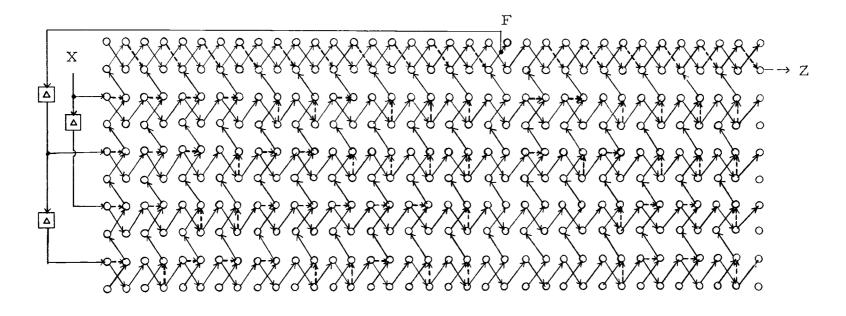

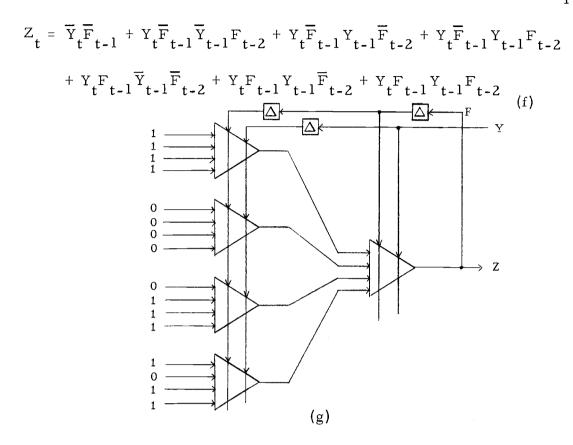

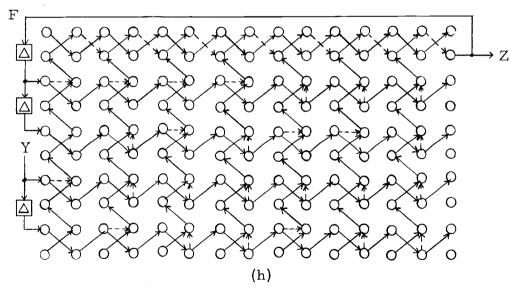

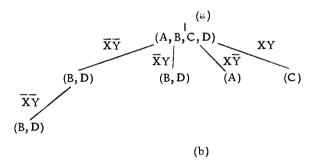

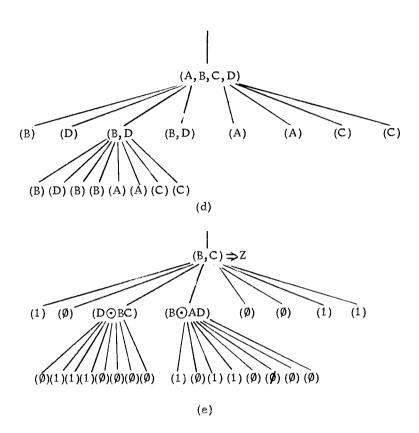

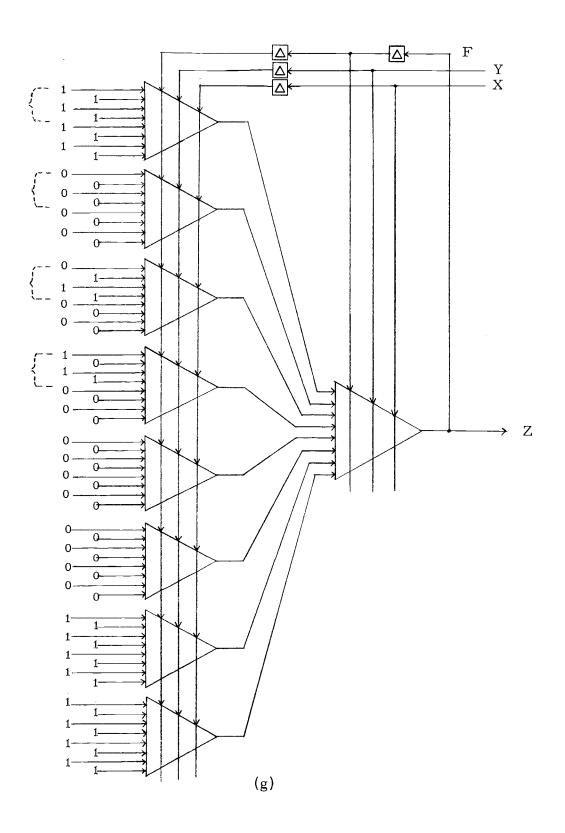

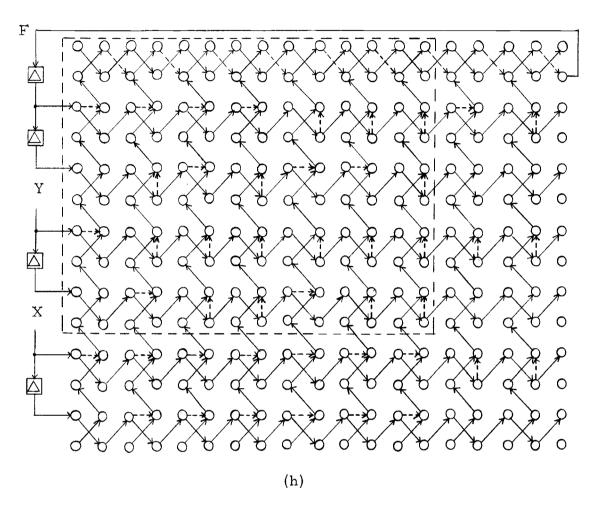

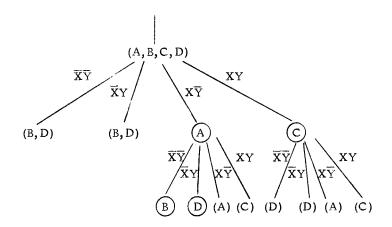

| 43     | M6 and its synthesis procedures  (a) Flow table.  (b) D-successor tree test.  (c) M6 with the feedback input.  (d) F-successor tree test.  (e) The predecessor tree.  (f) Output equation.  (g) Tree realization.  (h) Array realization.                                                 | 118<br>118<br>118<br>118<br>118<br>119<br>119        |

| 44     | Recoverable version of M6 and its synthesis  (a) Flow table of M6' - recoverable version of M6.  (b) D-successor tree test.  (c) M6' with the feedback input.  (d) F-successor tree test.  (e) The predecessor tree.  (f) Output equation.  (g) Tree realization.  (h) Array realization. | 120<br>120<br>120<br>121<br>121<br>121<br>122<br>123 |

| 45     | Recovering tree of M6'.                                                                                                                                                                                                                                                                   | 124                                                  |

| 46     | Cell structure for matrix arrays by employing triplicated redundancy technique and using majority gate as the decision making element.                                                                                                                                                    | 124                                                  |

| 47     | Quadded version of Spandorfer's array.                                                                                                                                                                                                                                                    | 125                                                  |

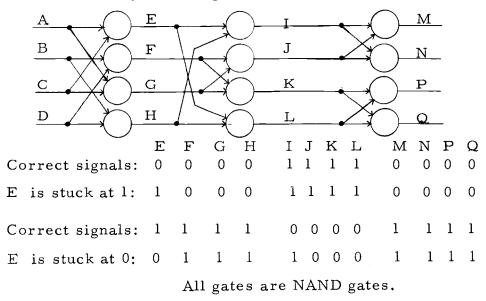

| 48     | Error correcting mechanism in quadded logic.                                                                                                                                                                                                                                              | 125                                                  |

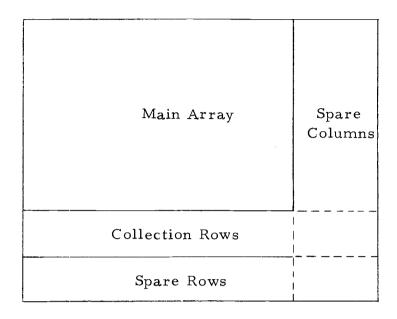

| 49     | Cellular array with spare arrangement.                                                                                                                                                                                                                                                    | 126                                                  |

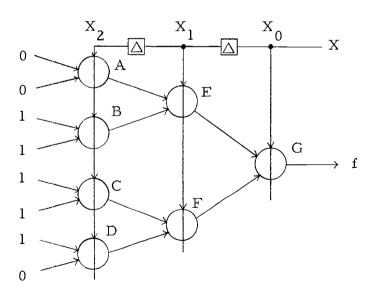

| 50     | Tree structure for realizing the function $f = \overline{X}_0 X_1 + X_0 \overline{X}_1 X_2 + X_0 \overline{X}_1 \overline{X}_2$ .                                                                                                                                                         | 126                                                  |

| 51     | <ul><li>(a) Truth table describing the tree circuit of Figure 50.</li><li>(b) Possible functions for a single fault in Figure 50.</li><li>(c) Same as (b) with some row permutations.</li></ul>                                                                                           | 129<br>129<br>129                                    |

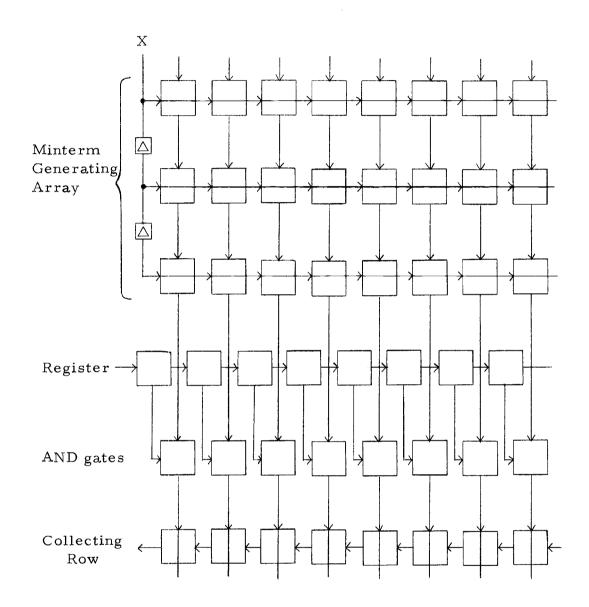

| 52     | Programmable cut-point cellular array.                                                                                                                                                                                                                                                    | 128                                                  |

| Figure |                                                                                                                                 | Page       |

|--------|---------------------------------------------------------------------------------------------------------------------------------|------------|

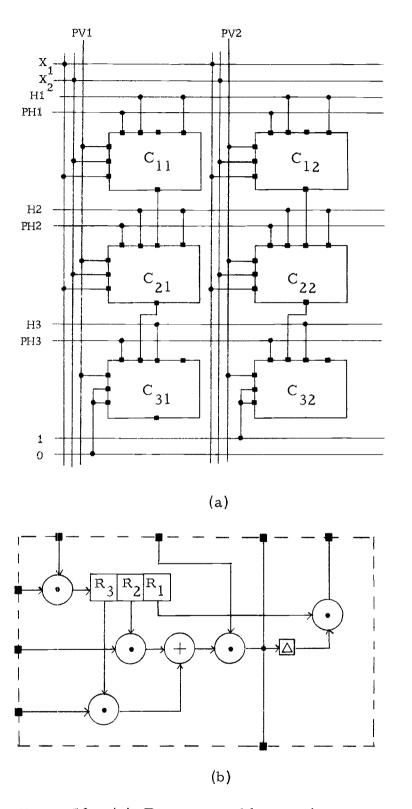

| 53     | <ul><li>(a) Programmable matrix structure.</li><li>(b) The structure of cells used in (a).</li></ul>                            | 129<br>129 |

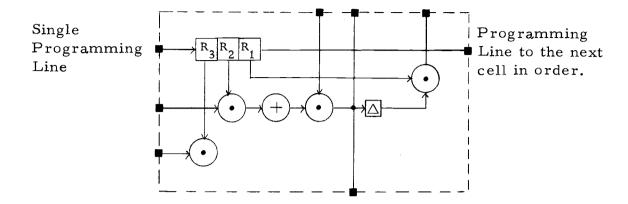

| 54     | Cell structure used in linear select scheme of programming.                                                                     | 130        |

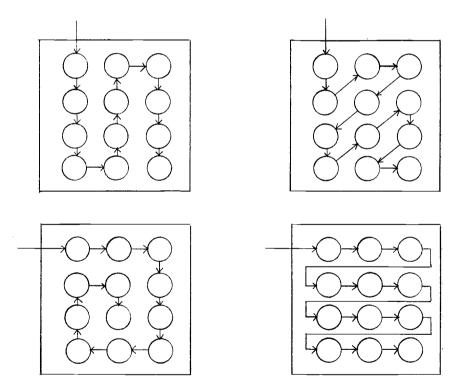

| 55     | Some possible arrangements of the programming bus in linear select scheme.                                                      | 130        |

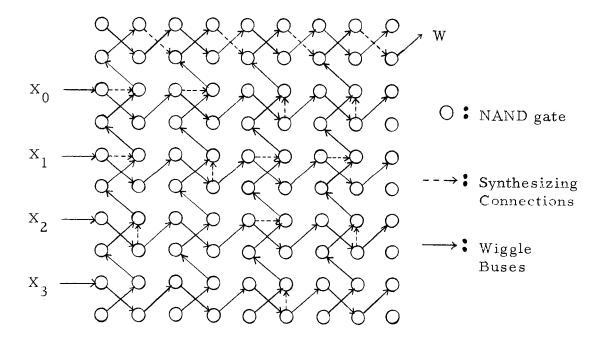

| A-1    | Two-input NAND gate array                                                                                                       | 139        |

| A-2    | Synthesizing arc for two-input NAND gate array.                                                                                 | 139        |

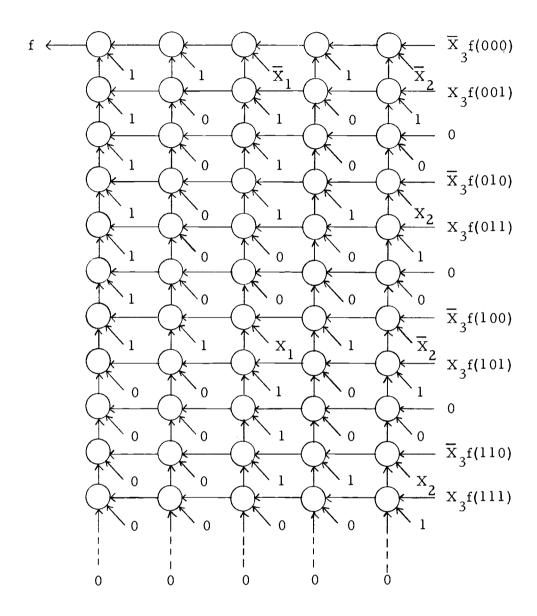

| A-3    | Cellular synthesis of the function $f = \overline{X}_1 X_3 + X_2 \overline{X}_3 + X_1 X_2 X_3$ using two-input NAND gate array. | 140        |

| A-4    | Diamond array synthesis of the function $f = \overline{X}_1 X_3 + X_2 \overline{X}_3 + X_1 X_2 X_3.$                            | 141        |

| A-5    | Majority-gate array for three variable functions.                                                                               | 142        |

| A-6    | Functional description of a cutpoint cell.                                                                                      | 143        |

| A-7    | Cutpoint cellular synthesis of the function $f = \overline{X}_1 X_3 + X_2 \overline{X}_3 + X_1 X_2 X_3$ .                       | 144        |

# CELLULAR SYNTHESIS OF SYNCHRONOUS SEQUENTIAL MACHINES

#### I. INTRODUCTION

# 1.1 Problems, Objectives, and Results

The two major problems in designing a synchronous sequential machine are state reduction and state assignment. The latter is especially difficult and is still a subject of intensive research. However, if we can devise a new synthesis technique which is independent of the assignment of states, then we do not have to bother with this difficult state assignment problem.

It cannot be denied that the current computer hardware technology is going toward large scale integration (LSI). The advantages of LSI are many and are well known. Cellular circuits seem to be the best fitted for this new technology. But, though work has been done in cellular combinational circuits, there have been few results, as yet, in the cellular synthesis of sequential machines.

It is safe to predict that future computing systems will continue to increase the demands on several sophisticated design areas. They will need to be more readily expandable and modifiable. Automatic error detection and correction will also play a more significant role. Therefore, modularity, reliability, and programmability are all important aspects of any new design techniques.

Our objectives are to derive new synthesis techniques which do not require state assignment and can be achieved by interconnecting uniform building blocks in a regular pattern. For easy addition or reduction of building blocks as desired, we emphasize the uniformity and the regularity requirements. For simplicity, we consider only binary, finite-state, deterministic synchronous sequential machines of the Moore type. All of our techniques, however, can be extended to include other types of machines.

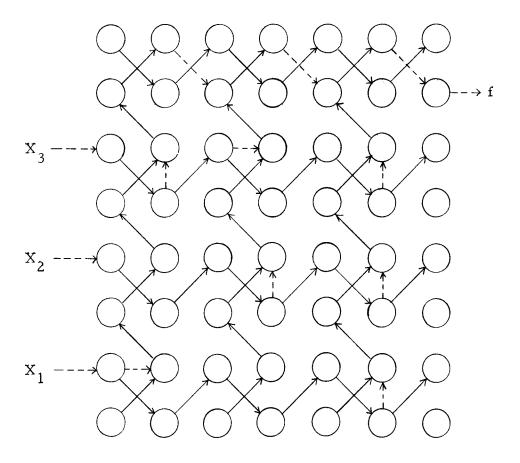

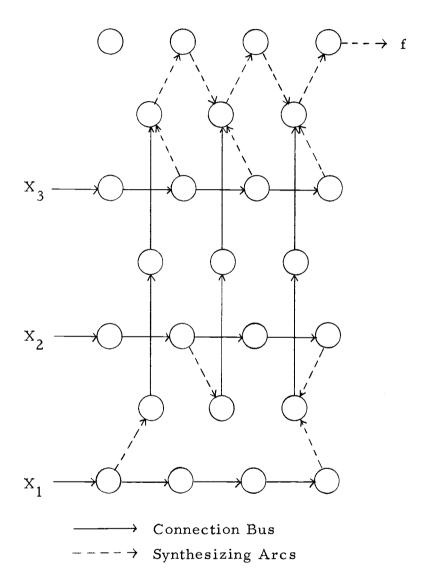

Two synthesis methods are developed, each is able to achieve the above objectives. The first method converts sequential functions into combinational-like equations. These combinational-like equations can then be implemented by conventional combinational cellular circuits together with delay elements. The second method employs an array of cells in which state transitions are accomplished by "row operations" and outputs are obtained by "column operations". Both methods are readily expandable to include features such as reliability and programmability. In each case, bounds on the number of cells are established and minimal realizations are studied. Methods of starting these cellular machines from a given state are also investigated.

For easy reference, all Figures are collectively given at the end of the text material and all example machines are listed in Appendix I.

Except where specific references are made, all developments presented in this paper are original.

#### 1.2 Definition of Terms

We define the following basic terms that are important to the understanding of this paper.

A sequential machine, SM, is a quintuple M=(I, Z, S, f, g), where  $I = (i_1, i_2, \dots, i_p)$  is a finite set of input symbols,  $Z = (z_1, z_2, \dots, z_q)$  is a finite set of output symbols,  $S = (s_1, s_2, \dots)$  is a set of states,  $S = (s_1, s_2, \dots)$  is a set of states,

and and

g :  $S \rightarrow Z$  is the output function.

A sequential machine in which the state set S contains only a finite number of elements is called a finite-state machine. A machine that satisfies all of the above requirements is called a Moore machine. If f is defined for all values of SXI the machine is transition complete; otherwise it is transition incomplete and the undefined values are called "don't cares". Similarly, if g is defined for all values of S, the machine is output complete; otherwise it is output incomplete and the unspecified values are also don't cares. If both transition and output are complete, the machine is completely specified; otherwise it is incompletely specified. Since the transition function and the output function characterize a machine, they are referred to as characterizing functions. A machine whose characterizing functions are not

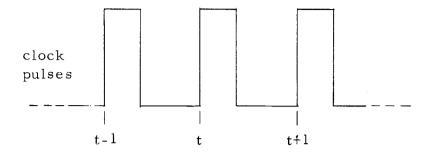

subject to any uncertainty is <u>deterministic</u>. When inputs and outputs of a machine are restricted to binary signals, the machine is a <u>binary machine</u>. A sequential machine is <u>synchronous</u> if the transition of states occurs only at prescribed instances of time controlled by a clock. The time unit in synchronous sequential machines is one clock time (see Figure 1).

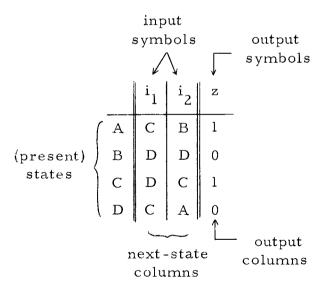

A sequential machine is often described by a flow table. A <u>flow</u> table for a Moore machine is the tabular form of Figure 2. Columns labelled by input symbols are <u>next-state columns</u>; columns labelled by output symbols are <u>outout columns</u>; each row represents a state of the machine; each entry at the intersection of the h-th input column and the j-th state row is the next-state  $f(s_j, i_h)$ ; the entries in the output columns at the j-th state row are outputs  $g(s_j)$ .

A next-state column is a permutation column if every state of the machine appears exactly once in that column; a next-state column is a reset column if all entries in that column are the same. A machine that consists only of permutation columns is a permutation machine; a machine that consists only of reset columns is a reset machine; a machine that consists only of permutation and reset columns is a permutation-reset machine or simply a P-R machine.

Zeiger in 1967 [29] showed that any machine can be composed of cascaded connections of only P-R machines.

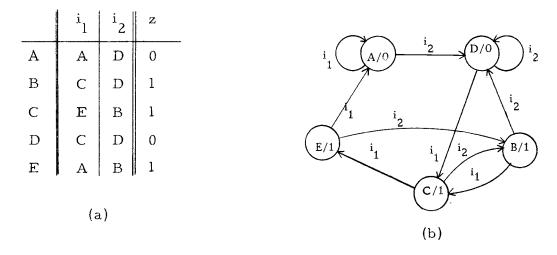

A machine can also be represented by a state graph, which is an alternative representation of the flow table. An example of a state graph for a Moore machine (Figure 3a) is shown in Figure 3b. Each node in the graph is a state-output pair. There are as many nodes as there are states. There is an arrow labeled by  $i_h$  going from node  $s_i$  to node  $s_i$  if and only if  $s_i = f(s_i, i_h)$ . If there exists a finite sequence of arrows going from node  $s_i$  to node  $s_i$  is said to be a predecessor state of the state  $s_i$  and state  $s_i$  a successor state of the state  $s_i$ . If there exists such a sequence in which the number of arrows is exactly one, then state  $s_i$  is an immediate predecessor of the state  $s_i$  and state  $s_i$  and immediate successor of the state  $s_i$  is called a transient state if there is a state  $s_i \in S$  such that  $s_i$  is not a predecessor state of  $s_i$ .

In circuit realizations of machines, sometimes an output is routed back into the circuit and is used as a decision influence parameter. This is called <u>feedback</u>. The function that describes this feedback is the <u>feedback function</u>. Since a feedback is essentially another input to the circuit, it is often referred to as a <u>feedback input</u>. If a machine can be realized without any feedback inputs, it is said to be <u>feedback free</u>. Friedman in 1966 [7] showed that any finite-state machine can be realized by sequential circuits with at most one feedback input. If none of the available output functions can be used as the feedback function, then an additional function must be constructed. If

we let F be this feedback function, then a machine is <u>finite input and</u> <u>feedback memory (FIFM)</u> if and only if its characterizing functions can be described by the present inputs and a finite number of past inputs and a finite number of past feedbacks. That is, for every non-transient state s at any given time t,

$$s_t = G(I_t, I_{t-1}, \dots I_{t-k_1}, F_{t-1}, F_{t-2}, \dots, F_{t-k_2}),$$

where  $k_1$  and  $k_2$  are smallest integers such that the above equation holds for all non-transient states of the machine.  $k_1$  is called the input memory of the machine;  $k_2$  is the feedback memory of the machine. Let

$$K = \max(k_1, k_2),$$

K is the <u>memory</u> of the machine. When K=0, the machine is combinational; otherwise it is sequential. If  $k_2=0$ , it is feedback free and is often called <u>definite</u>. Thus, in a feedback free machine, all non-transient states can be distinguished by applying a finite number of successive inputs. Transient states can be entered only by external manipulations and will be discussed later.

## 1.3 Historical Background

Aside from the general switching theory, the following areas are of special interest to this study.

A. Machine Decomposition. The decomposition of machines by partition was first introduced by Hartmanis and later expanded by Hartmanis and Stearns [10]. Gill [8], Yoeli [27] and Kohavi and Smith [13] also made considerable contributions in this area. Another approach to the problem of decomposition of machines is by the theory of semigroups. Krohn and Rhodes in 1962 [14] proved an abstract theorem which in effect says that any machine can be composed of cascaded connections of only two types of machines. This theorem was also proved by Zeiger in 1967 [29] who introduced P-R machines. Most of the work in this area are well discussed in the book by Hartmanis and Stearns [10]. The theory of machine decomposition provides us a good understanding of machine structures and difficulties involved in cellularizing sequential circuits by way of decompositions.

B. Definite Machines. A pioneer paper in the area of feedback free machine was given by J. M. Simon (1959) in his "A Note on the Memory Aspects of Sequential Transducers" [23]. Gill treated this subject in his 1962 book and called it an "output-independent machine" [9]. A more complete but abstract treatment of the topic was given by Perles, Rabin and Shamir in 1963 [20]. Several persons, such as Brzozowski [1] and Friedman [7], have since used the properties of definite machines for feedback studies. The FIFM machine which will be the center of this study is really an extension of the definite machine

to include a feedback.

- C. Shift Registers and Feedbacks. Elspas' paper [4] presented an excellent state-of-the-art compilation of linear feedback shift register circuits in 1959. Since then, the work has received much attention and has been expanded by many. Among them are Brzozowski [1] and Friedman [7]. Their results will be the bases for this study. They both discussed single-loop realizations of sequential machines. As was mentioned, properties of definite machines are used in their studies. Friedman showed that all sequential machines can be realized using only one feedback loop and presented techniques of constructing this feedback function.

- D. Cellular Circuits. Cellular circuits can actually be identified in designs of contact arrays in the 1930's and diode arrays in 1947. The contemporary investigation of cellular circuits was initiated in 1962 by Maitra in his classical paper "Cascaded Switching Networks of Two-input Flexible Cells" [16]. Unfortunately, the Maitra cascade is not logically complete. Short [22] in 1965 proposed two-rail cascades and these were shown to be complete. Other major contributions are made by Minnick and Short (1964)[17], and Spandorfer and Tonik (1965) [24] in fixed cell arrays and Minnick (1964) [18] in variable cell arrays. A good summary of results in this area with extensive

bibliography can be found in [19]. More recent and advanced theory of cellular logic can be found in a series of SRI reports [5, 6].

#### II SM SYNTHESIS USING FIFM PROPERTY

#### 2.1 Introduction

Friedman [7] has shown that all finite-state sequential machines can be realized by circuits with only one feedback. Hence we shall start our discussion by limiting the number of feedbacks to either zero or one. The following questions must be answered for efficient synthesis of a sequential machine.

- 1. Can we realize the machine without any feedback?

- 2. If the answer to question l is negative, can we use one of the outputs as the feedback?

- 3. If answers to both questions 1 and 2 are no, how can we construct a function which can be used as the feedback function?

The first two questions will be answered in Section 2.2 by giving testing procedures. The third question will be answered by illustrations in Section 2.3. In Section 2.4 we shall show that the memory K of a machine can be obtained from the tests performed. Two methods of characterizing an FIFM machine are given in Section 2.5. These characterizations will lead us directly to the hardware synthesis of sequential machines. In Section 2.6 we shall study three types of cellular structures. They are the linear cascade, the array, and the tree. Some aspects of minimal realizations and bounds on the number

of cells required will be discussed in Section 2.7. The question of how to initialize a machine to a certain desired state in cellular structures will be ansered in a separate chapter.

## 2.2 Tests for FIFM

### 2.2.1 Definiteness Test

Tests to determine whether a machine is feedback free or not are called <u>definiteness tests</u>. We present two definiteness test methods.

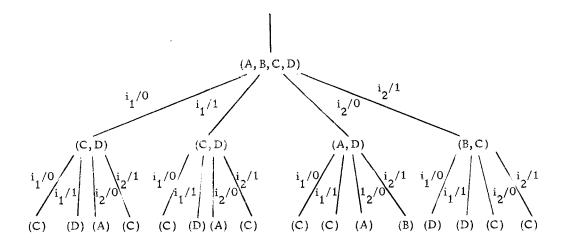

A. D-successor Tree Method. A state set is an unordered collection of a finite number of states in which all elements (states) are distinct. Let  $A \subseteq S$  be a state set consisting of states  $s_1, s_2, \dots, s_r$ , the  $i_h$ -successor of the state set A is another state set  $B \subseteq S$ , formed by next states  $f(s_1, i_h)$ ,  $f(s_2, i_h)$ , ...,  $f(s_r, i_h)$  with don't cares and repeating states eliminated. A D-successor tree is a tree structure as shown in Figure 4 for Ml. The structure is composed of branches arranged in successive levels, the highest level being the zeroth level. In a machine with p input symbols, each branch in the j-th level is plit into p branches in the (j+1)st level. The state sets in the (j+1)st level under the j-th level state set A are  $i_h$ -successors of the state set A, where  $h = 1, 2, \cdots, p$ . Two state sets are said to be connected if they are connected by branches going only upward (or

downward). A state set including all states of a machine is called the universal state set, designated by 1. Hence l = S. A state set with no states is a null state set, designated by  $\emptyset$ .

A D-successor tree always starts with the universal state set.

Any state that is not a successor state of any state (including the state itself) of the machine will disappear in the lower levels of the D-successor tree. Each branch of the tree is terminated by one of the following conditions.

- 1. The state set consists of a single state.

- 2. The state set is empty (don't cares only).

- 3. The state set is identical to a connected state set appearing in a lower order level.

Lemma 2.1. A machine M is not definite (i.e., is not feedback free) if and only if at least one of the branches in its D-successor tree is terminated by condition 3.

Proof: Without loss of generality, we assume, as an example, that state set (A, B) is a terminal state set due to condition 3. That is, state set (A, B) repeats itself along a path in the tree. We name this path R. In this case, we can write equations in the form given at the top of page 6 neither for state A nor for state B because an input sequence corresponding to the path R (or multiple repititions of R) could not determine whether the machine is in state A or in state B.

In other words, knowing a finite number of successive inputs is not enough to determine whether the machine is in state A or in state B.

On the other hand, if M is not definite, then at least two states, say C and D, cannot be distinguished by a finite number of successive inputs. This implies that at least one branch in the D-successor tree is terminated by condition 3 with the state set (C, D). For, if it is terminated by condition 1, say with state C, then only state C will have the term corresponding to this path. If it is terminated by condition 2, then the state corresponding to this path is undefined.

O.E. D.

Theorem 2.2. A machine M is feedback free (definite) if and only if its D-successor tree is terminated by conditions 1 and 2.

Proof: By contra positive of Lemma 2.1

Q. E. D.

Corollary 2.3. If a machine is completely specified and feedback free, its D-successor tree is terminated by condition 1.

Hence, to test whether a machine M is feedback free or not, we construct the D-successor tree of M. A machine is not feedback free as soon as we find a branch in the D-successor tree that is terminated by condition 3. If every branch of the tree is terminated by either conditions 1 or 2, then M is feedback free. Figure 4 shows the D-successor tree of M1. Since some of its branches are terminated by condition 3, M1 is not a feedback free machine.

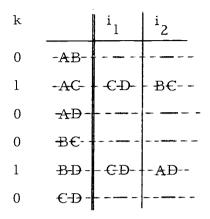

- B. D-pair table Method. A D-pair table is a flow table of the form shown in Figure 5.

- A column for every input symbol; no output columns are needed.

- 2. A row for each pair of distinct states  $s_i$  and  $s_k$ .

- 3. The entry at the intersection of the  $i_h$ -column and the  $(s_j, s_k) row is (s_u, s_v) or (s_v, s_u) where s_u = f(s_j, i_h) and$  $s_v = f(s_k, i_h). \text{ If } s_u = s_v \text{ enter only } s_u(\text{or } s_v).$

As an example, the D-pair table of Ml is given in Figure 5.

To test whether a given machine is feedback free or not, we follow

Algorithm 2.1.

Algorithm 2.1. (D-pair table test)

- 1. Construct the D-pair table of the machine.

- 2. Let k = 0.

- 3. Cross out the rows in which all next-state entries are either one of the following types or combinations of them.

- a. don't care,

- b. single state,

- c. a state pair have already been crossed out in an earlier iteration.

- 4. If not even a single row can be crossed out in step 3, go to step 7; otherwise go to step 5.

- 5. If all rows of the table have been crossed out, go to step 8; otherwise go to step 6.

- 6. Let k = k+1, go to step 3.

- 7. The machine is not feedback free. Stop.

- 8. The machine is feedback free. Stop.

Theorem 2.4. Algorithm 2.1 works.

<u>Proof:</u> The D-pair table method is equivalent to the D-successor tree method going backwards. A crossed-out state pair in the D-pair table represents a pair of states that can be distinguished by a finite input sequence. If every state pair in the D-pair table is crossed out, then every pair of states can be distinguished by a finite number of successive inputs. Hence M is feedback free. Q. E. D.

Figure 5 shows the D-pair table of Ml. Since no rows can be crossed out by following the steps of Algorithm 2.1, we conclude that Ml is not feedback free, which agrees with the conclusion of the D-successor tree test.

# 2.2.2 Finiteness Tests

Tests to determine whether a machine can use one of its output functions as the feedback are called <u>finiteness tests</u>. Since feedback free machines are particular cases of FIFM machines, we would expect that the testing methods presented in the previous section can be

expanded for finiteness tests. This is indeed the case.

A. F-successor Tree Method. Let A be a state set consisting of states  $s_1, s_2, \dots, s_r$ , the  $\frac{i}{h}/z_d$ -successors of the state set A are state sets formed by next states  $f(s_1, i_h)$ ,  $f(s_2, i_h)$ ,  $\cdots$ ,  $f(s_r, i_h)$  with equal  $z_d$ -output. Thus in a binary machine, there are two  $i_h/z_d$ successors to each state set. Don't cares and repeating states are eliminated in all state sets. An F-successor tree is a tree structure similar to a D-successor tree as shown in Figure 6. Each branch in the j-th level is split into 2p branches in the (j+1) -st level, where p is the number of input symbols. The state sets in the (j+1)-st level under the state set A of the j-th level are  $i_h/z_d$ -successors of A. To form an F-successor tree we always start with the universal state set as the zeroth level state set. The conditions for terminating a branch are identical to those given for the D-successor trees. The following properties are analogous to Lemma 2.1 and Theorem 2.2 and are presented without proof.

Lemma 2.5. An output function  $z_d$  of a machine M can <u>not</u> be used as the feedback function if and only if at least one of the branches in its F-successor tree is terminated by condition 3.

Theorem 2.6. An output function  $z_d$  of a machine M can be used as the feedback function to make M an FIFM machine if and only if its F-successor tree is terminated by conditions 1 and 2.

In summary, if we wish to test whether an output function  $z_d$  can be used as the feedback function, we simply construct the F-successor tree for  $z_d$ . Conclusions can then be drawn according to the above Lemma and Theorem. Figure 6 shows the F-successor tree of Ml. It shows that the output function can be used as the feedback function.

B. F-pair Table Method. An F-pair table for an output z is a flow table of the following form.

- A column for every input symbol; no output columns are needed.

- 2. A row for each pair of distinct states  $s_j$  and  $s_k$ .

- 3. If  $g(s_j) = g(s_k)$  for  $z_d$ , the entry at the intersection of  $(s_j, s_k)$ -row and  $i_h$ -column is  $(s_u, s_v)$  or  $(s_v, s_u)$  where  $s_u = f(s_j, i_h)$  and  $s_v = f(s_k, i_h)$ . If  $g(s_j) \neq g(s_k)$  for  $z_d$ , the entries at the row  $(s_j, s_k)$  are don't cares under all inputs.

As an example, the F-pair table of Ml is given in Figure 7.

Algorithm 2.2 describes the procedures of performing the F-pair table test.

Algorithm 2.2.(F-pair Table Test)

- 1. Let c = 0, d = 1.

- 2. Construct the F-pair table for  $z_d$ .

- 3. Let k = 0.

- 4. Cross out all rows in which all next state entries are either one of the following types or combinations of them.

- a. don't care,

- b. single state,

- c. a state pair have already been crossed out in an earlier iteration (smaller k but same d).

- 5. If not even a single row can be crossed out in step 4, then z<sub>d</sub> cannot be used as the feedback function, go to step 10. If all rows have been crossed out, go to step 8; all other cases go to step 7.

- 7. Let k = k + 1, go to step 4.

- 8. z can be used as the feedback function. If we wish to continue tests of other output functions, go to step 9; otherwise stop.

- 9. Let c = c + 1.

- 10. Is d = q? If not, go to step 11; if yes, go to step 12. q is

the number of output functions.

- 11. Let d = d + 1, go to step 2.

- 12. Stop. c = the number of output functions can be used as the feedback function. If c = 0, there is no output function can be used as the feedback function.

Theorem 2.7. Algorithm 2.2 works.

Proof: By following the proof of Theorem 2.4. Q.E.D.

Figure 7 shows the F-pair table of Ml. Since all rows can be crossed out by carrying out Algorithm 2.2, we conclude that Ml is FIFM by using the output function as the feedback function.

# 2.3. Converting non-FIFM Machines to FIFM Machines--Construction of the Feedback Function

If we find a machine is not feedback free and also none of its output functions can be used as the feedback function, how can we construct a function such that the machine becomes FIFM? Friedman [7] has answered this question. In this section, we simply present the basic principles involved and illustrate them by simple examples.

More detailed treatment can be found in Friedman's paper.

A <u>D-implication graph</u> of a machine M is a state graph constructed according to the D-pair table of M. A <u>loop</u> on a D-implication graph is a closed directed path. If the path does not pass through any node more than once, then the loop is called an <u>elementary loop</u>. A machine M is feedback free if and only if the D-implication graph of M has no elementary loops.

Figure 8a shows the flow table of M3. The D-pair table test in Figure 8b shows that M3 is not feedback free. The F-pair table test in Figure 8c tells us that the output function cannot be used as the feedback function. Hence, we must construct a function, together with the inputs, will make M an FIFM machine. We call this function F.

F is not only an output function but also an input. The D-implication graph of M3 is shown in Figure 8d. There are four elementary loops in that graph. They are

1. (C, D)

$$\stackrel{i_1}{\rightarrow}$$

(C, D)

2. (C, D)

$$\stackrel{i_2}{\rightarrow}$$

(A, C)  $\stackrel{i_1}{\rightarrow}$  (C, D)

3. (C, D)

$$\stackrel{i_2}{\rightarrow}$$

(A, C)  $\stackrel{i_2}{\rightarrow}$  (B, C)  $\stackrel{i_2}{\rightarrow}$  (C, D)

4. (A, B)

$$\stackrel{i_2}{\rightarrow}$$

(B, D)  $\stackrel{i_2}{\rightarrow}$  (A, D)  $\stackrel{i_2}{\rightarrow}$  (A, B)

Since it is the elementary loops that are causing the trouble, we wish to add an additional input, F, such that all elementary loops become non-loop. To do so, at least one state pair in each loop should have different values of F for the two states. For example, if we assign 0 as the F value for state C and 1 for state D, then the state pair (C, D) will go to state C under input  $i_1$ -0 (original input plus F) and will go to state D under input  $i_1$ -1. Thus eliminate the elementary loop (1). Hence, to break the elementary loop (1), state C and D should have different F values. Similarly, to break the elementary loop (2), either states C and D or states A and C should be assigned different F values. Similar reasonings apply to the other two loops. If we use the notations

A = state A has assigned F value 1,

$A_0$  = state A has assigned F value 0,

$$A_1 B_0 = A_1$$

and  $B_0$ ,

$A_1 + B_0 = A_1$  or  $B_0$ ,

then, we can write the requirements for F in a more compact form.

To break loop (1), we need

$$C_0D_1 + C_1D_0$$

;

to break loop (2), we need  $C_0D_1 + C_1D_0 + A_0C_1 + A_1C_0$ ;

to break loop (3), we need  $C_0D_1 + C_1D_0 + A_0C_1 + A_1C_0 + B_0C_1 + B_1C_0$ ;

to break loop (4), we need  $A_0B_1 + A_1B_0 + B_0D_1 + B_1D_0 + A_0D_1 + A_1D_0$ .

F must satisfy all above criteria. Hence,

$$F = (C_0D_1 + C_1D_0)(C_0D_1 + C_1D_0 + A_0C_1 + A_1C_0)$$

$$(C_0D_1 + C_1D_0 + A_0C_1 + A_1C_0 + B_0C_1 + B_1C_0)$$

$$(A_0B_1 + A_1B_0 + B_0D_1 + B_1D_0 + A_0D_1 + A_1D_0).$$

(2.1)

By using the obvious properties that

$$A_0 A_1 = 0,$$

$A_0 + A_1 = 1,$   $A_1 A_1 = A_1,$   $A_1 + A_1 = A_1,$   $A_0 A_0 = A_0,$   $A_0 + A_0 = A_0,$   $A_$

We can simplify Equation 2.1 to

$$F = (C_0D_1 + C_1D_0)(1 + A_0C_1 + A_1C_0(1 + B_0C_1 + B_1C_0))$$

$$(A_0B_1 + A_1B_0 + B_0D_1 + B_1D_0 + A_0D_1 + A_1D_0)$$

$$= (C_0D_1 + C_1D_0)(A_0B_1 + A_1B_0 + B_0D_1 + B_1D_0 + A_0D_1 + A_1D_0)$$

$$= B_1C_1D_0 + B_0C_0D_1 + A_1C_1D_0 + A_0C_0D_1.$$

(2.2)

Hence, F can be obtained by choosing any one of the following assignments:

a.

$$B_1C_1D_0$$

, i.e., 1--B, 1--C, 0--D, A can be either 0 or 1,

b.

$$B_0C_0D_1$$

, i.e., 0--B, 0--C, 1--D, A can be either 0 or 1,

c.

$$A_1C_1D_0$$

, i.e., 1--A, 1--C, 0--D, B can be either 0 or 1,

d.

$$A_0 C_0 D_1$$

, i.e., 0--A, 0--C, 1--D, B can be either 0 or 1.

Note that whatever assignments we choose, the F values are associated with states and can be obtained by making F an output function of the machine. Figure 9a shows M3' (M3 with an added output F). The F-pair table test of M3' using F as the feedback function is shown in Figure 9b. It shows that M3' is an FIFM machine. Thus, F is a valid feedback function.

There are cases when a simple feedback function cannot be found because of conflicting conditions required to resolve all elementary loops. In these cases, some or all states have to be split. The process of state splitting is given in [7].

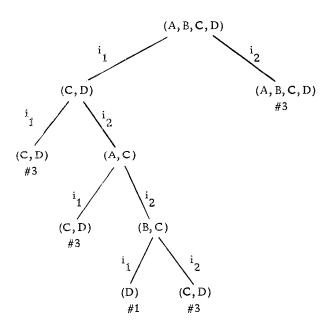

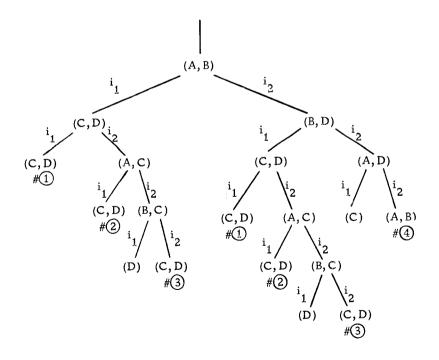

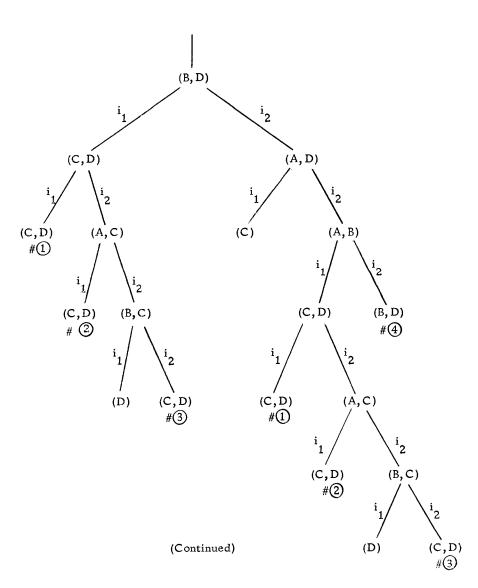

Sometimes when the D-implication graph is complicated, it is rather difficult to find all elementary loops. D-pair trees may be helpful in this respect. A <u>D-pair tree</u> is like a D-successor tree except that it is constructed according to the D-pair table and the

zeroth level state set is a state pair. To find all elementary loops, we construct a D-pair tree for every state pair of the machine. Any branch which is terminated by condition 3 represents an elementary loop (not necessarily different from the other elementary loops). As an example, the D-pair trees of M3 are given in Figure 10. Though all four types of elementary loops are evident in the first D-pair tree, in general we must construct all D-pair trees of M to make sure that there are no other loops. Of course, experience can always cut a great amount of unnecessary work.

## 2.4. Determination of K

In this section, we shall relate the memory  $\,K\,$  of a machine  $\,M\,$  to the testing methods of earlier sections.

Theorem 2.8. The memory K of a feedback free machine M is equal to the last level number, L, in a longest branch of the D-successor tree. i.e., K = L.

<u>Proof:</u> Without loss of generality, we assume that the state set along a longest branch in the (L-1)st level is (A, B). Then, one of the following conditions must be true for  $h = 1, 2, \dots, p$ .

a.

$$f(A, i_h) = f(B, i_h)$$

or

b.  $f(A, i_h)$  and/or  $f(B, i_h)$  are undefined.

If not, then the tree would either have (L+1)-st level or is terminated by condition 3 --- both contradict our assumptions. Therefore, L

past inputs together with the present input are sufficient to determine the present state of M. It is obvious that L is the minimal number of successive past inputs required. Hence, K = L. Q.E.D.

Theorem 2.9. The memory K of a feedback free machine M is equal to the final k value in carrying out the D-pair table test.

Let N be the final k value, then K = N.

Proof: By similar arguments given above. Q.E.D.

Theorem 2.10. The memory K of an FIFM machine with  $z_d$  as the feedback function is equal to the total number of levels in a longest branch of the F-successor tree for  $z_d$ . i. e., K = L + 1.

<u>Proof</u>: Similar to that of Theorem 2.8. Since the feedback obtained at t-1 is used as an input at t, the feedback input at t-L is the feedback obtained at t-(L+1). In other words, the feedback input has one more delay than the original inputs. Hence, K = L + 1. Q.E.D.

Theorem 2.11. The memory K of an FIFM machine M with  $z_d$  as the feedback is equal to the total number of iterations required in carrying out the F-pair table test for  $z_d$ . i.e., K = N + 1.

Proof: Obvious. Q.E.D.

If an added function is used as the feedback function, we simply consider it as an output function  $z_d$  and K can then be found. From the above results, we can see that if different output functions

are used as the feedback function, we may have different memory K. For economy (see Section 2.7), we usually choose the output function that will give the minimal K as the feedback function. By the same reason, we always select the feedback function, among all possibilities, the one will give minimal K. This is done, more or less, by trial and compare method.

## 2.5. Characterization of FIFM Machines

In this section we shall introduce two methods of characterizing a machine using the results developed earlier in this chapter. They will lead us to easy construction of sequential circuits in the subsequent section.

## 2.5.1 Difference Equations

When time also becomes a factor in a Boolean equation, it is called a difference equation. We define

$$\Delta^{O} f(t) = f(t).$$

$$\Delta f(t) = \Delta^{I} f(t) = f(t-1).$$

$$\Delta^{M} f(t) = f(t-m).$$

$$\Delta^{-M} f(t) = f(t+m).$$

Δ is called the difference operator. Examples:

$$\Delta^{O}(x_{t} + y_{t-1} + x_{t-2}z_{t}) = x_{t} + y_{t-1} + x_{t-2}z_{t}.$$

$$\Delta(x_{t} + y_{t} + x_{t-1}y_{t-1}) = x_{t-1} + y_{t-1} + x_{t-2}y_{t-2}$$

$$\Delta^{O}(x_{t}) = x_{t-3}$$

$$\Delta^{-O}(x_{t-2} + y_{t-3} + z_{t-4}) = x_{t} + y_{t-1} + z_{t-2}$$

Some direct and obvious properties of the difference operator are given below.

$$\begin{split} & \Delta C = C, \quad C \quad \text{is a constant.} \\ & \Delta \left[ \Delta f(t) \right] = \Delta^2 f(t). \\ & \Delta^m \left[ \Delta^n f(t) \right] = \Delta^n \left[ \Delta^m f(t) \right] = \Delta^{m+n} f(t). \\ & \Delta^m \left[ f(t) + g(t) \right] = \Delta^m f(t) + \Delta^m g(t). \\ & \Delta^m \left[ f(t) \right] \left\{ g(t) \right\} = \left\{ \Delta^m f(t) \right\} \left\{ \Delta^m g(t) \right\}. \\ & \Delta^m \left[ f(t) + g(t) \right] = \Delta^m f(t) + \Delta^m g(t). \\ & \Delta^m \left[ f(t) \right] \left[ \Delta^n f(t) \right] = \left\{ \Delta^m f(t) \right] \left[ \Delta^m f(t) \right] \left[ \Delta^n g(t) \right] \left[ \Delta^n f(t) \right] \left[ \Delta^n g(t) \right] \left[ \Delta^n f(t) \right] \left[ \Delta^n g(t) \right] \right] \\ & \left\{ \Delta^m f(t) + \Delta^n g(t) \right\} \left[ \Delta^m f(t) \right] \left[ \Delta^n g(t) \right] \left[ \Delta^n g(t) \right] \right] \end{split}$$

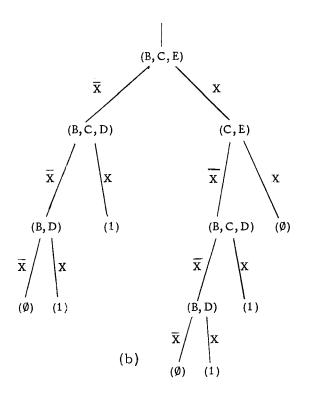

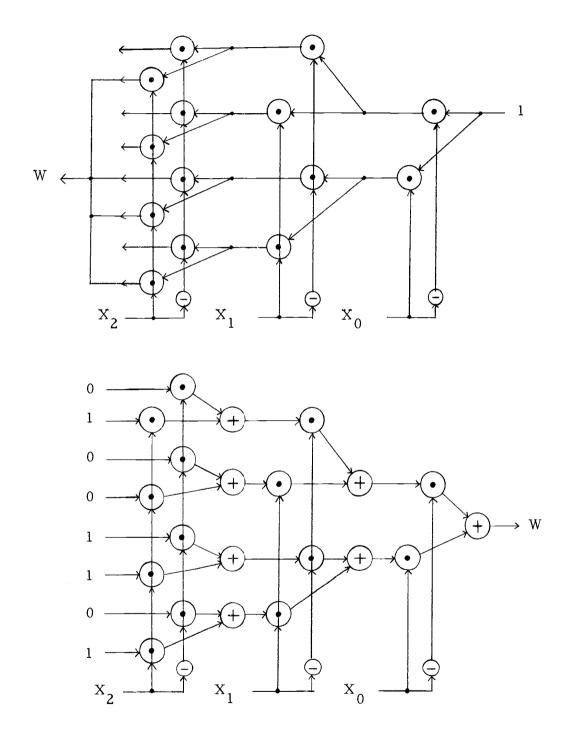

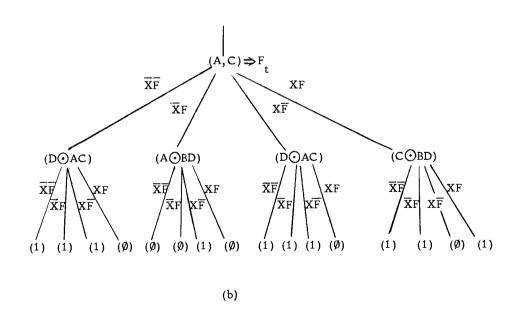

We now show that how an FIFM machine can be described by difference equations. M2 with X as the input variable is shown in Figure 11a. The D-pair table test in Figure 11b shows that M2 is a

feedback free machine with K = 3. Hence, we would expect that the machine can be described by the present input and three successive past inputs.

Note that the output of M2 is 1 when it is in states B, C or E. We associate our output Z with the state set (BCE).

$$Z_{t} = (BCE)_{t}$$

(2.3)

Also note that M2 is in the state set (BCE) only if it was (assuming zero transition time)

- 1. in the state set (BCD) and the input is  $\overline{X}$ , or

- 2. in the state set (CE) and the input is X.

In our notation,

$$(BCE)_t = \overline{X}_t \Delta(BCD)_t + X_t \Delta(CE)_t.$$

By similar reasonings,

$$(BCD)_{t} = \overline{X}_{t} \Delta (BD)_{t} + X_{t} \Delta (ABCDE)_{t} = \overline{X}_{t} \Delta (BD)_{t} + X_{t} \Delta I$$

$$= \overline{X}_{t} \Delta (BD)_{t} + X_{t},$$

$$(CE)_{t} = \overline{X}_{t} \Delta (BCD)_{t},$$

$$(BD)_{t} = \overline{X}_{t} \Delta (ABCDE)_{t} = X_{t} \Delta I = X_{t}.$$

Note that we use 1 for the universal state set and 0 for the empty set. Hence,

$$Z_{t} = (BCE)_{t}$$

$$= \overline{X}_{t} \Delta (BCD)_{t} + X_{t} \Delta (CE)_{t}$$

$$= \overline{X}_{t} \Delta \{ \overline{X}_{t} \Delta (BD)_{t} + X_{t} \} + X_{t} \{ \overline{X}_{t} \Delta (BCD)_{t} \}$$

$$= \overline{X}_{t} \Delta \{ \overline{X}_{t} \Delta (X_{t}) + X_{t} \} + X_{t} \Delta \{ \overline{X}_{t} \Delta [\overline{X}_{t} \Delta (BD)_{t} + X_{t} ] \}$$

$$= \overline{X}_{t} \Delta \{ \overline{X}_{t} \Delta (X_{t}) + X_{t} \} + X_{t} \Delta \{ \overline{X}_{t} \Delta [\overline{X}_{t} \Delta (X_{t}) + X_{t} ] \}$$

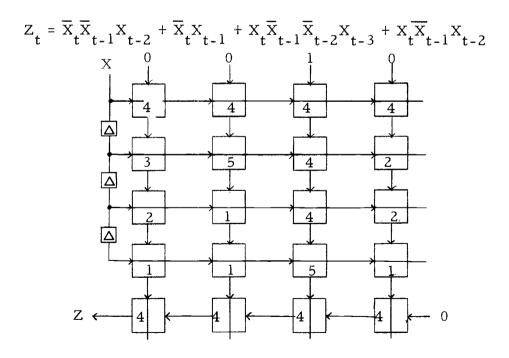

$$= \overline{X}_{t} \Delta \overline{X}_{t} \Delta^{2} (X_{t}) + \overline{X}_{t} \Delta X_{t} + X_{t} \Delta \overline{X}_{t} \Delta^{2} \overline{X}_{t} \Delta^{3} X_{t} + X_{t} \Delta \overline{X}_{t} \Delta^{2} X_{t}$$

$$= \overline{X}_{t} \overline{X}_{t-1} X_{t-2} + \overline{X}_{t} X_{t-1} + X_{t} \overline{X}_{t-1} \overline{X}_{t-2} X_{t-3} + X_{t} \overline{X}_{t-1} X_{t-2}$$

$$(2.4)$$

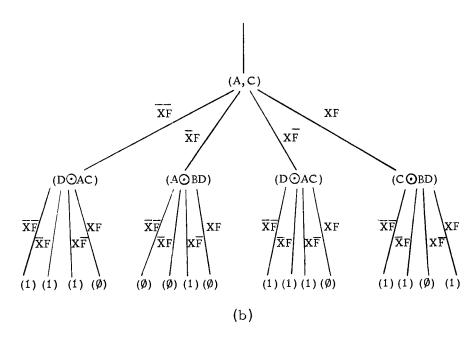

As another example, Ml is again given in Figure 12a. It was shown that Ml is FIFM using the output as the feedback. Since the feedback is used as another input, we expand the original flow table to that shown in Figure 12b. The next state entries for impossible combinations of inputs are don't cares, e.g., if the machine is in state A, then the Z value has to be 1. Hence the next state entries of A in the columns with  $\overline{F}$  (where  $\overline{F}_t$  is the same as  $\overline{Z}_{t-1}$ ) are don't cares.

$$Z_{t} = (AC)_{t}$$

$$(AC)_{t} = \overline{X}_{t} \overline{Z}_{t-1} \Delta (D \odot AC)_{t} + \overline{X}_{t} Z_{t-1} \Delta (A \odot BD)_{t} + X_{t} \overline{Z}_{t-1} \Delta (D \odot AC)_{t}$$

$$+ X_{t} Z_{t-1} (C \odot BD)_{t}$$

Notation: ⊙ → The term in front of ⊙ is required while the term after ⊙ is don't care and can either be included or not included as desired.

$$\begin{array}{lll} (\mathsf{D} \odot \mathsf{AC})_t &=& \overline{X}_t \overline{Z}_{t-1} \Delta (\mathsf{ABCD})_t + \overline{X}_t Z_{t-1} \Delta (\mathsf{ABCD})_t + X_t \overline{Z}_{t-1} \Delta (\mathsf{ABCD})_t \\ &+& X_t Z_{t-1} \Delta (\mathsf{O}) \\ &=& \overline{X}_t \overline{Z}_{t-1} + \overline{X}_t Z_{t-1} + X_t \overline{Z}_{t-1} \\ (\mathsf{A} \odot \mathsf{BD})_t &=& \overline{X}_t \overline{Z}_{t-1} \Delta (\mathsf{O}) + \overline{X}_t Z_{t-1} \Delta (\mathsf{O}) + X_t \overline{Z}_{t-1} \Delta (\mathsf{ABCD})_t + X_t Z_{t-1} \Delta (\mathsf{O}) \\ &=& X_t \overline{Z}_{t-1} \\ (\mathsf{C} \odot \mathsf{BD}) &=& \overline{X}_t \overline{Z}_{t-1} \Delta (\mathsf{ABCD})_t + \overline{X}_t Z_{t-1} \Delta (\mathsf{ABCD})_t + X_t \overline{Z}_{t-1} \Delta (\mathsf{O}) \\ &+& X_t Z_{t-1} \Delta (\mathsf{ABCD})_t \\ &=& \overline{X}_t \overline{Z}_{t-1} + \overline{X}_t Z_{t-1} + X_t Z_{t-1} \\ Z_t &=& (\mathsf{AC})_t \\ &=& \overline{X}_t \overline{Z}_{t-1} \Delta (\mathsf{D} \odot \mathsf{AC})_t + \overline{X}_t Z_{t-1} \Delta (\mathsf{A} \odot \mathsf{BD})_t \\ &+& X_t \overline{Z}_{t-1} \Delta (\mathsf{D} \odot \mathsf{AC})_t + \overline{X}_t Z_{t-1} (\mathsf{C} \odot \mathsf{BD})_t \\ &=& \overline{X}_t \overline{Z}_{t-1} \Delta (\overline{X}_t \overline{Z}_{t-1} + \overline{X}_t Z_{t-1} + X_t \overline{Z}_{t-1}) + \overline{X}_t Z_{t-1} \Delta (X_t \overline{Z}_{t-1}) \\ &+& X_t \overline{Z}_{t-1} \Delta (\overline{X}_t \overline{Z}_{t-1} + \overline{X}_t Z_{t-1} + X_t \overline{Z}_{t-1}) \\ &=& \overline{X}_t \overline{Z}_{t-1} \Delta (\overline{X}_t \overline{Z}_{t-1} + \overline{X}_t Z_{t-1} + X_t \overline{Z}_{t-1}) \\ &=& \overline{X}_t \overline{Z}_{t-1} \overline{X}_{t-1} \overline{Z}_{t-2} + \overline{X}_t \overline{Z}_{t-1} \overline{X}_{t-1} \overline{Z}_{t-2} + \overline{X}_t \overline{Z}_{t-1} \overline{X}_{t-1} \overline{Z}_{t-2} \\ &+& \overline{X}_t Z_{t-1} \overline{X}_{t-1} \overline{Z}_{t-2} + \overline{X}_t \overline{Z}_{t-1} \overline{X}_{t-1} \overline{Z}_{t-2} + \overline{X}_t \overline{Z}_{t-1} \overline{X}_{t-1} \overline{Z}_{t-2} \\ &+& X_t \overline{Z}_{t-1} \overline{X}_{t-1} \overline{Z}_{t-2} + \overline{X}_t \overline{Z}_{t-1} \overline{X}_{t-1} \overline{Z}_{t-2} + \overline{X}_t \overline{Z}_{t-1} \overline{X}_{t-1} \overline{Z}_{t-2} \\ &+& X_t \overline{Z}_{t-1} \overline{X}_{t-1} \overline{Z}_{t-2} + \overline{X}_t \overline{Z}_{t-1} \overline{X}_{t-1} \overline{Z}_{t-2} + \overline{X}_t \overline{Z}_{t-1} \overline{X}_{t-1} \overline{Z}_{t-2} \\ &+& X_t \overline{Z}_{t-1} \overline{X}_{t-1} \overline{Z}_{t-2} + \overline{X}_t \overline{Z}_{t-1} \overline{X}_{t-1} \overline{Z}_{t-2} + \overline{X}_t \overline{Z}_{t-1} \overline{X}_{t-1} \overline{Z}_{t-2} \\ &+& X_t \overline{Z}_{t-1} \overline{X}_{t-1} \overline{Z}_{t-2} + \overline{X}_t \overline{Z}_{t-1} \overline{X}_{t-1} \overline{Z}_{t-2} + \overline{X}_t \overline{Z}_{t-1} \overline{X}_{t-1} \overline{Z}_{t-2} \\ &+& X_t \overline{Z}_{t-1} \overline{X}_{t-1} \overline{Z}_{t-2} \end{array}$$

As the third example, we write the characterizing equations for M3 where F is the constructed feedback function. The expanded flow table with the feedback as one of the inputs is shown in Figure 13b.

$$Z_{t} = (CD)_{t} \tag{2.6}$$

$$F_{t} = (AC)_{t} \tag{2.7}$$

$$(CD)_{t} = \overline{X}_{t}\overline{F}_{t-1}\Delta(BD \odot AC)_{t} + \overline{X}_{t}F_{t-1}\Delta(AC \odot BD)_{t}$$

$$+ X_{t}\overline{F}_{t}\Delta(B \odot AC)_{t} + X_{t}F_{t-1}\Delta(C \odot BD)_{t}$$

$$(B \odot AC)_{t} = \overline{X}_{t}\overline{F}_{t-1}\Delta(0) + \overline{X}_{t}F_{t-1}\Delta(0) + X_{t}\overline{F}_{t-1}\Delta(0) + X_{t}F_{t-1}\Delta(ABCD)_{t}$$

$$= X_{t}F_{t-1}$$

$$(C \odot BD)_{t} = \overline{X}_{t}\overline{F}_{t-1}\Delta(ABCD)_{t} + \overline{X}_{t}F_{t-1}(ABCD)_{t} + X_{t}\overline{F}_{t-1}\Delta(0)$$

$$+ X_{t}F_{t-1}\Delta(ABCD)_{t}$$

$$= \overline{X}_{t}\overline{F}_{t-1} + \overline{X}_{t}F_{t-1} + X_{t}F_{t-1}$$

$$Z_{t} = (CD)_{t}$$

$$= \overline{X}_{t}\overline{F}_{t-1}\Delta(BD \odot AC)_{t} + \overline{X}_{t}F_{t-1}\Delta(AC \odot BD)_{t}$$

$$+ X_{t}\overline{F}_{t-1}\Delta(B \odot AC)_{t} + X_{t}F_{t-1}\Delta(C \odot BD)_{t}$$

$$= \overline{X}_{t}\overline{F}_{t-1} + \overline{X}_{t}F_{t-1} + X_{t}\overline{F}_{t-1}\Delta(C \odot BD)_{t}$$

$$= \overline{X}_{t}\overline{F}_{t-1} + \overline{X}_{t}F_{t-1} + \overline{X}_{t}F_{t-1}\Delta(C \odot BD)_{t}$$

$$= \overline{X}_{t}^{\overline{F}}_{t-1} + \overline{X}_{t}^{F}_{t-1} + X_{t}^{\overline{F}}_{t-1}^{X}_{t-1}^{F}_{t-2} + X_{t}^{F}_{t-1}^{X}_{t-1}^{\overline{F}}_{t-2} + X_{t}^{F}_{t-1}^{X}_{t-1}^{F}_{t-2} + X_{t}^{F}_{t-1}^{X}_{t-1}^{F}_{t-2}$$

$$+ X_{t}^{F}_{t-1}^{X}_{t-1}^{F}_{t-2} + X_{t}^{F}_{t-1}^{X}_{t-1}^{F}_{t-2}$$

(2.8)

Similarly,

$$F_{t} = \overline{X}_{t}^{\overline{F}}_{t-1} \overline{X}_{t-1}^{\overline{F}}_{t-2} + \overline{X}_{t}^{\overline{F}}_{t-1} \overline{X}_{t-1}^{F}_{t-2} + \overline{X}_{t}^{\overline{F}}_{t-1} X_{t-1}^{\overline{F}}_{t-2} + \overline{X}_{t-1}^{\overline{F}}_{t-2} +$$

The techniques described in this section are completely general and can be used for machines with multiple inputs and outputs. The difference equations thus obtained, however, may be long and it is easy to make mistakes in the calculations. We now introduce a more compact way of characterizing a sequential machine.

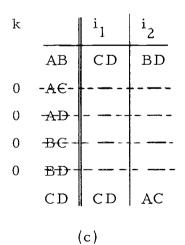

## 2.5.2 Predecessor Trees

When  $f(s_j, i_h) = s_k$ ;  $s_j$  is said to be the <u>immediate predecessor</u> state of  $s_k$  under  $i_h$ . We use the notation  $s_j = f^{-1}(s_k, i_h)$ . Let A be a state set consisted of states  $s_1, s_2, \dots, s_r$ , the  $i_h$ -predecessor of A is a state set formed by immediate predecessor states  $f^{-1}(s_l, i_h)$ ,  $f^{-1}(s_l, i_h)$ ,  $\dots$ ,  $f^{-1}(s_r, i_h)$ . The immediate predecessor states of don't care states can be included, if desired, in the  $i_h$ -predecessor

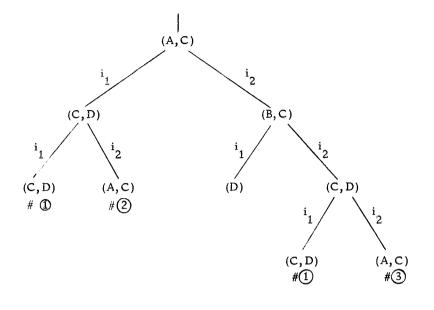

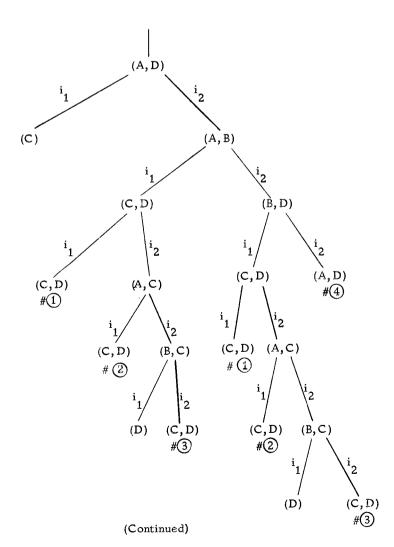

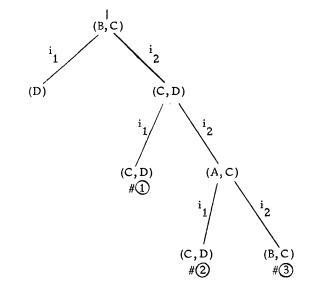

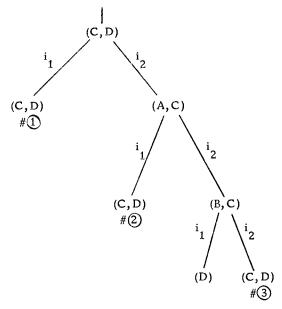

of A. The  $z_d$ -predecessor tree is a tree structure as shown in Figure 14. The structure is composed of branches arranged in successive levels, the highest level being the zeroth level and is a state set composed of states with g(s) = 1 for  $z_d$ . In a machine with p input symbols (including the feedback input ), each branch in the j-th level is split into p branches in the (j+1)-st level. The state set in the (j+1)-st level under a j-th level state set A and a branch  $i_h$  is the  $i_h$ -predecessor of A. A branch is terminated by meeting one of the following conditions.

- 1. A state set consisted of all states, (1)

- 2. A state set consisted of no states,  $(\emptyset)$

- 3. A state set repeats a connected state set appeared in an earlier level.

A machine that has identical outputs for all states or has nonzero outputs for transient states only is a trivial machine.

Lemma 2.12. For a nontrivial feedback free machine M, at least one branch of its predecessor tree is terminated by condition 1.

Proof: A nontrivial machine has at least one nontransient state, say state B, in the zeroth level state set of its predecessor tree. By definition, a feedback free machine is a machine which can start on any state and be led to any nontransient state by an input sequence.

This is the case for state B. Hence, there must be a branch in the

tree, corresponding to that input sequence, that is terminated by condition 1. Q.E.D.

Theorem 2.13. The predecessor tree of a feedback free machine M is terminated by conditions 1 and/or 2.

<u>Proof:</u> Necessity: 1. There are branches which are terminated by condition 1 as was discussed in Lemma 2.12. 2. There are states under a specified input does not have any predecessor states.

If every state in a state set has no predecessor under  $i_h$ , then the  $i_h$  branch under that state set is empty and is terminated by condition 2.

Sufficiency: We simply show that whenever a branch of a predecessor tree is terminated by condition 3, then M is not a feedback free machine. Without loss of generality, we assume that a state set (A, B) repeats itself along a certain path of the tree. If we consider this path in reverse order, it is exactly an elementary loop in a D-pair tree (or D-implication graph). Hence, M is not feedback free. Q. E. D.

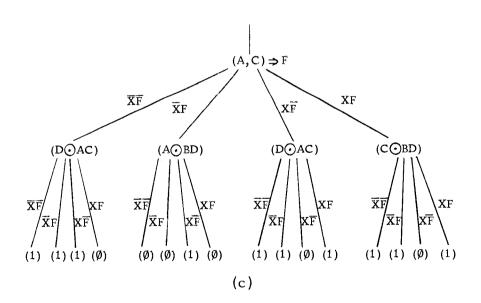

If in an FIFM machine, we consider F as an output and the feedback input as another input, the expanded machine, e.g., Figure 13b, can be thought as feedback free. Hence, an FIFM machine can also be characterized by predecessor trees. Examples used in Section 2.5.1 are again used in Figures 14--16 to illustrate this characterization technique.

Note that the reasoning behind the construction of predecessor trees is exactly the same as that of difference equations. Hence, there are close relations between the two. If we consider the branch between the zeroth level and the first level corresponding to the input at time t and the feedback at t-1, those between the first level and the second level corresponding to the input at time t-1 and the feedback at t-2, etc., we can easily write the difference equations for a given machine from its predecessor trees. The difference equation consists of a sum of product terms. Each product term is formed by the product of the terminal condition and the path leading to that terminal from the zeroth level. For example, the difference equation of M1 can be obtained from Figure 15b.

$$\begin{split} Z_t &= \overline{X}_t \overline{Z}_{t-1} (1 \cdot \overline{X}_{t-1} \overline{Z}_{t-2} + 1 \cdot \overline{X}_{t-1} Z_{t-2} + 1 \cdot X_{t-1} \overline{Z}_{t-2} + \cancel{\emptyset} \cdot X_{t-1} Z_{t-2}) \\ &+ \overline{X}_t Z_{t-1} (\cancel{\emptyset} \cdot \overline{X}_{t-1} \overline{Z}_{t-2} + \cancel{\emptyset} \cdot \overline{X}_{t-1} Z_{t-2} + 1 \cdot X_{t-1} \overline{Z}_{t-2} + \cancel{\emptyset} \cdot X_{t-1} Z_{t-2}) \\ &+ X_t \overline{Z}_{t-1} (1 \cdot \overline{X}_{t-1} \overline{Z}_{t-2} + 1 \cdot \overline{X}_{t-1} Z_{t-2} + 1 \cdot X_{t-1} \overline{Z}_{t-2} + \cancel{\emptyset} \cdot X_{t-1} Z_{t-2}) \\ &+ X_t Z_{t-1} (1 \cdot \overline{X}_{t-1} \overline{Z}_{t-2} + 1 \cdot \overline{X}_{t-1} Z_{t-2} + \cancel{\emptyset} \cdot X_{t-1} \overline{Z}_{t-2} + \cancel{\emptyset} \cdot X_{t-1} Z_{t-2}) \\ &= \overline{X}_t \overline{Z}_{t-1} \overline{X}_{t-1} \overline{Z}_{t-2} + \overline{X}_t \overline{Z}_{t-1} \overline{X}_{t-1} Z_{t-2} + \overline{X}_t \overline{Z}_{t-1} X_{t-1} \overline{Z}_{t-2} \\ &+ \overline{X}_t Z_{t-1} X_{t-1} \overline{Z}_{t-2} + X_t \overline{Z}_{t-1} \overline{X}_{t-1} \overline{Z}_{t-2} + X_t \overline{Z}_{t-1} \overline{X}_{t-1} Z_{t-2} \\ &+ \overline{X}_t Z_{t-1} X_{t-1} \overline{Z}_{t-2} + X_t \overline{Z}_{t-1} \overline{X}_{t-1} \overline{Z}_{t-2} + X_t \overline{Z}_{t-1} \overline{X}_{t-1} \overline{Z}_{t-2} \\ &+ X_t \overline{Z}_{t-1} X_{t-1} \overline{Z}_{t-2} + X_t \overline{Z}_{t-1} \overline{X}_{t-1} \overline{Z}_{t-2} + X_t \overline{Z}_{t-1} \overline{X}_{t-1} Z_{t-2} \\ &+ X_t \overline{Z}_{t-1} X_{t-1} \overline{Z}_{t-2} + X_t \overline{Z}_{t-1} \overline{X}_{t-1} \overline{Z}_{t-2} + X_t \overline{Z}_{t-1} \overline{X}_{t-1} \overline{Z}_{t-2} \\ &+ X_t \overline{Z}_{t-1} X_{t-1} \overline{Z}_{t-2} + X_t \overline{Z}_{t-1} \overline{X}_{t-1} \overline{Z}_{t-2} + X_t \overline{Z}_{t-1} \overline{X}_{t-1} \overline{Z}_{t-2} \\ &+ X_t \overline{Z}_{t-1} X_{t-1} \overline{Z}_{t-2} \cdot X_t \overline{Z}_{t-2} \cdot X_t \overline{Z}_{t-1} \overline{Z}_{t-2} + X_t \overline{Z}_{t-1} \overline{Z}_{t-2} \\ &+ X_t \overline{Z}_{t-1} X_{t-1} \overline{Z}_{t-2} \cdot X_t \overline{Z}_{t-2} \cdot X_t \overline{Z}_{t-2} \cdot X_t \overline{Z}_{t-2} \\ &+ X_t \overline{Z}_{t-1} X_{t-1} \overline{Z}_{t-2} \cdot X_t \overline{Z}_{t-2} \cdot X_t \overline{Z}_{t-2} \cdot X_t \overline{Z}_{t-2} \\ &+ X_t \overline{Z}_{t-1} X_{t-1} \overline{Z}_{t-2} \cdot X_t \overline{Z}_{t-2} \cdot X_t \overline{Z}_{t-2} \cdot X_t \overline{Z}_{t-2} \\ &+ X_t \overline{Z}_{t-1} X_{t-1} \overline{Z}_{t-2} \cdot X_t \overline{Z}_{t-2} \cdot X_t \overline{Z}_{t-2} \cdot X_t \overline{Z}_{t-2} \\ &+ X_t \overline{Z}_{t-1} X_{t-1} \overline{Z}_{t-2} \cdot X_t \overline{Z}_{t-2} \cdot X_t \overline{Z}_{t-2} \cdot X_t \overline{Z}_{t-2} \\ &+ X_t \overline{Z}_{t-1} X_{t-1} \overline{Z}_{t-2} \cdot X_t \overline{Z}_{t-2} \cdot X_t \overline{Z}_{t-2} \cdot X_t \overline{Z}_{t-2} \\ &+ X_t \overline{Z}_{t-1} X_t \overline{Z}_{t-2} \cdot X_t \overline{Z}_{t-2} + X_t \overline{Z}_{t-2} \cdot X_t \overline{Z}_{t-2} \\ &+ X_t \overline{Z}_{t-2} X_t \overline{Z}_{t$$

This is exactly the same as Equation 2.5 derived in the previous section. Note that unnecessary work can be eliminated by simply writing down the branches terminated by (1) and summing them up.

## 2.6 Cellular Synthesis

Since all sequential machines can be described by combinational type equations, they can be realized by conventional combinational circuits if variables of different time subscripts are all available at the same time. This can be easily achieved by delay elements. Because the number of input variables and the memory K are both finite, the required number of delay elements is also finite.

Prior to the advent of integrated circuit technology, the goal of every logic designer was concentrated around minimizing the number of individual components in hardware realizations. But with the new technology, aside from a given upper limit, a large percentage of the cost is independent of the complexity of each building block. The main objective is, instead, to minimize the number of building blocks (modules). The more uses that can be found for a given module, the less expensive the per unit cost will be. Hence, to adapt large scale integration into future machines,

- 1. the number of types of modules must be small, and

- 2. the interconnection of modules to form larger structures must be simple and regular.

To meet the first criterion, we limit our cell types to just one. That is, all cells are identical. To meet the second criterion, we investigate the feasibility of three different cellular structures. They are the linear cascade, the array, and the tree.

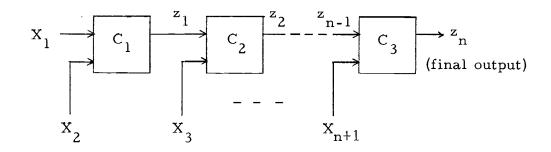

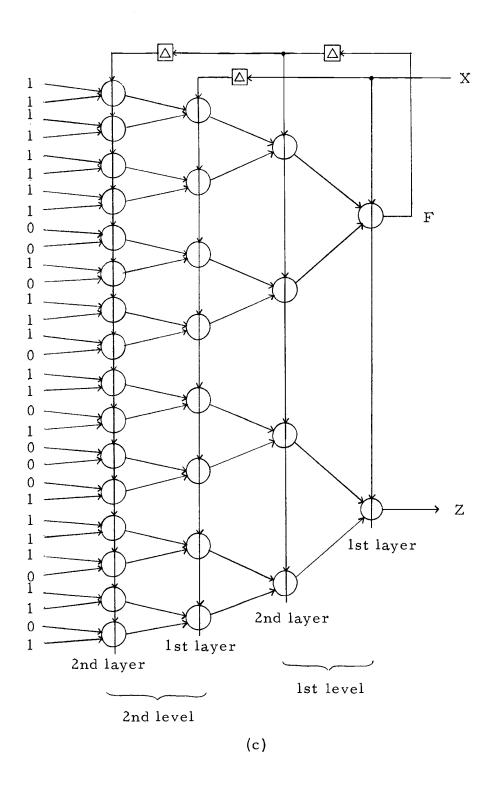

# 2.6.1 Linear Cascade

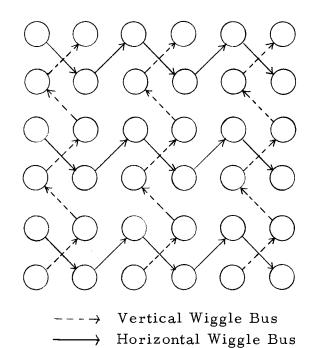

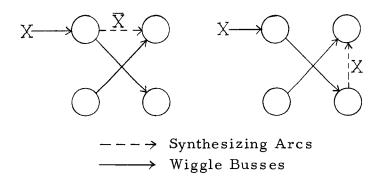

There are many ways to make linear cascades. We shall limit our investigation to that of unilatral linear cascades. The earliest cascade is the Maitra cascade [16] as shown in Figure 17. (These are called tributary switching network by Sklansky). The Maitra cascade, however, is not logically complete even if one allows redundant cascade (Stone and Korenjak [25]) in which the same external input may be connected to inputs of several cells. As pointed out by Short [22], in order to make the linear cascade functionally complete, the only logical direction is to expand the number of the interconnecting leads between cells. He showed that the two rail cascade is functionally complete. As an example, the realization of M2 using the two rail cascade is shown in Figure 18.

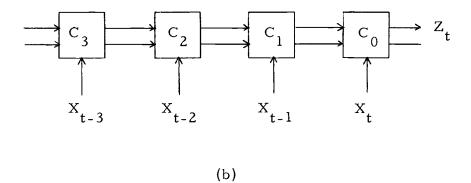

There are two ways to obtain necessary delays for the inputs.

All delay elements are assumed to be unit delay elements in our study.

1. Delayed input: inputs are delayed at different stages as shown in Figure 19a.

2. Delayed logic: delays are distributed throughout the logic circuits as shown in Figure 19b.

The circuit of Figure 19b has one more delay than that of Figure 19a and the output is actually

$$Z_{t} = \Delta(BCE)_{t} = \Delta(\overline{X}_{t}\overline{X}_{t-1}X_{t-2} + \overline{X}_{t}X_{t-1} + X_{t}\overline{X}_{t-1}\overline{X}_{t-2}X_{t-3} + X_{t}\overline{X}_{t-1}X_{t-2})$$

$$+ X_{t}\overline{X}_{t-1}X_{t-2}$$

$$= \overline{X}_{t-1}\overline{X}_{t-2}X_{t-3} + \overline{X}_{t-1}X_{t-2} + X_{t-1}\overline{X}_{t-2}\overline{X}_{t-3}X_{t-4} + X_{t-1}\overline{X}_{t-2}X_{t-3}.$$

Thus, when delayed input circuit is used, we are assuming the output is obtained with zero time. When delayed logic circuit is used, the output is obtained in one clock time. The advantage of delayed input is that it uses less delay elements while that of delayed logic is more uniform in structure.

The two rail cascade, however, can realize only one function per cascade. In many sequential machine syntheses, we need to realize both the output function and the feedback function not to mention multiple output functions. Although some studies in multiple function realization using two rail cascades have been done [3, 28], it is complicated and not efficient for general sequential machine realization. Of course, we can always realize multiple functions by multiple two rail cascades. This sort of approach comes very close to the array

type circuit we will discuss in the next section.

If we expand the number of the interconnecting leads further, we have the general multiple-rail cascade. But if the cell is to remain relatively simple, the number of rails that we may have must remain small. The difficulties of realizing multiple functions encountered in the two-rail cascade will also be present in this case.

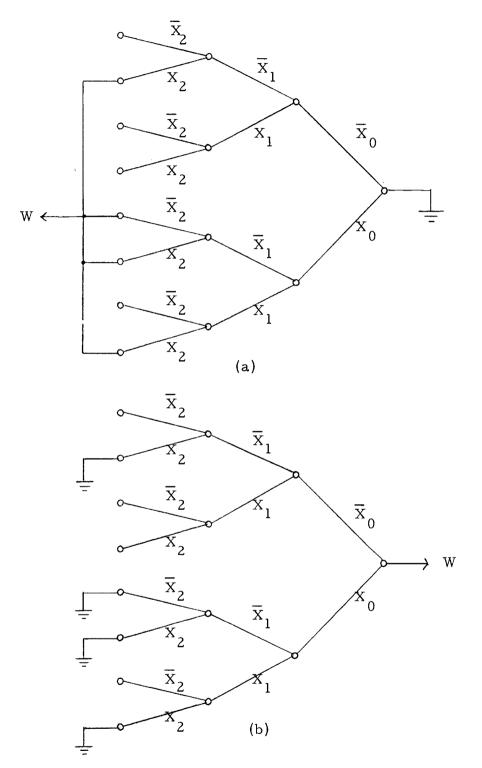

Now we consider the synthesis from the other direction--that of machine decomposition. Krohn and Rhodes [14] stated that each finite state machine M can be built as a cascade connection of two-state machine and permutation machines. Zeiger [29], in studying the cascaded P-R machine synthesis of sequential machines, also proved that this is possible. This is done by further decomposition of P-R machines into two-state machines and permutation machines. (Note that a two-state machine is a P-R machine.) However, in this kind of cascade, the number of different cell types can be very large (there are infinite number of P-R machines) and does not meet our criterion of single cell type.