### AN ABSTRACT OF THE THESIS OF

Stephen T. Flannagan for the degree of Master of Science, in the Department of Electrical and Computer Engineering, presented on March 16, 1982.

Title: SYNCHRONIZATION IN A CMOS TECHNOLOGY Redacted for Privacy Abstract approved:\_\_\_\_\_\_ Professor John Owen

The problem of synchronization arises in the interaction among digital systems not sharing a common clock reference. The reliability of synchronizers is related to metastable operation of bistable elements. Because of its subtle nature, the phenomenon until recently was not widely researched. However, the literature now contains a sound theoretical basis concerning the nature of metastability and its relationship to synchronization failure. Methods exist for construction of circuits with high synchronization reliability.

This paper describes the performance of synchronizers constructed in an integrated CMOS technology. A discussion of the characteristics of CMOS circuits in metastable operation is given, with attention to various device capacitances. The effect of transient channel charging current is included. A high-performance CMOS realization is described and experimental measurements of the synchronization reliability are compared with predicted performance curves. A comparison to NMOS circuits is given.

## (c) Copyright by S.T. Flannagan May 1982

**`**

All Rights Reserved

### SYNCHRONIZATION IN A CMOS TECHNOLOGY

by

Stephen T. Flannagan

### A THESIS

submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Master of Science

Completed March 16, 1982

Commencement June 1983

.

**APPROVED:**

1

# Redacted for Privacy

Professor of Electrical Engineering, Department Head; in charge of major.

Redacted for Privacy

Dean of Graduate School

Date thesis is presented \_\_\_\_\_ March 16, 1982

Typed by: Stephen T. Flannagan

### ACKNOWLEDGMENTS

The advisory committee consisted of professor John Owen and professor Richard Adams of Oregon State University, and William Lattin of Intel Corporation.

Ed Reese at Intel provided helpful comments and encouragement. Thanks is due to Ken Yu, Ron Chwang, Seth Stern and Paul Warkentin at Intel for fabrication of the devices. Paul Spencer provided support for photomask design.

Appreciation is expressed to Intel Corporation for their support of this work.

.

### TABLE OF CONTENTS

| Ι.   | Introduction<br>A. History of the Problem<br>B. Noise Independence<br>C. Review of Theory and Equations<br>Governing Metastable Action                                                                                                                                              | 1<br>1<br>3<br>4                 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| II.  | D. Probability of Synchronization Failure<br>Design Considerations for CMOS Flip-Flops<br>Used as Synchronizers<br>A. Capacitance<br>B. CMOS Circuit Behavior in the Metastable Region<br>C. NMOS Circuit Behavior in the Metastable Region<br>D. CMOS and NMOS Circuit Performance | 11<br>17<br>17<br>23<br>30<br>34 |

| III. | CMOS Synchronizer Design<br>A. Essential Requirements<br>B. Integrated CMOS Synchronization Test Circuit                                                                                                                                                                            | 40<br>40<br>40                   |

| IV.  | Experimental Measurement of Synchronization<br>Reliability<br>A. Test Set-up and Measurement Technique<br>B. Experimental Results                                                                                                                                                   | 48<br>48<br>51                   |

| ۷.   | Summary                                                                                                                                                                                                                                                                             | 54                               |

| ۷١.  | References                                                                                                                                                                                                                                                                          | 56                               |

| VII. | Appendix                                                                                                                                                                                                                                                                            | 58                               |

### LIST OF FIGURES

| Figure      |                                                                        | Page |

|-------------|------------------------------------------------------------------------|------|

| 1.          | Flip-Flop with asynchronous inputs                                     | 5    |

| 2.          | Proximity of input transitions                                         | 5    |

| 3.          | Metastable Decay                                                       | 6    |

| 4.          | Simple flip-flop circuit model                                         | 6    |

| 5.          | Typical phase trajectory for flip-flop outputs                         | 8    |

| 6 <b>a.</b> | Response to transitions on both inputs                                 | 10   |

| 6b.         | Response to transitions on one input                                   | 10   |

| 7.          | Logic configuration for synchronizer                                   | 13   |

| 8.          | Input characteristics showing cycle period                             | , 13 |

| 9.          | Typical plot of error rate versus time delay                           | 15   |

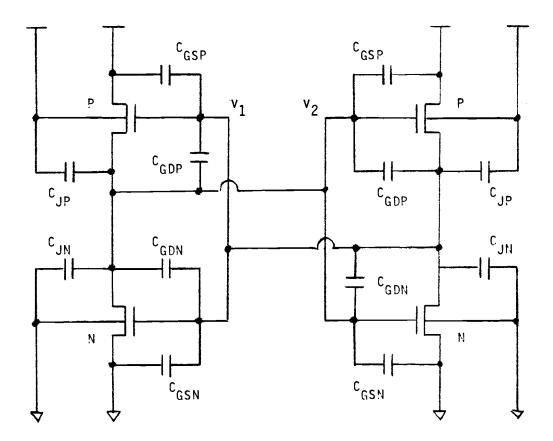

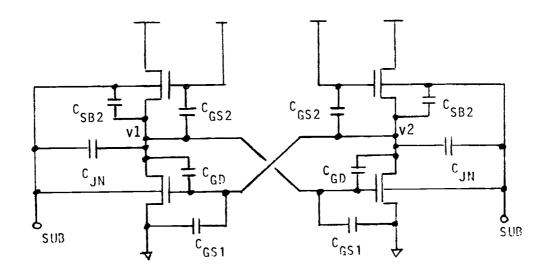

| 10.         | Capacitances associated with CMOS flip-flop                            | 18   |

| 11.         | Circuit model for CMOS flip-flop in metastable region                  | 21   |

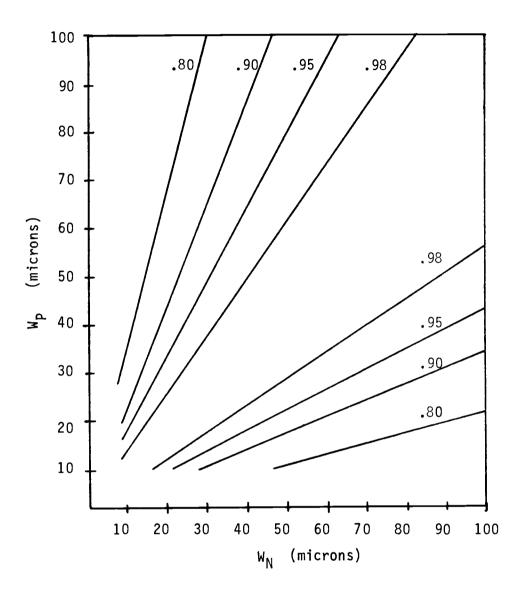

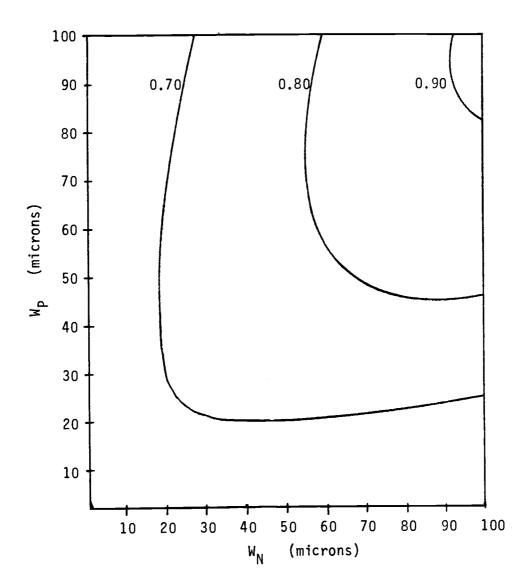

| 12.         | Loci of constant normalized $A\omega$ in ideal case                    | 26   |

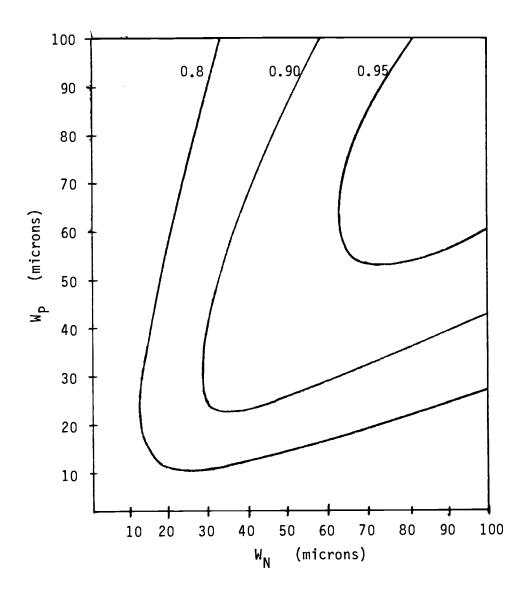

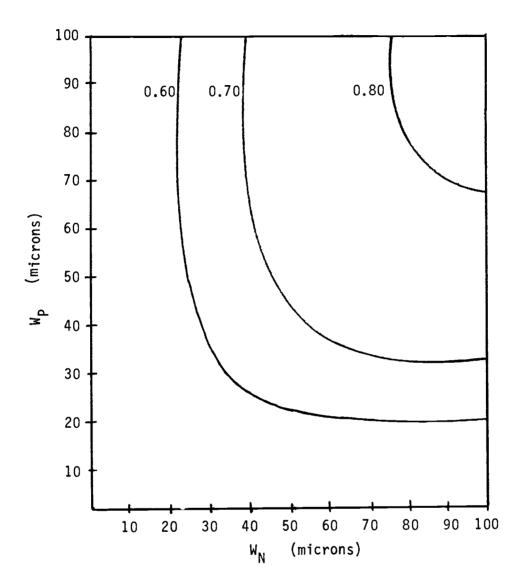

| 13.         | A $\omega$ variation with 3 percent load                               | 27   |

| 14.         | A $_\omega$ variation with 10 percent load                             | 28   |

| 15.         | A $\omega$ variation with 20 percent load                              | 29   |

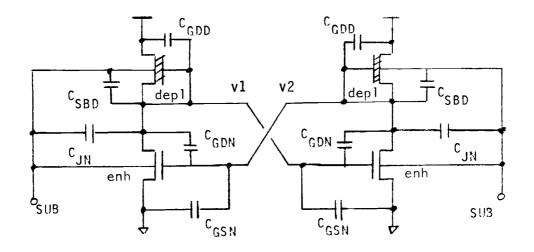

| 16.         | Depletion load flip-flop in NMOS                                       | 31   |

| 17.         | Enhancement load flip-flop in NMOS                                     | 31   |

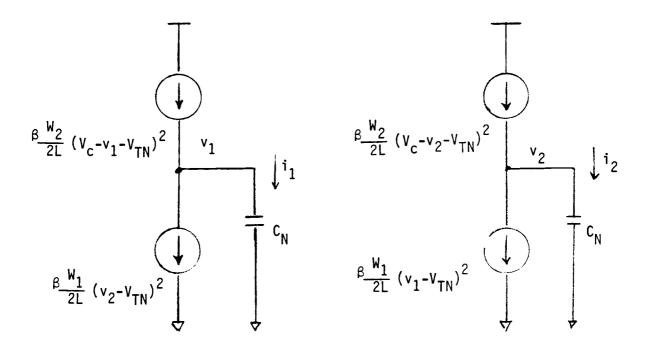

| 18.         | Circuit model for NMOS flip-flop                                       | 32   |

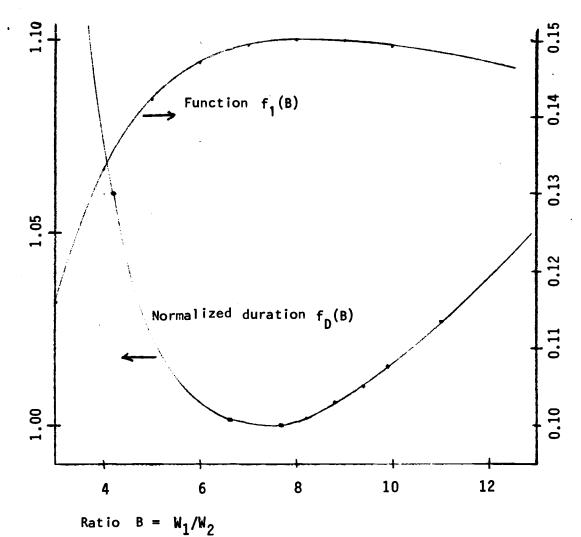

| 19.         | Normalized duration plotted with maximizing function                   | 35   |

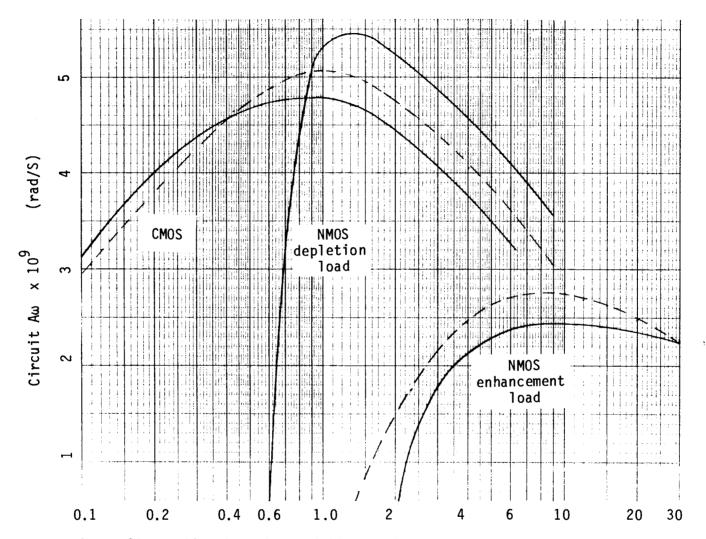

| 20.         | Comparison of $A\omega$ in CMOS and NMOS, plotted against device ratio | 37   |

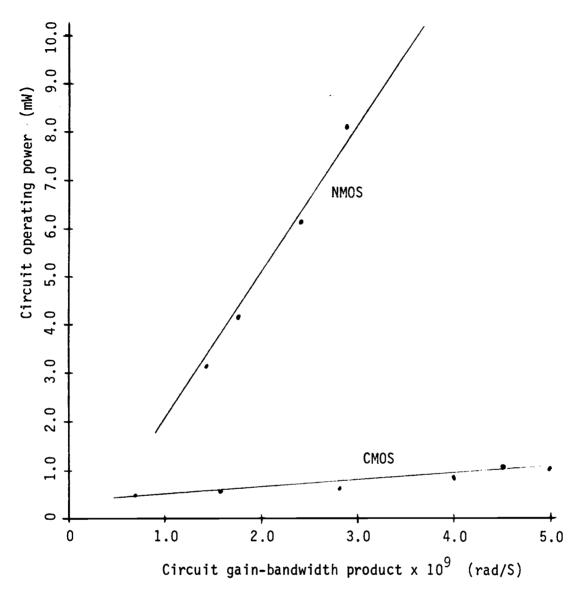

| 21.         | Circuit Gain-Bandwidth product versus<br>supply power requirement      | 38   |

| Figure                                                         |       |

|----------------------------------------------------------------|-------|

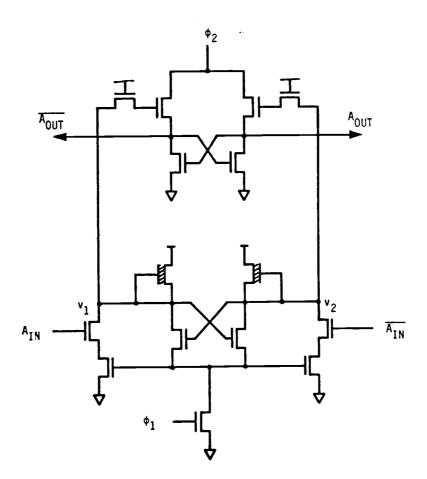

| 22. NMOS synchronizer circuit                                  | 39    |

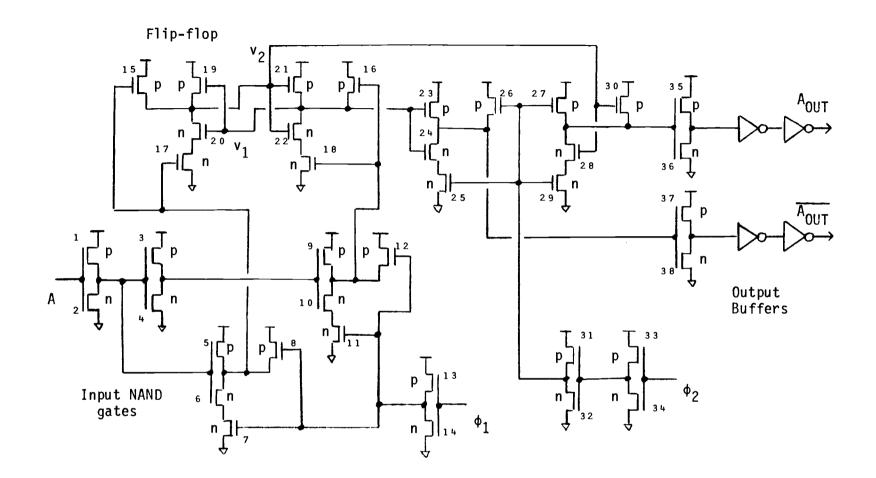

| 23. Integrated CMOS synchronizer test circuit                  | 41    |

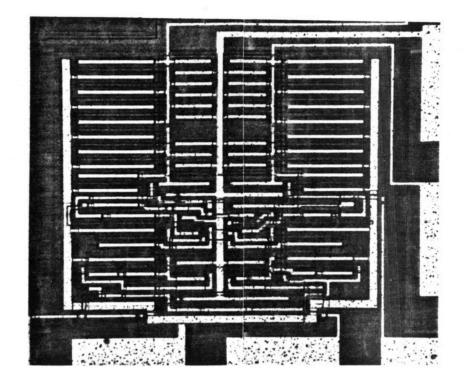

| 24. Photomicrograph of integrated realization                  | 43    |

| 25. Alternate sampling circuit for integrated designs          | 44    |

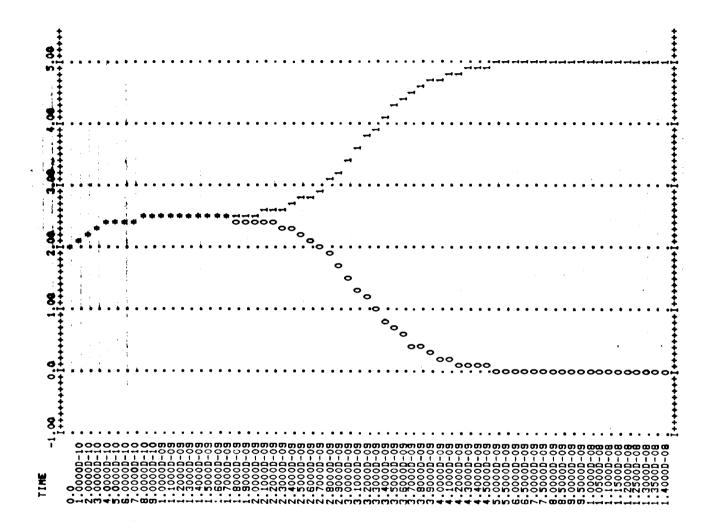

| 26. Graphic output of simulation of metastable decay           | 47    |

| 27. Experimental test set-up                                   | 49    |

| 28. Photograph of test circuit board                           | 50    |

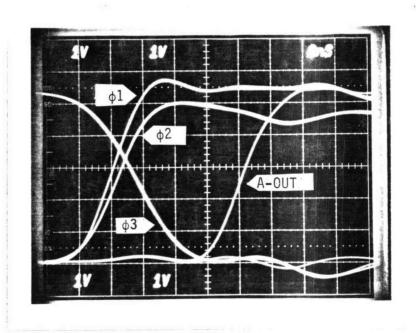

| 29. Oscilloscope traces for inputs and outputs of CMOS circuit | 50    |

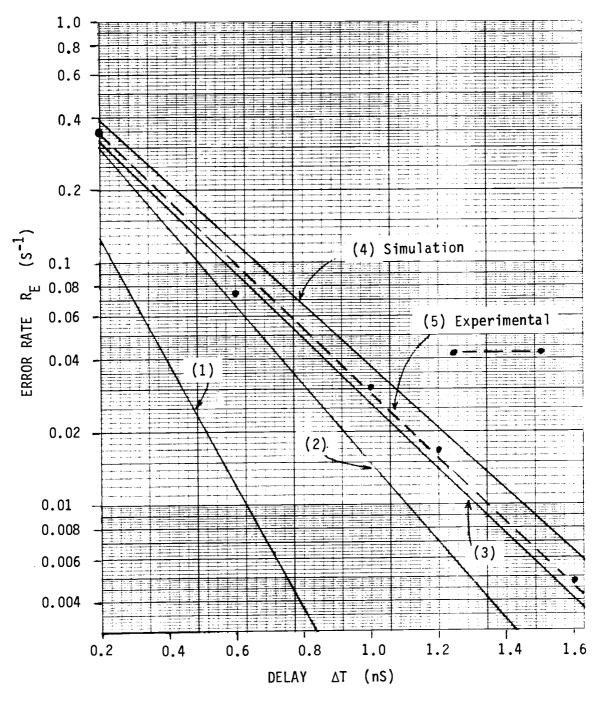

| 30. Comparison of theoretical and experimental error rat       | es 53 |

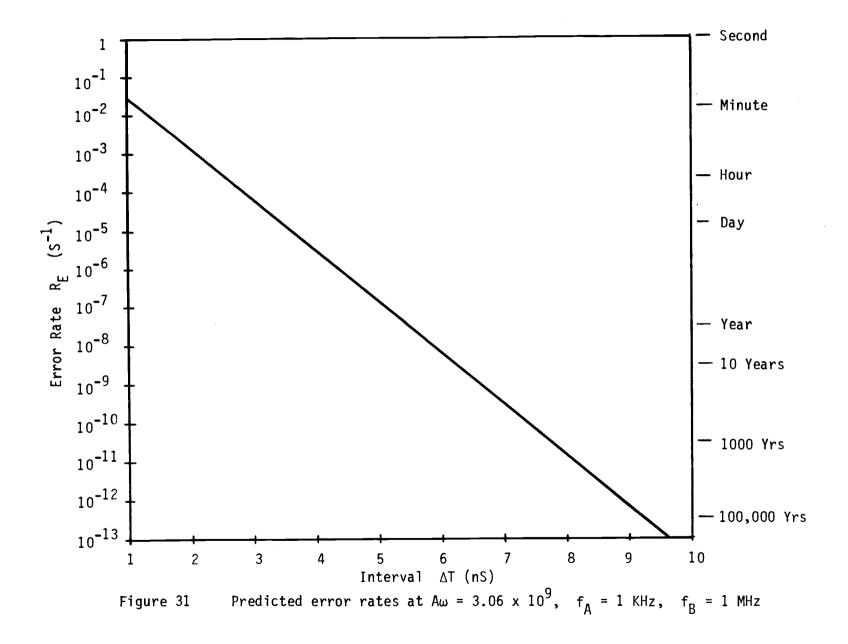

| 31. Predicted error rates                                      | 54    |

### LIST OF TABLES

| Table |                                                   |    |

|-------|---------------------------------------------------|----|

| 1.    | Tabular output for simulation of metastable decay | 46 |

| 2.    | Experimental measurements of error rate           | 52 |

#### SYNCHRONIZATION IN A CMOS TECHNOLOGY

I. Introduction

A. History of the Problem

Given two or more mutually asynchronous digital systems (i.e. not sharing a common clock reference) interactions among them can result in signals of non-defined logic levels. The sampling of an input while it is in the transition region can result in anomalous events in the circuit.

Sequential logic machines require that asynchronous inputs (those which may change at any time with respect to the machine clock) be processed by an input synchronizer. Otherwise, such an input may change while the machine is in transition from one state to another, in which case some machine registers may respond to the new value of the input, while others may respond to the previous value, thus resulting in a nonvalid state for the machine. Synchronizers are needed on interrupts and other similar inputs to computers, and in interlocks to mediate conflicting requests on common resources, in which an arbiter configuration is used.

Synchronization and arbitration failure relate to the event in which an undefined input causes a bistable decision element to enter a metastable state for some period of time. If such a state is not resolved before the information is required, a failure can result.

The use of bistables in synchronizers and the problem of metastable behavior resulting from asynchronous inputs was discussed in an early paper by Catt [1]. However, until the early 1970's the problem of metastable action was not widely recognized due to its subtle nature and low probability of occurrence. In 1972 Chaney et. al. [2,3] awakened new interest in the problem and suggested that it might be responsible for a number of previously unexplained computer "crashes". The problem has been the subject of some papers [4-15] and the theory is well established. Design principles exist for construction of systems with known reliability. The probability of failure can be reduced to negligibly small values, at the cost of introducing delay elements which provide time for metastable states to resolve.

The question as to whether or not it is possible to develop a bistable completely free of metastable operation has been a subject of controversy. Some have assumed that certain circuits, such as a schmitt trigger, could "regularize" transitional levels, thereby avoiding metastable action. However Chaney [16] provided experimental evidence that this assumption is not true, and that a metastable region does exist for the circuit in question. In fact, there is considerable theoretical evidence that any device having two stable states must necessarily have a region of metastable behavior. Hurtado and Elliot [7] give an abstract proof of the inevitability of metastable operation for any bistable device. The theory is further generalized and extended by Marino [15] to include any digital system exhibiting sequential behavior.

The possibility of processing asynchronous input changes with an Asynchronous Sequential Network (ASN) combined with a device known as an inertial delay was discussed in [10] and it was con-

2

cluded therein that none of the types examined were free of anomalous behavior. Strom [11] has proven that reliable inertial delays and time-bounded arbiters are equally realizable. Consequently, all theoretical limitations which apply to one will also apply to the other.

In summary, there is very compelling evidence that in a synchronizer or arbiter, a region of metastable behavior must necessarily exist, notwithstanding the presence of any other special circuits interconnected with the decision elements. Therefore, the correct design strategy is not to attempt to avoid metastable action, but rather to provide means with a high probability of resolution of such states. The relationship of this probability to synchronizer reliability is reviewed in section I-D.

Equally important is the strategy whereby synchronizers are placed in systems. The nature of the signal interactions determines the locations in which synchronizers are needed, and how they are to be interfaced with the elements which they support.

#### B. Noise Independence

The probability of escape from the metastable region, and hence the synchronization reliability, is not dependent on the level of noise in the circuit. A proof of noise independence is given by Couranz and Wann [6] using a Fourier Transform method. In another treatment, Kinnament and Woods [9] show that a noise signal is equally likely to move a bistable element into the metastable region as to move it away from that region, thus demonstrating noise independence of the error rate.

### C. Review of Theory and Equations Governing Metastable Action

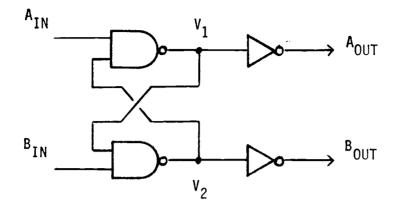

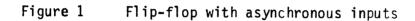

A bistable can be applied as the decision element of either an arbiter or synchronizer. Figure 1 shows a flip-flop with two controlling inputs. (For discussion, only the flip-flop is shown. It is not intended to represent a complete synchronizer circuit.) The inputs "A" and "B" may change at any time with respect to each other, as shown in figure 2. In an arbiter, "A" and "B" originate from two asynchronous and conflicting commands entering a system. and in the case of nearly simultaneous requests the problem is to determine which of the signals occurred first. In a synchronizer, "B" is considered to be a machine clock which marks the validity of the asynchronous input "A", and the problem is to determine whether "A" is high or low. Thus, the proximity of the two signals can be regarded in terms of their time separation  $\delta$  or in terms of the differential voltage  $\Delta V$ , both of which may be arbitrarily small or negative (figure 2). In this context, the problems of synchronization and of arbitration are equivalent. A component which contains an input synchronizer is referred to as "asynchronous" because it is capable of dealing with asynchronous inputs.

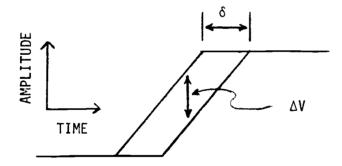

The event of interest is the transition of both inputs within some very small interval, such that the flip-flop will enter a metastable condition. Such a state will resolve within a finite time  $\tau$  as shown in figure 3. Smaller values of  $\delta$  will result in

Figure 2 Proximity of inputs "A" and "B" can be defined in terms of time separation or voltage difference, both of which may be arbitrarily small.

Figure 3 Metastable decay

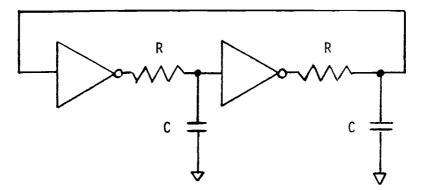

smaller initial offset  $V_0$  and hence longer resolution time. A typical circuit model for a flip-flop is shown in figure 4.

In the following discussion, the variables  $x_1$  and  $x_2$  represent the voltage displacements from the metastable level  $V_{MS}$ , so that  $v_1$  and  $v_2$  represent the actual voltages at the nodes.

A generalized nonlinear gain can be given as

(1)

$$V_{out} = A_1 V_{in} + A_2 V_{in}^2 + A_3 V_{in}^3$$

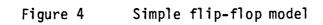

Methods of dealing with nonlinear systems are discussed, for example, in reference [17]. Figure 5 shows a phase plane trajectory for one of the flip-flop outputs x. This trajectory reflects the fact that the rate-of-change of the output increases with the output level, until the flip-flop approaches one of its stable states, when the rate of change returns to zero. (Actually the stable state is never reached but is approached asymptotically.)

The region we are interested in is the portion of the trajectory near the origin in figure 5. For circuits in which a linear approximation is valid, in the metastable region, the following equations can be written:

(2)

$$\dot{x}_1 = \frac{1}{RC} (-Ax_2 - x_1)$$

(3)  $\dot{x}_2 = \frac{1}{RC} (-Ax_1 - x_2)$

Typical phase trajectory for one of the outputs of a flip-flop. The variable x represents the displacement of the voltage from the metastable level, so that  $x(t) = v(t)-v_{ms}$ . Thus, metastable operation is associated with the origin. The applicability of the linear model depends upon the approximation of the phase trajectory as a straight line near the origin. the full solution is given by

(4)

$$x_1 = K_1 e^{\frac{1}{RC}(A-1)t} + K_2 e^{\frac{-1}{RC}(A+1)t}$$

(5)

$$x_2 = -K_1 e^{\frac{1}{RC}(A-1)t} + K_2 e^{\frac{-1}{RC}(A+1)t}$$

the variable of interest is the differential offset v given by:

(6)

$$v = v_1 - v_2 = x_1 - x_2$$

so that the equation for v(t) can be determined as

(7)

$$v(t) = 2K_1 e^{\frac{1}{RC}(A-1)t}$$

Clearly, the initial offset is  $V_0 = 2 K_1$ . Since A >> 1 we approximate A-1 simply as A. The factor A/RC is interpreted as the closed-loop gain-bandwidth product for the circuit, and may be written as A $\omega$ . Therefore we have

(8)

$$v(t) = v_0 e^{A\omega t}$$

Justification of the linear model for the circuits to be discussed in this paper will be given in section II-B.

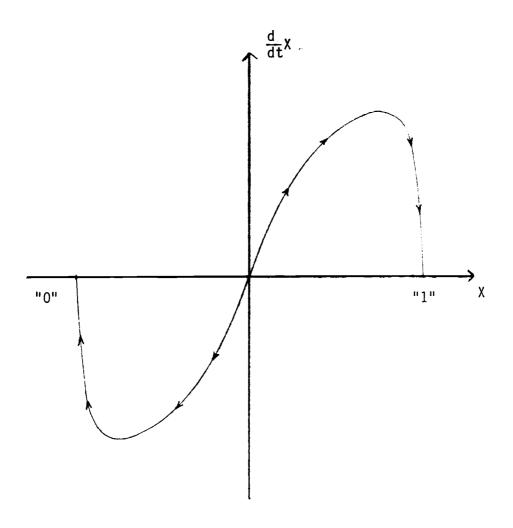

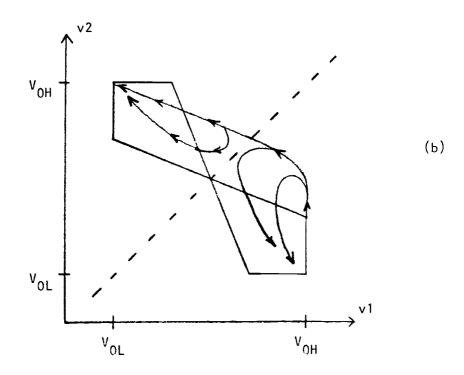

A metastable state can be induced by full-level transitions occurring nearly at the same time, or by a single input with insufficient level or duration. These two possibilities are shown in figure 6. The state variables are the flip-flop outputs  $v_1$  and  $v_2$ . Metastable operation is associated with a trajectory located within some small vicinity of the 45-degree line. The resolution time increases as the distance from this line to the locus of operation decreases. Figure 6-a represents the system response to

Figure 6 Flip-flop response to (a) nearly simultaneous transitions on both inputs, and (b) a pulse on one input, with insufficient duration.

nearly simultaneous transitions on inputs "A" and "B" in which neither signal returns to its original state before the response of the flip-flop has settled. Paths #1 and #2 represent the response to a transition on a single input. Paths #3 - #6 show the response to inputs on both "A" and "B" when their time separation is less than the response time of the circuit. In such an event, metastable operation near the midline is possible. Figure 6-b shows the system response to a pulse on one input whose duration is shorter than the flip-flop transition time. This type of a non-standard input can generate a metastable state even if only one input is active.

#### D. Probability of Synchronization Failure

By definition, successful arbitration or synchronization consists in the choice of exactly one of two conflicting possibilities within some specified time requirement. A failure then would result in the selection of both actions, or neither action within the required time interval. Neither choice by itself can be classified as the "right" or "wrong" action in terms of the state of any other part of the system nor its inputs.

The recognized method for ensuring acceptable synchronization reliability is to provide a very high-gain flip-flop and to isolate the element during some fixed time delay. Approaches using variable delays have been described [8,12]. One technique for providing such a variable delay is the use of a flip-flop combined with level detectors, [2,9] called an indicating flip-flop in [9]. The variable delay method, however, is subject to the same basic constraint, i.e., that the resolution time of a flip-flop is nonzero and is unbounded. This paper will deal only with the fixed-delay approach.

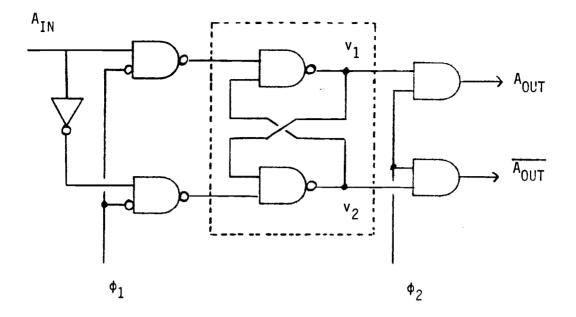

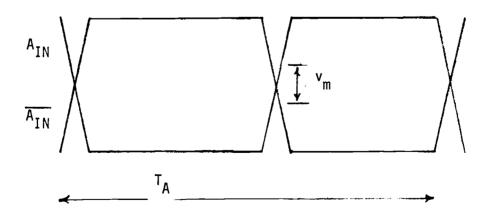

Figure 7 shows a typical logic configuration for a time-bounded synchronizer.  $\phi_1$  is a system clock which determines the validity of the input "A". A necessary condition is that the asynchronous inputs be isolated from the flip-flop at the beginning of the interval. This requirement is important because behavior of the flip-flop must be independent of input changes subsequent to the transition of  $\phi_1$ .

Transitions on "A" may occur at any time with respect to  $\phi_1$ . Thus, the probability distribution of  $\delta$  is uniform in the region of interest, so that arbitrarily small values of flip-flop offset may occur. A failure is defined as a trajectory persisting in the metastable region for a time longer than the interval  $\Delta T$ , so that the probability of failure in any one event is:

(9)

$$P_f = P(\tau > \Delta t)$$

From equation 8 the time required for resolution  $\tau$  is:

(10)

$$\tau = (\ln \frac{v_f}{v_o})(\frac{1}{A\omega})$$

where  $v_f$  is the minimum signal required for a meaningful output. The probability of failure is then

(11)

$$P_f = P(V_o < v_f e^{-A\omega\Delta t})$$

so that a minimum required input signal can be calculated as:

Figure 7 Conceptual logic configuration for synchronizer. Delay from clock  $\phi_1$  to  $\phi_2$  is fixed. Input A<sub>IN</sub> is asynchronous. The elements enclosed by dotted line form a flip-flop which may enter a metastable (balanced) condition at the time of phase 1. Synchronization failure can occur if this condition is not resolved at the time of the transition on phase 2.

Figure 8 Characteristics of input.  $T_{\underline{A}}$  may vary from one cycle to another.  $v_{\underline{m}}$  is shown exaggerated for clarity.

(12)

$$v_m = v_f e^{-A\omega\Delta t}$$

Values of  $V_0$  greater than  $v_m$  are then required for successful resolution. In these equations it is clear that the probability of failure must necessarily be nonzero. There are several treatments of this probability, for example [4,6,9,14]. Following the analysis of [9], the probability of failure is

(13)

$$P_f = \frac{2}{T_A A \omega} e^{-A \omega \Delta t}$$

the error rate per unit time is

(14)

$$R_{E} = P_{f} f_{B}$$

thus the error rate can be expressed as

(15)

$$R_{E} = \frac{2f_{A}f_{B}}{A\omega} e^{-A\omega\Delta t}$$

Where  $T_A$  is the average period of the asynchronous input,  $f_B$  is the system sampling frequency, and  $f_A$  is defined as  $1/T_A \cdot$

In equation 15, the factor  $(2f_{A}f_{B}) / (A\omega)$  gives a measure of the probability of a metastable state being generated. The exponent relates to the probability that a metastable state will not be successfully resolved. The error rate is the product of these two factors.

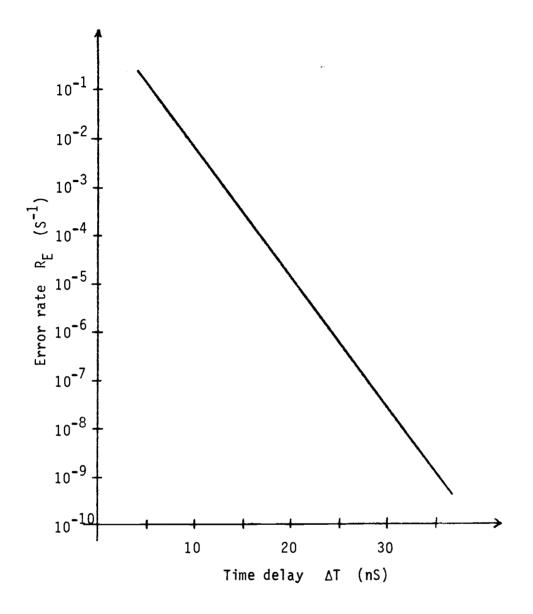

This equation shows that the critical factor governing the reliability is  $A\omega\Delta T$ . Figure 9 shows the theoretical error rate vs  $\Delta T$  for a given value of  $A\omega$ . This curve indicates that an increase in the gain-bandwidth product will allow a proportionate

Figure 9

Example of synchronization error rate vs time delay

decrease in the delay required, thus increasing the overall system speed without altering the reliability.

An offset or inherent asymmetry in the flip-flop will not remove the possibility of metastable states. Such an imbalance would shift the relative positions of inputs "A" and "B" required to produce a metastable condition. The validity of this fact is a special case of the previously cited evidence that all bistable devices must necessarily have a region of metastability.

As an example of synchronization reliability, we consider a 1.0 MHz system clock in which an asynchronous input occurs once per second. Suppose the value of A $\omega$  is  $5 \times 10^8$  S<sup>-1</sup> and an interval of 20 nS is available before a decision must be made. Then from equation 15,  $R_E = 1.82 \times 10^{-7}$  corresponding to approximately one error every 64 days. However, if the average frequency of inputs were increased to  $10^6$  per second,  $R_E$  would become  $1.82 \times 10^{-1}$  which would probably be unacceptable. If the factor  $A\omega$  cannot be further increased, it would be necessary to increase  $\Delta T$  in order to restore the original intended level of reliability.

Synchronization has also been treated in terms of the energy input to the device [5]. Mead and Conway [13] give an interesting analysis of the switching energy and also suggest an ultimate limit based on the probability that a flip-flop changes state due to random thermal motion of electrons.

### II. Design Considerations for CMOS Flip-Flops used as Synchronizers

An analysis of NMOS flip-flops used as synchronizers was given by Veendrick [14]. This section will examine CMOS flip-flop behavior and determine their performance in synchronizers. The design constraints for the CMOS technology will be determined, with attention to the effects of intrinsic and extrinsic capacitance. A detailed expression for capacitance will be used, and the effect of transient channel-charging current will be included. Comparisons to NMOS and passive load circuits will be made.

### A. Capacitance

The parameter A $\omega$  is proportionate to the conductance of the active elements in the circuit and is inversely related to the total effective capacitance associated with the nodes of the flip-flop. Methods of determining MOSFET capacitances are well established [18-24]. In general, treatment of the capacitances is separated into extrinsic capacitance (that associated with junctions, etc.) and intrinsic capacitance (associated with the intrinsic device, which excludes source and drain junctions.) Capacitances such as Cgd and Cgb, because of their dependence on the operating state of the device, can be determined in the context of a model incorporating "partitioning" as in references [21,22].

Figure 10 shows a CMOS flip-flop and capacitances. The gate length (L) is assumed to be the same for all devices. The width (W) may be chosen differently for p-type and n-type devices. In the metastable region, all four devices are in saturation. Since an

17

Capacitances associated with CMOS flip-flop. In the metastable region, all transistors are in saturation.  $C_{\rm GD}$  is negligible in both p-type and n-type transistors due to pinch-off. However, in the charging-current model a non-zero capacitance  $C_{\rm DG}$  is introduced into the circuit model in order to account for transient currents associated with variation of the channel charge. exit from that region requires only a small change in voltages  $v_1$ and  $v_2$ , the devices will be in saturation during the entire period of interest. In this analysis, voltage dependent parameters which do not change appreciably in this region will be treated as constant. Further, the values of channel length, mobility, and threshold used in these equations shall be those applicable in the metastable region. Because of pinch-off, C<sub>gd</sub> is zero in the gatecapacitance model. However, when channel charging is considered, a capacitance C<sub>dg</sub> can be introduced.

The gate capacitance approach to device analysis does not accurately reflect source, drain or substrate currents under transient conditions in which the channel charge is changing. Methods for analyzing MOS transient drain and source currents are discussed by Oh, Ward, and Dutton [23,24]. The total drain and source currents are expressed as a superposition of two components, a transport current and a charging current. The effects of channelcharging current are discussed in terms of non-reciprocal capacitances in reference [23]. In saturation, the drain voltage is separated from the channel by pinch-off, so that a change in V<sub>d</sub> does not affect  $Q_6$ , and therefore the capacitance

$$C_{gd} = \frac{\partial Q_{G}}{\partial V_{D}}$$

is zero in saturation. However, a change in gate voltage causes a change in channel charge, some of which is associated with drain current. This capacitance is given by

$$C_{dg} = \frac{\partial Q_D}{\partial V_G}$$

and can be treated as non-zero in order to account for the fact that some of the drain current is associated with the change in channel charge.

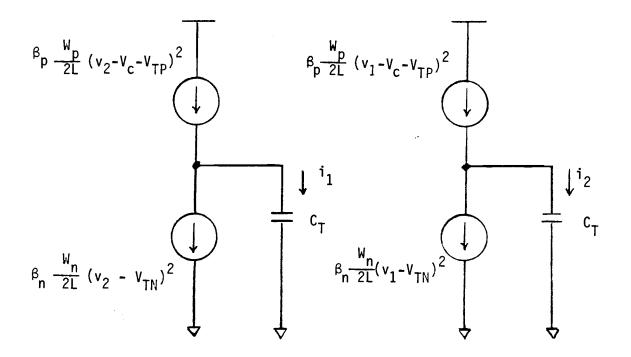

Figure 11 shows a model for the flip-flop using the simple MOS formula for saturation current. The effective nodal capacitance applicable to this model is given as:

(16)  $C_T = C_{GSN} + C_{GSP} + C_{MIL} + C_{iN} + C_{iP} + C_{MIL2} + C_{LOAD}$

where:

$C_{T} = Total effective nodal capacitance$   $C_{GSN} = N-device gate-to-source$   $C_{GSP} = P-device gate-to-sourve$   $C_{jN} = Junction at drain of n-device$   $C_{jP} = Junction at drain of p-device$   $C_{MIL} = Miller capacitor equivalent of C_{dg}$   $C_{MIL2} = Miller equivalent of overlap capacitance$   $C_{LOAD} = Capacitance of subsequent circuit stage, interconnect parasitic and other capacitances$

The following definitions of terms will be used (CMOS equations):

$$C_{o} = C_{ox}(L)(W_{N} + W_{P})$$

$$a_{0} = (C_{GSN} + C_{GSP}) / C_{o}$$

$$a_{1} = C_{MIL} / C_{o}$$

$$a_{2} = (C_{jn} + C_{jp}) / C_{o}$$

$$a_{3} = (C_{LOAD}) / C_{o}$$

$$a_{4} = C_{MIL2} / C_{o}$$

$$a = a_{0} + a_{1} + a_{2} + a_{3} + a_{4}$$

Figure 11

Circuit model for CMOS flip-flop in the metastable region of operation

so that  $a_2$  and  $a_3$  give a measure of the efficiency of the circuit. We then have:

$$C_{T} = C_{0}(a_{0}+a_{1}+a_{2}+a_{3}+a_{4})$$

$a_2$  is relatively constant for a given technology because junction capacitance will increase roughly proportionate to device widths.  $a_3$  however can be minimized by making the active devices of the flip-flop large with respect to the load elements in the subsequent circuit stages and with respect to interconnect capacitance.

In saturation,  $C_{gs}/C_{ox}$  is 2/3, therefore  $a_0 = 0.67$ . The analysis in [23] shows that partitioning of the channel charge in saturation is 3/8 to the drain and 5/8 to the source. Therefore,

$C_{dg} = (3/8)(2/3)C_0$ .

Because this capacitor couples v1 and v2, it translates into the model of figure 11 as a Miller capacitor. The Miller factor is given as (1-K) where K is the ratio of the small-signal components of v<sub>1</sub> and v<sub>2</sub>. For this factor we use the approximation K = -1 resulting in:

$C_{MIL} = (1-K)(C_{dg})$  $C_{MIL} = (2)(3/8)(2/3)(C_0) = (0.50)(C_0)$

Therefore,  $a_1 = 0.50$  for CMOS.

The term  $a_4$  accounts for the Miller capacitance associated with overlap, and is estimated at  $a_4 = 0.3$ . Summarizing the above:

$C_T = (a)C_0$

$a_{CMOS} = (0.67 + 0.5 + 0.3 + a_2 + a_3)$

These parameters will be used in the calculations in sections II-D and III-B.

### B. CMOS Circuit Behavior in the Metastable Region

Referring to the simple model in figure 11 and treating the total capacitance as  $C_{\rm T}$  we write the equations describing  $v_1$  and  $v_2$  as

(17)

$$\dot{\mathbf{v}}_{1} = \frac{1}{2C_{T}} \left[ \beta_{p} \frac{W_{p}}{L} (v_{2} - V_{c} - V_{TP})^{2} - \beta_{n} \frac{W_{n}}{L} (v_{2} - V_{TN})^{2} \right]$$

(18)

$$\dot{v}_2 = \frac{1}{2C_T} \left[ \beta_p \frac{w_p}{L} (v_1 - V_c - V_{TP})^2 - \beta_n \frac{w_n}{L} (v_1 - V_{TN})^2 \right]$$

These equations can be written in the form:

(19)

$$\dot{v}_1 = -A_1 v_2^2 - A_2 v_2 - A_3$$

(20)

$$\dot{v}_2 = -A_1 v_1^2 - A_2 v_1 - A_3$$

where the constants are:

$$A_{1} = \frac{(\mu_{n}W_{n} - \mu_{p}W_{p})}{2L^{2}(W_{p} + W_{n})(a)}$$

$$A_{2} = \frac{-(\mu_{n}W_{n}2V_{TN} - \mu_{p}W_{p}2(V_{c} + V_{Tp}))}{2L^{2}(W_{p} + W_{n})(a)}$$

$$A_{3} = \frac{(\mu_{n}W_{n}V_{TN}^{2}) - \mu_{p}W_{p}(V_{c} + V_{TP})^{2}}{2L^{2}(W_{p} + W_{n})(a)}$$

The metastable voltage is given by

(21)

$$V_{MS} = \frac{V_c + V_{TP} + V_{TN} \sqrt{RQ}}{1 + \sqrt{RQ}}$$

where  $R = W_N / W_P$  and  $Q = \frac{\mu_N}{\mu_P}$ equations 19 and 20 are combined and written in terms of the differential offset  $v = v_1 - v_2$

(22)

$$\dot{\mathbf{v}} = \begin{bmatrix} A_1(\mathbf{v}_1 + \mathbf{v}_2) + A_2 \end{bmatrix} \mathbf{v}$$

The linear model can be justified if the phase trajectory is approximately linear in the region of interest. The time-variations of  $v_1$  and  $v_2$  are opposite in sign, and the coefficient in equation 22 will not vary substantially with time. We make the approximation

(23)

$$v_1 + v_2 = 2V_{MS}$$

so that the linear approximation for equation 22 is then

(24)

$$\mathbf{v} = \begin{bmatrix} 2A_1V_{MS} + A_2 \end{bmatrix} \mathbf{v}$$

combining equations 8 and 24, the gain-bandwidth product is:

$$(25) \qquad A\omega = 2A_1V_{MS} + A_2$$

substituting the parameters previously defined, we get

(26)

$$A\omega = \frac{\mu_{n}W_{n}(V_{MS}-V_{TN}) + \mu_{p}W_{p}(V_{c}+V_{TP}-V_{MS})}{L^{2}(W_{p}+W_{n})(a)}$$

The fact that the coefficients associated with each device width are positive reflects the fact that both P and N type devices contribute to gain in the circuit. In NMOS and passive-load circuits only the pull-down device coefficient would be positive.

The conditions for maximizing  $A\omega$  in terms of  $W_N$  and  $W_P$  can be obtained by substitution of equation 21 into equation 26. After some algebra the parameters  $W_N$  and  $W_P$  are arranged so as to appear only in terms of the ratio R. The result is

(27)

$$A\omega = \frac{(V_c + V_T P - V_T N)\sqrt{\mu_n \mu_p}}{L^2(a)} \left[\frac{\sqrt{R}}{1 + R}\right]$$

In this first-order analysis, then,  $A\omega$  will be maximized when R = 1. The value of  $A\omega$  scales with the inverse-square of channel length. Oxide thickness does not appear in the equation, but would have an indirect effect, for example, due to its influence on threshold, unless the threshold is intentionally compensated so as not to change as the technology is scaled. Other second order effects are channel length variation, and mobility reduction associated with high vertical and lateral fields. When this effect becomes more severe, it is then necessary to use the lower value of mobility appropriate to the metastable region of operation.

The parameter  $a_3$  requires that device widths in the flip-flop be sufficiently large so that C<sub>LOAD</sub> will be small compared with C<sub>0</sub>. Beyond this point, A<sub> $\omega$ </sub> does not change substantially with device width.

A simple computer program was used to determine the variation of gain-bandwidth product with respect to device ratio and to loading. The results for the ideal case (with no load) is shown in figure 12, which gives lines of constant A $\omega$ . Because of the process dependence, the graphs have been normalized. Figures 13-15 show the effects of non-zero load capacitance. The graphs give lines of constant A $\omega$ , normalized globally over these graphs. CLOAD is given as a percentage of C<sub>0</sub> at the midpoint of each graph. These results indicate that even for small values of C<sub>LOAD</sub> the ratio optimization criterion breaks down. Therefore, the flip-flops must have low external capacitive loading and be well buffered if maximum performance is to be achieved. Further, a precise selection of

Figure 12

Loci of constant normalized  $A\omega$  for the ideal case of zero external capacitance

.

Lines of constant A  $\omega$  for C  $_{LOAD}$  of 3.0 % of the internal capacitance at midpoint of the graph.

Figure 14 Lines of constant A $\omega$  for C $_{LOAD}$  of 10.0 %

Lines of constant A $\omega$  for C  $_{LOAD}$  of 20.0 %

device ratio R is not critical, as the regions of 90 percent efficiency are wide.

C. NMOS Circuit Behavior in the Metastable Region

The nature of NMOS flip-flops is such that their load devices do not provide gain, but they do add nodal capacitance which tends to reduce  $A\omega$ . Figure 16 shows a depletion-load flip-flop, and figure 17 shows the corresponding enhancement-load circuit. Depletion loads of course are superior because they provide a full supply-voltage level without capacitive boosting techniques, in circuits where full-level transitions are important. In the metastable region they are preferred because of gain. Enhancement loads cause a reduction in gain because of the negative feedback which they introduce into the closed-loop gain for the circuit.

Referring to figure 18 and applying the same assumptions as before, the NMOS equations are:

(28)

$$\dot{\mathbf{v}}_{2} = \frac{\beta}{2C_{T}} \left[ \frac{W_{2}}{L} (V_{c} - V_{2} - V_{TN})^{2} - \frac{W_{1}}{L} (V_{1} - V_{TN})^{2} \right]$$

(29)

$$\dot{\mathbf{v}}_{1} = \frac{\beta}{2C_{T}} \left[ \frac{W_{2}}{L} (V_{c} - V_{1} - V_{TN})^{2} - \frac{W_{1}}{L} (V_{2} - V_{TN})^{2} \right]$$

(30)

$$V_{MS(NMOS)} = \frac{V_{C} + V_{TN} (\sqrt{B} - 1)}{\sqrt{B} + 1}$$

(31)

$$A\omega_{(NMOS)} = \frac{\mu_n W_2 (V_{MS}(NMOS)^{+}V_{TN}^{-}V_c) + \mu_n W_1 (V_{MS}(NMOS)^{-}V_{TN})}{L^2 (W_2^{+}W_1)(a)}$$

where for NMOS circuits the parameters are defined as:

$$C_T = C_{GS1} + C_{GS2} + C_j + C_{MIL} + C_{MIL2} + C_{LOAD}$$

Figure 17

.

Figure 18

Circuit model for NMOS flip-flop in the metastable region. Enhancement loads are indicated here. The model for a depletion load flip-flop would substitute constantcurrent sources for the pull-up devices.  $C_{T} = C_{O}(a_{0}+a_{1}+a_{2}+a_{3}+a_{4})$   $W_{2} = width of pull-up device$   $W_{1} = width of pull-down device$   $C_{O} = C_{OX}(W_{1}+W_{2})(L)$   $C_{MIL} = Miller equivalent of Cdg$   $C_{MIL2} = Miller equivalent of overlap$   $a_{0} = (C_{GS1} + C_{GS2})/C_{O}$   $a_{1} = C_{MIL} / C_{O}$   $a_{2} = C_{j} / C_{O}$   $a_{3} = C_{LOAD} / C_{O}$   $a_{4} = C_{MIL2} / C_{O}$   $B = W_{1} / W_{2}$

The value of  $a_1$  for the NMOS circuit depends on  $C_{dg}$  for the pulldown device and can be approximated as a constant at the optimum value of B, later shown to be B=8. Thus,  $a_1$  for NMOS is (2)(3/8)(2/3)(8/(1+8)) or 0.45. Therefore we have, for NMOS,

$C_T = (a)C_0$

$a_{NMOS} = (0.67 + 0.45 + 0.3 + a_2 + a_3)$

Proceeding as before, the optimization equation is obtained:

(32)

$$A\omega_{(NMOS)} = \frac{\mu_n (v_c - 2v_{TN})}{L^2(a)} \left[ \frac{\sqrt{B}}{B+1} \cdot \frac{\sqrt{B} - 1}{\sqrt{B} + 1} \right]$$

Equation 32 differs from the result reported in reference [14]. The magnitude includes a more complete expression for capacitance. The maximizing factor (in square brackets) differs due to the inclusion of the capacitance  $C_{GS2}$  from figure 17. We expect that the maximum of  $A_{\omega}$  and the minimum metastable state duration should both occur at the same value of B. The analysis given in [14] noted some

disagreement between these two extremes. Figure 19 shows that when equation 32 is applied, a better agreement between these two extremes is obtained.

### D. CMOS and NMOS Circuit Performance

A comparison can be made between equations 27 and 32 which give  $A\omega$  for CMOS and NMOS circuits, respectively. The NMOS equation contains  $\mu_n$  where the CMOS equation has  $\sqrt{\mu_n \mu_p}$ . The mobility ratio  $\mu_p / \mu_n$  is typically less than 0.3, but as electron mobility decreases, the ratio increases. Further, as channel length L is decreased the ratio also increases, as described by K. Yu. et. al. [25]. The transistors are operating in the saturation region.

Circuit simulations were performed to determine the variation of A $\omega$  with device ratio for CMOS and NMOS circuits. The simulator used is a highly complex model which incorporates various higherorder effects such as those affecting channel length, mobility reduction, channel charge, etc. The device size ratio B was varied with different values of W<sub>1</sub> and W<sub>2</sub> while maintaining a constant total (W<sub>1</sub> + W<sub>2</sub>) = 100. A 20 percent capacitive load was used (a<sub>2</sub>+a<sub>3</sub> = 0.2). Substrate bias was zero. The circuit parameters were:

$$V_c = 5 v$$

$V_{TD} = -2.5 v$

$V_{TD} = -2.5 v$

$V_{TD} = -2.5 v$

$L = 2.5 \mu m$

$V_{TP} = -0.8 v$

$a_2^{+a_3} = 0.2$

Simulated curves of  $A\omega$  were determined by applying equation 8 to the simulated decay of a metastable state. The results are plotted in figure 20, for CMOS, NMOS enhancement-load, and NMOS depletion-

## Figure 19

Curve of normalized duration  $f_D(B)$  and function  $f_1(B)$  showing coincidence of extremes when load capacitance  $C_{GS2}$  is taken into account.

35

load circuits. The CMOS characteristic is wider, indicating that the optimization of device-size ratio is less critical. As predicted by equation 27, the maximum occurs at R=1. The depletionload characteristic reaches a high maximum value, but falls very quickly as the width of the load device increases.

The values of mobility applicable in this region are significantly lower than the low-field values. For the calculations, we substitute the values obtained by applying the simple MOS formula to the current at  $V_{ds} = V_{gs} = 2.5$ , resulting in 543 cm<sup>2</sup>/V-S for electrons (in both CMOS and NMOS) and 176 cm<sup>2</sup>/V-S for holes. (In the actual circuit, these will not be constant but will have some dependence on device-size ratio.) Determination of effective channel length is given in the Appendix.

Curves based on equations 27 and 32 (shown in dashed lines in figure 20) are calculated using the effective values of mobility and channel length in the region of operation. (An analytical curve is not shown for the depletion load case, because equation 27 is not applicable to that circuit.)

Simulations were performed to determine the supply power versus  $A\omega$  for various flip-flop circuits (figure 21). A clocking frequency of 1.0 MHz was used. The graph shows a lower power requirement for CMOS for a given value of  $A\omega$ . The slopes of the curves are technology specific, and have units of energy.

NMOS synchronization circuits in integrated form have been given in references [14] and [26]. Figure 22 shows an NMOS synchronizer circuit with a provision for input isolation, as described in reference [26].

Figure 20 Circuit gain-bandwidth product variation with device size ratio in NMOS and CMOS. Simulation result is in solid line. Dashed line is result of calculation using equations 27 and 32, with known effective channel lengths and mobility as parameters.

# Figure 21

$A\omega$  vs operating power at 1.0 MHz for CMOS and NMOS. The slope of each curve has units of energy.

38

Figure 22

NMOS Synchronization Circuit given in reference [26].

### III. CMOS Synchronizer Design

A. Essential Requirements

The recognized requirements for ensuring compliance with established design principles are summarized as:

- 1. High gain-bandwidth product. A High-gain bistable element is provided, with synchronous (i.e. system) clocks to gate the asynchronous inputs into the bistable, and to gate the result out of the bistable. The bistable is isolated during the interval between the system clock transitions.

- 2. Input isolation. The first system clock isolates the inputs from the bistable so that input changes cannot influence the bistable after the beginning of the interval.

- 3. Output isolation. Data from the bistable is gated to the next circuit stage of the machine by the occurrence of the second system clock, at the end of the time interval (a constant in time-bounded designs.)

When used as an arbiter to mediate conflicting requests in a system, there may be another circuit to fulfill some queuing requirement for the rejected request. Each asynchronous input should be processed by an input synchronizer before it is allowed to influence the machine's control signals.

B. Integrated CMOS Synchronization Test Circuit

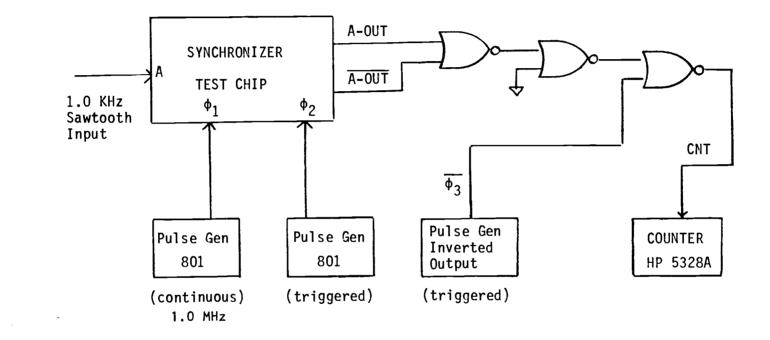

Figure 23 shows the integrated configuration used to test synchronization in a CMOS process. This circuit was constructed in a high-performance CMOS process similar to that described by K. Yu et. al. [25] Except that channel length was 2 microns in [25] and 2.5 microns in the circuit of figure 23. A photomicrograph of

Figure 23 Integrated CMOS Synchronization Test Circuit

the integrated realization is shown in figure 24.

NAND gates formed by M1-M14 isolate the asynchronous input "A".  $\phi_1$  and  $\phi_2$  are system clocks which control the delay interval. After the sampling event, M15-M16 are "off" and M17-M18 are "on" so that the flip-flop M19-M22 will be free of external influence during the interval. The transition of  $\phi_2$  controls special output buffers which have been added to drive external measuring equipment. In an actual system these buffers would not be necessary, and the clock  $\phi_2$  could be used to control series transfer devices, as shown in figure 25. The use of these circuits would further reduce the nodal capacitance, and thus increase overall performance. The addition of another cross-coupled circuit at the output could be added if needed to drive some following circuit load, but such an addition would be effective only after completion of the arbitration event, and hence would not increase the arbitration speed.

A calculation can be made for the gain-bandwidth product of the flip-flop of figure 23, by using equation 27 and the effective parameters applicable in the metastable region of operation as described in section II-D. The values of R,  $a_2$  and  $a_3$  are obtained from the mask design geometries. The values used for this circuit were:

$$V_{TN} = 0.71 v \qquad V_{C} = 5.0 v \\ V_{TP} = -0.71 v \qquad R = 0.66 \\ L = 2.45 \mu m \qquad a_{2} = 0.72 \\ \mu_{n} = 524 \text{ cm}^{2}/\text{V-S} \qquad a_{3} = 0.97 \\ \mu_{n} = 226 \text{ cm}^{2}/\text{V-S}$$

resulting in a calculated value of  $A\omega$  :

$A\omega$  (cal) = 3.2 x 10<sup>9</sup> rad/S

Figure 24 Photomicrograph of the circuit of figure 23. Synchronizing flip-flop is in the center. Large devices at the top are the output buffers. Logic NAND gates for inputs are at the lower left and right. Power supply interconnect is provided at center and at sides.

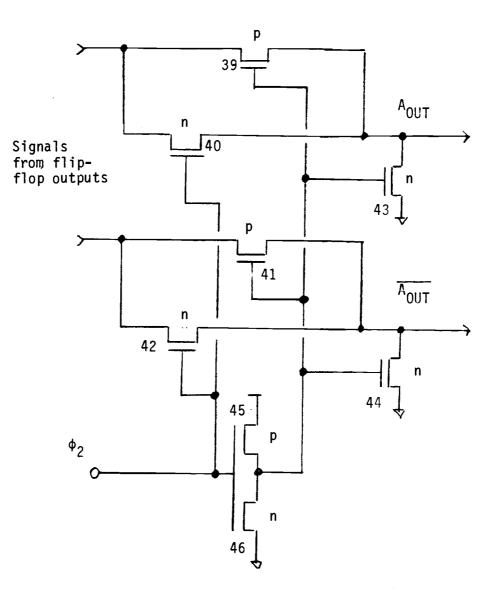

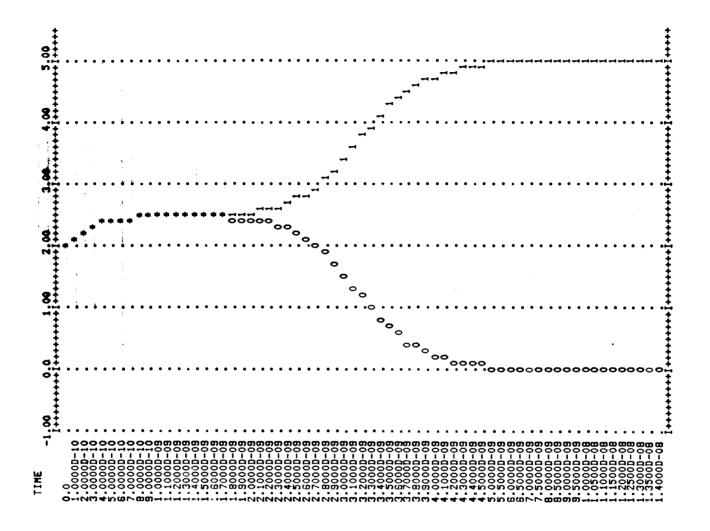

Alternate sampling circuit can be used in integrated synchronizers not requiring output amplifiers as the test circuit does. M39-M42 are "off" during the critical resolution period, so that flip-flop nodes have a lower load capacitance. The outputs then are used to drive other on-chip circuitry and do not need high-current capability. M43 and M44 are provided for noise clamping so that the outputs will not be "floating" (i.e. high impedance) during resolution time. Simulations were performed to predict the settling characteristics of the flip-flop in this circuit. The network model included junction, interconnect and fringing capacitances. The network simulation input is given in appendix A. The simulation output in tabular form is given in table 1. The graphic simulation output is shown in figure 26. Equation 8 is applied to this data, resulting in a value of:

$A\omega$  (simulation) = 2.91 x 10<sup>9</sup> rad/S

Equation 15 is then applied to determine the predicted error rate for the synchronizer. The simulated and calculated error rates are plotted and compared with experimental data in section IV.

| TIME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ♥                                                                                                                                                                                                                                                                                                                                                       | ♥                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | *1.0D+00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <b>*</b> 1.0D+00                                                                                                                                                                                                                                                                                                                                        | ₩1.0D+00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 8 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 7 0                                                                                                                                                                                                                                                                                                                                                     | ₿ 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |