#### AN ABSTRACT OF THE THESIS OF

| Hantak Kwak for the degree of Doctor of Philosophy in Electrical and Computer Engi-                  |

|------------------------------------------------------------------------------------------------------|

| neering presented on <u>December 7, 1998</u> . Title: <u>A Performance Study of Multithreading</u> . |

| Abstract approved:                                                                                   |

| Ben Lee                                                                                              |

As the performance gap between processor and memory grows, memory latency will be a major bottleneck in achieving high processor utilization. Multithreading has emerged as one of the most promising and exciting techniques used to tolerate memory latency by exploiting thread-level parallelism. The question however remains as to how effective multithreading is on tolerating memory latency. Due to the current availability of powerful microprocessors, high-speed networks and software infrastructure systems, a cost-effective parallel machine is often realized using a network of workstations. Therefore, we examine the possibility and the effectiveness of using multithreading in a networked computing environment. Also, we propose the Multithreaded Virtual Processor model as a means of integrating multithreaded programming paradigm and modern superscalar processor with support for fast context switching and thread scheduling. In order to validate our idea, a simulator was developed using a POSIX compliant Pthreads package and a generic superscalar simulator called SimpleScalar glued together with support for multithreading. The simulator is a powerful workbench that enables us to study how future superscalar design and thread management should be modified to better support multithreading. Our studies with MVP show that, in general, the performance improvement comes not only from tolerating memory latency, but also due to the data sharing among threads.

# © Copyright by Hantak Kwak December 7, 1998

All Rights Reserved

## A Performance Study of Multithreading

by

Hantak Kwak

#### A THESIS

submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Completed December 7, 1998

Commencement June 1999

| APPROVED:                                     |                                                                                                                                                            |

|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| THING TEST                                    |                                                                                                                                                            |

|                                               |                                                                                                                                                            |

|                                               |                                                                                                                                                            |

| Major Professor, repr                         | resenting Electrical and Computer Engineering                                                                                                              |

|                                               | $\sim$                                                                                                                                                     |

|                                               |                                                                                                                                                            |

|                                               |                                                                                                                                                            |

| Head of Department                            | of Electrical and Computer Engineering                                                                                                                     |

|                                               |                                                                                                                                                            |

|                                               |                                                                                                                                                            |

|                                               |                                                                                                                                                            |

|                                               |                                                                                                                                                            |

| Dean of Graduate Sc                           | hool                                                                                                                                                       |

|                                               |                                                                                                                                                            |

| I understand that my                          | thesis will become part of the permanent collection of Oregon Sta                                                                                          |

| I understand that my                          | thesis will become part of the permanent collection of Oregon Sta                                                                                          |

| I understand that my<br>University libraries. | thesis will become part of the permanent collection of Oregon State My signature below authorizes release of my thesis to any reached Redacted for Privacy |

#### **ACKNOWLEDGMENT**

I would like to express my sincere gratitude to my advisor, Dr. Ben Lee. He has inspired me throughout my academic years, and this thesis work would have not been possible without his encouragement and patience. Also, I wish to thank Dr. James Herzog, Dr. Shih-Lien Lu, Dr. Un-Ku Moon, and Dr. Mina Ossiander for acting as my program committees.

My friends and colleagues at the Department of Electrical and Computer Engineering have always offered an inspiring and friendly atmosphere. In particular, I would like to thank Ryan Carlson, Mark Dailey, Daniel Ortiz, Mike Miller, YongSeok Seo, YunSeok Kim, KyoungSik Choi, HoSeok An, and many others for their help.

My special thank goes to all my families for their understanding and devotion. They made my life joyful and worthwhile. I would like to thank my father for his unconditional support and encouragement, wife for believing in me, and parent-in-laws for their kindness. Finally, this thesis is dedicated to my mother who is fighting her illness.

### TABLE OF CONTENTS

| <u>P2</u>                                                                                                                                                                                                                                            | age                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 1. Introduction                                                                                                                                                                                                                                      | 1                          |

| 2. Multithreading                                                                                                                                                                                                                                    | 4                          |

| 2.1 Performance Models                                                                                                                                                                                                                               | 4                          |

| 2.1.1 Basic Model                                                                                                                                                                                                                                    |                            |

| 2.2 Programming Models                                                                                                                                                                                                                               | 16                         |

| 2.2.1 Cilk                                                                                                                                                                                                                                           |                            |

| 2.3 Examples of Multithreaded Systems                                                                                                                                                                                                                | 21                         |

| 2.3.1 Threaded Abstract Machine       2         2.3.2 Tera MTA       2         2.3.3 StarT-NG       2         2.3.4 EM-X       2         2.3.5 Alewife       2         2.3.6 The M-Machine       3         2.3.7 Simultaneous Multithreading       3 | 24<br>27<br>29<br>31<br>33 |

| 2.4 New Generation of Multithreading                                                                                                                                                                                                                 | 38                         |

| 2.4.1 Multiscalar                                                                                                                                                                                                                                    | 40                         |

| 3. Viability of Multithreading on Networks of Workstations                                                                                                                                                                                           | 15                         |

| 3.1 Multithreading4                                                                                                                                                                                                                                  | 16                         |

| 3.2 Analytical Models for Matrix Multiplication                                                                                                                                                                                                      | <b>1</b> 7                 |

| 3.2.1 Matrix Multiplication using Message-Passing                                                                                                                                                                                                    |                            |

| 3.3 Experimental Results5                                                                                                                                                                                                                            | 54                         |

| 3.4 Conclusion                                                                                                                                                                                                                                       | 59                         |

| 4. Multithreaded Virtual Processor6                                                                                                                                                                                                                  | 50                         |

| 4.1 MVP Architecture                                                                                                                                                                                                                                 | 51                         |

## TABLE OF CONTENTS (CONTINUED)

| <u>I</u>                                      | <u>Page</u>          |

|-----------------------------------------------|----------------------|

| 4.1.1 Software Layer of MVP                   | . 62<br>. 73         |

| 4.2 MVPsim                                    | . 78                 |

| 4.3 Benchmark Programs                        | . 80                 |

| 4.4 Simulation Results                        | . 82                 |

| 4.4.1 Locality in Caches                      | . 85<br>. 92<br>. 96 |

| 4.5 Conclusion and Future Research Directions | . 98                 |

| Bibliography                                  | 100                  |

## LIST OF FIGURES

| <u>Figure</u>                                                      | Page |

|--------------------------------------------------------------------|------|

| 2.1: Memory latency L is completely hidden in saturation           | 6    |

| 2.2: An example of Cilk program                                    | 17   |

| 2.3: An example of Fibonacci in Cilk.                              | 19   |

| 2.4: TAM activation tree.                                          | 23   |

| 2.5: The organization of Tera MTA.                                 | 25   |

| 2.6: A site structure of *T-NG                                     | 28   |

| 2.7: The structure of EMC-Y                                        | 30   |

| 2.8: The organization of an Alewife node.                          | 33   |

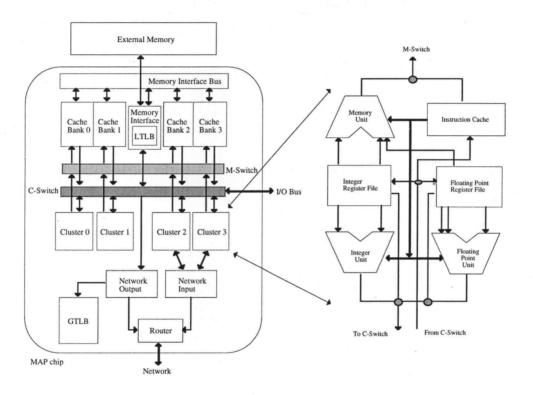

| 2.9: The MAP architecture and its four clusters.                   | 34   |

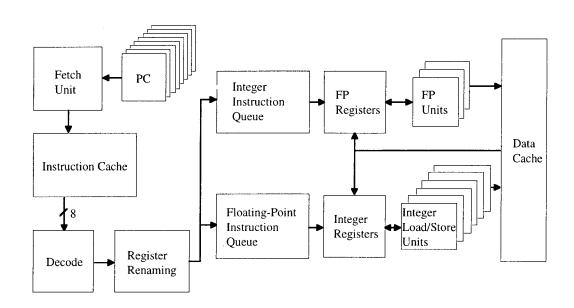

| 2.10: An overview of SMT hardware architecture                     | 36   |

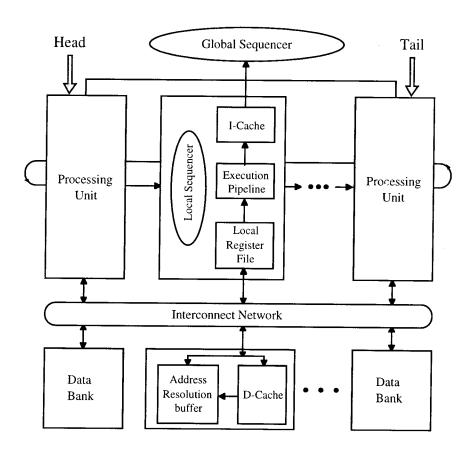

| 2.11: The Multiscalar hardware                                     | 40   |

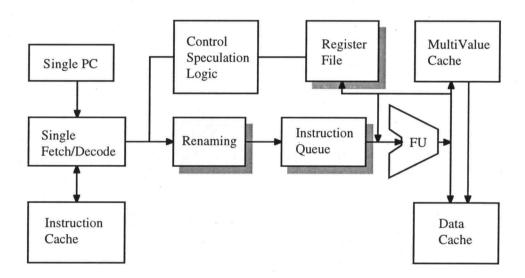

| 2.12: The DeSM architecture                                        | 43   |

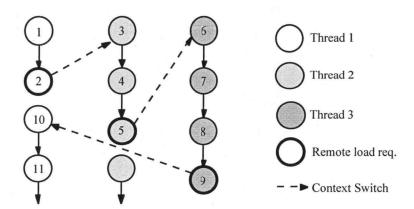

| 3.1: An example of multithreading                                  | 46   |

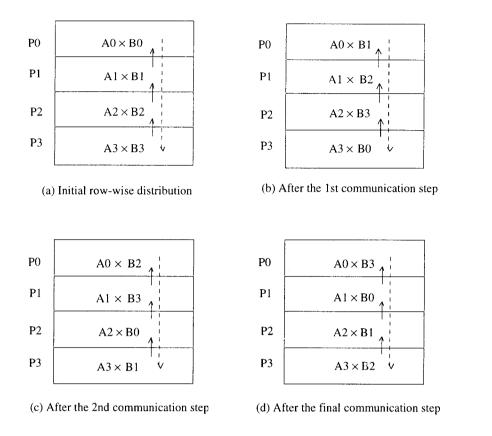

| 3.2: Data distribution among four processors                       | 50   |

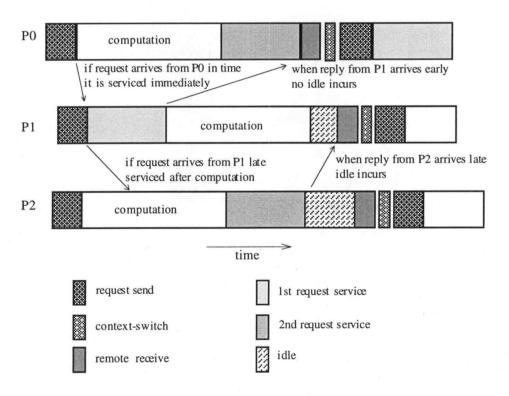

| 3.3: An example of multithreaded execution as a function of time   | 51   |

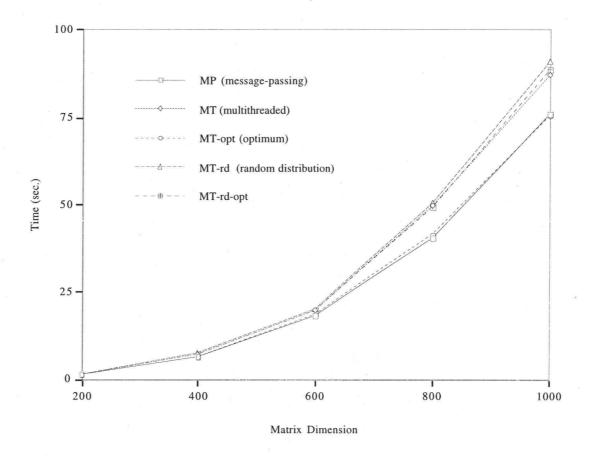

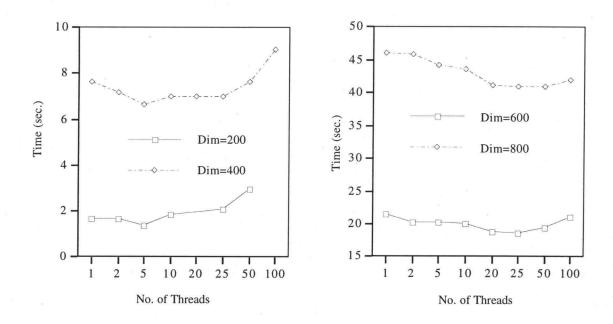

| 3.4: Execution times of message-passing and multithreaded versions | 56   |

| 3.5: Execution time vs. number of threads per processor            | 57   |

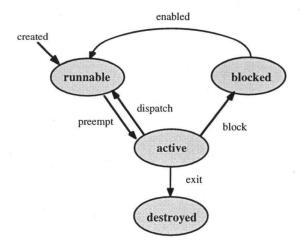

| 3.6: Percentages of various components of a thread execution       | 58   |

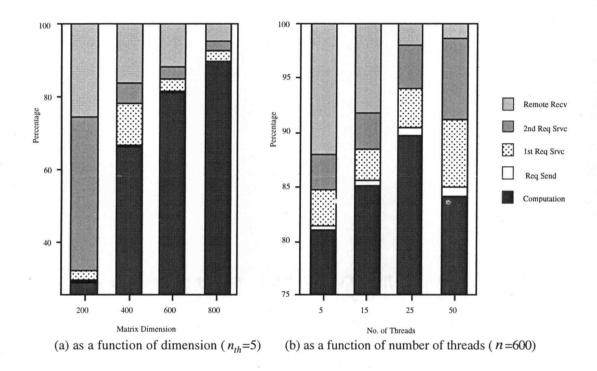

| 4.1: An overview of MVP system                                     | 62   |

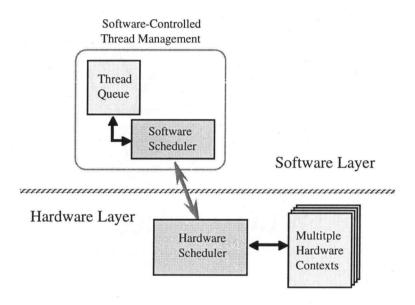

| 4.2: A simplified view of the thread state                         | 65   |

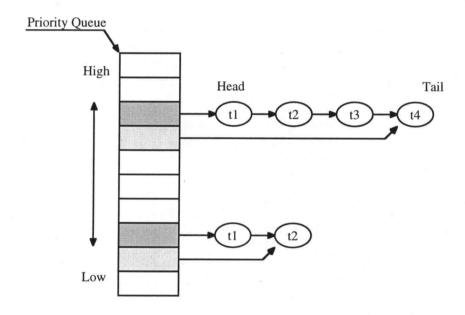

| 4.3: A structure of priority queue in Pthreads                     | 66   |

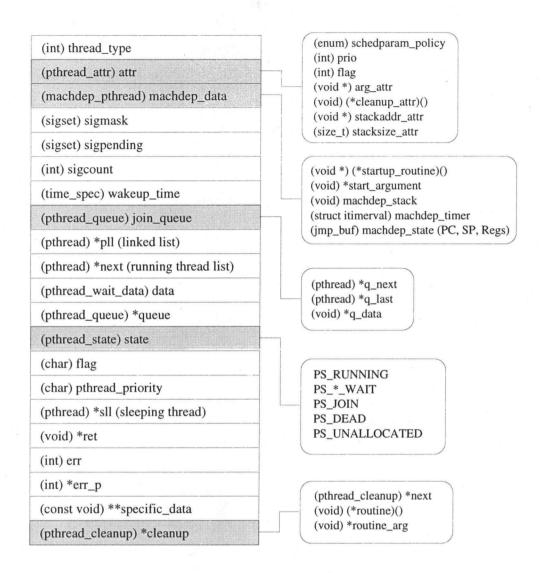

| 4.4: The data structure of Pthreads.                               | 68   |

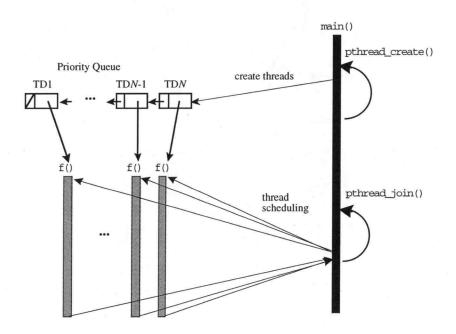

| 4.5: The execution of the given sample Pthreads program.           | 71   |

## LIST OF FIGURES (CONTINUED)

| <u>Figure</u>                                                  | <u>Page</u> |

|----------------------------------------------------------------|-------------|

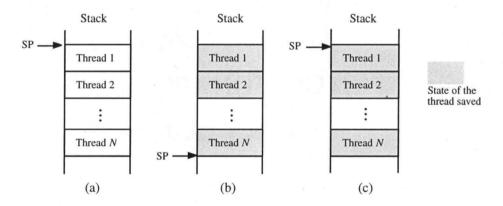

| 4.6: A diagram of stack states                                 | 72          |

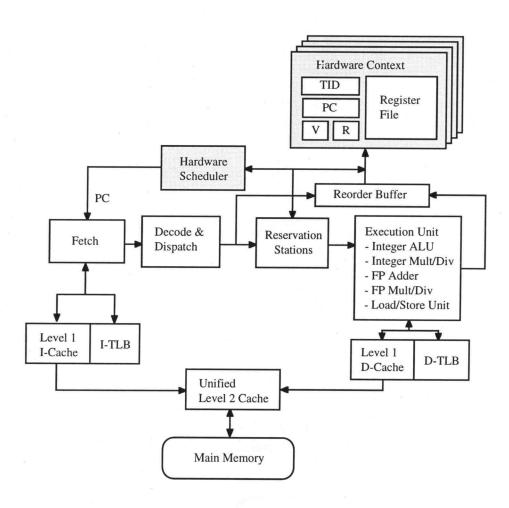

| 4.7: An overview of the MVP hardware system                    | 74          |

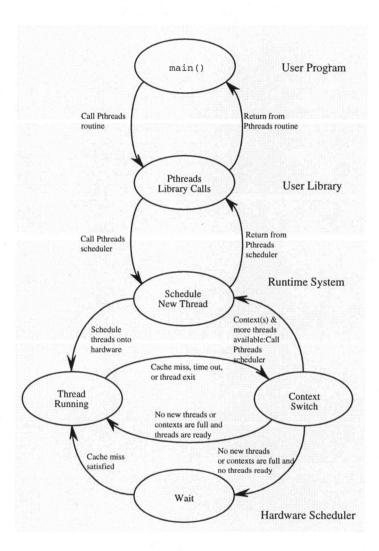

| 4.8: The MVP execution model                                   | 75          |

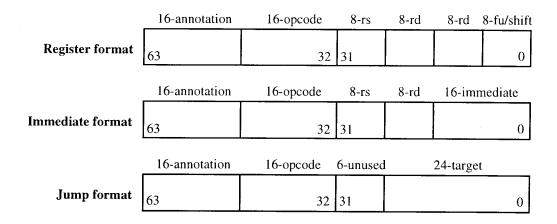

| 4.9: Register definition and Instruction format of MVP.        | 78          |

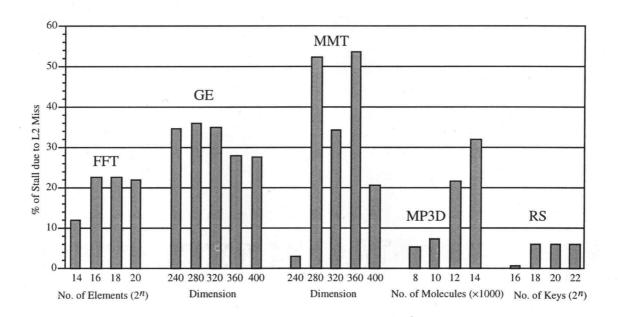

| 4.10: Percentage of latency incurred due to L2 cache misses.   | 83          |

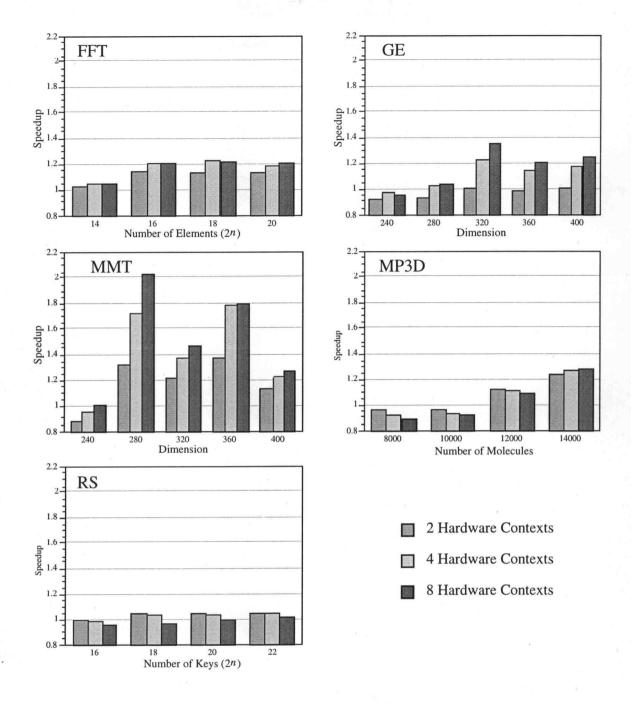

| 4.11: Speedup of five benchmarks over serial execution.        | 84          |

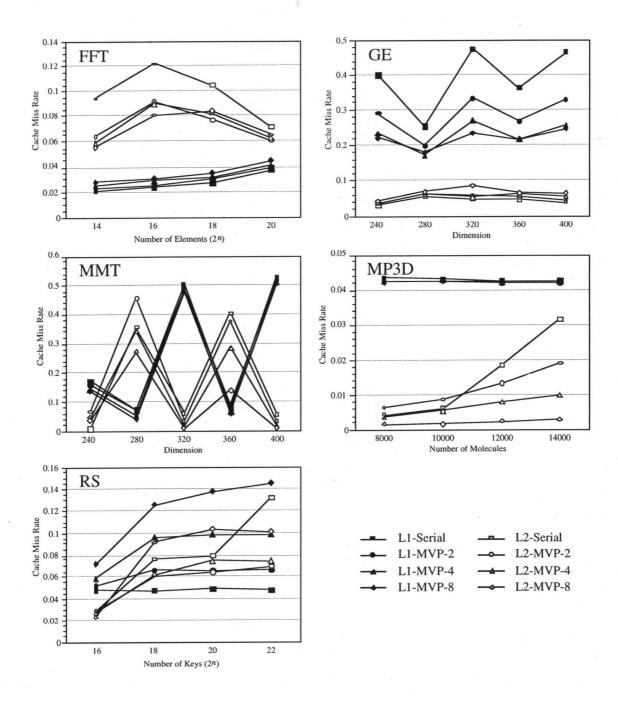

| 4.12: The miss rates for L1 D-cache and L2 cache.              | 86          |

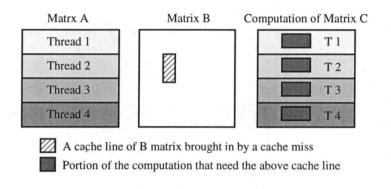

| 4.13: An example of data sharing in MMT.                       | 87          |

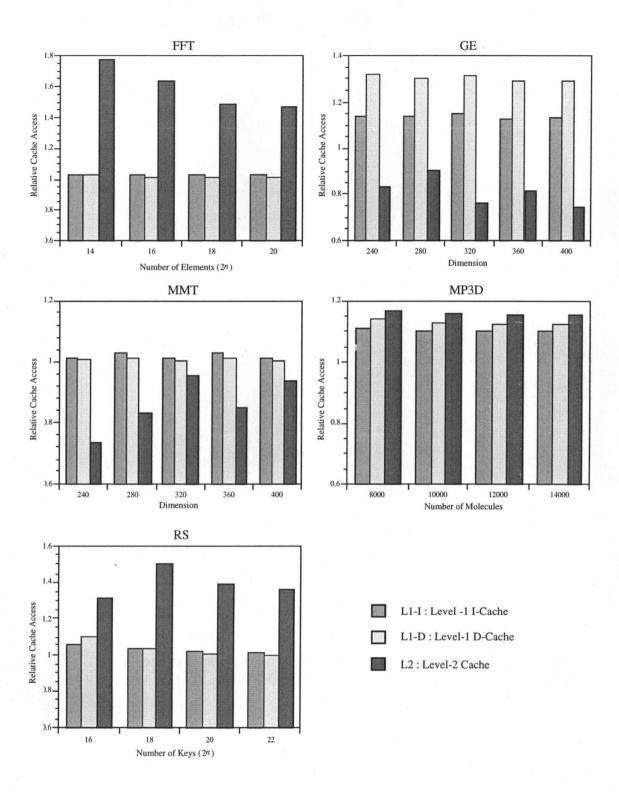

| 4.14: The relative cache accesses made by MVP.                 | 89          |

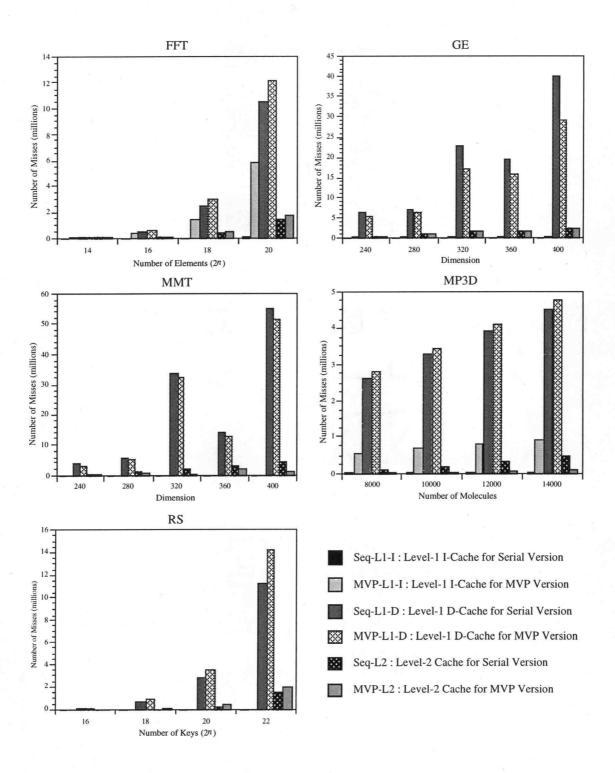

| 4.15: The number of misses in L1 and L2 caches.                | . 91        |

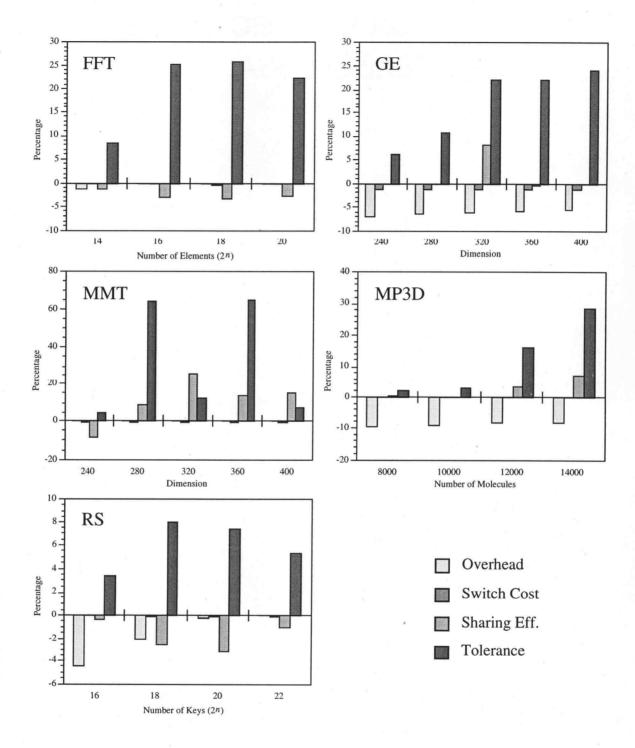

| 4.16: Breakdown of the various components of the MVP execution | . 95        |

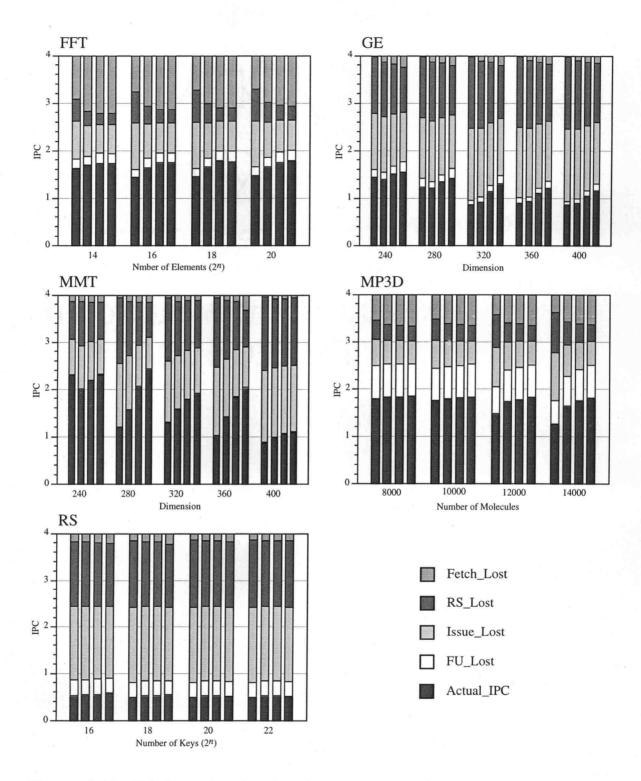

| 4.17: IPC for various benchmarks.                              | . 97        |

## LIST OF TABLES

| <u>Table</u>                                                 | Page |

|--------------------------------------------------------------|------|

| 2.1: The access control values.                              | 27   |

| 3.1: Speedup of multithreaded version vs. sequential version | 55   |

| 4.1: Some of the features provided by Pthreads.              | 64   |

| 4.2: Various queues and their associated functions           | 65   |

| 4.3: Description of registers in MVP.                        | 77   |

| 4.4: Simulated FUs and their latencies.                      | 80   |

| 4.5: Configuration of L1 and L2 caches.                      | 80   |

#### A PERFORMANCE STUDY OF MULTITHREADING

#### 1. Introduction

In an effort to overcome the limitations of circuit technology, computer architects have resorted to exploiting instruction-level parallelism (ILP) for improving processor utilization. In addition, techniques such as on-chip caches, superpipelining, long instruction words, branch prediction and speculative execution are also employed. The superscalar architecture, which almost all of the current microprocessors are based on, has been very successful in exploiting ILP. However, recent studies have shown that the single-threaded paradigm used by conventional programming languages and runtime systems do not fully utilize the processor's capabilities. This is due to the fact that the advances in VLSI technology have led to faster clocks and processor designs that can issue multiple instructions per cycle; yet the performance of memory system has not increased proportionally. The speed of commercial microprocessors has increased by a factor of twelve over the past ten years while the speed of memories has only doubled [24].

The widening of processor-memory gap reduces the processor utilization since the processor has to spend more cycles for memory accesses. Also, stalls due to cache misses severely degrade the overall performance by disrupting the pipeline. The result is the decrease in the number of potential instructions that can be issued in each cycle for superscalar, thus effectively reducing the ILP. Consequently, no matter what microarchitectural techniques are used, the performance of a processor will soon be limited by the memory characteristics. Therefore, this thesis examines an alternative technique, called multithreading, as a solution to the memory latency and the limited ILP problems.

Multithreading has emerged as one of the most promising and exciting techniques to tolerate the memory latency. While a single threaded model of computation

does not provide mechanisms to tolerate the memory latency, multithreading provides the processor with a pool of threads and context switching occurs between the threads not only to hide memory latency, but also other long latency operations such as I/O and synchronization operations. The processor may also interleave instructions on a cycle-by-cycle basis from multiple threads to minimize pipeline breaks due to dependencies among instructions within a thread. This allows the threads to dynamically share the processor's resources and increases the processor utilization.

To provide better understanding of multithreading, Chapter 2 introduces analytical models of multithreading that characterize the performance of multithreading as well as its limitations. Also, a comprehensive survey of multithreaded systems is provided that includes programming languages, compiling techniques and various architectures along with the latest multithreading techniques.

As an alternative to expensive Massively Parallel Processors (MPP) or Symmetric Multiprocessor (SMP) systems, it is possible to build a low-cost parallel machine by utilizing a network of workstations (NOWs). A software infrastructure system facilitates a construction of a virtual parallel machine using a collection of workstations. A shared-memory abstraction can also be provided on top of physically distributed memory system. However, the performance of a parallel machine based on NOWs may suffer from long and unpredictable memory latency due to the distributed nature of the underlying physical memory system. Therefore, Chapter 3 studies the viability and effectiveness of multithreading in a network-based multiprocessor system. In particular, we examine a matrix multiplication problem on a network of workstations to see how effective multithreading is in a distributed shared-memory (DSM) environment.

Finally, Chapter 4 investigates how future processors can adopt the multithreaded architecture such that the departure from current microarchitecture is minimal, yet provides better performance. We propose the Multithreaded Virtual Processor (MVP) system that exploits the synergy between the multithreaded programming paradigm and the well-designed contemporary microprocessors.

#### 2. Multithreading

In the last decade, researches on multithreading techniques have led to substantial improvements over traditional single threaded abstractions. This chapter provides a summary of these efforts in designing multithreaded systems that includes new programming languages, new compiling techniques, and architectures. The organization of the chapter is as follows: Section 2.1 presents analytical models of multithreading. Section 2.2 discusses the multithreading in terms of programming models. Section 2.3 provides an overview of various multithreaded architectures along with their key features. Finally, Section 2.4 presents current research efforts in multithreading.

#### 2.1 Performance Models

A multithreaded system contains multiple *loci of control* (or threads) within a single program, and the processor switches among threads to hide long latencies. Therefore, multithreading allows the exploitation of thread-level parallelism and improves the processor utilization. However, there is a limitation to the improvement that can be achieved. The most important limitation is due to the fact that applications running on a multithreaded system may not exhibit sufficiently large degrees of parallelism to permit the identification and scheduling of multiple threads to the processor. Even if sufficient parallelism exists, the cost of multithreading should be traded off against any loss in performance due to active threads sharing the cache and processor cycles wasted during context-switch.

The performance of a multithreaded processor depends on several architectural and program parameters—the memory latency, the remote reference rate, the number of threads, the thread length, the context switching cost, etc. A simple analytical model of

multithreaded processor behavior provides a better understanding of (1) how these parameters are interrelated, (2) how the number of threads affects the processor utilization, (3) how much context switching costs contribute to the overall performance, and (4) how the program should be partitioned into threads.

#### 2.1.1 Basic Model

Saavedra *et al.* proposed a simple multithreaded processor model based on a set of parameters that reflects the architectural and software characteristics [76]. Assume the processor switches between threads only on long latency operations, such as remote memory accesses. Let L denote a fixed latency for such operations. Let R be the average amount of time that each thread executes before encountering a long latency operation. Let C be the fixed overhead in switching between threads. The processor utilization of a single thread model can be described by

$$U_1 = \frac{R}{R+L}. (2.1)$$

Equation 2.1 shows that the utilization is limited by the frequency of long latency operations (i.e., 1/R), and the average time required to service the long latency operation L. Therefore, the large memory latency has an adverse effect on the utilization in a processor with a single thread.

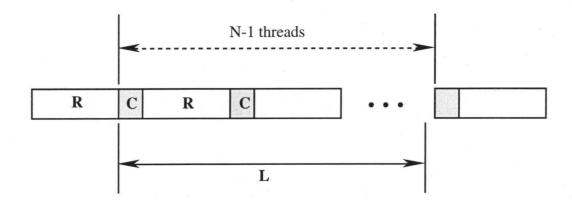

If L is much larger than the time to context-switch between threads, C, then useful work can be performed during long latency operations. In addition, if the number of threads is sufficiently large, the latency can be completely hidden as shown in Figure 2.1. In such a case, the processor utilization can be described as

$$U_{sat} = \frac{R}{R+C},\tag{2.2}$$

where the number of threads required to totally mask L is assumed  $N_{sat}$ . This saturation number of threads satisfies the following requirement:

$$N_{sat} \ge \frac{R+L}{R+C}$$

.

Note that increasing the number of threads beyond  $N_{sat}$  will not increase the processor utilization.

Figure 2.1: Memory latency L is completely hidden in saturation.

If there are insufficient number of threads to totally mask the latency L, the processor utilization can be described by

$$U_{N} = \frac{NR}{R+L},$$

where N is the number of threads. This equation shows that the utilization increases linearly with the number of available contexts until the number reaches the saturation point  $N_{sat}$ . Note that  $U_{sat}$  is the upper limit on the utilization achievable through multithreading in this performance model. Using the above equations, the speedup that can be achieved is given by

$$S_N = \frac{U_N}{U_1} = \begin{cases} N & \text{if } N < N_{SAT} \\ \frac{R+L}{R+C} & \text{otherwise} \end{cases}.$$

As shown above, the minimum number of threads needed to achieve maximum utilization,  $N_{sat} \ge (R+L)/(R+C)$ , depends on time between context-switches (R), the time to service long latency operation (L), and the context switching overhead (C). For example, assuming a fine grained multithreaded system with R=1 and the context switching overhead is negligible (e.g., using multiple hardware contexts), the optimum utilization requires at least (1+L) threads. When C is not negligible, R should be much larger (i.e., coarser-grain multithreading) to achieve useful performance gains. Also, the improved processor utilization comes at an increased cost of supporting multiple threads, such as additional hardware for multiple contexts and the processor cycles wasted for context switching.

The above model ignored the performance impact due to higher cache miss rates in a multithreaded system and higher demands on the network placed by higher processor utilization. In addition, the above model assumed fixed latencies, and fixed frequency of long latency operations in threads. Assuming a context-switch occurs on every cache miss, we can equate cache miss rate m with the frequency of long latency operations,  $\rho = 1/R$ . Then, the speedup of a multithreaded system can be rewritten as

$$S_N = \frac{U_N}{U_1} = \begin{cases} N & \text{if } N < N_{sat} \\ \frac{1 + mL}{1 + mC} & \text{otherwise} \end{cases}.$$

The cache miss penalty is the primary contributor to L. Note that we assume constant cache miss rate and miss penalty in the above equation. The effect of context switching on other long latency operations such as synchronization delays can also be added to above equation.

#### 2.1.2 Cache and Network Model

In the previous section, it is assumed that cache miss rate and miss penalties are not affected by multithreading. The analytical performance model, proposed by Agarwal [6], considers multithreading with cache interference, network contention, and context switching overhead. In multithreaded processors with caches, multiple threads are simultaneously active and they interfere with each other, creating a higher cache miss rate and a higher network contention. The cache miss rate is negatively affected by increasing the degree of multithreading. Likewise, the miss penalty increases with the number of threads due to higher network utilization—leading to longer delays in accessing remote memory modules. Therefore, a mathematical model of multithreaded processors must reflect these characteristics. In conducting this analysis, the following assumptions are made:

- All threads resident in a processor have the same cache miss rate and working set size.

- The processes execute useful instructions between cache misses.

- Context-switch occurs only on a cache miss and the processor cycles spent for context switching are considered wasted.

- Network requests occur only on cache misses and cache invalidation.

- Data sharing and compulsory cache misses (i.e., misses that occur when the part

of resident working set or new blocks are brought in the cache) are ignored.

The parameters used to develop the model are as follows:

- p the number of threads resident in a processor.

- C context switching overhead.

Suppose that a process executes useful instructions for R cycles, and then a cache miss occurs. Assuming the cache miss requires L cycles before the process can resume, Equations 2.1 and 2.2 can be rewritten such that the processor utilization is expressed in terms of cache miss rates m(p). Since cache the miss rate is simply the inverse of R, the utilization is then,

$$U(p) = \begin{cases} \frac{p}{1 + Lm(p)}, & \text{for } p < \frac{1 + Lm(p)}{1 + Cm(p)} \\ \frac{1}{1 + Cm(p)}, & \text{for } p \ge \frac{1 + Lm(p)}{1 + Cm(p)}. \end{cases}$$

First, consider the network effect. The cache miss service time, L, depends on the network latency and memory access time. In particular, for a packet-switched k-ary n-cube interconnection network with cut-through routing, the network parameters and assumptions can be defined as follows:

#### **Parameters**

- *M* memory access time.

- B message size.

- *k* network radix.

- *n* network dimension.

- $\rho$  network channel utilization.

- $k_d$  -average distance a message travels.

- h network switch delay (i.e., the number of hops a message make).

#### **Assumptions**

- Uniform traffic rate for all nodes.

- Uniform distribution of message target nodes.

- Infinite buffering at each intermediate node.

Then, the average L for buffered k-ary n-cube direct network is given in [2] as

$$T(p) = \left[1 + \frac{\rho B \frac{1}{k_d} \left(1 - \frac{1}{k_d}\right)}{\left(1 - \rho\right)}\right] h + M + B - 1.$$

(2.3)

This cache miss service time is calculated as the sum of memory access time, M, the pipeline latency of the message size, B-1, and network switch delay h (i.e., h/2 for request and h/2 for response). Assuming separate communication channels for both directions, the expected number of hops,  $k_d$ , between two randomly chosen node in a 1-dimensional array can be estimated by the ratio of the sum of distances for all source-destination pairs to the total number of such pairs [2].

$$k_d = \frac{k^2 - 1}{3k} \approx \frac{k}{3}.\tag{2.4}$$

The probability of a network request on any cycle is 2p/[R+L] (the factor two accounts for both memory requests and responses), and the channel utilization factor  $\rho$  is given in [6] as

$$\rho = \frac{2p}{R+L} \cdot \frac{Bnk_d}{2n} = \frac{p}{R+L} Bk_d. \tag{2.5}$$

Substituting Equation 2.4 and 2.5 into 2.4, and setting R = 1/m(p), we arrive at

$$L = \frac{T_o}{2} + \frac{Bpk}{6} - \frac{1}{2m(p)} + \frac{1}{2}\sqrt{\left(T_o - \frac{Bpk}{3} + \frac{1}{m(p)}\right)^2 + 8pB^2n\frac{k}{3}\left(1 - \frac{3}{k}\right)},$$

where  $T_0 = h + M + B - 1$ . Note that L increases almost linearly with p, the number of threads.

Now consider the cache effect. The cache model must characterize the increase in the miss rate as the number of threads resident in a processor increases. The assumptions in this model include:

- direct-mapped cache and uniform address mapping

- working-set cache model (i.e., only small portion of program is required in the cache at a time for the execution of a program)

In order to study the impact of multiple threads on cache miss rates, the cache misses are classified into four categories [3]: nonstationary, intrinsic interference, multiprogramming, and coherence-related misses. The nonstationary misses,  $m_{ns}$ , occur when a miss brings a new block into the cache for the first time. The intrinsic interference,  $m_{intr}$ , results when the blocks interfere with each other in the cache during block replacements. The multiprogramming misses, m(p), account for the cases when one process (or

thread) displaces the cache blocks of another thread. Coherency related invalidation,  $m_{inv}$ , occurs in multiprocessor systems where the changes made in one processor may require invalidation of other processor cache entries. The cache model is based on the following additional parameters.

- S cache size.

- *u* working set size in blocks.

- $\tau$  period between measurement of working set.

- c collision rate used for interference misses.

- v size of the carry-over set.

- $m_{fixed}$  fixed miss rate assumed in this model, i.e.,  $m_{fixed} = m_{ns} + m_{inv}$ .

The computation of intrinsic interference and multiprogramming miss rate requires the estimation of the carry-over set size. The size of carry-over set, v, is the number of blocks a thread leaves behind in the working set when it switches out. Assuming every block maps into the cache with the same probability 1/S, the v is then given by

$$v = S[1 - (1 - 1/S)^{u}], \tag{2.6}$$

where the term  $\left[1-(1-1/S)^u\right]$  indicates the probability that at least one block maps into a cache set. When S >> 1, Equation 2.6 simplifies to

$$v = S(1 - e^{-\frac{u}{S}}).$$

Let v'(p) denote the steady state carry-over set size under the condition that p processors share the cache for short duration of context switching. In a multithreaded cache, a thread effectively sees a smaller cache, resulting in an increase in both the intrinsic interference and multiprogramming miss rates [6]. Also, the additional context switching component of miss rate,  $m'_{cs}(p)$ , is introduced due to restoring of thread's displaced blocks when a new thread is scheduled on a processor. The  $m'_{cs}(p)$  can be obtained as a function of v'(p) as

$$m'_{cs}(p) = \frac{v - v'(p)}{v} \cdot \frac{u}{\tau}.$$

(2.7)

If we consider the probability that a block of intervening (p-1) threads maps to the top of a block, an alternative expression for  $m'_{cs}(p)$  is also obtained:

$$m'_{cs}(p) = \frac{v'(p)}{S}(p-1) \cdot \frac{u}{\tau}.$$

(2.8)

By equating (2.7) and (2.8), the v'(p) is expressed as

$$v'(p) = \frac{v}{1 + v \frac{(p-1)}{S}}.$$

(2.9)

Equation 2.9 signifies two occasions: (1) when the cache is very large (S >> v), the approximation  $v'(p) \approx v \approx u$  holds, indicating the cache can hold the entire working set of all the threads, and (2) when S = v, the effective size of cached working set of each thread becomes v/p.

The intrinsic interference miss rate in a direct-mapped cache given in [1] is

$$m_{intr} = \frac{c}{\tau} \left[ u - S \cdot bin(u, \frac{1}{S}, d = 1) \right] = \frac{c}{\tau} \left[ u - u \left( 1 - \frac{1}{S} \right)^{(u-1)} \right]$$

$$\approx \frac{c}{\tau} \left( u - u e^{\frac{u}{S}} \right), \tag{2.10}$$

where  $bin(u,1/S,d) = \binom{u}{d} \binom{1}{S}^d \left(1 - \left(\frac{1}{S}\right)\right)^{u-d}$ . The binomial distribution above indicates the probability that d blocks from the working set of size u map into one of the S cache sets. In general, the size of the carry-over set of a thread in a multithreaded cache is smaller than the size in a multiprogrammed cache (i.e.,  $v'(p) \le v(p)$ ). The number of colliding blocks in a multithreaded caches also increases. The colliding blocks are the blocks that map into the same cache set. Assuming random placement of blocks in the cache, the estimated number of non-colliding blocks in multithreaded cache is given by

$$u\left(1 - \frac{1}{S}\right)^{u-1} \frac{v'(p)}{v} \approx ue^{-\frac{u}{S}} \frac{v'(p)}{v}.$$

(2.11)

From (2.10) and (2.11), the intrinsic interference miss rate of the multithreaded cache becomes

$$m'_{intr} = \frac{c}{\tau} \left[ u - ue^{-\frac{u}{S}} \frac{v'(p)}{v(p)} \right].$$

Thus, the net increase in the miss rate of multithreaded cache, m'(p), is

$$m'(p) = m'_{cs}(p) + m'_{intr}(p) - m_{intr}(p)$$

$$=v'(p)\frac{(p-1)}{S}\cdot\frac{u}{\tau}+\frac{c}{\tau}ue^{-\frac{u}{S}}\left[1-\frac{v'(p)}{v(p)}\right].$$

Finally, the overall cache miss rate is computed by considering three components of fixed miss rate  $m_{fixed}$ , the single thread interference miss rate  $m_{intr}$ , and the multithreading components  $m'_{intr}$ , yielding

$$m(p) = m_{fixed} + m_{intr}(p) + m'(p)$$

$$= m_{fixed} + m_{intr}(p) \left( 1 + \frac{(p-1)(1+1/c)}{1+(p-1)\frac{u}{S}} \right),$$

where

$$m_{intr}(p) \approx \frac{c}{\tau} \cdot \frac{u^2}{S}$$

.

Increasing the degree of multithreading will effect both the intrinsic-interference and the multiprogramming component of the cache misses. When more threads occupy the cache, we can assume that each thread is allocated a smaller working set, and this in turn leads to higher intrinsic conflicts. Likewise, as the number of threads increases, the multiprogramming-related component also increases since there is a higher probability that cache blocks of active threads displace those of inactive threads. It is interesting to note that with sufficiently large cache memories, the multiprogramming related component of the cache miss rate is not affected by the number of threads. This is because the cache memory is large enough to hold the working sets of all resident threads. Set associativity is another issue that significantly affects the performance of cache memories for multithreaded systems. The higher associativity of cache can compensate for the increased intrinsic interference in a multithreaded system.

#### 2.2 Programming Models

A thread can be viewed as a unit of execution that can be active within a process sharing certain resources such as files, address space with other threads in the process space. The notion of threads or lightweight processes permits the programming of applications using *virtual processes* such that a process can continue execution even when one or more of its threads are blocked. This concurrency can be supported in many different ways. For example, thread library, such as C-threads [23] and Pthreads [15], provide the programmers with API (Application Programming Interface) for creating, invoking, and scheduling threads.

The library implementation of threads usually supports the coarse-grain block multithreading. The block multithreading often requires synchronization among threads using semaphores, mutexes, and conditional variables. Also, thread scheduling mechanism is usually implemented using join, suspend, detach, and terminate calls. On the other hand, functional programming languages such as Multilisp [36] and Id [65] have proposed a different approach on multithreading, often supporting fine-grain threads. In such languages, traditionally blocking or synchronous function calls are made non-blocking or asynchronous. For example, when a function is invoked in conventional languages, the control transfers to the called function (blocking the execution of the caller) and the control is returned to the caller upon its completion. However, Multilisp function calls, e.g., *futures*, are non-blocking so that several futures can be invoked without waiting for their completion. In the following subsections, two programming models that support multithreading, namely *Cilk* and *Cid*, are introduced. The description of Pthreads is deferred until Chapter 4.

#### 2.2.1 Cilk

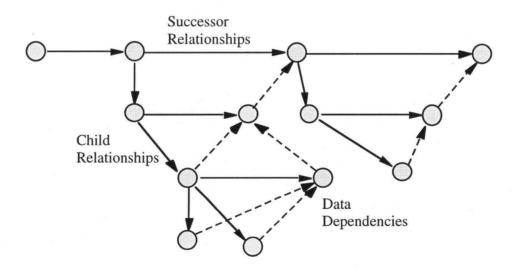

Cilk language is an extension of C which provides an abstraction of threads in explicit continuation passing style [12]. The Cilk runtime supports work stealing for scheduling threads and achieves load balancing across a distribute processing environment. A Cilk program consists of a collection of procedures, each in turn consists of threads. These threads of a Cilk program can be viewed as the nodes of a directed acyclic graph as shown in Figure 2.2. Each horizontal edge represents a creation of a successor thread, and a downward edge represents the creation of child threads while data dependencies are represented by the dashed lines.

Figure 2.2: An example of Cilk program.

Like TAM threads, Cilk threads are non-blocking. This requires the creation of successor threads that expect the results from the child threads. The successor thread is blocked until the necessary synchronization events (or release conditions) are satisfied.

Cilk threads can spawn child threads to execute a new procedure. The child threads normally return values or synchronize with the successor threads created by their parent thread.

The runtime system keeps track of the active threads and threads awaiting for initiation. The data structure used for thread management is called a *closure*. A closure consists of a pointer to the code of the thread, a slot for each of the input parameters, and a join counter indicating the number of missing values (or synchronization events). The closure (hence the thread) becomes ready to executed when the join counter becomes zero; otherwise the closure is known as waiting. The missing values are provided by other threads using *continuation passing*, which identifies the thread closure and the argument position within the thread.

The following shows a Cilk program segment for computing the  $n^{th}$  Fibonacci number.

```

thread fib (cont int k, int n)

{

if (n<2)

send_argument (k, n)

else{

cont int x, y;

spawn_next sum (k, ?x, ?y);

spawn fib (x, n-1);

spawn fib (y, n-2);

}

}

thread sum (cont int k, int x, int y)

{

send_argument (k, x+y);

}</pre>

```

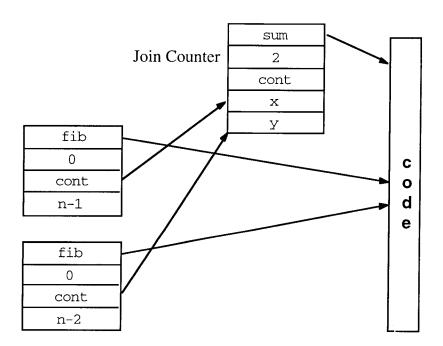

The program consists of two threads, fib and its successor sum (which waits for the recursive fib calls to complete and provide the necessary values to sum). The fib threads test the input argument n, and if it is greater than 2, it spawns the successor thread sum

by passing the continuation k. Since sum requires two inputs x and y before becoming enabled, it spawns two child threads with n-1 and n-2 as their arguments as well as the slots where they should send their results (specified by the cont parameter). The statement send\_argument sends the results to the appropriate continuation. The closure structure for the above Fibonacci program is shown in Figure 2.3.

Cilk run-time system uses an innovative approach to load distribution known as work stealing [11]. In this scheme, an idle worker (processor) randomly selects a heavily loaded processor and steals a portion of its work, thus achieving load balancing. However, only the ready threads are stolen in order to avoid the complications of relocating the continuation slots of the stolen threads.

Figure 2.3: An example of Fibonacci in Cilk.

#### 2.2.2 Cid

Cid is a parallel extension of C that provides a MIMD threads plus shared objects programming model even though it runs on distributed memory machines, such as workstation farms (Note that there is no explicit message-passing in Cid) [64]. Cid provides all threads with a shared memory space of objects. A Cid thread is an asynchronous C function call. Any C variable or data structure can be registered as a Cid global object, and each global object is associated with a pointer which is unique to across all processors. Given its global pointer, any thread on any PE can access any object, and the Cid run-time system manages all the necessary coherency of the objects. Also, Cid run-time scheduler can automatically achieve load-balancing based on a work-stealing mechanism. However, a thread does not further migrate between PEs once initiated.

Unlike TAM and Cilk, Cid threads can block, waiting for synchronization. Each Cid thread can be viewed as a C function with appropriate mechanism to specify synchronization. The simplest type synchronization is based on Join and the associated variables. Consider the following Cid implementation of the Fibonacci function.

```

int fib(int n)

{

int fibN1, fibN2;

cid_initialized_jvar(joinvariable);

if (N<2) return n

else

{

cid_fork(joinvariable;)

fibN1 = fib(n-1); fibN2=fib(n-2);

cid_jwait(&joinvariable);

return fibN1+fibN2;

}

}</pre>

```

When the value of N is greater than 2, two new threads are forked using cid\_fork to compute fib(n-1) and fib(n-2). The cid\_fork also indicates that these computations synchronize using join on the joinvariable specified. The parent thread will wait for the completion of the child threads and then returns the sum of fib(n-1) and fib(n-2) and signals appropriate joinvariable. Note that the Cid system is responsible for initializing the joinvariable as indicated by cid\_initialized\_jvar.

#### 2.3 Examples of Multithreaded Systems

This section provides an overview of various multithreaded architectures and discusses some of the software and hardware features that represent the past and the current research efforts in the multithreading community. The architectures included in the discussion are TAM, Tera, MIT's Alewife, M-Machine, Electrotechnical Lab's EM-X, DEC/MIT's StarT-Next Generation, Stanford's FLASH, and Simultaneous Multithreading.

#### 2.3.1 Threaded Abstract Machine

David E. Culler and his colleagues at U. C. Berkeley proposed the Threaded Abstract Machine (TAM) as an efficient execution model which maps the dataflow execution model onto a self-scheduled control flow execution model [27]. The novel aspect of TAM is how it allows the compiler to integrate the interactions among the scheduling of parallel threads, the asynchronous message events, and the utilization of the storage hierarchy. TAM exposes the scheduling of threads so that the compiler can optimize the storage resources (e.g., registers, local memory, etc.) by scheduling the related instructions together within a thread or even across threads. This improves the register utiliza-

tion and the cache behavior by enhancing the locality of references, which is not present in the traditional dataflow architecture.

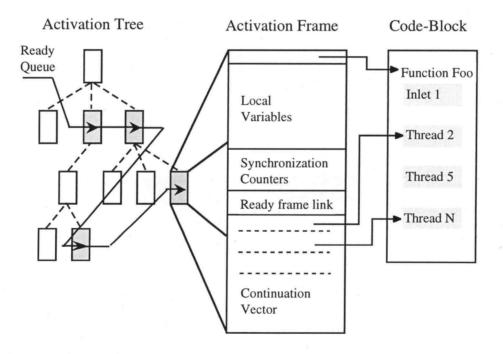

Thread partitioning in TAM involves several steps: Id90 to dataflow graphs, program graphs to TAM threads, and finally TAM to native machine code. The threaded machine language, TLO, was designed to permit programming using the TAM model. TAM recognizes three major storage resources—code-blocks, frames, and structures—and the existence of critical processor resources, such as registers. A program is represented by a collection of re-entrant code-blocks, corresponding roughly to individual functions or loop bodies in the high-level program text. A code-block comprises a collection of threads and inlets. Invoking a code-block involves allocating a frame—much like a conventional call frame—depositing argument values into locations within the frame, and enabling threads within the code-block for execution. The compiler statically determines the frame size for each code-block and is also responsible for correctly using slots and registers under all possible dynamic thread orderings. The compiler also reserves a portion of the frame as a continuation vector, used at run-time, to hold pointers to enabled threads. The global scheduling pool is a set of frames that contain enabled threads.

Executing code-block may invoke several code-blocks concurrently because the caller is not suspended as opposed to conventional languages. Therefore, the set of frames in existence at any time forms a tree (the activation tree) rather than a stack, reflecting the dynamic call structure shown in Figure 2.4. An activation is enabled if its frame contains any enabled threads, and multiple subset of enabled activations may be resident in the processor at any time.

Threads can be categorized as synchronizing or non-synchronizing. A synchronizing thread specifies a frame slot containing the entry count for the thread. The compiler is responsible for initialization of the correct entry counts for synchronizing threads. Each *fork* to a synchronizing thread causes the entry count to be decreased by

one, and the thread may execute only when the count reaches zero. Synchronization occurs only at the start of a thread, and the thread executes to completion when the synchronization requirement is met. A thread ends with stop instruction, causing another thread to be scheduled.

Conditional flow of execution is supported by a switch instruction, which forks one of two threads based on a boolean input value. Also, fork operations may occur anywhere within a thread and cause additional threads to be enabled for execution. Long latency operations, such as I-Fetch or Send, implicitly fork a thread that resumes when the request completes. This allows the processor to continue with useful work while the remote access is outstanding.

Figure 2.4: TAM activation tree.

#### 2.3.2 Tera MTA

Tera MTA (MultiThreaded Architecture) computer is a multistream MIMD system developed by Tera Computer Company in the late 1980's [8], and it is the only commercially available multithreaded architecture. The designers of the system tried to achieve the following three goals: (1) high-speed, highly-scalable architecture, (2) be applicable to a wide variety of problems, including numeric and non-numeric languages, and (3) ease the implementation of compiler.

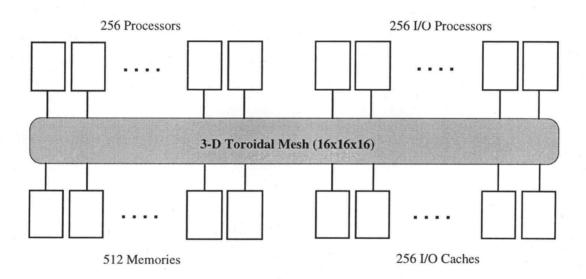

The interconnection network of Tera system is composed of pipelined packet switching nodes in a three-dimensional mesh with a wrap-around. On every clock cycle, each link can simultaneously transmit a packet containing source/destination addresses, an operation, and 64-bit data in both directions. For example, a 256 processor system consists of 4096 switching nodes arranged in  $16\times16\times16$  toroidal mesh, among which 1280 nodes are attached to 256 processors, 512 data memory units, 256 I/O cache units, and 256 I/O processors as shown in Figure 2.5. In general, the number of network nodes grows as a function of  $p^{\frac{3}{2}}$ , where p is the number of processors in the system.

In Tera, each processor can simultaneously execute multiple instruction streams from one to as many as 128 active program counters. On every clock cycle, the processor logic selects an instruction stream that is ready to execute, and a new instruction from a different stream may be issued in each cycle without interfering with the previous instruction. Each instruction stream maintains the following three states: one 64-bit Stream Status Word (SSW), 32 64-bit General Registers (R0-R31), and eight 64-bit Target Registers (T0-T7). Each processor also has a large number of registers (128 SSWs, 4096 General Registers, and 1024 Target Registers) in order to support context

switching on every cycle. Program addresses are 32 bits long, and the program counter is located in the lower half of the its SSW. The upper half is used to specify the various modes (e.g., floating-point rounding), trap mask, and four recently generated condition status. Target Registers are used for branch targets, and the computation of a branch address and the prediction of a branch are separated, allowing the prefetching of target instructions. A Tera instruction typically consists of three operations: a memory reference operation, an arithmetic operation, and a control operation. The control operation can also be of another arithmetic operation, i.e., if the third operation specifies a floating-point operation, it will perform two floating-point operations per cycle.

**Figure 2.5**: The organization of Tera MTA.

Each processor needs to execute on the average about 70 instructions to achieve peak performance by hiding remote latencies (i.e., the average latency for remote access is about 70 cycles). Therefore, if each instruction stream can execute some of its instructions in parallel, less than 70 streams are required to achieve the peak performance. To reduce the required numbers of streams, Tera introduced a new technique called *ex*-

plicit-dependence lookahead to utilize instruction-level parallelism. The idea is that each instruction contains a three-bit lookahead field that explicitly specifies how many instructions from this stream will be issued before encountering an instruction that depends on the current instruction. Since seven is the maximum possible lookahead value with three bits, at most eight instructions can be executed concurrently from each stream. Therefore, only nine streams are needed to hide 72 clock cycles of latency in the best case, compared to 70 different streams required for the worst case.

A full-size Tera system contains 512 128-Mbyte data memory units. Memory is 64-bit wide and byte-addressable. Associated with each word are four additional *access state bits* consisting of two data trap bits, a forward bit, and a full/empty bit. The trap bit allows application-specific use of data breakpoints, demand-driven evaluation, runtime exception handling, implementation of active memory objects, stack limit checking, etc. The forward bit implements invisible indirect addressing, where the value found in the location is to be interpreted as a pointer to the target of the memory reference rather than the target itself. The full/empty bit is used for lightweight synchronization.

Load and store operations use the full/empty bit to define three different synchronization modes along with the access control bits defined in the memory word. The values for access control for each operation is shown in Table 2.1. For example, if the value of the access control field is 2, the store operation waits for the memory location to be written before writing to the location, and sets the full/empty bit to full. When a memory access fails, it is placed in a retry queue and memory unit retries the operation several times before the stream that issued the memory operation results in a trap. Retry requests are interleaved with new memory requests to avoid the saturation of the communication links.

**Table 2.1**: The access control values.

| Value | LOAD                                               | STORE                                               |

|-------|----------------------------------------------------|-----------------------------------------------------|

| 0     | read regardless of the state of the full/empty bit | write regardless and set the full/empty bit to full |

| 1     | not used                                           | not used                                            |

| 2     | wait for full state and read                       | wait for full state and write                       |

| 3     | read only when full and set the bit empty          | write only when empty and set the bit full          |

#### 2.3.3 StarT-NG

StarT-NG (Next Generation) is a joint project between MIT and Motorola, which attempts to develop a general-purpose parallel system using commodity components [20], such as PowerPC 620—a 64-bit 4-way superscalar processor with a dedicated 128-bit wide L2 cache interface/128-bit wide L3 path to memory. StarT-NG is a symmetric multiprocessors (SMP) system that examines how the multithreaded codes can run on a stock processor and emphasizes the importance of cache-coherent global shared-memory supported by efficient message-passing. Influenced by the predecessor StarT [66], multithreading in StarT-NG relies heavily on software support. The instruction fork creates a thread by pushing a continuation specified in registers onto a continuation stack. The compiler is required to generate switch (jump) instructions in the instruction stream for thread switching. Also, the compiler needs to generate the necessary save/restore instructions to swap the relevant register values from the continuation stack, resulting in a large context switching cost.

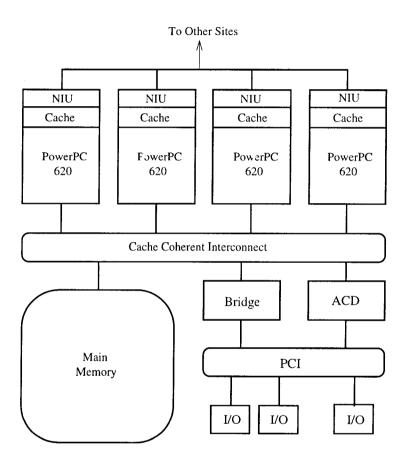

StarT-NG has 4-processor card slots, where one to four slots are filled with Network-Endpoint-Subsystem (NES) cards. Each NES contains a single PowerPC 620

processor with 4 MBytes of L2 cache and a Network Interface Unit (NIU) as depicted in Figure 2.6. Each site has an Address Capture Device (ACD) on the NES board, which manages bus transactions. When an access to global shared-memory is necessary, a processor is used as a Service Processor (SP) for servicing the bus transactions. Otherwise, a processor is used as an Application Processor (AP) for running applications.

Figure 2.6: A site structure of \*T-NG.

StarT-NG is built on a *fat-tree* network using MIT's Arctic routers connected to NIU [13]. The NIU's packet buffers are memory-mapped into an application's address space enabling users to send and receive messages without kernel intervention. The arrival of a message is signaled either by polling or interrupt. Generally, PowerPC 620

will poll the NIU by reading a specified location of the packet buffer with minimum overhead. On the other hand, when the frequency of the message arrival is estimated to be low, an interrupt mechanism can be used either for a kernel message or a user message in order to minimize the overhead of polling.

Cache coherent distributed shared-memory in a prototype StarT-NG is implemented in software to experiment with the directory-based protocol by programming the Shared Memory Unit (SMU) consisting of ACD and SP. When a cache miss occurs, the local SMU determines whether the operation is local or global by examining the appropriate bits of the address—a higher order bit of the physical address distinguishes the global and local address space. If it is local, the directory information is updated and the cache line is read from the local memory. If it is global requiring remote access, cache-coherence action message is sent out to either invalidate remote caches or flush a dirty cache-line.

#### 2.3.4 EM-X

The EM-X parallel computer, which is a successor to EM-4 architecture [78], is being built at Electrotechnical Laboratory in Japan [77]. Based on dataflow model, EM-X integrates the communication pipeline into the execution pipeline by using small and simple packets. Sending and receiving of packets do not interfere with the thread execution. Threads are invoked by the arrival of the packets from the network or by matching two packets. When a thread suspends, a packet on the input queue initiates the next thread. EM-X also supports direct matching for synchronization of threads, and the matching is performed prior to the buffering of the matching packets. Therefore, one clock cycle is needed for pre-matching of two packets, but the overhead is hidden by simultaneously executing other threads.

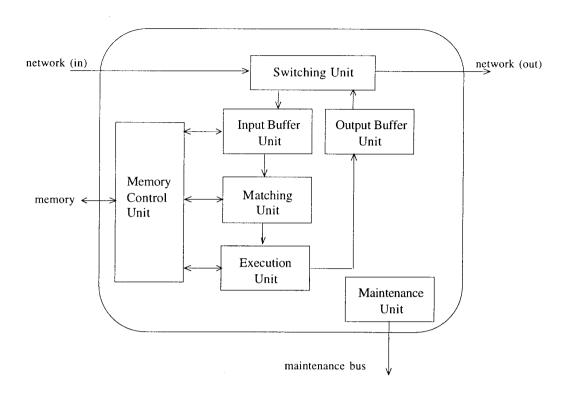

Figure 2.7: The structure of EMC-Y.

The EM-X consists of EMC-Y nodes connected in a circular Omega Network with virtual cut-through routing scheme. The EMC-Y processor is capable of 20 MIPS and 40 MFLOPS (e.g., the instruction fma, FP multiply and add, performs two single-precision floating-operations simultaneously) with clock rate of 20 MHz, and Figure 2.7 shows its internal the structure. The Switching Unit is a 3-by-3 crossbar connecting input and output of network and the processor. Packets arriving at the processor are received in the Input Buffer Unit (IBU). The IBU has an on-chip packet buffer which holds up to 8 packets. When the on-chip buffer overflows, packets are stored in the data memory and automatically restored back when the buffer space becomes available.

EM-X implements a flexible packet scheduling by maintaining two separate priority buffers. The packets in the high priority buffer are first transferred to the Matching Unit (MU), and low priority packets are transferred only when the high priority buffer is empty. The MU prepares the invocation of a thread by using the direct matching scheme

[55]. This is done by first extracting the base address of the operand segment from the incoming packet. The operand segment is an activation frame shared among threads in a function and holds the matching memory and local variables. Next, the partner data is loaded from the matching memory specified in the packet address, and the corresponding presence flag is cleared. Then, a template (i.e., a code frame) is fetched from the top of the operand segment, and the first instruction of the enabled thread resident in the template is executed on the execution unit (EXU).

The EXU, a RISC-based thread execution unit with 32 registers, provides four SEND instructions for invoking a thread, remote memory access, returning the result from the thread execution, and implementation of variable size operand segments or a block access of remote memory [77]. EM-X performs a remote memory access by invoking packet handlers at the destination processor, and the packets are entirely serviced by hardware which does not disrupt the thread execution in the execution pipeline. The round trip distances of the Omega Network in EM-X are 0, 5, 10, and 15 hops for request/reply sequences with the average of 10.13 hops requiring less than  $1 \mu sec$  on a unloaded network. On a loaded network, the latency is  $2.5 \mu sec$  on the average with random communication of 100 Mpackets/sec.

#### 2.3.5 Alewife

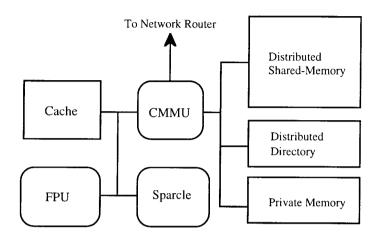

MIT Alewife machine improves scalability and programmability of modern parallel systems by providing software-extended coherent cache, global memory space, integrated message-passing, and support for fine-grain computation. Underneath the Alewife's abstraction of globally shared memory, each PE has a physically distributed memory managed by a Communication and Memory Management Unit (CMMU). This CMMU maintains the locality by caching both private and shared data on each node, and a scalable software-extended scheme, called LimitLESS, manages the cache coherence

[5]. The LimitLESS scheme implements a full-map directory protocol that supports up to five read requests per memory line directly in hardware and more by trapping into software.

Each Alewife node, shown in Figure 2.8, consists of a Sparcle processor, 64 Kbytes of direct-mapped cache, 4 Mbytes of data and 2 Mbytes of directory, 2 Mbytes of private unshared memory, a floating-point unit, and mesh routing chip. The nodes communicate via two-dimensional mesh network using wormhole routing technique. Sparcle is a modified SPARC processor that facilitates block multithreading, fine-grain synchronization, and rapid messaging. In Sparcle, the register windows of SPARC are modified to represent four independent contexts: one for trap handlers and other three for user threads. A context-switch is initiated when the CMMU detects a remote memory access and causes a synchronous memory fault to Sparcle. The context switching is implemented by a short trap handler that saves the old program counter and status register and switches to a new thread by restoring a new program counter and status registers. Currently, the context switching takes 14 clock cycles, but it is expected to be reduced to four clock cycles.

Sparcle provides new instructions that manipulate the full/empty bits in memory for data-level synchronization [2]. For example, ldt (read location if full, else trap) and stt (write location if empty, else trap) instructions can be used to synchronize on an element-by-element basis. Fast message handling is also implemented via special instructions and memory-mapped interface to the interconnection network. To send messages, Sparcle first writes a message to the interconnection network queue using stio instruction, and then ipillaunch instruction is used to launch the message into the network. A message usually contains the message opcode, the destination node address, and data values (e.g., content of a register or address/length pair which invokes DMA on blocks from memory). The arrival of a message invokes a trap handler that loads the incoming

message into registers using Idio instruction, or initiates a DMA sequence to store the message into memory.

Figure 2.8: The organization of an Alewife node.

#### 2.3.6 The M-Machine

The M-machine is an experimental multicomputer being developed by MIT. The M-Machine achieves better utilization by devoting more chip area to the processor, and it is claimed that a 32-node M-Machine system with 256 MBytes of memory has 128 times the peak performance of uniprocessor with the same memory capacity at 1.5 time the area, yielding 85 times improvement in peak performance/area [30]. The M-Machine consists of a collection of computing nodes interconnected by a bidirectional 3-D mesh network. Each node consists of a multi-ALU (MAP) and 8 MBytes of synchronous DRAM. A MAP contains four execution clusters, four cache banks, a network interface, and a router. Each of the four MAP cluster is a 64-bit, three-way issue, pipelined processor consisting of a memory unit, an integer unit, and a floating-point unit as

shown in Figure 2.9. The memory unit is used for interfacing memory system and cluster switch. The cache is organized as four word-interleaved 32-KByte banks to permit four consecutive accesses. Each word has a synchronization bit which is manipulated by special load and store operations for atomic read-modify-write operations.

**Figure 2.9**: The MAP architecture and its four clusters. A cluster consists of 3 execution units, 2 register files, an instruction cache, and interface to the memory and cluster switches.

The M-Machine supports a single global virtual address space through a global translation lookaside buffer (GTLB). GTLB is used to translate the virtual address into physical node identifiers in the message. Also, messages are composed in the general registers of a cluster and launched atomically using a user-level SEND instruction. Arriving messages are queued in a register-mapped FIFO, and a system-level message handler performs the requested operations specified in the message.

Each MAP instruction contains one to three operations and may complete out-of-order. The M-Machine exploits instruction-level parallelism by running up to 12 parallel instruction sequences (called H-Thread) concurrently. Also, the MAP interleaves the 12-wide instruction streams (called V-Thread) from different threads of computation to exploit thread-level parallelism and to mask various latencies that occurs in the pipeline (i.e., during memory accesses and during communication). Six V-Threads are resident in a cluster, and each V-Thread consists of four H-Threads. A V-Thread consists of a sequence of 3-wide instructions containing integer, memory, and floating-point operation. Within an H-Thread, instructions are issued in order, but may complete out of order. Synchronization and communication among H-Threads in the same V-Thread is done using a scoreboard bit associated with each register. However, H-Threads in different V-Threads may only communicate and synchronize through massages and memory. The M-Machine provides a fast user-level message passing substrate through hardware support. Also, register-to-register communication is provided to reduce the memory accesses.

# 2.3.7 Simultaneous Multithreading

Simultaneous multithreading (SMT) is a technique that allows multiple independent threads from different programs to issue multiple instructions to a superscalar processor's functional units. Therefore, SMT combines the multiple instruction-issue features of modern superscalar processors with the latency-hiding ability of multithreaded architectures, alleviating the problems of long latencies and limited per-thread parallelism. This means that the SMT model can be realized without extensive changes to a conventional superscalar processor architecture.

Figure 2.10 shows the processor organization of an 8-thread simultaneous multithreading machine proposed by Tullsen D. M. *et al.* at University of Washington [57].

The processor execution stage is composed of three Floating-Point Units and six Integer Units. Therefore, the peak instruction bandwidth is nine. However, throughput of the machine is bounded to eight instructions per cycle due to the bandwidth of Fetch and Decode Units. Each Integer and Floating-Point Instruction Queue (IQ) holds 32 entries, and the caches are multi-ported and interleaved. Also, there are 256 physical registers (i.e., assumed 32-register instruction set architecture per each of 8 threads) and 100 additional registers for renaming.

Figure 2.10: An overview of SMT hardware architecture.

When running on a single thread, the throughput of the basic SMT system is 2% less than a superscalar with similar hardware resources due to the need to accommodate longer pipeline for a large register file; on the other hand, its estimated peak throughput is 84% higher than that of a superscalar processor when running on multiple threads. However, it is shown that the actual throughput peaks at IPC of 4 even with eight threads. This saturation is caused by the three factors: (1) small IQ size. (2) limited

fetch throughput (only 4.2 useful instruction fetch per cycle). (3) lack of instruction-level parallelism.

The fetch throughput can be improved by using techniques such as partitioning of fetch unit among threads, selective fetching, or eliminating conditions that block the fetch. It has been shown that the best performance is obtained when the Fetch Unit is partitioned in such a way that eight instructions are fetched from two threads, and the priority is given to the threads with the fewest instructions in the decode stage. Also, fetch misses can be reduced by examining the I-cache tag lookups a cycle early and selecting only threads that do not cause misses. However, this scheme requires extra ports in the I-cache tags and increases misfetch penalties due to one more pipeline stage needed for early lookup. The resulting performance shows that a 2.5 throughput gain over a conventional superscalar architecture when running at 8 threads, yielding an IPC of 5.4. The conclusions drawn from the experiments are as follows:

- Techniques such as dynamic scheduling and speculative execution in a superscalar processor are not sufficient to take full advantage of a wide-issue processor without simultaneous multithreading.

- Instruction scheduling in SMT is no more complex than that of a dynamically scheduled superscalar processor.

- Register file data paths in SMT are no more complex than those in a superscalar, and the performance implication on the register file and its longer pipeline is minimal.

- The required instruction fetch throughput is attainable without increasing the fetch bandwidth by partitioning Fetch Unit and employing selective fetching.

# 2.4 New Generation of Multithreading

The current multithreaded systems can execute several threads concurrently by providing multiple hardware contexts and hardware scheduler mechanisms to support fast context switching and thread management within the processor. The concurrent execution of multiple threads requires the programs to be expressed as multiple interacting threads. In order to obtain such threads, traditionally two approaches have been taken: (1) The programmers write programs using thread packages, where threads are explicitly expressed in APIs provided by the thread packages. (2) Multiple programs are used, where each program represents a thread. However, some of the programs do not lend themselves to parallel programming, making it difficult to express the program using threads.

On the other hand, new emerging multithreaded systems use various software and hardware speculation techniques to obtain multiple threads from a sequential program, eliminating the need to program using threads. These next generation multithreaded systems use compiler techniques and hardware mechanisms to identify threads in a speculative fashion and provide the support for resolving inter-thread register dependencies and memory disambiguation. This section introduces such multithreaded architectures, namely *Multiscalar*, *I-ACOMA* and *DeSM*.

#### 2.4.1 Multiscalar

Traditional processors execute sequential programs following a single flow of control and build a large window of instructions in order to achieve high performance. On the other hand, the Multiscalar executes a single sequential program following multiple flows of control by relying on hardware support for maintaining sequential seman-

tics between those flows of control [41]. This allows the programmer to use a sequential programming style while efficiently executing the program in parallel. The Multiscalar introduces new instructions to support two levels of control speculation: *inter-task* speculation and *intra-task* speculation. First, a program is converted into a task flow graph (TFG). A TFG is directed graph with nodes representing tasks and arcs representing control dependencies, in which each task is a conventional control flow graph (CFG). The Multisclar relies on the compiler for generation of tasks which encapsulate groups of instructions containing arbitrary control flows. The compiler identifies the tasks and inserts task start and task end instructions at the task boundaries. The task start instruction loads the special state register with a task header containing a bit mask that indicates which registers may be updated within the task along with the information about the tasks that may follow. The task end instruction is used to indicate an exit point of the task by setting special bits and transferring the control. These special bits are then used in the speculation of the next task.

The global sequencer in Multiscalar, shown in Figure 2.11, traverses the program's TFG and distributes the tasks to the processing units (PUs) in speculation of the program paths (inter-task speculation). The responsibility of global sequencer is to predict the starting address of the next tasks to be executed using information from the task header of the most recently predicted tasks and the dynamic prediction hardware. At any given time, only one unit can execute the non-speculative task and other units execute speculative tasks. For each task, the processing unit uses traditional control speculation to extract instruction level parallelism (intra-task speculation). The PU ring in Multiscalar operates as a circular queue with a head pointing to the non-speculative task and a tail pointing to the most recently started speculative task. When the task pointed by the head finishes, it informs the global sequencer of its actual non-speculative target address. If the predicted target address followed by the speculative tasks turns out to be incorrect, all tasks following the head task are squashed and execution is redirected to the correct

task. The task misprediction penalty can be large in terms of wasted work. However, this task speculation mechanism, supported by both hardware and software, enables the Multiscalar to effectively build a very large instruction window and increases the performance.

Figure 2.11: The Multiscalar hardware.

#### **2.4.2 I-ACOMA**

Researchers at University of Illinois have proposed a software/hardware solution that allows speculative execution of threads using a sequential binary on a clustered SMT architecture, namely Illinois Aggressive Coma (I-ACOMA) [48]. They utilize the

loop iterations to identify threads and multiple threads from the successive iterations of the loop are speculatively spawned onto each SMT-based processor. In order to support this thread speculation, a binary annotator is developed to identify basic blocks in loops and generate threads. The annotation involves the following processes: (1) Identification/annotation of entry and termination points of the loops. (2) Checking register-level dependencies and identifying *looplive* registers. The looplive registers define the interthread dependencies that exist at the entry or exit points of the loop. Also, the registers that are modified within the loop are identified. (3) Finally, the registers holding loop-carried variables, called *induction variables*, are identified and the instructions associated with the induction variables are moved close to the entry point of the loop in order to minimize the waiting cycles before the spawning of next iteration.

Speculative execution of threads requires special hardware support for inter-thread register synchronization and memory disambiguation. The inter-thread register synchronization is done by Synchronizing Scoreboard (SS). The SS associates three bits, namely Busy (B), Valid (V), and Sync (S), with each register to handle inter-thread dependencies. The B-bit is set when the register value is being created. The S-bit indicates whether or not the register value is available to the succeeding thread. When a thread is initiated, the S-bits for all the looplive registers are set and later cleared when the release instruction for that register is executed. At this point, the register becomes safe to use by the succeeding thread. The V-bit indicates whether the thread has valid copy of the register. When a given thread need to access a register, the B-bit is checked first. If the B-bit is set, indicating the unavailability of the register, the thread execution is stalled. Otherwise, the thread gets the register value from the predecessor thread if the V-bit set.

To preserve the sequential semantics of memory operation in speculative execution, the Memory Disambiguation Table (MDT) is used to maintain the address of the load/store operations along with *Load* (L) bit and *Store* (S) bit. In addition, each thread