#### AN ABSTRACT OF THE THESIS OF

| Haowei Zhang for the degree of Master of Science in                           |

|-------------------------------------------------------------------------------|

| Electrical and Computer Engineering presented on January 14, 1997.            |

| Title:                                                                        |

| A High-Performance, Low-Power and Memory-Efficient VLD for MPEG Applications. |

| Abstract approved:                                                            |

| Mario E. Magana                                                               |

An extremely important area that has enabled or will enable many of the digital video services and applications such as VideoCD, DVD, DVC, HDTV, video conferencing, and DSS is digital video compression. The great success of digital video compression is mainly because of two factors. The state of the art in very large scale integrated circuit (VLSI) and a considerable body of knowledge accumulated over the last several decades in applying video compression algorithms such as discrete cosine transform (DCT), motion estimation (ME), motion compensation (MC) and entropy coding techniques. The MPEG (Moving Pictures Expert Group) standard reflects the second factor. In this thesis, MPEG standards are discussed thoroughly and interpreted, and a VLSI chip implementation (CMOS  $0.35\mu$  technology and 3 layer metal) of a variable length decoder (VLD) for MPEG applications is developed. The VLD developed here achieves high performance by using a parallel and pipeline architecture. Furthermore, MPEG bitstream patterns are carefully analyzed in order to drastically improve VLD memory efficiency. Finally, a special clock scheme is applied to reduce the chip's power consumption.

#### digit.

## A High-Performance, Low-Power and Memory-Efficient VLD for MPEG Applications

by

Haowei Zhang

#### A THESIS

submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Master of Science

Completed January 14, 1997 Commencement June 1998 Master of Science thesis of Haowei Zhang presented on January 14, 1997

APPROVED:

Redacted for Privacy

Major Professor, representing Electrical and Computer Engineering

## Redacted for Privacy

Head of Department of Electrical and Computer Engineering

## Redacted for Privacy

Dean of Graduate School

I understand that my thesis will become part of the permanent collection of Oregon State University libraries. My signature below authorizes release of my thesis to any reader upon request.

# Redacted for Privacy

Haowei Zhang, Author

#### TABLE OF CONTENTS

|    |      |                                     | Page |

|----|------|-------------------------------------|------|

|    |      |                                     |      |

| 1  | INT  | RODUCTION                           | . 1  |

|    | 1.1  | Motivation                          | . 1  |

|    | 1.2  | Outline of the thesis               | 3    |

| 2  | STII | LL IMAGE COMPRESSION                | . 5  |

|    | 2.1  | Introduction                        | 5    |

|    |      | 2.1.1 Color Spaces                  | . 5  |

|    |      | 2.1.2 Human Visual System           | . 7  |

|    |      | 2.1.3 DCT and Fast DCT              | . 8  |

|    | 2.2  | Image Compression Systems           | . 11 |

|    |      | 2.2.1 Introduction to JPEG Standard | 11   |

|    |      | 2.2.2 Quantization                  | 12   |

|    |      | 2.2.3 Entropy Coding                | 15   |

|    | 2.3  | Operation Modes                     | . 17 |

| 3  | LOS  | SY VIDEO COMPRESSION                | . 22 |

|    | 3.1  | Introduction                        | . 22 |

|    | 3.2  | Motion Estimation                   | . 22 |

|    | 3.3  | Motion Compensation                 | . 30 |

| Į. | MPE  | G STANDARDS                         | . 36 |

|    | 4.1  | Background                          | . 36 |

|    | 4.2  | Digital Video Formats               | . 39 |

|    | 4.3  | Temporal processing                 | . 41 |

## TABLE OF CONTENTS (Continued)

|     |       | <u> 1</u>                                 | Page |

|-----|-------|-------------------------------------------|------|

|     | 4.4   | Encoder and Decoder                       | . 43 |

|     | 4.5   | Bit Stream Structure                      | 45   |

|     | 4.6   | Macroblock Coding                         | . 48 |

|     | 4.7   | Scalable Bit Streams                      | . 50 |

| 5   | VLSI  | ARCHITECTURE FOR VIDEO COMPRESSION        | . 53 |

|     | 5.1   | Overview                                  | . 53 |

|     | 5.2   | Architectures for Motion Estimation       | 55   |

|     | 5.3   | Mapping Algorithms to VLSI                | 62   |

|     | 5.4   | Low Power Design                          | . 68 |

| 6   | VLSI  | IMPLEMENTATION OF VARIABLE LENGTH DECODER | . 73 |

|     | 6.1   | Overview                                  | . 73 |

|     | 6.2   | System Model                              | . 73 |

|     | 6.3   | VLSI Architectures                        | . 76 |

|     | 6.4   | VLSI Implementation                       | . 80 |

| 7   | CON   | CLUSIONS                                  | . 88 |

| ΒI  | BLIO  | GRAPHY                                    | . 90 |

| 4.F | PENI  | DICES                                     | 94   |

|     | A DDI | ENDIY A VID Lavout                        | 95   |

#### LIST OF FIGURES

| rig | <u>Page</u>                                 |    |  |

|-----|---------------------------------------------|----|--|

|     |                                             |    |  |

| 2.1 | JPEG Encoder Decoder                        | 19 |  |

| 2.2 | Entropy Coding                              | 20 |  |

| 2.3 | Zig-zag scan of the AC Coefficients         | 20 |  |

| 2.4 | Three-level Hierarchical Coder              | 21 |  |

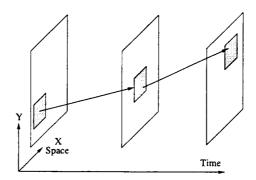

| 3.1 | Temporal Correlation Between Pictures       | 23 |  |

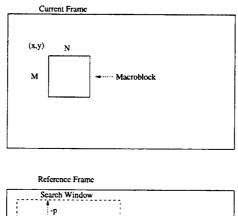

| 3.2 | Block Matching Motion Estimation            | 25 |  |

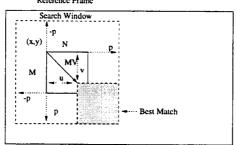

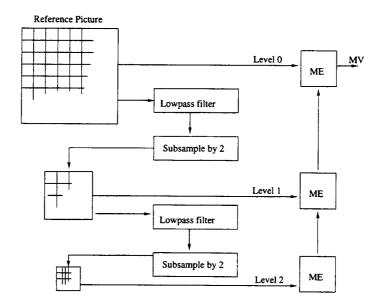

| 3.3 | Hierarchical Motion Estimation              | 29 |  |

| 3.4 | Half-Pel accurate MV estimation             | 31 |  |

| 3.5 | Field Image                                 | 32 |  |

| 3.6 | Dual Prime for ME                           | 35 |  |

| 4.1 | I B P frame in a Video Sequence             | 41 |  |

| 4.2 | Bidirectional Motion Compensation           | 42 |  |

| 4.3 | MPEG Encoder ( P Pictures )                 | 44 |  |

| 4.4 | MPEG Decoder                                | 45 |  |

| 4.5 | Bitstream Layer of MPEG-1                   | 46 |  |

| 4.6 | I Frame Macroblock Coding                   | 49 |  |

| 4.7 | B Frame Macroblock Coding                   | 50 |  |

| 4.8 | MPEG-2 Profiles                             | 51 |  |

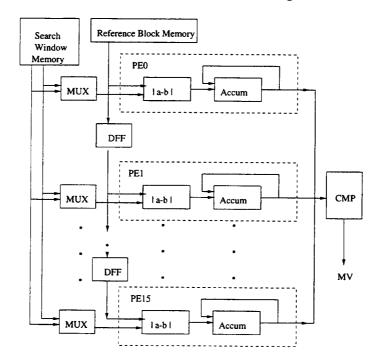

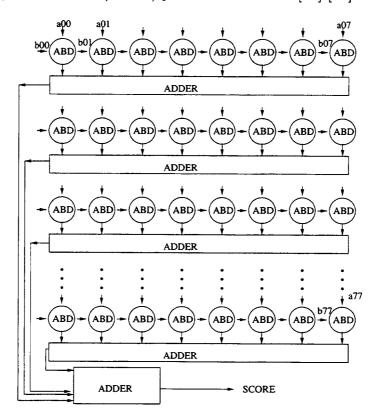

| 5.1 | Data-flow Design                            | 57 |  |

| 5.2 | Architecture for ME using Linear Array      | 57 |  |

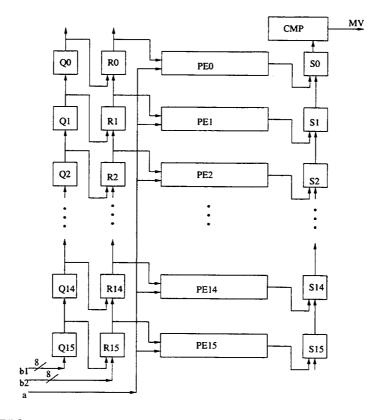

| 5.3 | Architecture 2 for ME using Linear Array    | 58 |  |

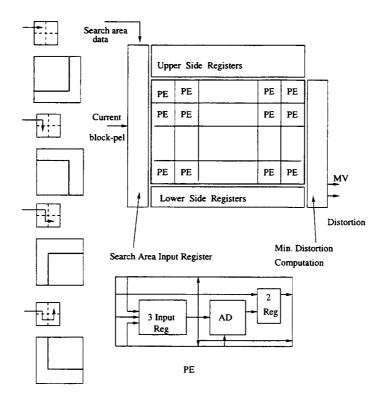

| 5.4 | Architecture for ME using 2-D Linear Array  | 60 |  |

| 5.5 | New Architecture for ME                     | 62 |  |

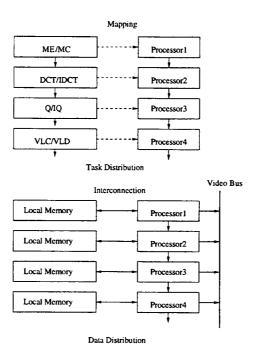

| 5.6 | Task Distribution and Function Distribution | 64 |  |

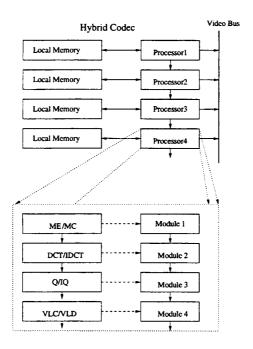

| 5.7 | Hybrid Architecture                         | 65 |  |

## LIST OF FIGURES (Continued)

| Figure |                                            | Page |

|--------|--------------------------------------------|------|

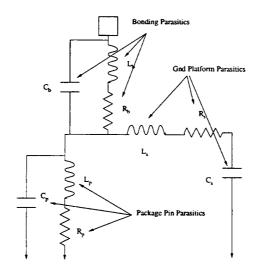

| 5.8    | Chip Package Interface                     | . 67 |

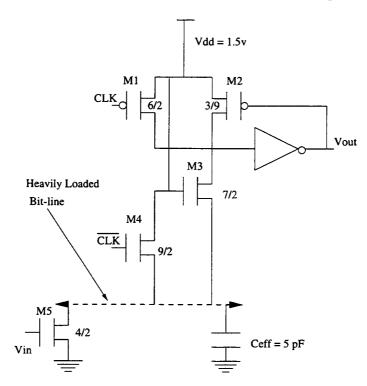

| 5.9    | Voltage Swing Reduction Circuit            | . 72 |

| 6.1    | Simple Huffman Coding example              | . 74 |

| 6.2    | Block Layer Pseudocode                     | . 75 |

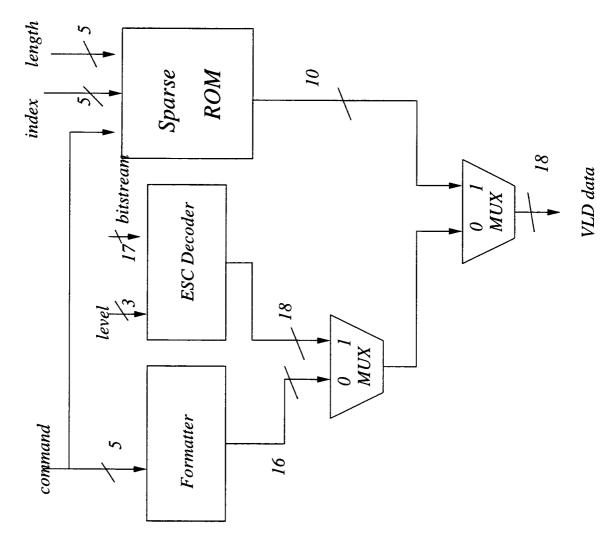

| 6.3    | System Model Pseudocode                    | . 82 |

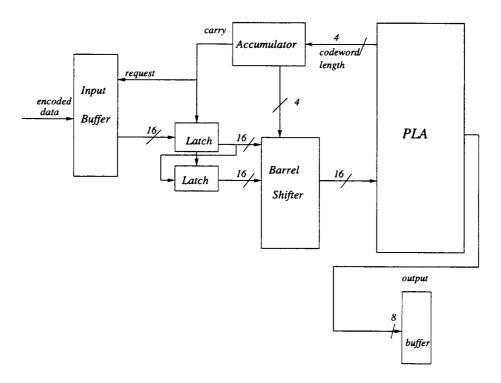

| 6.4    | PLA-based constant-output rate VLD         | . 83 |

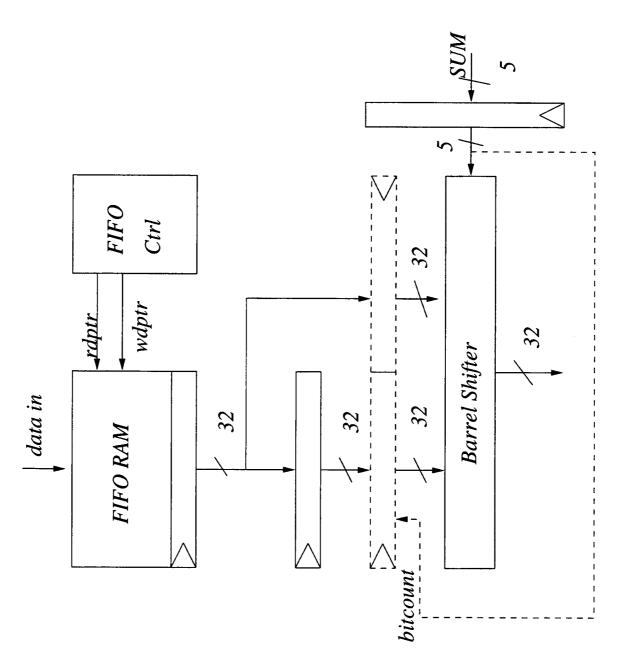

| 6.5    | Barrel Shifter and Control Logic           | 84   |

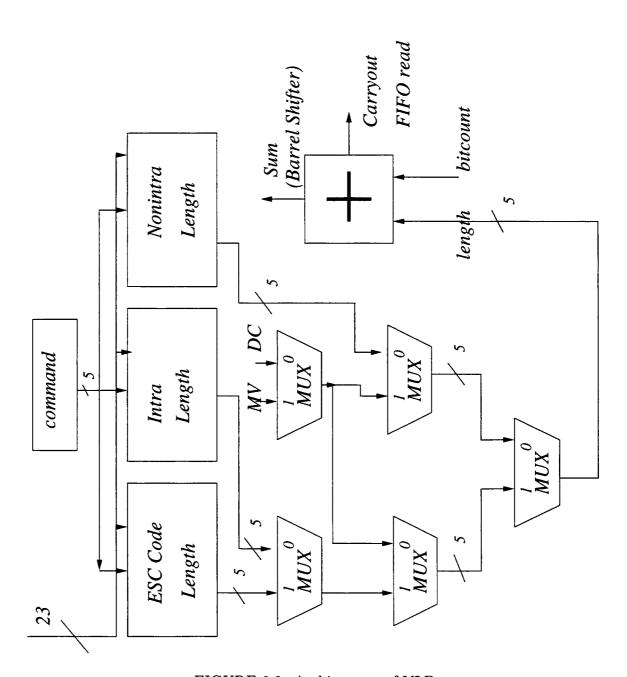

| 6.6    | Architecture of VLD                        | 85   |

| 6.7    | Architecture of VLD (Contd)                | 86   |

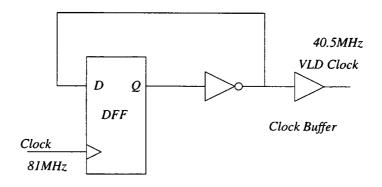

| 6.8    | VLD Pipeline Clock                         | 86   |

| 6.9    | Verilog Code for Start Code Length Decoder | 87   |

### LIST OF TABLES

| <u> Fable</u> |                                       | Page |

|---------------|---------------------------------------|------|

|               |                                       |      |

| 4.1           | MPEG-2 Profiles Levels                | 52   |

| 5.1           | Basic Data Flow for ME                | 59   |

| 6.1           | Variable Length Codes for Motion-code | 79   |

# A HIGH-PERFORMANCE, LOW-POWER AND MEMORY-EFFICIENT VLD FOR MPEG APPLICATIONS

#### 1. INTRODUCTION

#### 1.1. Motivation

Now that we are in the midst of a major revolution in human computer interface, the multimedia interface is becoming the combination of computer, television and telephone. The coming of the information super-highway is indeed a big merge of communications, computation and consumer electronics. The core technology of this transition is digital video which will be the bulk of the traffic in future ATM networks. Also it is the key to many applications such as interactive TV, video-on-demand, video conferencing, HDTV, video phone, set-top box, videoCD and DVD, just to name a few.

The current two important topics in digital video communications are representation and transmission. The efficient digital representations of video signals (also called source coding) has been the subject of considerable research over the past twenty years.

Compression is the most critical aspect of digital video, because uncompressed video is far too huge to transmit, store, and manipulate. For example, a 640\*480 color video will require transmit rate at 27.6MB/s, and a 2-hour full motion video will need 99,360 MB storage space which is certainly not practical.

This field is sufficiently mature that several standards are now available. These include the ITU-T H.261 standard for teleconferencing and the ISO/IEC MPEG family of standards. Right now these standards are all based on the same general architecture, namely motion-compensated temporal coding coupled with block discrete cosine transform spatial coding. The standards and their implementations will be discussed throughly in the following chapters.

Although a great deal of work remains to be done to approach fundamental limits of coding performance, these standard coding algorithms will form the basis for many services in the coming years. In particular, the telecommunication and semiconductor industries are working on these standards. However, standardization is a time-consuming process and development goes on.

The intraframe coding of video signals is very similar to the still image compression standard developed by the Joint Photographic Experts Group and the coding standard is accordingly called JPEG. JPEG is based on a division of the image into blocks of 8x8 pixels. Each block is transformed with discrete cosine transform (DCT). After the transform, the DCT coefficients are quantized and each frequency is weighted according to its importance to the human visual system (HVS). Finally, the coefficients are zig-zag scanned, run length coded and the data stream is send to a entropy coder such as Huffman encoder.

The above schemes are the core part of video coding standards such as H.261 and MPEG-1 and MPEG-2. For low bit rate applications like video conference and videotelephony the Recommendation H.261 of the International Consultative Committee for Telephone and Telegraph (CCITT) was internationally adopted in 1991. The Moving Pictures Expert Group of the International Organization for Standardization (ISO/IEC) has been developing a similar but extended and improved scheme. MPEG-1 is intended for the storage of video (For example, CD-ROM and

VideoCD) and associated audio at low to medium bit rates and was standardized in 1992. MPEG-2 is intended for the transmission of video and associated audio at high bit rates, such that it can also be used for digital high definition television (HDTV). It can also be used for the broadcasting of standard digital television.

The Subband related coding techniques are promising especially for HDTV because they have an inherent multiresolution structure, so the normal digital TV can extract the low-resolution video from the video stream without affecting the high resolution quality. Nevertheless, compared to DCT related techniques, subband coding has a short history for standardization. However, it may play an important role in the forcoming MPEG-4 video coding standard which is for very low bit rate special-purpose applications such as wireless video transmission.

#### 1.2. Outline of the thesis

This thesis discusses digital video compression algorithms (MPEG) and their VLSI implementations. Moreover, a VLSI implementation (CMOS  $0.35\mu$  technology and 3 layer metal) of a variable length decoder (VLD) for MPEG applications is developed. The VLD achieves high performance by using parallel and pipeline architecture. MPEG bitstream patterns have been carefully analysed to drastically improve VLD memory efficiency. In addition, a special clock scheme is applied to reduce the power consumption.

Chapter 2 contains overview of different techniques for still image compression. JPEG standard has been extensively studied. Several important fast DCT methods are presented. Huffman coding as one of the VLC methods has been explained. Rate Distortion function is used to evaluate the performance.

Chapter 3 describes the fundamentals of lossy video compression, emphasis on motion estimation (ME) and motion compensation (MC).

Chapter 4 introduces the very important digital video coding standards: MPEG-1 and MPEG-2. Both field and frame based coding are introduced.

Chapter 5 describes the VLSI architectures of video compression. First the different architectures are compared, then several ways of designing ME are presented. The practical issues involved are also studied, including low power design techniques and interconnection analysis.

In Chapter 6, a high-performance, low-power and memory-efficient VLD has been designed for MPEG applications.

.

#### 2. STILL IMAGE COMPRESSION

#### 2.1. Introduction

At eight bits/sample, the image has sufficient precision to be considered a gray scale or continuous-tone image. For binary images (e.g. fax image), there is only one bit per sample and are usually images of text or line drawings. They only have two tones, black and white. A process called *digital halftoning* creates the effect of continuous tones in a binary image by alternating between closely spaced black and white samples.

JPEG works best on "continuous tone" images; images with many sudden jumps in color values will not compress well. There are a lot of parameters to the JPEG compression process. By adjusting the parameters, one can trade off compressed image size against reconstructed image quality over a wide range.

JPEG has defined a "baseline" capability which must be present in all the JPEG modes of operation which use the DCT. It also defines optional extensions for progressive and hierarchical coding. There is also a separate lossless compression mode which typically gives about 2:1 compression where the lossy one gives about 10 to 20:1 compression or even higher compression depending on different applications.

#### 2.1.1. Color Spaces

Red, green and blue (RGB) is one example of a color representation requiring three independent values to describe the colors. Each of the values can be varied independently, and we can therefore create a three-dimensional space with R, G, and B as independent coordinates. Colors are represented as points in this space.

RGB may not always be the most convenient way of color representation. One particularly important color space for digital image compression is called Luminance-chrominance representation where one component is the luminance (Provides a grayscale version of the image) and the other two components provide the extra information that converts the grayscale image to color image.

The reason for doing this is that one can afford to lose a lot more information in the chrominance components than you can in the luminance component, because the human eye is not as sensitive to high-frequency color information as it is to high-frequency luminance. So the first step in JPEG is the color space transformation.

If the values of the three colors R, G and B are expressed by a relative scale from 0 to 1, then the luminance(Y) of any color can be calculated from the following weighted sum:

$$Y = 0.3R + 0.6G + 0.1B$$

.

The scaling is chosen such that the luminance is also expressed by a relative scale from 0 to 1 and weights reflect the contributions of the individual primaries to the total luminance.

The term *chorminance* is defined as the difference between a color and a reference white at the same luminance. The chrominance information can therefore be expressed by a set of color differences, V and U, where V and U are defined by:

$$V = R - Y; U = B - Y.$$

These color differences are zero whenever R=G=B, as this condition produces gray, which has no chrominance. The V component controls colors ranging from red

V>0 to blue-green V<0, whereas the U component controls ranging from blue U>0 to yellow U<0. Together with the luminance, these chrominance coordinates make up the color coordinate system know as YUV.

Another color coordinate system, YCbCr, was used extensively in the development of the JPEG standard. This system is closely related to YUV where the U and V are scaled and zero-shifted to produce the variables Cb and Cr, respectively:

$$Cb = (U/2) + 0.5Cr = (V/1.6) + 0.5$$

This will ensure that Cb and Cr are always in the range 0 to 1 so they can be multiplied by 255.

A number of other color spaces, including the YIQ can also be related to these spaces by simple linear transformation.

#### 2.1.2. Human Visual System

The frequency response of the human eye is more sensitive to low frequency than to high frequency. For vertical patterns, it is similar to the response for horizontal patterns. On the diagonals, however, the response is significantly reduced. Furthermore, the human eyes are much less sensitive to the high frequency of the color information which is a very important property from the standpoint of data compression [30].

Down-sampling is the typical technique to compress the color image. The luminance component is left at full resolution, while the color components are usually reduced 2:1 horizontally and either 2:1 or 1:1 (no change) vertically. This step immediately reduces the data volume by one-half or one-third, while having almost no impact on perceived quality. (Obviously this would not be true if we tried it in RGB color space).

However, simple down-sampling methods such as discard every other samples may introduces "aliasing artifacts", therefore the method of averaging together groups of pixels in the processing of down-sampling. This is equivalent to lowpass filtering.

#### 2.1.3. DCT and Fast DCT

The discrete cosine transform was first applied to image compression in Ahmed, Natarajan, and Rao's pioneering work, in which they showed that this particular transform was very close to the KLH (Karhunen-Loeve-Hotelling) transform, a transform that produces uncorrelated coefficients [44].

We have seen that the human visual system response is very dependent on spatial frequency. If we could somehow decompose the image into a set of waveforms, each with a particular spatial frequency, we might be able to separate the image structure the eye can see from the structure that is imperceptible.

Group the pixel values for each component into 8x8 blocks. Transform each 8x8 block through a discrete cosine transform (DCT) with following equations

$$F(u,v) = \frac{C(u)}{2} \frac{C(v)}{2} \sum_{x=0}^{7} \sum_{y=0}^{7} f(x,y) \cos(\frac{(2x+1)u\pi}{16}) \cos(\frac{(2y+1)v\pi}{16})$$

and the Inverse DCT (IDCT):

$$f(x,y) = \sum_{u=0}^{7} \sum_{v=0}^{7} \frac{C(u)}{2} \frac{C(v)}{2} F(u,v) \cos(\frac{(2x+1)u\pi}{16}) \cos(\frac{(2y+1)v\pi}{16})$$

where  $C(u), C(v) = \frac{1}{\sqrt{2}}$  for u, v = 0 and C(u), C(v) = 1 otherwise.

We can think the DCT as a harmonic analyzer. This is a relative of the Fourier transform and likewise gives a frequency map, with 8x8 components. Each 8x8 block of source image samples is effectively a 64 point discrete signal which is a function of the two spatial dimensions x and y. The DCT takes such a signal as

its input and decomposes it into 64 unique 2D "spatial frequencies" which comprise the input signals "spectrum". The output is the set of 64 basis-signal amplitudes whose values are uniquely determined by the particular 64 -point input signal.

Thus we now have numbers representing the average value in each block and successively higher-frequency changes within the block. The motivation for doing this is that we can now throw away high-frequency information without affecting low-frequency information. (The DCT transform itself is reversible except for roundoff error.)

The most straightforward way to implement the DCT is to follow the theoretical equations. When we do this, we get an upper limit of 64 multiplications and 56 additions for each 1-D 8-point DCT. Or, 1024 multiplications and 896 additions for 8x8 block.

If the DCT really required this many operations to compute, JPEG would have chosen a different algorithm. In fact, there are many fast DCT techniques take advantage of the symmetries in the DCT equations. And there exists a close connection between DCT and DFT. For example, It has been shown that the N-point DCT can be expressed in terms of the real and imaginary parts of an N-point DFT and rotations of the DFT outputs. It has also been shown that the first N coefficients of a 2N-point DFT with appropriate symmetry of input values can be used to compute an N-point DCT. This will also lead to avery efficient scaled DCT structure. This can be shown as follows:

Let  $W_K = exp(-j2\pi/K)$ , then the K-point DFT is given by:

$$F(u) = \sum_{x=0}^{K-1} s(x) W_K^{ux}$$

We then define the appropriate symmetry of the input value by using the mirror of the input, that is, extend the N-point sequence s(x), x = 0, ..., N - 1 by defining another N points with symmetry about the point (2N-1)/2,

$$s(x) = s(2N - x - 1), x = N, ..., 2N - 1$$

then the 2N-point DFT becomes

$$F(u) = \sum_{x=0}^{N-1} s(x)W_K^{ux} + \sum_{x=N}^{2N-1} s(2N-x-1)W_K^{ux}.$$

If we define the new index k=2N-x-1 (Note that  $W_K^{2N}=1$ ), this becomes

$$F(u) = \sum_{x=0}^{N-1} s(x) W_K^{ux} + \sum_{k=0}^{N-1} s(k) W_K^{-u(k+1)}.$$

Replacing the index k by x and multiplying by  $(1/2)W_K^{u/2}$ , yields

$$(1/2)F(u)W_K^{u/2} = \sum_{x=0}^{N-1} s(x)\cos((2x+1)u\pi/2N),$$

which proves that multiplying a complex scaling factor by the first eight DFT coefficients (of the 16-point DFT), gives the 8-point DCT coefficients.

Take one step further and we can show that the DCT coefficients can be obtained by a simple scaling of the real part of the DFT coefficients, that is,

$$(1/2)Re(F(u))sec(\pi u/2N) = \sum_{x=0}^{N-1} s(x)\cos((2x+1)u\pi/2N)$$

Because of the orthogonal nature of the DCT transform, the IDCT has the identical computational complexity of the DCT.

#### 2.2. Image Compression Systems

#### 2.2.1. Introduction to JPEG Standard

We now study a generic transform based image coding system, normally speaking, a coding system which exploits the intra-frame correlation composed of several major subsystems [29].

Figure 2.1 represents the core computation pipeline employed in all the popular lossy image and video compression algorithms. In the encoder the DCT transforms each 8x8 block into a set of DCT coefficients. There is no compression at this step, in fact, there is expansion because each DCT coefficient needs 12 bits to represents it. The "lossy" comes from the next step, namely, quantization. This process is an irreversible process and thus we will encounter information loss. After quantization, the nonzero DCT coefficients are further compressed using an entropy coder. In most applications, the entropy coder combines a run-length coder with a Huffman coder. This process is lossless. In the following section, JPEG will be given as an example to illustrate the various steps performed during compression and decompression:

For the color RGB image, one approach would be handle each color component separately. However, as we mentioned before, there is significant correlation between the color components. Thus, the approach is to transform the RGB image into another component such YCbCr. There is very little correlation among the components in this representation, furthermore, since most of the spatial information is in the luminance (Y) component, we lose little information if we subsample the Cb and Cr components by a factor of two in both dimensions. Therefore we have reduced the image size by half before it goes into the encoder.

For more efficient processing, images with multiple components can be interleaved. A data unit is defined as the smallest logical unit (LU) of source data that can be processed by JPEG. For lossy JPEG, this is a single 8x8 block of data. A minimum coded unit (MCU) is formed by interleaving the Y, Cb and Cr data units.

The interleaved data come to the encoder in 8x8 blocks, then the pixel values are changed to frequency domain by 2-D DCT. Which can be any one of the fast DCT algorithm. Then the coefficients are quantized and entropy coded.

#### 2.2.2. Quantization

The quantizer is the main source of compression. To do this, an 8x8 quantization matrix is required. It can be designed based on human perception and psycho visual experiments or based on rate-distortion theory and bit-rate control. First we give a quick review of rate-distortion theory. However, before going into the details, a review of information theory is necessary.

We define the information content of a message, x, as  $I_x$  in:

$$I_x = \log \frac{1}{P_x},$$

where the  $P_x$  is the probability of occurrence of the event (message) x. Note that if we use base 2 for the logarithm, the unit of information is called the *bit of information*.

Entropy is defined as the average information per message. To calculate the entropy, we take the various information contents associated with the messages and weight each by the fraction of time we can expect that particular message to occur. This fraction is the probability of the message. Thus, given n messages,  $x_1$  through  $x_n$ , the entropy is defined by

$$H = \sum_{i=1}^{n} P_{xi} \log(\frac{1}{P_{xi}}).$$

The spatial redundancy of an image can be modeled by a two-dimensional covariance function. A typical isotropic (non-separable) one looks like

$$Cov_X(i, j) = \sigma^2 e^{-\alpha \sqrt{i^2 + j^2}},$$

where  $\sigma^2$  is the variance of the image and i and j refer to the distance from the reference pixel about which the covariance function is defined. It can be seen from the above equation that the covariance function decays rapidly beyond i, j > 8. This is also one of the reason that 8x8 block is chosen.

Using quantization, with some loss of information, much higher compression ratios are possible. However, there is a tradeoff between distortion (D) and the bit rate (R)of the compressed bit stream. For a given D, the rate-distortion function R(D) is defined as the minimum possible rate R necessary to achieve average distortion D or less. Note that R(D) is independent of the particular compression method and depends only on the underlying stochastic model for the input images and the distortion measure [30].

For the isotropic covariance function above with  $\sigma^2=1$ , the 2-D power spectral density of an image X has the form

$$S_x(f_x, f_y) = \frac{f_0}{2\pi (f^2 + f_0^2)^{\frac{3}{2}}} = S_0(f),$$

where  $f = \sqrt{f_x^2 + f_y^2}$ . It has been shown by Berger [43] that the optimal encoder-decoder tandem yields distortion  $D(\theta)$  and a minimum rate  $R(\theta)$  given by

$$D(\theta) = \int_{-\infty}^{\infty} \int_{-\infty}^{\infty} min(\theta, S_x(f_x f_y)) df_x df_y$$

$$R(\theta) = \int_{-\infty}^{\infty} \int_{-\infty}^{\infty} max(0, \frac{1}{2} \log_2 \frac{S_x(f_x f_y)}{\theta}) df_x df_y$$

The R(D) function has several practical uses, for example, one can measure D and the corresponding rate R and compare them against the theoretical limit R(D), it can even be used to optimize the design of functional blocks within the encoder and decoder. For instance, the design of quantization tables.

The techniques for the design of quantization tables can be divided into two main classes: (1) those based on human perception and psycho visual experiments, and (2) those that are based on rate-distortion theory and bit rate control. The first method defines the elements of the quantization matrix from visibility thresholds for the DCT coefficients so that the human eyes will not detect them.

The tables give very good perceptual quality for most natural scenes. Moreover, one can tradeoff between image quality and data compression by uniformly scaling the original quantization table by a *quality factor*, for example, halving them will get nearly indistinguishable quality. This technique will become very handy when we try to design a video compression system.

One recent actively researched area is rate control techniques based on rate distortion functions. This can yield better compression result.

The idea behind this kind of rate control is to allocate more bits to the coefficients with large variances. Thus it also known as *Bit-Allocation* [23]. From rate-distortion theory, the optimum bit allocation is given by

$$b_{i,j} = r + \frac{1}{2} \log_2 \frac{\sigma_{i,j}^2}{\left[\prod_{i,j} \sigma_{i,j}^2\right]^{\frac{1}{64}}},$$

where  $b_{ij}$  is the bits allocated to each DCT coefficients and

$$\mu_{i,j} = \frac{1}{B} \sum_{k=1}^{B} y_k[i,j]$$

where B is the number of 8x8 blocks in the image,

$$\sigma_{i,j}^2 = \frac{1}{B} \sum_{k=1}^{B} [y_k[i,j] - \mu_{i,j}]^2$$

and r is the desired average compressed bit rate.

$$r = \frac{1}{64} \sum_{i=1}^{8} \sum_{j=1}^{8} b_{ij}.$$

Therefore we get the quantization matrix:

$$Q[i,j] = \frac{2046}{2^{b_{ij}}}.$$

Note that we use 2046 because the AC coefficients (Any component of the DCT output except the (0,0) component) range of eight bits pixel is from -1023 to 1023.

#### 2.2.3. Entropy Coding

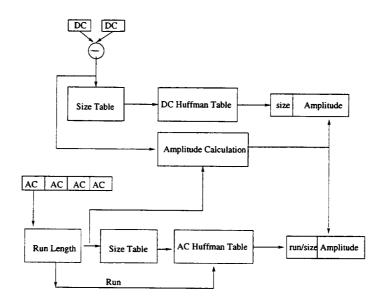

The coefficients after quantization can be further compressed using entropy coder as in Figure 2.2. This normally includes a Run-Length coder and a Variable Length Coder (VLC) which can be a Huffman coder or Arithmetic Coder. The baseline JPEG implementation uses Huffman coding only. Now we describe the operation of the entropy coder in JPEG.

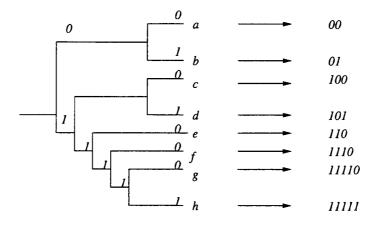

Huffman code construction procedure the following steps:

- 1. Order the symbols according to their probabilities. The frequency of occurrence of each symbol must be known a priori. In practice, the frequency of occurrence can be estimated from a training set of data that is representative of the data to be compressed in a lossless manner. If, say, the alphabet is composed of N distinct symbols  $s_1, s_2, ..., s_N$  and the probabilities of occurrence are  $p_1, p_2, ..., p_N$ , then the symbols are rearranged so that  $p_1 \geq p_2 \geq p_3... \geq p_N$ .

- 2. A contraction process is applied to the two symbols with the smallest probabilities. This can be viewed as the construction of a binary tree, since at each

step we are merging two symbols. At the end of this recursion process, all the symbols  $s_1, s_2, ..., s_N$  will be leaf nodes of this tree.

3. The codeword for each symbol  $s_i$  is obtained by traversing the binary tree from its root to the leaf node.

As we have seen, the Huffman encoding process is relatively straightforward. Fixed-length input symbols are mapped into variable-length codewords. Hence the name VLC. One of the desirable features of a Huffman code is that it is a prefix-condition code which makes it uniquely decodable. Since there are no fixed-sized boundaries between codewords, if some of the bits are incorrectly received, the error will propagate such that all the data is lost. So, special markers are designated to indicate the start or end of a compressed stream packet. Huffman decoding has several implementations, such as Bit-Serial decoding and Lookup-Table-Based Decoding.

There are separately coding methods for DC coefficients (The (0,0) component of the DCT output) and AC coefficients because of their different statistics. Due to the high correlation of DC values among adjacent blocks, JPEG uses differential coding for the DC coefficients. That is, instead of coding each DC, the difference between the DC coefficients of two blocks  $(DC_i - Dc_{i-1})$  are coded. Actually, the residual is not directly Huffman coded, instead, it is expressed as a pair of symbols: the category and the magnitude. The first symbol represents the number of bits needed to encode the magnitude. Only this value is Huffman coded. This notion of using a category table is a form of context modeling and simplifies the Huffman coder. Without categorization of the difference, we would require a very large Huffman table.

For 8 bit-per-pixel data, DC differentials can take values in the range [-2,047, 2,047]. This range is divided into 12 size categories. Thus, after a table lookup, each

DC differential can be described by the pair (size, amplitude), where *size* defines the number of bits required to represent the amplitude, and *amplitude* is simply the amplitude of the differential.

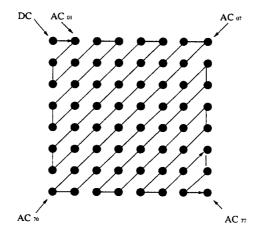

AC coefficients are processed in a different manner. They are scanned in Zig-Zag order (Figure 2.3) which allows for a more efficient operation of the run-length coder.

A run-length coder yields the value of the next nonzero AC coefficient and a run. This sturcture is motivated by the fact that there are lots of zeros among AC coefficients after quantization. Therefore, each nonzero AC coefficient can be described by the pair (run/size, amplitude). Similar to the case for DC coefficients, the value of run/size is Huffman coded instead of amplitude. For example, an AC coefficient with value 3 is preceded by 3 zeros. Hence, the coefficient is represented by (3/2,3), If the Huffman code of 3/2 is 111110111 then the code will look like 11111011111. Another important symbol is end of block (EOB) which denotes that the rest of the AC coefficients are all zeros. This way we can greatly reduce the code table size.

#### 2.3. Operation Modes

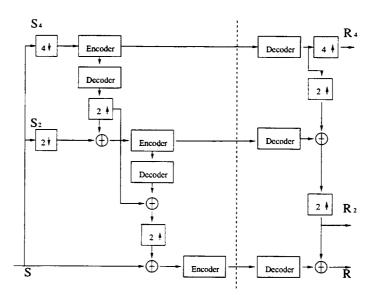

The JPEG standard specifies four modes of operation: Sequential DCT-based, left to right, top to bottom; progressive DCT-based, coarse to sharp resolution; lossless, exact reconstruction; hierarchical, can decode lower resolution without decoding full resolution image first (Figure 2.4).

Under the lossless mode, a predictive coder followed by either a Huffman or an arithmetic coder is used instead of a DCT-based thus get rid of the quantization step where the information is lost [36]. In the progressive mode, coding is performed in *multiple scans*. There are two procedures that are allowed for progressive coding: *spectral selection* where DCT coefficients are grouped into "spectral" bands of related spatial frequencies and the lower-frequency bands are sent first, and *successive approximation* which the information is first sent with lower precision and then refined in later scans. Figure 2.4 is a detail graph of another operation mode, namely, hierarchical coding. This mode is very useful when there are multiresolution requirement. This will also lead us to next chapter when we introduce the multiresolution techniques using wavelets.

From this three-level hierarchical coder we can get some ideas of the coding procedure. First, the source image data S is subsampled twice  $S_2$  and  $S_4$ . The reconstructed pictures have different resolution,  $R_4$  is constructed from  $S_4$ .  $R_2$  is constructed from the encoded difference of  $S_2$  and its upsampled version.

Table

FIGURE 2.2. Entropy Coding

FIGURE 2.3. Zig-zag scan of the AC Coefficients

FIGURE 2.4. Three-level Hierarchical Coder

#### 3. LOSSY VIDEO COMPRESSION

#### 3.1. Introduction

Video can be regarded as still images with another dimension: time. Video is merely still images displayed at a speed of 30 frames per second. This is not only true in the digital world but also applies to the analog world, TV is broadcast at 30 frame or 60 fields per second whereas movies are showed at 24 frames per second. Most of the video compression is lossy because it is not possible to achieve very high compression ratio by employing lossless compression methods. Nor is it necessary because human eyes cannot tell the loss if the compression is done gracefully. Although most of the still image compression methods are used in video compression, or *intra-frame coding*, many efforts have been made in to explore the redundancy along the temporal domain to remove the correlation between the frames, or, *inter-frame coding*. Among all the techniques, motion estimation (ME) is by far the most widely used and implemented methods for reducing the temporal redundancy [25].

#### 3.2. Motion Estimation

Consider a picture sequence of a singer singing on stage, we will find that two kinds of correlation exist, one is the spatial correlation among the pixels composed of a singer. Whereas the other is the temporal correlation, the same object (the singer) appears in many frames and the background is almost fixed. Thus, the successive frames of a video sequence are analyzed to estimate the motion (displacement) vectors of moving pixels or blocks of pixels. Many different types of algorithms such

as Blocking-Matching Algorithms (BMA), Pel-Recursive Algorithms (PRA), Phase Correlation, etc., have been developed and implemented in video encoders. We will focus on BMA since it is the more widely used in real-time video encoders. And it is also used in MPEG standard [31].

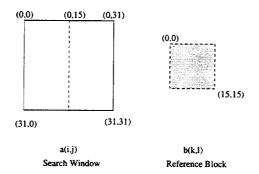

FIGURE 3.1. Temporal Correlation Between Pictures

In BMA, each video frame is partitioned into blocks. The motion vectors are extracted on a block by block basis. Two frames are used in motion estimation: a reference frame and a current frame (Figure 3.1). For each block in the current frame, it is searched in a search-window in the previous frame for a best matched block based on a match-criterion. If we define a frame as a current frame at time t, we define a reference frame at past time t - n for forward motion estimation, and future time t + k for backward motion estimation. If we define the location of current macroblock as (x, y), then the best matching block with MV (u, v) is located at (x + u, y + v). However, we make the assumption that all the pixels in the macroblock go through the same common displacement. In BMA, the motion vectors have to be transmitted to the decoder for reconstruction of the image. These are transmission overheads compared to the simple pel-by-pel predictive coding. The amount of the overhead is dependent on the block-size and the search-window size. Larger block-sizes result in fewer blocks in a frame, and thus, less transmission overhead. However, since the algorithms assume that the displacement is constant

within the block, larger block-sizes will degrade the performance. In most video coding standards, the size of the block is 16x16.

The most used matching criterion is the MAD or Mean Absolute Difference, or

$$MAD(i,j) = \frac{1}{MN} \sum_{k=0}^{M-1} \sum_{l=0}^{N-1} |C(x+k,y+l) - R(x+k+i,y+l+j)|,$$

where C(x+k,y+l) is the pixel value of the current block, R(x+k+i,y+l+j) is the reference block and  $-p \le i \le p$ . The best matching block R(x+i,y+j) is the one with the minimized MAD. It can be shown that MAD almost performs as well as other much more complicated cost functions such as MSE (mean squared error). Therefor, for the rest of the thesis, the best match for ME means minimum MAD is considered.

In order to be able to track large motion, it is desirable to search in a large search-window. However, a larger search-window results in more search positions in the window and the required computation increases rapidly. Also, the transmission overhead is increased since more bits are needed to represent the motion vector. In videoconference applications, for example, H.261 standard a search-window that does not exceed +/- 15 is defined. However, to track a car chasing scene we may need a larger search-window.

There are several strategies to search for the best matched blocks. The most straightforward and brute-force method is the full-search (FS) which searches all the  $(2p+1)^2$  locations in the search window. For each position, MAD is calculated and the smallest generates the motion vector as illustrates in Figure 3.2.

The FS method will guarantee the optimum solution since all possible positions of search-window are exhaustively searched. However, it also requires very large amount of computations and data-accesses. If we ignore the operation of load-

FIGURE 3.2. Block Matching Motion Estimation

ing and storing of the current and reference blocks, then for each NxM macroblock we need to do  $3(2p+1)^2MN$  operations, where 3 means a subtraction, an absolute-value calculation, and one addition. For a typical TV broadcast with resolution 720x480 and 30 frames/s, and if we take N=M=16, p=15 the total operation need will be  $3(31)^2720\times480\times30$  or 28.89 GOPS (Giga operations per second ). It should be noted that the amount of computation is independent of the block-size and is a quadratic function of the search-range. So for higher search range (which is necessary for high quality sports broadcast) the required number of operations is even higher. If we consider the memory access, the required I/O bandwidth is very difficult to achieve [43].

In order to reduce the amount of required computations and data accesses, many fast search methods have been developed. These algorithms are suboptimum in the sense that the search strategies do not guarantee that we will find the minimum MAD value. However, the complexity is significantly reduced either by decreasing the number of search locations or by computing fewer pixel difference per location. In the following we will give some examples of these methods.

The three-step search (TSS) is a fast ME method that decreases the number of search areas. Instead of searching all the locations inside the search-window we only search the major points in the search window. First we compute the minimum MAD from the locations of  $(0,0), (0,d_1), (0,-d_1), (d_1,-d_1), (d_1,0), (d_1,d_1), (-d_1,d_1), (-d_1,0), (-d_1,-d_1)$  where  $d_1$  is given by  $d_1 = 2^k - 1$  where  $k = \log_2 p - 1$  and p is the search range.

After we find the best match among these locations (for TSS where k=3 there are nine locations), we continue this process using  $d_2 = \frac{d_1}{2}$  until the we find the minimum. This greatly reduces the computation requirements. For instance, with p=7 only 25 locations need to calculated instead of the 225 locations if we use full search. Comparing the implementation complexity of this method with that of full search, for the same resolution TV (720x480, 30 frames/s) and p=15, yields  $3 \times 720 \times 480 \times 30 \times (8[\log_2 p]+1)$  or about 1 GOPS.

Similar to TSS, PHODS (Parallel Hierarchical One-dimensional Search) also uses the idea of reducing the search locations. However, in PHODS the search is done independently along the two dimensions, in this case, the MAD calculations are parallelizable and it has a regular data flow, since the search locations are always along the x and y axis. However, PHODS and TSS all assume that the MAD increases monotonically as the search area moves away from the best-matched location. If this assumption fails, search for a global minimum may get trapped into a local minimum, in other words, the search may be misguided by local minima at the beginning steps.

As we mentioned before, there exists another method to reduce the computation requirement of ME, by using reduced pixel numbers. Since block matching implies that all pixels within the macroblock have the same motion, an estimate of the motion can also be obtained with fewer pixels. One straightforward way is by pixel subsampling. However, this decimation has to be done very carefully such that the ME accuracy will not be greatly affected. For example, for each macroblock, one fourth of the pixels can be used to calculate MAD, by alternating the pixel patterns and associating a different pattern for each neighboring search location, all the pixels within the block can be covered thus minimizing the possibility of not considering one-pixel-wide horizontal, vertical and diagonal lines.

The two fast ME methods we discussed before are such that one reduces the search locations and the other reduces the pixel numbers. How about combining them together? Their combination will lead naturally to Hierarchical Motion Estimation (HME) which combines two features together and is widely used in almost all the video compression algorithms. In the HME, the matching of blocks is performed in two or three steps with decreasing block-size and increasing search resolutions. Lowpass filtering is applied to improve the reliability. Subsampling is used to reduce the required computation load. In the following example we give in depth introduction to a 3 level hierarchical motion estimation.

First, several low-resolution versions of the current picture and the reference picture is formed by lowpass filtering and subsampling. In Figure 3.3 we show two low levels (namely, level 1 and level 2) of the original resolution (level 0). This step applies to both the reference picture and the current picture.

The ME starts from the lowest resolution, in our case, level 2. Because the picture size is small so the 4x4 macroblock is used in ME instead of 16x16. The scaled versions of search parameter can also be used, that is we use  $\frac{p}{4}$  instead of

p. We can use any of the search methods mentioned before. However, because of the smaller search area and smaller macroblock, full search method can be used to increase the accuracy. If we assume that the search origin in level 0 is (x, y) then it will be  $(\frac{x}{4}, \frac{y}{4})$  at level 2. The complexity of ME at level 2 will be:

$$\frac{picture size}{Macroblock size} \times (2 \times p + 1)^2 \times (Macroblock size) \times 3,$$

where picture size will be 180x120 and p is 4, and the result is 157.46 MOPS. Assume the MV we found at this step is  $(u_2, v_2)$ , then we go up one level and do the ME at level 1. Because the  $(u_2, v_2)$  is the MV we found at the lower resolution, we need to refine the search. Therefore we do not have to search in a very big area, instead the search is centered around the  $(u_2, v_2)$ . Thus, a search region [-1, 1] is enough. As before, we use full search since only 9 locations are needed to compute. We need to compute the origin  $(x/2 + 2u_2, y/2 + 2v_2)$  again because in this level we are using macroblocks of size 8x8. Repeating the complexity analysis, we can get 69.98 MOPS, assuming the minimized MAD is found at  $(u_1, v_1)$ .

At level 0 or the reference picture level, again we search 9 locations around origin  $(x + 2u_1, y + 2v_1)$  with marcoblock size of 16x16, the computation complexity is now 279.9 MOPS. At this level the final MV will be generated.

If we add the computation requirement at each level together, we will get the total complexity of 507.38 MOPS, which is greatly reduced from the 28.89 GOPS needed for full-search, and almost half of the TSS search of 1 GOPS. Therefore, this is by far the most popular ME algorithm [28] (Figure 3.3).

By subsampling the reference picture will also created some problems since inaccurate MV may be generated for regions containing small objects. Because the search starts from the coarse version of the reference picture, regions containing small objects maybe completely eliminated and thus failed to be traced. If there are

FIGURE 3.3. Hierarchical Motion Estimation

lots of small objects moving then the situation gets worse. Moreover, the subsampled version of the picture has to be stored for use in ME, thus increasing the system memory requirement. On the other hand, the creation of low-resolution version (especially the lowpass filtering) will reduce noise.

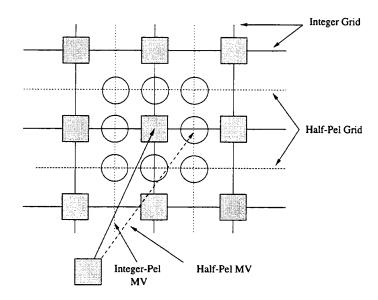

Because the true motion between frames is unrelated to the sampling grid, if the displacement estimates are obtained at a finer resolution, a better prediction can also be obtained. The ME we talked about before is all restricted to integer pixel grids. This means that we can have half-pixel or even quarter-pixel accuracy motion vector.

Half-pixel accuracy MV can be easily found by interpolating the current and reference pictures by a factor of two and then using any of the ME methods described in the previous section. However, if both interpolated pictures have to be stored for computation, excessive memory has to be provided. To avoid this, we can follow these steps for the half-pixel ME.

In the first step, a MV with integer-pel accuracy using any of the ME methods is obtained. The resulting integer-pel motion vector (u, v) which yields the minimum MAD is shown in the figure.

In the following steps, we refine the results of the first step to obtain the motion vector with the desired half-pel accuracy. As shows in Figure 3.4, eight new MAD are calculated at the new half-pel locations around the origin. The macroblock is 16x16 and the top-left corner of each block being at the locations marked circle in the figure. For each of these eight new search blocks, we know only those pixel values with coordinates matching our original integer-pel grid. The remaining values on the half-pel grid can be estimated using simple interpolation techniques. The MAD is computed by comparing each of these eight search blocks with the original macroblock. Therefore, the position where the MAD is minimum is the location for the half-pel MV. If we define this location as (k, l) then the refinement MV will be (u + k/2, v + l/2).

The quarter-pel ME can be done in the same manner. One of the computation intensive steps of the above procedure is the interpolation step. There are some fast interpolation methods discussed in the literature [43], thus, we are not going to discuss them in greater detail. We will come back to this topic when we are discusses the VLSI implementation of the ME.

## 3.3. Motion Compensation

The next step after the step of ME where the MV is found, is to use this information to reduce the interframe redundancy. The output of the motion estimator, the coordinates (u, v) which define the relative motion of a block from one frame to another, are used to define the motion compensation (MC) as the process of com-

FIGURE 3.4. Half-Pel accurate MV estimation

puting changes among frames by establishing correspondence between frames. In other words, as the process of compensating for the displacement of moving objects from one frame to another. The prediction error as:

$$e(x, y, t) = I(x, y, t) - I(x - u, y - v, t - 1),$$

where I(x, y, t) is the pixel value at spatial location (x, y) in frame t and I(x-u, y-v, t-1) is the *corresponding* pixel value at spatial location (x-u, y-v) in frame t-1.

Note that the above temporal prediction definition is very similar to the differential coding scheme DPCM. The difference is that we form the temporal prediction using temporally adjacent samples, which are determined through the process of motion estimation, so it gives a better prediction. Notice the MC is performed in both the encoder and the decoder but ME is needed only in the encoder.

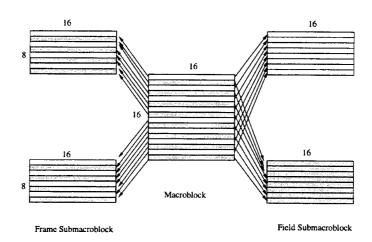

We can now start to put everything together and build a hybrid coding system using the methods we mentioned so far. Before that, we need to discuss the concepts of frame and field. In current TV industry the video is interlaced, which means that each frame is comprised of fields, a top field and a bottom field (or odd and even field, Figure 3.5). Scanlines from the two fields are interleaved. Note that, spatially adjacent scanlines are not temporally adjacent. For example, at 30 fps, the adjacent scanlines are  $\frac{1}{60}$ -th of a second apart.

FIGURE 3.5. Field Image

In order to exploit the presence in a macroblock of lines from two temporally separated fields, two fundamental modes of MC are defined: the *frame-MC* and the *field-MC* modes. The frame-MC mode does not discriminate between the two fields inside a macroblock, it compensates a macroblock with another macroblock containing lines from both fields. In the field-MC mode, the lines from each field in a macroblock are compensated with a block containing only lines from the field of the same parity. For the frame-MC mode two block sizes are allowed, with dimensions of 16x16 and 16x8, respectively. In the latter case, a macroblock is separated into two horizontal halves. In the field-MC mode a macroblock is separated into two fields. From only one field with a size of 16x8.

A MV can point either to a field in another reference frame or to a field in the current frame. For example, the first field can be predicted either from the top or the bottom fields in a reference frame, or the field can be predicted either from the bottom field of another frame or from the top field of the current frame. The vertical range for the integer MV is halved, since one field-line shift is equivalent to a two-line shift in the picture. The half-pixel positions for the field-MC mode are obtained as follows. A first intra-field spatial interpolation operation places the interpolated pixels where the lines of the other field lie. Since these positions correspond to integer-line locations of the picture, a second intra-field interpolation set up is performed that places the interpolated pixels at half-line positions of the picture, which is equivalent to quarter-line positions inside the field. MV for the field-MC mode are defined with respect to these quarter-line field positions. The half-pel search thus consists of updating the field integer motion vector in two successive steps. The effect is that the frame-mode and field-mode MV have the same resolution relative to the picture.

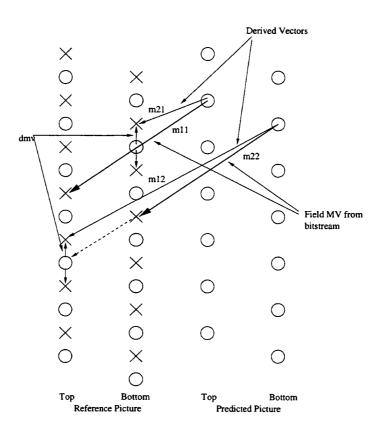

Another MC mode that will be discussed in the later chapter is the *Dual-prime* motion compensation in which only one MV is encoded (in its full format) in the bitstream together with a small differential MV. In the case of field pictures two MVs are then derived from this information. These are used to form predictions from two reference fields (top and bottom) which are averaged from the final prediction. In the case of frame pictures this process is repeated for the two fields so that a total of four field predictions are made.

In order to form a MV for the opposite parity, the existing MV is scaled to reflect the different temporal distance between the fields. A correction is made to the vertical component to reflect the vertical shift between the lines of top field and bottom field and then a small differential MV is added. This process is illustrated in Figure 3.6, which shows the situation for a frame picture.

Therefore, rather than sending four vectors, a single vector is sent with the four required vectors derived using a constant velocity model, and then a small accurately tuning parameter allows an independent adjustment of +/-1 pel vertically in two of the vectors. Thus we can achieve low delay and less overhead. Assuming that  $m_{11}$  is the MV predicted from reference picture top field to the predicted picture top field, then we have the following relationship:

$$m_{22} \approx m_{11} + \delta$$

$$m_{21} \approx 1/2m_{11} + \delta$$

$$m_{12} \approx 3/2m_{11} + \delta$$

where  $\delta$  can take the values in -1, 0 or 1.

Similar to ME, there is also frame DCT and field DCT and this can also be selected based on the analysis before coding. So if we have adaptive DCT and adaptive MC, then we have the major building blocks for adaptive frame/field (AFF) [4].

FIGURE 3.6. Dual Prime for ME

## 4. MPEG STANDARDS

# 4.1. Background

The MPEG committee was established by ISO in 1988 with the mission to develop standards for the coded representation of moving pictures and associated audio information on digital storage media. Over the next few years, participation amassed from international technical experts in the areas of Video, Audio, and Systems, reaching over 200 participants by 1992. By the end of the third year (1990), a syntax emerged, which when applied to code SIF (standard input format) video and compact disc audio samples rates at a combined coded bit rate of 1.5 Mbit/sec, approximated the perceptual quality of consumer video tape (VHS). Formally known as ISO standard 11172, or MPEG-1 which is mainly used in CD-ROM and VideoCD applications [20].

After demonstrations proved that the syntax was generic enough to be applied to bit rates and sample rates far higher than the original primary target application, a second phase (MPEG-2) [21] was initiated within the committee to define a syntax for efficient representation of broadcast video. Efficient representation of interlaced (broadcast) video signals was more challenging than the progressive (non-interlaced) signals coded by MPEG-1. Similarly, MPEG-1 audio was capable of only directly representing two channels of sound. MPEG-2 introduce a scheme to correlate multichannel discrete surround sound audio. Need for a third phase (MPEG-3) was anticipated in 1991 for High Definition Television, although it was later discovered by late 1992 and 1993 that the MPEG-2 syntax simply scaled with the bit rate could phase out MPEG-3 [37]. In 1994, this effort lead to the ISO

standard 13818. MPEG-4 was launched in late 1992 to explore the requirements of a more diverse set of applications, while finding a more efficient means of coding low bit rate/low sample rate video and audio signals, such as wireless transmission of video and audio signals. MPEG-4 is expected to be defined by 1998.

From the beginning, MPEG has been embraced by industry, in fact, it is the driving force behind this effort. In 1991 C-Cube Microsystem made the world's first MPEG-1 decoder, then the world's first MPEG-1 encoder in 1993 and the world's first MPEG-2 encoder in 1994. Other companies then joined the band wagon, e.g., AT&T, IBM, IIT, LSI, NEC, SGS-Thomson and TI, etc.. MPEG applications such as VideoCD player (MPEG-1 decoder) and Direct TV set top box (MPEG-2 decoder) have become the most successful consumer electronics ever. Moreover, MPEG is an exclusive syntax of the United States Grand Alliance HDTV specification, the European Digital Video Broadcasting (DBS) and Sony/Toshiba Digital Video Disk (DVD).

The MPEG standards are published in four parts: systems, video, audio, and conformance testing [8].

Part 1—Systems: The first part of the MPEG standard has two primary purposes: 1) a syntax for transporting packets of audio and video bit streams over digital channels and storage mediums (DSM), 2) a syntax for synchronizing video and audio streams.

Part 2—Video: describes syntax (header and bit stream elements) and semantics (algorithms telling what to do with the bits). Video breaks the image sequence into a series of nested layers, each containing a finer granularity of sample clusters (sequence, picture, slice, macroblock, block, sample/coefficient). At each layer, algorithms are made available which can be used in combination to achieve efficient compression. The syntax also provides a number of different means for

assisting decoders in synchronization, random access, buffer regulation, and error recovery. The highest layer, sequence, defines the frame rate and picture pixel dimensions for the encoded image sequence.

Part 3—Audio: describes syntax and semantics for three classes of compression methods. Known as Layers I, II, and III, the classes trade increased syntax and coding complexity for improved coding efficiency at lower bit rates. The Layer II is the industrial favorite, applied almost exclusively in satellite broadcasting (Hughes DSS) and compact disc video (White Book). Layer I has similarities in terms of complexity, efficiency, and syntax to the Sony MiniDisc and the Philips Digitial Compact Cassette (DCC). Layer III has found a home in ISDN, satellite, and Internet audio applications. The sweet spots for the three layers are 384 kbit/sec (DCC), 224 kbit/sec (CD Video, DSS), and 128 Kbits/sec (ISDN/Internet), respectively.

Part 4—Conformance: defines the meaning of MPEG conformance for all three parts (Systems, Video, and Audio), and provides two sets of test guidelines for determining compliance in bit streams and decoders. MPEG does not directly address encoder compliance.

Part 5—Software Simulation: Contains an example ANSI C language software encoder and compliant decoder for video and audio. An example system encoder/decoder is also provided which can multiplex and demultiplex separate video and audio elementary streams contained in computer data files.

As of March 1995, the MPEG-2 volume consists of a total of 9 parts under ISO/IEC 13818. Part 2 was jointly developed with the ITU-T, where it is known as recommendation H.262. The four additional parts are listed below:

Part 6—Digital Storage Medium Command and Control (DSM-CC): provides a syntax for controlling VCR-style playback and random-access of bit streams

encoded onto digital storage mediums such as compact disc. Playback commands include Still frame, Fast Forward, Advance, Goto.

Part 7—Non-Backwards Compatible Audio (NBC): addresses the need for a new syntax to efficiently -correlate discrete multichannel surround sound audio. By contrast, MPEG-2 audio (13818-3) attempts to code the surround channels as an ancillary data to the MPEG-1 backwards-compatible Left and Right channels. This allows existing MPEG-1 decoders to parse and decode only the two primary channels while ignoring the side channels (parse to /dev/null). This is analogous to the Base Layer concept in MPEG-2 Scalable video. NBC candidates include non-compatible syntaxes such as Dolby AC-3. Final document is not expected until 1996.

Part 8—10-bit video extension. Introduced in late 1994, this extension to the video part (13818-2) describes the syntax and semantics to coded representation of video with 10-bits of sample precision. The primary application is studio video (distribution, editing, archiving). This part has not been finished.

Part 9—is the real time interface.

All MPEG standards are generic, that is, application independent, they do not specify the operations of the encoder, instead, they specify the syntax of the coded bit stream and decoding process [15] [3].

# 4.2. Digital Video Formats

Both MPEG-1 and MPEG-2 video syntax can be applied at a wide range of bit rates and sample rates. The MPEG-1 that most people are familiar with has parameters of 30 SIF pictures (See following table) per second and a bit rate less than 1.86 megabits/s. Also known as "Constrained Parameters Bitstreams". This

popular interoperability point is promoted by Compact Disc Video (White Book) [7].

| Video Format | Frame Size (Y) | Frame Rate | Size     |

|--------------|----------------|------------|----------|

| HDTV         | 1920*1250      | 50 Hz      | 1.9 Gb/s |

| CCIR 601     | 720*576 (PAL)  | 25 Hz      | 166 Mb/s |

|              | 720*480 (NTSC) | 30 Hz      | 166 Mb/s |

| SIF          | 360*240        | 30 Hz      | 31 Mb/s  |

| QSIF         | 180*120        | 30 Hz      | 8 Mb/s   |

| QQSIF        | 90*60          | 30 Hz      | 2 Mb/s   |

Although MPEG bit-stream syntax allows for picture sizes of up to 4095\*4095 pixels with a bitrates up to 100 Mb/s, many of the applications have been optimized for SIF (MPEG-1) and CCIR601 (MPEG-2 main level, main profile). A color video source has three color components, Y, Cb and Cr. One of the most useful formats is called 4:2:0 subsampling format where the resolution of the chroma components is half of the luminance resolution in both the horizontal and vertical dimensions. This is the only format for MPEG-1. Multiplex order within macroblock is YYCbCr, and targets main stream television and consumer entertainment. MPEG-2 also supports the 4:2:2 and 4:4:4 color subsampling formats. In the 4:2:2 format, the chrominance components have the same vertical resolution as the luminance component, but the horizontal resolution is halved. Multiplex order is YYYYCbCrCbCr, mainly used in studio production environments, professional editing equipment, distribution and servers. In the 4:4:4 format, all components have identical horizontal and vertical resolutions. Multiplexed order is YYYYCbCrCbCrCbCr and used in computer graphics application [14].

# 4.3. Temporal processing

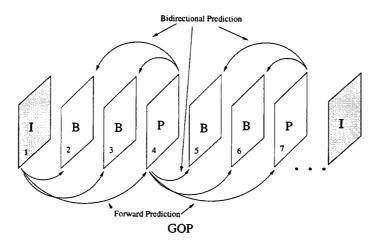

One of the main applications of MPEG is in consumer and computer electronics. Thus it requires the random access of the video data, such as forward, rewind, still, stop and index. Because of the conflicting requirements of random access and highly efficient compression, three main picture types are defined, namely, I, B, P, as in Figure 4.1.

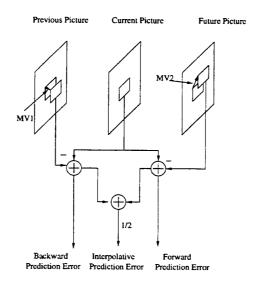

FIGURE 4.1. I B P frame in a Video Sequence

Intra coded pictures (I pictures) are coded without reference to other pictures. They provide access points to the coded sequence where decoding can begin, but are coded with only moderate compression. Predictive coded pictures (P pictures) are coded more efficiently using motion compensated prediction from a past intra or predictive coded picture and are generally used as a compensated prediction from a past intra or predictive coded pictures and are generally used as a reference for further prediction coded pictures (B pictures) provide the highest degree of compression but require both past and future reference pictures for motion compensation (Figure 4.2). B pictures are never used as references for prediction. B pictures are disliked by lots of people because the computational complexity, bandwidth, end-

to-end delay and picture buffer size all get much larger. We will discuss how to generate the B pictures in the following sections. (In MPEG-1 there is another type of picture defined as D picture which is coded like I picture but only with the DC coefficients of DCT output. D pictures are not used in MPEG-2)

FIGURE 4.2. Bidirectional Motion Compensation

The organization of the three picture types in a sequence is very flexible, it usually goes like:

# IBBPBBPBBPBBIBBPBBPB...,

where there are 12 frames from I to I. This is based on a random access requirement that is needed as a starting point at least once every 0.4 seconds or so. The ratio of P's to B's is based on experience.

The order of the coded frames in the bitstream, also called coded order, is the order in which a decoder reconstructs them. The order of the reconstructed frames at the output of the decoding process, also called the display order, is not always the same as the coded order.

When the sequence contains no coded B pictures, the coded order is the same as the display order. When B pictures are present, then the frame reordering

is performed according the following rules: If the current frame in coded order is a I or P, then the output frame is the frame reconstructed from the previous I or P. If the current frame is a B, then the output frame is the frame reconstructed from that B.

One example is Figure 4.1, which has two coded B frames between successive coded P frames and I frames. Frames '1I' is used for prediction of frame '4P'. '1I' and '4P' are both used for prediction of frames '2B' and '3B'. Therefore the order of coded frames in the coded sequence shall be '1I', '4P', '2B', '3B'. However, the decoder shall display them in the order of '1I', '2B', '3B', '4P'.

There is no special requirement to use either P pictures or B pictures in the MPEG bit stream. However, B pictures require significantly fewer bits than either I or P pictures. Increasing the number of B between I and P may not lead to better compression due to a drop off in temporal correlation as the distance between B and I or P increases.

### 4.4. Encoder and Decoder

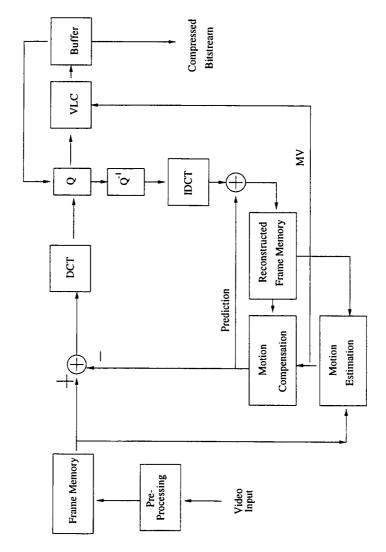

The MPEG standard does not define an encoding process. Figure 4.3 shows the basic functions that need to be executed by a typical MPEG encoder [26].

## Preprocessing

This process may include color conversion, format translation, prefiltering, and subsampling. None of these operations is specified in the standards.

#### ME and MC

Figure 4.2 shows the bidirectional ME and MC. After the preprocessing, the encoder selects the coding type for the input picture, namely, I, B or P. The decision is made differently for each macroblock for every different types of picture. The I

FIGURE 4.3. MPEG Encoder ( P Pictures )

frame is coded like a still image. As P or B frame., the encoder does not code the picture directly. Instead it codes the prediction errors. Figure 4.3 shows a P coding. B frame can be coded very similar with more complicated ME methods.

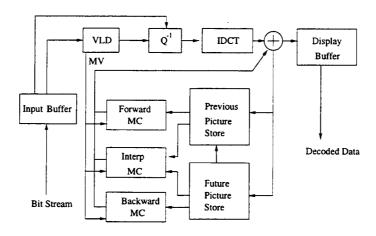

As we noticed from the Figure 4.4, the decoder is very similar to the feedback loop of the encoder.

FIGURE 4.4. MPEG Decoder

### 4.5. Bit Stream Structure

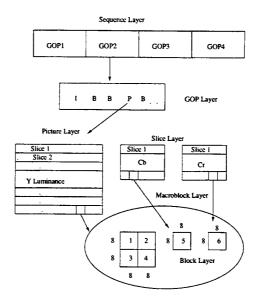

The MPEG-1 syntax has a hierarchical representation with six layers (Figure 4.5: sequence, GOP, picture, slice, macroblock and a block layer.

**Sequence** a sequence of pictures. Information about frame size, pixel aspect ratio, quantization matrices, etc.

**GOP** or Group of Pictures, a set of pictures bracketed by I-frames. Permits random access.

Picture a single frame. Defines I, P, or B frame.

Slice a set of blocks within a frame. Header allows resynchronizations after errors

Macroblock a set of four luma blocks and two chroma blocks corresponding to the same spatial region of he picture.

**Block** a single 8x8 block for DCT coding.

The concept of the Group of Pictures layer does not exist in MPEG-2. It is an optional header useful only for establishing a SMPTE time code or for indicating

FIGURE 4.5. Bitstream Layer of MPEG-1

that certain B pictures at the beginning of an edited sequence comprise a brokenlink. This occurs when the current B picture requires prediction from a forward reference frame has been removed from the bitstream by an editing process. In MPEG-1, the Group of Pictures header is mandatory, and must follow a sequence header.

Progressive frames are a logic choice for video material which originated from film, where all pixels are integrated or captured at the same time instant. Most electronic cameras today capture pictures in two separate stages: a top field consisting of all odd lines of the picture are nearly captured in the time instant, followed by a bottom field of all even lines. Frame pictures provide the option of coding each macroblock locally as either field or frame. An encoder may choose field pictures to save memory storage or reduce the end-to-end encoder-decoder delay by one field period.

To aid implementations which break the decoding process into parallel operations along horizontal strips within the same picture, MPEG-2 introduced a general semantic mandatory requirement that all macroblock rows must start and end with at least one slice. Since a slice commences with a start code, it can be identified by inexpensively parsing through the bitstream along byte boundaries. Before, an implementation might have had to parse all the variable length tokens between each slice (thereby completing a significant stage of decoding process in advance) to know the exact position of each macroblock within the bitstream. In MPEG-1, it was possible to code a picture with only a single slice. Naturally, the mandatory slice per macroblock row are restrictions also facilitates error recovery.

Motion vectors are now always represented along a half-pel grid for MPEG-2, A intrinsic half-pel accuracy can encourage use by encoders for the significant coding gain which half-pel interpolation offers.

In both MPEG-1 and MPEG-2, the dynamic range of motion vectors is specified on a picture basis. A set of pictures corresponding to a rapid motion scene may need a motion vector range of up to +/- 64 integer pixels. A slower moving interval of pictures may need only a +/- 16 range. Due to the syntax by which motion vectors are signaled in a bitstream, pictures with little motion would suffer unnecessary bit overhead in describing motion vectors in a coordinate system established for a much wider range. It later became practice in industry to have a greater horizontal search range than vertical, since motion tends to be more prominent across the screen than up or down. Secondly, a decoder has a limited frame buffer size in which to store both the current picture under decoding and the set of pictures (forward, backward) used for prediction by subsequent pictures. A decoder can write over the pixels of the oldest reference picture as soon as it no longer is needed by subsequent pictures for prediction. A restricted vertical motion vector

range creates a sliding window, which starts at the top of the reference picture and moves down as the macroblocks in the current picture are decoded in raster order. The moment a strip of pixels passes outside this window, they have ended their life in the MPEG decoding loop. As a result of all this, MPEG-2 created separate horizontal and vertical range specifiers, greater restrictions are also placed on the maximum vertical range than on the horizontal range. In Main Level frame pictures, in range [-128,+127.5] vertically, and [-1024,+1023.5] horizontally. In field pictures, the vertical range is restricted to [-64,+63.5].

Also, macroblock stuffing or the "0000 0001 111" is a stuffing code and can be inserted into the bit stream wherever the encoder detects the possibility of a buffer underflow. Because the difficulty to implement in VLSI and the reduction of bit efficiency ( This stream is ignored by the decoder ). Stuffing is not permitted in MPEG-2.

# 4.6. Macroblock Coding

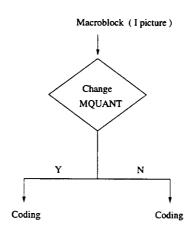

For the above discussion we assume that all the macroblocks with each frame are coded the same way. Actually, in a real application, even within a single I, B or picture, macroblocks can be coded differently. The decision trees for coding macroblocks are shown in Figure 4.6 and Figure 4.7.

I pictures are coded without MC, nevertheless, MPEG syntax allows each macroblock to be coded using a different effective quantization matrix. For the AC coefficients of DCT, the quantization step depends not only on the value of the corresponding element in the quantization matrix but also on the scale factor which is also referred to as MQUANT. Thus, the macroblocks in I pictures can be coded using a new MQUANT or using the old MQUANT (Figure 4.6). After this stage

the DC coefficients are DPCM coded similar to JPEG. However, for AC coefficients, only the most frequent run/amplitude values are coded the same as JPEG. For the rest values are coded by an *escape* code followed by separate Huffman codes for the run-length and the amplitude.

FIGURE 4.6. I Frame Macroblock Coding

For P pictures the encoder has more coding choices for each macroblock due to MC. First, decide if there is substantial motion between the two frames, if not, the MV can be set to zero. For example, if the background seldom changes between the frames, then there will not be bits to allocate to MV. If there exists a high level of temporal activity, in other words, the ME may fail (If the best match macroblock moved out of search window), the energy of prediction error may be greater than the macroblock; in this case, the decisions have to be made if the macroblock will be coded in intra-mode or inter-mode.

If the ME is very accurate and we almost have found the perfect match (Accurate MV), then after MC, the prediction error may be so small that the following quantization step will make every coefficient prediction error to zero. Thus, a macroblock like this can be skipped (without coding) to reduce the bits count to code the picture. Sometimes, the whole macroblock may not have to be quantized to

zero, instead, one or more blocks of the six blocks are all zero, in this case, a six-bit pattern referred to as the *coded block pattern* will indicate to the decoder which of the six blocks within the macroblock have been coded.

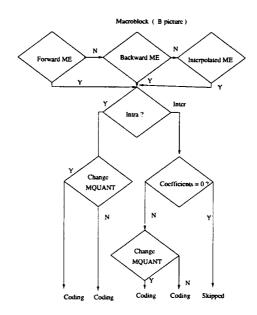

B pictures are very similar to the P pictures except that the MC mode, namely, forward, backward, or interpolated MC mode, has to be decided before all the above decisions can be made (Figure 4.7).

FIGURE 4.7. B Frame Macroblock Coding

## 4.7. Scalable Bit Streams

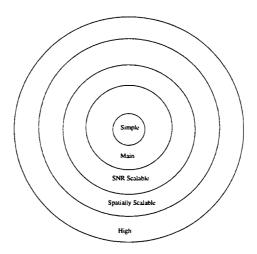

A new feature of MPEG-2 is bit stream scalability, which allows for a layered representation of the coded bit stream. The syntax allows four basic modes of bit stream scalability:

Data Partitioning The bit stream is split into two layers, one layer for critical header information (Such as headers and MV). This is intended for use in applications that can allocate two channels for a single bit steam.

SNR Scalability Support video transmission at multiple quality levels. All the layers have the same spatial resolution but different video qualities. This mode provides for better resilience to transmission errors.

**Spatial Scalability** Support different spatial resolution transmission. Very similar to hierarchical JPEG coding mode where subsampled version can send first with enhancement follows..

**Temporal Scalability** All layers have the same frame size and chrominance formats but different frame rates.

FIGURE 4.8. MPEG-2 Profiles