## AN ABSRACT OF THE THESIS OF

Chelsea Lalla for the degree of Master of Science in

Electrical and Computer Engineering presented on September 18, 2009.

Title: <u>A High Power Emulation of a Wind Farm.</u>

Abstract approved: \_\_\_\_\_

#### Ted K.A. Brekken

As more wind farms are connected to the grid, the variable nature of wind energy begins to influence grid stability. Energy storage could help smooth the variable nature of wind energy. Laboratory demonstration and exploration of the interaction between different energy storage devices and wind energy could help improve and encourage wind energy integration. To this end, a wind energy and energy storage project will be implemented in WESRF's lab comprising of a zinc bromine battery, supercapacitors, hydropower, and wind energy. In this thesis, a scale model of the wind farm component of the project is modeled and experimentally tested. The wind farm is physically modeled by a 120kVA three-phase controllable voltage source and controlled in the synchronous reference frame.

© Copyright by Chelsea Lalla September 18, 2009 All Rights Reserved A High Power Emulation of a Wind Farm

by

Chelsea Lalla

## A THESIS

#### submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Master of Science

Presented on September 18, 2009 Commencement June 2010 Master of Science thesis of Chelsea Lalla presented on September 18, 2009

APPROVED:

Major Professor, representing Electrical Engineering

Director of the School of Electrical Engineering and Computer Science

Dean of the Graduate School

I understand that my thesis will become part of the permanent collection of Oregon State University libraries. My signature below authorizes release of my thesis to any reader upon request.

Chelsea Lalla, Author

## ACKNOWLEDGEMENTS

I am very grateful to Dr. Ted Brekken and Dr. Annette von Jouanne for the opportunity to work and learn at the WESRF lab. I am lucky to have worked with all the wonderful people in the Energy Systems group; their help and enthusiasm made this thesis possible. I would also like to thank my family for their love and patience.

# TABLE OF CONTENTS

| 1 | INTROE | DUCTION                                                                                                                                   |      | 1                    |

|---|--------|-------------------------------------------------------------------------------------------------------------------------------------------|------|----------------------|

|   | 1.1    | Background                                                                                                                                |      | 1                    |

|   |        | <ul><li>1.1.1 Energy Storage</li><li>1.1.2 Scope of Thesis</li></ul>                                                                      |      | 1<br>4               |

|   | 1.2    | Wind Farm Modeling                                                                                                                        |      | 7                    |

| 2 | SYSTEM | I MODEL                                                                                                                                   |      | 8                    |

|   | 2.1    | Simulation Model                                                                                                                          |      | 8                    |

|   | 2.2    | Controller Design                                                                                                                         |      | 10                   |

|   |        | <ul><li>2.2.1 DQ Overview</li><li>2.2.2 Plant Characterization</li><li>2.2.3 PI Current Control</li><li>2.2.4 Phase Locked Loop</li></ul> | n    | 11<br>13<br>17<br>22 |

|   | 2.3    | Simulation Results                                                                                                                        |      | 28                   |

| 3 | HARDW  | ARE TESTING                                                                                                                               |      | 33                   |

|   | 3.1    | Programmable Source                                                                                                                       |      | 33                   |

|   | 3.2    | Initial Testing                                                                                                                           |      | 36                   |

|   | 3.3    | Open Loop Testing                                                                                                                         |      | 38                   |

|   | 3.4    | Closed Loop Testing                                                                                                                       |      | 40                   |

| 4 | CONCL  | USION AND FUTURE W                                                                                                                        | VORK | . 48                 |

| 5 | BIBIOL | OGRAPY                                                                                                                                    |      | 49                   |

## Page

# LIST OF FIGURES

| <u>Figure</u> | 2                             | <u>Page</u> |

|---------------|-------------------------------|-------------|

| 1.1           | WESRF BPA Lab Project Grid    | <br>5       |

| 1.2           | Schematic of WESRF Lab Set-up | <br>6       |

| 2.1           | Top Level Block Diagram       | <br>9       |

| 2.2           | Programmable Source Block     | <br>9       |

| 2.3           | System Controller             | <br>11      |

| 2.4           | DQ Projections                | <br>12      |

| 2.5           | DQ Transformations            | <br>12      |

| 2.6           | Reactor – System Plant        | <br>13      |

| 2.7           | Control Topology              | <br>18      |

| 2.8           | Fast Controller Design        | <br>20      |

| 2.9           | Slow Controller Design        | <br>21      |

| 2.10          | Current Controller            | <br>21      |

| 2.11          | Phase Locked Loop             | <br>23      |

| 2.12          | PLL Controller Design         | <br>25      |

| 2.13          | PLL Locking onto Frequency    | <br>26      |

| 2.14          | PLL Vq Lock                   | <br>26      |

| 2.15          | Wrapped theta d               | <br>27      |

| 2.16          | Commanded Power, Fast Control | <br>29      |

| 2.17          | Commanded Power Slow Control  | <br>29      |

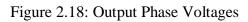

| 2.18          | Output Phase Voltage          | <br>30      |

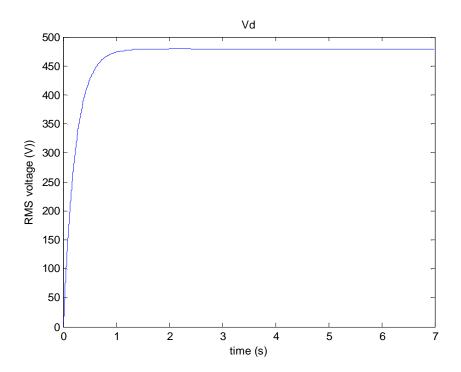

| 2.19          | Vd, Fast Control              | <br>30      |

# LIST OF FIGURES (Continued)

| Figure | 2                               |   | Page |

|--------|---------------------------------|---|------|

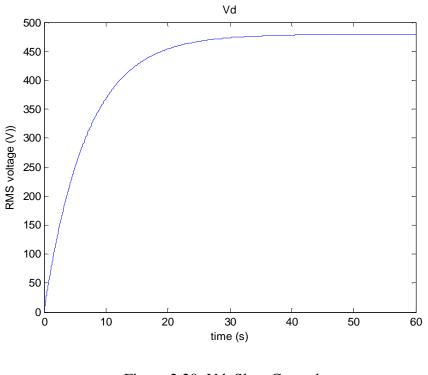

| 2.20   | Vd, Slow Control                |   | 31   |

| 2.21   | Output Current                  |   | 31   |

| 2.22   | Commanded Power, Pulse input    |   | 32   |

| 2.23   | Id and Iq, Pulsed Input         |   | 32   |

| 3.1    | Current Amplifier               |   | 34   |

| 3.2    | Current Amplifier Board         |   | 35   |

| 3.3    | Programmable Source Linearity   |   | 35   |

| 3.4    | Integrators with Reset          |   | 37   |

| 3.5    | Slowed PLL                      |   | 39   |

| 3.6    | Slowed PLL Short Scale          |   | 39   |

| 3.7    | Phase Currents, Pdesired $= 0$  |   | 40   |

| 3.8    | Commanded and Measured Voltage  | s | 41   |

| 3.9    | Phase Currents, Power Commanded |   | 42   |

| 3.10   | Slow Controllers, 20W           |   | 43   |

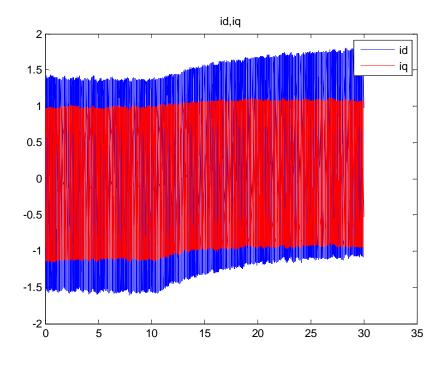

| 3.11   | Id and Iq Current, 20W          |   | 44   |

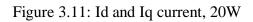

| 3.12   | Id and Iq currents, short scale |   | 44   |

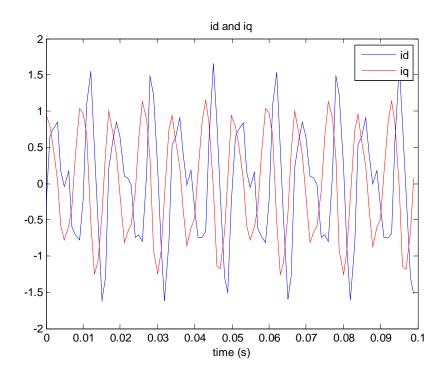

| 3.13   | Filtered Vd in per unit         |   | 44   |

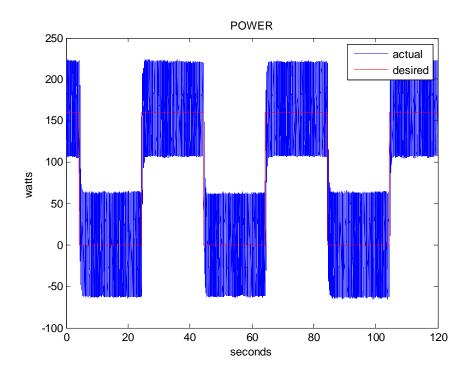

| 3.14   | Faster Controller, Pulse Input  |   | 46   |

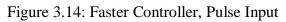

| 3.15   | Id and Iq with $P = 160W$       |   | 46   |

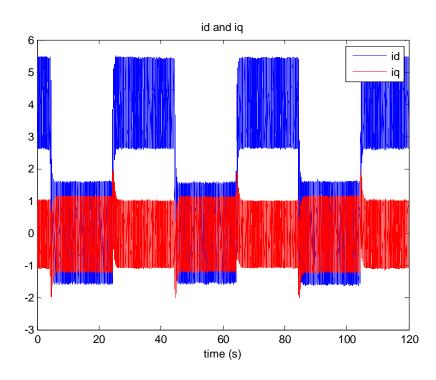

| 3.16   | Close-up of Pulse Power         |   | 47   |

# LIST OF TABLES

| <u>Table</u> |                                | Page   |

|--------------|--------------------------------|--------|

| 2.1          | Currrent Design Values Summary | <br>20 |

| 2.2          | PLL Design Values Summary      | <br>24 |

#### A High Power Emulation of a Wind Farm

#### Chapter 1 – INTRODUCTION

#### 1.1 Background

Wind is a variable quantity in both space and time. This variability is amplified through the relationship of wind power to the cube of the wind's speed. As more wind farms are connected to the grid, the variable nature of wind energy begins to influence grid stability. The variable nature of wind energy also requires the presence of spinning reserve, such as gas turbines as backup generation, which keeps the cost of wind energy high. The projected economic limit of wind penetration is about 20% of system capacity [1]. However, increasing demand for energy and decreasing supply of fossil fuel increases the growth of wind energy [2]. The application of energy storage technologies could smooth the output power from wind farms, making it more feasible to have a higher percentage of wind generated electricity.

#### 1.1.1 Energy Storage

Energy storage technologies such as batteries, flywheels, supercapacitors, SMES and pumped hydro could decrease the variability of wind farm output and decrease required spinning reserve. The fitness of the various energy storage technologies to mitigate output variability of wind farms depends on a web of physical characteristics and economic constraints. Key characteristics to consider are: instantaneous power output, total energy capacity, lifetime, and efficiency. In addition, operating and capital costs, and environmental safety must be studied. Each of these technologies has unique discharge characteristics that lend themselves to different situations. Supercapacitors and flywheels are best used when energy storage is required on a short timescale; batteries are better suited for longer term storage. Where locations allow, pumped hydro could be a renewable form of long term, slow ramping energy storage. A mix of these technologies may yield a more optimal solution.

There are many different types of batteries available for commercial sized energy storage. Rechargeable batteries ubiquitous in everyday devices, such as lithium ion and NiCd, have disadvantages in key areas that prevent them from being used as bulk energy storage. For example, lithium ion batteries suffer from shortened lifespan when discharged deeply. NiCd batteries, although free from deep cycling issues, have relatively low efficiencies. Sodium-sulfur batteries (NaS) have been demonstrated for use in power systems projects in Japan for decades. However, these batteries require constant heating, which affects their long term performance. The batteries mentioned so far are static batteries, and store energy in the electrode structure [3,4]. Flow cell batteries generally consist of two tanks of electrolytes separated by a membrane and pumped through a reactor. Flow cell batteries can store large amounts of energy, have a long lifetime, high efficiency, low operating costs, and smaller environmental impact due to possible recycling of certain components. Due to these factors, flow cell batteries may be a good choice for integrating into power systems with large wind penetration [3].

There are many varieties of flow cell batteries; some examples include vanadium redox, zinc bromine, and polysulfide/bromine (Regenesys batteries). The main disadvantage of flow cell batteries is lifespan depreciation due to charge cycling. However, main components of the batteries can be replaced individually to extend their lifetime for low cost. Zinc bromine batteries in particular have been highlighted in the literature as a good potential bulk rechargeable energy source due to low cost modular components and high energy density [5].

Superconducting magnetic energy storage (SMES) holds energy in the magnetic field of a superconducting coil. Although SMES has a fast response time with very high efficiency, it is a new technology with high associated cost. Supercapacitors are another nascent technology that has the potential to provide energy storage with rapid response time. Flywheels are a more mature technology for bulk energy storage that have the attractive characteristics of long cycle life, high efficiency, and quick response time. Large scale flywheel systems energy storage systems have been tested in locations in California, USA at 100kW levels [4]. Pumped hydro is a mature technology for utility scale power regulation. The major hurdles associated with hydro are topographic constraints, water levels set by environmental factors to protect native fish species, and response time. Combing a pumped hydro resource with a fast response technology and batteries would yield an optimal mix of energy storage characteristics for smoothing power variability [4].

#### 1.1.2 Scope of Thesis

BPA has funded a study at OSU involving the investigation of energy storage to control and smooth wind energy. An integrated system of energy storage devices and a wind farm will be modeled in Matlab/Simulink with a variety of control schemes. The results of the modeling will be applied hardware for model verification. In this thesis, a scale model of the wind farm component of the project is modeled and experimentally confirmed.

The physical system is tested in a real time environment using dSPACE and the high power lab equipment at OSU. The wind farm is modeled in-the-hardware-loop with a three-phase 120kVA programmable source controlled by an 1103 dSPACE unit with a Simulink control system. The programmable source is directed to produce a power signal profile that follows the scaled down output of a real wind farm.

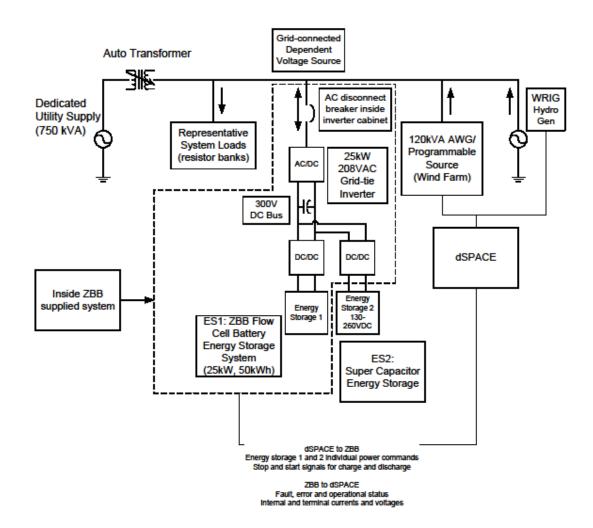

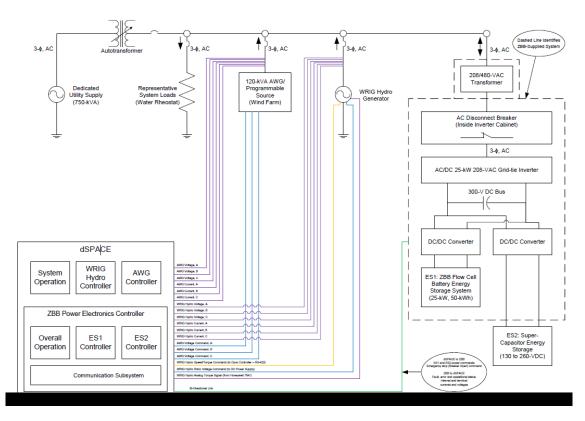

The BPA project grid is shown in figure 1.1. The autotransformers, powered by the lab's dedicated utility supply, will act as the grid. At the culmination of the BPA project the bus will be connected to the "wind farm" and several energy storage technologies, including a flow battery, supercaps, and an emulated hydro resource. Figure 1.2 shows the signal level project grid. The phase currents and line voltages at the output of the programmable source and the line voltages at the grid will be measured and used in control system to ensure a stable power output.

#### WESRF BPA Wind Project Grid

Figure 1.1: WESRF Project Grid

#### WESRF BPA Wind Project Grid

Figure 1.2: WESRF Grid Schematic

#### 1.2 Wind Farm Modeling Literature Review

With the increasing amount of wind energy connected to the grid, the development of accurate wind farm models are needed to represent the behavior of grid connected wind farms. The literature contains much research concerning the control of wind energy conversion systems (WECS) and simulation of high power wind energy parks for power stability studies [6, 7, 8, 9]. An important aspect to these simulation studies is the mathematical complexity of completely modeling a large wind farm, with all internal and external electrical networks. A method for lowering the complexity of wind farm models is developed in several papers by mathematically aggregating a large number of wind turbines into an equivalent model. These lower order models require less computation time. The interaction of aggregated wind generators or wind farms with energy storage systems in hardware does not seem to be a well documented area of study. Lower power WECS are more easily studied with hardware in experimental laboratory investigations using DC machines. The dynamics of single wind turbines with associated energy storage devices have been studied in a laboratory setting [10].

#### Chapter 2 – SYSTEM MODEL

The wind farm must be modeled at the current and voltage level for control design. This low level model cannot be simulated in real-time due to memory limitations. The low level modeling is used to demonstrate stability.

#### 2.1 Simulation Model

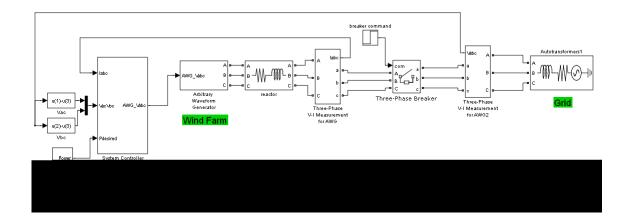

The model used in the lab testing consists of an 1103 dSPACE unit, the programmable source, and a three-phase transformer to act as a stiff grid. In Simulink, the wind farm power output data is hosted in a lookup table, which is fed into the control block. The resulting commanded signal is routed into the AWG block, which consists of three controlled voltage sources and some impedance, all SimPower blocks. The output of the AWG is measured in a three-phase VI measurement block, and fed back into the overall control block to close the loop, as shown in figure 2.1. In the Simulink, the grid is modeled as a small impedance at 480V and grounded on the end. Stiff grids have small impedance in order to be resistant to changes in voltage and currents. Utility grids are stiff; if a component connected to the grid suddenly changes in voltage or current, the voltage and frequency of the grid will not react since the relative impedance of the attached component is small.

The control system was designed with line-to-line voltages in order to reduce the required number of measured signals, since the dSPACE breakout board has a limited number of analog inputs.

Figure 2.1: Top Level Block Diagram

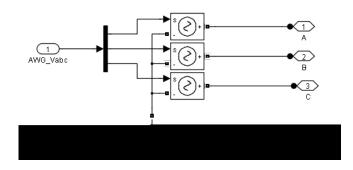

The programmable source/AWG is modeled by three controllable voltages sources, one per phase, as seen in figure 2.2. The source sets its output to regulate around its internal impedance. There is a scaling factor between Simulink, the dSPACE outputs, and the programmable source input. Simulink outputs a signal between -1 and 1, which dSPACE scales to -10 and 10 peak to peak. The programmable source takes an input from -10 to 10V peak to peak and outputs 0 to 326Vrms.

Figure 2.2: Programmable Source Block

#### 2.2 Controller Design

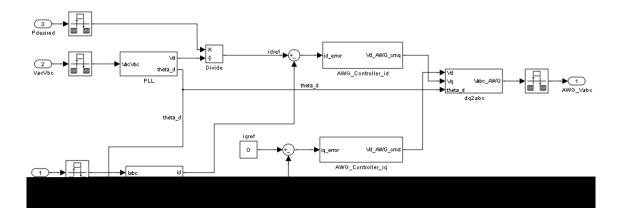

To ensure a stable output, the AWG is controlled with a closed loop scheme through dSPACE and Simulink. The space voltage vector of the AWG must be transformed into a synchronous reference frame for vector control. The control plant determines command signals in two-phase dq space, which are transformed into threephase sinusoidal signals to be scaled and implemented by dSPACE. Closed-loop dq control means that the output should have zero steady state error. The voltages are taken into the dq reference frame with the help of a phase-locked loop (PLL). The output of the PLL gives the angle  $\theta$  between the reference voltage Vd and the virtual phase A winding. This angle is then used in subsequent vector transformations.

The input to the overall control scheme is a desired power, which is divided by Vd to obtain a reference current. The measured output current is fed back into the system controller and compared to the reference current to generate an error signal. The current error is regulated to zero by PI controllers in the id and iq control blocks. These control blocks output a voltage signal, which the programmable source will produce at its output. The output current will regulate appropriately so that Pout = Pdesired = I\*V. The block diagram of the overall system controller is shown in figure 2.3.

Figure 2.3: System Controller

### 2.2.1 DQ Overview

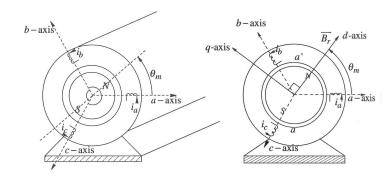

The synchronous reference frame is a projection of a three-phase system onto two-phase. This transformation brings a sinusoidal signal into the dc realm, reducing the complexity of the input signal and control variables. When the signals are in dc, steady state errors and response time are easier to control. The concept of dq control is often used in motor design, with the d-axis aligning with the virtual phase A winding, as seen in figure 2.4. Typically, the id current is used to control Vd, and iq is used to control Vq. The mathematical relationship between the dq windings derived in Mohan [11] was used in the abc to dq transformations for this controller. The transformation equations are shown in figure 2.5.

Figure 2.4: DQ Projections [11]

$$\begin{bmatrix} i_{sd}(t) \\ i_{sq}(t) \end{bmatrix} = \sqrt{\frac{2}{3}} \begin{bmatrix} \cos(\theta_{da}) & \cos(\theta_{da} - \frac{2\pi}{3}) & \cos(\theta_{da} + \frac{2\pi}{3}) \\ -\sin(\theta_{da}) & -\sin(\theta_{da} - \frac{2\pi}{3}) & -\sin(\theta_{da} + \frac{2\pi}{3}) \end{bmatrix} \begin{bmatrix} i_a(t) \\ i_b(t) \\ i_c(t) \end{bmatrix}$$

Figure 2.5: ABC to DQ Transformation [11]

A similar transformation is used to transform the line voltages into Vd and Vq. In this reference frame, Vq represents reactive power, which should be regulated to zero, and Vd represents the RMS voltage of the sinusoidal input.

#### 2.2.2 Plant Characterization

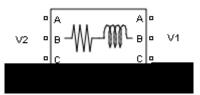

Since the programmable source sets its output voltage to the commanded voltage, the reactor is needed for separation between the measured voltage and the commanded voltage. Therefore the control system must be designed around the impedance of the reactor, which is the system plant. The reactor used is an MTE CORE three-phase line reactor with 1.2mH, and 65W loss at 45A. The percent impedance of the reactor can be

calculated by:  $\% TX_{imp} = \frac{\&L_{TX}}{|Z_{TX}|} x100 = 5\%$ , where  $|Z_{TX}| = \frac{|V_{LL}|^2}{|S_T|}$ . The reactor is modeled

by its impedance values in a SimPower block, as seen in figure 2.6.

Since the reactive impedance is much larger than the resistive impedance, the voltage drop across the reactor due to resistance is much smaller than the voltage drop due to inductance. Assuming the voltage phasors on the input and output of the reactor are in phase with each other, increasing the voltage will increase the current quadrature to the voltage. This relationship can be seen by inspection in the transfer functions associated with the reactor in equations 2.10-2.13.

Figure 2.6: Reactor - System Plant

To derive the transfer function of the plant, assume V1 is the voltage on the output of the reactor, and V2 is the voltage on the input of the reactor, which is connected to the terminals of the programmable source. Taking the voltage drops across the reactor, where vs stands for space vector and  $\theta$  is the angle between the d-axis and the virtual phase A winding.

$$V_{1_{SV}} + R * i_{SV} + L * \frac{d}{dt}(i_{SV}) = V_{2_{SV}}$$

2.1

$$V_{1_{sv}} = \sqrt{\frac{3}{2}} * \left( V_{1_d} + i * V_{1_q} \right) * e^{i * \theta_{da}}$$

2.2

$$i_{sv} = \sqrt{\frac{3}{2}} * (i_d + i * i_q) * e^{i * \theta_{da}}$$

2.3

$$\frac{d}{dt}(i_{sv}) = \sqrt{\frac{3}{2}} * \left(\frac{d}{dt}(i_d) + i * \frac{d}{dt}(i_q)\right) * e^{i*\theta_{da}} + i * w_d * \sqrt{\frac{3}{2}} * \left(i_d + i * i_q\right) * e^{i*\theta_{da}}$$

2.4

$$(V_{1d} + i * V_{1q}) + R * (i_d + i * i_q) + L * \frac{d}{dt}(i_d + i * (i_q) + i * w_d * L * (i_d + i * i_q)$$

=  $V_{2d} + i * V_{2q}$  2.5

$$V_{1d} + R * i_d + L * \frac{d}{dt}(i_d) - w_d * L * i_q = V_{2d}$$

2.6

$$V_{1q} + R * i_q + L * \frac{d}{dt}(i_q) + w_d * L * i_d = V_{2q}$$

2.7

$V_{\mathbf{1}_{\vec{a}}}$  and  $V_{\mathbf{1}_{\vec{a}}}$  are ideally constant, and so can be dropped for linearization. Packaging equations 2.6 and 2.7 into the standard matrix state space form of equation 2.8 yields:

$$\dot{x} = Ax(t) + Bu(t)$$

$$\frac{d}{dt} \begin{pmatrix} id \\ iq \end{pmatrix} = \frac{1}{L} * \begin{bmatrix} -R & W_{cl} * L \\ -W_{cl} * L & -R \end{bmatrix} * \begin{bmatrix} id \\ iq \end{bmatrix} + \frac{1}{L} * \begin{bmatrix} 1 & 0 \\ 0 & 1 \end{bmatrix} * \begin{bmatrix} V_{2d} \\ V_{2q} \end{bmatrix}$$

2.9

Equation 2.9 encompasses the relationship between the two states id and iq and the two inputs Vd and Vq. Information about the system's open loop stability can be gathered from the eigenvalues of the state A matrix in equation 2.9, which are:  $-8.92 \pm i*376$ . 99. Since the reactor system's eigenvalues have a negative real part, the uncontrolled system is stable and will not have an unbounded output. However, since the system is second order with two undamped complex poles, the open loop step response oscillates significantly until reaching steady state.

Matlab's 'tf' function is used to determine the system's transfer functions. The transfer function from Vd to -iq has a much higher gain than the transfer function from Vd to id, which means that a change in input from iq will have a much larger impact over Vd than Vq. This makes the Vd voltage have more control over the –iq current, and the Vq component have more control over the id current. Dq analysis for electromechanical machines typically has id controlling Vd and iq controlling Vq.

28

$$\frac{V_{2_d}}{l_d} = \frac{833.3s + 7430}{s^2 + 17.83s + 1.422E5}$$

2.10

$$\frac{V_{2_d}}{i_{\sigma}} = \frac{-3.142E5}{s^2 + 17.83s + 1.422E5}$$

2.11

$$\frac{V_{2_q}}{l_d} \frac{3.142E5}{s^2 + 17.83s + 1.422E5}$$

2.12

$$\frac{V_{2_q}}{l_q} = \frac{833.3s + 7430}{s^2 + 17.83s + 1.422E5}$$

2.13

The poles of the transfer functions are the eigenvalues of the state A matrix, and give the same information about the system's open loop response. The denominators of the transfer functions are the system's characteristic equation, and are of the form:

$$s^2 + 2 * w_n * \zeta * s + wn^2$$

2.14

In equation 2.14, the parameter  $w_{re}$  is the natural frequency of the system and describes the time scale of the system response. The parameter  $\zeta$  is the damping factor, which determines the shape of the system response [12]. The reactor's characteristic

equation possesses the desired natural frequency of 377 rad/s and a very small damping constant. Feedback control can stabilize the closed loop system, and regulate the rise time and overshoot.

It can be seen that the system is controllable by looking at the controllability matrix formed from the A and B matrices of equation 2.9.

Controllability matrix =

$$\begin{bmatrix} B & AB \end{bmatrix} = \begin{bmatrix} 830 & 0 & -7430 & 314160 \\ 0 & 830 & -314160 & -7430 \end{bmatrix}$$

2.15

The controllability matrix in equation 2.15 has a rank of 2, so it is full rank and the system is controllable. This means that the plant can be brought from any initial state to any desired state in a finite amount of time [13]. With this information known, a control system to improve the behavior of the system states, the id and iq currents, can be designed.

#### 2.2.3 PI Current Control

The id and iq currents are controlled separately with a proportional-integral controller designed using Matlab's single-input single-output design GUI. The controller is placed in series with the system plant, with the feedback from the output used to generate an error signal, as seen in figure 2.7.

Figure: 2.7: Control Topology [13]

The desired outcome for this control system is zero steady state error, which in this case is the difference between a reference value and the system's measured output current. The output y(t) for this control topology is the sum of a term proportional to the error current plus a term proportional to the integral of the error current. The integral term brings the steady state error to zero by keeping track of the residual error over time. The transfer function of a PI controller looks like:

$$G_{\sigma}(s) = \frac{K_i \left(1 + \frac{K_p}{K_i} s\right)}{s}$$

2.13

where Ki is the integral gain and Kp is the proportional gain. Generally, increasing Ki reduces the time it takes the system to reach steady state and will eliminate steady state error. However, increasing Ki also tends to decrease the stability of the system due to an additional phase lag, so a controller must have an appropriate balance between response time and stability. Stability is commonly expressed in terms of stability margins, which are measures of the distance between the Nyquist curve and the critical point. Stability margins are determined from the Bode plot of the closed loop system. The gain margin is

a measure of absolute stability, and is calculated from the inverse of the gain where the phase crossover frequency is at -180 degrees. The phase margin is a measure of relative stability, and is calculated from the gain crossover frequency plus 180 degrees. Gain and phase margins can reveal how close a system is to instability [12].

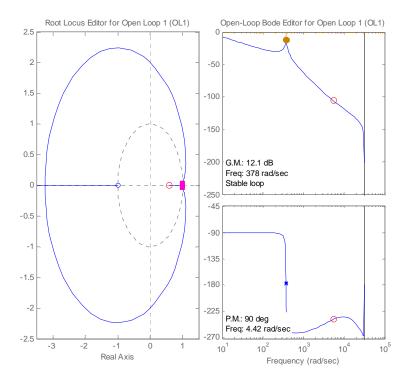

Since our plant is second order, introducing a PI controller will make the closedloop system third order. Our plant has two complex poles, which lead to oscillatory open loop behavior. The plant and controllers are brought into discrete time using Matlab continuous-to-discrete conversion function to match the desired discrete Simulink topology. For the discrete system, the closed loop poles must reside inside the unit circle for stability.

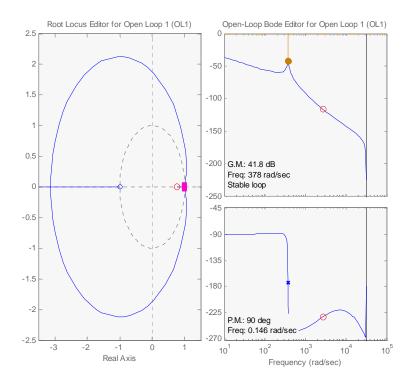

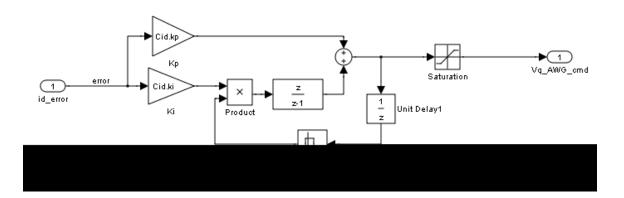

The first controller design is very slow, to be used for initial testing. The gain and phase margins are within standard safety ranges, as seen in figure 2.8. The second controller is faster with a larger crossover frequency and smaller gain and phase margins, as seen in figure 2.9. A summary of the design values appears in table 2.1. Both the id and iq controllers were designed with saturation protection; in case the system was unstable, the controllers will not output values above the prescribed limit. In addition to this protection, the AWG will fault and open its output for both over voltage and over current situations. The additional delay present in the protection interval branch seen in figure 2.10 is required by Matlab to avoid algebraic loops.

|                 | Slow Controller | Fast Controller |

|-----------------|-----------------|-----------------|

| Кр              | 2.09E-5         | 0.002726        |

| Ki              | 6.6182E-6       | 2E-4            |

| Phase crossover | 0.165 rad/s     | 4.22 rad/s      |

| Phase margin    | 90 degrees      | 90 degrees      |

| Gain margin     | 41.8 dB         | 12.1 dB         |

Table 2.1: Current Design Values Summary

Figure 2.8: Fast Controller Design

Figure 2.9: Slow Controller Design

Figure 2.10: Current Controller

#### 2.2.4 Phase Locked Loop

Grid synchronization is an important part of grid connection. The output of a generator or other power source must match the phase of the grid supply prior to connection. The phase angle of the grid voltage vector is used to synchronize the control variables of a connected system. There are many different techniques to achieve synchronization. A basic method involves detecting the zero crossings of the grid voltage to obtain phase information. The drawback to this method is that the phase relations can be detected at most every half cycle, which leads to slow performance. Additionally, noise can affect the zero crossing detection and lower the quality of the synchronization [15].

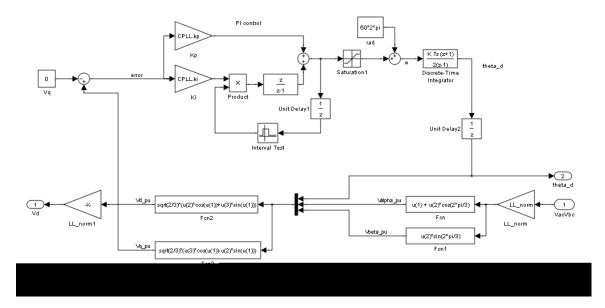

Phase locked loops are a more robust method for grid synchronization. Threephase systems can use a synchronous reference frame phase-locked loop. There are drawbacks to this method when voltage imbalances are present in the input signal, which can cause a double frequency ripple in the PLL. However, the PLL involved in this project will operate during normal operating conditions. The phase angle of the lab grid will be used in the synchronous reference transformations of the necessary control variables [16]. In the synchronous frame, the input signal is an easy to control dc value. PI control is used to regulate the Vq component to zero, which locks the reference to the voltage vector phase angle. The frequency is integrated to obtain the phase angle  $\theta_{d}$ , which is the angle between the d-axis and the phase virtual A winding. This angle is then used for the abc to dq transformations. The designed PLL block is in per unit, with line to line AC and BC voltages. A block diagram of the PLL is shown in figure 2.11.

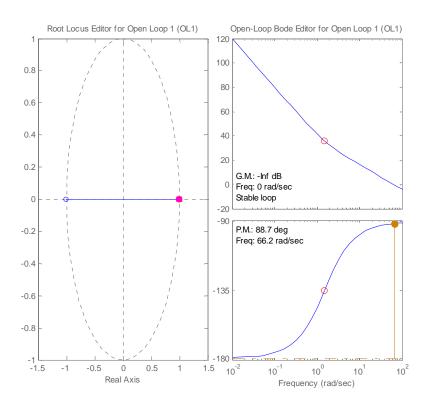

Figure 2.11: Phase Locked Loop

The dq current commands are determined by a PI (proportional-integral) controller. The controller gains are calculated in Matlab's sisotool in a similar manner to the current controller gains. Generally, the proportional gain decreases the error convergence time, and the integral gain ensures no steady state error and increases the rise time, depending on the Kp/Ki ratio. The PLL was designed around a nominal frequency of 10 Hz, with appropriate gain and phase margins. The plant of the PLL system is the loop integrator. A summary of the PLL design values appears in table 2.2, and the designed phase and gain margins appear in figure 2.12.

Table 2.2: PLL Design Values

|                 | PLL        |

|-----------------|------------|

| Кр              | 66.14      |

| Ki              | 1E-2       |

| Phase crossover | 66.2 rad/s |

Figure 2.12: PLL Controller Design

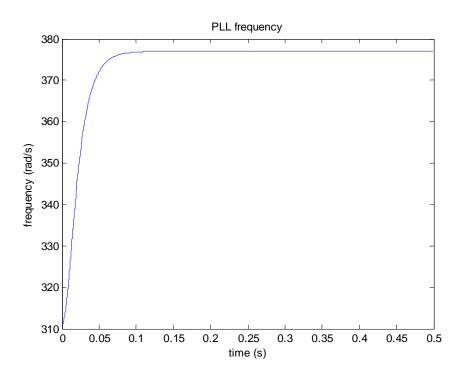

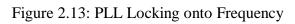

In the simulation, there are spikes in the frequency due to solver and digitization implementations that may not occur in the real world hardware environment. There is some behavior in the steady state theta output that is dependent on the solver type. A stiff solver is used due to the "bounce" behavior in the power output. The trapezoidal solver is faster, but has more transient behavior. The Euler solver (ODE1) returned the most believable results. Figure 2.13 shows the PLL locking onto the input frequency of 377 rad/s in less than a tenth of a second, and figure 2.14 shows the Vq component regulating to zero.

Figure 2.14: PLL Vq Lock

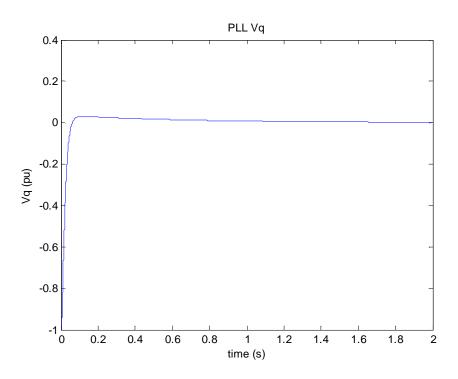

The angle  $\Theta_{a}$  from the output of the integrator is wrapped to keep it between 0 and 2\*pi, as shown in figure 2.15. This angle follows the synchronously rotating space vector.

Figure 2.15: Wrapped theta

### 2.3 Simulation Results

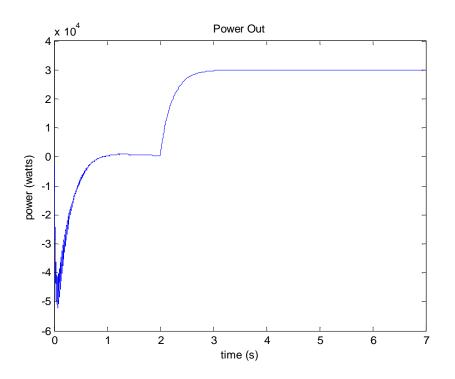

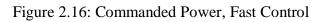

Both the slow and fast controller were simulated with a step response turned on at 2 seconds. The fast controller responded to the desired power level in a few seconds, as seen in figure 2.16. The slow controller reached steady state in around 30 seconds, as seen in figure 2.17. The simulation results included transient behavior before the step input which changed depending on the solver type.

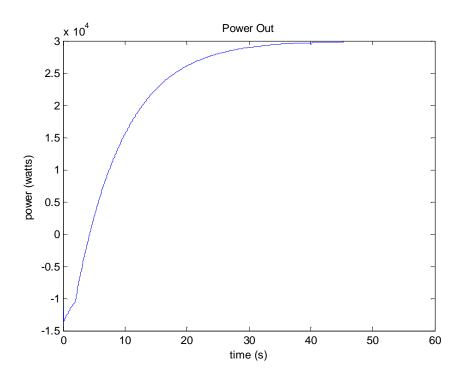

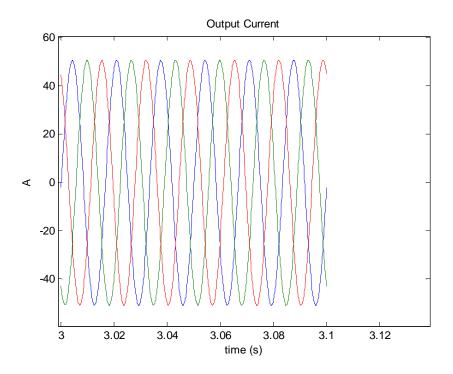

As seen in figure 2.18, the output phase voltage regulates to a peak value of 678V, which corresponds to 480Vrms. In Figure 2.19, Vd of the fast controller settles into the expected steady state value of 480V, which corresponds to the RMS of the input. The slow controllers give the same steady state results in figure 2.20. The output phase currents are shown in figure 2.21.

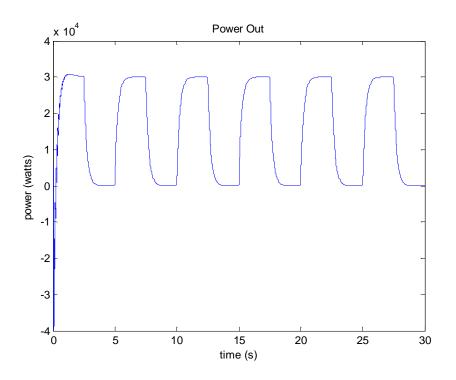

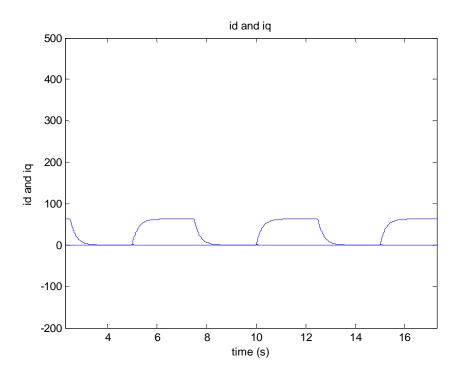

A pulsed desired power signal was also tested with the faster controller gains. In figure 2.22, the pulsed waveform is distinct, with clipped edges from the rise time. The iq current is regulated to zero, and the id current shows the expected pulse waveform, as shown in figure 2.23.

Figure 2.17: Commanded Power, Slow Control

Figure 2.19: Vd, Fast Control

Figure 2.21: Output Curren

Figure 2.22: Commanded Power, Pulsed Input

Figure 2.23: Id and Iq, Pulsed Input

#### Chapter 3 – Hardware Testing and Results

#### 3.1 Programmable Source and AWG

The Behlman programmable source and embedded Arbitrary Wave Generator is a 120kVA three-phase power source which can provide a variable amplitude and frequency voltage output. The programmable source has a multi-tapped input transformer, one solid state transformer per phase, and a step-up output transformer for each phase. The current limit is 144A rms per phase, with a peak voltage of 0-460V instantaneous line to neutral and a frequency range of 45 Hz to 2 kHz. [17, 18]. In order for the output voltage to be commanded from the outside, the source must be in programmable mode. The commanded programmable source voltage is the voltage at the output terminals, so the transformer impedance is taken care of by internal closed loop controls. The embedded arbitrary waveform generator can drive the source's input, but will not be used for this work.

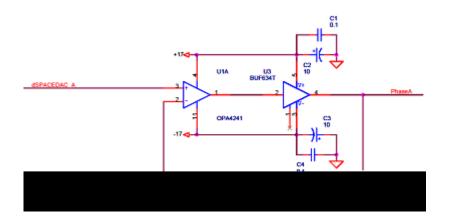

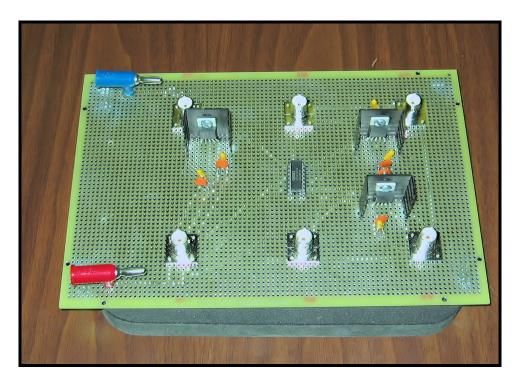

The programmable source is used to produce a scaled power signal of given wind farm output data, acting as the "wind farm" for the project. In this experiment, the commanded voltage signal comes from a dSPACE 1103 unit. The dSPACE breakout box can supply  $\pm$  10 V and 5 mA. The dSPACE voltage range corresponds to the expected input range of the AWG, 10V = 480Vrms at the output. However, the programmable source input requires a signal to be provided with several hundred milliamps of current, which the dSPACE board cannot provide. A current amplifier with unity voltage gain was built to boost the current to the necessary level. A 250mA high speed buffer, the BUF634 chip, was chosen due to its high output current and fast response. This chip was designed to work in the feedback path of an op amp; the OPA241 op amp was chosen to provide the pre-amplification. Additionally, the BUF634 buffer chips were heat-sinked in order to maintain high performance during long periods of use. Surface-mounted BNC terminals were soldered to the vector board in order to provide solid input and output connections. Figure 3.1 shows the final current amplifier schematic, and figure 3.2 shows the board connections.

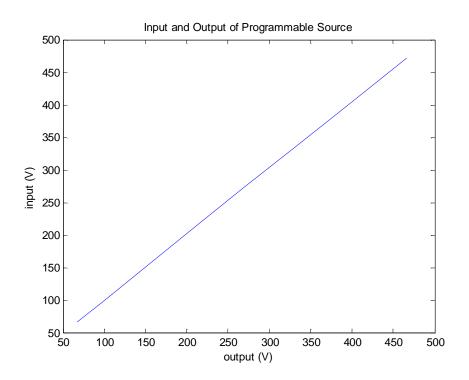

The linearity of the programmable source was confirmed by comparing input and output measurements. The data in figure 3.3 have an R squared value of 99% for a linear fit.

Figure 3.1: Current Amplifier

Figure 3.2: Current Amplifier Board

Figure 3.3: Programmable Source Linearity

# 3.2 Initial Testing

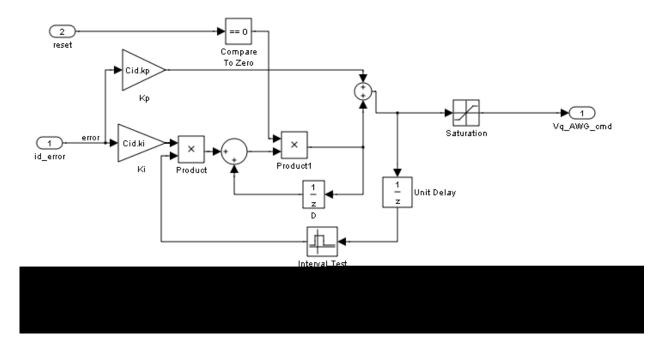

The lab system was tested in stages, starting at low voltage for safety reasons. The current controller topology was reconfigured in order to insert an external reset. The relationship between the input and output of the integral branch of the original PI controller is:

$$\frac{y}{x} = \frac{z}{z-1}$$

3.1

which is mathematically equivalent to

$$\frac{1}{1-z^{-1}}$$

Rearranging equation 3.2 yields:

•

$$y = x + yz^{-1}$$

3.3

The relationship of equation 3.3 is expressed in the Simulink block diagram shown in figure 3.4. Inserting a zero after the summing junction resets both the output and the internal state of the integrator. This reset function allows the current controllers to be turned on manually, which closes the loop, for the initial testing procedure.

20

Figure 3.4: Integrators with Reset

Since the autotransformers provide power to the programmable source, they could not be used for low voltage testing. Instead, a synchronous generator rotating at 1200 RPM and was used as the stiff grid. Unfortunately, the generator did not provide a stiff enough voltage for the control system, although the PLL was able to lock onto the frequency of the generator. When the loop was closed the current pushed into the generator caused the generator voltage to wobble, which made the frequency out of the PLL wander away from the required steady 60 Hz. Under these conditions the current controllers could not stabilize the system. The rest of the hardware testing was performed with a three-phase variac operating at 40V.

#### 3.3 Open Loop with Variac

The system was started with both the grid and reactor output disconnected but operating at 40V. Differential voltage probes were used to measure the variac voltage as a reference for the PLL. The integrators in the current controllers were turned off, and a desired Vd and Vq were input manually. With the breaker closed, it was confirmed that an increase in Vd led to a decrease in the iq current, and an increase in Vq led to an increase in id current.

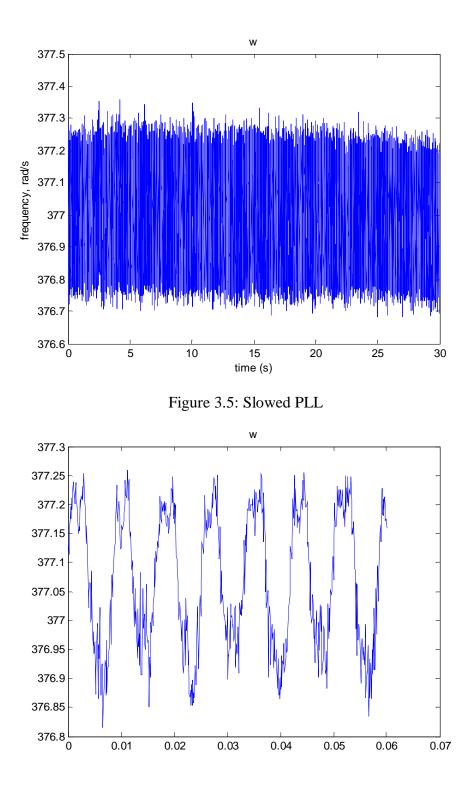

There was some sinusoidal behavior present in the PLL frequency, which could indicate imbalance in the grid voltage. The PLL gains were redesigned with a lower crossover frequency so that the PLL would not respond to the wobble in the grid space vector. The slower and less sensitive PLL provided a more solid frequency signal, shown in figure 3.5 and figure 3.6. When the PLL was locked onto the grid voltage with the proper sign, the breaker was flipped and the integrators were turned on, closing the loop.

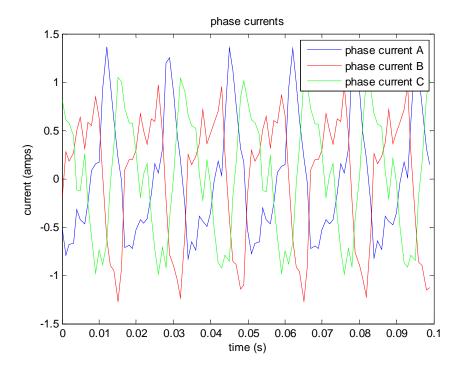

The phase currents were measured between the programmable source and the variac when the loop was closed. Although no power was commanded, the current probes did measure some current, as seen in figure 3.7. This may be caused by the small difference in voltage between the system output and the voltage of the variac, which must be adjusted by hand. The waveforms have some notches which may indicate the involvement of the programmable source's power electronics. The notches may occur as a result of the switches commutating the current.

Figure 3.6: Slowed PLL short scale

Figure 3.7: Phase Currents, Pdesired = 0

# 3.4 Closed Loop with Variac

When the loop was closed, a desired power was input to the system controller. Since the variac had a 15 Amp fuse, only a few amps were commanded for this proof of concept testing. This wind farm model will be used for future lab testing at 480V and 30KW, which will command 36A. The control system was tested with a desired power of 160 Watts.

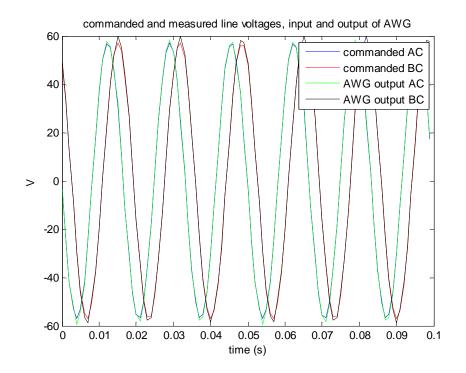

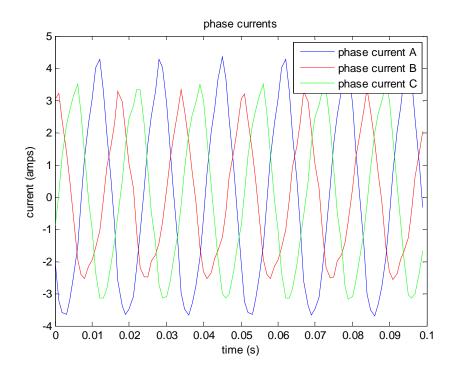

The commanded and measured line voltages matched well in phase and amplitude. Since the voltages were measured line-to-line, the AC and BC voltages were 60 degrees out of phase, as shown in figure 3.8. There was some peaking in the measured voltages at the output of the reactor. The variac may have some unwanted harmonics at low voltage levels. As more power was commanded and the current increased, the current waveforms shown in figure 3.9 became cleaner.

Figure 3.8: Commanded and Measured Line Voltages

Figure 3.9: Phase Currents when power commanded

The control system was tested with the slow current controllers at first. In case of instability, there is more time to close the breakers when the output changes slowly. The power was calculated as:

$$P = V_d * i_d + V_q * i_q \qquad 3.4$$

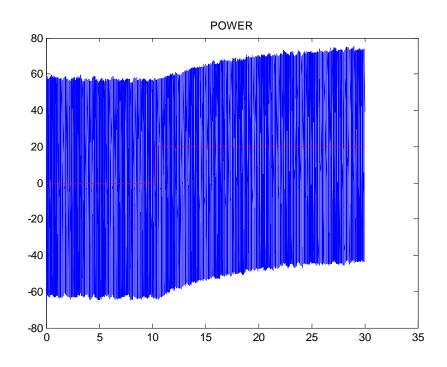

The average power level increased to the desired level with the slow controllers, in around 20 seconds, as seen in figure 3.10. The id current increased, and the iq current regulated around zero, which was the reference value. However, the current and power waveforms had a lot of associated noise. Even with no power commanded there was a lot of noise from the current waveforms. Figure 3.11 shows the id and iq current waveforms with the associated noise as the desired power signal increases. Figure 3.12 shows id and iq currents on the short scale. The noise in the id and iq currents has a sinusoidal patterns, with a frequency of a few hundred Hertz.

The Vd signal also had some noise. This signal was low pass filtered with a fast pole which would not interfere with the control behavior. However, filtering Vd did not improve the measured power signal. Figure 3.13 shows Vd before and after filtering.

Figure 3.10: Slow Controllers, 20W

Figure 3.12: Id and Iq currents, short scale

Figure 3.13: Filtered Vd in per unit

The system was also tested with the faster current controllers and a pulsed desired input power. The average measured power followed the commanded power, as seen in figures 3.14 - 3.16. Figure 3.16 shows a close-up of the pulsed power measure and desired waveforms. The envelope of the commanded power signal follows the desired power with a similar rise time and shape to the simulation in figure 2.22.

Figure 3.15: Id and Iq with P = 160

Figure 3.16: Closed of Pulsed Power

#### Chapter 4– Conclusion and Future Work

The synchronous control methodology used to control the active and reactive power was successful in simulation. The hardware testing demonstrated the stability of the closed loop current controllers and the ability of the PLL to lock onto the frequency of an external voltage vector. The noise associated with the power and current measurements prevented the controllers bringing the physical system to zero steady state error for an applied desired power. However, the average power was brought to the desired commanded level.

In order to follow a wind park power profile, the output power from the programmable source should be less noisy. Using the active current probes might yield less noisy measurements. Filtering the current measurements with a pole far away from the current controllers might be able to smooth out the current readings without interfering with the control action, which would clean up the power signal.

The next step in the testing procedure after resolving the noise issue is to step up the voltage to 480V and increase commanded power level. An appropriately sized breaker with remote signaling is needed in order to perform testing at a larger base voltage. It was very difficult to adjust the "grid" voltage and the output of the programmable source to exactly the same level; at larger base voltage values, the difference across the breaker before closing would be even larger. The ability to close the breaker from a distance would be an improvement on this experimental situation.

### BIBLIOGRAPHY

[1] David Milborrow. Renewable *Electricity and the Grid: The Challenge of Variability*, edited by Godfrey Boyle. Earthscan, London. 2007, pages 31-51.

[2] Millais C, Teske S. Wind Force 12: a blueprint to achieve 12% of the world's electricity from wind power by 2020. Greenpeace and European Wind Energy Association. <<u>http://www.ewea.org/03publications/WindForce12.htm></u>; May 2004.

[3] C. Ponce de Leon et al. "Redox Flow Cells for Energy Conversion." *Journal of Power Sources*. Vol. 160, Issue 1, September 2006, Pages 716-732.

[4] Bo Yang; Makarov, Y.; Desteese, J.; Viswanathan, V.; Nyeng, P.; McManus, B.; Pease, J. "On the use of energy storage technologies for regulation services in electric power systems with significant penetration of wind energy." *European Electricity Market*, 2008. *EEM* 2008. *5th International Conference on*. 28-30 May 2008 Page(s):1-6.

[5] T. Fuji, M. Kanazashi "Development of a Zinc Bromine Battery for Electric Power Storage" *Prog. Batteries Solar Cells* 1984, *5*, 331-338.

[6] Feijoo, A.E. Cidras, J. "Modeling of wind farms in the load flow analysis." Power Systems, IEEE Transactions on, Feb. 2000 Volume: 15, Issue: 1.

[7] L.M. Fernandez, J.R. Saenz and F. Jurado, "Dynamic models of wind farms with fixed speed wind turbines," *Renew Energy* **31** (8) (2006), pp. 1203–1230.

[8] .G. Slootweg and W.L. Kling, "Aggregated modelling of wind parks in power system dynamics simulations", *IEEE Power Tech Conf* **3** (2003), pp. 626–631.

[9] L.M. Fernandez, J.R. Saenz and F. Jurado, "Aggregated dynamic model for wind farms with doubly fed induction generator wind turbines", *Renew Energy* **33** (1) (2008), pp. 129–140.

[10] Christoph Saniter, Jörg Janning, Aurélie Bocquel. "Test Bench for grid code simulations for multi-MW wind turbines" *Power Electronics and Applications*, 2007 *European Conference* Date: 2-5 Sept. 2007. page(s): 1-10

[11] Mohan, Ned. *Advanced Electric Drives: Analysis, Control and Modeling using Simulink*. Minneapolis: MNPERE, 2001.

[12] Cha, Rosenberg, and Dym. *Fundamentals of Modeling and Analyzing Engineering Systems*., Cambridge University Press, 2000. pp.427

[13] Ogata, *Modern Control Engineering*, Prentice Hall, New Jersey 2002. pp. 779.

[14] Kuo, Benjamin C, and Farid Golnaraghi. Automatic Control Systems. New Jersey: Wiley, 2003.

[15] Limongi, L.R. Bojoi, R. Pica, C. Profumo, F. Tenconi, A. "Analysis and Comparison of Phase Locked Loop Techniques for Grid Utility Applications." Power Conversion Conference - Nagoya, 2007. PCC '07

[16] M. Karimi-Ghartemani, H. Karimi, and M. Iravani, "A Magnitude/Phase-Locked Loop System Based on Estimation of Frequency and In-Phase/Quadrature-Phase Amplitudes," *IEEE Transactions on Industrial Electronics*, Vol. 51, No. 2, pp. 511-517, April 2004.

[17] Behlman Electronics Inc, *Operating Manual: PA Plus series AC power source,* revision B, July 1996

[18] Matheson, E. von Jouanne, A. Wallace, A. "A remotely operated power quality test platform based on a 120 kVAfully programmable three-phase source." Industry Applications Conference, 2001. Thirty-Sixth IAS Annual Meeting. Conference Record of the 2001 IEEE, 30 Sep-4 Oct 2001, Volume: 2, On page(s): 1188-1195