#### AN ABSTRACT OF THE THESIS OF

<u>Haiqing Lin</u> for the degree of <u>Doctor of Philosophy</u> in <u>Electrical & Computer Engineering</u> presented on <u>May 8th, 1998.</u>

Title: <u>Multi-bit Delta-Sigma Switched-Capacitor DACs Employing Element-Mismatch-Shaping.</u>

|                    | Redacted for privacy |  |

|--------------------|----------------------|--|

| Abstract approved: |                      |  |

|                    | Richard Schreier     |  |

Delta-sigma modulators are currently a very popular technique for making high-resolution analog-to-digital and digital-to-analog converters (ADCs and DACs). Most delta-sigma modulators in production today employ single-bit quantization because a 1-bit DAC is inherently linear, whereas a multi-bit DAC is not. Were it not for this drawback, the use of multi-bit quantization would improve a delta-sigma modulator's performance by increasing the modulator's resolution or increasing the modulators's bandwidth, while at the same time whitening the quantization noise and improving modulator stability. This thesis explores the element-mismatch-shaping technique, which attenuates the noise caused by static element mismatch in a multi-level DAC by a method similar to delta-sigma modulation.

Existing element-matching techniques are reviewed and some analytical and architectural work related to the realization of mismatch-shaping logic is presented. A custom switched-capacitor (SC) DAC is used to verify various element mismatch-shaping algorithms. Experiments show that mismatch-shaping can reduce harmonic distortion by up to 30 dB.

©Copyright by Haiqing Lin May 8, 1998 All Rights Reserved

# Multi-bit Delta-Sigma Switched-Capacitor DACs Employing Element-Mismatch-Shaping

by

Haiqing Lin

A THESIS

submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Completed May 15, 1998 Commencement June 1998

# Doctor of Philosophy thesis of Haiqing Lin presented on May 8, 1998

| APPROVED:                                                                                |

|------------------------------------------------------------------------------------------|

| Redacted for privacy                                                                     |

| Major Professor, representing Electrical & Computer Engineering                          |

| Redacted for privacy                                                                     |

| Chair of Department of Electrical & Computer Engineering                                 |

| Redacted for privacy                                                                     |

| Dean of Graduate School                                                                  |

|                                                                                          |

|                                                                                          |

|                                                                                          |

| I understand that my thesis will become part of the permanent collection of Oregon State |

| University libraries. My signature below authorizes release of my thesis to any reader   |

| upon request.                                                                            |

|                                                                                          |

| Redacted for privacy                                                                     |

|                                                                                          |

| Haiqing Lin, Author                                                                      |

#### ACKNOWLEDGMENTS

My respect and gratitude to my advisor Prof. Richard Schreier is beyond my words. I am indebted to him for introducing me to the wonderful world of delta-sigma modulators and mixed-mode IC design. I wish to thank him for his guidance, support, help and encouragement, without which this work would not have been possible.

Many thanks to Prof. Dwight J. Bushnell of the Mechanical Engineering

Department for taking time out of his busy schedule to serve as the Graduate Council

Representative on my graduate committee.

I would like to thank my graduate committee members: Prof. Un-Ku Moon, Prof. John T. Stonick, Prof. Gabor C. Temes and other ECE Department faculty members such as: Prof. David J. Allstot and Prof. Sayfe Kiaei for valuable suggestions, comments and help. Thanks to Rita Wells, Sarah O'Leary, Kim Rowe, Jodi Nickerson, Sharon Ortiz, Jennifer Heim, Otto Gygax, Roger Traylor, Tim Heldt and other ECE department staff and support members for their support throughout my time here.

Special thanks to Luis Hernandez and Forrest Hudson for helping me to setup the test bed. Thanks also go to my colleague Bo Zhang for helping me to start my study and research at OSU. I will never be able to thank Bo and his wife Bing enough. Without their unselfish help during my early days in this country, my life would have been much harder.

I would also like to thank David Robertson, Todd Brooks, Doug Mercer, Paul Ferguson, Dave Carr, Chris Yaceshyn and other friends at Analog Devices, Inc. for a fruitful summer internship, the test board for my first prototype DAC chip, and the laser surgery of my second prototype chip. I am also grateful to Dru Cabler, Joe Peterson,

Geoffrey Brehmer and other friends at Advanced Micro Devices, Inc. for my second summer internship which was as great as the first.

Thanks to the National Science Foundation (NSF) Center for the Design of Analog/Digital ICs (CDADIC), Westinghouse Electric Corporation and Northrop Grumman Corporation for their generous support, and to Orbit Semiconductor, Inc. for their support in chip fabrication.

Thanks to my Chinese friends Bo Wang, Yunteng Huang, Tao Shui, Min Shen, Yihai Xiang, Yuming Cao, Tao Sun, Xiangping Qiu and their lovely families, with whom I shared many great times in Corvallis. Thanks also go to the OSU international advisors and many other friends whom I am not able to mention one by one due to the limited length of this acknowledgment.

Special thanks to my parents, for their constant support and encouragement in all aspects of life and study, for their love, help, advice, backup and belief in me.

Finally, thanks to my beautiful and lovely bride, Ying, for her deep love and blessings, and for filling my life with happiness.

### TABLE OF CONTENTS

|         |     | <u>Page</u>                                             |

|---------|-----|---------------------------------------------------------|

| Chapter | 1.  | Introduction                                            |

|         | 1.1 | Motivation1                                             |

|         | 1.2 | Thesis Outline                                          |

| Chapter | 2.  | Background: Delta-Sigma Modulation and Mismatch-Shaping |

|         | 2.1 | Quantization                                            |

|         |     | 2.1.1 Quantization and Quantization Noise               |

|         | 2.2 | First-Order Delta-Sigma Modulator                       |

|         | 2.3 | High Order Delta-Sigma Modulators9                      |

|         | 2.4 | Bandpass Delta-Sigma Modulators                         |

|         | 2.5 | Multi-bit Delta-Sigma Modulator                         |

|         | 2.6 | Existing Dynamic Matching Schemes                       |

|         |     | 2.6.1 Parallel Single-Bit Modulators                    |

|         |     | 2.6.2 Element Randomization                             |

|         |     | 2.6.3 Individual Level Averaging16                      |

|         |     | 2.6.4 First-Order Mismatch-Shaping Architectures        |

|         |     | 2.6.5 General Mismatch-Shaping Architectures            |

|         | 2.7 | Conclusions                                             |

| Chapter | 3.  | Element-Mismatch-Shaping Architectures                  |

|         | 3.1 | Comparison between Delta-Sigma ESL and Tree Shuffler24  |

|         | 3 2 | Delta-Sigma ESL 28                                      |

# **TABLE OF CONTENTS (Continued)**

|                                                                                 | <u>Page</u> |

|---------------------------------------------------------------------------------|-------------|

| 3.2.1 A Study on the Delta-Sigma ESL                                            | 28          |

| 3.2.2 A Design of a Vector Quantizer                                            | 31          |

| 3.2.3 A Revised Delta-Sigma ESL                                                 | 35          |

| 3.3 Butterfly Shuffler                                                          | 38          |

| 3.3.1 Modeling a Swapper                                                        | 38          |

| 3.3.2 Modeling a Butterfly Shuffler                                             | 39          |

| 3.3.3 Mismatch-Shaping Swappers and Butterfly Shufflers                         | 42          |

| 3.3.4 1st-Order Lowpass Swapper                                                 | 43          |

| 3.3.5 Bandpass Swapper                                                          | 44          |

| 3.3.6 Comparisons between the Mismatch-Shaping Butterfly Shuffler               | and the     |

| $\Delta\Sigma$ ESL                                                              |             |

| 3.4 Conclusions                                                                 | 48          |

| Chapter 4. A Segmented DAC with Mismatch-Shaped MSBs                            | 50          |

| 4.1 DAC Core                                                                    | 50          |

| 4.2 MSB-Mismatch Shaping: Direct Form                                           | 51          |

| 4.3 MSB-Mismatch Shaping: Cascade Structure                                     | 52          |

| 4.4 Simulation Results                                                          | 54          |

| 4.5 Bit-True Details                                                            | 55          |

| 4.6 Conclusions                                                                 | 58          |

| Chapter 5. A 16-Element Switched-Capacitor Mismatch-Shaping DAC                 | 59          |

| 5.1 Motivation                                                                  | 59          |

| 5.2 System-Level Definitions and Specifications of the $\Delta\Sigma$ Modulator | 60          |

# **TABLE OF CONTENTS (Continued)**

| Page                                                               |

|--------------------------------------------------------------------|

| 5.2.1 General Design Chart for Multi-Bit $\Delta\Sigma$ Modulators |

| 5.2.2 Number of Quantization Levels                                |

| 5.2.3 Oversampling Ratio63                                         |

| 5.2.4 Order of the Modulator64                                     |

| 5.2.5 Summary of the System-Level Definitions                      |

| 5.3 System Diagram                                                 |

| 5.4 16-Element SC DAC                                              |

| 5.4.1 Top Level the DAC68                                          |

| 5.4.2 Capacitor Sizing                                             |

| 5.4.3 Digital Interface and Clock Generator72                      |

| 5.4.4 Op Amp75                                                     |

| 5.4.5 Bias Circuit                                                 |

| 5.4.6 Floor Plan and Pin-Out of the Chip79                         |

| 5.5 Modulator Design81                                             |

| 5.5.1 Optimized rms output noise82                                 |

| 5.5.2 Design of Lowpass Modulators84                               |

| 5.5.3 8th-Order Bandpass Modulator89                               |

| 5.6 ESL and other Digital Logic90                                  |

| 5.6.1 1st-Order ESL90                                              |

| 5.6.2 Pseudo-Random Scrambler92                                    |

| 5.7 Summary93                                                      |

| Chapter 6. Experimental Results on the Mismatch-Shaping SC DAC94   |

| 6.1 The SC DAC Chip94                                              |

| 6.2 The Test Bed95                                                 |

| 6.3 Op Amp Test97                                                  |

# **TABLE OF CONTENTS (Continued)**

|            |                                                                    | <u>Page</u> |

|------------|--------------------------------------------------------------------|-------------|

|            | 6.3.1 Offset Voltage                                               | 97          |

|            | 6.3.2 DC Open-Loop Gain                                            | 98          |

|            | 6.3.3 Unity-Gain Bandwidth                                         | 98          |

|            | 6.3.4 Step Response                                                |             |

| 6          | .4 Element Matching                                                | 100         |

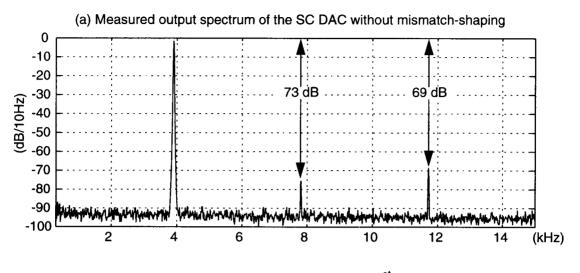

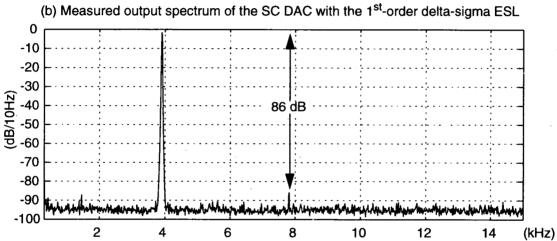

|            | 6.4.1 1st-Order Mismatch-Shaping DAC                               | 100         |

|            | 6.4.2 2nd-Order Mismatch-Shaping DAC                               | 102         |

|            | 6.4.3 Bandpass Mismatch-Shaping DAC                                | 107         |

| 6          | 5.5 Some Circuit Level Considerations for Mismatch-Shaping SC DAC. | 109         |

|            | 6.5.1 Mismatch-Shaping at 2 MHz Clock Rate                         | 109         |

|            | 6.5.2 Effect of Incomplete Settling                                | 111         |

|            | 6.5.3 More Measurements at 2 MHz and 500 kHz                       | 112         |

|            | 6.5.4 The Use of the Deglitching filter                            | 115         |

|            | 6.5.5 "Dynamic Mismatch"                                           | 117         |

|            | 6.5.6 Other Issues                                                 | 121         |

| 6          | 6.6 Conclusions                                                    | 122         |

| Chapter 7. | . Conclusions and Future Work                                      | 123         |

| 7.         | .1 Summary                                                         | 123         |

| 7.         | .2 Future Work                                                     | 124         |

| Bibliograp | ohy                                                                | 125         |

| Appendice  | es                                                                 | 131         |

## LIST OF FIGURES

| <u>Page</u>                                                                                                                                                         | igure |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| (a) An example of uniform multi-level quantization characteristic. (b) Single-bit quantization.                                                                     | 2.1   |

| A first-order single-bit $\Delta\Sigma$ modulator                                                                                                                   | 2.2   |

| (a) The frequency response of , and (b) the simulated spectrum of first-order $\Delta\Sigma$ modulator with sine-wave input shows the shaping of quantization noise | 2.3   |

| 4 A general $\Delta\Sigma$ modulator.                                                                                                                               | 2.4   |

| Second-order $\Delta\Sigma$ modulator                                                                                                                               | 2.5   |

| The passbands and pole/zero locations of the noise transfer functions for (a) low pass and (b) bandpass $\Delta\Sigma$ modulation.                                  | 2.6   |

| A diagram of a bandpass $\Delta\Sigma$ ADC                                                                                                                          | 2.7   |

| β A multi-bit $δΣ$ modulator                                                                                                                                        | 2.8   |

| Multi-level $\Delta\Sigma$ DAC using parallel 1-bit modulators                                                                                                      | 2.9   |

| 10 An 8-element DAC driven by a butterfly shuffler                                                                                                                  | 2.10  |

| 11 A 1st-order mismatch-shaping swapper                                                                                                                             | 2.11  |

| 12 1st-order mismatch-shaping with element rotation scheme                                                                                                          | 2.12  |

| 13 A mismatch-shaping DAC with an ESL analogous to $\Delta\Sigma$ modulation 20                                                                                     | 2.13  |

| Mismatch-shaping DAC using tree-structure shuffler                                                                                                                  | 2.14  |

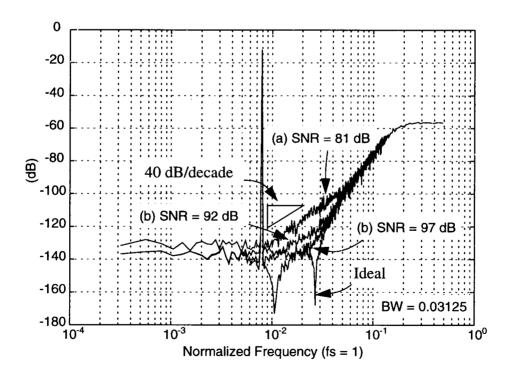

| SNR and spectra of a 4th-order 17-level delta-sigma DAC with (a) an ideal DAC and (b) a 16-element DAC possessing 0.5% mismatch                                     | 3.1   |

| SNR and spectra of a 4th-order 17-level delta-sigma DAC with 1st-order mismatch-shaping using (a) tree-structure shuffler, (b) delta-sigma-like ESL 20              | 3.2   |

| SNR and spectra of a 4th-order 17-level delta-sigma DAC with 2nd-order mis-                                                                                         | 3 3   |

| <u>Figure</u> | Page                                                                                                                                                                                                                                                                                                                        |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | match-shaping using (a) tree-structure shuffler, (b) delta-sigma-like ESL and (c) optimized delta-sigma-like ESL.                                                                                                                                                                                                           |

| 3.4           | A mismatch-shaping DAC with an ESL analogous to $\Delta\Sigma$ modulation 28                                                                                                                                                                                                                                                |

| 3.5           | Spectrum of one of the se components                                                                                                                                                                                                                                                                                        |

| 3.6           | A 16-component vector quantizer                                                                                                                                                                                                                                                                                             |

| 3.7           | Unit-element DAC with the elements grouped in pairs                                                                                                                                                                                                                                                                         |

| 3.8           | SNR and spectra of an 4th-order 17-level delta-sigma DAC using (a) no mismatch-shaping with internally matched element pairs, (b) revised 2nd-order optimized delta-sigma ESL driving internally mismatched element pairs and (c) revised 2nd-order optimized delta-sigma ESL driving internally matched element pairs.  37 |

| 3.9           | A swapper cell                                                                                                                                                                                                                                                                                                              |

| 3.10          | A 2-stage Butterfly Scrambler for driving a 4-element DAC40                                                                                                                                                                                                                                                                 |

| 3.11          | A noise-shaping swapper                                                                                                                                                                                                                                                                                                     |

| 3.12          | A 1st-order lowpass noise-shaping swapper                                                                                                                                                                                                                                                                                   |

| 3.13          | A bandpass noise-shaping swapper45                                                                                                                                                                                                                                                                                          |

| 3.14          | SNR and spectra of an 4th-order 17-level delta-sigma DAC with element mismatch-shaping using (a) 1st-order delta-sigma ESL, (b) 1st-order butterfly shuffler and (c) 2nd-order butterfly shuffler                                                                                                                           |

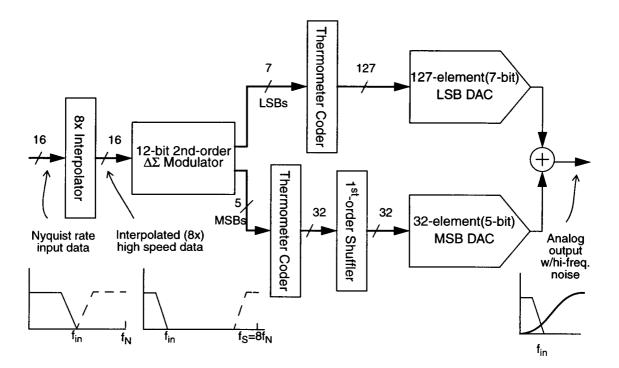

| 4.1           | System diagram for a 12-bit delta-sigma DAC                                                                                                                                                                                                                                                                                 |

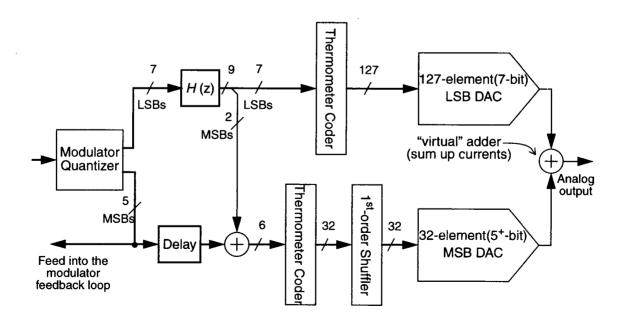

| 4.2           | A cascade structure with 12-bit equivalent quantization                                                                                                                                                                                                                                                                     |

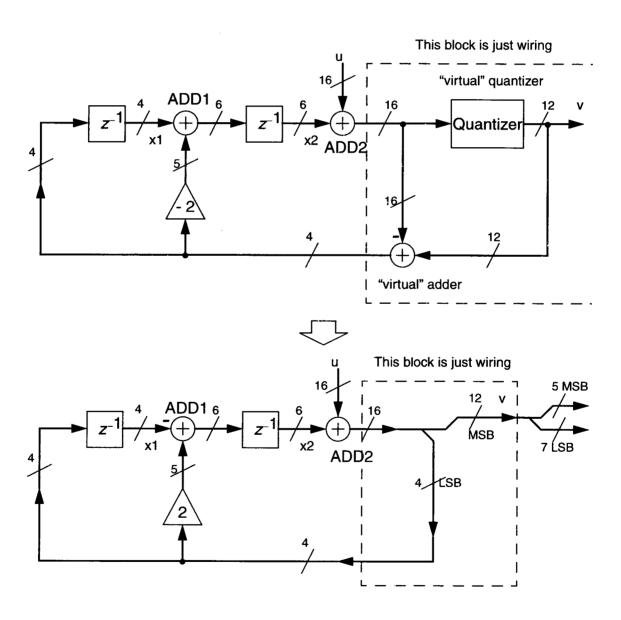

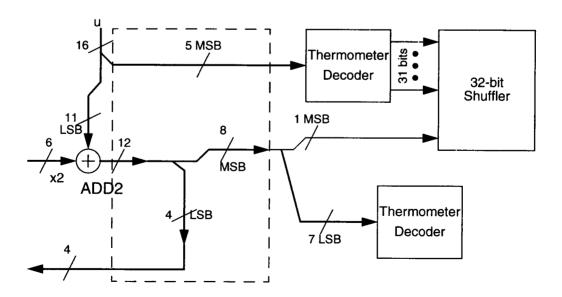

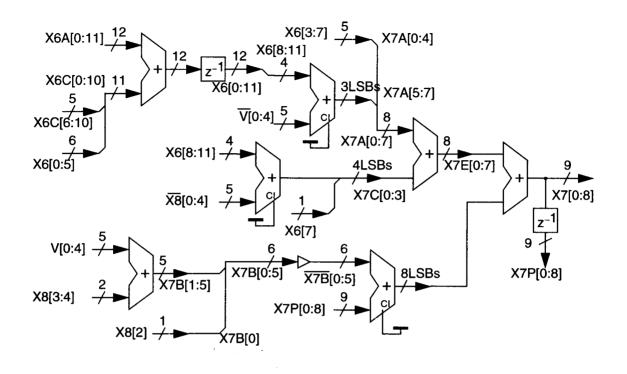

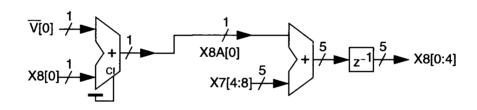

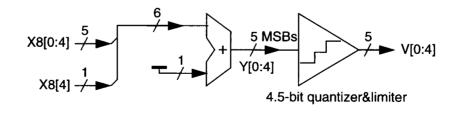

| 4.3           | The bit-true system diagram of the 2nd-order 12-bit lowpass digital $\Delta\Sigma$ modulator                                                                                                                                                                                                                                |

| <u>Figure</u> | Page                                                                 |

|---------------|----------------------------------------------------------------------|

| 4.4           | An improved structure with the adder A2 cut down to 11-bit           |

| 5.1           | Block diagram of a $\Delta\Sigma$ ADC.                               |

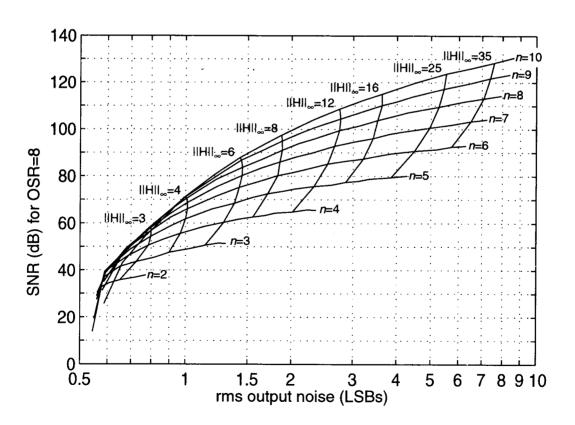

| 5.2           | Design chart for multi-bit $\Delta\Sigma$ modulators                 |

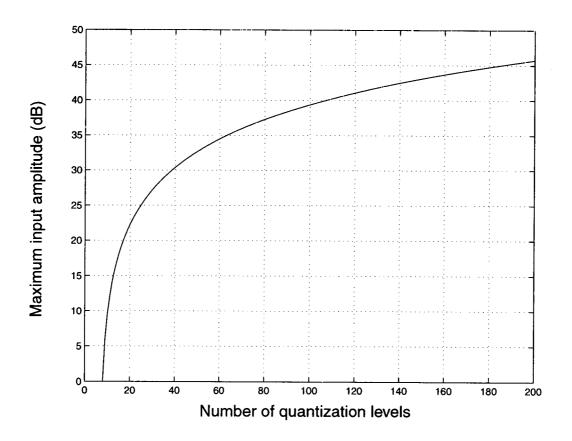

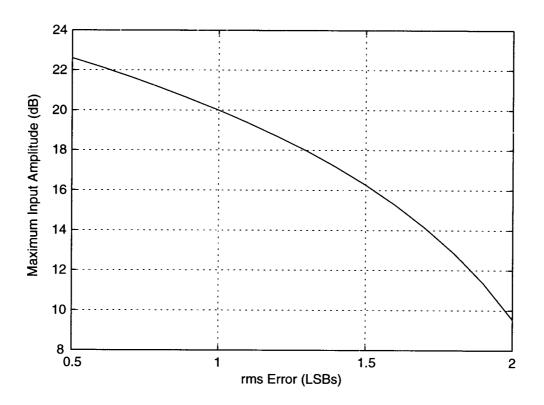

| 5.3           | Maximum input amplitude VS. number of quantization levels            |

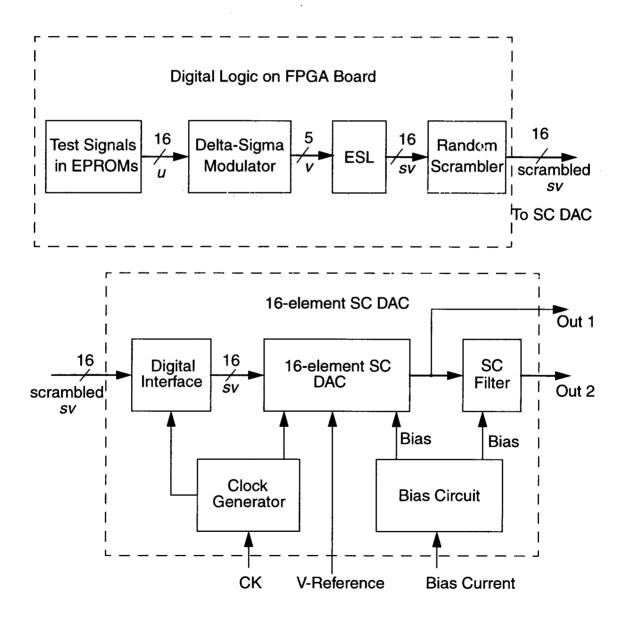

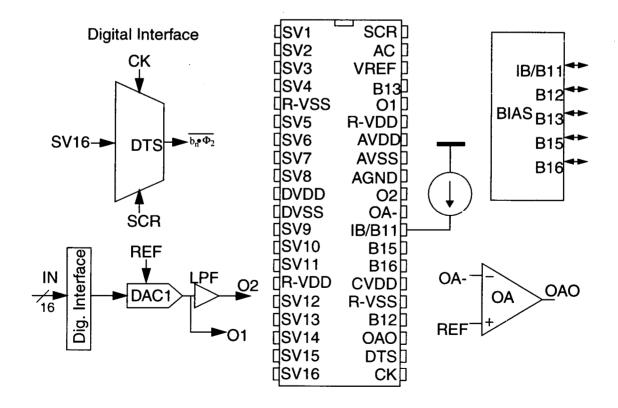

| 5.4           | System diagram. 67                                                   |

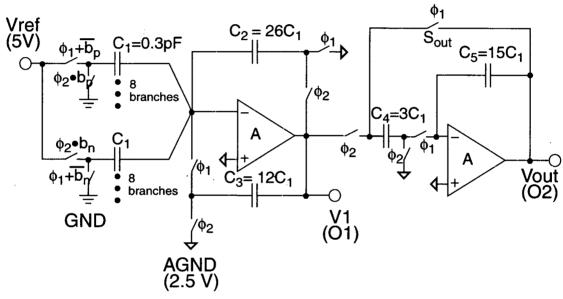

| 5.5           | The SC DAC and output buffer                                         |

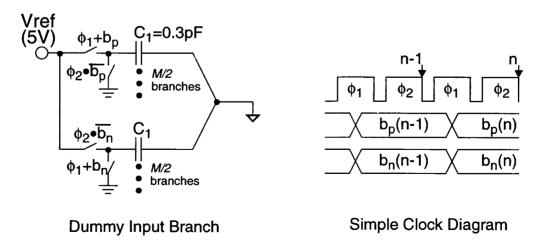

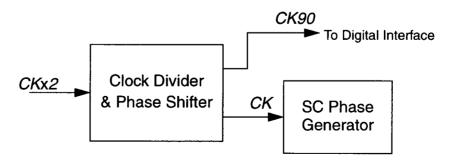

| 5.6           | System diagram of the clock generator                                |

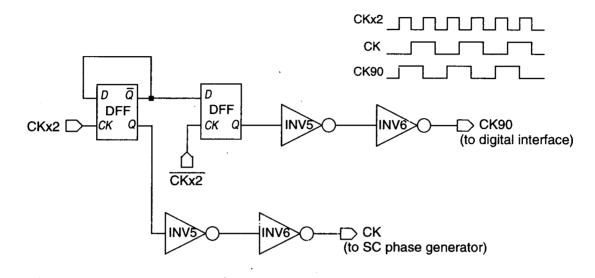

| 5.7           | Clock-divider & phase-shifter                                        |

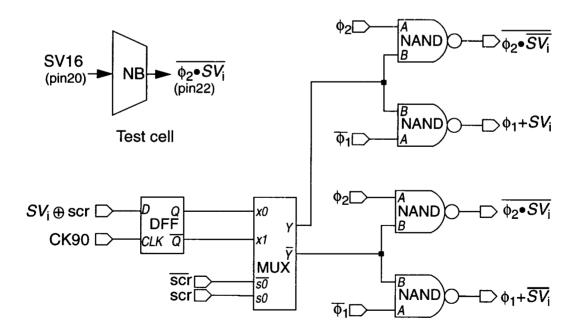

| 5.8           | A cell of the digital-to-analog interface                            |

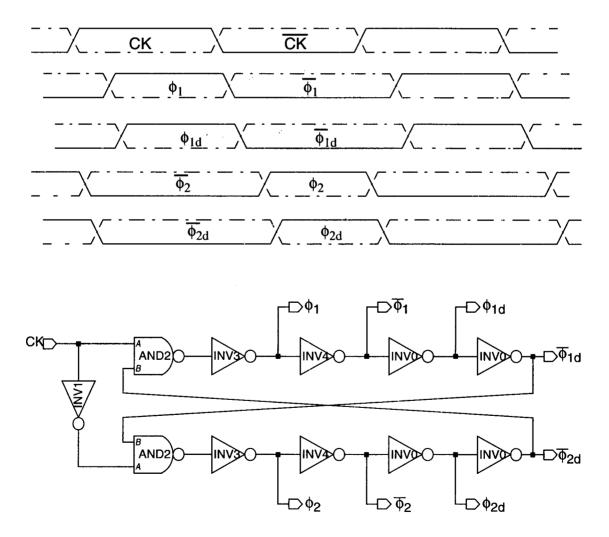

| 5.9           | SC clock generator and diagram                                       |

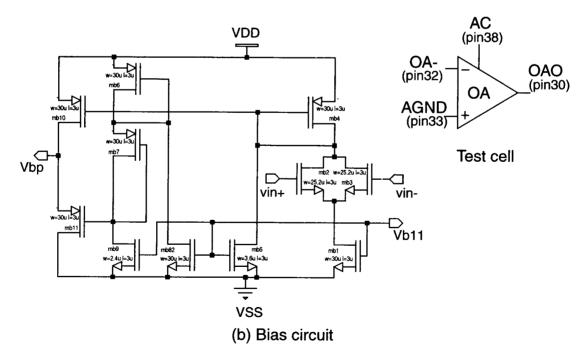

| 5.10          | The output buffer amplifier and its bias circuit                     |

| 5.11          | Bias circuit                                                         |

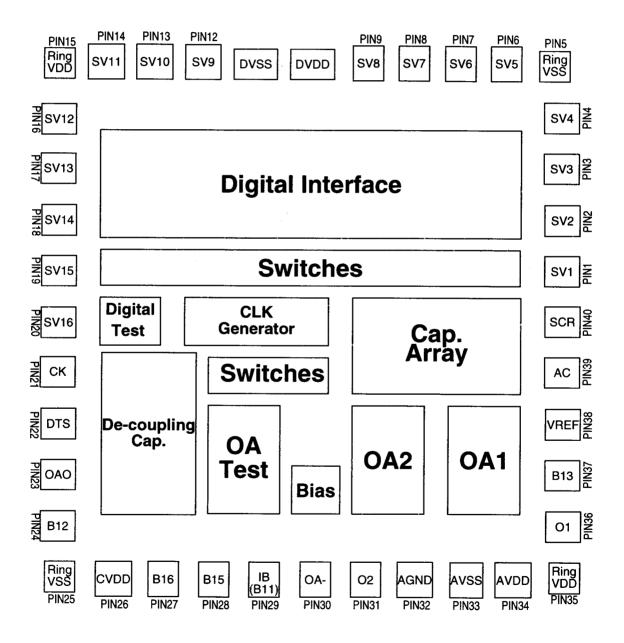

| 5.12          | Floor plan for the SC DAC layout                                     |

| 5.13          | Pin-out of the SC DAC chip                                           |

| 5.14          | Maximum input amplitude VS. rms quantization error                   |

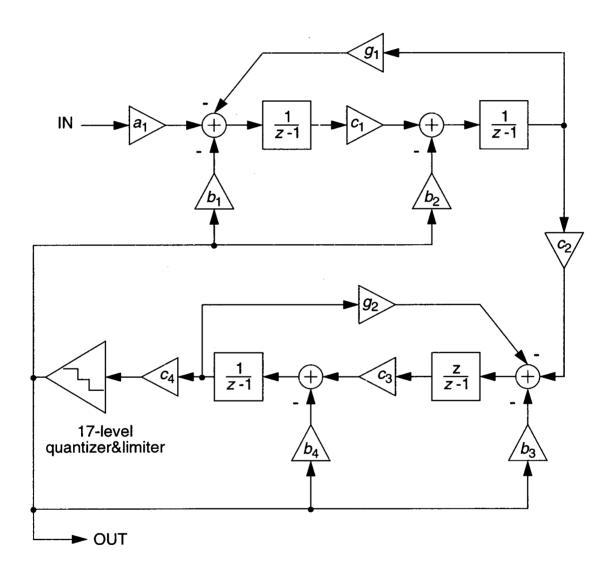

| 5.15          | Structure of the 4th-order modulator                                 |

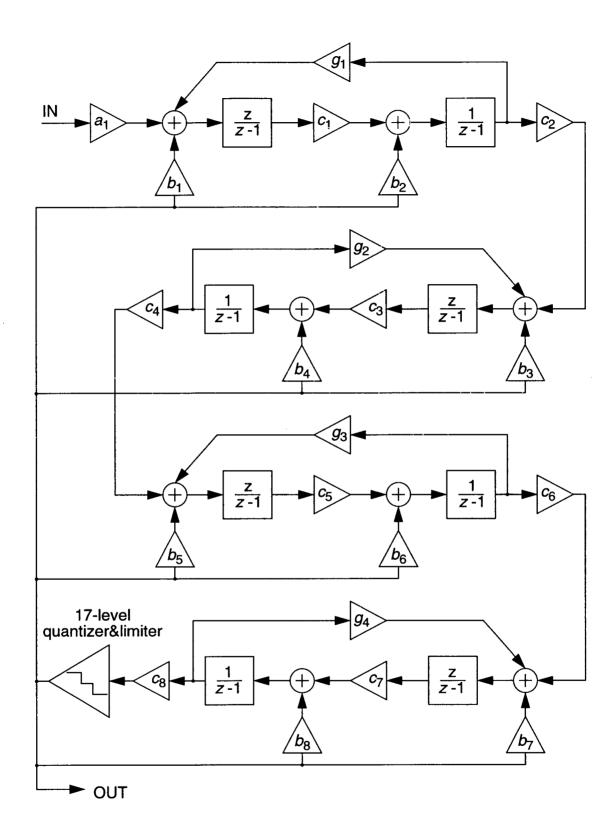

| 5.16          | Structure of the 8th-order modulator                                 |

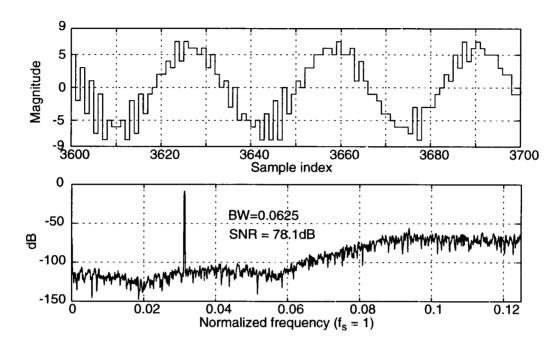

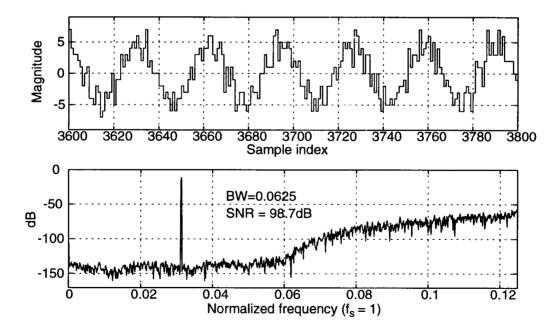

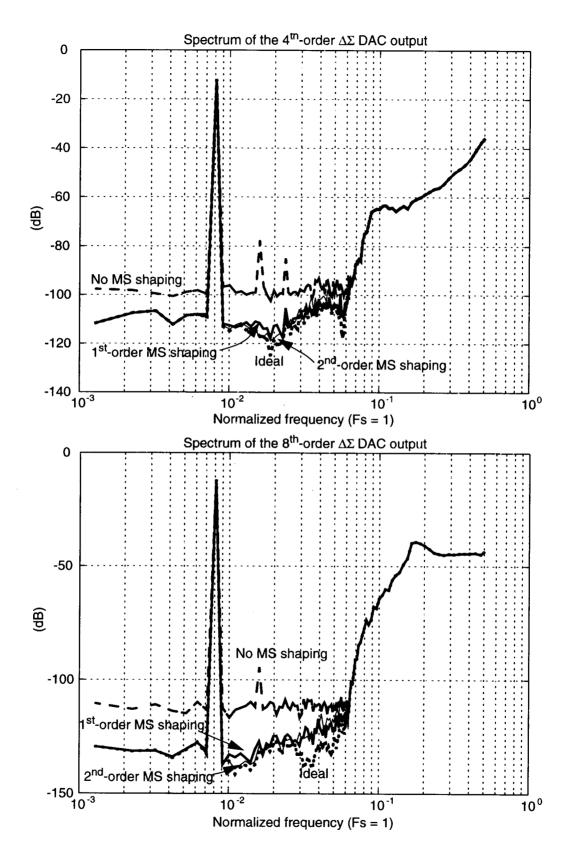

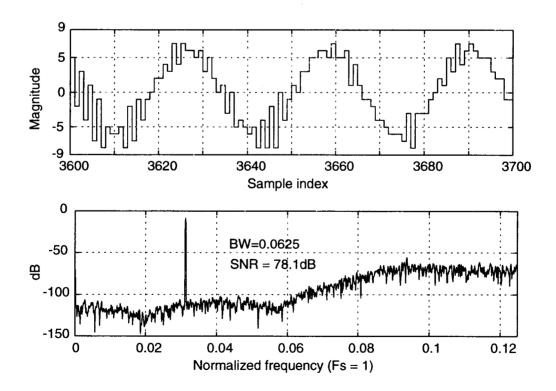

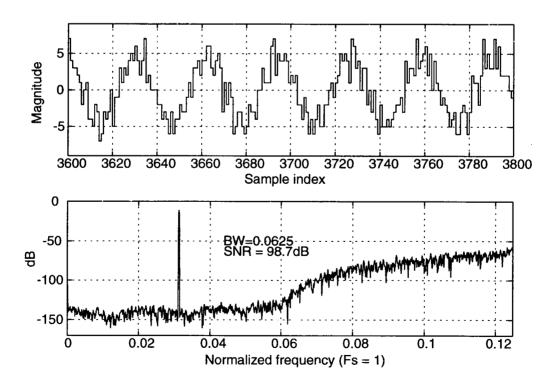

| 5.17          | Output waveform and spectrum of the 4th-order modulator (OSR = 8) 88 |

| 5.18          | Output waveform and spectrum of the 8th-order modulator (OSR = 8) 88 |

| <u>Figure</u> | <u>Page</u>                                                                                                              |

|---------------|--------------------------------------------------------------------------------------------------------------------------|

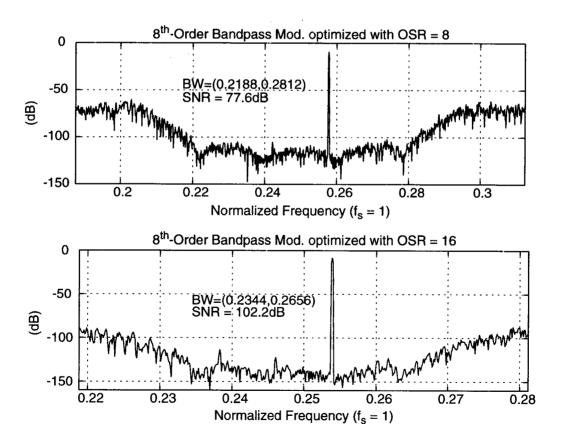

| 5.19          | Output spectra of 8th-order bandpass modulators                                                                          |

| 5.20          | Output spectra of the mismatch-shaping $\Delta\Sigma$ DAC                                                                |

| 5.21          | Scrambling and decrambling SV bits                                                                                       |

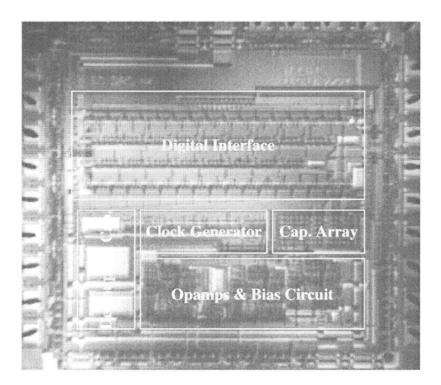

| 6.1           | Chip photo94                                                                                                             |

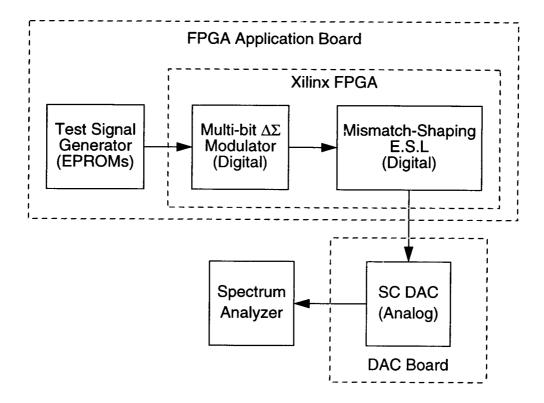

| 6.2           | The mismatch-shaping SC DAC test bed95                                                                                   |

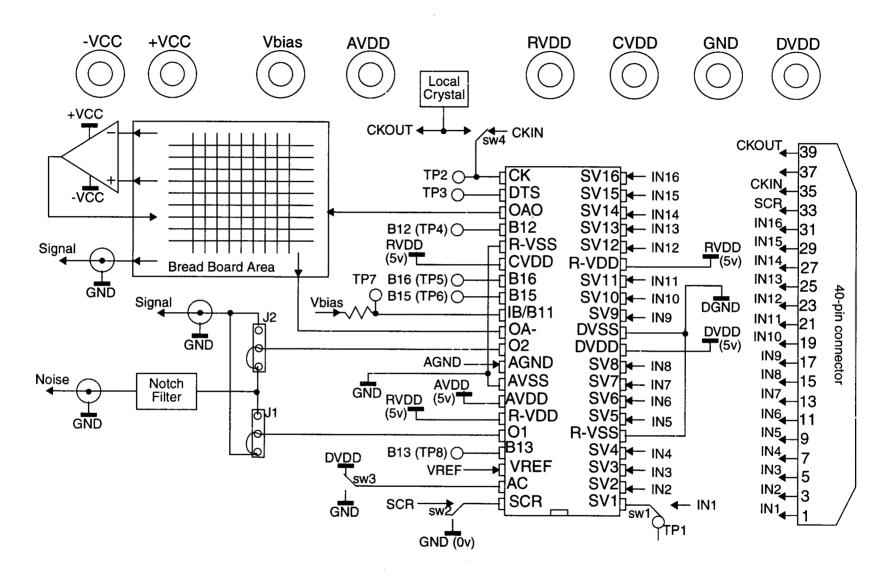

| 6.3           | The DAC board96                                                                                                          |

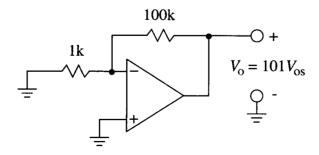

| 6.4           | Vos test circuit                                                                                                         |

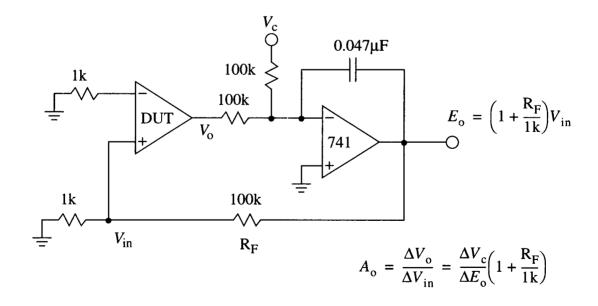

| 6.5           | Ao test circuit                                                                                                          |

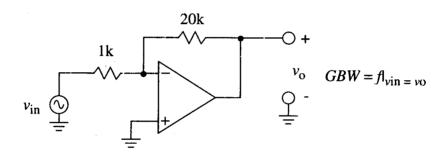

| 6.6           | GBW test circuit                                                                                                         |

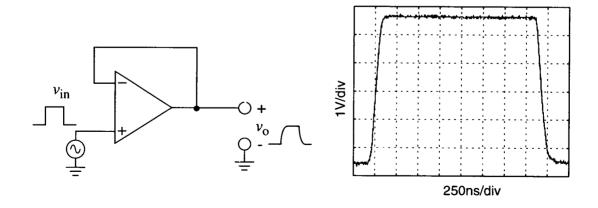

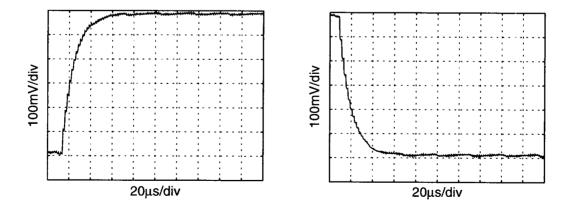

| 6.7           | The step response of the op amp99                                                                                        |

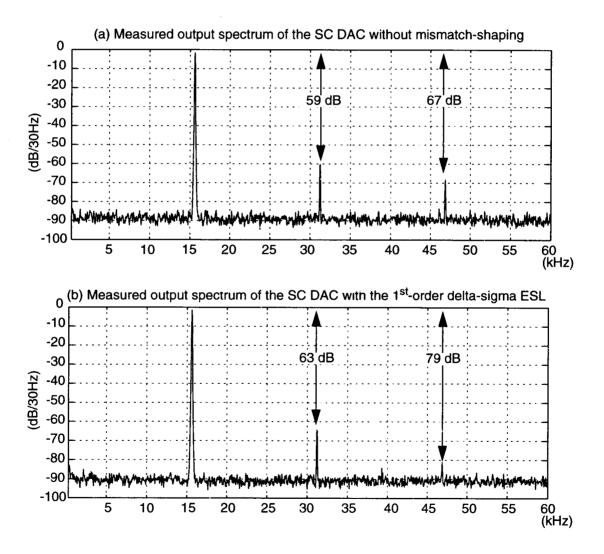

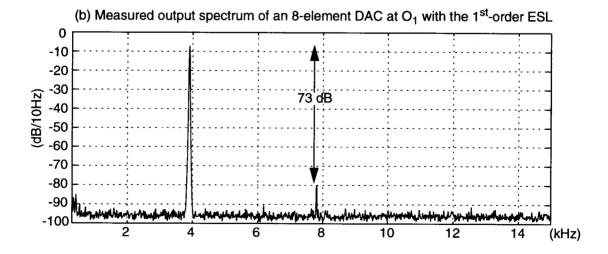

| 6.8           | Measured spectra of the 4th-order delta-sigma SC DAC with 4-bit quantization at a sampling frequency of 500 kHz          |

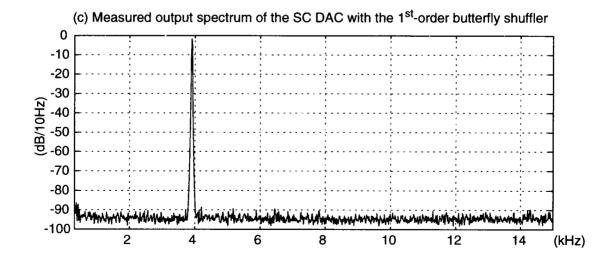

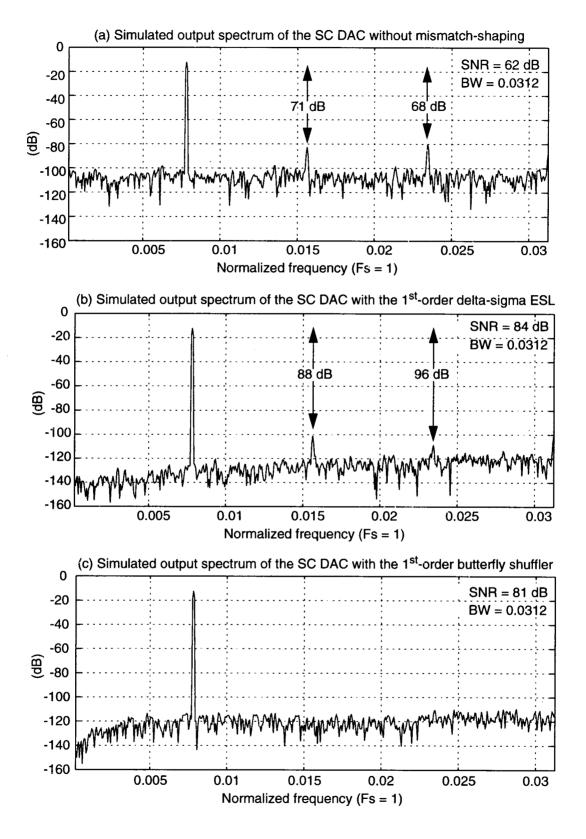

| 6.9           | Simulated spectra of the 4th-order delta-sigma SC DAC with 4-bit quantization at a sampling frequency of 500 kHz         |

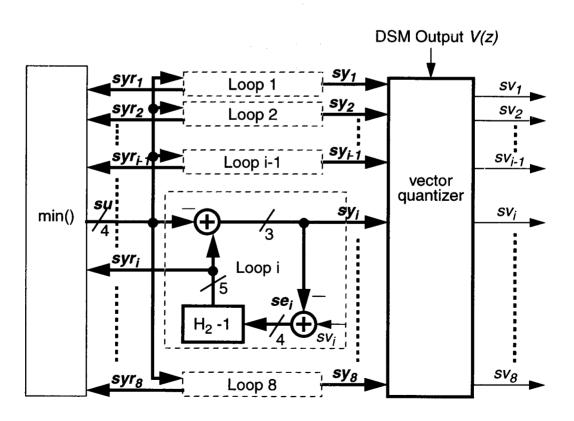

| 6.10          | A 2nd-order 8-element ESL                                                                                                |

| 6.11          | Measured spectra of the 4th-order delta-sigma SC DAC with 3-bit quantization at a sampling frequency of 500 kHz          |

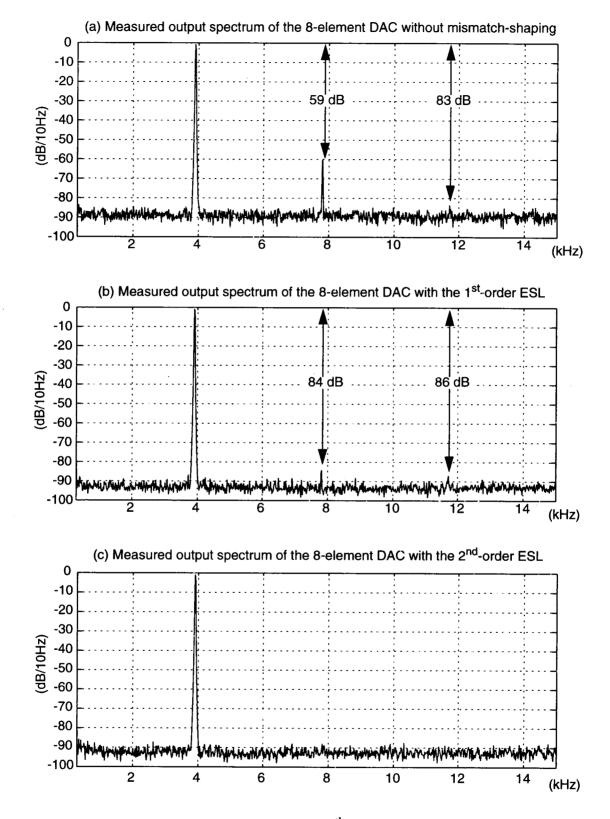

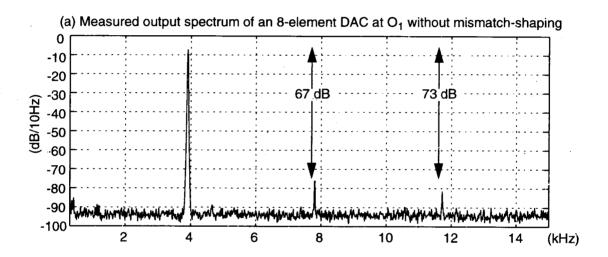

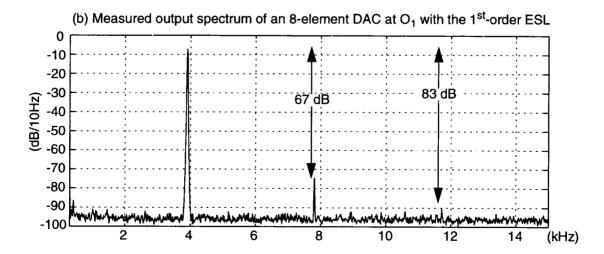

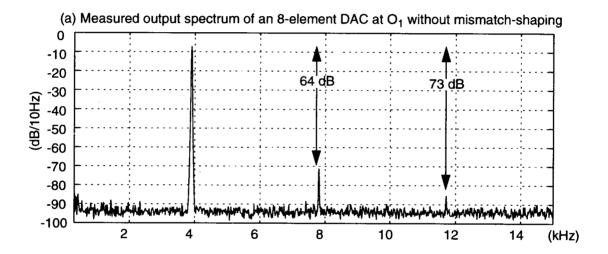

| 6.12          | Demonstration of 1st-order and 2nd-order mismatch shaping                                                                |

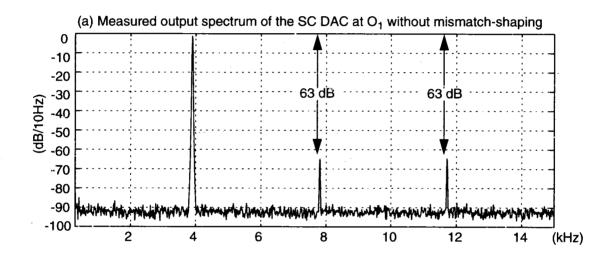

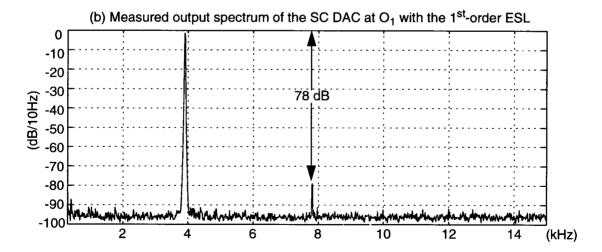

| 6.13          | Measured spectra of the 8th-order bandpass delta-sigma SC DAC with 4-bit quantization at a sampling frequency of 500 kHz |

| 6.14          | Measured spectra of the 4th-order delta-sigma SC DAC with 4-bit quantization at a sampling frequency of 2 MHz            |

| <u>igure</u> P                                                                                                       | <u>age</u> |

|----------------------------------------------------------------------------------------------------------------------|------------|

| 6.15 The transient output of the SC DAC at O1 given step input                                                       | 114        |

| 6.16 Measured spectra of the 4th-order delta-sigma SC DAC at O1 with a sampli frequency of 2 MHz.                    | _          |

| 6.17 The transient output of the SC DAC at O2 given a step input                                                     | 116        |

| 6.18 Measured spectra of the 4th-order delta-sigma 16-element DAC at O1 with sampling frequency of 500 kHz.          |            |

| 6.19 The dynamic mismatch between a positive branch and a negative branch                                            | 119        |

| 6.20 Measured spectra of the 4th-order delta-sigma 8-negative-element DAC at 0 with a sampling frequency of 500 kHz. |            |

| 6.21 Measured spectra of the 4th-order delta-sigma 8-element DAC at O1 with a sampling frequency of 500 kHz.         |            |

## LIST OF TABLES

| <u>Table</u> |                                                                                 | <u>Page</u> |

|--------------|---------------------------------------------------------------------------------|-------------|

| 2.1          | 1st-order mismatch-shaping swapper truth table.                                 | 18          |

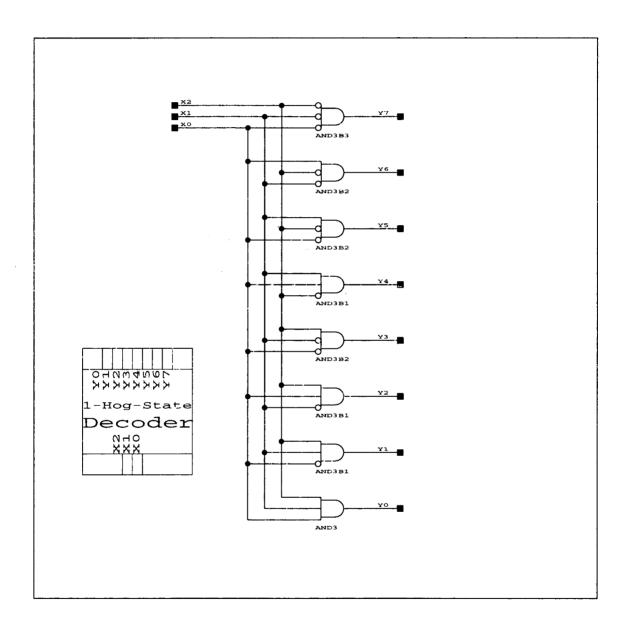

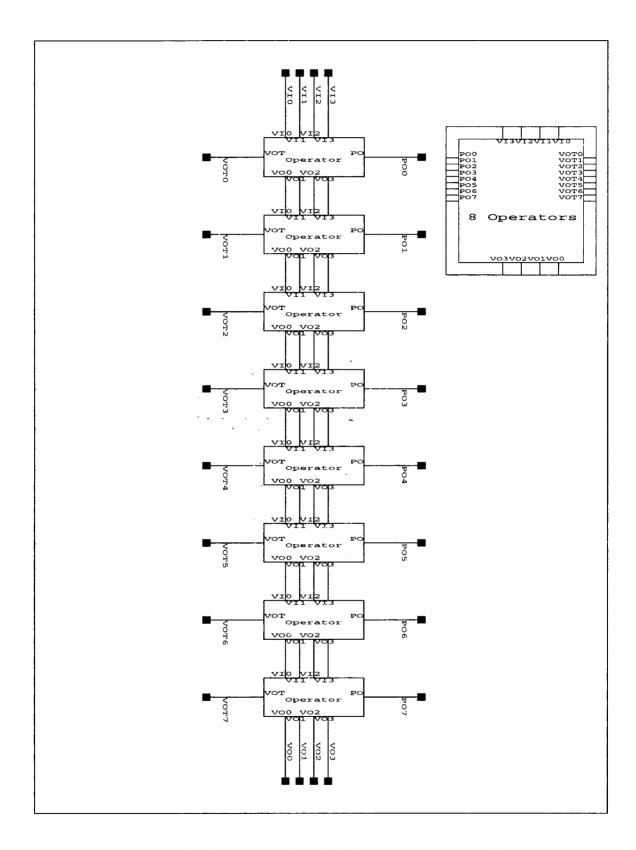

| 3.1          | 3-to-8 "single-hog-status" decoder truth table.                                 | 32          |

| 4.1          | SNR of the $\Delta\Sigma$ DAC with different structures and matching conditions | 54          |

| 5.1          | System-level definitions and specifications.                                    | 66          |

| 5.2          | Simulated op amp parameters.                                                    | 77          |

| 5.3          | Pin list of the SC DAC.                                                         | 81          |

| 5.4          | "Optimum" points in the design example.                                         | 83          |

| 5.5          | Coefficients and peak SNRs of the lowpass modulators.                           | 87          |

| 6.1          | The measured harmonic distortion of the bandpass DAC.                           | 109         |

| 6.2          | The DAC under test matching data.                                               | 112         |

## LIST OF APPENDICES

| <u>Pa</u>                                                                  | age |

|----------------------------------------------------------------------------|-----|

| Appendix I. Design Details of the Modulators in Chapter 4                  | 132 |

| App.1.1 4th-Order Lowpass Modulator optimized with OSR = 8 1               | 132 |

| App.1.2 4th-Order Lowpass Modulator optimized with OSR = 16                | 36  |

| App.1.3 8th-Order Lowpass Modulator optimized with OSR = 8 1               | 36  |

| Appendix II. Schematics of an 8-element 2nd-order ESL in VIEWDRAW Format 1 | 44  |

## LIST OF APPENDIX FIGURES

| <u>Figure</u> | <u>P</u>                                                                          | <u>age</u> |

|---------------|-----------------------------------------------------------------------------------|------------|

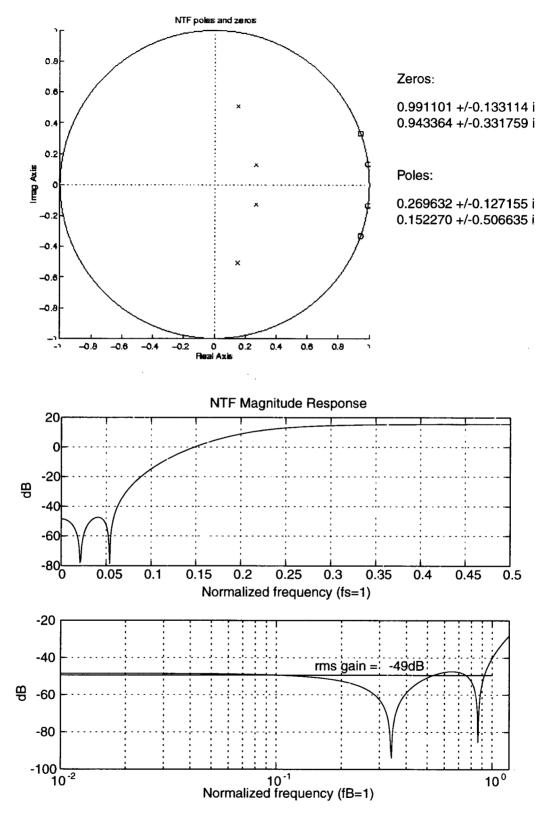

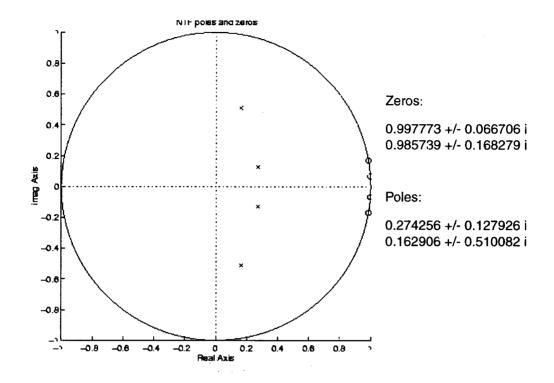

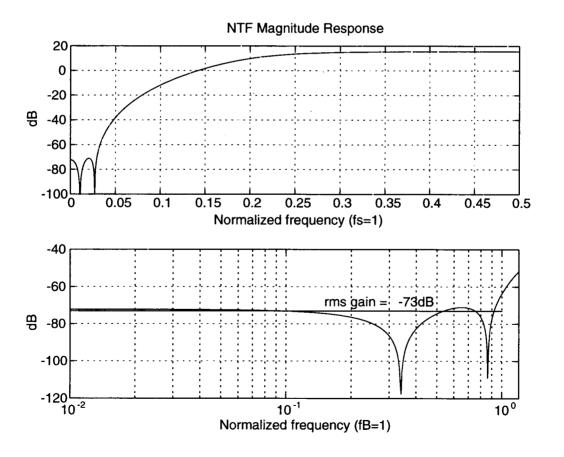

| A.1.1         | Original 4th-order NTF optimized with OSR = 8.                                    | 133        |

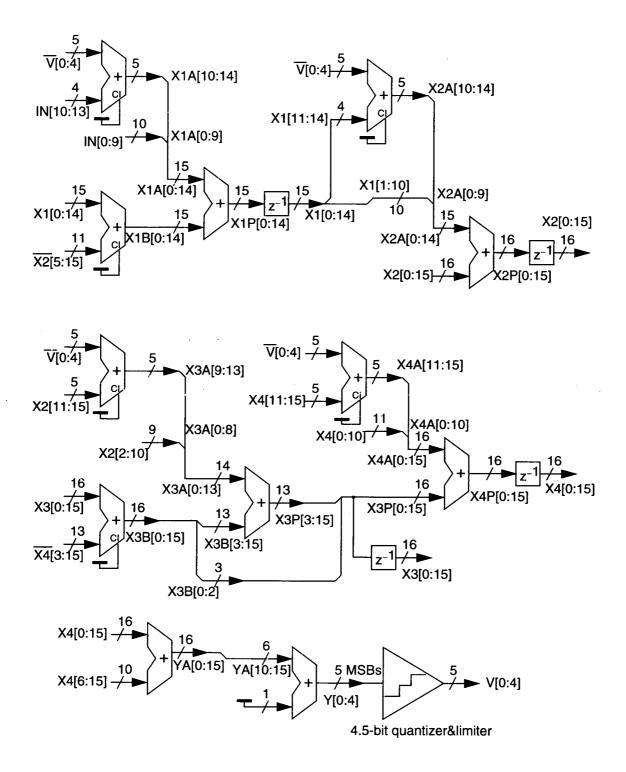

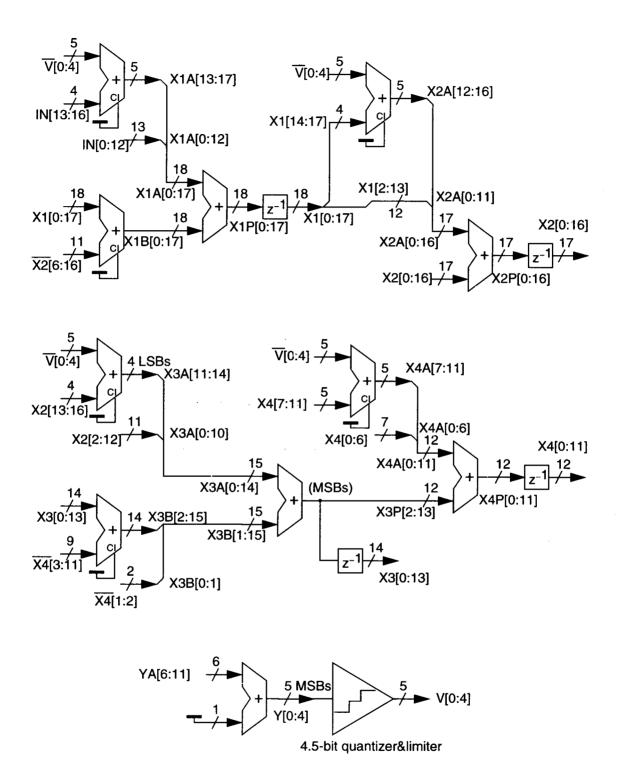

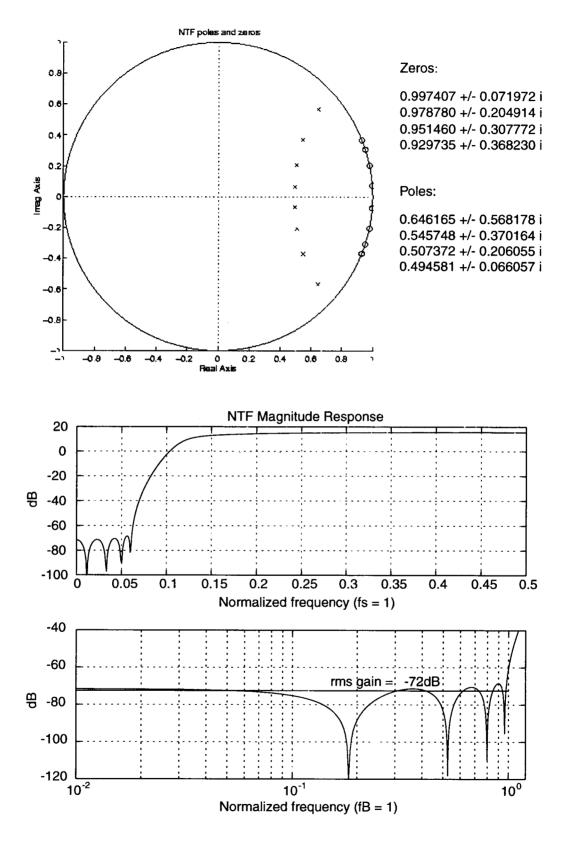

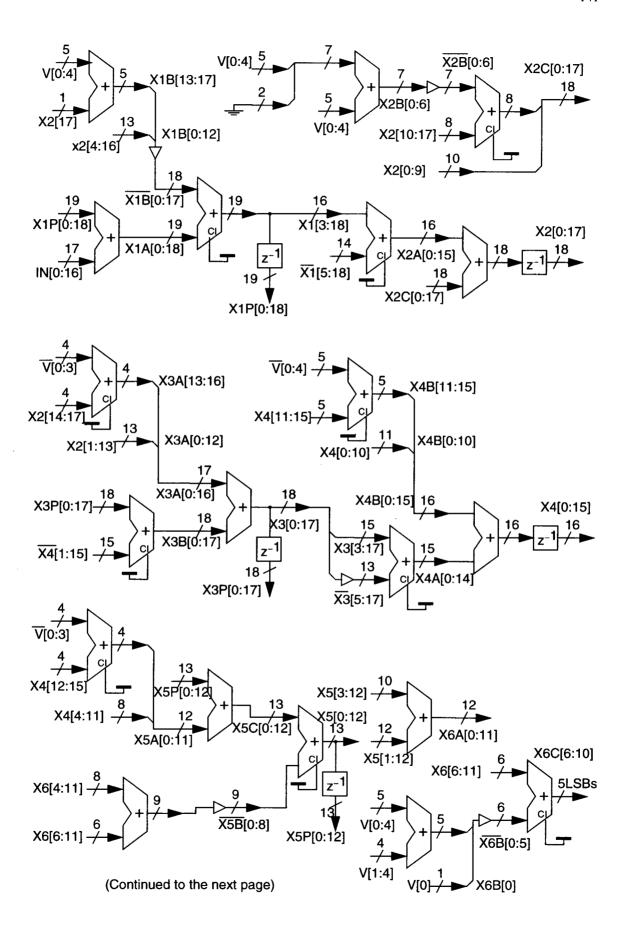

| A.1.2         | Schematic of a 4th-order 4.5-bit $\Delta\Sigma$ modulator optimized with OSR = 8  | 134        |

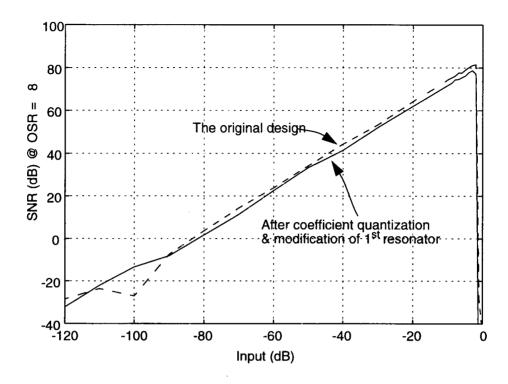

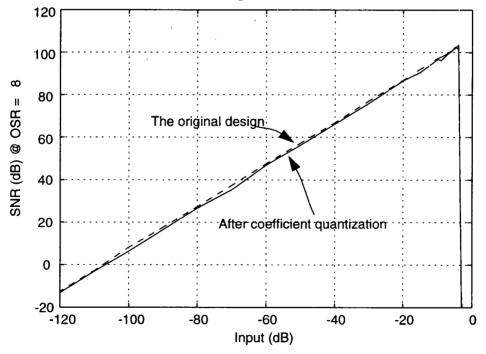

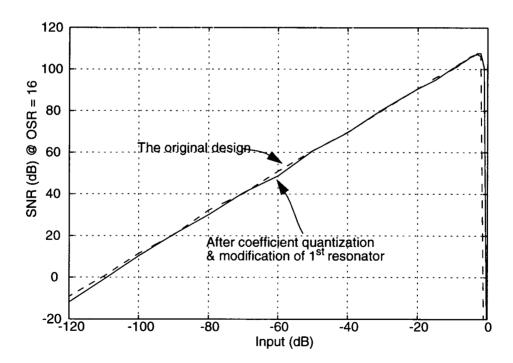

| A.1.3         | SNR v.s. input tone amplitude. (4th-order, OSR = 8)                               | 135        |

| A.1.4         | Output waveform and spectrum of the 4th-order modulator (OSR = 8)                 | 135        |

| A.1.5         | Original 4th-order NTF optimized with OSR = 16                                    | 137        |

| A.1.6         | Schematic of a 4th-order 4.5-bit $\Delta\Sigma$ modulator optimized with OSR = 16 | 138        |

| A.1.7         | SNR v.s. input tone amplitude. (4th-order, OSR = 16)                              | 139        |

| A.1.8         | Original 8th-order NTF optimized with OSR = 8.                                    | 140        |

| A.1.9         | Schematic of a 8th-order 4.5-bit $\Delta\Sigma$ modulator optimized with OSR = 8  | 142        |

| A.1.10        | SNR v.s. input tone amplitude. (8th-order, OSR = 8)                               | 143        |

| A.1.11        | Output waveform and spectrum of the 8th-order modulator (OSR = 8)                 | 143        |

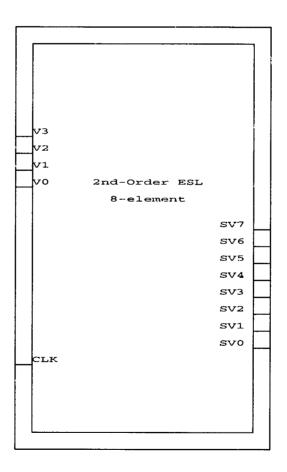

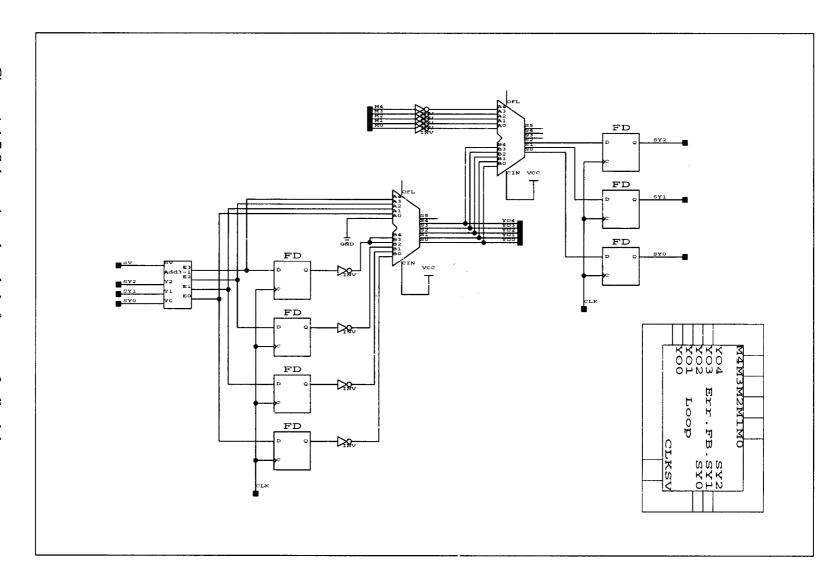

| A.2.1         | The symbol of the 2nd-order ESL.                                                  | 144        |

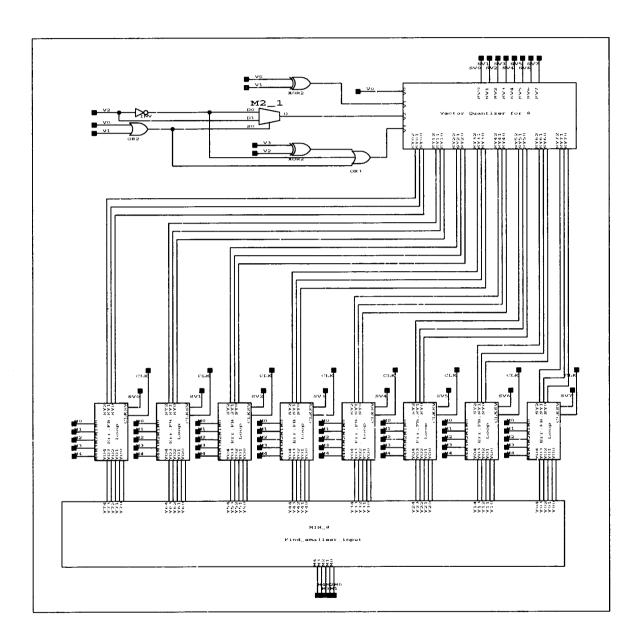

| A.2.2         | Schematic of the 2nd-order ESL.                                                   | 145        |

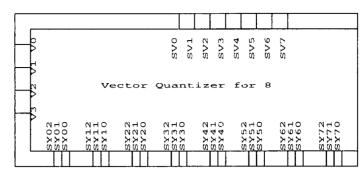

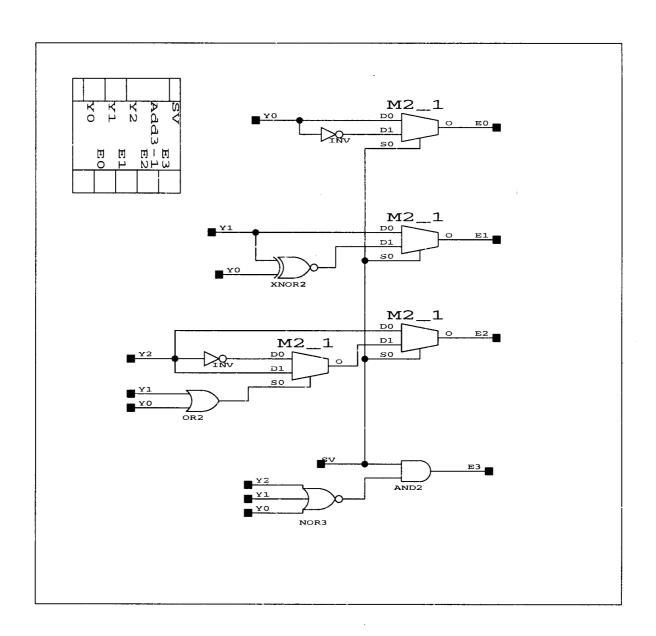

| A.2.3         | Schematic and symbol of vector quantizer.                                         | 146        |

| A.2.4         | Schematic and symbol of "single-hog-state" decoder.                               | 147        |

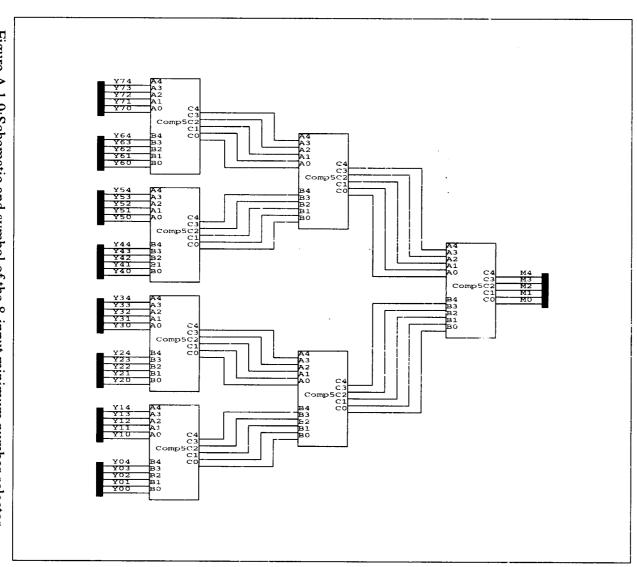

| A.2.5         | Schematic and symbol of an operator group of 8.                                   | 148        |

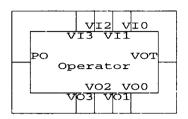

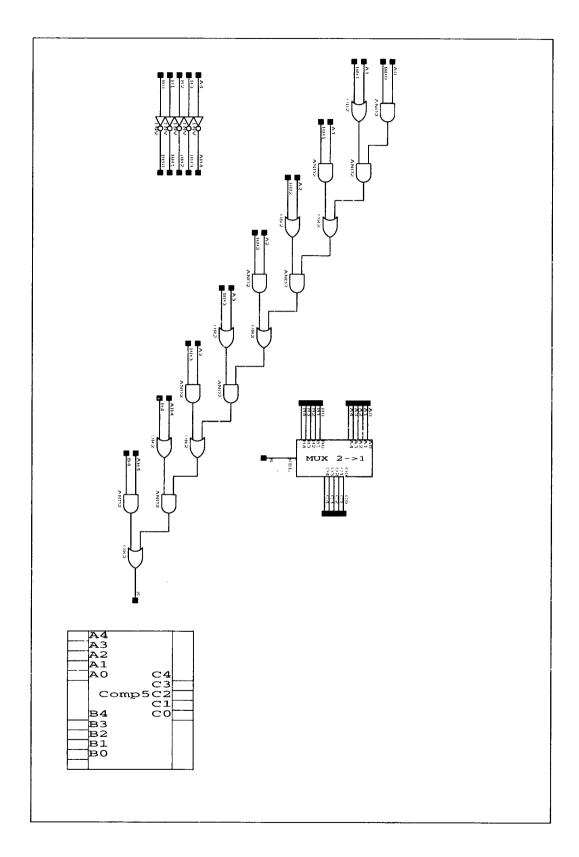

| A.2.6         | Schematic and symbol of an operator cell.                                         | 149        |

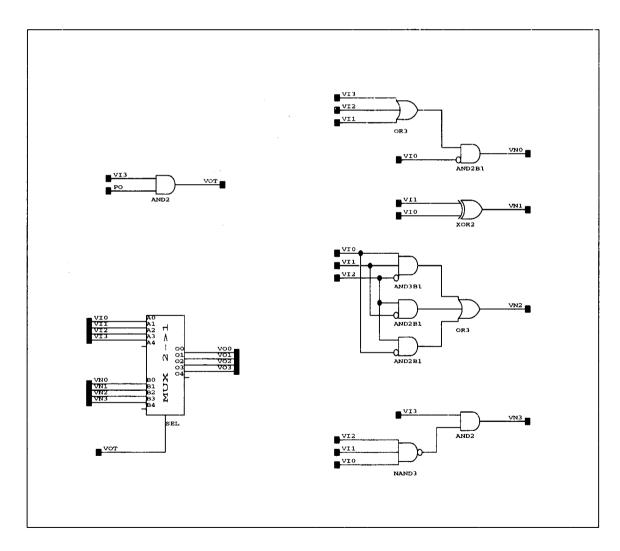

| A.2.7         | Schematic and symbol of an error feedback loop.                                   | 150        |

| A.2.8         | Schematic and symbol of the "3-bit number minus 1"logic.                          | 151        |

# LIST OF APPENDIX FIGURES (Continued)

| <u>Figure</u> |                                                             | <u>Page</u> |

|---------------|-------------------------------------------------------------|-------------|

| A.2.9         | Schematic and symbol of the 8-input minimum number selector | 152         |

| A.2.10        | Schematic and symbol of a 5-bit comparator                  | 153         |

# Multi-bit Delta-Sigma Switched-Capacitor DACs Employing Element-Mismatch-Shaping

#### **Chapter 1. Introduction**

By a process similar to delta-sigma modulation [1, 2], the noise caused by static element mismatch in a multi-level digital-to-analog converter (DAC) [3] can be attenuated in a narrow frequency band. The purpose of this thesis is to explore this mismatch-shaping technique for high-resolution wide-band multi-bit delta-sigma switched-capacitor (SC) DACs.

#### 1.1 Motivation

Because of its insensitivity to many analog imperfections, delta-sigma modulation [1, 2] has become one of the most popular techniques for making high-resolution ADCs (analog-to-digital converters) and DACs which are widely used for data conversion at the front-end of mixed-signal ICs.

Most delta-sigma modulators in production today employ single-bit quantization. A key feature of an ADC or DAC based on one-bit delta-sigma modulation is its ability to achieve arbitrarily high linearity. This feature is the result of the inherent linearity of a one-bit DAC. A multi-bit DAC cannot be made perfectly linear since it is impossible to create a transfer characteristic with steps of exactly equal height. Since non-idealities in the DAC are equivalent to noise added directly to the input signal of a delta-sigma ADC (or to the output in delta-sigma DAC), DAC errors can easily be the performance-limiting factor in a delta-sigma converter.

Were it not for this drawback, the use of multi-bit quantization would improve a delta-sigma modulator's performance by increasing the modulator's resolution or increasing the modulators's bandwidth, while at the same time, whitening the quantization noise and improving modulator stability. These powerful incentives have led a number of researchers to develop such schemes as element-randomization [4-6], individual-level averaging [7, 8], and digital calibration [9] to combat the problems caused by imperfect DACs.

More recently, schemes were invented which make the errors caused by mismatch in a multi-bit unit-element DAC appear as first-order shaped noise [10-15]. One of the methods has since been generalized to arbitrary-order lowpass and bandpass shaping in [16]. This thesis explores the implementation of the mismatch-shaping technique, presenting new schemes which are more hardware-efficient, and designing prototype ICs to corroborate the theory.

#### 1.2 Thesis Outline

The fundamentals of delta-sigma modulation are reviewed in Chapter 2, along with brief descriptions of some existing element-matching techniques. Chapter 3 presents some analytical and architectural work related to the realization of mismatch-shaping logic. A generalized butterfly shuffler scheme capable of implementing various noise transfer functions (NTFs) is also presented in Chapter 3. Chapter 4 explores the possibility of applying mismatch-shaping to non-unit-element DACs by designing a 2-segmented DAC with mismatch-shaping only on the MSB part. A 16-element SC DAC which has been implemented on a prototype IC, along with some high-order delta-sigma modulator designs is given in Chapter 5. The experimental results are presented in Chapter 6. Chapter 7 summarizes the work and gives a few suggestions for future work.

#### Chapter 2. Background: Delta-Sigma Modulation and Mismatch-Shaping

This chapter presents the material necessary to understand  $\Delta\Sigma$  modulators in general and this thesis in particular. Starting with a brief review of quantization, the discussion progresses to 1<sup>st</sup>-order, then high-order and bandpass  $\Delta\Sigma$  modulators. Multibit modulators are introduced thereafter. At the end of the chapter, the effect of DAC nonlinearity in  $\Delta\Sigma$  modulators is discussed along with some means for dealing with this important issue.

#### 2.1 Quantization

#### 2.1.1 Quantization and Quantization Noise

Quantization refers to the process of subdividing a quantity into a small but measurable increment. In electrical engineering, such a quantity can be the magnitude of an analog signal, such as voltage or current. It can even be a digital signal if quantization involves reducing the bit-width. A clock is needed to sample the signal and to initiate the quantization. Periodically sampling a continuous signal at a rate more than twice the signal bandwidth does not introduce distortion, but quantization does.

The most commonly used quantization is uniform quantization, which has equal quantization steps denoted as  $\Delta$ . An example is shown in Figure 2.1 (a), where the continuous amplitude signal x is rounded to the nearest of 8 discrete levels. It is evident that the quantized signal y can be represented by

$$y = Gx + e, (2.1)$$

where the gain G is the slope of the straight line that passes through the center of the quantization characteristic, and e is the quantization error shown in the same picture.

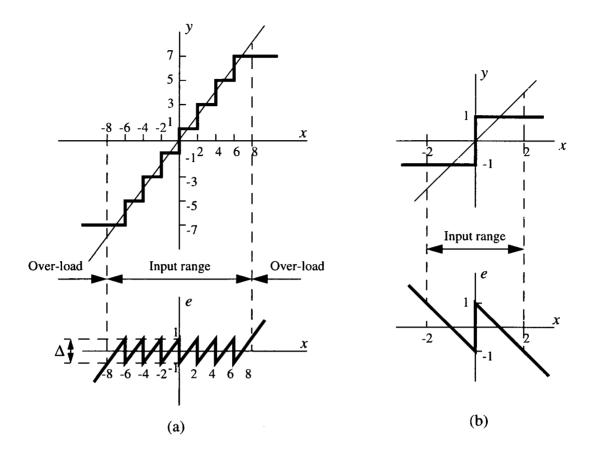

Figure 2.1: (a) An example of uniform multi-level quantization characteristic. (b) Single-bit quantization.

Other non-ideal effects, such as dc offset and non-linear gain error, can be added into Eq. (2.1) when necessary.

If there are a total of  $2^n$  quantization levels, we call it an *n*-bit quantization. For the example shown in Figure 2.1 (a) the quantizer is a 3-bit quantizer. If the input range is normalized to  $\pm 1$ , the quantization step, or the value of the least-significant-bit (LSB) is then given by  $\Delta = 2/(2^n - 1)$ . The error *e* is completely defined by the input, but if the input changes randomly between samples by amounts comparable with or greater than  $\Delta$ , and without saturating the quantizer, then *e* is largely a random variable uniformly distributed in the range  $\pm \Delta/2$ . Under these assumptions the mean-square value of *e*, i.e. the power of the quantization error is given by

$$\sigma_e^2 = \frac{1}{\Delta} \int_{-\frac{\Delta}{2}}^{\frac{\Delta}{2}} e^2 de = \frac{\Delta^2}{12}.$$

(2.2)

Through simple calculations, the peak signal-to-noise ratio (SNR) of an ideal n-bit linear quantizer with a full-scale sine-wave input can be found to be approximately 6n dB.

Notice that the above consideration remains applicable to a 2-level (single-bit) quantizer, as illustrated in Figure 2.1 (b), but in this case the choice of the gain G is arbitrary.

In conventional Nyquist rate ADCs or DACs, higher resolution is achieved by using smaller step sizes (i.e. increasing *n*), which requires precisely matched analog components. As a result, the practical limit with current (untrimmed) circuit techniques is about 14 bits of resolution. Trimmed circuits can achieve 16 or more bits of resolution, but are expensive. In a Nyquist rate ADC or DAC, precision analog circuits, such as highgain op amps, linear integrators, etc., have no opportunity to exert their power because a complete conversion must be performed in every clock period.

#### 2.1.2 Oversampling in Quantization

Oversampling [1, 2] is simply the process of sampling faster than the Nyquist criterion requires. If the signal occupies the band from DC to  $f_B$  and the sampling rate is  $f_s$ , the oversampling ratio (OSR) R is defined as  $R = f_s/(2f_B)$ . Oversampling eases the anti-alias filter design since a wide transition band is created by the increased separation between the signal band and its first alias. For quantizers with broadband quantization noise, oversampling also reduces the amount of in-band quantization noise. This allows the conversion to be more accurate than the resolution of the quantizer. Specifically, each

octave increase in the OSR results an increase in resolution of 3 dB (0.5 bit). As the next section will show,  $\Delta\Sigma$  modulation improves significantly on this trade-off.

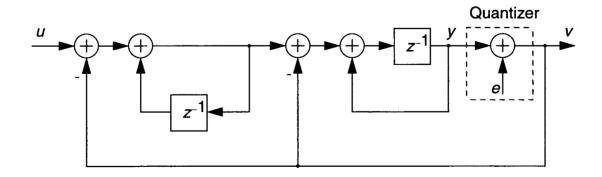

#### 2.2 First-Order Delta-Sigma Modulator

A 1<sup>st</sup>-order lowpass  $\Delta\Sigma$  modulator with a single-bit quantizer is shown in Figure 2.2. Since the loop contains two operations: subtraction (" $\Delta$ ") of the fed back output signal from the input signal and integration (" $\Sigma$ ") of the differences, it is called a "delta-sigma" modulator. The modulator works in the following way: if an error is introduced at the quantizer at one time step, it will be subtracted from the next output so that the output tracks the input at low frequencies. From a system level point of view, the negative feedback forces the DC value of the modulator output,  $\nu$ , to be the same as the input signal,  $\mu$ , so that the integrator, which otherwise would be unstable, sees an input with zero DC content. Therefore, a 1<sup>st</sup>-order  $\Delta\Sigma$  modulator has ideally unlimited resolution for DC signals.

The z-domain description of the system is

$$V(z) = z^{-1}U(z) + (1 - z^{-1})E(z), \qquad (2.3)$$

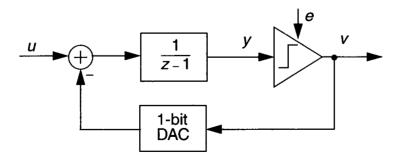

Figure 2.2: A first-order single-bit  $\Delta\Sigma$  modulator.

where v(n) is a discrete-time 2-level signal, and E is the quantization error [17]. According to Eq. (2.3), the quantization error is frequency-shaped by the function  $H(z) = 1 - z^{-1}$ . H(z) is called the noise transfer function (NTF) which, in this example, has a zero at DC and thus suppresses the quantization noise in the vicinity of DC. Likewise, the input signal U is also frequency-shaped by a function called signal transfer function (STF) G(z) which is simply  $z^{-1}$  in this example. An STF can be viewed as the signal gain of the modulator and should be unity or a constant within the-band-of-interest. The spectrum of the output of MOD1 in Figure 2.3 clearly shows the shaping of the quantization noise.

Assuming that E is white with power  $\sigma_e^2$ , the in-band noise power is given as

$$N_0^2 = \frac{\sigma_e^2}{\pi} \int_0^{\frac{\pi}{R}} |H(e^{j\omega})|^2 d\omega \approx \frac{\sigma_e^2}{\pi} \int_0^{\frac{\pi}{R}} \omega^2 d\omega = \frac{\sigma_e^2 \pi^2}{3R^3} , \qquad (2.4)$$

Figure 2.3:(a) The frequency response of  $1-z^{-1}$ , and (b) the simulated spectrum of first-order  $\Delta\Sigma$  modulator with sine-wave input shows the shaping of quantization noise.

where R is the OSR. If E is uniformly distributed in [-1, 1], according to Eq. (2.2),  $\sigma_e^2 = \frac{\Delta^2}{12} = \frac{1}{3}.$

Eq. (2.4) predicts that an octave (factor of two) increase in R will increase the SNR by 9 dB. In principle, the in-band noise can be made as small as desired, simply by making R large enough. Thus,  $1^{\text{st}}$ -order  $\Delta\Sigma$  modulators have potentially unlimited accuracy, independent of component matching and many other idealities. In general, the resolution of a  $\Delta\Sigma$  converter is improved by clocking faster (which is easy) and not by making larger, more sensitive analog circuitry (which is hard).

An important property of single-bit modulators is what is often referred to as "inherent linearity" [18]. This property comes from the fact that the input-output transfer curve of any static two-level DAC can be modeled exactly by a straight line joining the two points on the curve. A binary DAC is therefore ideal and cannot introduce errors other than simple offset and gain errors. These errors do not introduce distortion and the conversion is "linear."

The primary disadvantage of 1<sup>st</sup>-order  $\Delta\Sigma$  modulators is that a high oversampling ratio is needed to achieve high resolution. For example, if we want 16-bit resolution, the oversampling ratio must be about 1500. Except for very low-frequency applications, a high oversampling ratio leads to a high sampling frequency and thus difficulties in implementation. As the next section will show, the oversampling ratio required to achieve a given resolution can be made smaller if higher-order  $\Delta\Sigma$  modulators are used.

#### 2.3 High Order Delta-Sigma Modulators

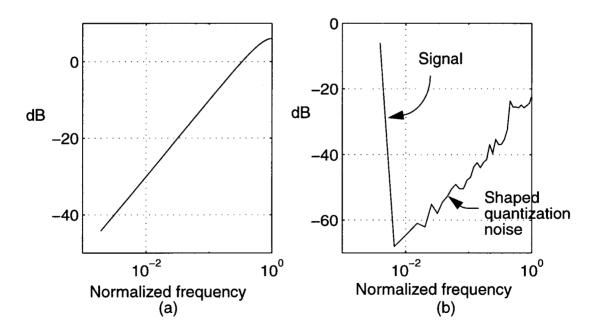

Figure 2.4 shows a general model of a  $\Delta\Sigma$  modulator followed by a decimation filter. The modulator consists of three parts: a loop filter, a quantizer and a feedback DAC. Modeling the quantizer with V=Y+E, the output of the modulator is

$$V(z) = G(z)U(z) + H(z)E(z),$$

(2.5)

where G(z) and H(z) are the STF and the NTF, respectively, of the modulator. To achieve spectral separation between signal and noise, the STF must be approximately one in the band of interest whereas the NTF must be approximately zero. The decimation filter eliminates the out-of-band noise and downsamples the signal to the Nyquist rate. Decimation is beyond the scope of this thesis, and will not be discussed further.

The NTF of the  $1^{st}$ -order  $\Delta\Sigma$  modulator discussed in the previous section has a zero at DC and thus suppresses the quantization noise in the vicinity of DC by a first-order

Figure 2.4: A general  $\Delta\Sigma$  modulator.

filtering. More aggressive suppression of the in-band quantization noise can be achieved by constructing higher order NTFs which place more than one zero at DC. Figure 2.5 shows a simple  $2^{nd}$ -order  $\Delta\Sigma$  modulator. The loop filter consists of two integrators in cascade. The feedback DAC is omitted for the sake of simplicity. The output of the modulator is

$$V(z) = z^{-1}U(z) + (1 - z^{-1})^{2}E(z),$$

(2.6)

so the NTF is  $H(z) = (1 - z^{-1})^2$ ; H(z) has two zeros at DC. Assuming that E is white with power  $\sigma_e^2$ , the in-band noise power is then given as

$$N_0^2 = \frac{\sigma_e^2}{\pi} \int_0^{\pi} |H(e^{j\omega})|^2 d\omega \approx \frac{\sigma_e^2 \pi^4}{5R^5}.$$

(2.7)

Eq. (2.7) predicts that an octave (factor of two) increase in R will increase the SNR by 15 dB, which, compared with the 1<sup>st</sup>-order  $\Delta\Sigma$  modulator, is a 6 dB/octave improvement.

Even higher order modulators can be built by employing higher order NTFs. Also, the positions of the zeros in high order NTFs do not need to be all at DC. Certain loop filter coefficients can be chosen to split the zeros around DC to optimize the in-band NTF response.

Figure 2.5: Second-order  $\Delta\Sigma$  modulator.

In deriving the transfer functions, the quantizer was modeled as v = y + e. This allows the quantizer, a nonlinear system, to be treated as a linear system with independent inputs y and e. Note that e and y are in reality functionally related and therefore not independent. For linear systems with stable transfer functions, the output and the internal states are bounded if the input is bounded. However, the same cannot be said for  $\Delta\Sigma$  modulators with stable signal and noise transfer functions, because e is not a real input—e is derived from y, in a nonlinear way. It is possible for G(z) and H(z) to be stable and yet result in a modulator with unbounded internal states. For a  $1^{st}$ -order modulator, it is easy to show [18] that if  $|u| \le 1$ , then the state y is bounded with  $|e| \le 1$ . But for higher-order modulators, the stability issue is much more complicated [19-27].

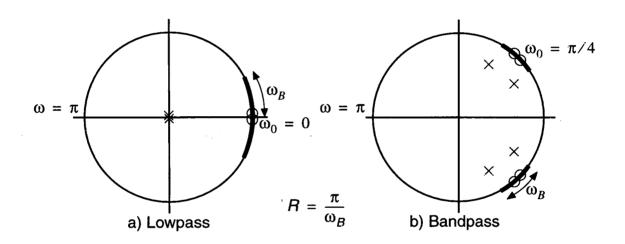

#### 2.4 Bandpass Delta-Sigma Modulators

A lowpass  $\Delta\Sigma$  modulator places NTF zeros near  $\omega=0$  in order to null quantization noise in a narrow band around DC. Noise-shaping can be extended to the bandpass case simply by placing the NTF zeros at a non-zero frequency  $\omega_0$ . Quantization noise is then suppressed in a narrow band around  $\omega_0$ , and the output bit-stream accurately represents the input signal in this narrow band. A system which achieves this result is called a bandpass  $\Delta\Sigma$  modulator [28-30]. Figure 2.6 compares the pole/zero locations of a lowpass NTF and a bandpass NTF.

A conceptual diagram of a bandpass  $\Delta\Sigma$  ADC is given in Figure 2.7. A narrowband analog input is converted directly to a 1 bit oversampled digital signal with noise-shaping around the passband. The decimation filter suppresses the out-of-band quantization noise and downsamples the filtered signal to a baseband digital signal.

The obvious advantage of a bandpass  $\Delta\Sigma$  modulator is that the sampling frequency is only several times  $(2\pi/\omega_0)$  greater than the signal center frequency  $\omega_0$ . A direct implementation of lowpass  $\Delta\Sigma$  modulator for an intermediate-frequency (IF) or radio-frequency (RF) narrow band signal would result in a sampling rate which is much higher than that required by a bandpass modulator.

Bandpass  $\Delta\Sigma$  modulators are most attractive for the conversion of high-frequency narrowband signals to digital form [28-32]. However, in such applications, discrete-time

Figure 2.6: The passbands and pole/zero locations of the noise transfer functions for (a) lowpass and (b) bandpass  $\Delta\Sigma$  modulation.

Figure 2.7: A diagram of a bandpass  $\Delta\Sigma$  ADC.

modulators must sample fast-slewing signals and will therefore require a sample-and-hold circuit with low aperture error.

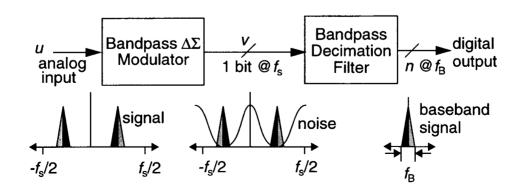

#### 2.5 Multi-bit Delta-Sigma Modulator

Although most  $\Delta\Sigma$  modulators in production today employ single-bit quantization, the discussions in the previous sections can be applied to systems with multi-bit quantizers. The same 1<sup>st</sup>-order, high-order, and bandpass modulation structures can be realized with multiple quantization levels. The advantage is obvious: since the quantization step  $\Delta$  in Eq. (2.2) is now smaller, the overall power of the quantization error  $\sigma_e^2$  is reduced. Therefore, higher resolution can be achieved. From another point of view, since the noise level is lower, there is now more room for us to expand the signal bandwidth by decreasing the OSR while at same time maintaining the same resolution. The stability is also improved. This improvement in the stability makes higher-order and more aggressive NTFs feasible. Furthermore, the design of the decimation filter after a multi-bit  $\Delta\Sigma$  ADC or the analog reconstruction filter after a DAC is eased and can have a lower order since the out-of-band noise floor is lower. In other words, the unfiltered output more closely resembles the desired output in the multi-bit case. Also, in a DAC system the slew rate requirements of the analog output stage can be relaxed and the system has better immunity to edge jitter due to smaller output steps. Lastly, in an ADC system where the loop filter processes the difference between the input and the fed-back output, loop filter linearity is much less of a problem with multi-bit feedback since the difference signal is small. A more subtle advantage of multi-bit quantization is that it helps to whiten the quantization noise so that the modulator suffers less from tone problems.

Despite all these advantages, there is one major obstacle which stands in the way of using multi-bit quantizers in  $\Delta\Sigma$  modulators: DAC nonlinearity. Figure 2.8 shows how

DAC non-idealities (D) affect  $\Delta\Sigma$  modulators. In a  $\Delta\Sigma$  ADC system, D is frequency-shaped by (H-1). Since the NTF H has to be approximately zero within the band-of-interest in order to attenuate the quantization error E, D can not be suppressed at the same frequencies. In a  $\Delta\Sigma$  DAC system, non-idealities in the DAC are equivalent to noise added directly to the output. Therefore, DAC mismatch errors can easily be the performance-limiting factors in a  $\Delta\Sigma$  ADC or DAC. On the other hand, a binary DAC is "inherently linear" and so does not require precise component matching. That is why single-bit quantizers became so popular that many people misunderstood it as a peculiarity of  $\Delta\Sigma$  modulation and proudly printed "1-bit DAC" on their products.

a) ADC system

Figure 2.8: A multi-bit  $\Delta\Sigma$  modulator.

#### 2.6 Existing Dynamic Matching Schemes

The powerful incentives for using multi-bit  $\Delta\Sigma$  modulators have led a number of researchers to employ such technologies as laser trimming, digital calibration [9], and dynamic element-matching [4-8] [10-16] [33-37] to combat the problems caused by component mismatch. This thesis focuses on developing dynamic element-matching schemes. Some of the existing dynamic matching architectures are introduced in the following sections.

#### 2.6.1 Parallel Single-Bit Modulators

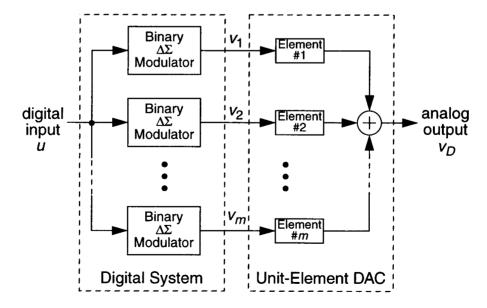

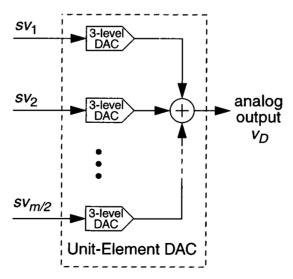

The most straight-forward way of making an m-level  $\Delta\Sigma$  DAC insensitive to element mismatch is to use m parallel single-bit modulators to drive m one-bit DACs, as shown in Figure 2.9. The output of the system (neglecting DC offsets) is

$$V_D(z) = KU(z) + H(z)(E_1(z) + \dots + E_m(z))$$

(2.8)

Figure 2.9: Multi-level  $\Delta\Sigma$  DAC using parallel 1-bit modulators.

where K is the sum of the gains of the m binary DACs, and the E's are the quantization errors introduced by each modulator. This system shows that DAC errors can be rendered harmless. Other than that, the architecture does not seem to be very useful because it can hardly be called a "multi-bit" modulator. It duplicates the same branches, puts them in parallel, and then sums up their outputs. By doing so, it actually ends up with nothing but higher power consumption and larger chip area. From the frequency domain, it is more clear because all it does is add m 1-bit spectra together. By nature, it is still a single-bit modulator.

#### 2.6.2 Element Randomization [4-6]

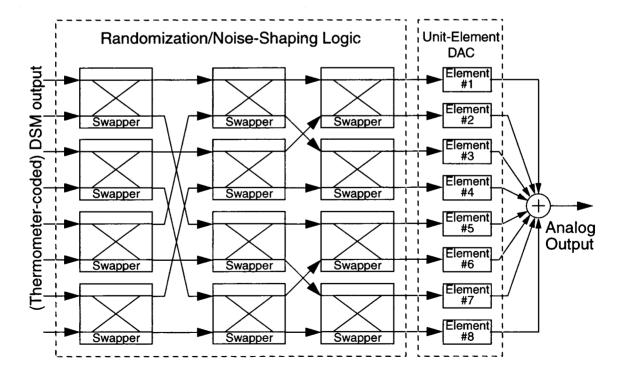

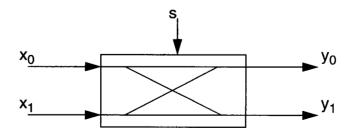

There are many element-matching schemes today. Although some may not use the term, they all fall under what is called "dynamic element-matching" [6] in this thesis, because they all try to attenuate element mismatch errors by using some algorithm to select among equivalent elements when constructing the analog representation of a given code. Perhaps the first dynamic matching idea was simply to randomly pick the elements to use [4]. Figure 2.10 shows a unit-element-randomization structure, namely a butterfly shuffler which is constructed with swapper cells [6, 15]. As will be discussed in later sections, the butterfly shuffler can be used to noise-shape the mismatch errors if a certain noise-shaping logic is designed to control the swappers. Random selection whitens the spectrum of the mismatch-induced error, but does not provide spectral shaping of the DAC errors.

#### 2.6.3 Individual Level Averaging [7, 8]

In 1992, Leung proposed the individual level averaging approach [7]. Each time a certain input code appears, the unit-element DAC tries to construct the analog output using a different set of elements. After all the patterns are explored, the operation resets

and iterates. It was found that this approach not only reduced the harmonic distortion introduced by the DAC mismatch errors but also moved some of the error energy from low frequencies to high frequencies. Although the technique proved to be less effective than later schemes, it is one of the earliest demonstrations that the mismatch noise can be spectrally shaped. An important feature of a unit-element DAC, namely that the average of the analog output over all element permutations is error-free, was the key to this algorithm.

#### 2.6.4 First-Order Mismatch-Shaping Architectures [10-15]

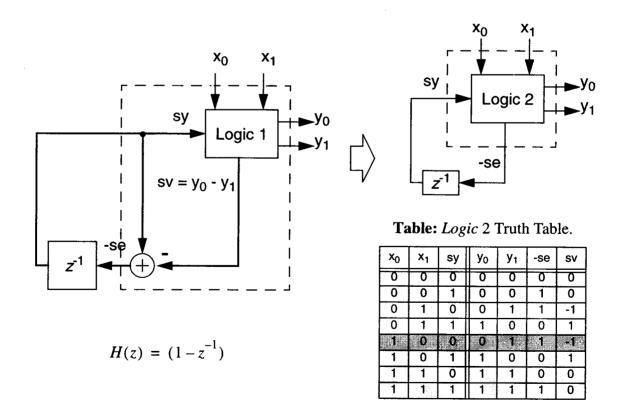

Two efficient mismatch-shaping schemes will be introduced in this section. They both demonstrate 1<sup>st</sup>-order lowpass mismatch-shaping.

Figure 2.10:An 8-element DAC driven by a butterfly shuffler.

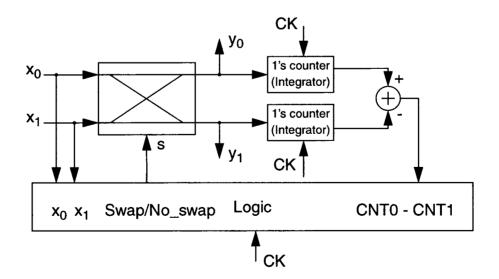

The first scheme is based on the butterfly shuffler introduced in Section 2.6.2. By making the swapper cells into finite-state-machines which seek to equalize the activity of their outputs, Adams and Kwan found that mismatch errors in the DAC become 1<sup>st</sup>-order-shaped [15]. A 1<sup>st</sup>-order mismatch-shaping swapper cell is shown in Figure 2.11. The truth table of the swapper is shown below. A detailed analysis will be given in Chapter 3.

| x <sub>1</sub> | x <sub>0</sub> | CNT0-CNT1 | S | New CNT0-CNT1 |

|----------------|----------------|-----------|---|---------------|

| 0              | 0              | 0         | х | 0             |

| 0              | 0              | 1         | x | 1             |

| 0              | 1              | 0         | 1 | 1             |

| 0              | 1              | 1         | 0 | 0             |

| 1              | 0              | 0         | 0 | 1             |

| 1              | 0              | 1         | 1 | 0             |

| 1              | 1              | 0         | × | 0             |

| 1              | 1              | 1         | х | 1             |

Table 2.1: 1st-order mismatch-shaping swapper truth table.

Figure 2.11:A 1<sup>st</sup>-order mismatch-shaping swapper.

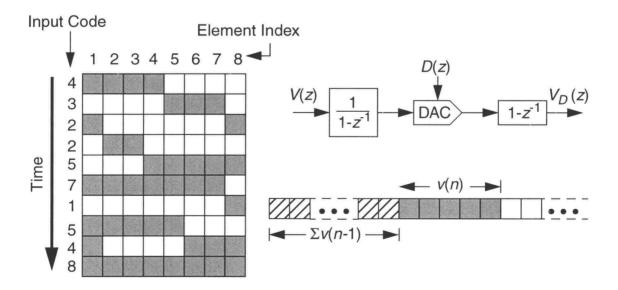

Another highly practical scheme which results in 1<sup>st</sup>-order shaped mismatch errors is the element rotation scheme [10-14]. To illustrate this algorithm, an 8-element DAC example is shown in Figure 2.12. When choosing the DAC elements to construct an analog output, the algorithm starts from the "next" element instead of always starting from the very first element (say, element 1) as a conventional DAC does. For example, as shown in Figure 2.12, since it stopped at element 4 after finishing with the first input code, it starts from element 5 when the second code comes in. When the end of the element array (i.e. element 8 in the example) is reached, the algorithm wraps around to element 1. A conceptual explanation of the element rotation scheme is shown in the left part of Figure 2.12. Evidently,  $V_D(z) = KV(z) + (1-z^{-1})D(z)$ , where K is the DAC gain, so DAC errors are 1<sup>st</sup>-order shaped. To see how this result emerges, imagine there is a DAC with infinite number of elements. Each time when a digital input code v(n) comes in, the integrator which precedes the DAC will activate v(n) more elements starting from where it stopped previously, while the differentiator will deactivate the previous elements at the same time. Merging these two operations together and stacking a real

Figure 2.12:1st-order mismatch-shaping with element rotation scheme.

DAC's elements end-to-end, we then end up with the element rotation scheme. This scheme is very hardware-efficient.

Both of the schemes discussed in this section demonstrate 1<sup>st</sup>-order lowpass mismatch-shaping.

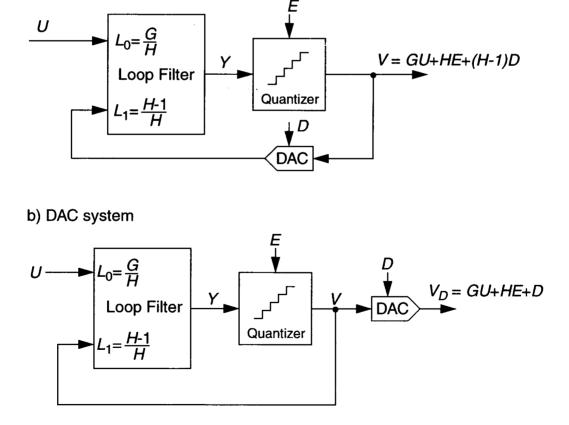

# 2.6.5 General Mismatch-Shaping Architectures [16, 33, 34, 35]

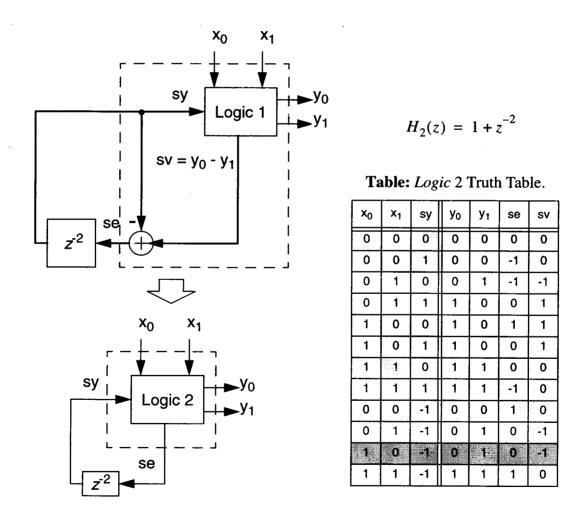

After 1<sup>st</sup>-order shaping was demonstrated, the question, "Are there any schemes capable of high-order or bandpass mismatch-shaping?" springs immediately to mind. The answer is "yes." Two general mismatch-shaping DAC architectures are introduced in the following paragraphs.

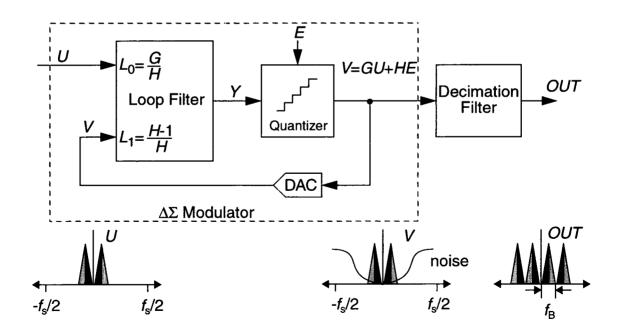

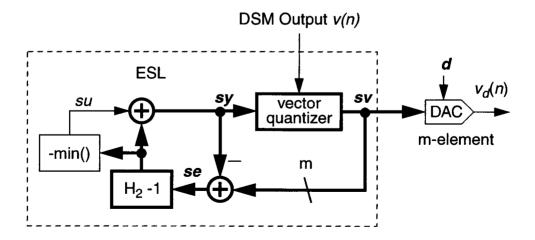

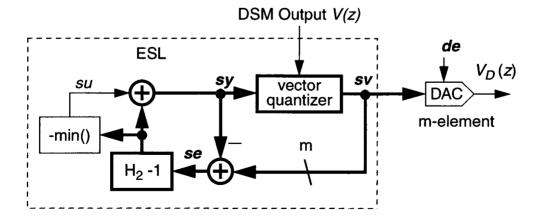

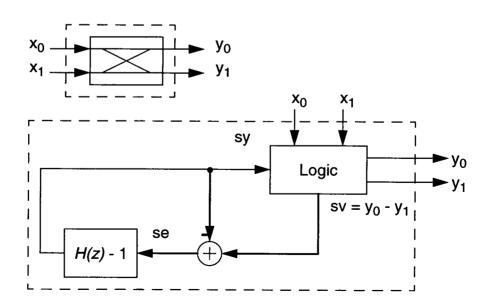

Figure 2.13 shows the block diagram of a general element-selection logic (ESL) [16, 33]. The bold font and the thick lines in the diagram represent m-dimensional vectors. Each element in sv is a 1-bit number (i.e. either "1" or "0"), while the word-length of the elements in se and sy are in general larger. The "vector quantizer" quantizes sy to sv in

Figure 2.13:A mismatch-shaping DAC with an ESL analogous to  $\Delta\Sigma$  modulation.

such a way that the distance between the two vectors is minimized, with the restriction that the sum of the elements in sv equals v(n). The analog output of the DAC is given by

$$V_D(z) = V(z) + H(z)(SE(z) \cdot de). \tag{2.9}$$

where de is an m-element vector containing the difference between the actual value and the ideal value of each element. By properly choosing a mismatch transfer function (MTF) H(z) which yields a bounded se sequence, higher order and bandpass mismatch-shaping can be achieved. If  $H(z) = 1 - z^{-1}$ , the system is equivalent to the element rotation scheme. More detailed discussions will be given in Chapter 3.

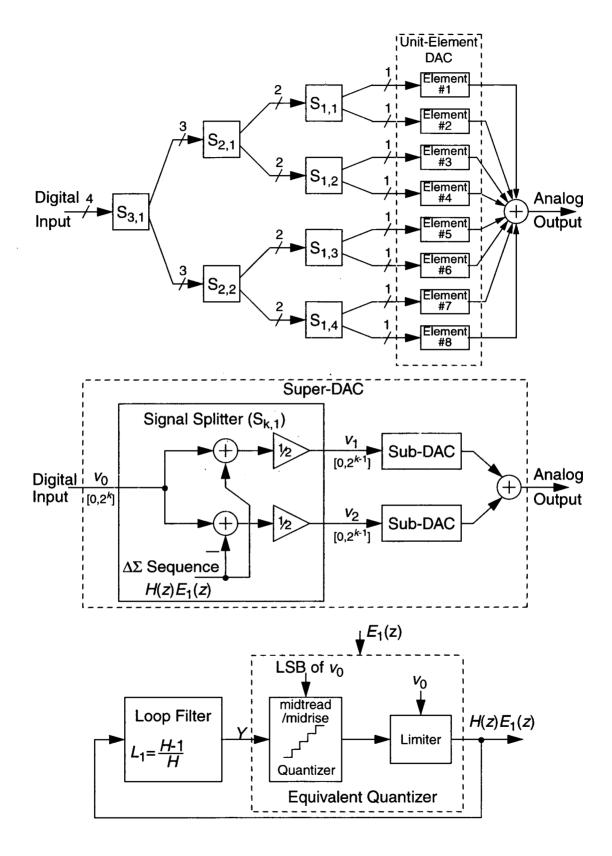

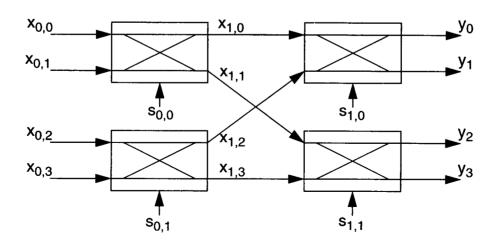

Another scheme capable of arbitrary mismatch-shaping is the tree-structure shuffler presented by Galton [34, 35]. As shown in Figure 2.14, a  $2^n$ -element DAC can be recursively decomposed into pairs of sub-DACs until the sub-DACs are reduced to the binary case. Notice that in the binary case, this structure is equivalent to the swapper described in Section 2.6.4. At each level of recursion the signal splitters are driven by  $\Delta\Sigma$  sequences in the way shown in the bottom of the diagram. Assume that the digital input signal  $v_0(n)$  to the decomposed system shown in Figure 2.14 can be written as some desired signal v(n) plus a (bounded) error term which is shaped by a transfer function H(z), i.e.  $V_0(z) = V(z) + H(z)E_0(z)$ . Suppose the shaped sequence which drives the signal splitter can be described as  $H(z)E_1(z)$  (the  $e_1$  sequence is assumed to be bounded). Thus, the signals which drive the two sub-DACs are  $V_{1,2}(z) = V(z)/2 + H(z)(E_0(z)\pm E_1(z))/2$  and are therefore of the same form as that supposed originally. Applying induction, we conclude that the sequences which drive the unit-elements (i.e. binary DACs) are  $\Delta\Sigma$  sequences. Thus the DAC output, neglecting DC offsets, is

$$V_D(z) = (1 + \overline{D})V(z) + H(z)E_D(z),$$

(2.10)

where  $\overline{D}$  is the average of the element errors and  $E_D(z)$  is a linear combination of the  $E_i(z)$  signals with weighting factors that are themselves linear combinations of the

Figure 2.14:Mismatch-shaping DAC using tree-structure shuffler.

element errors. Assuming the  $e_D$  sequence is bounded, Eq. (2.10) shows that the DAC output consists of the ideal output (multiplied by a scaling factor) plus a noise-shaped error term.

Also shown in Figure 2.14 is a shaped sequence generator structure presented in [34, 35] but drawn in a more general form here. Similar to the other structure mentioned earlier in this section, a delta-sigma loop with zero input is used to generate the shaped sequence. The equivalent quantizer block in the loop imposes certain constraints which force the signal splitter to split the input signal in such a way that no overflow will occur. These constraints are the sources which introduce the selection errors  $E_i$ , and hence are the key factors in determining the loop's stability.

Both of the DAC architectures introduced in this section have demonstrated highorder and bandpass mismatch-shaping in simulation. More details will be discussed in the next chapter.

#### 2.7 Conclusions

$\Delta\Sigma$  modulation basics and some of the existing mismatch-shaping schemes were reviewed and discussed in this chapter. By combining these techniques, high-performance multi-bit  $\Delta\Sigma$  modulators can be constructed.

## **Chapter 3. Element-Mismatch-Shaping Architectures**

This chapter takes a closer look at some mismatch-shaping architectures. Comparisons between the delta-sigma ESL and the tree-shuffler are made using simulations and analytical techniques. A design of the vector quantizer and a revised delta-sigma ESL are proposed, and a butterfly shuffler architecture capable of high-order/bandpass mismatch-shaping is presented.

# 3.1 Comparison between Delta-Sigma ESL and Tree Shuffler

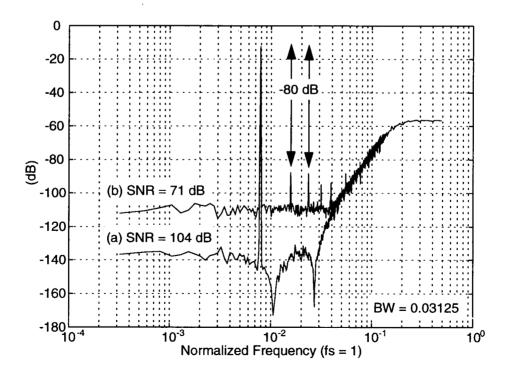

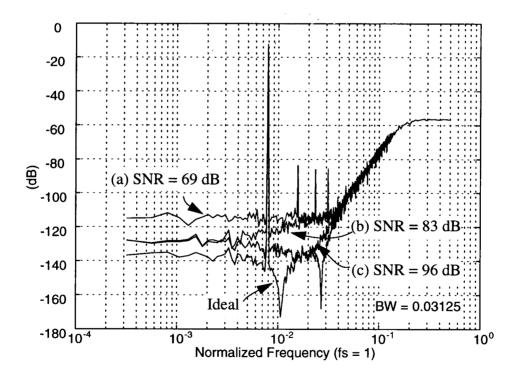

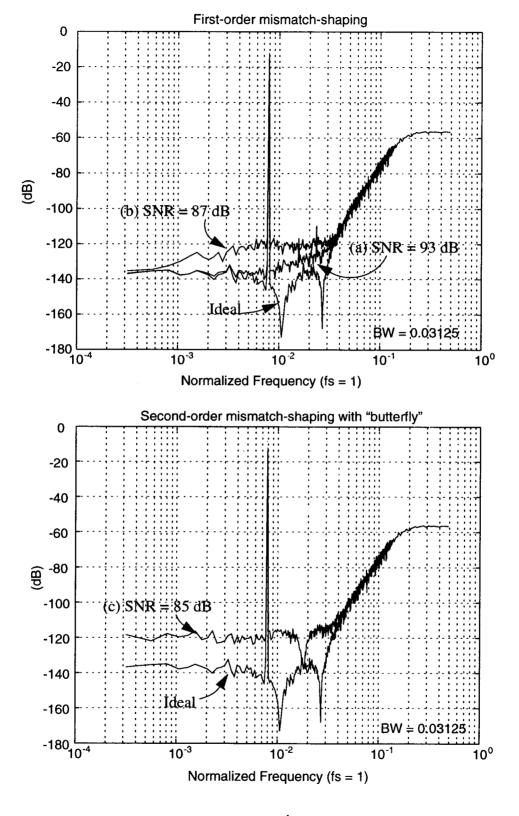

Simulations were done to compare the delta-sigma ESL and the tree shuffler. A 17-level modulator with a  $4^{th}$ -order lowpass NTF optimized for OSR = 16 whose infinity norm is 4 is used in the comparisons. The modulator is driven by a sine wave input situated at 1/4 of the band-of-interest with a magnitude of 3/4 of full-scale. The modulator output v is shuffled by the mismatch-shaping logic and then converted to analog form by a 16-element DAC whose element values have a standard deviation of 0.5%. As shown in Figure 3.1, with an OSR of 16, the SNR is reduced from 104 dB in the ideal case to 71 dB without any dynamic matching effort, and the  $2^{nd}$ - and  $3^{rd}$ -order harmonics are both around 80 dB below the signal tone.

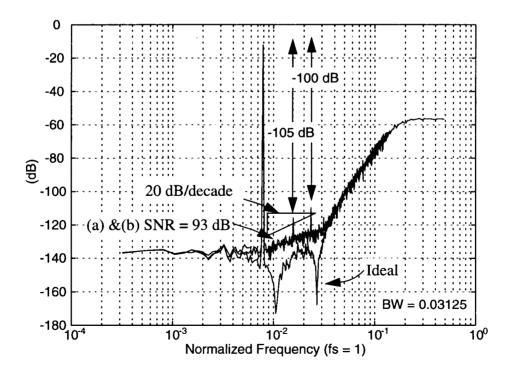

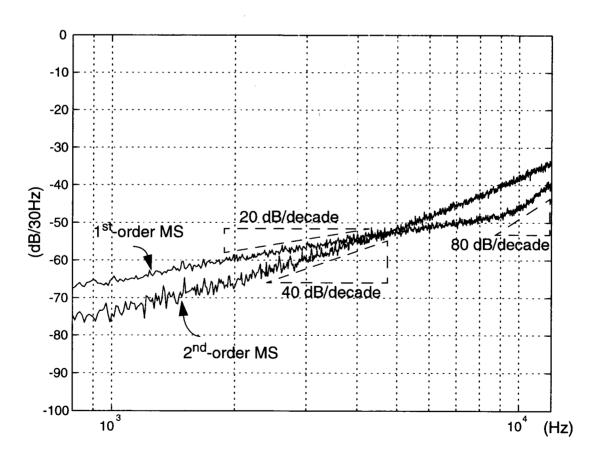

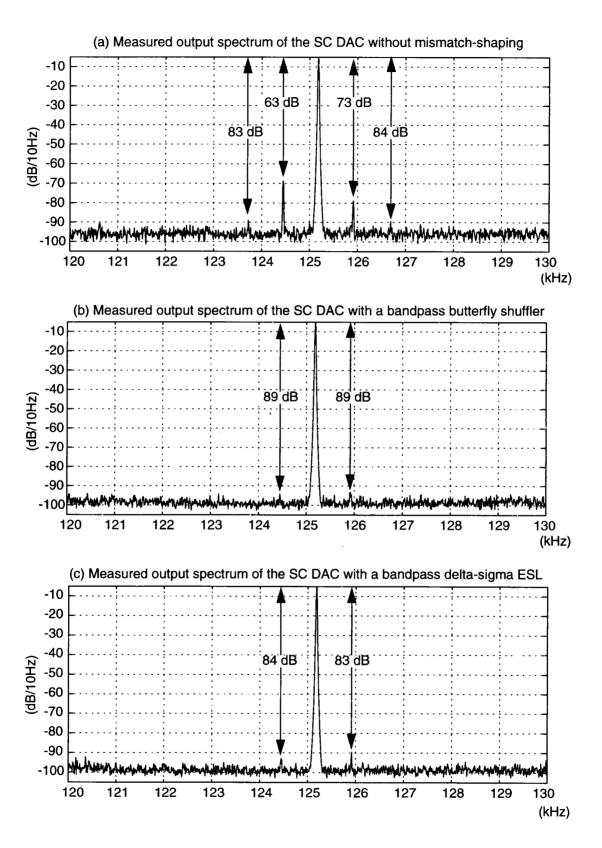

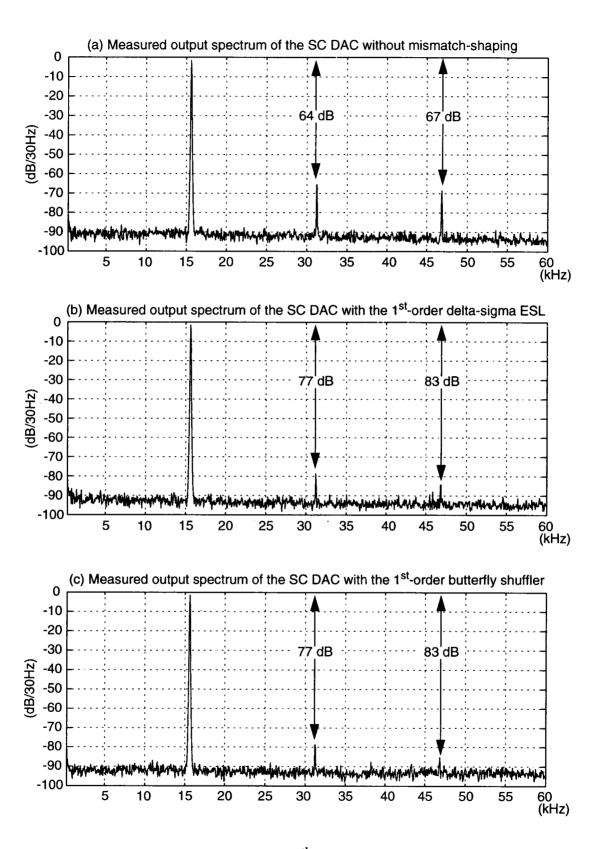

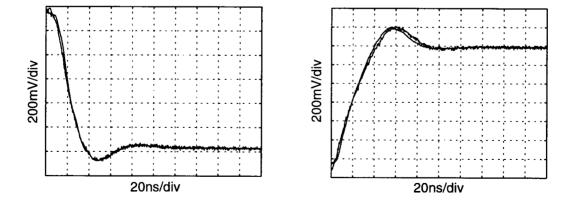

With first-order mismatch-shaping, great improvements are obtained, with both structures yielding similar performance. Figure 3.2 shows that the SNR is improved to 93 dB, and the 2<sup>nd</sup>- and 3<sup>rd</sup>-order harmonics are below -100 dB. The 20 dB/decade slope of the noise floor is consistent with the fact that the MTF is first-order.

Shown in Figure 3.3 are the spectra for second-order mismatch-shaping using these two competing architectures. The 2<sup>nd</sup>-order MTF  $H(z) = \frac{z^2 - 2z + 1}{z^2 - 1.25z + 0.5}$  that was simulated with the tree shuffler in [34, 35] is used in both schemes here. The delta-sigma

ESL yields an SNR of 92 dB, while the SNR of the tree shuffler is only 81 dB. The harmonics in both spectra are merged into the noise floor and hence invisible. The number of element permutations for the tree shuffler is much less than  $2^m$ , whereas a delta-sigma ESL can, in principle, select any of the  $2^m$  permutations. Therefore, the selection errors  $E_1$  introduced by the "equivalent quantizer" in the shaped sequence generator of the tree shuffler (shown in Figure 2.14) are relatively large with high-order MTFs. On the other hand, the delta-sigma ESL is open to all the possible element selection patterns, and the selection error SE (refer to Figure 2.13 and Eq. (2.9)) is minimized by the vector quantizer which takes the entire set of elements into account simultaneously. Therefore, the delta-sigma ESL tends to be more stable than the tree shuffler because there are less selection errors introduced. More aggressive MTFs can be tolerated by the delta-sigma ESL.

Figure 3.1: SNR and spectra of a 4<sup>th</sup>-order 17-level delta-sigma DAC with (a) an ideal DAC and (b) a 16-element DAC possessing 0.5% mismatch.

To demonstrate the theory, the delta-sigma ESL is simulated with an MTF optimized at OSR = 16 whose infinity norm is 1.8, and the SNR improves to 97 dB, outperforming the first-order mismatch-shaping schemes even at this low OSR, while the tree shuffler is not stable with this optimized MTF and does not demonstrate any mismatch-shaping.

In terms of implementation complexity, the delta-sigma ESL is very hardware-efficient in the first-order case because it can be reduced to the element rotation scheme. For higher-order mismatch-shaping, both the swapper and delta-sigma ESL architectures are very complicated because multiple delta-sigma loop filters are needed to implement ESLs and "signal splitters." Although the number of these delta-sigma loops are nearly the same in both cases (*m* parallel loops in a delta-sigma ESL and (*m*-1) in the tree shuffler

Figure 3.2: SNR and spectra of a 4<sup>th</sup>-order 17-level delta-sigma DAC with 1<sup>st</sup>-order mismatch-shaping using (a) tree-structure shuffler, (b) delta-sigma-like ESL.

to drive an *m*-element DAC), the loop filters in the early stages of a tree shuffler tend to require longer word-lengths. Also, extra logic is needed to implement the "equivalent quantizers" in a tree shuffler. However, it is hard to claim that high order delta-sigma ESLs are any simpler because complicated sorting circuits are needed to realize the vector quantizer. The hardware costs for the vector quantizer can be reduced by employing incomplete sorting algorithms [37, 38]. This, however will increase selection errors and degrade performance somewhat. Another minor advantage of the delta-sigma ESL is that it can drive any number of elements, while the tree structure requires the number of DAC elements to be a power of 2.

The discussion in this section concludes that, by producing less selection errors, delta-sigma ESLs tolerate more aggressive MTFs and can provide better performance in

Figure 3.3: SNR and spectra of a 4<sup>th</sup>-order 17-level delta-sigma DAC with 2<sup>nd</sup>-order mismatch-shaping using (a) tree-structure shuffler, (b) delta-sigma-like ESL and (c) optimized delta-sigma-like ESL.

high order mismatch-shaping than tree shufflers. However, both architectures are very complicated when high order MTFs are used.

## 3.2 Delta-Sigma ESL

The delta-sigma ESL architecture is discussed in the following sections. A design of the vector quantizer and a revised delta-sigma ESL are also presented.

#### 3.2.1 A Study on the Delta-Sigma ESL

For easy reference, the system diagram of a mismatch-shaping DAC with a deltasigma ESL previously shown in Figure 2.13 is re-drawn in Figure 3.4. As shown in the diagram, de is an m-element vector whose components are the element errors  $de_i$ . Since the element errors are defined as the difference between the actual element values and the average of all element values, the sum of the element errors is zero:

$$\sum_{i=1}^{m} de_i = \begin{bmatrix} 1 & 1 & \dots & 1 \end{bmatrix} \bullet de = 0.$$

(3.1)

Figure 3.4: A mismatch-shaping DAC with an ESL analogous to  $\Delta\Sigma$  modulation.

Since the sum of all the elements in the selection vector  $\mathbf{s}\mathbf{v}$  is equal to the value of the DAC input  $\mathbf{v}$ , the analog output of the DAC can be described as:

$$V_D(z) = SV(z) \bullet \left( \left[ A \ A \ \dots \ A \right]' + de \right) = AV(z) + SV(z) \bullet de$$

(3.2)

where A is the DAC gain (i.e. the average of all element values). The first term in Eq. (3.2) represents the signal and the shaped quantization errors, while the second term represents the DAC mismatch error, which is the focus of the discussion here.

By noticing that the ESL in Figure 3.4 is simply a vector version of the error feed-back structure of a delta-sigma modulator [2], we immediately write that:

$$SV(z) = SU(z) \begin{bmatrix} 1 & \dots & 1 \end{bmatrix} + H_2(z)SE(z).$$

(3.3)

Therefore, the DAC error at the output can be written as:

$$E_D(z) = SV(z) \bullet de = SU(z) \begin{bmatrix} 1 & \dots & 1 \end{bmatrix} \bullet de + H_2(z)SE(z) \bullet de.$$

(3.4)

Substituting Eq. (3.1) into Eq. (3.4), we have:

$$E_D(z) = H_2(z)SE(z) \bullet de, \qquad (3.5)$$

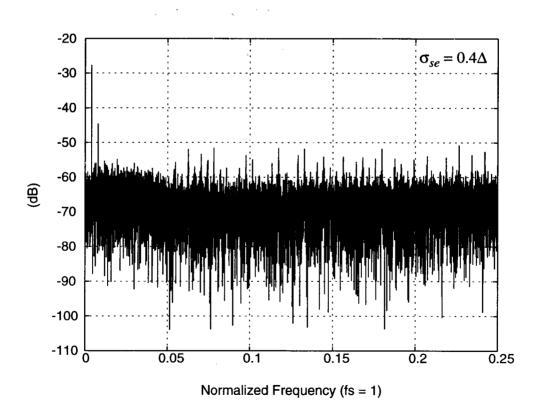

where  $H_2(z)$  is known, and de is an unknown vector with constant components for a given DAC. However, an analytical representation of se is somewhat hard to derive. A spectrum of one of the se components obtained from the simulation of the best performing system described in Section 3.1 (i.e.  $4^{th}$ -order modulator with  $2^{nd}$ -order optimized delta-sigma ESL) is shown in Figure 3.5. The spectra of the other se components are almost the same. Except for the signal tone and the  $2^{nd}$ -order harmonic, the rest of the spectrum is nearly white. The tone at the signal frequency usually does no harm to the DAC (it gives rise to a gain error), whereas the  $2^{nd}$ -order harmonic must be dealt with separately. Taking these two bins out of the spectrum, we derive a new vector  $se_N$  whose components can be treated as white noise which are the causes of the mismatch noise

described by Eq. (3.5). Assuming that the components of  $se_N$  are uncorrelated and white with rms values of  $\sigma_{se}$ , the corresponding noise spectral density is:

$$S_{DN}(\omega) = \frac{|H_2(e^{j\omega})|^2 \sigma_{se}^2}{\pi} \sum_{i=1}^m de_i^2 = \frac{|H_2(e^{j\omega})|^2 \sigma_{se}^2 m \sigma_{de}^2}{\pi},$$

(3.6)

where  $\sigma_{de}^2$  is the mean-square value of the *m* element errors. The in-band noise power at the DAC output can then be written as:

$$\sigma_{dv}^2 = \frac{1}{OSR} [(\sigma_1 \sigma_e)^2 + m(\sigma_2 \sigma_{se} \sigma_{de})^2], \qquad (3.7)$$

Figure 3.5: Spectrum of one of the se components.

where  $\sigma_1$  and  $\sigma_2$  are the rms values of  $H_1$  (NTF) and  $H_2$  (MTF) in the band of interest, respectively. Due to difficulties in calculating  $\sigma_{se_N}$  analytically, simulation is the main approach to estimate the SNR and to verify the stability of the system. Simulations with second-order MTFs appear to yield bounded state variables, while it is likewise easy to show that with higher order algorithms, the element selection logic is unstable.

Eq. (3.7) shows that the resolution of the DAC can be improved by reducing  $\sigma_{se}$ , the rms value of the selection error, as well as by the more obvious methods of reducing the element mismatch and optimizing the MTF. Enabling the DAC elements which correspond to the v(n) largest components of sy(n) minimizes the norm of the se(n) vector, and thus helps to keep signals finite. Since the priorities of the elements are obtained by sorting the components of sy(n), no difference will be made by alternative choices for su as long as it is a scalar. Setting su(n) to the negative of the minimum value of the output of the  $H_2(z)$ -1 block removes commonality in the sy(n) vector and helps to keep the components of sy finite and positive. According to Eq. (3.4), it is unlikely that  $E_D$  can be further reduced by generating a vector su(n) instead of using a scalar su(n) because it will make the first term non-zero, unless doing so can somehow cause the se(n) sequence to have a smaller  $\sigma_{se}$ . Vector quantizers with other algorithms producing smaller  $\sigma_{se}$  might also exist.

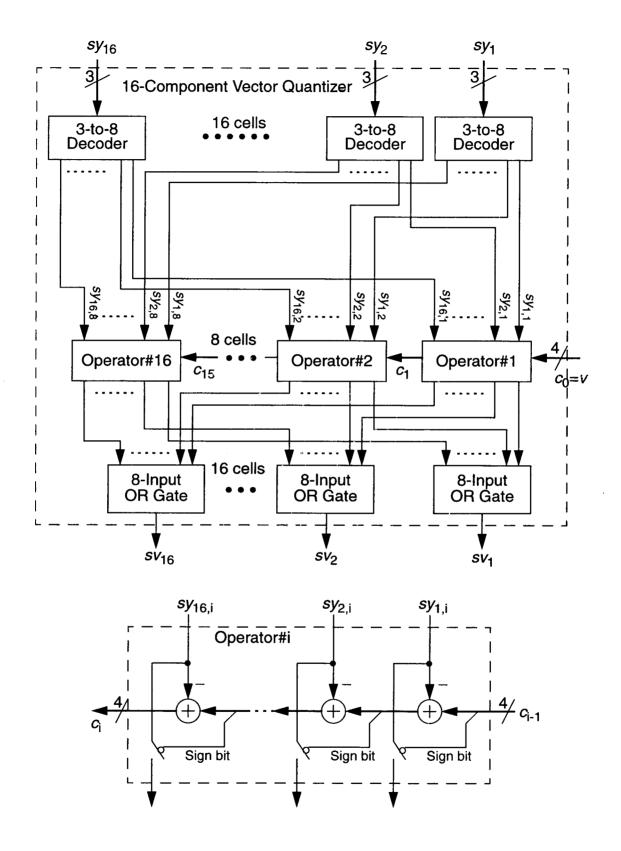

# 3.2.2 A Design of a Vector Quantizer

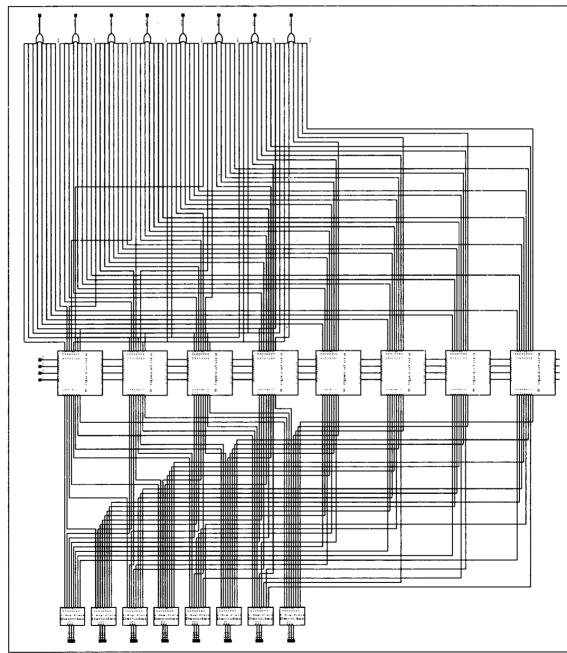

All blocks in the delta-sigma ESL shown in Figure 3.4 can be implemented with simple digital logic and normal digital filter structures, except for the vector quantizer. In the software version, the vector quantizer completely sorts the components of sy(n) in order to choose which elements to enable. Performing this operation in hardware requires complicated circuits, one of which is presented in this section.

A vector quantizer capable of sorting a 16-component sy(n) vector within a single clock cycle is shown in Figure 3.6. Each sy(n) component is assumed to be 3 bits wide. According to simulations, 3 bits should be enough to prevent overflow. Also notice that, since su(n) is set to the negative of the minimum value of the output of the  $H_2(z)$ -1 block, all the sy(n) components are positive at the input of the vector quantizer. The output of the quantizer is the sv(n) vector containing 16 single-bit components that are used to drive a 16-element DAC which is not shown.

The first stage in the quantizer is a layer of 16 1-of-8 decoders. Each takes a 3-bit component of sy(n) and translates it to an 8-bit word with only one of the bits equal to "1" based on the truth table shown below. Each component of sy is assigned to one of 8

Table 3.1:1-of-8 decoder truth table.

| sy <sub>i</sub> | <i>sy</i> <sub>i,8~1</sub> |  |  |

|-----------------|----------------------------|--|--|

| 000             | 10000000                   |  |  |

| 001             | 01000000                   |  |  |

| 010             | 00100000                   |  |  |

| 011             | 00010000                   |  |  |

| 100             | 00001000                   |  |  |

| 101             | 00000100                   |  |  |

| 110             | 0000010                    |  |  |

| 111             | 0000001                    |  |  |

priorities with  $sy_{i,1} = 1$  standing for the first priority and  $sy_{i,8} = 1$  standing for the last priority.

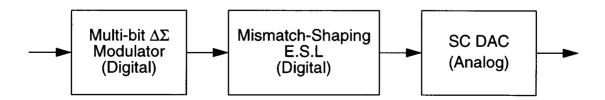

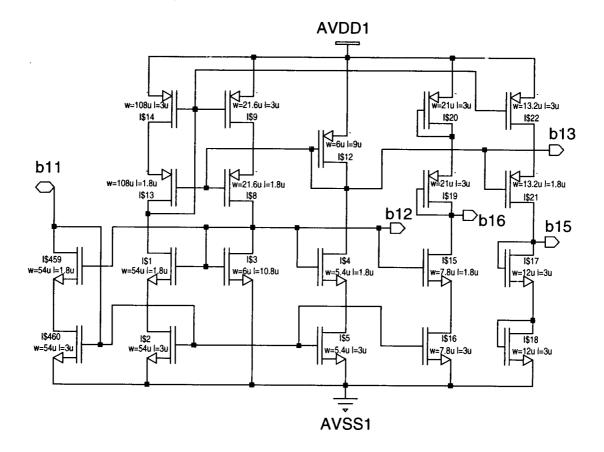

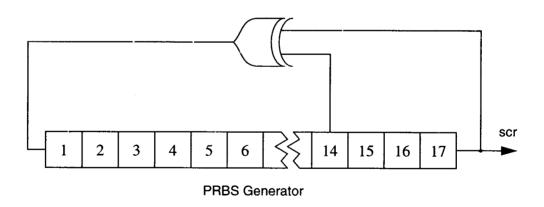

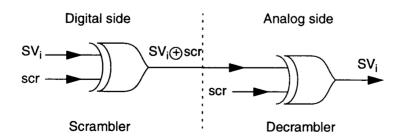

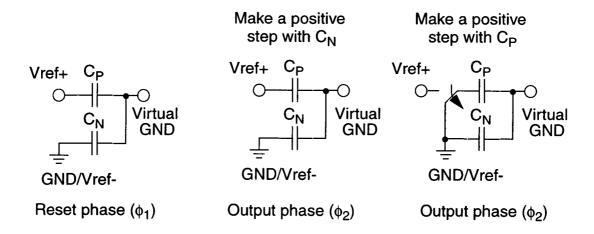

Figure 3.6: A 16-component vector quantizer.