#### AN ABSTRACT OF THE DISSERTATION OF

<u>Allen Waters</u> for the degree of <u>Doctor of Philosophy</u> in

Electrical and Computer Engineering presented on March 5, 2015.

Title:

Automated Verilog-to-Layout Synthesis of ADCs Using Custom Analog Cells.

Abstract approved: \_

#### Un-Ku Moon

A procedure for automating the design and layout of analog-to-digital converters (ADCs) is presented. This procedure makes use of the existing synthesis and place-and-route tools that are common in digital circuit design. A method for adding rudimentary analog cells to the standard library is described, allowing the designer to synthesize mixed-signal designs from Verilog code. By using cells that are simple and highly scalable, the same Verilog code may be used to implement the design in any number of process nodes, for rapid portability and scalability. Two different ADC architectures are implemented as proofs of concept: first, a third-order MASH ADC is fabricated in 130nm and 65nm CMOS, taking advantage of the structure's tolerance to the mismatch introduced by the automated place-and-routing. Second, a Nyquist-rate pipeline ADC using the highly-scalable ring amplifier is fabricated in 65nm CMOS. The measurement results from these chips show that synthesized ADCs can achieve moderate performance with drastically reduced design time compared to manual layout. <sup>©</sup>Copyright by Allen Waters March 5, 2015 All Rights Reserved Automated Verilog-to-Layout Synthesis of ADCs Using Custom Analog Cells

by

Allen Waters

## A DISSERTATION

submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Presented March 5, 2015 Commencement June 2015 Doctor of Philosophy dissertation of <u>Allen Waters</u> presented on March 5, 2015

APPROVED:

Major Professor, representing Electrical and Computer Engineering

Director of the School of Electrical Engineering and Computer Science

Dean of the Graduate School

I understand that my dissertation will become part of the permanent collection of Oregon State University libraries. My signature below authorizes release of my dissertation to any reader upon request.

Allen Waters, Author

#### ACKNOWLEDGMENTS

I would like to first express my appreciation to Dr. Un-Ku Moon for his guidance as my research advisor. When I first joined his group, I did not fully understand how lucky I was to be working under such an experienced and accomplished professor. I'm very grateful for the kindness he has shown me the last five years. I'll do my best to make good use of his technical knowledge and insight in my future career.

Secondly, I give thanks to the other members of my graduate committee: Dr. Karti Mayaram, Dr. Gabor Temes, and Dr. Huaping Liu. I appreciate their time and the technical feedback they have given me along the way. Furthermore, I would like to thank them for the valuable knowledge they provided through their teaching and coursework. Many thanks to Dr. Karen Shell from the College of Earth, Ocean, and Atmospheric Sciences for serving as my Graduate Council Representative. I appreciate the time and energy she has dedicated to my exams and program meetings over the past years.

I would like to express my gratitude to the senior group members who assisted me during my first years of graduate study: Skyler Weaver, Omid Rajaee, Tawfik Musah, Nima Maghari, Ho-Young Lee, Ben Hershberg, Jon Guerber, Taehwan Oh, Manideep Gande, Hari Prasath Venkatram, and Yue Hu. It was a real privilege to learn from these guys, and my only regret is that I didn't ask more questions from the beginning. Matt Brown has also provided terrific support as the AMS lab manager.

I offer my gratitude and best wishes to the current (including recently graduated) group members, who have been great friends: Jason Muhlestein, Jerry Leung, Spencer Leuenberger, Hyuk Sun, Yang Xu, Brandilyn Coker, Praveen Kumar Venkatachala and Farshad Farahbahkshian. I will miss our time together in Dr. Moon's research group, and wish them the best in the remainder of their grad school years.

There are many other students, current and former, in the KEC 4130 grad office who I want to thank... I won't list all their names here. Being a grad student feels like a pretty raw deal sometimes, when you're putting in crazy hours working on a tapeout or preparing for an exam. Having other people in the office working the same crazy hours makes it a lot more bearable, and these guys have been a great support network.

Without going into too much detail, I'd like to acknowledge some other people and organizations that helped me get through my degree: the ARCS Foundation (Portland Chapter), the 26th Street Superette, Galen Wigg, Rex Goliath, the Coalition of Graduate Employees, Suds and Suds.

Finally, I want to recognize and thank the members of my family who made this possible. My parents Tom and Bonnie have been supportive and encouraging throughout all of my schooling. I'm thankful that I've finally reached the end and want to thank them for all the contributions they've made along the way, both large and small. I'd like to thank my brother Ben for being my closest friend the entire time, and my older brother Patrick for being my greatest role model.

There are too many other friends, family members and colleagues to list here. For all those people, I appreciate the individual contributions you've made that helped me along my way.

## TABLE OF CONTENTS

|   |     |                                                                                                                                                                                                                                                                          | 0                          |

|---|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 1 | INT | RODUCTION                                                                                                                                                                                                                                                                | 1                          |

|   | 1.1 | Motivation                                                                                                                                                                                                                                                               | 1                          |

|   | 1.2 | Thesis Structure                                                                                                                                                                                                                                                         | 3                          |

| 2 | PRI | OR WORK                                                                                                                                                                                                                                                                  | 6                          |

|   | 2.1 | Prior Work in Highly Digital ADCs                                                                                                                                                                                                                                        | 6                          |

|   |     | 2.1.1Highly Digital Flash2.1.2Basic Time-to-Digital Converters2.1.3Highly-Digital $\Delta\Sigma$ Modulator                                                                                                                                                               | 6<br>8<br>12               |

|   | 2.2 | Prior Work in Synthesized Analog Blocks                                                                                                                                                                                                                                  | 13                         |

|   |     | <ul><li>2.2.1 Synthesized Stochastic Flash ADC</li><li>2.2.2 Analog Design Automation</li></ul>                                                                                                                                                                          | 14<br>15                   |

|   | 2.3 | Summary                                                                                                                                                                                                                                                                  | 17                         |

| 3 | PRO | POSED ANALOG SYNTHESIS TOOLCHAIN                                                                                                                                                                                                                                         | 18                         |

|   | 3.1 | Existing Digital Synthesis Toolchain                                                                                                                                                                                                                                     | 19                         |

|   | 3.2 | Library Information for Digital Standard Cells                                                                                                                                                                                                                           | 22                         |

|   |     | <ul> <li>3.2.1 Graphic Database System (GDS) Information</li> <li>3.2.2 Library Exchange Format (LEF) Information</li> <li>3.2.3 Liberty (LIB) Timing File Information</li> </ul>                                                                                        | 22<br>23<br>27             |

|   | 3.3 | Creating Custom Analog Cell Information                                                                                                                                                                                                                                  | 27                         |

|   |     | <ul> <li>3.3.1 Minimalist Set of Analog Cells</li> <li>3.3.2 Creating .GDS File for Custom Cell</li> <li>3.3.3 Creating .LEF File for Custom Cell</li> <li>3.3.4 Creating .LIB File For Custom Cell</li> <li>3.3.5 Controlling Floorplanning for Analog Cells</li> </ul> | 31<br>32<br>35<br>35<br>39 |

# TABLE OF CONTENTS (Continued)

| Р | а   | g      | e |

|---|-----|--------|---|

|   | cu, | $\sim$ | v |

|   | 3.4   | Final                                                                             | Toolchain                                                                                                                                                                                              | 40                               |

|---|-------|-----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

|   |       | $3.4.1 \\ 3.4.2$                                                                  | New Automated Analog Design Toolchain<br>Capabilities and Limitations                                                                                                                                  | 43<br>43                         |

|   | 3.5   | Sumn                                                                              | nary                                                                                                                                                                                                   | 48                               |

| 4 | A 1-1 | l-1 MA                                                                            | ASH ADC SYNTHESIZED FROM VERILOG CODE                                                                                                                                                                  | 49                               |

|   | 4.1   | Backg                                                                             | ground on $\Delta\Sigma$ Modulation                                                                                                                                                                    | 49                               |

|   |       | $\begin{array}{c} 4.1.1 \\ 4.1.2 \\ 4.1.3 \\ 4.1.4 \\ 4.1.5 \\ 4.1.6 \end{array}$ | Nyquist-Rate SQNR Limit<br>Improving Resolution with Oversampling<br>First-Order Noise Shaping<br>Low Distortion Topology<br>Higher-Order Noise Shaping<br>Finite Integrator Gain and Gain Compression | 49<br>52<br>54<br>57<br>61<br>66 |

|   | 4.2   | Propo                                                                             | osed System Architecture                                                                                                                                                                               | 69                               |

|   |       | $\begin{array}{c} 4.2.1 \\ 4.2.2 \\ 4.2.3 \end{array}$                            | Top-Level DesignNoise SourcesCapacitor Sizing                                                                                                                                                          | 69<br>73<br>75                   |

|   | 4.3   | Minin                                                                             | nalist Sub-Block Design                                                                                                                                                                                | 77                               |

|   |       | $\begin{array}{c} 4.3.1 \\ 4.3.2 \\ 4.3.3 \\ 4.3.4 \end{array}$                   | Operational Amplifier<br>Three-Level Quantizer Design<br>Feedback DAC Design<br>Final Simulation Results                                                                                               | 77<br>79<br>81<br>81             |

|   | 4.4   | Expe                                                                              | rimental Results                                                                                                                                                                                       | 83                               |

|   |       | $\begin{array}{c} 4.4.1 \\ 4.4.2 \\ 4.4.3 \end{array}$                            | MASH ADC in 130nm CMOS<br>MASH ADC in 65nm CMOS<br>Comparison to State-of-the-Art                                                                                                                      | 83<br>87<br>93                   |

|   | 4.5   | Sumn                                                                              | nary                                                                                                                                                                                                   | 93                               |

## TABLE OF CONTENTS (Continued)

## Page

| 5  |      | G AMPLIFIER-BASED PIPELINE ADC SYNTHESIZED FROM<br>ILOG CODE                                                                            |

|----|------|-----------------------------------------------------------------------------------------------------------------------------------------|

|    | 5.1  | Background on Ring Amplifier                                                                                                            |

|    | 5.2  | Proposed System Architecture                                                                                                            |

|    |      | 5.2.1       Top-Level System Design       98         5.2.2       Noise Sources       101         5.2.3       Capacitor Sizing       102 |

|    | 5.3  | Minimalist Sub-Block Design 103                                                                                                         |

|    |      | 5.3.1Ring Amplifier Output Stage1035.3.2Sub-ADC Reference Ladder1045.3.3Final Simulation Results104                                     |

|    | 5.4  | Experimental Results 105                                                                                                                |

|    |      | 5.4.1Pipeline ADC in 65nm CMOS1075.4.2Comparison to State-of-the-Art107                                                                 |

|    | 5.5  | Summary 109                                                                                                                             |

| 6  | CON  | ICLUSION 110                                                                                                                            |

|    | 6.1  | Summary 110                                                                                                                             |

|    | 6.2  | Future Work 111                                                                                                                         |

|    |      | <ul> <li>6.2.1 Automating Architecture Design</li></ul>                                                                                 |

| BI | BLIO | GRAPHY 117                                                                                                                              |

| AI | PPEN | DICES 122                                                                                                                               |

|    | А    | Finite Gain in Switched-Capacitor Integrators                                                                                           |

# TABLE OF CONTENTS (Continued)

# Page

| B List of Acronyms 1 | 129 |

|----------------------|-----|

|----------------------|-----|

#### LIST OF FIGURES

| Fig | jure                                                                                                                                                                             | Page |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

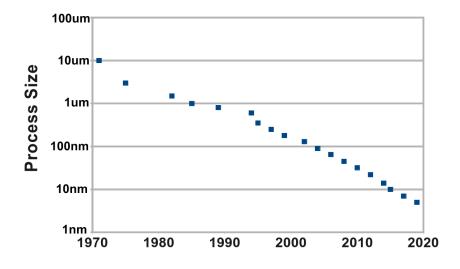

| 1.1 | Scaling trend in CMOS process sizes                                                                                                                                              | . 2  |

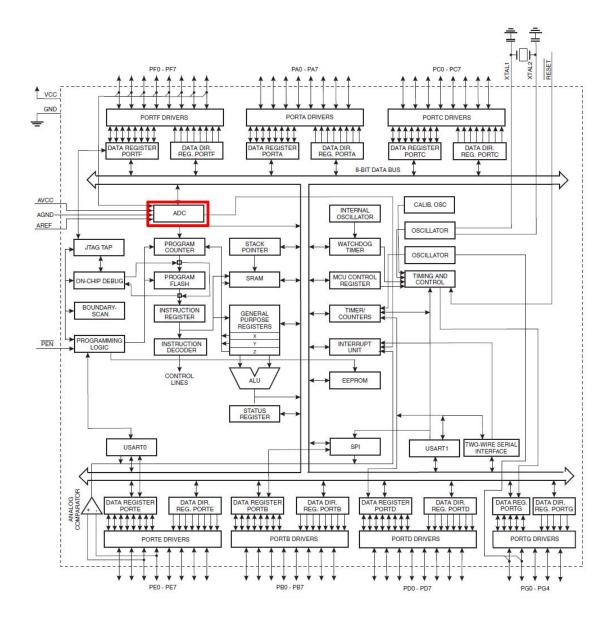

| 1.2 | Block diagram of ATMega128 microcontroller, highlighting ADC                                                                                                                     | . 4  |

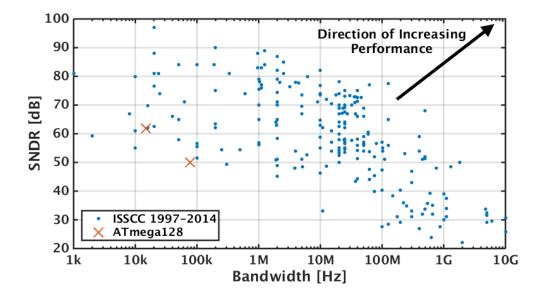

| 1.3 | Survey of modern ADC performance, compared to ATMega128 example.                                                                                                                 |      |

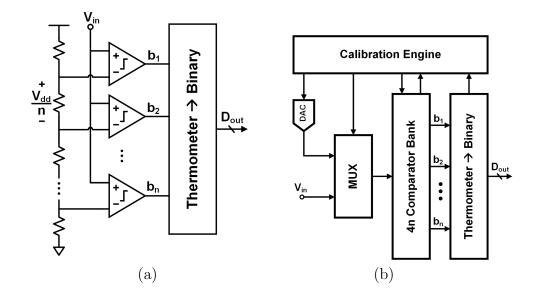

| 2.1 | Modifying the (a) standard flash ADC to create a (b) redundant flash.                                                                                                            |      |

| 2.2 | Highly digital dynamic comparator, with $k$ input device stack of variable widths                                                                                                |      |

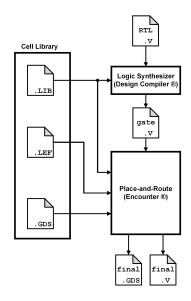

| 2.3 | Toolchain used for digital circuit synthesis                                                                                                                                     | . 9  |

| 2.4 | Effect of voltage noise with scaling supply voltage for (a) ADC and (b) TDC.                                                                                                     |      |

| 2.5 | Examples of TDC architectures: (a) flash TDC, (b) Vernier TDC, (c) VCO-based TDC. Voltage-to-time operation displayed in gray                                                    |      |

| 2.6 | TDC delay cells used in (a) multi-path GRO and (b) SRO                                                                                                                           | . 12 |

| 2.7 | Using a DSM loop to suppress VCO nonlinearity                                                                                                                                    | . 13 |

| 2.8 | An analog comparator constructed from (a) two cross-coupled<br>NAND3 logic gates, to achieve the (b) transistor-level schematic<br>for a comparator                              |      |

| 2.9 | Previous work in automating the (a) traditional analog design<br>process, showing hightlighted blocks where automation has been<br>achieved by (b) ASTRX, (c) KOAN, and (d) WREN |      |

| 3.1 | Toolchain used for digital circuit synthesis.                                                                                                                                    |      |

| 3.2 | Instantiations in Verilog can be (a) logical, (b) primitive gate-<br>level, or (c) process-specific gate-level. All describe the same (d)<br>schematic                           |      |

| 3.3 | Example of how a standard cell might appear in (a) layout view, and (b) a hexdump of the binary GDS file describing it                                                           |      |

| 3.4 | Example technology LEF layer definitions                                                                                                                                         | . 25 |

| Fig  | ure                                                                                                                                                                                 | Pa  | ge |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----|

| 3.5  | Example technology LEF contact definitions.                                                                                                                                         |     | 26 |

| 3.6  | Example LEF macro statement                                                                                                                                                         | ••  | 28 |

| 3.7  | Example LIB technology definitions.                                                                                                                                                 | • • | 29 |

| 3.8  | Example LIB cell definition.                                                                                                                                                        | ••  | 30 |

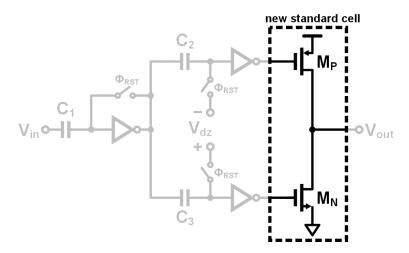

| 3.9  | A minimal set of custom cells for analog design                                                                                                                                     | ••• | 31 |

| 3.10 | Example of multi-pitch custom cell layout, for a MIM capacitor.                                                                                                                     |     | 33 |

| 3.11 | Streaming out a GDS file for a custom cell                                                                                                                                          | ••  | 34 |

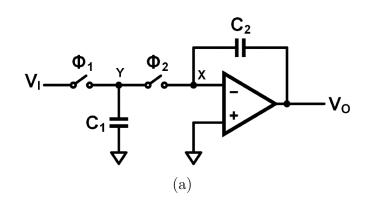

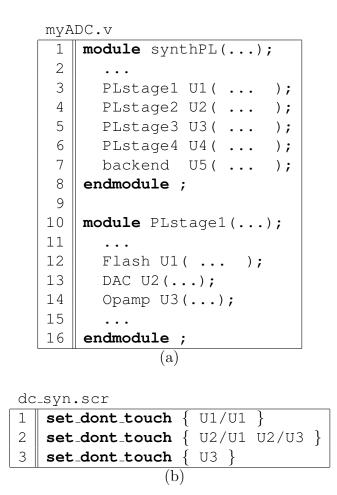

| 3.12 | Example of describing the inverting integrator (a) schematic integration (b) Verilog code using explicit instantiations of custom cells                                             |     | 37 |

| 3.13 | Using Design Compiler directives to explicitly instantiate analog custom cells without a logical description.                                                                       | ,   | 38 |

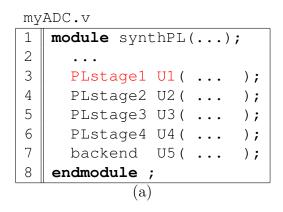

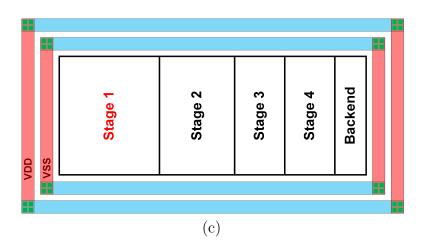

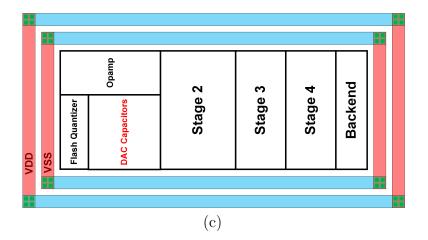

| 3.14 | Example of controlling floorplanning with the "setObjFPlanBox" directive. The modules in (a) Verilog are floorplanned in (b) TCL to achieve a good starting point in the (c) layout | 1   | 41 |

| 3.15 | Using PNR floorplanning, one level deeper                                                                                                                                           | ••  | 42 |

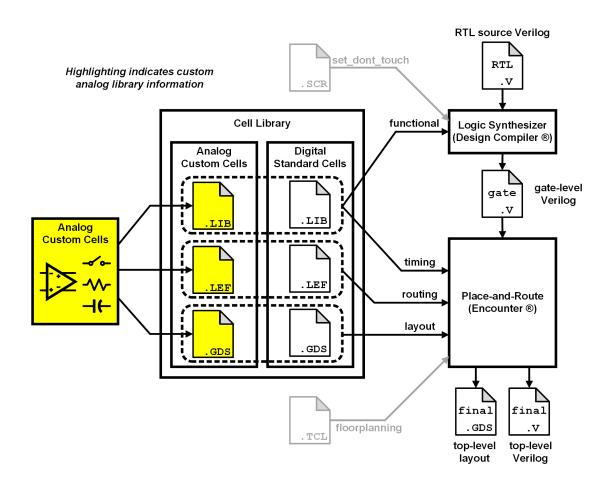

| 3.16 | Toolchain used for analog circuit synthesis                                                                                                                                         | ••• | 44 |

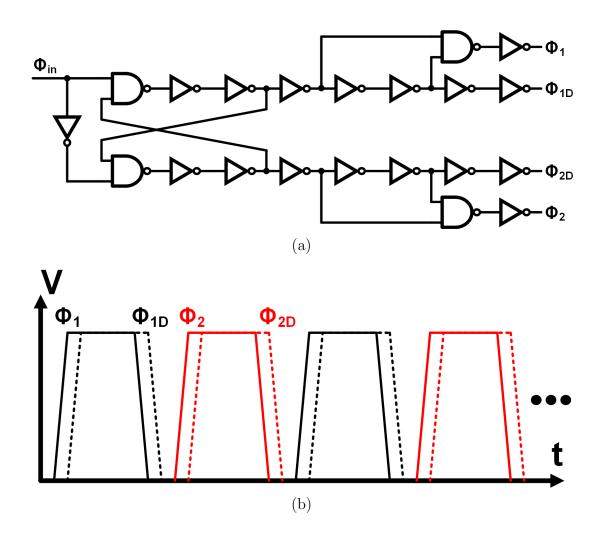

| 3.17 | A possible non-overlapping clock generator (a) schematic and (b) waveform.                                                                                                          |     | 47 |

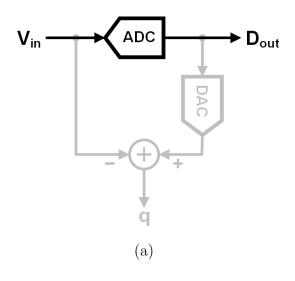

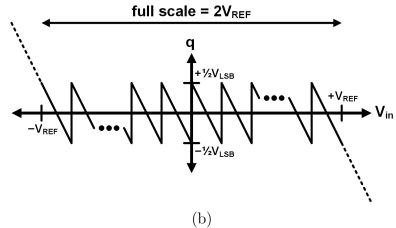

| 4.1  | Ideal ADC quantization error shown in (a) schematic and (b) transfer function.                                                                                                      |     | 50 |

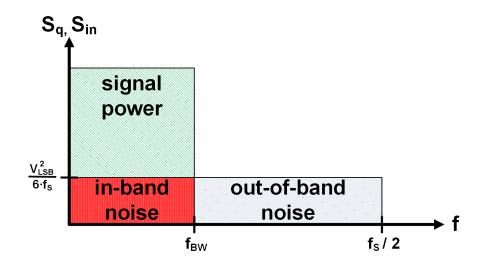

| 4.2  | Reducing quantization noise with oversampling                                                                                                                                       | ••• | 52 |

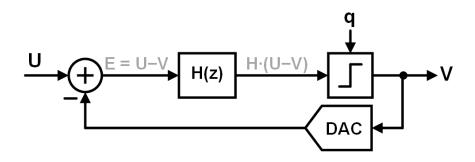

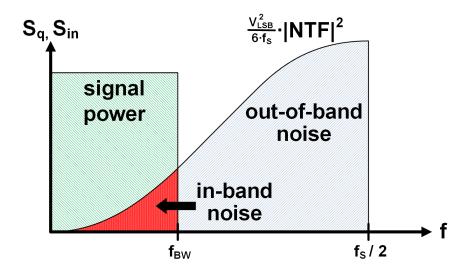

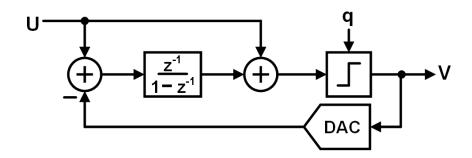

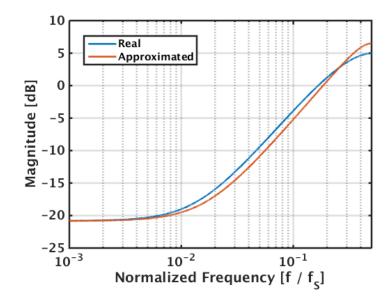

| 4.3  | A first-order $\Delta\Sigma$ ADC                                                                                                                                                    | ••• | 54 |

| 4.4  | Power spectral density with first-order noise shaping                                                                                                                               | ••  | 56 |

| 4.5  | A first-order $\Delta\Sigma$ ADC, using low-distortion architecture                                                                                                                 | ••  | 58 |

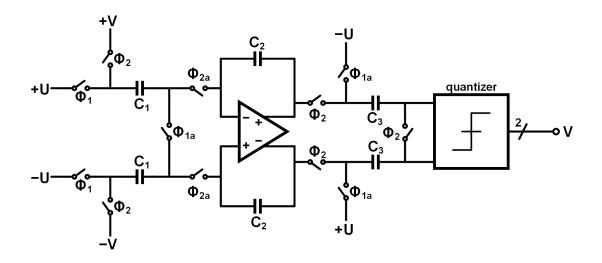

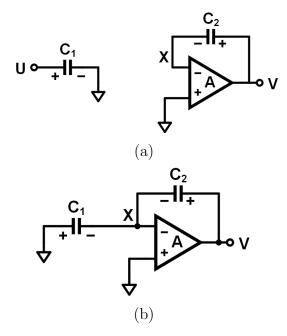

| 4.6  | Switched capacitor implementation of low-distortion DSM topolog                                                                                                                     | gy. | 59 |

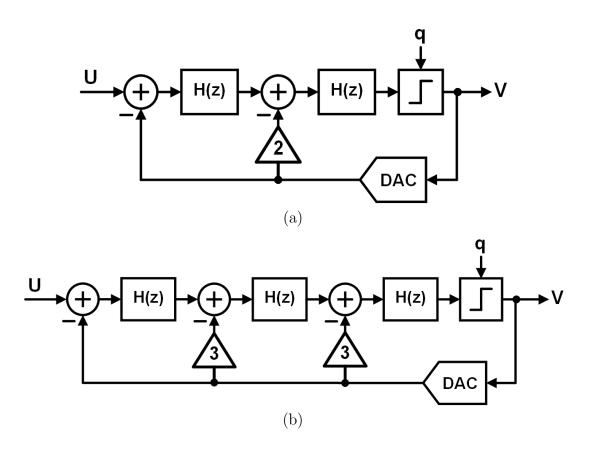

| 4.7  | DSM modulators with (a) second and (b) third-order noise shaping                                                                                                                    | ng. | 60 |

| Figu | <u>Ire</u> <u>Pa</u>                                                                                               | ge |

|------|--------------------------------------------------------------------------------------------------------------------|----|

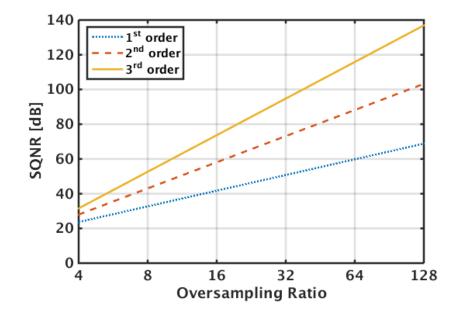

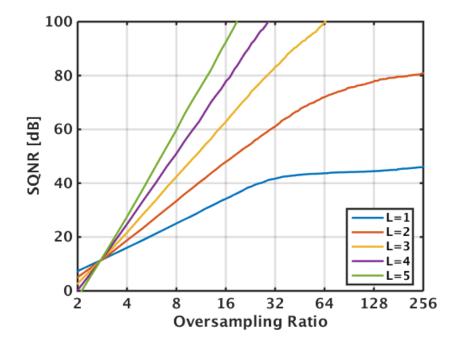

| 4.8  | Theoretical SQNR limit of 1.5-bit modulators with various orders.                                                  | 64 |

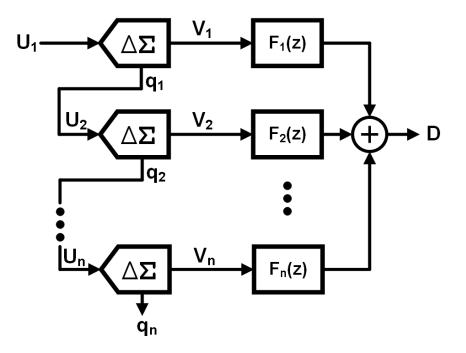

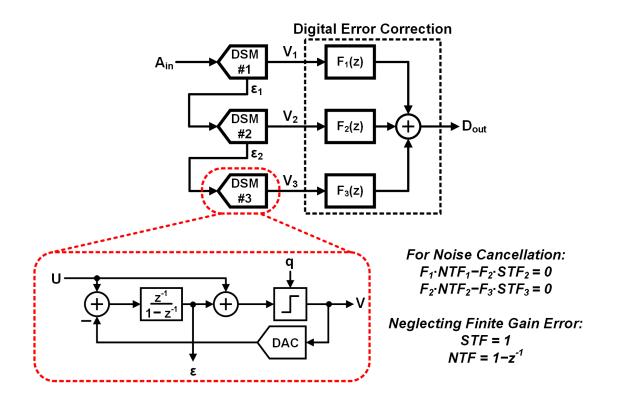

| 4.9  | An <i>n</i> -stage MASH ADC                                                                                        | 64 |

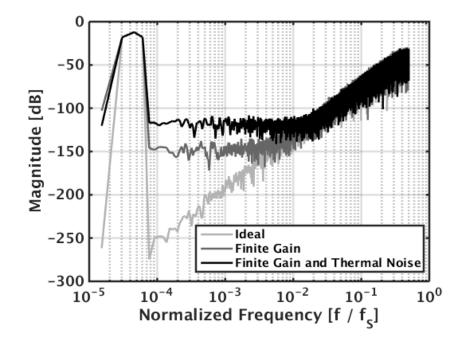

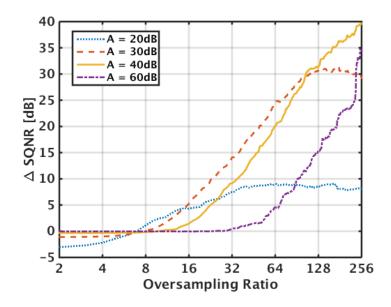

| 4.10 | Simulation results showing effect of finite gain and thermal noise.                                                | 67 |

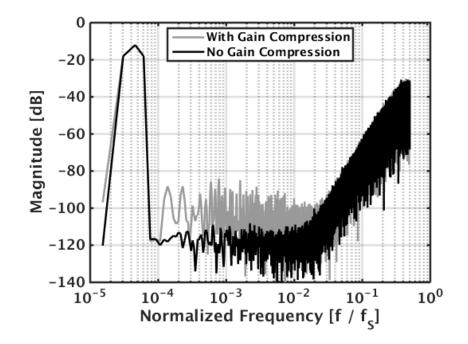

| 4.11 | Simulation results showing effect of gain compression in integrator.                                               | 68 |

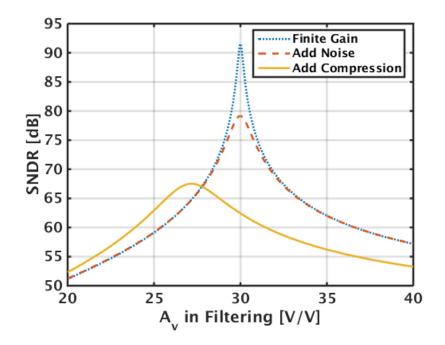

| 4.12 | Simulation results showing sensitivity of finite-gain calibration in 1-1-1 MASH, for a nominally 30dB amplifier    | 69 |

| 4.13 | Maximum SQNR for different MASH orders using 30dB opamps (perfectly calibrated)                                    | 71 |

| 4.14 | Top-level architecture of 1-1-1 MASH ADC.                                                                          | 72 |

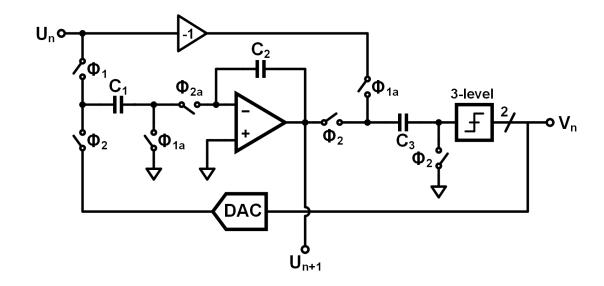

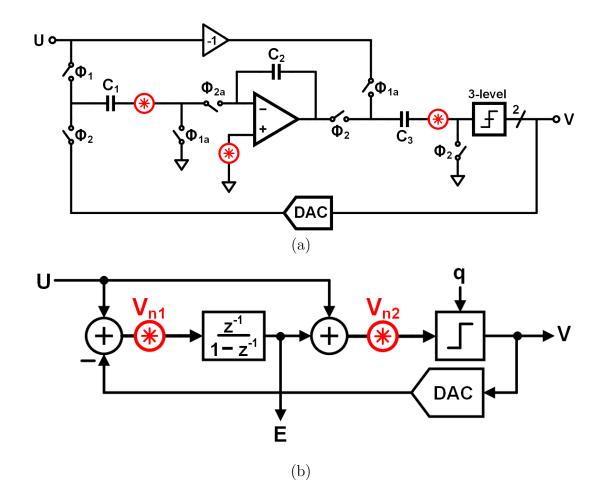

| 4.15 | Switched-capacitor implementation of first-order DSM (shown single-<br>ended for simplicity).                      | 73 |

| 4.16 | Location of noise sources (a) in the first-order DSM, and (b) an equivalent representation combining sources       | 74 |

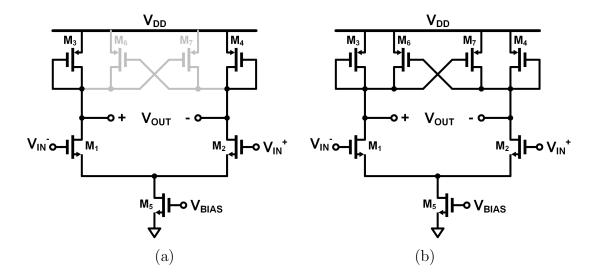

| 4.17 | Minimalist single stage opamp design using (a) basic differential pair and (b) additional cross-couple active load | 78 |

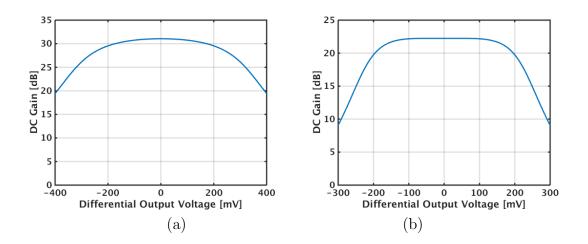

| 4.18 | DC gain of the simple opamp as a function of output swing, for<br>(a) 130nm and (b) 65nm processes                 | 79 |

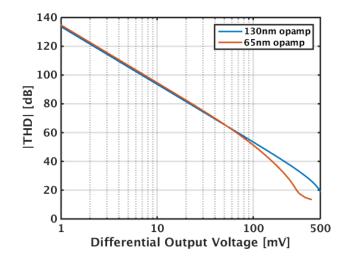

| 4.19 | Harmonic distortion of the opamp transfer functions across output swing.                                           | 80 |

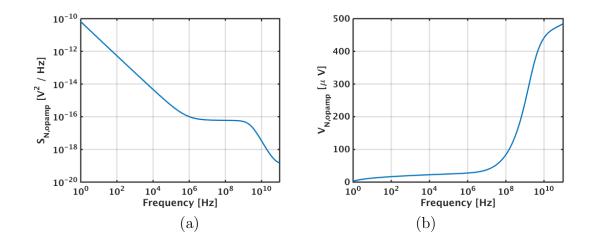

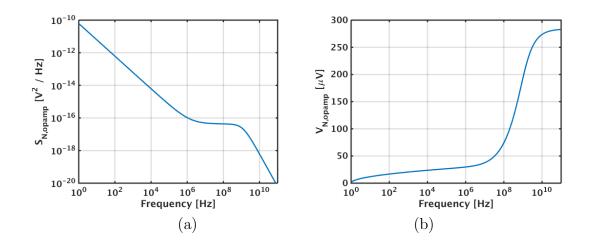

| 4.20 | Opamp performance in 130nm process, showing (a) noise PSD and (b) integrated noise voltage.                        | 80 |

| 4.21 | Opamp performance in 65nm process, showing (a) noise PSD and (b) integrated noise voltage                          | 81 |

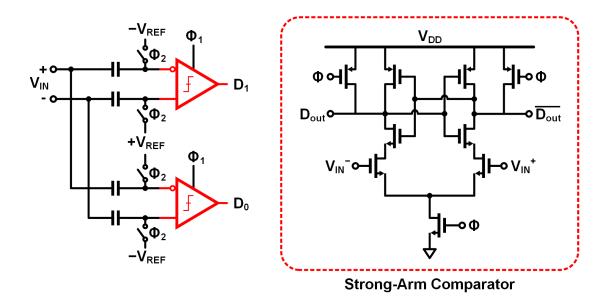

| 4.22 | Switched-capacitor implementation of three-level quantizer, using<br>a Strong-Arm latch as the quantizer.          | 82 |

| 4.23 | Voltage-switched three-level DAC (shown single-ended for sim-<br>plicity).                                         | 82 |

| Figu | ure                                                                                                                                                      | Page  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

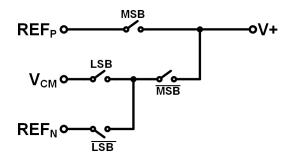

| 4.24 | Final simulation results with transient noise, for (a) transistor-<br>level and (b) post-layout extraction                                               | . 84  |

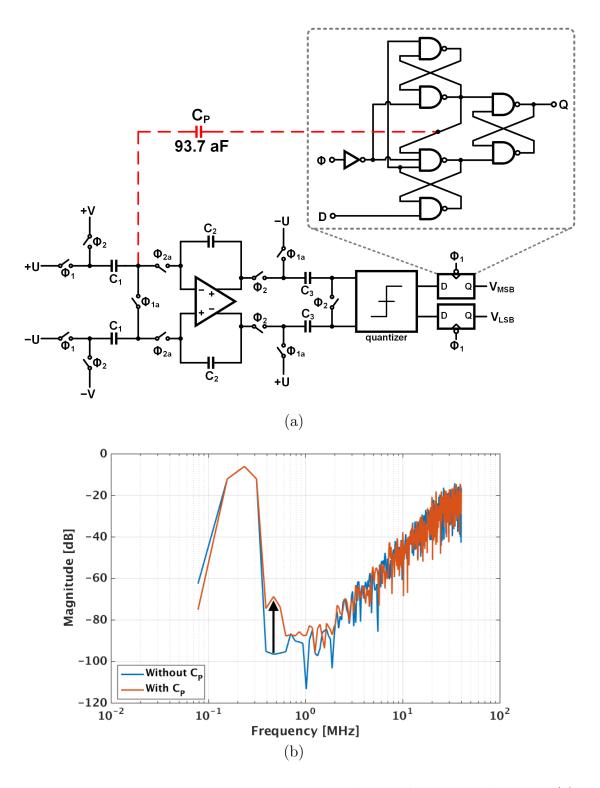

| 4.25 | Parasitic capacitance causing 2nd-order distortion, shown in (a) schematic and (b) the resulting FFT spectrum                                            | . 85  |

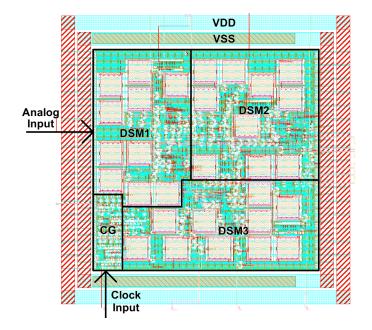

| 4.26 | Layout view of floorplanning for MASH ADC in 130nm process.                                                                                              | . 86  |

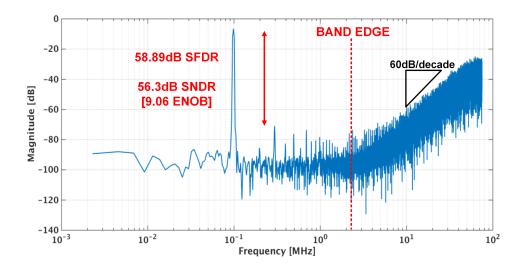

| 4.27 | Example output spectrum of 130nm MASH ADC                                                                                                                | . 86  |

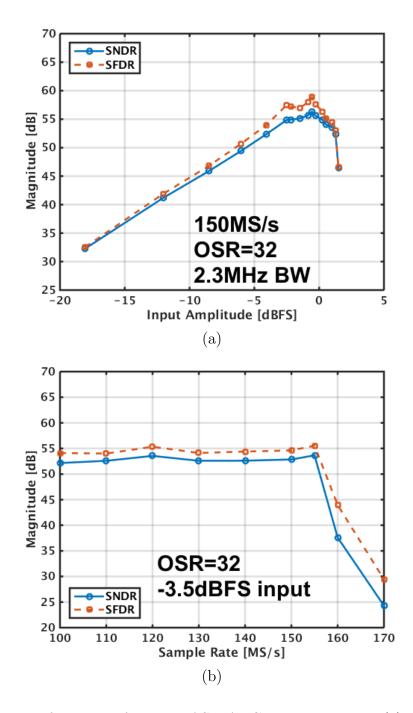

| 4.28 | Performance of 130nm MASH ADC, sweeping across (a) input amplitude and (b) sample rate. Results use $OSR = 40$ in all case                               | s. 88 |

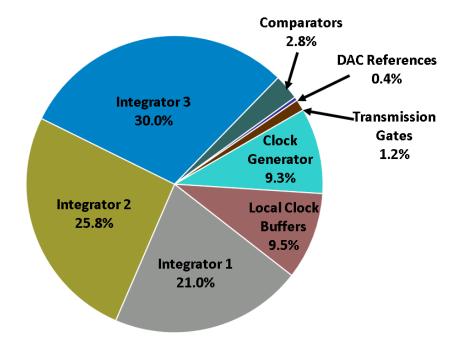

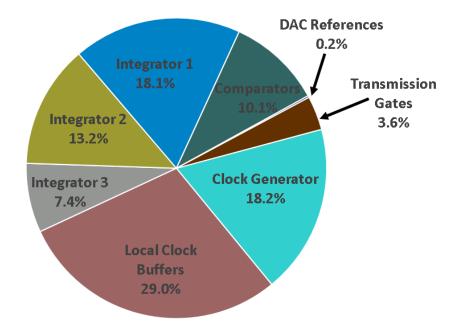

| 4.29 | Estimated power breakdown in 130nm MASH ADC                                                                                                              | . 89  |

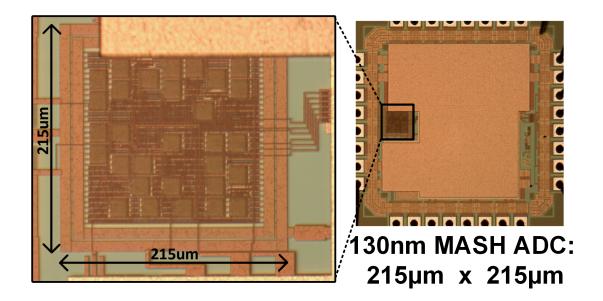

| 4.30 | Die photo of synthesized MASH ADC in 130nm process                                                                                                       | . 89  |

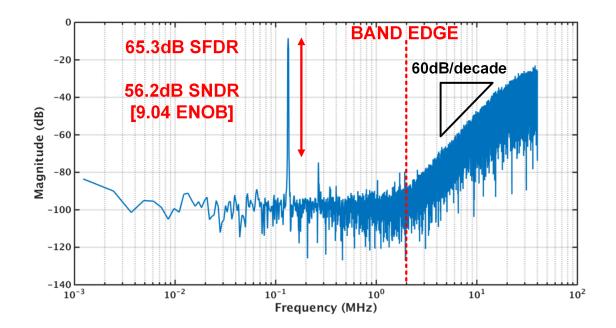

| 4.31 | Example output spectrum of 65nm MASH ADC                                                                                                                 | . 90  |

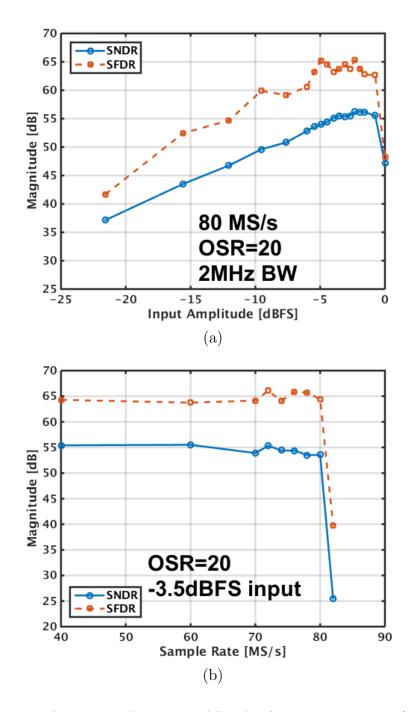

| 4.32 | Performance of 65nm MASH ADC, sweeping across (a) input amplitude and (b) sample rate. Results use $OSR = 75$ in all cases.                              | . 91  |

| 4.33 | Estimated power breakdown in 65nm MASH ADC                                                                                                               | . 92  |

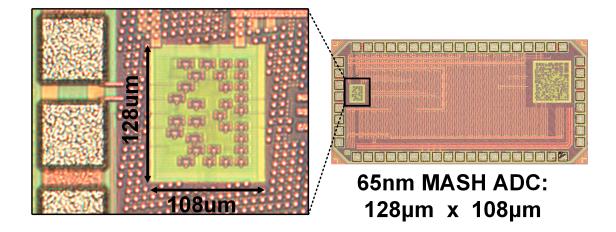

| 4.34 | Die photo of synthesized MASH ADC in 65nm process                                                                                                        | . 93  |

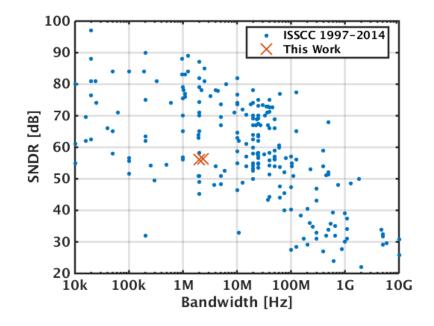

| 4.35 | Comparison of this work to ISSCC publications                                                                                                            | . 94  |

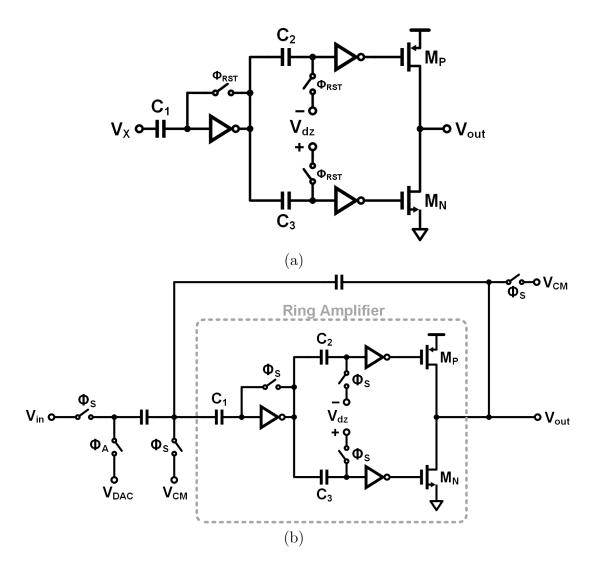

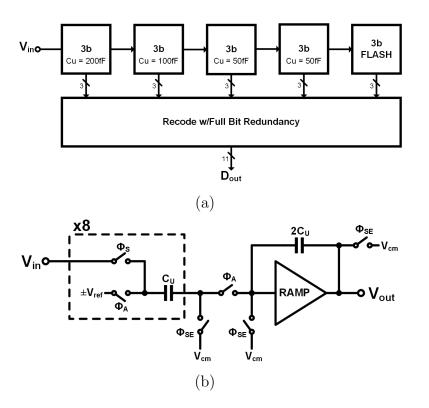

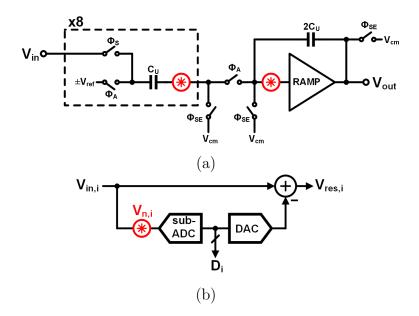

| 5.1  | Basic architecture of (a) stand-alone ring amplifier and (b) ring amplifier-based MDAC.                                                                  | . 96  |

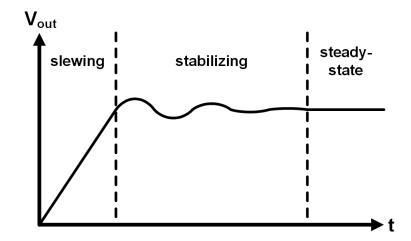

| 5.2  | Example ring amplifier output waveform showing the three phases of operation                                                                             | . 97  |

| 5.3  | (a) Top-level architecture of proposed pipeline ADC, and (b) schematic of MDAC stage (shown single-ended for simplicity)                                 | . 99  |

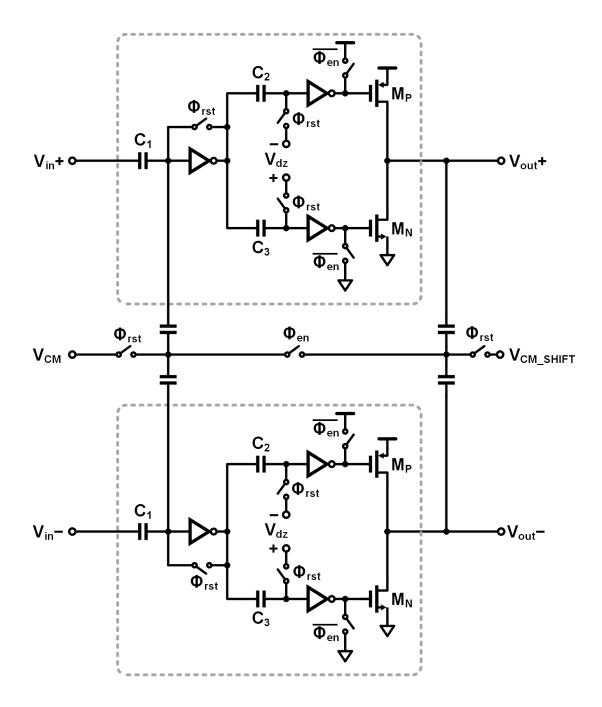

| 5.4  | Pseudo-differential ring amplifier implementation, with added pow<br>saving feature and switched-capacitor CMFB                                          |       |

| 5.5  | Location of noise sources (a) in switched-capacitor MDAC stage,<br>and (b) an equivalent block diagram combining sources for <i>i</i> -th<br>MDAC stage. | . 101 |

| 5.6  | Output stage of ringamp, to be added as custom analog cell                                                                                               | . 104 |

#### Dago

Figure

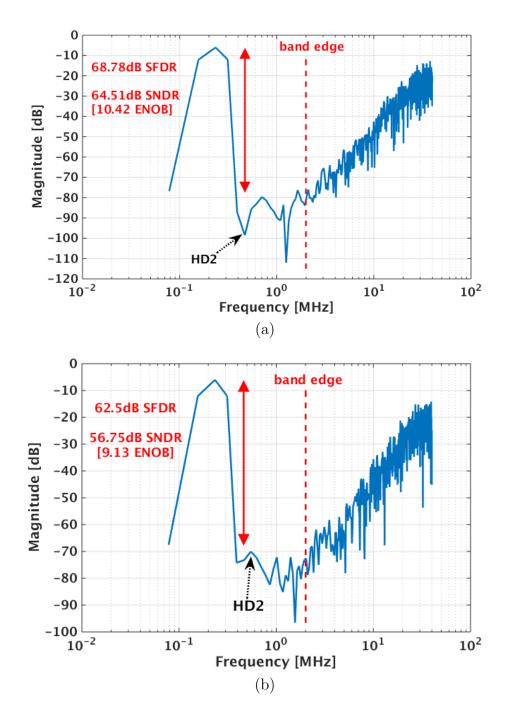

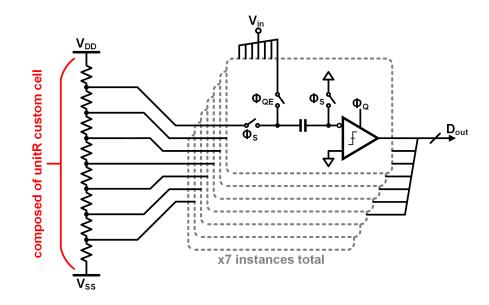

| 5.7  | Implementation of sub-ADC and resistive reference ladder (shown single-ended for simplicity).              | 105 |

|------|------------------------------------------------------------------------------------------------------------|-----|

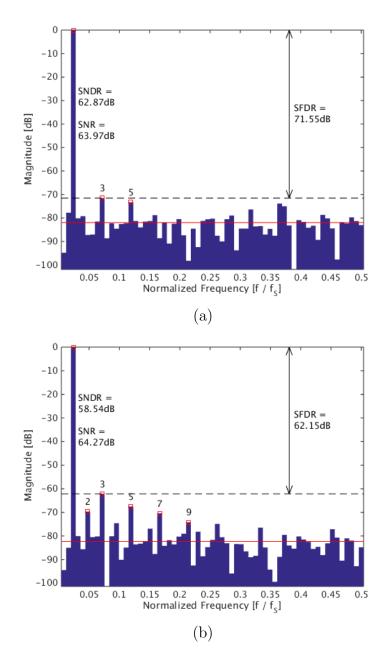

| 5.8  | Final simulation results with transient noise, for (a) transistor-<br>level and (b) post-layout extraction | 106 |

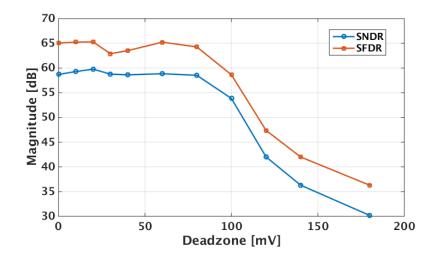

| 5.9  | Extracted simulation results across deadzone settings                                                      | 107 |

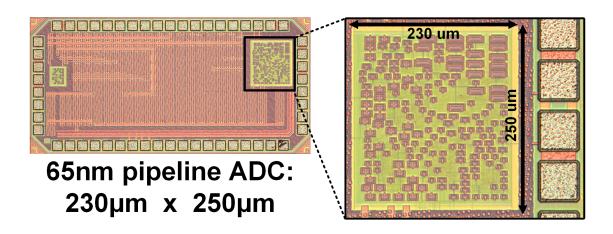

| 5.10 | Die photo of synthesized pipeline ADC in 65nm process                                                      | 108 |

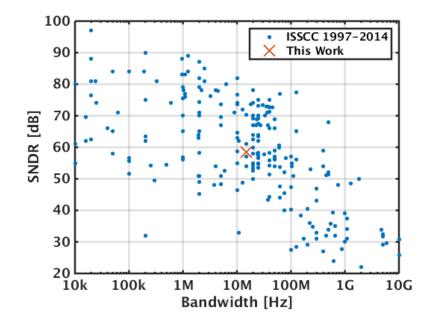

| 5.11 | Comparison of this work to ISSCC publications.                                                             | 109 |

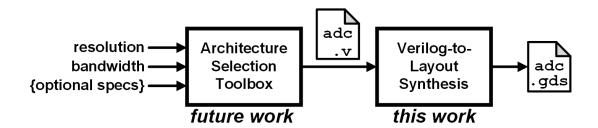

| 6.1  | Automating the creation of the Verilog code in future work                                                 | 111 |

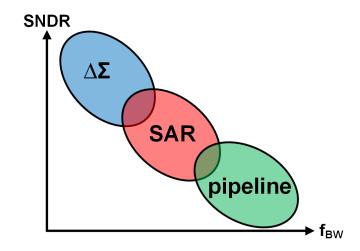

| 6.2  | Graphical representation of resolution/bandwidth look-up table used by automation toolbox.                 | 112 |

| A.1  | Switched-capacitor integrator with a finite-gain amplifier                                                 | 124 |

| A.2  | Switched-capacitor integrator during (a) phase 1 and (b) phase 2.                                          | 125 |

| A.3  | Deviation in first-order NTF using finite gain approximation, for<br>an amplifier with 20dB DC gain        | 127 |

| A.4  | Reduction in theoretical SQNR from approximating $H(z)$ for a third-order DSM                              | 128 |

# Page

## LIST OF TABLES

| Tal | ble                                               | Pa | ige |

|-----|---------------------------------------------------|----|-----|

| 4.1 | OptiMASH ADC Summary of Performance               |    | 87  |

| 4.2 | OptiMASH Prime ADC Summary of Performance         |    | 92  |

| 5.1 | Ringamp-based Pipeline ADC Summary of Performance |    | 108 |

For my parents.

# AUTOMATED VERILOG-TO-LAYOUT SYNTHESIS OF ADCS USING CUSTOM ANALOG CELLS

# **CHAPTER 1. INTRODUCTION**

"Then as it was, then again it will be And though the course may change sometimes Rivers always reach the sea."

— Led Zeppelin (*Ten Years Gone*)

## 1.1 Motivation

Since the formulation of Moore's Law in the 1960's, the effects of semiconductor process scaling continue to reduce feature sizes and increase transistor densities [1]. The scaling trends (compiled from annual reports from the International Technology Roadmap for Semiconductors [2]) are shown in Figure 1.1. The effects on individual transistors are increased transition frequency  $(f_t)$ , higher transconductance  $(g_m)$ , lower output impedance  $(r_o)$ , and lower supply voltages (necessary for device reliability). Digital circuits benefit greatly from these effects: they achieve increased operating speeds, and decreased power and area. Furthermore, the low sensitivity to physical layout allows digital design to be automatically synthesized from Verilog code. When implementing the same digital design in a smaller process, the same Verilog source may be reused for a fast time-to-market.

Figure 1.1: Scaling trend in CMOS process sizes.

While analog circuits benefit from faster speeds in smaller process nodes, they suffer from many other drawbacks. Since  $r_o$  decreases faster than  $g_m$  increases, these devices have reduced intrinsic gain  $(g_m r_o)$  [3]. Smaller supply voltages mean less available signal swing (reducing signal-to-noise ratio) and less headroom for cascodes. Furthermore, the designer faces laborious redesign and manual layout. The result is that process scaling provides no guarantee of better analog performance, and requires high design cost.

Mixed-signal design inherently contains a combination of analog and digital blocks, such that some parts may be re-synthesized from the same Verilog code while others require a costly custom design and layout. Consider as a case study the Atmel ATMega128 microcontroller shown in Figure 1.2. The microcontroller is almost entirely a digital design, which could be described in Verilog code and rapidly ported among different process nodes. However, consider the highlighted ADC... one pesky analog block within a sea of synthesizable digital logic. This will require manual redesign and layout in a new process, creating a bottleneck in the design. Furthermore, the performance specifications for this ADC are quite moderate: the two operating points are 10-bit resolution at 15kS/s, or 8-bit resolution at 76.9 kS/s [4]. As shown in Figure 1.3, these are far from state-of-the-art [5].

Considering the modest performance specifications, is it possible that by adding a few rudimentary analog components to the digital standard cell library, the ADC block could be synthesized along with the rest of the microcontroller? Certainly an automatically routed ADC layout would never outperform that of a manual design. However, for mixed signal designs with moderate speed and resolution requirements, the much faster design time may be worth the power/area overhead.

#### **1.2** Thesis Structure

The remainder of this thesis will be structured as follows. Chapter 2 begins with a review of how synthesis and place-and-route tools are currently used for digital design, and offers a vision of how analog Verilog-to-layout synthesis could be implemented. Chapter 3 summarizes previous work in the synthesis of analog circuits. Chapter 4 presents the design and synthesis of a 1-1-1 MASH  $\Delta\Sigma$ ADC, along with measurement results for prototypes in both 130nm and 65nm CMOS. Chapter 5 presents the design and synthesis of a Nyquist-rate pipeline ADC, with measurement results. Finally, Chapter 6 summarizes the thesis and offers suggestions for future work in this area.

Figure 1.2: Block diagram of ATMega128 microcontroller, highlighting ADC.

Figure 1.3: Survey of modern ADC performance, compared to ATMega128 example.

"The past, like the future, is indefinite and exists only as a spectrum of possibilities."

Stephen Hawking

### 2.1 Prior Work in Highly Digital ADCs

#### 2.1.1 Highly Digital Flash

In flash ADCs, effective resolution is limited by comparator offsets. Traditionally these offsets are controlled with analog techniques such as device sizing, trimming, offset nulling, and averaging. However, these have adverse effects on performance by increasing area and power consumption. Furthermore, these techniques do not scale easily to modern CMOS processes, so designers are forced to consider more scalable, digital-like solutions for controlling offsets.

Figure 2.1a shows a conventional flash ADC, for which there are strict inputreferred offset requirements. The solution presented in [6] is to use redundancy and create four different comparators with ideal trip-points at each code transition. Figure 2.1b shows a digital calibration engine that selects the closest of the four trip-points to each ideal value, achieving good linearity and greatly reducing the individual comparator offset requirements. The work in [7] studies the design trade-offs of this approach with a generalized number R of redundant comparators at each trip-point.

Figure 2.1: Modifying the (a) standard flash ADC to create a (b) redundant flash.

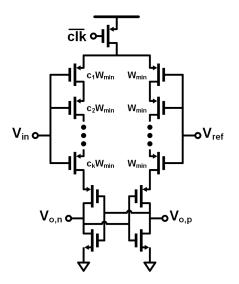

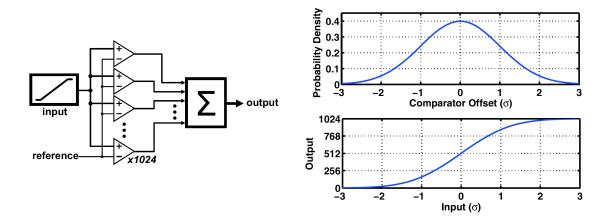

The flash ADC implemented in [8] uses a slightly different method of comparator redundancy to create a scalable flash ADC. It uses a large number of instances of the comparator shown in Figure 2.2. Rather than generate references using a resistor ladder, this comparator creates static voltage offsets by varying the number of minimum-sized input devices that are combined in series and in parallel. Since these thresholds will vary significantly, comparator redundancy is exploited and a digital background calibration scheme estimates the cumulative distribution function (CDF) in order to select a linear subset of the comparator bank. The redundancy and calibration allow the ADC to scale very well with supply voltage, but with two banks of 127 comparators achieves an effective number of bits (ENOB) of only 5.56-bits.

Similarly, [9] implements a highly digital stochastic ADC with comparators that are implemented from minimum-sized devices. It uses identical comparator instances and relies on the random mismatches in offset voltage, as shown in Figure

Figure 2.2: Highly digital dynamic comparator, with k input device stack of variable widths.

2.3. One downside of this approach is that the input signal swing is only 280 m $V_{pp}$  (differential). Another drawback of the stochastic flash is that the resolution scales more poorly than a conventional flash ( $n = 4^N$  as opposed to  $n = 2^N$ ). For this reason, 1152 comparators achieve a limited 33.6-dB SNDR.

While comparator redundancy in flash ADCs is more scalable than conventional analog techniques, the inflated number of comparators is an expensive area requirement. The following subsections explore architectures other than flash that are digital-like and can scale well to smaller process nodes.

#### 2.1.2 Basic Time-to-Digital Converters

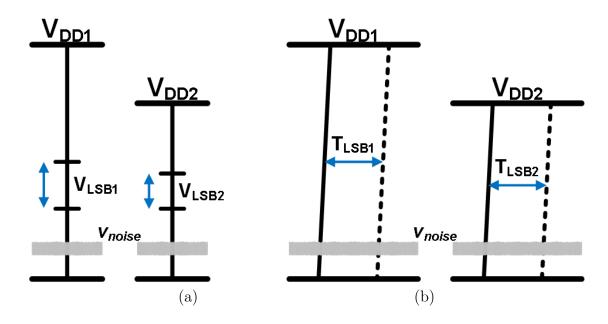

As mentioned in Section 1.1, shrinking supply voltages in modern processes reduces SNR. As shown in Figure 2.4a, if resolution is kept constant while supply

Figure 2.3: Toolchain used for digital circuit synthesis.

shrinks, then the size of a least-significant bit (LSB) decreases relative to the voltage noise. However, the time-domain LSB for a TDC suffers much less. While the voltage noise will translate into timing jitter, the effect is much less pronounced than for the ADC.

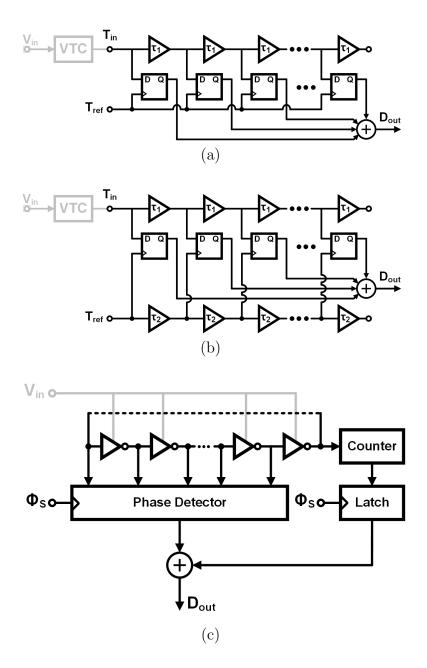

For this reason, a possible solution for process scaling is to use a front-end voltage-to-time converter (VTC) block followed by the scalable TDC. Overall this achieves an A/D operation. Some basic TDC architectures are shown in Figure 2.5. The basic flash TDC shown in 2.5a requires only digital cells and is highly synthesizable. This TDC counts the number of delay elements that the input time pulse propagates through until the reference clock edge arrives. However, the time resolution is limited to the minimum gate delay in the process [10, 11]. An improved structure is the Vernier TDC shown in Figure 2.5b, which adds a delay line to the  $T_{ref}$  path. The delay elements in the reference line have slightly shorter delays than those in the input chain ( $\tau_1 > \tau_2$ ), such that the time resolution is now the difference between the individual delay elements. These Vernier TDCs overcome the limitation from the minimum gate delay in the process, yet still only

Figure 2.4: Effect of voltage noise with scaling supply voltage for (a) ADC and (b) TDC.

achieve moderate resolution.

$$T_{res,flash} = \tau_1$$

$$T_{res,vernier} = \tau_1 - \tau_2$$

(2.1)

Other previous work [12, 13, 14, 15] has implemented the VCO-based quantizer shown in Figure 2.5b. This structure uses a ring oscillator delay chain to count the number of delays that occur within the sampling period. The VTC operation is inherent, by using the input voltage as the supply for the inverter ring. The benefit is that an analog VTC block is unnecessary and the structure is entirely standard cell elements, but the disadvantage is that the VTC is very nonlinear.

Figure 2.5: Examples of TDC architectures: (a) flash TDC, (b) Vernier TDC, (c) VCO-based TDC. Voltage-to-time operation displayed in gray.

Figure 2.6: TDC delay cells used in (a) multi-path GRO and (b) SRO.

More recent work has used a multi-path gated ring oscillator (GRO) to achieve very fine time resolution [16], but the added complexity to the delay elements push this further from our goal of digital-like design. Similarly, [17] creates a switched-ring oscillator (SRO) that improves upon the GRO but still requires analog complexity in the delay cell and the front-end VTC. While many blocks in the GRO/SRO are highly digital, overall it is not attractive for synthesized ADC design.

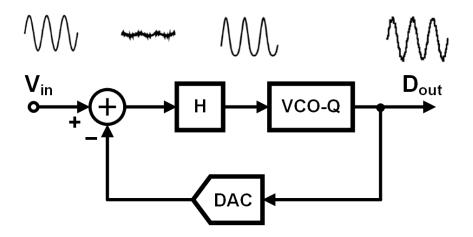

### 2.1.3 Highly-Digital $\Delta\Sigma$ Modulator

One solution to the linearity problems in the VCO quantizer (see Figure 2.5c) is to use it as the quantizer within a  $\Delta\Sigma$  modulator ADC. As shown in Figure 2.7, this pre-distorts the input to the VCO to suppress the quantizer nonlinearity

Figure 2.7: Using a DSM loop to suppress VCO nonlinearity.

and improve resolution [18, 19]. While this allows the highly digital VCO-based quantizer to achieve high linearity, it requires many analog blocks within the  $\Delta\Sigma$  loop, such as integrators and feedback DACs.

The work in [20, 21] similarly uses a VCO-based quantizer in a  $\Delta\Sigma$  ADC, but adds a digital calibration scheme and self-dithering technique that allow the ADC to achieve high resolution without analog integrators, comparators, voltage references or feedback DACs. The only analog requirement is an input V/I converter. By using mostly digital circuitry, it consumes less area and is better suited for technology scaling. These benefits are expected to improve even further with continued process scaling.

#### 2.2 Prior Work in Synthesized Analog Blocks

While the work discussed in Section 2.1 are more compatible with process scaling, they still require a time-consuming custom layout. The motivation for this work is to find architectures that are amenable to both process scaling and to

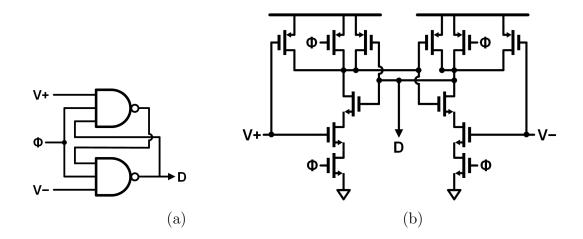

Figure 2.8: An analog comparator constructed from (a) two cross-coupled NAND3 logic gates, to achieve the (b) transistor-level schematic for a comparator.

automated layout. This section studies prior work that automates the layout of an ADC, as well as other design automation tools for analog circuit design.

#### 2.2.1 Synthesized Stochastic Flash ADC

Building on concept described in Section 2.1.1, the work in [22] synthesizes a stochastic flash ADC using an all-digital comparator cell. As shown in Figure 2.8, the comparator is constructed from cross-coupled NAND logic cells. An ADC similar to the one shown in Figure 2.3 is fully synthesized from Verilog code to layout. This offers accelerated design time that is robust to the random mismatch of automated place-and-route, because the only analog signals are the inputs. However, the resolution is still extremely limited (peak is 35.9-dB SNDR at low input frequency). The ability to include some basic analog functionality in addition to the standard digital library would allow the synthesized ADC to achieve greater performance [23].

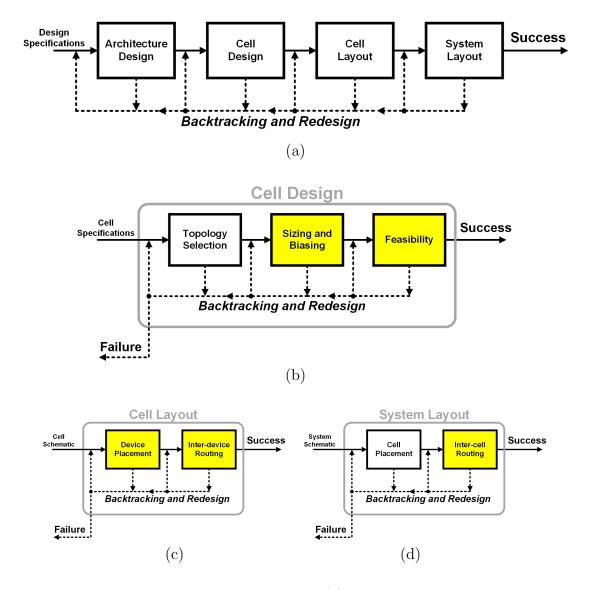

#### 2.2.2 Analog Design Automation

In the past, many designers have made effort to automate portions of the analog circuit design process. The phrase "analog synthesis" has been used to mean many different things, causing confusion and skepticism within the mixedsignal design community. This section will summarize and differentiate between the different analog design automation that has been performed in the past, so that the new contribution of the work presented here will be apparent. Figure 2.9 shows the traditional analog design process and highlights the points at which other tools have provided some level of automation.

First, consider the ASTRX cell design automation tool [24]. This automates the steps highlighted in Figure 2.9b; given the designer's description of the topology (in a format similar to SPICE) and a list of performance specifications, it automatically sizes and biases the circuit, then verifies whether the design will hold up to process variations.

A second example of previous analog design automation is the KOAN tool, for device-level placement and routing [25]. The KOAN algorithm successfully handles symmetries and other important analog layout concerns, but was demonstrated in an archaic  $2\mu$ m CMOS technology, for which the design rules are much more simple than in modern nanoscale processes. It is demonstrated for a simple opamp and a comparator.

The final example of previous analog design automation is shown in Figure 2.9d by the WREN tool, which automates system-level routing. After the designer places all the sub-blocks, this tool optimizes the routing among the blocks to ensure coupling parasitics are within user-defined limits [26]. Other tools provide similar automation, but attempt to minimize area or wirelength. While this is a useful

Figure 2.9: Previous work in automating the (a) traditional analog design process, showing hightlighted blocks where automation has been achieved by (b) ASTRX, (c) KOAN, and (d) WREN.

automation tool, it requires that the designer place the sub-blocks manually, which requires some knowledge of the optimal routing beforehand.

#### 2.3 Summary

Since digital circuits scale better than their analog counterparts, some recent research has focused on creating highly-digital ADC architectures. Redundant and stochastic flash ADCs scale well with process but achieve low resolution. Combining a front-end VTC with a back-end TDC takes advantage of the very scalable time-domain circuits, and pushes all the analog complexity to the frontend VTC. However, achieving high resolution still requires a more complicated, analog-intensive delay cell. This is not in line with the goals of synthesized ADC design.

Previous analog design automation has provided "synthesis" in cell design, cell layout, and system-level routing. But in each case, taking an architectural description to layout still requires some manual and time-consuming layout. To avoid manual layout, the traditional analog design process must be replaced with a different process that is more conducive to automation. The next Chapter describes a vision for a new process, based on the highly-automated digital synthesis and place-and-route tools that already exist.

# CHAPTER 3. PROPOSED ANALOG SYNTHESIS TOOLCHAIN

"I suppose it is tempting, if the only tool you have is a hammer, to treat everything as if it were a nail."

— Abraham Maslow

This Chapter describes a procedure for creating library information for analog cells and adding them alongside the standard digital cells, such that Verilog code describing analog functions can be synthesized into a layout. Using a minimal set of these rudimentary analog components (single-stage opamp, transmission gate, comparator, resistor and capacitor) ADCs may be described in Verilog code, then synthesized and automatically laid out. The same Verilog code may be used in different CMOS processes, demonstrating the rapid portability and scalability of this design technique. In each new process, like the logic gates in the digital standard library, layout and routing information for the custom analog cells must be created and then provided to the design automation tools. The creation of this library information is a one-time occurrence that can then be used in any number of analog designs within that same process node, just like the digital standard library.

## 3.1 Existing Digital Synthesis Toolchain

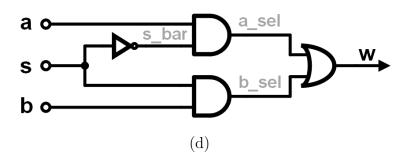

Figure 3.1 illustrates how digital circuits are automatically synthesized from Verilog code. First, the designer writes a register transfer level (RTL) Verilog file that describes the logic function of the circuit. Several examples are shown in Figure 3.2, each creating a 2:1 multiplexer with different levels of abstraction [27]. For example, the code snippet shown in Figure 3.2a uses a logical/Boolean expression for the multiplexing, at a high level of abstraction. While it very likely would arrive at the gate-level schematic shown in Figure 3.2d, it is possible that the logic synthesizer would instead use a different topology, but it is of no concern to the designer. The Verilog code in Figure 3.2b instead uses a primitive gate-level description. This lower level of abstraction specifies which gate functions should be used and how they should be wired, guaranteeing that the logic synthesizer arrives at the schematic shown in Figure 3.2d. However, the primitives are not process-specific, and this Verilog code could be reused in any number of different technologies. In contrast, the module in Figure 3.2c replaces the primitives with process specific logic gate names: for example, AND2X1\_DN\_QQD1 is a specific two-input AND gate with single (X1) drive strength. For a digital design this is not useful, it forces the Verilog to be rewritten to be used in a different process. However, it will be useful for the proposed analog circuit synthesis, as will be discussed in Section 3.3.4.

The second step in the toolchain uses the logic synthesizer tool (Cadence's "Design Compiler", in this example) to convert the RTL Verilog into gate-level Verilog. This requires information about the specific semiconductor process from the foundry, in order to determine which logic gates to use to achieve the RTL logic functions. This is provided in the .LIB file as shown in Figure 3.1. It is sometimes

Figure 3.1: Toolchain used for digital circuit synthesis.

provided in .DB or .TLF format instead, but will be labeled as a .LIB file here. The contents of this file will be described in detail in Section 3.2.3.

There may be multiple versions of cells performing the same logic function (for example, a three-input NAND gate), providing different sizes of the cell that are capable of driving larger/faster outputs at the expense of power consumption. Given the RTL Verilog, the logic synthesizer will find many different combinations of digital standard cells that all achieve the desired logic function. The designer may provide constraints regarding timing, power consumption, and area that will guide the synthesizer in optimizing the gate-level Verilog code. For these reasons, a logical/Boolean Verilog description as in Figure 3.2a may be synthesized into different topologies or versions of the same topology with different gate sizes. Any process-specific gates (as in Figure 3.2c) are passed directly to the gate-level Verilog, unchanged.

The third and final step in Verilog-to-layout synthesis is to convert the gate-

myMux.v

| - |                                                         |

|---|---------------------------------------------------------|

|   | <pre>module multiplexer(input a, b, s, output w);</pre> |

| 2 | <pre>assign w = s ? b : a;</pre>                        |

| 3 | endmodule                                               |

|   | (a)                                                     |

| my | Mux.v                                                   |

|----|---------------------------------------------------------|

| 1  | <pre>module multiplexer(input a, b, s, output w);</pre> |

| 2  | <pre>wire a_sel, b_sel, s_bar;</pre>                    |

| 3  | <b>not</b> U1 (s_bar, s);                               |

| 4  | <b>and</b> U2 (a_sel, a, s_bar);                        |

| 5  | <b>and</b> U3 (b_sel, b, s);                            |

| 6  | <pre>or U4 (w, a_sel, b_sel);</pre>                     |

| 7  | endmodule                                               |

|    | (b)                                                     |

| 1 | <pre>module multiplexer(input a, b, s, output w);</pre> |

|---|---------------------------------------------------------|

| 2 | <pre>wire a_sel, b_sel, s_bar;</pre>                    |

| 3 | <pre>INVX1_DN_QQD1 U1 (s_bar, s);</pre>                 |

| 4 | <pre>AND2X1_DN_QQD1 U2 (a_sel, a, s_bar);</pre>         |

| 5 | AND2X1_DN_QQD1 U3 (b_sel, b, s);                        |

| 6 | <b>OR2X1_DN_QQD1</b> U4 (w, a_sel, b_sel);              |

| 7 | endmodule                                               |

|   | (c)                                                     |

Figure 3.2: Instantiations in Verilog can be (a) logical, (b) primitive gate-level, or (c) process-specific gate-level. All describe the same (d) schematic.

level Verilog into a layout, using a place-and-route (PNR) tool. Cadence's "Encounter" is used in this work. This requires additional information about the standard digital library, as shown in Figure 3.1. The additional information is related to layout and routing of each standard cell, and will be described in Sections 3.2.1 and 3.2.2 respectively. It is possible that the routing will be sufficiently long that the PNR tool will deem it necessary to add digital buffers at certain points in the layout. These do not affect the logic function, but will cause the final Verilog file to be slightly different than the gate-level Verilog. The last output file is the top-level GDS layout.

## 3.2 Library Information for Digital Standard Cells

This Section provides information about each of the three library files used in digital synthesis. It explains what the files contain and how that information is used by the software tools. Code snippets of example library information are included to assist the reader. While examples are useful to illustrate the main points, it is impossible to include all the variations and subtleties here. References to more detailed and thorough User Guides are included for each file type, and will be indispensable for further work.

#### 3.2.1 Graphic Database System (GDS) Information

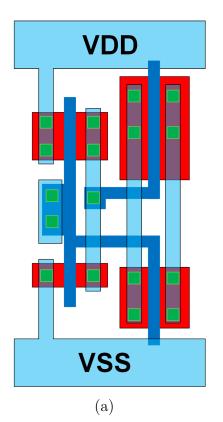

The GDS or GDSII file format is a binary description of geometry of the integrated circuit (IC) layout. It is organized hierarchically and contains the layer, location, and size of each material in the layout. This includes any text (such

as pin labels) added to the layout. It does not contain any information about the function of its contents, and there is no guarantee that the contents meet the Design Rule Check (DRC). Since it is a binary file it is not informative to go into detail here, but the interested reader should consult the Format Manual [28]. For our purposes, just consider that the GDS file describes the geometric layers of the layout, and can be visualized as the IC layout itself as shown in Figure 3.3.

## 3.2.2 Library Exchange Format (LEF) Information

Library Exchange Format (LEF) files contain information related to routing. It can be divided into two categories: technology information and individual cell information (called "macros"). The technology LEF contains definitions for each metal and via layer used in the process, including sizing, spacing and antenna information to meet DRC requirements. For metal layers, it describes the parasitic resistances and capacitances, and defines a routing direction. Finally, it defines different contacts that may be used by the place-and-route tool. Examples of the layer and contact definitions are shown in Figures 3.4 and 3.5, respectively.

The macro LEF file contains descriptions of each of the standard cells in the library. Another LEF file will contain macros for each of the digital standard cells. It identifies the dimension of each cell and the locations of its input/output pins. Each pin is identified by the appropriate metal layer(s) and areas. Diffusion and gate areas are specified for each pin to avoid antenna errors. Finally, "obstruction" areas are specified, to prevent the place-and-route tool from causing shorts with the metal routing. Examples of a cell macro and pin statement are shown in Figure 3.6. While this example gives the reader a feel for the information and organization of the file, there are many more options and variations that can be used. Cadence's

tgateX1.gds

| Ugatexi.gus |      |      |      |      |      |      |      |      |

|-------------|------|------|------|------|------|------|------|------|

| Address     | Data |      |      |      |      |      |      |      |

| 0000000     | 0600 | 0200 | 0500 | 1c00 | 0201 | 7000 | 0a00 | 0a00 |

| 0000010     | 0b00 | 0e00 | 1600 | 7000 | 0a00 | 0b00 | 0b00 | 2800 |

| 0000020     | 2600 | 0e00 | 0602 | 5953 | 414e | 4344 | 442e | 0042 |

| 0000030     | 1400 | 0503 | 413e | 3789 | c64b | efa7 | 4439 | 2fb8 |

| 0000040     | 9ba0 | 515a | 1c00 | 0205 | 4500 | 0c00 | 1f00 | 1000 |

| 0000050     | 0000 | 0000 | 7000 | 0a00 | 0a00 | 0a00 | 2300 | 0f00 |

| 0000060     | 0c00 | 0606 | 4c54 | 695f | 766e | 3158 | 0400 | 0008 |

| 0000070     | 0600 | 020d | 0200 | 0600 | 020e | 0000 | 7c00 | 0310 |

|             |      |      |      |      |      |      |      |      |

| 0000a30     | 0007 | 0400 | 0004 | 0000 | 0000 | 0000 | 0000 | 0000 |

| 0000a40     | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 |

| (b)         |      |      |      |      |      |      |      |      |

|             |      |      |      |      |      |      |      |      |

Figure 3.3: Example of how a standard cell might appear in (a) layout view, and (b) a hexdump of the binary GDS file describing it.

tech.lef

| 1  | LAYER metal1                                                      |

|----|-------------------------------------------------------------------|

| 2  | TYPE ROUTING ;                                                    |

| 3  | <b>direction</b> Horizontal ;                                     |

| 4  | <b>PITCH</b> 0.56 ;                                               |

| 5  | OFFSET 0.28 ;                                                     |

| 6  | WIDTH 0.23 ;                                                      |

| 7  | <b>AREA</b> 0.20 ;                                                |

| 8  | SPACING 0.23 RANGE 0 9.995 ;                                      |

| 9  | SPACING 0.6 RANGE 10.0 35.0 ;                                     |

| 10 | <pre># Resistance is in ohms/square</pre>                         |

| 11 | RESISTANCE RPERSQ 0.082 ;                                         |

| 12 | <pre># Area cap is in pF/um<sup>2</sup> using C/A=epsilon/d</pre> |

| 13 | CAPACITANCE CPERSQDIST 0.0000186 ;                                |

| 14 | # Edge cap is in pF/um                                            |

| 15 | EDGECAPACITANCE 0.0001177 ;                                       |

| 16 | THICKNESS 0.52 ;                                                  |

| 17 | ANTENNAAREARATIO 200 ;                                            |

| 18 | ANTENNASIDEAREARATIO 400 ;                                        |

| 19 | END metall                                                        |

| 20 | •••                                                               |

| 21 | LAYER vial                                                        |

| 22 | TYPE CUT ;                                                        |

| 23 | SPACING 0.26 ;                                                    |

| 24 | ANTENNAAREARATIO 20 ;                                             |

| 25 | END vial                                                          |

Figure 3.4: Example technology LEF layer definitions.

```

tech.lef

VIA M1_M2 DEFAULT

1

2

RESISTANCE 10 ;

3

LAYER metal2 ;

4

RECT -0.14 -0.19 0.14 0.19 ;

5

LAYER vial ;

6

RECT -0.13 -0.13 0.13 0.13 ;

7

LAYER metal1 ;

8

RECT -0.19 -0.14 0.19 0.14 ;

9

END M1_M2

10

. . .

11

VIA M1_POLY DEFAULT

12

RESISTANCE 12.5 ;

13

LAYER metal1 ;

RECT -0.17 -0.115 0.17 0.115 ;

14

15

LAYER contact ;

16

RECT -0.11 -0.11 0.11 ;

17

LAYER poly ;

18

RECT -0.21 -0.21 0.21 0.21 ;

19

END M1_POLY

```

Figure 3.5: Example technology LEF contact definitions.

LEF reference manual provides more details [29].

#### 3.2.3 Liberty (LIB) Timing File Information

Functional, area, timing and power information for each cell may be provided in either Timing Library Format (.TLF) or open-source Liberty (.LIB) file format. These ASCII representations may also be compiled into a binary database (.DB) format. Examples of the technology and individual cell information are shown in Figures 3.7 and 3.8, respectively. The logic synthesizer uses the functional information to first identify combinations of standard cells which achieve the desired RTL function, then to pick the optimal gate combination that achieves the timing constraints and area/power specifications provided by the designer.

While the examples here are useful to understand what information is provided, there is much more detailed and general descriptions of the file formatting available in the respective reference manuals [30, 31].

## 3.3 Creating Custom Analog Cell Information

With an understanding of how the digital toolchain synthesizes a final GDS layout from Verilog, we now move on to the task of adding analog functionality to the standard cell library. We begin by considering what "minimum effective dose" of analog cells will allow us to synthesize analog-to-digital converters. Then the procedure for creating the GDS, LEF and LIB information for these cells is described. This Section concludes with examples of instantiating and floorplanning analog cells in Verilog. myCell.lef

| myce | err.rer                                |

|------|----------------------------------------|

| 1    | MACRO invx1                            |

| 2    | CLASS CORE ;                           |

| 3    | FOREIGN invx1 0.000 0.000 ;            |

| 4    | ORIGIN 0.000 0.000 ;                   |

| 5    | SIZE 1.980 BY 5.040 ;                  |

| 6    | SYMMETRY x y ;                         |

| 7    | SITE CORE ;                            |

| 8    | PIN Y                                  |

| 9    | AntennaDiffArea 0.855 ;                |

| 10   | <b>DIRECTION</b> OUTPUT ;              |

| 11   | PORT                                   |

| 12   | LAYER metal1 ;                         |

| 13   | <b>RECT</b> 1.365 1.220 1.805 3.600 ;  |

| 14   | END                                    |

| 15   | END Y                                  |

| 16   | PIN A                                  |

| 17   | AntennaGateArea 0.27 ;                 |

| 18   | <b>DIRECTION</b> INPUT ;               |

| 19   | PORT                                   |

| 20   | LAYER metal1 ;                         |

| 21   | <b>RECT</b> 0.175 1.870 1.055 2.435 ;  |

| 22   | END                                    |

| 23   | END A                                  |

| 24   | PIN VSS                                |

| 25   | <b>DIRECTION</b> INOUT ;               |

| 26   | <b>USE</b> ground ;                    |

| 27   | SHAPE ABUTMENT ;                       |

| 28   | PORT                                   |

| 29   | LAYER metal1 ;                         |

| 30   | <b>RECT</b> 0.000 -0.400 0.465 0.400 ; |

| 31   | <b>RECT</b> 0.465 -0.400 0.885 1.500 ; |

| 32   | <b>RECT</b> 0.885 -0.400 1.980 0.400 ; |

| 33   | END                                    |

| 34   | END VSS                                |

| 35   | [VDD pin statement]                    |

| 36   | END invx1                              |

Figure 3.6: Example LEF macro statement.

myCells.lib

```

library(library_name) {

1

2

delay_model : table_lookup ;

3

time_unit : ``lns'' ;

voltage_unit : ``1V'' ;

4

current_unit : ``luA'' ;

5

``1kohm'' ;

6

pulling_resistance_unit :

7

capacitive_load_unit(1, pf) ;

8

leakage_power_unit : ``1nW'';

9

power_supply () { power_rail(VDD, 1.20) ; }

10

operating_conditions(TYP) {

11

12

process : 1.0 ;

13

temperature : 60 ;

14

voltage : 1.20 ; }

wire_load(``500_CELLS'') {

15

16

resistance : 0;

17

capacitance : 0.000140 ;

18

area : 0.01 ;

19

slope : 36

20

fanout_length(1,33) ;

21

. . .

22

fanout_length(5,198) ; }

23

[other wire load models]

24

25

slew_lower_threshold_pct_rise : 10 ;

26

slew_upper_threshold_pct_rise :

90 ;

27

[other threshold definitions]

28

29

input_voltage (I_VDD_120_Rail) {

30

vil : 0.1 * VDD ;

31

vih : 0.9 * VDD ;

vimin : -0.5;

32

33

vimax : VDD + 0.5 ; }

34

output_voltage (O_VDD_120_Rail) {

35

vol : 0.1 * VDD ;

36

voh : 0.9 * VDD ;

37

vomin : -0.1 \times VDD;

38

vomax : 1.1 * VDD ; }

39

lu_table_template(general_template_7_8) {

40

variable_1 : total_output_net_capacitance

41

index_1(``1, 2, 3, 4, 5, 6, 7'');

variable_2 : input_net_transition

42

index_2(``1, 2, 3, 4, 5, 6, 7, 8''); }

43

44

[other LUT template]

45

[cell definitions]

46

```

Figure 3.7: Example LIB technology definitions.

myCells.lib

| myC | ells.lib                                             |

|-----|------------------------------------------------------|

| 1   | cell(INVX1) {                                        |

| 2   | area : 6.65 ;                                        |

| 3   | cell_footprint : inv ;                               |

| 4   | <b>pin</b> (Y) {                                     |

| 5   | direction : output ;                                 |

| 6   | output_voltage : O_VDD_120_Rail ;                    |

| 7   | output_signal_level : VDD ;                          |

| 8   | function : ``(!A)''                                  |

| 9   | <pre>max_capacitance : 0.17 ;</pre>                  |

| 10  | internal_power() {                                   |

| 11  | related_pin : ``A'';                                 |

| 12  | fall_power(LUT size) {LUT}                           |

| 13  | rise_power(LUT size) {LUT} }                         |

| 14  | timing() {                                           |

| 15  | cell_rise(LUT size) {LUT}                            |

| 16  | rise_transition(LUT size) {LUT}                      |

| 17  | cell_fall( <i>LUT size</i> ) { <i>LUT</i> }          |

| 18  | fall_transition(LUT size) {LUT}                      |

| 19  | <pre>steady_state_current_high(LUT size) {LUT}</pre> |

| 20  | noise_immunity_high(LUT size) {LUT}                  |

| 21  | steady_state_current_low(LUT size) {LUT}             |

| 22  | noise_immunity_low(LUT size) {LUT}                   |

| 23  | timing_sense : negative_unate ;                      |

| 24  | <pre>related_pin : ``A'' ; }</pre>                   |

| 25  | }                                                    |

| 26  | <pre>pin(VDD) { direction : input ; }</pre>          |

| 27  | <pre>pin(VSS) { direction : input ; }</pre>          |

| 28  | pin(A) {                                             |

| 29  | direction : input ;                                  |

| 30  | input_voltage : I_VDD_120_Rail ;                     |

| 31  | input_signal_level : VDD ;                           |

| 32  | capacitance : 0.0029;                                |

| 33  | max_transition : 2.0000 ;                            |

| 34  | rise_capacitance : 0.0029;                           |

| 35  | fall_capacitance : 0.0029;                           |

| 36  | rise_capacitance_range(0.0029, 0.0029);              |

| 37  | fall_capacitance_range(0.0029, 0.0029);              |

| 38  | }                                                    |

| 39  | leakage_power () {                                   |

| 40  | when : ``(!A)'';                                     |

| 41  | value : ``9.199620'' ; }                             |

| 42  | leakage_power () {                                   |

| 43  | when : ``A'';                                        |

| 44  | value : ``8.225110'' ; }                             |

| 45  | cell_leakage_power : 8.712365                        |

| 46  | }                                                    |

|     | ر <sub>ا</sub>                                       |

Figure 3.8: Example LIB cell definition.

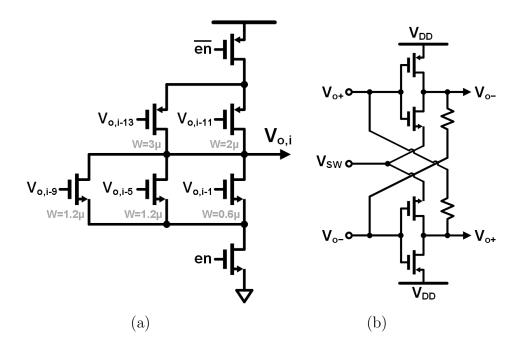

Figure 3.9: A minimal set of custom cells for analog design.

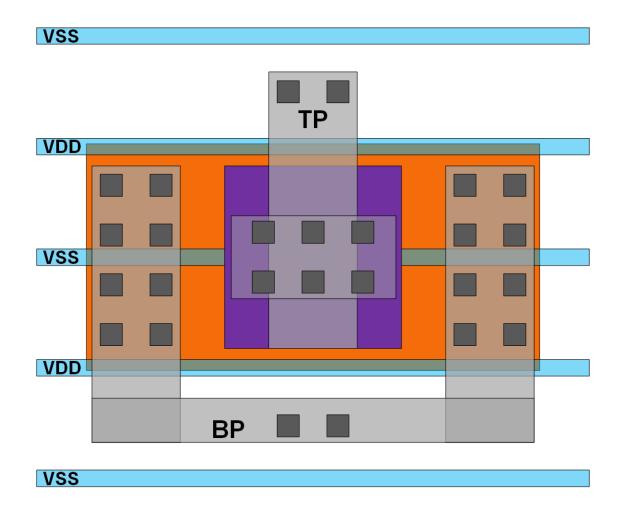

#### 3.3.1 Minimalist Set of Analog Cells

Figure 3.9 shows set of analog cells that enable a designer to synthesize ADCs. The most obvious is a comparator cell, which is necessary for building a quantizer. Second, a unit capacitor and switch cell are needed to implement the switchedcapacitor circuits that are fundamental to discrete-time ADCs. To maintain the "digital-like" nature of the synthesized data converters, bootstrapping will not be used. A simple transmission gate should suffice. Third, a unit resistor cell is useful for implementing reference ladders and other simple analog functions. Finally, some amplification technique will prove useful in many different architectures. This is the most analog of the custom cells and will prove the most difficult to design, because the traditional analog techniques like gain-boosting and compensation are too complex for synthesized ADCs. Other techniques like cascoding are not friendly with process scaling, and should be avoided. Simple and scalable amplification solutions will be described in later Chapters.

#### 3.3.2 Creating .GDS File for Custom Cell

Creating a custom cell begins the same as in traditional analog design: a transistor-level schematic is created, then laid out. However, since the cell will be place-and-routed alongside standard digital cells, it must fit within the digital supply pitches. An easy way to start is to copy a filler cell from the digital standard library, and delete everything except the supply rails. If more room is necessary, the rails can be widened or the cell can span multiple supply pitches, as shown in Figure 3.10. To avoid DRC violations with adjacent cells, it is necessary to leave a gap between the layers and the right and left edges of the custom cell. The width of this gap will depend on the DRC rules for the given process.

In Cadence, the layout view will be saved as a Cadence DataBase (.CDB) file type. To stream it out in GDS format, open the Integrated Circuit Front-to-Back (ICFB) window. The default setup may result in a licensing error, so run the following command in ICFB terminal (Figure 3.11a):

```

>> hiSetMenuItemCallback(eval(ExportItem) 'StreamOut

'pipoDisplay(transStreamOutForm)'')

```

Similarly, the following command prevents licensing errors for the stream-in process that will be used later:

```

>> hiSetMenuItemCallback(eval(ImportItem) 'StreamIn

'pipoDisplay(transStreamInForm)'')

```

To complete the stream-out process, select  $File \rightarrow Export \rightarrow Stream...$  in the ICFB window. This will open the "Virtuouso Stream Out" menu shown in Figure 3.11b. Complete the menu with the library name and cell name you wish to export. Selected "OK" to begin the PIPO STRMOUT. When it is complete, the tool will notify you that the process was successful as shown in Figure 3.11c.

Figure 3.10: Example of multi-pitch custom cell layout, for a MIM capacitor.

| icfb ·                                                                                                      | · Log: /nfs/guille/u | 2/w/watersal/CDS.log                  | _    | □ × |

|-------------------------------------------------------------------------------------------------------------|----------------------|---------------------------------------|------|-----|

| File Tools Options                                                                                          |                      |                                       | Help | 1   |

| Loading acv.cxt<br>Loading auCore.cxt<br>Loading schView.cxt<br>Loading selectSv.cxt<br>Loading seismic.cxt |                      |                                       |      |     |

| hiSetMenuItemCallback(eval(Expo                                                                             | rtItem) 'StreamOu    | t "pipoDisplay(transStreamOutForm)")] |      |     |

| mouse L:                                                                                                    | M :                  | R:                                    |      |     |

| >                                                                                                           |                      |                                       |      |     |

(a)

| Uirtuoso                           | ® Stream Out _ 🗆 🗙                    |

|------------------------------------|---------------------------------------|

| OK Cancel Defaults Apply           | Help                                  |

| User-Defined Data And Options User | Defined Data Options Set Fast Options |

| Template File Load Save Browse     | Ĭ                                     |

|                                    | Library Browser                       |

| Run Directory                      | Į.                                    |

| Library Name                       | synTSMC                               |

| Top Cell Name                      | unitC_25f                             |

| View Name                          | layout                                |

| Output                             | 🔶 Stream DB 😞 ASCII Dump              |

| Output File                        | unit0_25f.gds Browse                  |

| Compression 🔷                      | gzip 🔷 bzip2 🔷 compress 🔶 none        |

| Scale UU/DBU                       | 0.00100000                            |

| Units                              | ◆ micron 🔷 millimeter 🔷 mil           |

| Process Nice Value 0-20            | 0                                     |

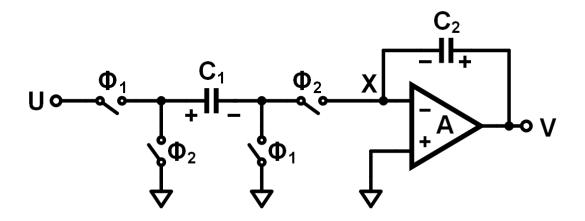

| Error Message File                 | PIPO. LOĞ Browse                      |