#### AN ABSTRACT OF THE THESIS OF

Homayoon Haddad for the degree of Doctor of Philosophy in

Electrical and Computer Engineering presented on February

20, 1990

Title: Characterization of Oxygen and Carbon Effects in Silicon Material and MOSFET Devices.

# Redacted for privacy

Abstract approved. Leonard Forbes

Material defect characterization has proved to be a valuable tool in today's submicron Metal-Oxide-Semiconductor Field Effect Transistor development. As the complexity of new processes grows, devices have to become more reliable in order to stand several levels of plasma etching, ion implantation and three or more layers of metallization. DLTS and photocapacitance have been used to characterize oxygen induced microdefects and stacking faults in silicon. Stacking faults in wafers with low carbon impurity were electrically active and an energy level  $E_{\rm c}$ - $E_{\rm t}$ =.48 +/- .05 eV was detected. Wafers with a trace of carbon did not show any electrically active centers. From this observation, carbon

was implanted at Si-SiO<sub>2</sub> interface in MOSFET devices. Carbon implanted devices with an effective gate length of 0.8 micron were subjected to hot carriers degradation and a lower degradation was detected.

Copyright by Homayoon Haddad

April 27, 1990

All Rights Reserved

# Characterization of Oxygen and Carbon Effects in Silicon Material and MOSFET Devices

by

Homayoon Haddad

#### A THESIS

submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of Doctor of Philosophy

Completed February 20, 1990

Commencement June 1990

#### APPROVED:

## Redacted for privacy

Professor of Electrical and Computer Engineering in charge of major

# Redacted for privacy

Head of department of Electrical and Computer Engineering

## Redacted for privacy

Dean of Graduate School

Date thesis is presented:

February 20, 1990

Typed by researcher for:

Homayoon Haddad

To my mother, wife, and son

#### **ACKNOWLEDGMENTS**

I would like to express my sincere appreciation to Professor L. Forbes for his guidance and support during this investigation. I am grateful to Dr. Peter Burke for his interest and many valuable discussions. I would like to thank Dr. John Aurthor and Dr. J. Van Vechton for reviewing this work and their suggestions.

Thanks are also extended to Steve Shevenock for his initial support and Wayne Richling for his interest and support throughout this work. I am also grateful to the Staff at Hewlett-Packard's Northwest Integrated Circuit Division (NID) for their financial and moral support and also for the opportunity to use the excellent equipment and many useful discussions throughout this investigation.

### TABLE OF CONTENTS

| 1. | Intro   | duction                                                     | 1        |

|----|---------|-------------------------------------------------------------|----------|

| 2. | Technic | cal background                                              | 5        |

|    | 2.1     | Oxygen induced microdefects in n-type silicon               | 5        |

|    | 2.1.1   | Oxygen in silicon                                           | 6        |

|    | 2.1.2   | Oxygen precipitation                                        | 7        |

|    | 2.1.3   | Nucleation Model                                            | 8        |

|    | 2.1.4   | Growth of bulk stacking faults (BSF)                        | 11       |

|    | 2.2     | Carbon in silicon                                           | 14       |

|    | 2.3     | Electrical activity of microdefects in silicon              | 17       |

|    | 2.3.1   | Electrical activity of dislocations                         | 18       |

|    | 2.3.2   | Electrical activity of defects in silicon after deformation | 19       |

|    | 2.3.3   | Electrical activity of oxygen precipitates (OP'S)           | 21       |

|    | 2.3.4   | Electrical activity of stacking faults (SF)                 | 24       |

|    | 2.4     | N-channel hot carrier reliability                           | 26       |

|    | 2.4.1   | Hot carrier generation Impact ionization                    | 27<br>28 |

|    | 2.4.2   | Hot carrier injection Lucky electron model                  | 29<br>30 |

|    | 2.4.3   | Hot carrier trapping Fair and Sun Model                     | 31<br>32 |

| 3. | Experi  | mental techniques                                           | 36       |

|    | 3.1     | Deep level transient spectroscopy (DLTS)                    | 37       |

|    | 3.1.1   | Transient analysis                                          | 39       |

|    | 3.1.2   | Capacitance DLTS                                            | 41       |

|    | 3.1.3            | Time filtering technique of DLTS                                                   | .42 |

|----|------------------|------------------------------------------------------------------------------------|-----|

|    | 3.2              | Current DLTS                                                                       | 46  |

|    | 3.3              | Photocapacitance measurement                                                       | 48  |

|    | 3.4              | FTIR                                                                               | 51  |

|    | 3.5              | MOSFET device and aging measurement systems                                        | 53  |

| 4. | Experi<br>Part I | mental procedures and results . Material characterization                          | 55  |

|    | 4.1 H            | eat treatment cycles                                                               | 55  |

|    | 4.2 S            | chottky diode fabrication                                                          | 58  |

|    | 4.3 D            | LTS characterization of heat treated wafers                                        | 62  |

|    |                  | hotocapacitance characterization of heat reated wafers                             | 81  |

| 5. | Experi<br>Part I | mental procedure and results I. Device characterization                            | 86  |

|    | 5.1 Ho           | t electron aging procedure and results                                             | 86  |

|    | 5.2 Ho           | t hole aging procedure and results                                                 | 96  |

|    | 5.3 Ca           | rbon effects on Si-SiO <sub>2</sub> interface                                      | 98  |

| 6. |                  | L FOR THE EFFECT OF CARBON ON OXYGEN INDUCED NG FAULTS AND Si-SiO2 INTERFACE TRAPS | 101 |

| 7. | Conclus          | sions and Future work                                                              | 109 |

| 8. | Refere           | nces                                                                               | 111 |

## LIST OF FIGURES

| FIGUI | RE PA                                                                                                                                                                        | AGE |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

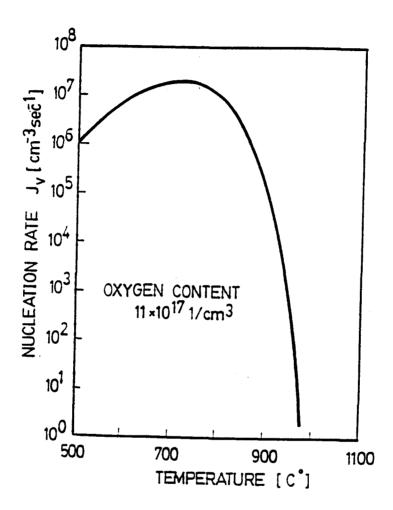

| 1.    | Nucleation rate of precipitates vs temperature after Wada et al [8]                                                                                                          | .10 |

| 2.    | Schematic of the stages in the development of bulk staking faults after Patel et al [13]                                                                                     | 12  |

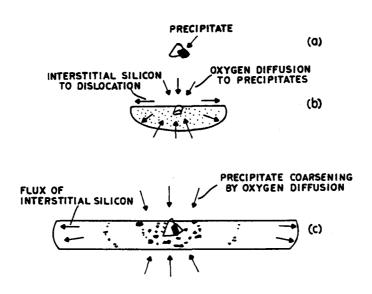

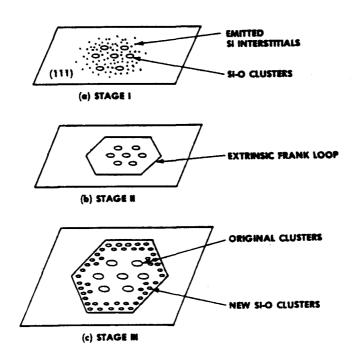

| 3.    | Schematic of the formation of an extrinsic stacking faults after Mahajan et al [4]                                                                                           | 13  |

| 4.    | Scanning Auger measurements data showing a high concentration of carbon at stacking faults corners and no carbon in the clear area next to faults after WE Bailey et al [18] | 16  |

| 5.    | Schematic comparison of dislocation levels in silicon by variety of experimental techniques                                                                                  | 19  |

| 6.    | DLTS spectra for different deformation of n-type silicon after P. Omling [27]                                                                                                | 21  |

| 7.    | Schematic of silicon band diagram with band bending due to positive fixed charges in OP's after Hwang and Schroder [28]                                                      | 23  |

| 8.    | Lifetime and OP's density as function of annealing at 850 C after Massumi [29]                                                                                               | 23  |

| 9.    | Hot carrier effects in n-channel devices                                                                                                                                     | 26  |

| 10.   | Band diagram for lucky electron model with barrier lowering after Ning [38]                                                                                                  | 31  |

| 11.   | The Si-SiO <sub>2</sub> interface defects after Svensson [12] (b) H <sub>2</sub> anneal after Fair [44]                                                                      | 33  |

| 12.   | Model of interface and fixed charge formation after Fair [44]                                                                                                                | 34  |

| 13.   | The OSU capacitance DLTS system diagram with detectability limit of 1.0E11 / cm 3                                                                                            | 38  |

### LIST OF FIGURES (continued)

| FIGUI | RE P                                                                                                                                                                                                              | AGE |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 14.   | N-type silicon with Schottky diode                                                                                                                                                                                | 41  |

| 15.   | Implementation of time filtering by means of a double-boxcar. The output corresponds to average difference at sampling time t1 and t2 after [52]                                                                  | 44  |

| 16a.  | The capacitance transient caused by thermal emission from a majority carrier trap [52]                                                                                                                            | 45  |

| 16b.  | The capacitance transient caused by thermal emission from a minority carrier trap [52]                                                                                                                            | 46  |

| 17.   | The drain current deep level transient spectroscopy system diagram                                                                                                                                                | 47  |

| 18.   | The photocapacitance system diagram                                                                                                                                                                               | 50  |

| 19.   | FTIR measurements of absorbance versus wavenumber of heat treated wafers                                                                                                                                          | 52  |

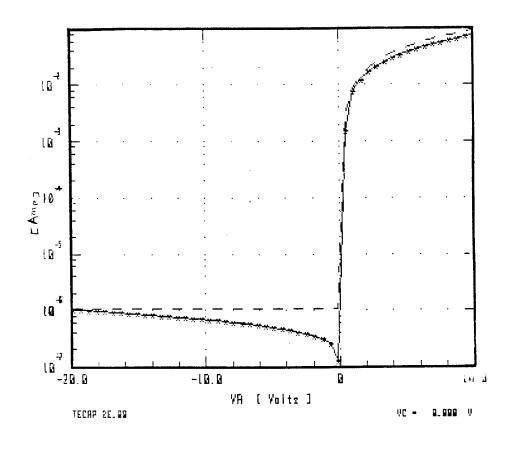

| 20.   | TECAP transistor measurement system [63]                                                                                                                                                                          | 54  |

| 21.   | Heat treatment cycles for studying bulk microdefects and stacking faults                                                                                                                                          | 56  |

| 22.   | A three step process to make Schottky diodes on a chemically or plasma etched silicon surface                                                                                                                     | 59  |

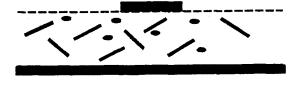

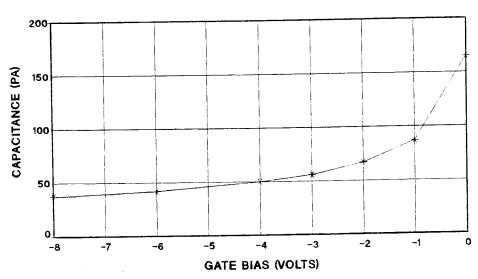

| 23.   | I-V and C-V characteristics of a heat treated wafer and plasma etched surface (wafer #71)                                                                                                                         | 60  |

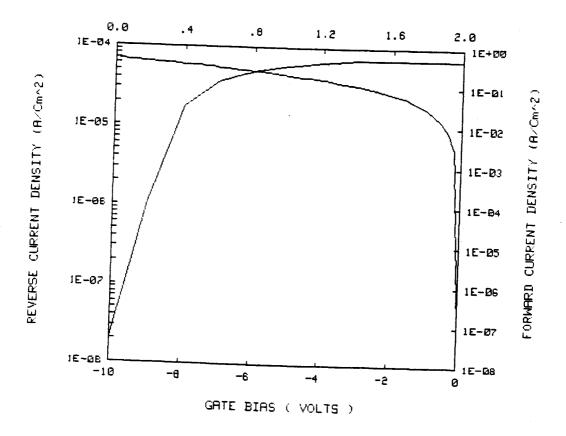

| 24.   | Saturation current and ideality factor can be obtained from a log-linear plot (wafer #25)                                                                                                                         | 61  |

| 25.   | DLTS spectra of control sample #25 with no surface etch or heat treatment, $t_1/t_2=10/40$ , $N_T=0$                                                                                                              | 65  |

| 26.   | DLTS spectra of control sample I with no heat treatment, but about 25 micron was plasma etched from the wafer surface to examine the plasma etching effect on the silicon surface, $t_1/t_2$ =10/40 mS , $N_T$ =0 | 66  |

### LIST OF FIGURES (continued)

| FIGUI | PAGE PAGE                                                                                                                                 |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------|

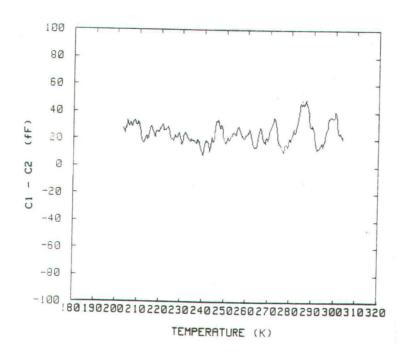

| 27.   | DLTS spectra of wafer #9. Carbon concentration is $2.6E16 / cm^3$ . No electrical activity is detected, $t_1/t_2 = 10/40 mS$ , $N_T=0$    |

| 28.   | DLTS spectra of wafer #10. Carbon concentration is $6.8E15 / cm^3$ . No electrical activity is detected, $t_1/t_2 = 10/40 mS$ , $N_T=0$   |

| 29.   | DLTS spectra of wafer #16. Carbon concentration is 1.349E15 /cm $^3$ . No electrical activity is detected, $t_1/t_2$ = 10/40 mS, $N_T$ =0 |

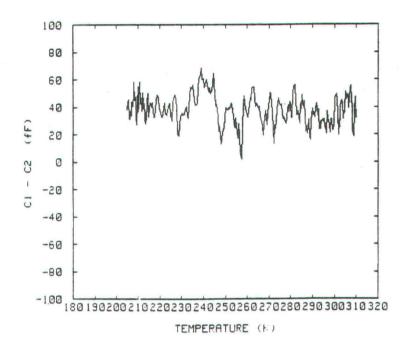

| 30.   | DLTS spectra of wafer #17. Carbon concentration is zero, $t_1/t_2$ = 10/40 mS, $N_{\rm T}$ = 2.0E12 /cm <sup>3</sup> 70                   |

| 31.   | DLTS spectra of wafer #24. Carbon concentration is zero, $t_1/t_2 = 10/40$ mS, $N_T = 7.0E11$ /cm <sup>3</sup> 71                         |

| 32.   | DLTS spectra of wafer #26. Carbon concentration is zero, $t_1/t_2$ = 10/40 mS, $N_{\rm T}$ = 3.69E11 /cm <sup>3</sup> 72                  |

| 33.   | DLTS spectra of wafer #27. Carbon concentration is zero, $t_1/t_2$ = 10/40 mS, $N_{\rm T}$ = 8.10E11 /cm <sup>3</sup> 73                  |

| 34.   | DLTS spectra of wafer #31. Carbon concentration is zero, $t_1/t_2$ = 10/40 mS, $N_{\rm T}$ =6.0E11 /cm <sup>3</sup>                       |

| 35.   | DLTS spectra of wafer #55. Carbon concentration is zero, $t_1/t_2$ = 10/40 mS, $N_T$ = 2.9E12 /cm <sup>3</sup>                            |

| 36.   | DLTS spectra of wafer #71. Carbon concentration is zero, $t_1/t_2$ = 10/40 mS, $N_T$ = 3.2E12 /cm <sup>3</sup> 76                         |

| 37.   | DLTS spectra of wafer #107. Carbon concentration is zero, $t_1/t_2$ = 10/40 mS, $N_{\rm T}$ = 7.7E11 /cm <sup>3</sup> 77                  |

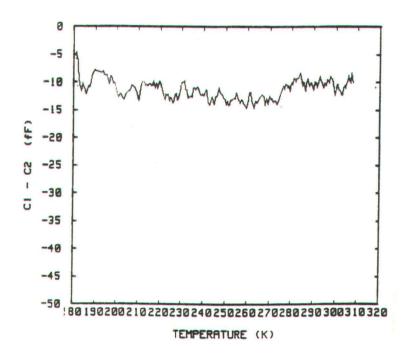

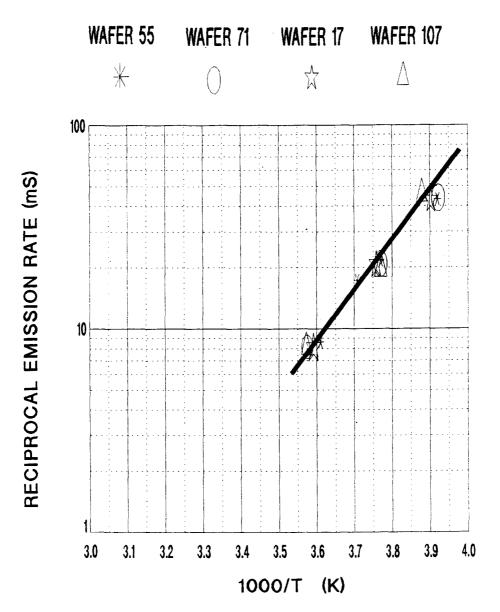

| 38.   | Arrhenius plots of emission rates for wafers 17, 55 71, and 107. A single energy level at $E_c$ - $E_t$ =.48 eV was detected              |

### LIST OF FIGURES (continued)

| FIGU | RE PAG                                                                                  | GE |

|------|-----------------------------------------------------------------------------------------|----|

| 39.  | DLTS spectra of control wafer B before and after mechanical damage                      | 80 |

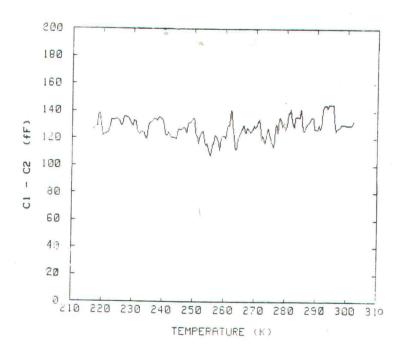

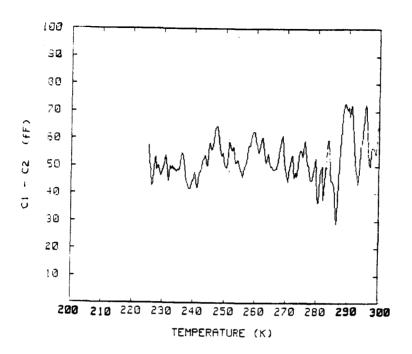

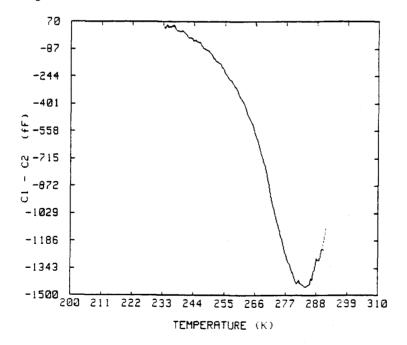

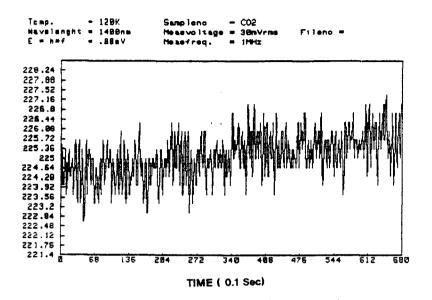

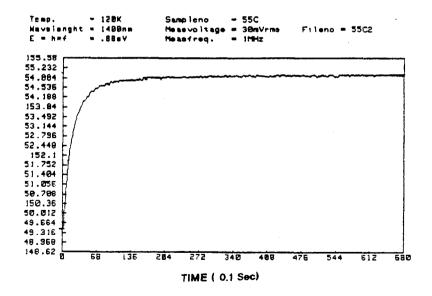

| 40.  | Photocapacitance transient associated with control and wafer #55                        | 84 |

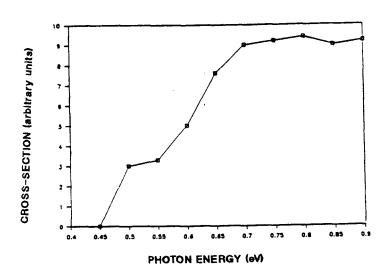

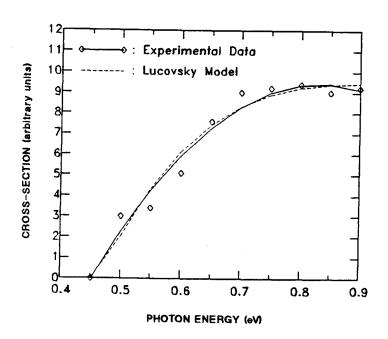

| 41.  | Optical cross section vs photo energy and comparison to the Lucovsky model on wafer #55 | 85 |

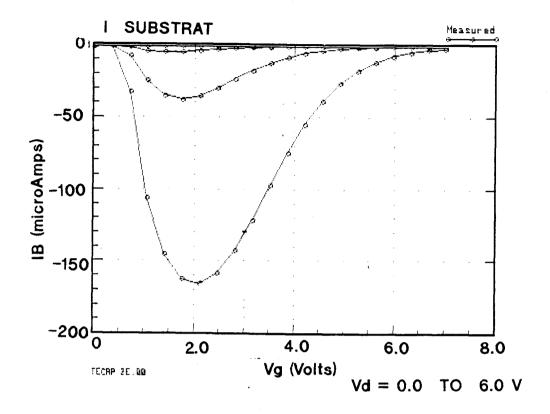

| 42.  | Substrate current as a function of gate voltage                                         | 38 |

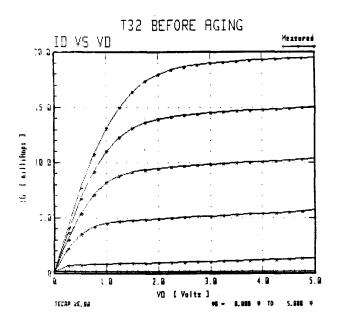

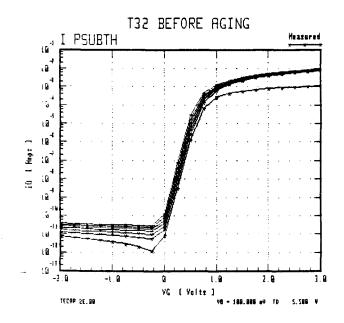

| 43.  | TECAP measurement of device T32 parameters                                              | 91 |

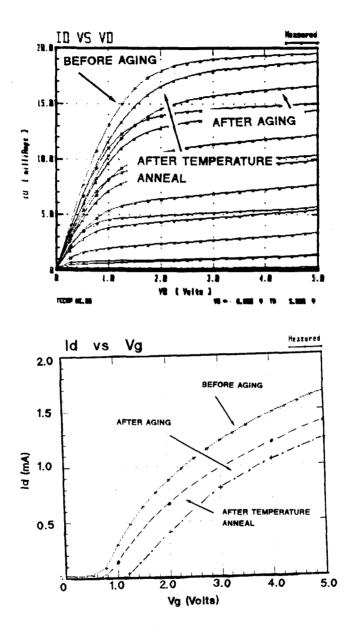

| 44.  | Device T32 parameters after aging and temperature annealing                             | 92 |

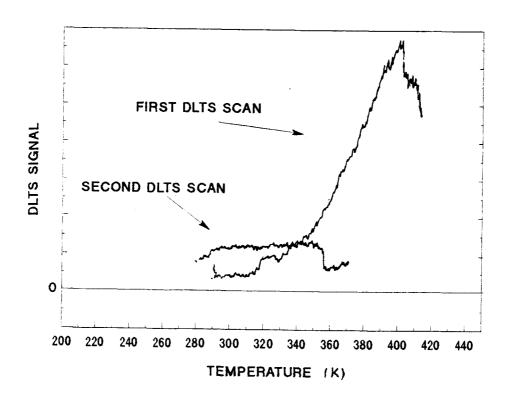

| 45.  | Drain current DLTS results of device T34                                                | €3 |

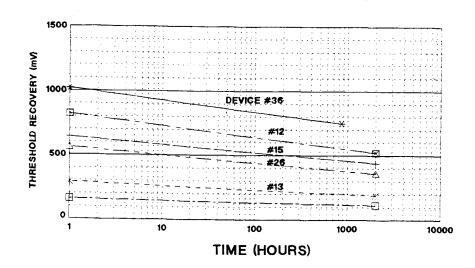

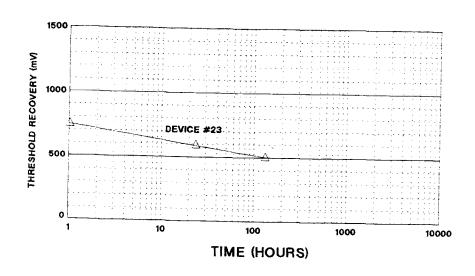

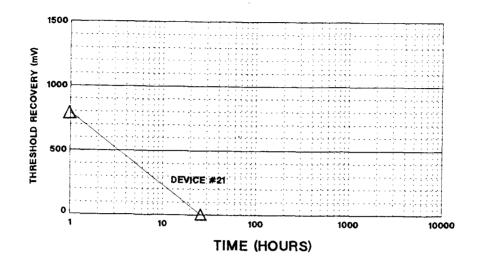

| 46.  | Hot electron detrapping as a function of time at 25, 70, 150 C                          | 94 |

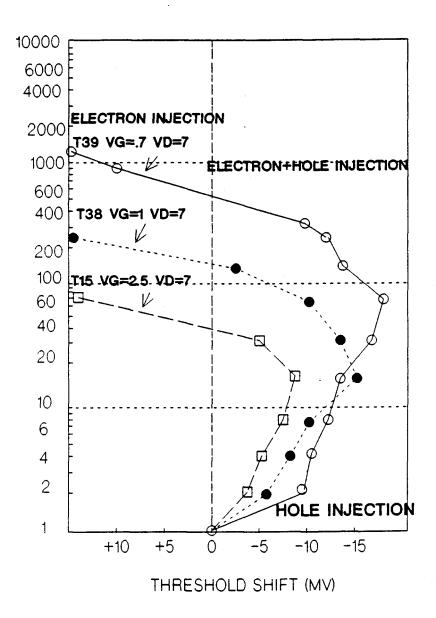

| 47.  | Hole injection process for device T15, T38, and T39                                     | ∍7 |

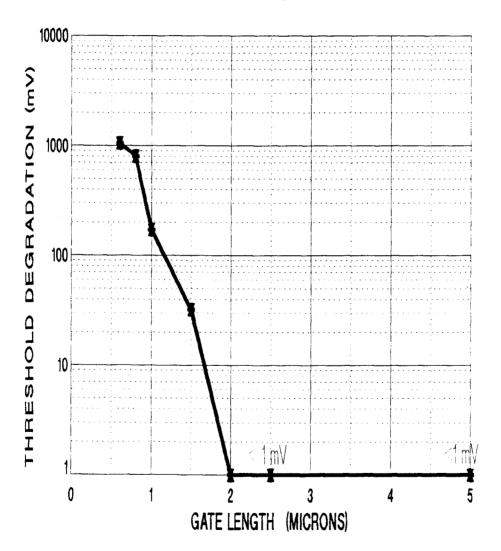

| 48.  | Threshold degradation vs gate length for devices from 5 micron to .6 micron             | €  |

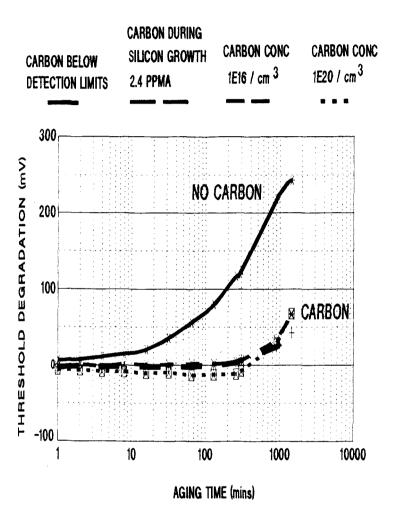

| 49.  | Threshold degradation vs aging time for devices with carbon and control device [75]     | 00 |

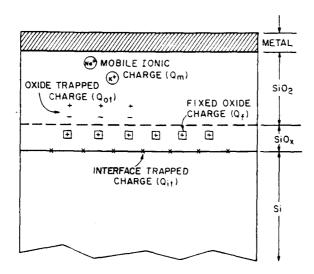

| 50.  | Interface charges associated with Si-SiO <sub>2</sub> [76] 10                           | )1 |

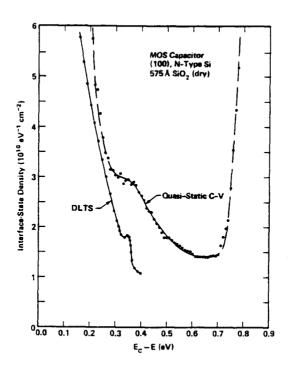

| 51.  | Quasi-Static CV and DLTS analysis of MOS capacitor [82]                                 | )4 |

| 52.  | Density distribution of interface states at Si/OP interface [28]                        | )6 |

# LIST OF TABLES

| TABLE |                                                                                   |    |

|-------|-----------------------------------------------------------------------------------|----|

| 1.    | A summary of wafers used for studying bulk defects by DLTS                        | 57 |

| 2.    | A summary of electrical activity of wafers with stacking faults used in this work | 78 |

CHARACTERIZATION OF OXYGEN AND CARBON EFFECTS IN SILICON MATERIAL AND MOSFET DEVICES

#### 1. INTRODUCTION

Silicon material and devices have continued to dominate the integrated circuit industry for the last three decades. Silicon is undoubtedly the most widely researched semiconductor. The projections of new investments on research and development on submicron CMOS and BICMOS processes and creation of SEMATECH show the commitment to this material for a long time in the future. Silicon has been through a history of continuing perfection. Improved perfection of silicon crystals will enhance device and circuit performance and reliability. There has been a constant interest in imperfections and impurities in the crystals and devices since early semiconductor diodes through today's ULSI circuits.

Resent submicron process developments have exposed the need for well understood materials characterization. Specifically the power supply scaling for submicron MOSFET devices from 5.0 volts to 3.3 or 2.2 volts due to hot carriers requires an in-depth defect characterization at the Si-SiO<sub>2</sub> interface. Since the subject of imperfections and defects tends to be a dynamic and rapidly changing, it is difficult to obtain a clear picture of the available data. One of the important considerations is the condition of each

individual industrial or university laboratory. Since the defects and imperfections are very closely related to the yield and cleanliness of the equipment set and the process, a unified and comprehensive theory is very difficult to obtain. For example, leakage currents of 4 pA to 500 uA per stacking fault have been reported, and for dislocations in silicon energy levels from 1.2 eV to 0.3 eV have been measured.

There are two main parts to this research work, the first part is related to the electrical characterization of oxygen induced microdefects and the other part is related to submicron device reliability. In both cases it has been found that the role of carbon is the determining factor.

## 1.1 ELECTRICAL CHARACTERIZATION ON OXYGEN INDUCED MICRODE-FECTS

Oxygen in silicon was discovered by C.S. Fuller at Bell labs in 1954. He reported the observation of oxygen related thermal donors which appear on annealing at 450 C. This discovery marked the beginning of what we now know to be process-induced defects. However many other process-induced defects have appeared since then, e.g., metal related defects, oxide related defects, new thermal donors which appear at 650 C and ion-implantation defects. There has been considerable progress on the microscopic identification of defects with the use of better tools such as SEM and TEM;

however the electrical characterization has been limited.

In this work CZ-grown wafers with oxygen concentration of about  $1.0 \times 10^{18}$  cm<sup>-3</sup> were heat treated to induce a large number of precipitates and stacking faults. Deep level transient spectroscopy (DLTS) and photocapacitance measurements indicated a correlation between the stacking fault size and trap density when the initial carbon level is below the measurement system's detection limit. An energy level of  $E_c$ - $E_t$ =.48ev has been detected with both DLTS and photocapacitance measurement systems. However, wafers with a small trace of carbon did not show any electrical activity, even in the presence of stacking faults.

#### 1.2 SUBMICRON N-CHANNEL MOSFET DEVICE RELIABILITY

Device problems due to hot carriers have been recognized as one of the major constraints in submicron device scaling. The injection of hot carriers generated by impact ionization in the high field region degrades the device characteristics.

Submicron n-channel transistors were subjected to hot carriers aging to investigate the properties of electrically active defects in  $SiO_2$  and at  $Si-SiO_2$  interface. These defect are important because hot carrier cause instabilities in threshold voltage and drive current. Devices with effective gate lengths of .8 micron were subjected to hot electron (high  $V_{\rm d}$  and medium  $V_{\rm g}$ ) and hot hole degradation condi-

tions (high  $V_{\tt a}$  and low  $V_{\tt g}$  ) and then to high temperature to investigate the detrapping as a function of temperature.

Carbon was implanted at 15 Kev with concentrations of 1E16 to 1E20 /cm³ and also was incorporated during growth of a silicon ingot at 2.4 PPMA. Carbon reduced the device's aging process. This suggests a new way to improve the Si-SiO₂ interface that with optimization might be able to provide of submicron devices with no hot carrier degradation.

#### 2. TECHNICAL BACKGROUND

In this chapter, the theoretical background of oxygen induced micordefects and device hot carriers effects are described. The first section will discuss n-type silicon heat treatments, microprecipitates, stacking fault generation and their electrical activity. The second section will be on n-channel MOSFET transistor hot carrier reliability effects.

#### 2.1 OXYGEN INDUCED MICRODEFECTS IN N-TYPE SILICON

The growth of high-purity silicon material and the fabrication of electronic devices and circuits uses long series of complicated chemical, physical and thermal Silicon is manufactured by refining silica sand through several carbon reduction steps. The result is known as polysilicon which is used for single crystal silicon production. Single crystal silicon is produced in the of long cylindrical ingots. These ingots are sliced and chemically and mechanically polished to produce aged-free surfaces. Throughout these processes the purity requirement are extremely high and normally in the part per billion range.

#### 2.1.1 OXYGEN IN SILICON

Oxygen is incorporated in silicon during the crystal growth at a concentration of 1018 atom/cm3. The source of oxygen is the reaction of molten silicon with its container ( quartz crucible). The oxygen concentration varies along a silicon ingot, from a high oxygen concentration at seed section to a low concentration at the tang section. This is due to crucible-melt interface contact area. Other factor such as crucible rotation velocity affect the dissolution rate of oxygen from crucible into the melt and can be used to make an ingot with relatively uniform oxygen concentration. The solubility of oxygen in silicon decreases exponentially with temperature [1]. This means at temperature higher than 300 C oxygen becomes mobile and reduces supersaturation via outdiffusion or formation of SiOx (cluster precipitates). Kimerling and Patel [2] have summarized the behavior of oxygen in silicon with heating in various temperature regimes as following.

- (1) 400-500 C: Electrically active, oxygen-related donors are formed, presumably due to oxygen aggregates. No direct evidence of such complexes exist.

- (2) 600-700 C: First visible evidence of oxygen precipitation, rodlike structure identified (small 20 A amorphous precipitates.

- (3) 800-1000 C: Platelike structures with {100} habit planes (presumably amorphous) in size ranges of 100-5000 A.

- (4) 1000 C: Platelike precipitate accompanied by punched out prismatic dislocation loops and extrinsic stacking faults with the associated colonies.

- (5) 1200 C: Large polyhedral precipitates identified as being amorphous and large extrinsic stacking faults.

In our work a two step heat treatment was used; a 750 C for the nucleation step and 1050 C for precipitate growth. The nucleation and growth of precipitates have been studied extensively since 1976 [3-8]. However, the nucleation kinetics is not yet well understood due to the variety of starting silicon specimens. In contrast, the growth kinetics of bulk stacking faults formed by oxygen precipitation has been modeled. A brief description of nucleation and growth mechanisms will be presented.

#### 2.1.2 OXYGEN PRECIPITATION

Oxygen interstitials are supersaturated during cooling of crystal growth. They tend to cluster and form large precipitates (a few 1000 A), but most of them form small embryos of about 10-40 A at sites of oxygen interstitials which is called HOMOGENEOUS NUCLEATION or at other sites (other impurities such as carbon) which is HETEROGENEOUS NUCLEATION. Formation of embryos requires a certain length of time, i.e., induction time (long at low temperature and short at high temperature). Therefore, during the cooling

process of the silicon ingot more embryos are formed at high temperature. The size and density of large and small precipitates depends on concentration of oxygen interstitials, number of heterogeneous nucleation sites, and the growth and cooling condition of the starting wafer.

#### 2.1.3 NUCLEATION MODEL

Homogenous nucleation can take place in silicon there is a large driving force, i.e., a departure from equilibrium, such as supersaturation of solute atoms The embryos formed in homogeneous nucleation must become large enough to exceed a certain critical radius order for precipitates to grow. This is based on the theory developed by Volmer et al [8] to explain the combination of surface energy and volume energy necessary for an object grow. As a particle grows due to precipitation, a new surface is created; hence energy must be added, and thus surface free energy is always positive. The volume free energy is negative, because as a precipitate grows it removes oxygen atoms from the silicon crystal and the overall material system becomes closer to equilibrium. Thus the two opposing free energies are added together and the free surface energy is initially larger than the free volume energy. As the radius of the particle grows in size, the sum of free energies goes through a maximum at a radius ro (called the critical radius). The condition of maximum free energy

corresponds to the state of minimum stability of the precipitate particle. Therefore, a particle with radius less than ro can lower its free energy by decreasing its size, and thus will tend to dissolve; a particle with radius larger than ro can decrease its overall free energy by growing [9].

Wada [8] used the Volmer theory and developed a general equation for the nucleation rate J as,

$$J = ZNW^* \exp\left(\frac{-\Delta G}{KT}\right) \exp\left(-\frac{t_t}{t}\right)$$

(1)

where Z is the Zeldovich non-equilibrium factor, W\* is the frequency factor, N the atomic nucleation site density,  $^{46}$  is the free energy for formation of the critical nucleus, and  $t_1$  the induction time. Figure 1 shows the nucleation rate of oxygen precipitates as a function temperature. Wada et al [8] also proposed the overall nucleation process as

$$J_{total} = J_{homo} + J_{hetero} \tag{2}$$

Figure 1) Nucleation rate of precipitates vs temperature after Wada et al [8].

#### 2.1.4 GROWTH OF BULK STACKING FAULTS (BSF)

The formation of stacking faults involves accumulation of excess planes of atoms (extrinsic) or reduction planes of atoms (intrinsic). Stacking faults in silicon were initially found to be extrinsic in nature and were bounded by partial dislocation loops based on TEM studies [10]. Stacking faults can form in IC processes such epitaxy growth , ion implantation, silicon oxidation from oxygen micro-precipitate growth. The source of these extra atoms includes supersaturated self-interstitials self-interstitials created during the growth of oxygen precipitates (This is referred to as the self-interstitial model). Recently, there have been some experimental evidence [11] that suggests both self-interstitials in supersaturation and vacancies in undersaturation coexist during oxidation. A model based on vacancies in undersaturation ( referred to as the vacancy model) has been proposed for bulk stacking fault growth [12]. J. Patel [13] proposed a model for the formation of stacking faults in heat treated con containing oxygen (Fig. 2). During the nucleation of precipitate (at 700 C), which is presumed to be SiO2 volume change associated with the growth of the precipitate which is  $V_{sio2} / V_{si} = 2$ ; thus a dislocation is then occurs generated around the precipitate. During subsequent heat treatments the particle grows by the diffusion of oxygen from the surrounding silicon matrix to its surface. The

large volume change associated with the growth of the precipitate is accommodated by the displacement of silicon atoms. These excess silicon atoms can either diffuse away and form a Frank loop or can cause the growth of bulk stacking faults.

Figure 2) Schematic of the stages in the development of bulk staking faults after Patel [13]

Mahajan et al [4] propose a slightly different role for oxygen in their BSF growth model which is shown in Figure 3. It is assumed that the initial stage in the formation of a stacking fault is the formation of silicon-oxygen clusters on [111] planes. When the oxygen atoms occupy position between pairs of silicon atoms along <111> directions, a compression of the adjoining silicon matrix along <111> will

result. For the growth of the Si-O clusters silicon interstitials must be emitted into the silicon matrix. When these silicon interstitials reach a certain critical level, they can condense into Frank loops. Further growth of BSF occurs by repeating the Si-O formation process.

Figure 3) Schematic of the formation of an extrinsic stacking fault after Mahajan et al [4].

#### 2.2 CARBON IN SILICON

Carbon is introduced into silicon as early as polysilicon manufacturing during which the initial step the reduction of silicon by reaction of quartz with carbon [14]. Carbon also can be introduced into silicon during the Czochralski process from the crystal growth chamber The concentration range of the carbon atoms can below measurement detection limits ( for FTIR this is  $10^{15}/\text{cm}^3$ ) to  $2.5 \times 10^{17}/\text{cm}^3$ . The role of carbon on precipitation and its electrical activity in silicon has not been well understood. Seigo Kishino [5] argues that in the heterogeneous nucleation model the carbon atoms are the cleation sites. However, Kung et al [16] did not find correlation between a reduction in the carbon concentration and oxygen precipitation. Hahn et al [17] recently have shown that oxide precipitates (OP's) increase with increasing substitutional carbon concentration. They also found in samples with high carbon concentration the stress at Si/SiO2 is lower through formation of SiC. The most interesting observation has been made by Bailey et al [18] who found that carbon can be gettered to damage sites such as dislocations, stacking faults and wafer surfaces. Figure 4 shows typical stacking faults with large dislocations and precipitates which are observed at the corners of the stacking

faults. Scanning Auger data also showed that the precipitates have a high concentration of carbon instead of the expected heavy metals.

| Stacking      | Sputter     | Atomic       | Relative | Percent      |

|---------------|-------------|--------------|----------|--------------|

| Fault 1       | Time (Min.) | C            | O        | Si           |

| Corner-1      | 1.0<br>5.0  | 30.7<br>13.9 | 4.0      | 65.1<br>84.4 |

| Corner-2      | 1.0<br>5.0  | 24.9<br>25.7 | 4.1      | 70.8<br>72.0 |

| Corner-3      | 1.0         | 31.3         | 6.4      | 62.2         |

|               | 5.0         | 43.0         | 2.7      | 54.1         |

| Corner-4      | 1.0         | 37.4         | 9.0      | 53.5         |

|               | 5.0         | 38.8         | 1.7      | 59.3         |

| Clear Area    | 1.0         | 2.2          | 2.1      | 95.6         |

| Next To Fault | 5.0         | 0.0          | 1.9      | 98.0         |

Figure 4) Scanning Auger data showing a high concentration of carbon at stacking fault number 1 corners and no carbon in the clear area next to the faults after Bailey [18].

#### 2.3 ELECTRICAL ACTIVITY OF MICRODEFECTS IN SILICON

The problem of electrical activity of silicon defects in general and oxygen induced microprecipitates and stacking in particular has been a complex and often confusing No one better than Sokrates T. Pantelides has plained this problem in his recently edited published book [19], He wrote " With advent of the junction techniques 1970's ( deep level transient spectroscopy ) quit often the results of different experiments or different researchers were in disagreement, but the origins of the discrepancies were not usually investigated. Typically, measured cross sections would be fit to a simple model to locate the energy levels in silicon bandgap. This type of work led to a proliferation of energy levels quoted in the literature for given impurity. There was little effort spent on verifying whether the energy level thus reported indeed correspond to simple impurities or complexes. This confusion led to the often-mention quote: the deeper the level, the shallower the understanding."

In this work, an energy level for stacking faults has been determined. However, the sole purpose is not the energy level, but rather a comparative study between samples with different concentrations of oxygen and carbon impurities. In the next sections, a review of current data about the

electrical activity of dislocations, silicon after deformation, oxygen induced precipitation, and stacking faults will be presented.

#### 2.3.1 ELECTRICAL ACTIVITY OF DISLOCATIONS

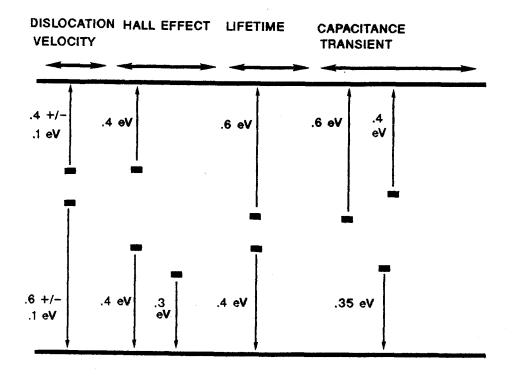

A literature search for electrical activity of dislocations in silicon revealed the proliferation of energy levels reported for this defect. Dislocations have been extensively studied for their effect on transport properties such mobility, lifetime, conductivity and their energy levels in silicon crystals. Glazer et al [20] found an acceptor level below conduction band (Et-Ec= .52eV) for dislocations silicon using lifetime measurements. Petal et al [21] found  $E_{t}$ - $E_{v}$ = 1.2 +/- .2 eV using dislocation velocity measurement in 1968. Erofeev [22] found Et=.58 eV with Patel's measurement method [21]. Jones [23] based on theoretical methods found  $E_t=.8$  eV. Grazhuis [24] reported a  $E_t=.43$ +/- .03 eV using the Hall Effect. Patel [25] again in 1977 reported a Et=.63 eV using DLTS. Finally Weber et al [26] found a level at .68 eV with the electron paramagnetic resonance (EPR) measurement method. There were other reported energy levels for dislocations in silicon which vary from one laboratory to another. A schematic of the defect energy levels due to dislocations by a variety of different techniques is shown in Figure 5.

Figure 5) Schematic comparison of dislocation levels in silicon by a variety of experimental techniques Kimerling [2]

## 2.3.2 ELECTRICAL ACTIVITY OF DEFECTS IN SILICON AFTER DE-FORMATION

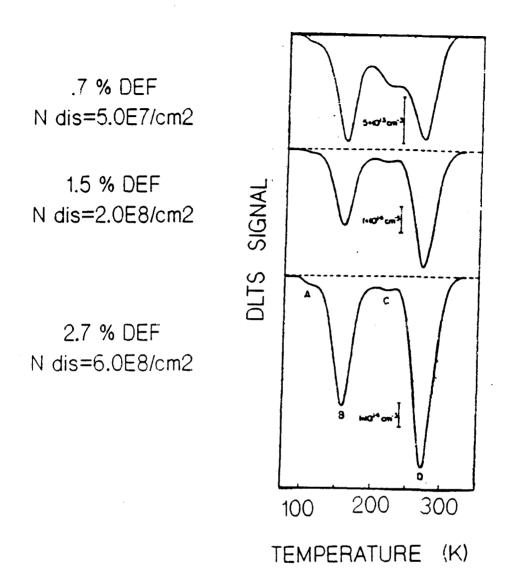

Deep level defects are generated after silicon samples are plastically deformed. In deformed samples the dislocation density can reach 10<sup>7</sup>-10<sup>9</sup> per cm<sup>2</sup>. P. Omling et al [27] used deep level transient spectroscopy (DLTS) and electron-paramagnetic resonance (EPR) to investigate induced

deep level defects after plastically deforming n-type silicon samples at 650 C. Figure 6 shows the DLTS spectra for four traps, labeled A, B, C, and D. With different deformations the B and D traps are clearly resolved, however both A and C are more complicated and not easily resolved. Our results (chapter IV) also show a dominant level very similar to level D for samples with oxygen induced stacking faults and low carbon concentrations. Omling's EPR results show DLTS line D is dominant in strongly deformed silicon and shows characteristics which are comparable to Si-K1/K2. Photo-EPR shows a midgap level of this center (D level) and from a comparison of the DLTS lines with EPR centers, Omling suggested the D line is related to "dangling bond" centers.

Figure 6) DLTS spectra for different deformations in n-type silicon after Omling [27]

### 2.3.3 ELECTRICAL ACTIVITY OF OXYGEN PRECIPITATES (OP'S)

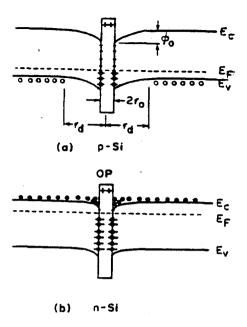

J.M. Hwang and D.K. Schroder [28] proposed a model for the electrical activity of oxygen precipitates (OP) based on a Si and SiO<sub>2</sub> interface model. They observed that lifetime degradation is mainly due to OP's and that recombination at

OP's takes place through the Si/OP interface. They also observed that lifetime degradation is more severe in p-type silicon than n-type for similar densities and sizes of OP's. A model was presented based on a band bending around OP's which is caused by positive fixed charges similar to the Si/SiO2 interface. Figure 7 illustrates that in p-type silicon samples a depletion region is formed around OP's providing a large collection volume for minority carriers, i.e. In n-type the positive charge causes an accumulation layer which could act as reflecting barrier to minority carriers or holes. M. Miyagi et al [29] also showed the effect of OP's on minority carrier lifetimes. They found that homogenous OP's decreased the lifetime when length is greater than 100 A. Miyagi indicated that heterogeneous nucleated OP's are about 1000 A in size and normally cause the lifetime degradation. Figure 8 trates the lifetime as function of OP density and annealing time.

Figure 7) Schematic band diagrams with band bending due to positive fixed charges in OP's after Hwang and Schroder [28]

Figure 8) Lifetime and OP density as a function of annealing at 850 C after Miyagi [29]

# 2.3.4 ELECTRICAL ACTIVITY OF STACKING FAULTS (SF)

The perfect silicon lattice can be described as a sequence of planes such as AA'BB'CC'AA'BB'CC'.....(stacked in {111} directions).

In the case of intrinsic stacking faults a pair of planes, say BB' is missing then the lattice sequence becomes AA' CC'AA'BB'CC'..... For extrinsic stacking faults an extra plane, say BB'is inserted between CC' and AA' such as AA'BB'CC'BB'AA'BB'CC'.....

Weigal et al [30] concluded that there is a only a minor charge distribution around a stacking fault. L.C. Kimerling [31] reported an energy level of Ec-Et=.1 ev for undecorated extrinsic faults using charge collection scanning electron microscopy. Ogden et al [32] compared data in the literature for leakage current per stacking fault. The calculations were from electrical measurements and stacking faults counts after preferential etching. Ogden found values ranging from 4 pA to 500 uA per stacking fault which is eight order of magnitudes variation from one report to another one. A major part of this wide range of leakage current has been attributed to decorated stacking faults with (primarily transition metals impurities such as Ni, Co., Pd, Cu, and Fe). Seidel et al [33] found that a clean stacking fault ( no decoration) can contribute only order of 0.1 to 10 pA to the reverse current of a The discrepancies in the electrical activities of stacking

faults which are similar to those of dislocations could be due to different types of stacking faults, i.e., ion implantation stacking faults, oxidation induced stacking faults or oxygen precipitation induced stacking faults. Some of the differences also might be due to processing conditions and wafer thermal history.

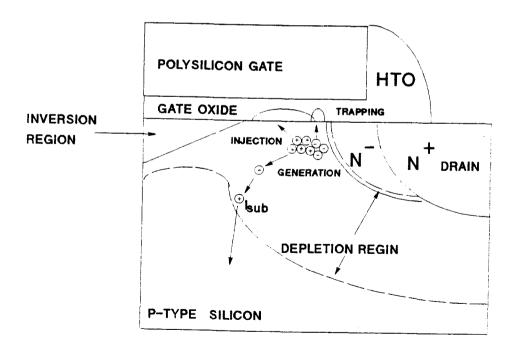

#### 2.4 N-CHANNEL HOT CARRIER RELIABILITY

MOSFET devices are being continuously scaled down in size while the power supply remains fixed at 5.0 volts (however for devices of gate length below half a micron it has to be reduced to 3.3 or less with current material limitations); as a result the maximum electric field in the channel increases. If the electric field in the channel becomes too large, hot carriers can be generated which could cause device degradation and reliability problems [34-35]. Figure 9 illustrates the three main hot carrier effects: hot carrier generation, injection and trapping.

Figure 9) Hot carrier effects in n-channel devices

Since our work is focused on the material aspects of hot carrier effects, it is the trapping and detrapping of electrons and holes that will make up the major part of this section. However, hot carrier generation and injection will be discussed briefly.

#### 2.4.1 Hot CARRIER GENERATION

In MOS transistor's the gate and substrate currents are referred to anomalous currents which are measured at side and at gate contacts. These current are largest short channel devices where the channel lengths, doping concentrations and junction depths have all been scaled. parameter which is not usually scaled is the drain voltage which causes a high field of about 105 to 106 V/cm near This high field which is parallel to the channel, is drain. the result of the scaling the channel lengths and doping concentration without scaling the drain voltage. Carriers which pass through this high electric field region are accelerated to the point of impact ionization which can result in formation of electron-hole pairs. These electron-hole pairs in turn can be accelerated by the electric field if this multiplication continues without bound, avalanche breakdown results.

#### IMPACT IONIZATION

Impact ionization imposes an upper limit on the reverse bias junction breakdown voltage. Zener [36] explained the high field breakdown mechanism, i.e. above 10° V/cm. McKay et al [37] have provided an explanation for electrical breakdown at lower fields by showing that carriers injected into depletion regions can create more carriers by impact ionization. If a is the ionization rate per unit length can be written as

$$\frac{dn_1}{dx} = (n_0 + n_1)\alpha = n_\alpha \alpha \tag{3}$$

where  $n_0$  is the number of injected electron,  $n_1$  is the number of electron produced between 0 and x by impact ionization. This expression can be integrated from x=0 where  $n_1-n_2$  to x=0 where  $n_1-n_2-n_3$ . M is called the multipilication factor and for carriers created by impact ionization an expression is given as

$$\int_{0}^{d} (\alpha) dx = \int_{n_{0}}^{n_{0}M} \left( \frac{dn_{1}}{n_{\alpha}} \right) = \ln M = 1 - \frac{1}{M}$$

(4)

The quantity 1- 1/M is the number of carriers created by impact ionization divided by the total number of carriers. For avalanche breakdown this ratio is equal one. The problem with the above impact ionization treatment is that it assumes the ionization rate for holes is the same as electron. For silicon the impact ionization for holes is an order of magnitude less than the rate for electrons. Experimentally,

the ionization rates for both electrons and holes vary with E-field as

$$\alpha = Cexp(-b/E) \tag{5}$$

where C and b are constant and E is the electric field.

#### 2.4.2 HOT CARRIER INJECTION

The second major mechanism of device degradation is the injection of hot carriers into the interface or dielectric SiO<sub>2</sub>. Ning et al [38] have studied the emission of hot carriers and mainly hot electrons from silicon into SiO<sub>2</sub>, where they had to make many simplifying assumptions, for example an energy independent mean free path and a parabolic band structure. At energies of 3.0 eV (hot carrier energy) the band structure is highly nonparabolic. Karl Hess [39] has taken a more realistic band structure and with a Monte Carlo simulation has shown a barrier lowering effect for hot electron emission. Note that both Ning and Hess have used the "lucky electron model" for their hot electron emission process. Shockley developed this model for explanation of avalanche multiplication in p-n junctions [40].

#### LUCKY ELECTRON MODEL

The model used for p-n junctions contained three adjustable parameters; threshold energy for pair production by impact ionization  $E_{\text{\tiny L}}$ , mean free path for electron-phonon

scattering  $L_{\rm P}$  and the ratio  $r=L_{\rm I}/L_{\rm P}$  where  $L_{\rm I}$  is the mean free path for scattering due to impact ionization for carriers with energy greater than  $E_{\rm I}$ . The ratio r is the number of phonons emitted between each ionizing collision. The probability of a carrier travelling a distance  $L_{\rm P}(E-E_{\rm I})/E_{\rm P}$  without an ionizing collision is

$$P_a = A \exp \frac{-L_p(E - E_I)}{L_I E_P} \tag{6}$$

where A is a normalization constant. Therefore for a carrier with energy greater than  $E_{\scriptscriptstyle \rm T}$  the probability of an ionizing collision is

$$P_b = 1 - P_a \tag{7}$$

This model can be used to account for the exp(-b/E) dependence of the ionization rate described previously.

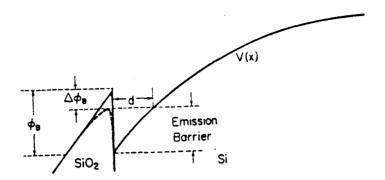

Ning used the original lucky electron model to describe carrier injection at the Si-SiO<sub>2</sub> interface. At the Si-SiO<sub>2</sub> interface the critical energy is the barrier potential 3.1 eV for electrons and 3.7 eV for holes. Figure 10 illustrates the concept of the lucky electron as proposed by Ning. Electrons located a distance d away form the interface and having a potential energy equal to the barrier will overcome the barrier and go into silicon dioxide if they encounter no scattering events.

Figure 10 ) Band diagram for lucky electron model with barrier lowering after Ning [38]

Equation (6) can be written as

$$P = A \exp\left(-\frac{d}{\lambda}\right) \tag{8}$$

where wis mean free path and A is the normalization constant. The barrier lowering according to Ning is due to the Schottky effect and tunneling which is approximated in the following form

$$\phi_B = 3.1 \, \text{eV} - b E_{ox}^{1/2} - a E_{ox}^{2/3} \tag{9}$$

where 3.1 eV is the Si-SiO<sub>2</sub> interface barrier,  $E_{ox}$  is the oxide field,  $aE_{ox}$  comes from the Schottky lowering and  $bE_{ox}$  accounts for tunneling.

#### 2.4.3 HOT CARRIER TRAPPING

The third part of the hot carrier degradation is the trapping which is the major focus of the device part of this

work. Most of original works have extensively been trated on hot electron trapping in the silicon dioxide. recent experimental results suggest that hole trapping cedes electron trapping and can be the main degradation mechanism. Our work examines device aging (trapping) subsequent temperature annealing (detrapping) with device DC measurements. From trapping and detrapping, it is possible to calculated the trap energy levels. Electrons and holes when injected into the interface or SiO2 can be captured by sites which are called traps. Electrons can move rapidly with a mobility of 20-40 cm<sup>2</sup>/v-sec in SiO<sub>2</sub> and move toward the positively biased gate contact [41]. Holes are mobile enough to drift significant distance in SiO2, with mobility determined from transit time measurements that in the range  $\langle 2x10^{-5} \text{ cm}^2/\text{v-sec} [42-43]$ . Several have been proposed as an explanation for device aging. ever, the model proposed by R. Fair et al [44] to the author's belief is the one that could best explain most of the processes that are occurring at the Si-SiO2. Fair's model proposes that the instability is caused by the trapping of hot-holes emitted into the Si-SiO2 interface or gate oxide.

#### FAIR AND SUN MODEL

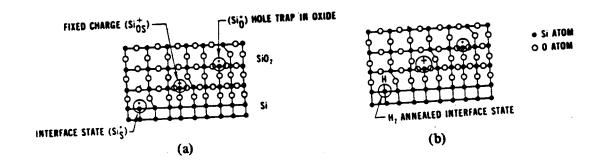

Fair used the Svensson's trivalent silicon model [45] to explain the the hot hole trapping process. Figure 11 illustrates the three forms of trivalent silicon, i.e., are

surface silicon Sis, bonded to three other silicon, Sisbonded to three oxygen and oxide trivalent silicon Siss close to the surface.

Fig.11 (a) The Si-SiO<sub>2</sub> interface defects after Svensson [12]. (b) H<sub>2</sub> anneal after Fair [44]

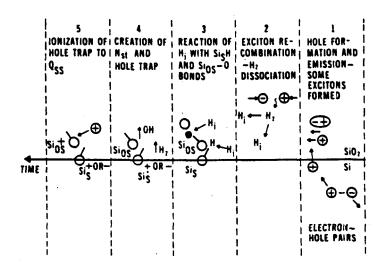

Sevensson postulated that  $Si_s$  is a surface trap or interface state,  $Si_o$  is a deep hole trap, and  $Si_{ox}$  is a deep hole trap which is easily ionized and is assumed to be the fixed surface charge  $Q_{ss}$ . Figure 12 shows the five step process of device degradation.

Figure 12 ) Model of interface and fixed charge formation after Fair [44]

The Fair model starts with hole formation in Si due to impact ionization and then proposes that the electric field normal to the Si-SiO<sub>2</sub> interface E<sub>normal</sub> being maximum at the drain would make the hole injection likely close to drain. In most CMOS processes the final step is a H<sub>2</sub> or N<sub>2</sub> anneal at 400 C for radiation damage and interface trap density reduction through the reaction of H<sub>1</sub>( interstitial hydrogen) and Si<sub>s</sub> to form Si<sub>s</sub>H. The production of interstitial hydrogen could be either from Si-H or H-H bond breakage. The source of breakage energy could come from the recombination of holes and electrons at hydrogen-related centers in the SiO<sub>2</sub>. Energy release from recombination events is through

phonon-generation processes [46]. The following reaction shows the H-H dissociation

$$h^{+} + e^{-} + H_{2} ---> 2H_{i}$$

In the presence of  $H_i$ , interface states  $Si_s$  can be created  $Si_sH + H_i$  --->  $Si_s + H_2$

Interstitial hydrogen can also create a hole trap  $Si_{os}$

$$Si_{os}$$

-O-Si<sub>o</sub> + H<sub>i</sub> --->  $Si_{os}$  +  $Si_{o}$ OH

The final reaction is the ionization of Sios with another hole

$$Si_{os} + h^+ \longrightarrow Si_{os}$$

The morphology and chemical structure of Si-SiO<sub>2</sub> interface defects have been under extensive investigation [47-49] because of their effects on MOSFET devices, we will present a more detailed picture of Si-SiO<sub>2</sub> interface in chapter 7 of this work.

## 3. EXPERIMENTAL TECHNIQUES

In the semiconductor materials a variety of different techniques are used to investigate the defects in the forbidden gap. For example the carrier population can changed thermally, optically and electrically and the resulting effects can be used in variety of ways to characterize material and device defects. Beginning at 1970 a new technique based on semiconductor junctions was developed by Sah et al [50]. In the junction technique the position of Fermi level relative to the band edges is altered by applied bias. For example in the reverse biased junction. the junction is depleted of mobile carrier. This condition can be treated using linearized rate equations. turbation to the junction will decay exponentially with time and can be monitored with either capacitance or current and is a function of the charge-state of the defects in junction. One of the most widely used versions of junction method is deep level transient spectroscopy (DLTS) introduced by Lang [51] in 1974.

In this chapter, the measurement systems used for characterization of oxygen induced microdefects and hot carriers degradation are described. The first section is devoted to deep level transient spectroscopy and a brief description of both capacitance and current DLTS will be presented. In the following sections photocapacitance measurement, fast fourier infrared spectrophtometry (FTIR), and MOSFET device measurement and aging systems will be presented.

# 3.1 DEEP LEVEL TRANSIENT SPECTROSCOPY (DLTS)

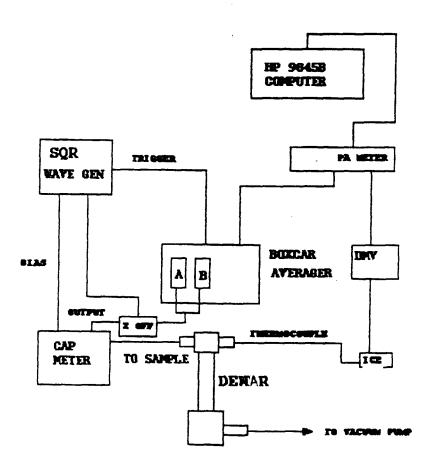

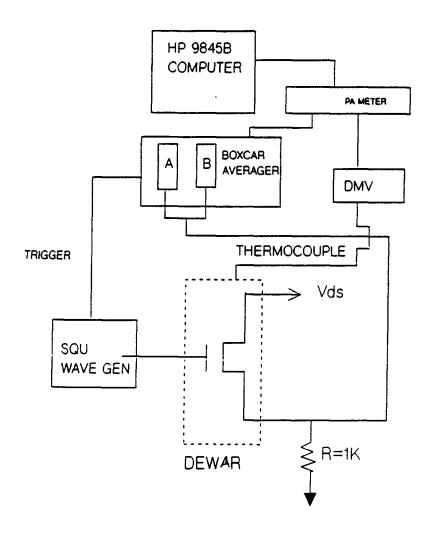

Deep level transient spectroscopy is an efficient method of evaluating deep level impurities in semiconductors. A Schottky diode or a p-n diode can be used as junction. DLTS provides a rapid spectroscopic analysis method, a measurement taking less than an hour can give at least some information about all the deep levels in a sample. During a measurement an average is formed over a large number of transients and this can reduce the noise. weak points of DLTS are its inability to determine accurately the temperature of DLTS peaks [52], and the energy of nonexponential transients [53-54]. Figure 13 DLTS system. It consists of a sensitive capacitance meter ( Boonton 72B with a response time of ~1 ms), a pulse tor, and a dual-gated signal integrator which takes difference between time t<sub>1</sub> and time t<sub>2</sub> and then averages this by means of a boxcar averager. An X-Y recorder or HP9845B computer is used for plotting the boxcar averaged output versus temperature. The temperature was varied between 100K and 420K. Most of measurements were done in 200K to 350K range.

Figure 13) The OSU capacitance DLTS system diagram with detectability limit of 1.0E11 /  ${\rm cm}^3$

#### 3.1.1 TRANSIENT ANALYSIS

When a defect is present in a semiconductor it normally gives rise to an energy level in the band gap. energy level is close to edge of the valence band or the conduction band (SHALLOW level), it can be ionized and termines the conductivity of the semiconductor. Levels sitioned more centrally are DEEP levels. These levels could be due to crystal lattice defects or impurity atoms. levels can act as a trap centers causing either electron or hole to bound to them. The emission of charge from the trap will occur only after a finite length of time te, the time constant of a trap. Emission rate of electrons  $e_n$  is function of temperature of the material, and activation energy AF. Here the analysis is for electrons, there is analogous emission and capture of holes. The emission rate can be expressed as

$$e_n = \frac{\sigma_n < \nu_n > N_c}{g} \exp\left(\frac{-\Delta E}{KT}\right)$$

(10)

where  $\sigma$ , is electron capture cross section,  $\nu$ , is thermal velocity of electron, and  $N_{\rm e}$  is the effective density of states at the conduction band. The activation energy in equation (10) is a free energy, however the thermodynamic quantity derived from the temperature dependence of the emission rate is an enthalpy [52]. The enthalpy and the free energy are equal only at T=0. Therefore, the activation energy obtained from an Arrhenius plot is the free

energy obtained by a linear extrapolation to T=0 of the temperature dependent free energy at the measurement temperature. However, this is not always the same as the free energy at the measurement temperature. The inverse process of emission is capture and associated capture rate C<sub>n</sub>. An expression for the time rate of change of electrons at a trap can be written using emission and capture rates

$$\frac{dn}{dt} = e_n n_T - C_n n p_T \tag{11}$$

The rate of change for holes is

$$\frac{dp}{dt} = e_p p_T - C_p p n_T \tag{12}$$

where  $n_{\scriptscriptstyle \rm T}$  and  $P_{\scriptscriptstyle \rm T}$  are the trap concentrations of electrons and holes respectively, and their sum equals  $N_{\scriptscriptstyle \rm T}$ . n an p are untrapped electron and hole concentrations respectively. The rate equation for trapped electrons is,

$$\frac{dn_T}{dt} = (C_n n + e_p)(N_T - n_T) - (C_p p + e_n)n_T$$

(13)

For an electron trap where we have only emission (  $C_n$ ,  $e_p$ ,  $C_p \sim 0$ ) equation (13) can be written as

$$\frac{dn_T}{dt} = -e_n n_T \tag{14}$$

where the solution to this differential equation (14) is

$$n_T(t) = n_T(0)e^{\frac{-t}{t_c}}$$

(15)

#### 3.1.2 CAPACITANCE DLTS

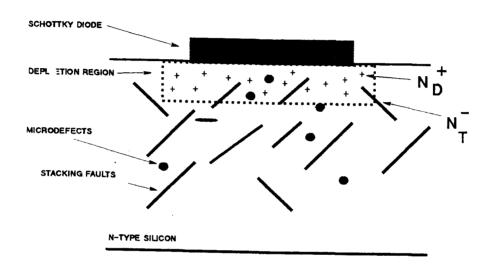

For an asymmetric p-n junction the space charge region (scr) is essentially on the side with lowest doping and for a Schottky diode is all in semiconductor. Figure 14 shows a Schottky diode with stacking faults and micorprecipitates.

Figure 14) N-type silicon with Schottky diode

The capacitance for a plate capacitor is

$$C = \frac{\epsilon \epsilon_0 A}{W} \tag{16}$$

where  $\epsilon\epsilon$ , is the dielectric constant, A is the area of the capacitor, and W is space charge width. The capacitance expression for the diode Figure 14 is

$$C = \sqrt{\frac{q \epsilon \epsilon_0 (N_D - n_T)}{2(V + V_{bi})}} \sim = C_0 \left(1 - \frac{n_T}{2N_D}\right)$$

(17)

From equation 15 and 17 an expression for the capacitance transient is given by:

$$C = C_0 \left( 1 - \frac{n_T}{2N_D} \right) = C_0 \left( 1 - \frac{n_T(0)e^{\frac{-t}{t_c}}}{2N_D} \right)$$

(18)

From Equation 18 the following equation follows at t=0.

$$\Delta C = \frac{N_T}{2N_D} C_0 \tag{19}$$

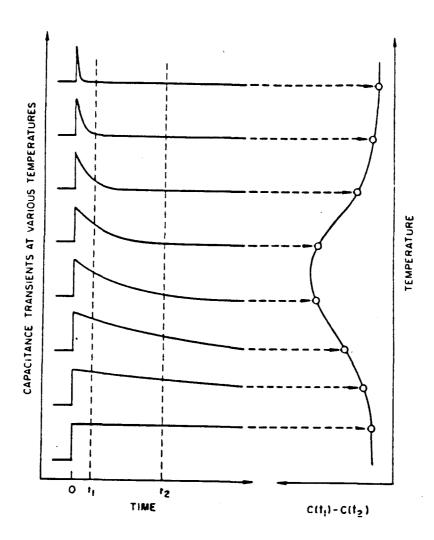

# 3.1.3 TIME FILTERING TECHNIQUE OF DLTS

One way of determining the time constant of an exponential transient is to record the full transient and to plot log AC versus time and calculate the slope of a line which results (this method will be used in the next section for the photocapacitance technique). This technique is very time consuming and since it uses only one transient, it does not have the noise reduction capability. DLTS uses a sampling technique to determine the time constant of an exponential transient. One sample is taken after a time t<sub>1</sub> and another after a time t<sub>2</sub>, their difference can be plotted versus temperature. Figure 15 after Lang [52] shows that at low and high temperature the difference between t<sub>1</sub> and t<sub>2</sub> essentially goes to zero. The difference S(T) is given by:

$$S(T) = \Delta C(t_1) - \Delta C(t_2) = \Delta C(0) \left( \exp\left(\frac{-t_1}{t_c}\right) - \exp\left(\frac{t_2}{t_c}\right) \right)$$

(20)

S(T) has a maximum for certain time constant  $t_{\text{max}}$ . the relation between the time constant  $t_{\text{max}}$  and  $t_1$  and  $t_2$  is determined by differentiating S(T) with respect to  $t_c$  and setting the result equal to zero which results in the following expression

$$t_{\text{max}} = \frac{\left(t_2 - t_1\right)}{\ln\left(\frac{t_2}{t_1}\right)} \tag{21}$$

A peak will occur when t1 and t2 satisfy equation (20), at some particular temperature. The peak height is independent of the absolute value of  $t_1$  and  $t_2$ , only the ratio between them is important. For all measurements in chapter Four we selected  $t_2/t_1=4$  which is a reasonable choice for high sensitivity and a range of different time windows. The capacitance transient is always positive for a minority carrier trap and negative for majority carrier trap [52].

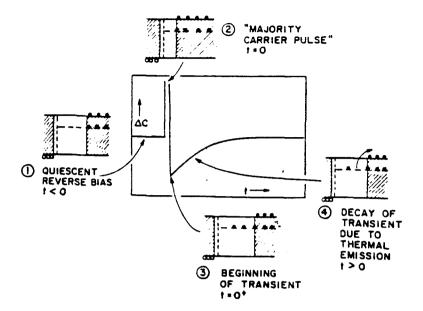

thermal emission from a majority carrier trap in a p+n diode. At t<0, the junction is under reverse bias to establish space charge conditions in which states in the space charge region (scr) are empty because no mobile carriers are available for capture. At t=0, a biased pulse toward zero momentarily collapses the scr and making the majority carriers available for capture, the depletion region goes to zero and capacitance is large. At t=0+, the pulse is turned off and reverse bias restablished the junction capacitance is reduced because the compensating majority carrier charge has been trapped in the space charge region. At t>0 the capaci-

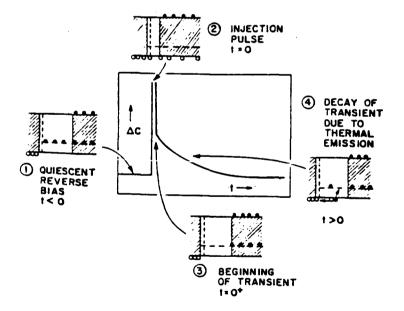

tance goes back to its quiescent values due to thermal emission of trapped electrons. Figure 16b is an analogous process for thermal emission from a minority carrier trap.

Figure 15) Implementation of time filtering by means of a double-boxcar. The output correspond to average difference at sampling time  $t_1$  and  $t_2$  after [52]

Figure 16a) The capacitance transient caused by thermal emission from a majority carrier trap.

Figure 16b ) The capacitance transient caused by thermal emission from a minority carrier trap after Lang [52].

#### 3.2 CURRENT DLTS

The capacitance DLTS technique is limited in the case of small FET devices which have only very small capacitances. Instead, current DLTS is used for characterizing MOS. devices [55-60]. An schematic diagram of current DLTS can be seen in Figure 17. As shown, a pulse V<sub>G</sub> is applied to the gate of a transistor which repeatedly turns the transistor "on" and "off". During the off state any trap at the interface of Si-SiO<sub>2</sub> and channel of MOSFET device will be filled, and during the on state the filled traps present in the resulting depletion layer will emit the captured carriers. Chen et al [57] have derived an expression for the resulting drain current from the emission rate and concentration of bulk traps. The expression is for linear region of the transistor operation where Vds is small, and is given as

$$I_{ds} = \mu C_0 \frac{W}{L} \left( V_{gs} - \left\{ V_{FB} + 2\phi_F + \frac{Q_B}{C_0} \left( 1 - \frac{N_T}{2N_A} \exp\left(\frac{-t}{\tau}\right) \right) \right\} - \frac{V_{ds}}{2} \right) V_{ds}$$

(22)

$N_{\mathrm{T}}$  represents the trap concentration. Using the rate window concept, the same procedures are applied to the current transient measurements as were presented for capacitance deep level transient spectroscopy to obtain the position of the traps in the bandgap and the trap concentration.

Figure 17) The current deep level transient spectroscopy system diagram.

#### 3.3 PHOTOCAPACITANCE MEASUREMENT

Photocapacitance transient measurements have been used here to further investigate the oxygen induced microdefects. The measurements were made on the same samples used for DLTS measurements to ensure a correlation of the observations. Photocapacitance is related to DLTS and TSCAP (Thermally simulated capacitance). All these systems are parametric measurements, i.e., the effect of the filling and emptying of traps is monitored by the change in junction capacitance. Photon stimulated emission processes have been summarized by White [61] and Bois et al [62] where photocapacitance is a slowly varying function of the incident photon energy, and fitting parameters are needed to determine the threshold energy and optical cross section. The rate equation (13) can be modified to include the optical emission rate.

$$\frac{dn_T}{dt} = (C_n n + e_p + e_p^o)(N_T - n_T) - (C_p p + e_n + e_n^o)n_T$$

(23)

Where

$$e_p^o = \sigma_p^o S \tag{24}$$

$$e_n^\circ = \sigma_n^\circ S \tag{25}$$

and of are the optical electron and hole emission rates, of and of are electron and hole capture rates respectively, and S is the optical flux in photons/cm² sec. The optical properties of a given defect can be defined by of and of, which are functions of photon energy. In n-type samples, of the

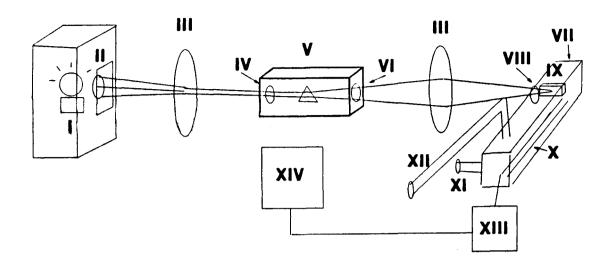

the optical absorption cross section. To obtain the cross section, samples were maintained at steady low temperature of 120 K with an expander DE-2 and a Helium pump. A monochromatic light (tungsten halide source through a mochromator) is focussed on the sample with a wavelength photon energy is then slowly such that hv < OE . The creased. When the photon energy comes close to being equal to the defect energy level, trapped electrons are promoted to the conduction band by the photoelectric effect, will produce a change in the junction capacitance. The photocapacitance method is complicated by the fact that the photoionization threshold the capture cross-section a function of photon energy. Furthermore, the optical cross sections are usually very small and the light sources not very intense. The photocapacitance method overall very slow and calculation of energy levels are very time consuming, i.e., the time constant of a photocapacitance exponential transient is obtained by plotting log &C time and calculate the slope of the line which results one wavelength; this will be one point on the energy versus the cross-section plot. Other points are obtained by repeating the time constant calculation process. photon energy versus cross-section plot, the optical ionization energy is obtained. Figure 18 shows the photocapacitance system diagram.

- I. Tungsten halide source

- II. Silicon/Germanium filter

- III. Convex lens

- IV. Input grating of the monochromater

- V. Jarrell-Ash Monochrometer

- VI. Output Grating of the monochromater

- VII. Expander DE-2

- VIII. Quartz window

- IX. Schottky diode

- X. Temperature regulator

- XI. Cryogenic vacuum pump

- XII. Helium pump

- XIII. HP 4280A Capacitance measurement system

- XIV. HP9836 Computer

Figure 18 ) The Photocapacitance system diagram.

# 3.4 FAST FOURIER INFRARED SPECTROPHOTOMETRY (FTIR)

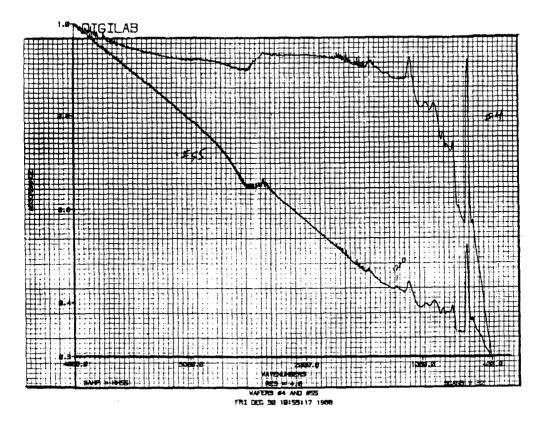

FTIR measurements were used before heat treatment measure the oxygen and carbon concentration and after treatment to measure the reduction in these two concentra-The infrared region starts at a wavelength 0.7 Normally infrared measurments are and ends at 500 um. pressed in terms of wavenumber which is the inverse of wavelength in units of centimeters. Infrared absorption generally corresponds to changes in vibrational and rotational levels of a molecule. Infrared absorption occurs when the frequency of the alternating electric field associated with the incident radiation matches a possible change in the vibration or rotational frequency of the absorbing molecule. When a match occurs the incident frequency can be absorbed by the molecule causing a change in the amplitude of the vibration or a change in the rate of rotation. A change of dipole moment is necessary for a molecule in order to able to absorb the incident electromagnetic radition. Otherwise, no energy transfer to molecule is possible. For example N2 or O2 which have symmetric1 charge distributions can not be detected by the infrared method. Figure 19 shows meaurement of absorbance vs wavenumber where the carbon absorption is at 604 cm<sup>-1</sup> and oxygen at 1106 cm<sup>-1</sup>. A correlation factor is defined based on ASTM standards and is used to calculate the concentration of oxygen and carbon in silicon.

Figure 19) FITR measurements of absorbance vs wavenumber of heat treated wafers

# 3.5 MOSFET DEVICE AND AGING MEASUREMENT SYSTEM4

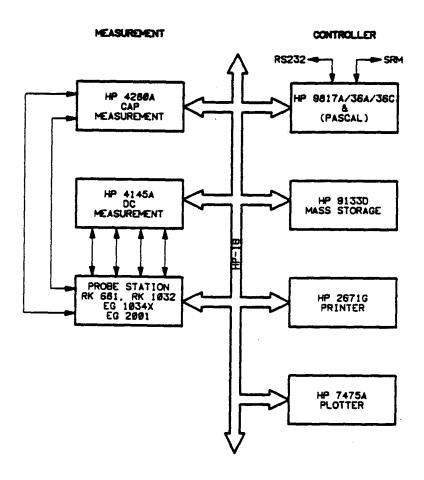

A TECAP (Transistor Electrical Characterization Analysis Program ) system was used to analyze MOSFET devices before and after aging. TECAP is a set of HP software which transforms measured data into transistor model parameters [63] which are used for circuit simulation systems. TECAP was used in this study to accurately measure device parameters such as threshold voltage, device currents and threshold currents before and after aging. The TECAP hardware consist of an HP9836 desktop comuputer, HP4145 semiconductor parameter analyzer, HP2671 thermal printer and probe station. The communication between the hardware through HP-IB. An HP4280A can be added to TECAP to measure C-V plots. Figure 20 shows the TECAP system. For the aging system a set of hardware similar to the TECAP system was used with an in-house developed software [64] to monitor automatically device parameters such as threshold, transconductance, substrate current, device linear and saturation currents at predefined times and calculate the degradation rate of these parameters. After aging n-channel devices, some of these were used for current-DLTS measurements some for hot chuck measurements for studing the defect energy levels and detrapping processes.

Figure 20) TECAP Transistor parameter measurement system [63]

# 4. EXPERIMENTAL PROCEDURES AND RESULTS PART I. MATERIAL CHARACTERIZATION

In first section of this chapter different heat treatment cycles for inducing oxygen micordefects and stacking faults will be presented. In the second section a brief introduction to the fabrication of Schottky diodes on polished silicon surfaces will be discussed. The last section will be on DLTS and photocapacitance characterization of heat treated wafers with different initial concentrations of oxygen and carbon impurities.

## 4.1 HEAT TREATMENT CYCLES

The wafers used in this work were provided from vendors and then numbered alphanumerically. They were phosphorus-doped, n-type, 100 mm diameter Czochralski (CZ) silicon of (100) orientation with resistivity of 5-7 ohm-cm. To induce microdefects and stacking faults various annealing cycles were carried out, as shown in Figure 21. Since, are interested in studying the bulk stacking faults and microdefects, wafers were not subjected to the first high oxygen outdiffusion as is normally done in the three (high-low-high) CMOS heat treatment cycle. Wafers were heat treated at 750 C for 16 hours in nitrogen to maximize various oxygen precipitation and then were subjected to high temperatures in a nitrogen gas ambient for precipitate

growth. An hour oxidation was done after the low 750 C anneal to reduce surface pits.

Figure 21 ) Heat treatment cycles for studying the bulk microdefects and stacking faults.

The oxygen and carbon concentrations were determined with FTIR measurements using either a Nicolet or Digilab instrument. All the measurements were based on 1979 ASTM standards. Table 1 shows the FTIR measurement of oxygen and carbon concentrations before and after a 750 C/ 16 hours and 1050 C/ 16 hours heat treatment cycle. Stacking faults were not detected optically on wafers 3,4,16,18,22,and 23.

# WAFERS HEAT TREATED AT HEWLETT-PACKARD

| WAFER                                                                         | O <sub>F</sub> -O <sub>I</sub>                                                                                                        | C <sub>I</sub>                                                         | C <sub>F</sub>                                                                 | STACKING<br>FAULTS                                    |

|-------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|--------------------------------------------------------------------------------|-------------------------------------------------------|

| 3<br>4<br>9<br>10<br>16<br>17<br>18<br>19<br>22<br>23<br>24<br>26<br>27<br>31 | 20.879<br>19.61<br>20.195<br>19.708<br>21.84<br>20.373<br>19.221<br>16.332<br>19.299<br>19.45<br>17.143<br>17.535<br>21.102<br>19.618 | .038<br>.096<br>.034<br>.096<br>0<br>.103<br>.093<br>.043<br>.051<br>0 | .032<br>.113<br>.053<br>.137<br>.027<br>0<br>.124<br>.073<br>.119<br>.105<br>0 | NO NO YES YES NO YES NO YES NO NO YES YES YES YES YES |

|   | WAFERS | НЕАТ | TREATED A | T | osu |

|---|--------|------|-----------|---|-----|

| - |        |      |           |   |     |

| 55<br>71<br>26.010<br>107<br>19.136 | 0<br>0<br>0 | 0<br>0<br>0 | YES<br>YES<br>YES |  |

|-------------------------------------|-------------|-------------|-------------------|--|

|-------------------------------------|-------------|-------------|-------------------|--|

Table 1 ) A summary of main wafers used for studying the bulk defect with DLTS.

The possibility that facility-related impurities play a role in this study is reduced by heat treatments at two different locations, at the Hewlett-Packard fabrication facility, and at Oregon State's silicon material processing laboratory.

#### 4.2 SCHOTTKY DIODE FABRICATION

The theoretical models of metal-semiconductor interfaces have been described in several text books [65-66]. Investigation into the actual physical picture of the metal-semicondutor interface has been an active area of search due to the important effects on semiconductor characteristics [67]. In this work, we will use techniques to obtain low leakage diodes on n-type After a two steps heat treatment cycle, about 20 um etched from the sample surface to remove any denuded that might have formed. Initially, a combination of mechanical polish and chemical (CP4 or Planar) etch was this technique resulted in a very poor yield (high method was Schottky diodes). The second Plasma etch (SF6+O2) to etch silicon surface. The plasma method improved the silicon surfaces and resulted in a very repeatable process with low leakage Schottky diodes. Figure 22 shows three steps process to fabricate Schottky diodes etched silicon surface. After the plasma etch, the wafers were processed in a HF tank for two minutes to remove native oxide and then 5 mins in rinse and dry. Immediately, after these simple cleaning steps, the wafers were placed in a vacuum chamber for metal deposition. Back side contact were made initially with aluminum evaporation and then alloy at 300 C to ensure ohmic contacts. Then, aluminum was evaporated through a metal dot mask to fabricate Schottky

diodes on the front side of the wafers. Capacitance-voltage (C-V) and current-voltage (I-V) characteristics were checked before any DLTS measurement to ensure low leakage (less than 1 um). I-V and C-V curves of a typical Schottky diodes are shown in Figure 23. The current density of a diode can be expressed as

$$J = J_s \exp\left(\frac{qV}{nKT}\right) \qquad for V > \frac{kT}{q}$$

(26)

N-TYPE SILICON WAFER WITH STACKING FAULTS AND MICRODEFECTS

CHEMICALLY OR PLASMA ETCHED SURFACE

SCHOTTKY DIODES ON ETCHED SURFACE

Figure 22) A three step process to make Schottky diodes on an etched silicon surface.

Figure 23) I-V and C-V characteristics of a heat treated and plasma etched wafer (#71)

Figure 24) Saturation current and ideality factor can be obtained from log-linear I-V plot (wafer #25)

where Js is the saturation current density and can be obtained by extrapolating the current density from the a log-linear plot to V=0. Figure 24 shows the forward and reverse current densities of a Schottky diode on wafer #25. The parameter (n) is called the ideality factor. The ideality factors for Schottky diodes made for this study were very close to unity (n= 1.1).

#### 4.3 DLTS CHARACTERIZATION OF HEAT TREATED WAFERS

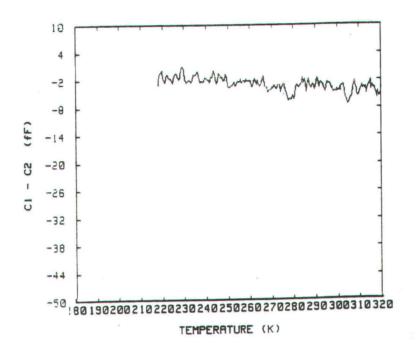

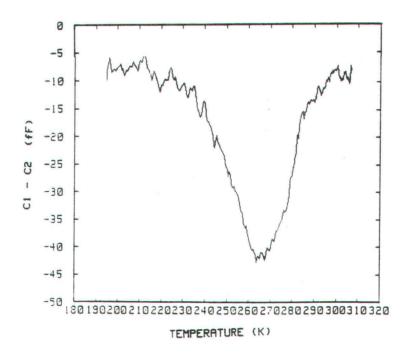

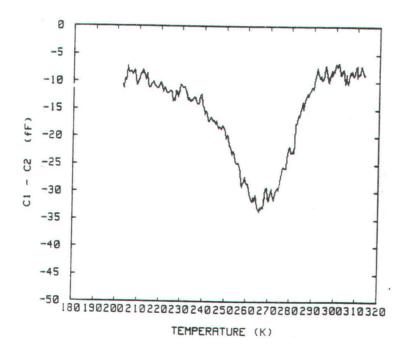

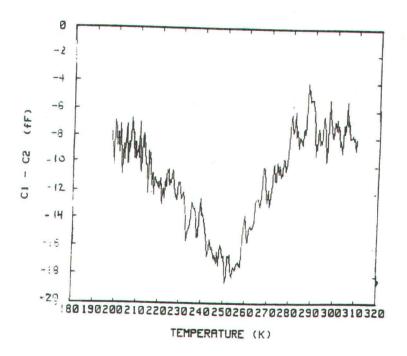

Schottky diodes on etched silicon surfaces with ceptable leakage currents (less than 50 uA at -2.5 volts reverse bias) were used for characterizing the oxygen duced microdefects. A C-V plot was done to ensure reasonable diode characteristics before measurement. any DLTS Schottky diodes are asymmetric junctions where the depletion region is primarily in the low doped silicon material side. DLTS signals are sensitive to only the defects in depletion region which is on the order of 2 um at the highest reverse Therefore, a denuded zone of 5-20 um has to be etched bulk microdefects and off for DLTS characterization of stacking faults. Capacitance DLTS measurements initially were performed on both n- and p-type silicon wafers [68]. In order to correlate the DLTS results with the physical defects, a Wright etch [69] was used to preferentially etch the silicon surfaces under the Schottky diodes. A correlation was found between the stacking fault size and density and the DLTS trap concentration measurement when the initial carbon concentration in a wafer was below the FITR detection limit which is  $1x10^{15}/cm^3$  [70]. Figure 25 shows the results wafer #25 with no heat treatment and no surface The DLTS spectra shows no peaks and there were no microdefects on the etched wafer surface after Wright etch with optical photo with magnification of about 1500X, as is shown in Figure 25. Plasma etch (SF<sub>6</sub>+O<sub>2</sub>) was used to etch of

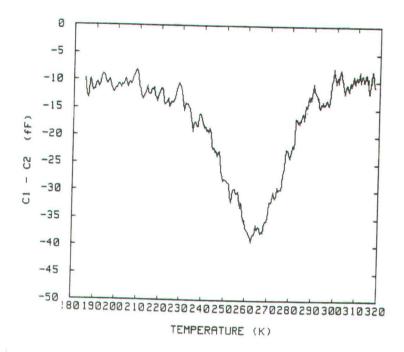

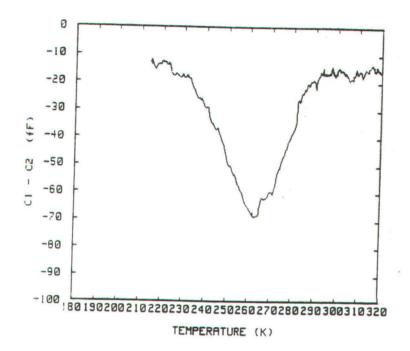

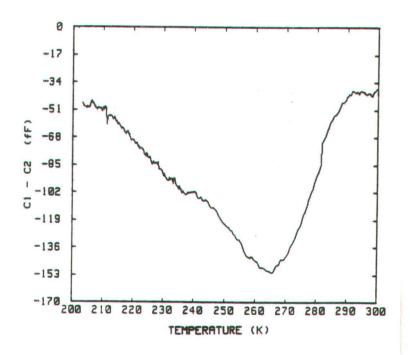

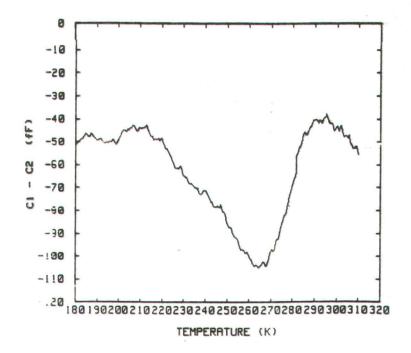

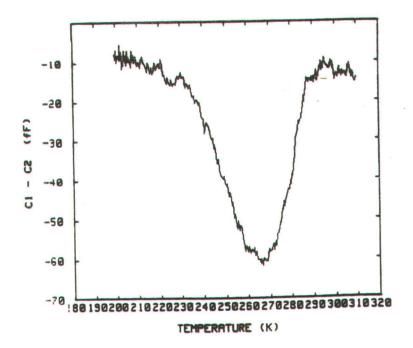

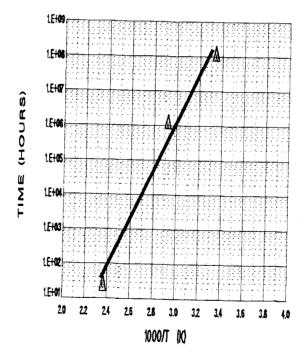

silicon surfaces since mechanical and chemical etches sulted in high leakage Schottky diodes . Figure 26 the DLTS measurement of a Schottky diode fabricated on control wafer with no heat treatment but with 25 microns the top surface etched off in a SF6+02 plasma. No DLTS peak was detected on plasma etched control samples, and method was used for etching off the denuded zone. 27-37 show that wafers 3, 4, 9, 10, 16, 18, 19, 22, and 23 have no DLTS peak even in the presence of stacking faults (Wafers 9, 10, 19 have stacking faults). Wafers 17, 24, 27, 31, 55, 71, and 107 all have a consistent DLTS peak at 260 K (for a DLTS rate window of t1/t2=10/40). The only difference between these two sets of wafers is the initial When a small trace of carbon is detected wafer, then the the oxygen induced micordefects show electrical activity. Table 2 summarizes the DLTS measurement results. The wafers were heat treated in two different locations to minimize the the possibility that facility-related impurity concentrations play a role in this study. Figure 38 shows the Arrhenius plot of the emission rates vs temperature. A single dominant energy level at Ec-Et=.48 +/- .05 ev was detected on wafers 17, 24, 26, 71, 55, and 107 independent of facility when the carbon concentration was detection limits (figure 38).

Figure 39a shows DLTS the spectra of control wafer B with no heat treatment or plasma etch before any mechanical damage to silicon surface. No peak was detected as expected.

However, after an intentional mechanical damage to the silicon surface under the Schottky diode a peak very similar to that which was detected on wafers with stacking faults but with low carbon was obtained. The interesting point is this peak is also very similar to Omling's [27] DLTS level D (see page 17-18). Omling related the DLTS line D to "Dangling bond" centers using EPR.

We will discuss this subject in chapter 7 and will develop a model that might account for these experimental results [71].

Figure 25) DLTS spectra of control sample #25 with no surface etch or heat treatment t1/t2= 10/40 mS,  $N_{\rm T}$ =0 and the optical photo of the etched silicon surface with magnification of 1500X