### AN ABSTRACT OF THE DISSERTATION OF

Qadeer Ahmad Khan for the degree of <u>Doctor of Philosophy</u> in <u>Electrical and Computer Engineering</u> presented on <u>May 11, 2012</u>. Title: <u>Digitally Assisted Control Techniques for High Performance</u> Switching DC-DC Converters .

Abstract approved: \_\_\_\_

#### Pavan Kumar Hanumolu

Digitally controlled switching DC-DC converters have recently emerged as an attractive alternative to conventional switching converters based on analog control techniques. This research focuses on eliminating the issues associated with the state of the art switching converters by proposing three novel control techniques: (1) a digitally controlled Buck-Boost converter uses a fully synthesized constant ON/OFF time-based fractional-N controller to regulate the output over a 3.3V-to-5.5V input voltage range and provides seamless transition from buck to buck-boost modes (2) a hysteretic buck converter that employs a highly digital hybrid voltage/current mode control to regulate output voltage and switching frequency independently (3) a 10MHz continuous time PID controller using time based signal processing which alleviates the speed limitations associated with conventional analog and digital.

All the three techniques employ digitally assisted control techniques and require no external compensation thus making the controllers fully integrated and highly cost effective. <sup>©</sup>Copyright by Qadeer Ahmad Khan May 11, 2012 All Rights Reserved

# Digitally Assisted Control Techniques for High Performance Switching DC-DC Converters

by

Qadeer Ahmad Khan

### A DISSERTATION

submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Presented May 11, 2012 Commencement June 2013 APPROVED:

Major Professor, representing Electrical and Computer Engineering

Director of the School of Electrical Engineering and Computer Science

Dean of the Graduate School

I understand that my dissertation will become part of the permanent collection of Oregon State University libraries. My signature below authorizes release of my dissertation to any reader upon request.

Qadeer Ahmad Khan, Author

#### ACKNOWLEDGMENTS

With immense faith, first of all I want to thank Almighty GOD, the creator of all worlds, the creator of intellectual and beautiful human being, the provider of sustenance to each and every living creature in this universe, the most merciful, the listener to every grief and the provider of relief, Who has given me this opportunity to accomplish my dream of Ph.D.

Then my heartiest gratitude goes to my advisor Prof. Pavan Kumar Hanumolu who gave me an opportunity to be the member of his group and work on my research of interest, power management IC design. Throughout my Ph.D., he encouraged me a lot with his innovative ideas, teachings and by providing freedom to work according to my aspiration. His technical guidance and friendly behavior is always enlivening for my research. I sincerely appreciate the time he spent reviewing my career goals and recommending strategies for achieving them. The association that I have with him is unforgettable and will always remain indebted to him.

It is a pleasure to express my gratitude to Prof. Un-Ku-Moon, Prof. Karti Mayaram and Prof. Ted Brekken for serving on my exam committee and providing constructive feedback on my thesis. I am also grateful to Prof. Gabor Temes for advising me during first year of my graduation and serving to my preliminary exam committee. I would like to thank Prof. William Warnes for taking time off his busy schedule and serving as graduate council representative in my Ph.D. defense program. My sincere thanks to all the EECS professors for teaching me various courses and providing guidance during course work and to Ferne Simendinger and Shannon Thompson for their administrative support.

I would like to thank my kind fellows Sachin Rao, Amr Elshazly, Wenjing

Yin, Brian Young, Rajesh Inti, Seokmin Jung, Mrunmay Talegaonkar, Karthikeyan Reddy, Tushar Uttarwar, Jeff Pai, Sarvesh Bang, Abhijith Arakali, Bangda Yang, Brian Drost, Romesh Nandawana and Saurabh Saxena from Prof. Hanumolu's group, for their support in my research projects and their advice both technical and non-technical. I am fortunate indeed to get such a wonderful colleagues who made my life enjoyable at OSU by providing fun and family environment. My sincere thank goes to other members of Analog/Mixed Signal group: Kyehyung Lee, Jeong Seok Chae, Yan Wang, Sang Hyeon Lee and Rishi Gupta from Prof. Temes' group, Hariprasath Venkatram, Manideep Gande, Simon Hu, Tawfiq Musah, Sunwoo Kwon, Dave Gubbins, Nima Maghari and Ho-Young Lee from Prof. Moon's group, Vikrant Pranesh, Ramin Zangbagi, Saeed Pourbagheri and Syed Feruz from Prof. Mayaram's group, Karthik Jayaraman and Jacob Postman from Prof. Patrick Chiang's group for their valuable discussions. I would also like to thank Matthew Brown for being so co-operative with testing my chips in the AMS lab.

Now my future journey gives me a call to face new challenges and accomplish more in life but I am going to miss both the Institution as well as all the professors and my fellows.

In addition I want to thank National Semiconductor for giving me the opportunity to have internship there and providing fabrication for my research projects. My special thank goes to Ali Djabbari, Jeff Morroni, Jianhui Zhang, Zhenyong Zhang, Raj Subramaniam and Bijoy Chatterjee for providing all technical and non-technical help during my internship. I would like to express my heartiest gratitude to Arun Rao, Damian Swank, William McIntyre, Keith Schoendoerfer and Nathanael Griesert from Grass Valley Design Center of National Semiconductor for their technical support and holding weekly meeting to review my research progress. Their constructive feedback helped in successful execution of my research projects. It was a wonderful experience working with all of them.

Finally I want to thank my brother Zameer and his wife (Saba), sisters (Salma, Naghma, Nasreen, Yasmeen, Tahseen and Nazreen), brothers-in-law, my nieces, nephews, other relatives and friends for their true assistance, encouragement and unconditional love. My wife (Farhat Jahan) has been a great support during last two years of my graduation since we got married. I would like to thank my in-laws for their love and blessings. And last but not least, my very special thank to the most important people in my life- my father Mr. Sagheer Khan and my loving mother Mrs. Saleha Begum, who have always been the constant source of my inspiration and ongoing support. Without their genuine support I would not have achieved my ambitions. Nothing can match the immeasurable love they provided me throughout my life. I dedicate this thesis to them.

### TABLE OF CONTENTS

Page

| 1 | INTI | RODUCTION                                                                           | 1              |

|---|------|-------------------------------------------------------------------------------------|----------------|

|   | 1.1  | Motivation and Research Contribution                                                | 1              |

|   | 1.2  | Thesis Organization                                                                 | 4              |

| 2 | AN ( | OVERVIEW OF SWITCHING DC-DC CONVERTER                                               | 6              |

|   | 2.1  | Linear vs. Switching Converter                                                      | 6              |

|   | 2.2  | Switching DC-DC Converter                                                           | 8              |

|   | 2.3  | Types of DC-DC Converters                                                           | 10             |

|   | 2.4  | Switching Converter Control Techniques                                              | 11             |

|   | 2.5  | Voltage Mode vs. Current Mode PWM Control                                           | 12             |

|   | 2.6  | Efficiency of A Switching DC-DC Converter                                           | 14             |

|   | 2.7  | Control Loop Dynamics of DC-DC Converter                                            | 18             |

|   | 2.8  | Switching Noise Caused by DC-DC Converter                                           | 20             |

|   |      | 2.8.2 Supply and Ground Bounce                                                      | 20<br>21<br>22 |

|   | 2.9  | Discontinuous Conduction Mode (DCM)                                                 | 24             |

| 3 |      | TAL CONSTANT ON/OFF TIME DELTA-SIGMA FRACTIONAL-<br>ONTROL FOR BUCK-BOOST CONVERTER | 28             |

|   | 3.1  | Introduction to Buck-Boost Converter                                                | 28             |

|   | 3.2  | Constant ON/OFF Time Operation                                                      | 32             |

|   | 3.3  | Proposed Architecture                                                               | 34             |

|   |      |                                                                                     | 36<br>36       |

## TABLE OF CONTENTS (Continued)

|   |     | $\underline{Pa}$                                                                                                                                  | ge       |

|---|-----|---------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|   | 3.4 | Fractional-N Controller Design                                                                                                                    | 38       |

|   | 3.5 | Experimental Results                                                                                                                              | 40       |

| 4 |     | D FREQUENCY HYBRID VOLTAGE AND CURRENT MODE<br>TERETIC BUCK CONVERTER                                                                             | 44       |

|   | 4.1 | A Voltage mode Hysteretic DC-DC Converter                                                                                                         | 44       |

|   |     | <ul><li>4.1.1 Stability of a Hysteretic DC-DC Switching Converter</li><li>4.1.2 Transient Response of a Hysteretic DC-DC Switching Con-</li></ul> | 46       |

|   |     | 4.1.3 Effect of Loop Delay on Switching Frequency and Voltage<br>Regulation                                                                       | 50<br>56 |

|   | 4.2 | Current Mode Hysteretic Converter                                                                                                                 | 59       |

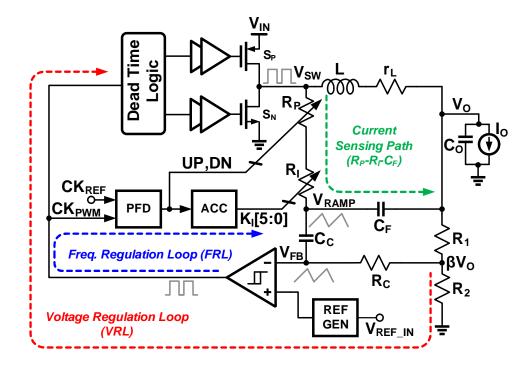

|   | 4.3 | Proposed Fixed Frequency Hybrid Voltage and Current Mode Hys-<br>teretic Converter                                                                | 63       |

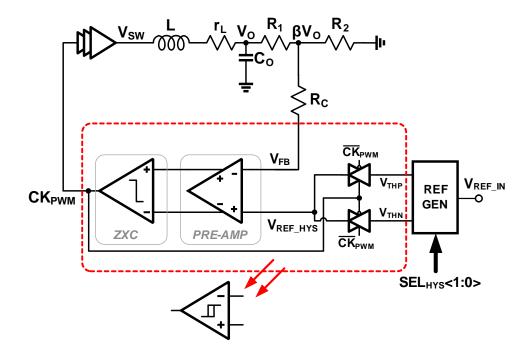

|   |     | <ul><li>4.3.1 Design of Voltage Regulation Loop (VRL)</li><li>4.3.2 Design of Frequency Regulation Loop (FRL)</li></ul>                           | 63<br>65 |

|   | 4.4 | Measured Results                                                                                                                                  | 67       |

| 5 |     | E BASED PWM CONTROLLER FOR HIGH FREQUENCY DC-<br>CONVERTERS                                                                                       | 75       |

|   | 5.1 | Trade-offs in high speed Switching Converter                                                                                                      | 75       |

|   | 5.2 | Time (phase) domain signal processing                                                                                                             | 78       |

|   |     | <ul><li>5.2.1 Time Domain Amplifier</li><li>5.2.2 Time Domain Integrator</li></ul>                                                                | 78<br>81 |

|   | 5.3 | Time based PID compensator (TPID)                                                                                                                 | 82       |

|   | 5.4 | Proposed Time based PWM (TPWM) Controller                                                                                                         | 85       |

|   | 5.5 | Designing TPID parameters                                                                                                                         | 89       |

## TABLE OF CONTENTS (Continued)

Page

|    | 5.6  | Design and implementation                                                             | 90  |

|----|------|---------------------------------------------------------------------------------------|-----|

|    | 5.7  | Simulation Results                                                                    | 94  |

|    | 5.8  | Issues with time based PWM controller                                                 | 95  |

|    |      | <ul><li>5.8.1 Duty Cycle Slipping</li><li>5.8.2 DC offset in output voltage</li></ul> |     |

|    | 5.9  | Future Research                                                                       | 106 |

| 6  | CON  | CLUSION                                                                               | 109 |

| BI | BLIO | GRAPHY                                                                                | 110 |

### LIST OF FIGURES

| Figu | ire                                                                  | Page  |

|------|----------------------------------------------------------------------|-------|

| 1.1  | Various applications requiring dc-dc converters                      | 2     |

| 1.2  | DC-DC Converter market. Source: isupply [1]                          | 2     |

| 2.1  | A linear regulator                                                   | 6     |

| 2.2  | Efficiency comparison of switching and linear regulators             | 7     |

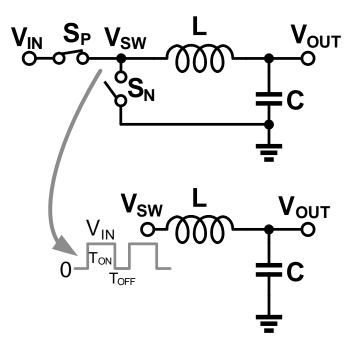

| 2.3  | Switching action of a dc-dc converter                                | 8     |

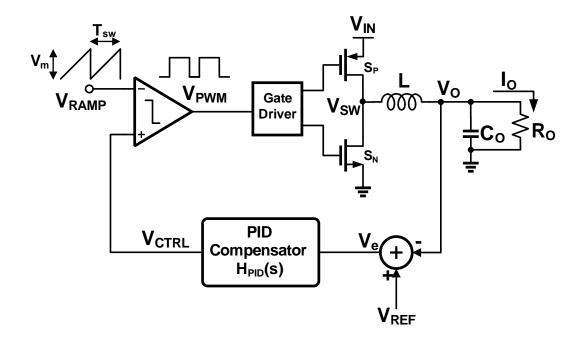

| 2.4  | A PWM controlled switching dc-dc converter                           | 9     |

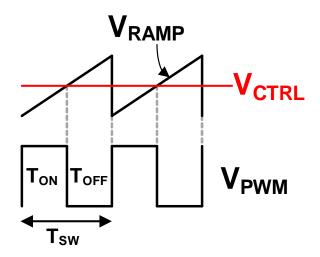

| 2.5  | A pulse width modulated signal                                       | 10    |

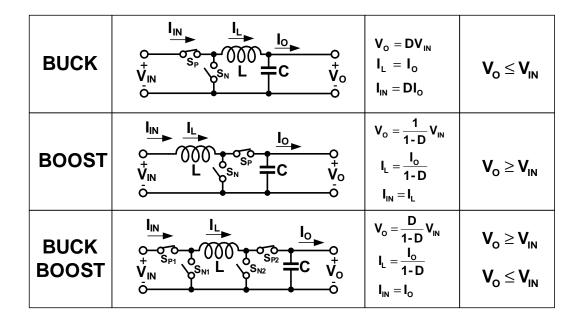

| 2.6  | Different classes of switching dc-dc converters                      | 11    |

| 2.7  | A current mode controlled dc-dc converter                            | 12    |

| 2.8  | Pulse width modulation in a peak current mode converter              | 13    |

| 2.9  | Different loss components associated with a dc-dc converter          | 14    |

| 2.10 | Hard switching losses $(P_{sw})$ in a dc-dc converter                | 16    |

| 2.11 | Dead time switching losses $(P_{dead})$ due to body diode conduction | n. 17 |

| 2.12 | Bode plot of the PID compensator                                     | 19    |

| 2.13 | Bode plot of an uncompensated and compensated buck converte          | r 20  |

| 2.14 | Substrate noise injection due to body diode conduction               | 21    |

| 2.15 | Supply and Ground noise in a DC-DC converter                         | 22    |

| 2.16 | Output voltage ripple of a buck converter                            | 23    |

| 2.17 | Inductor current valley hitting zero in case of light load           | 25    |

| 2.18 | Implementation of DCM in a buck converter                            | 25    |

| 3.1  | Discharging profile of a Li-ion battery                              | 29    |

| 3.2  | Conventional single-mode Buck-Boost converter                        | 29    |

| 3.3  | Tri-mode converter timing diagram.                                   | 30    |

| Figu | <u>ire</u> <u>H</u>                                                                                     | Page |

|------|---------------------------------------------------------------------------------------------------------|------|

| 3.4  | Overshoot during mode transition in a tri-mode buck-boost con-<br>verter                                | 31   |

| 3.5  | Inductor ripple current and output voltage of a buck converter for constant OFF time (variable ON time) | 33   |

| 3.6  | Proposed digital Buck-Boost converter                                                                   | 34   |

| 3.7  | Lookup table for control mapping                                                                        | 35   |

| 3.8  | Profile of inductor current in different states of buck-mode                                            | 37   |

| 3.9  | Profile of inductor current in buck-boost and boost states                                              | 38   |

| 3.10 | Digital Fractional-N controller implemented the proposed buck-<br>boost converter                       | 39   |

| 3.11 | Control signals and output voltage of the proposed controller                                           | 40   |

| 3.12 | Output voltage and spectrum plot of the proposed converter in buck and buck-boost modes                 | 41   |

| 3.13 | Output waveforms of the proposed converter during buck to buck-<br>boost mode transition                | 41   |

| 3.14 | Die photo of the proposed digital buck-boost converter                                                  | 42   |

| 3.15 | Measured $V_{IN}$ versus $V_{OUT}$                                                                      | 42   |

| 3.16 | Measured switching profile in different operating states                                                | 43   |

| 3.17 | Measured efficiency versus input voltage                                                                | 43   |

| 4.1  | A voltage mode hysteretic converter.                                                                    | 45   |

| 4.2  | Switching behavior of a hysteretic converter.                                                           | 46   |

| 4.3  | Ripple of a hysteretic converter                                                                        | 48   |

| 4.4  | Offset in the output ripple due to lower $R_{ESR}C_0$                                                   | 50   |

| 4.5  | Transient response of an ideal buck dc-dc converter.                                                    | 51   |

| 4.6  | Effect of load current slew rate $(dI_O/dt)$ on transient response of<br>a dc-dc converter              | 53   |

| Figu | <u>Ire</u> <u>Pa</u>                                                                                        | ige |

|------|-------------------------------------------------------------------------------------------------------------|-----|

| 4.7  | Effect of ESR on transient response of an ideal dc-dc buck converter.                                       | 54  |

| 4.8  | Transient response showing degradation with reduced $R_{ESR}C_O$ time constant.                             | 56  |

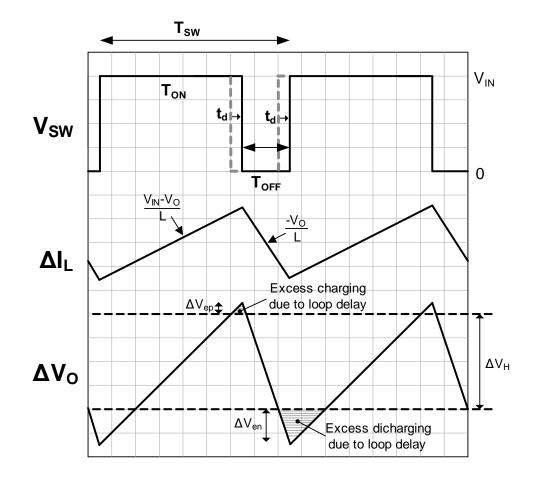

| 4.9  | Offset in the output ripple due to loop delay                                                               | 57  |

| 4.10 | A current mode hysteretic dc-dc converter.                                                                  | 59  |

| 4.11 | Switching behavior of a current mode hysteretic converter                                                   | 60  |

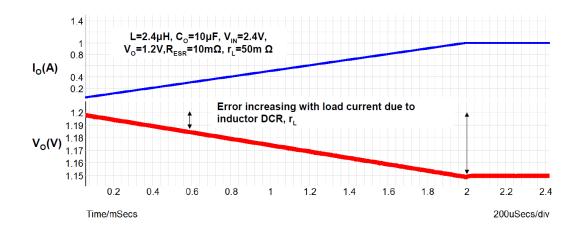

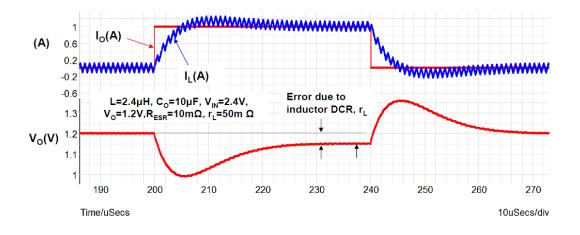

| 4.12 | Simulated output of a current mode hysteretic converter under varying current showing poor load regulation. | 62  |

| 4.13 | Simulated transient response of a current mode hysteretic con-<br>verter showing effect of inductor DCR.    | 62  |

| 4.14 | Architecture diagram of the proposed hysteretic dc-dc converter                                             | 64  |

| 4.15 | Circuit diagram of the voltage regulation loop (VRL)                                                        | 65  |

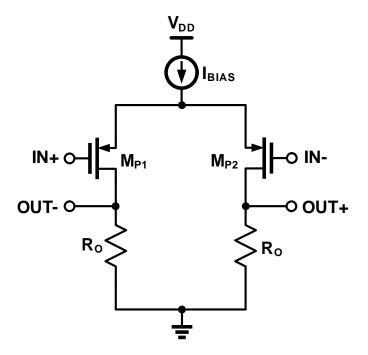

| 4.16 | Circuit diagram of the pre-amplifier.                                                                       | 66  |

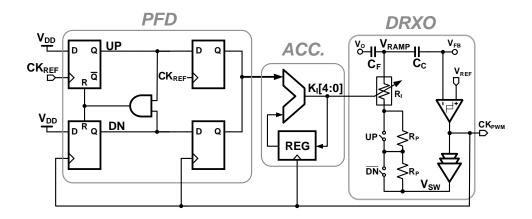

| 4.17 | Circuit diagram of the frequency regulation loop (FRL)                                                      | 67  |

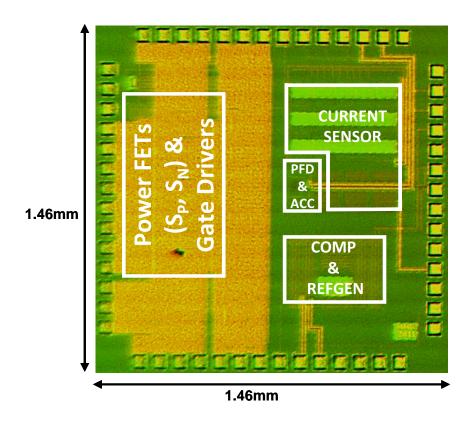

| 4.18 | Die photo of the proposed hysteretic converter                                                              | 68  |

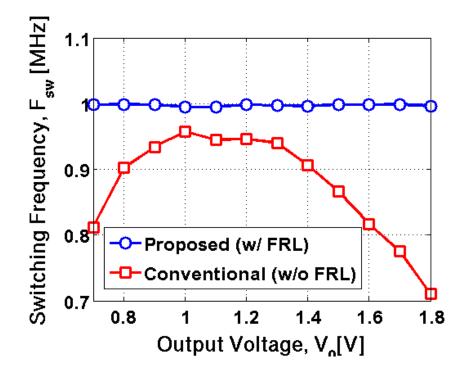

| 4.19 | Switching frequency, $F_{SW}$ vs input voltage, $V_{IN}$ at $V_O = 1.2V$                                    | 69  |

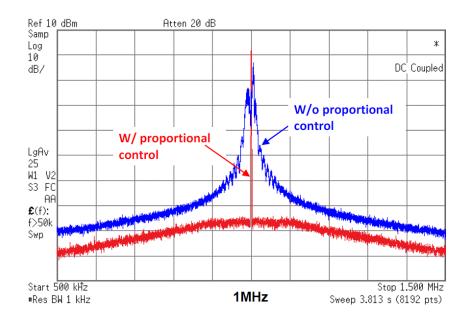

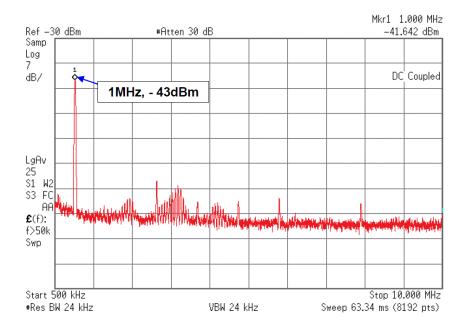

| 4.20 | Spectrum of the switching clock, $CK_{PWM}$                                                                 | 69  |

| 4.21 | Output voltage spectrum                                                                                     | 70  |

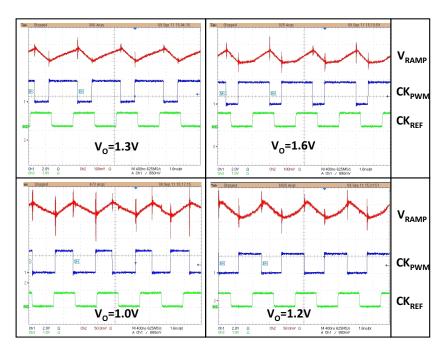

| 4.22 | Measured $V_{RAMP}$ and clock signals under locked condition for different duty cycles                      | 70  |

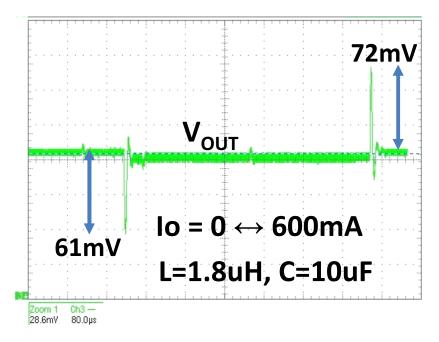

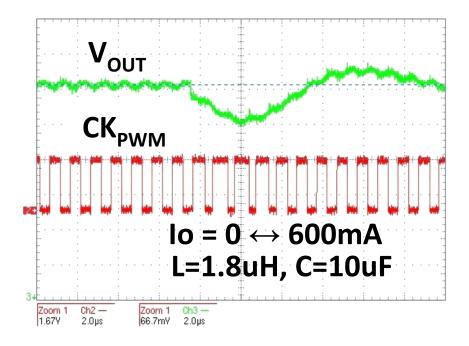

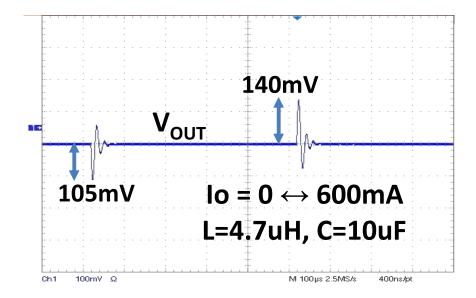

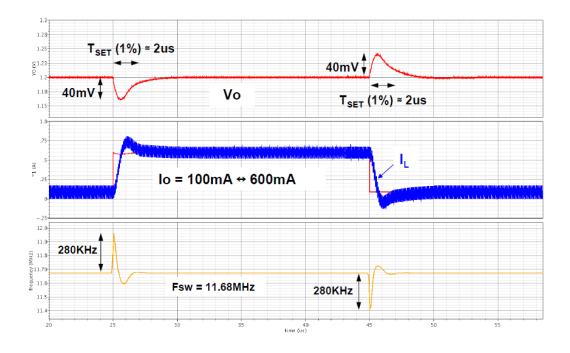

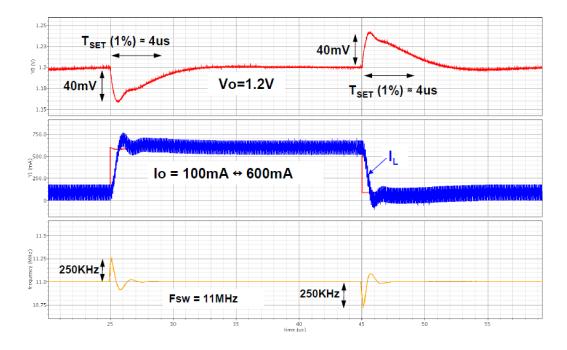

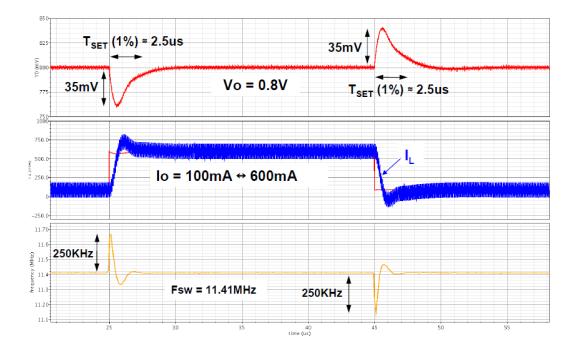

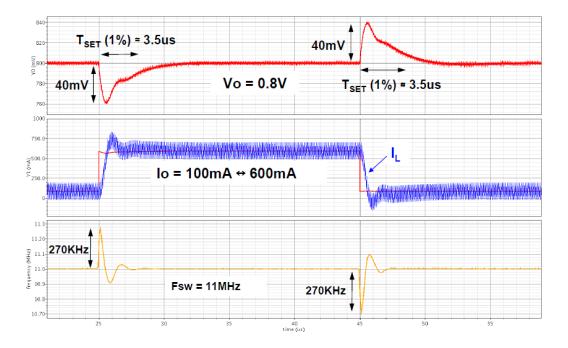

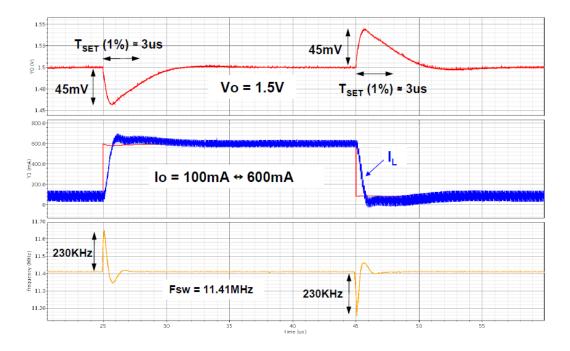

| 4.23 | Measured output transient response at $L = 1.8 \mu H$                                                       | 71  |

| 4.24 | Ouput setlling at $L = 1.8 \mu H$ .                                                                         | 72  |

| 4.25 | Measured output transient response at $L = 4.7 \mu H$                                                       | 72  |

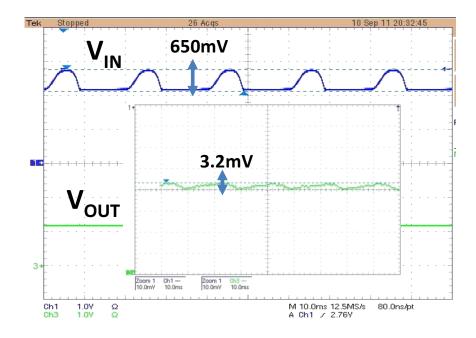

| 4.26 | Measured line regulation.                                                                                   | 73  |

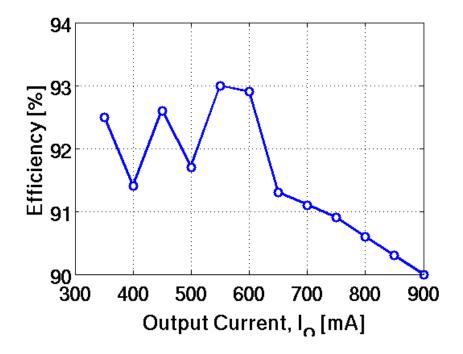

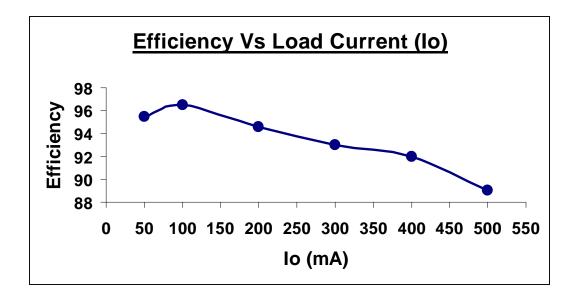

| 4.27 | Measured efficiency vs. $I_O$                                                                               | 73  |

| Figu | Figure                                                                                               |     | Page |  |

|------|------------------------------------------------------------------------------------------------------|-----|------|--|

| 4.28 | Performance summary                                                                                  |     | 74   |  |

| 5.1  | An analog PWM based dc-dc converter                                                                  |     | 76   |  |

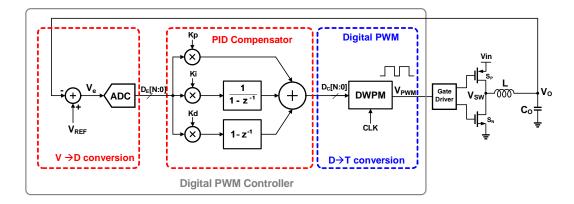

| 5.2  | A digital PWM based dc-dc converter.                                                                 |     | 77   |  |

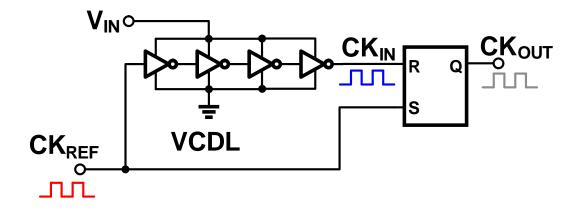

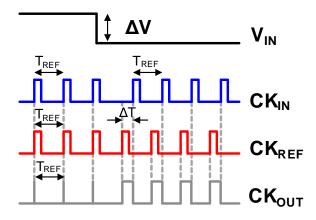

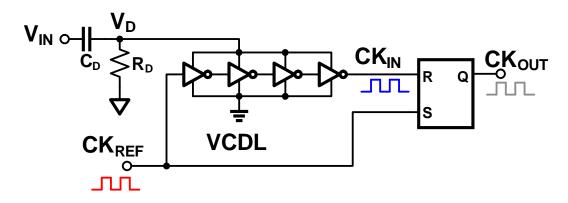

| 5.3  | A VCDL used as phase amplifier                                                                       |     | 79   |  |

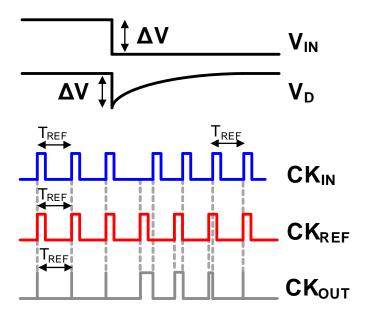

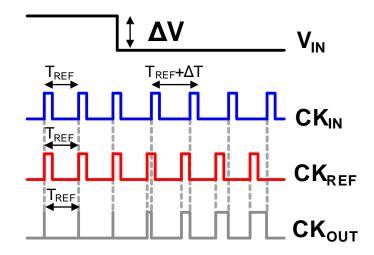

| 5.4  | Step response of a VCDL                                                                              |     | 79   |  |

| 5.5  | A phase differentiator using VCDL                                                                    |     | 80   |  |

| 5.6  | Step response of a phase differentiator                                                              |     | 81   |  |

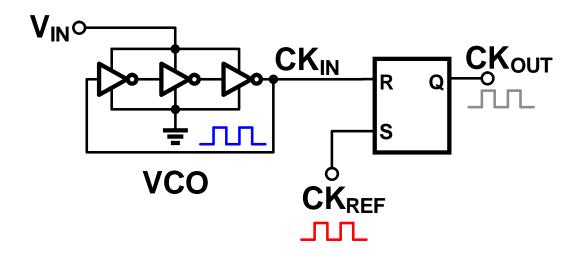

| 5.7  | A time based integrator using VCO                                                                    |     | 82   |  |

| 5.8  | Step response of time based integrator                                                               |     | 83   |  |

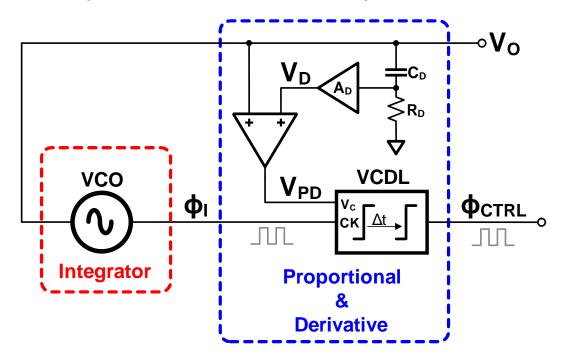

| 5.9  | Block diagram of a time based PID compensator                                                        |     | 84   |  |

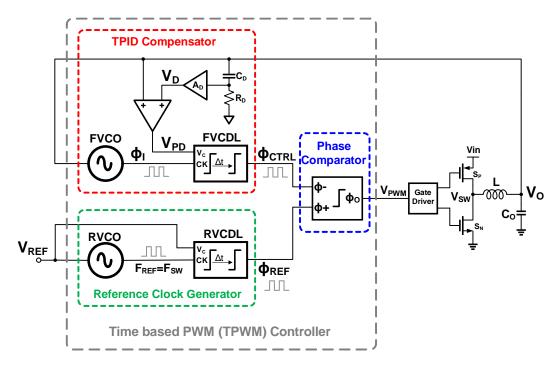

| 5.10 | Block diagram of the proposed time based PWM controller                                              |     | 86   |  |

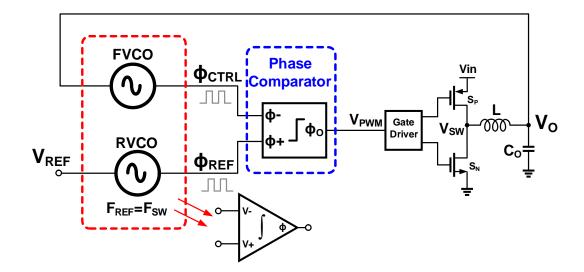

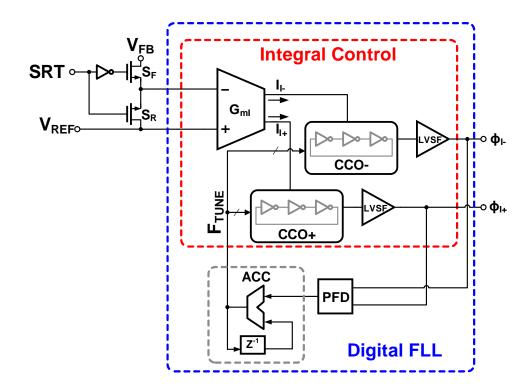

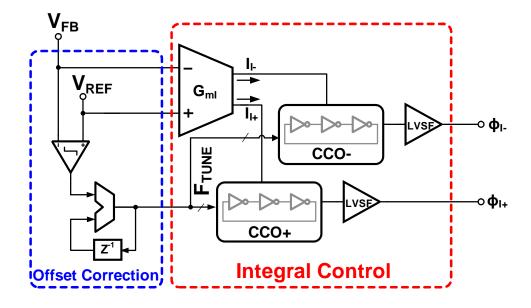

| 5.11 | A converter with only integral loop                                                                  |     | 87   |  |

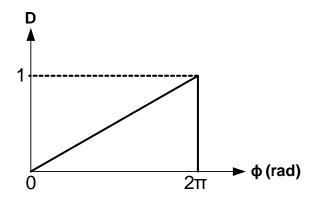

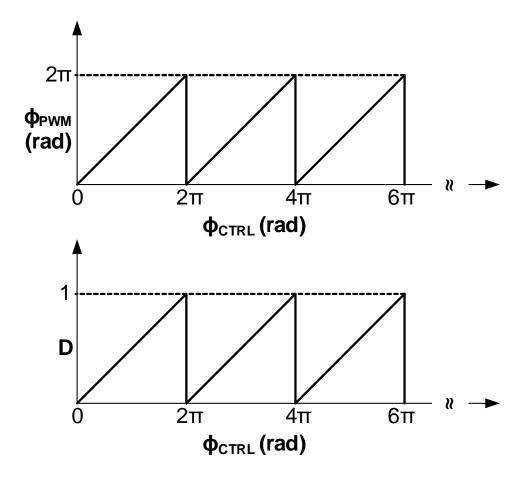

| 5.12 | Duty cycle vs. phase                                                                                 |     | 88   |  |

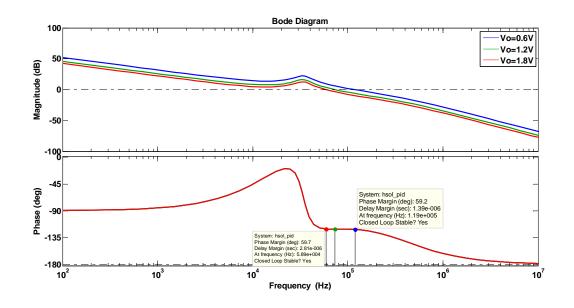

| 5.13 | Magnitude and phase response of the compensated dc-dc buck<br>converter at different output voltages |     | 91   |  |

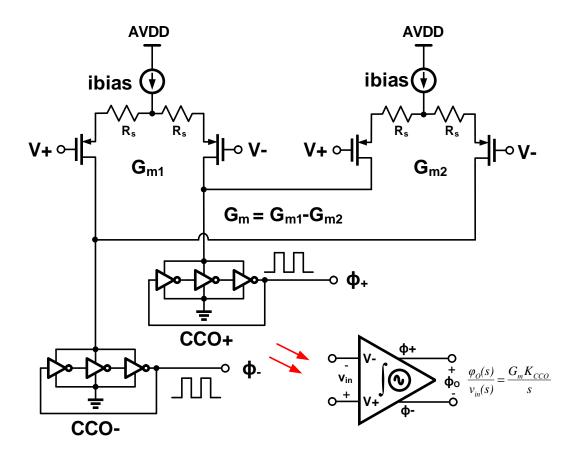

| 5.14 | A fully differential phase integrator with large time constant                                       |     | 92   |  |

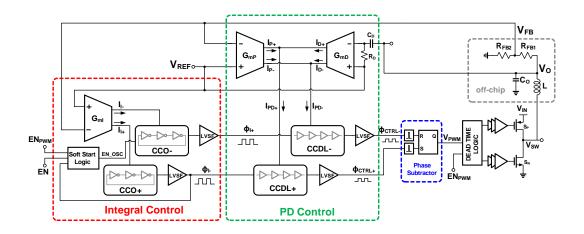

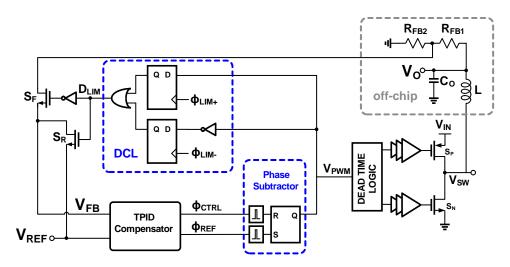

| 5.15 | Architecture of the buck converter implemented with proposed<br>time based PID controller            |     | 93   |  |

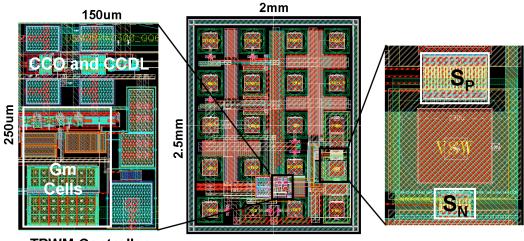

| 5.16 | Layout of the full chip dc-dc converter implemented with TPWM controller                             |     | 94   |  |

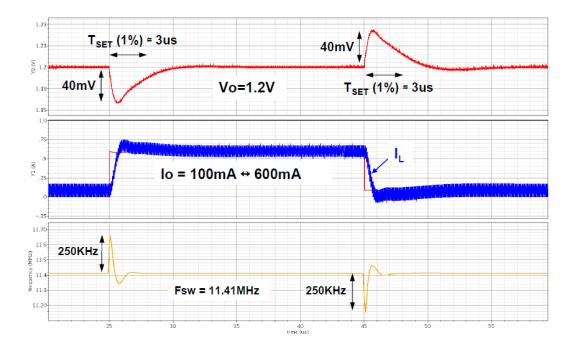

| 5.17 | Transient response at $V_O = 1.2$ V, typical process and 27 deg                                      |     | 95   |  |

| 5.18 | Transient response at $V_O = 1.2$ V, fast process and -40 deg                                        | • • | 96   |  |

| 5.19 | Transient response at $V_O = 1.2$ V, slow process and 27 deg                                         | • • | 96   |  |

| 5.20 | Transient response at $V_O = 0.8$ V, typical process and 27 deg                                      |     | 97   |  |

## Figure

## Page

| 5.21 | Transient response at $V_O = 0.8$ V, slow process and 27 deg    | 98  |

|------|-----------------------------------------------------------------|-----|

| 5.22 | Transient response at $V_O = 1.5$ V, typical process and 27 deg | 98  |

| 5.23 | Efficiency of the TPWM based buck converter vs load current     | 99  |

| 5.24 | Duty Cycle vs phase characteristic of phase subtractor          | 100 |

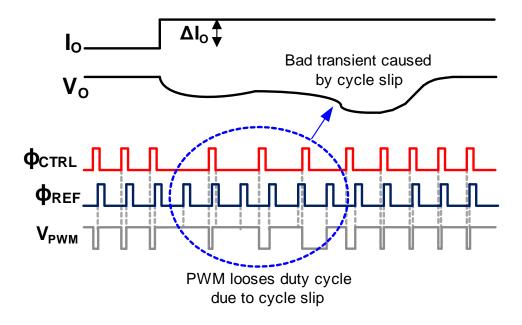

| 5.25 | Duty cycle slipping in TPWM controller                          | 101 |

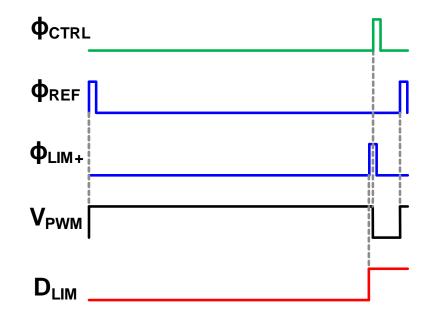

| 5.26 | Duty cycle limit (DCL) logic implemented with TPWM              | 101 |

| 5.27 | Timing diagram showing maximum duty cycle limit                 | 102 |

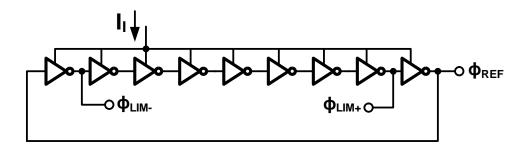

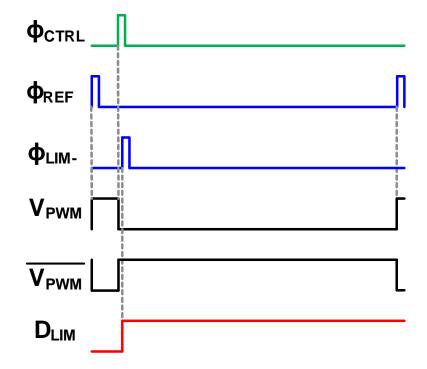

| 5.28 | A 9-stage ring oscillator                                       | 102 |

| 5.29 | Timing diagram showing minimum duty cycle limit                 | 103 |

| 5.30 | Offset correction by using VCO integrator in FLL                | 105 |

| 5.31 | Offset correction using a comparator                            | 106 |

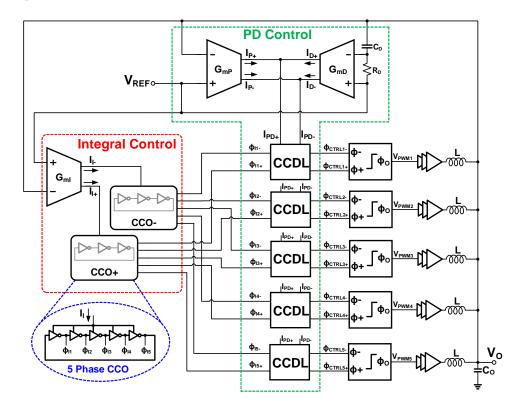

| 5.32 | A multi-phase buck converter using TPWM                         | 107 |

## DIGITALLY ASSISTED CONTROL TECHNIQUES FOR HIGH PERFORMANCE SWITCHING DC-DC CONVERTERS

### CHAPTER 1. INTRODUCTION

### 1.1 Motivation and Research Contribution

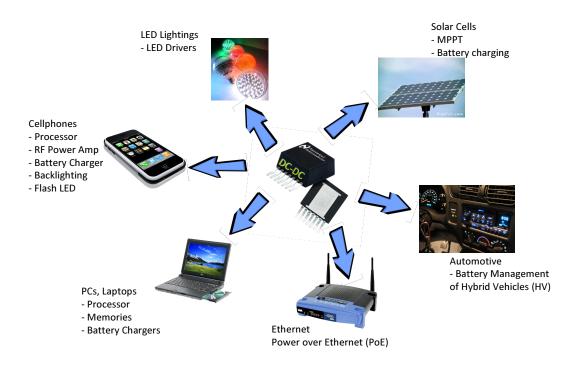

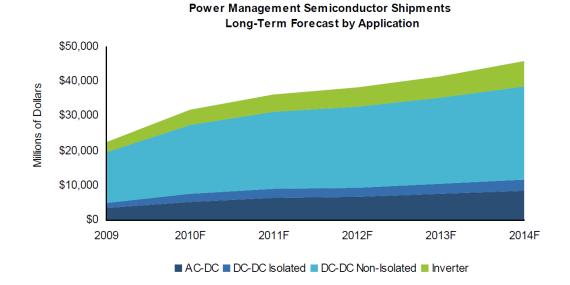

This research is motivated by the growing demand of high performance switching DC-DC converters in the consumer market. As shown in Fig. 1.1, there is hardly any application untouched by a dc-dc converter. According to a study [1] shown in Fig. 1.2, almost one third of \$30bn power market is contributed by the dc-dc converters (voltage regulators) and growing at a rapid pace with the rising demand of solar and LED.

As technology is advancing with an effort of integrating various features in portable and hand-held devices such as smart-phones, tablet PCs and media players, the power density requirement is growing exponentially due to limited board size available on these gadgets. The high efficiency and capability of operating across wide load and input/output voltage make switching dc-dc converters an ideal choice over linear regulators (which require bulky heat sinks due to poor efficiency) to cater this power density need. These switching converters can be implemented with a fixed frequency based pulse width modulation (PWM) or a

Figure 1.1: Various applications requiring dc-dc converters

Figure 1.2: DC-DC Converter market. Source: isupply [1]

variable frequency hysteretic controller. In applications where wide variation in switching frequency is tolerable, hysteretic controller is preferred because of its simpler design and faster dynamic response. However, in noise sensitive applications such as mobile phones and other wireless applications, fixed frequency PWM controllers are mostly used but they are expensive due to external compensation. Since state of the art semiconductor device technologies provide ease of integration and power switches can easily be integrated with the controller on a single chip, the size of a power module is mainly limited by its on-board passive components such as LC filter (inductor and capacitor) and external compensation. In an effort to integrate a PWM controller on a single chip, digital PWM controllers have gained popularity in the recent few years [16] and provided another research platform in the area of power converters. Even though a significant amount of research has been done in this area, the complexity and challenges associated with a digital PWM controller still provide an opportunity for current and future research. For instance, the requirement of high resolution Analog-to-Digital converter and high resolution PWM [20] either limit the switching frequency or require high quiescent current. This research work seeks to address the various issues of state of the art control techniques by providing ingenious solutions.

The first solution is aimed for a buck-boost converter which uses a fully synthesized digital fractional-N controller to solve the mode transition issue and eliminates the need of an external compensation capacitor. The technique is quite effective for applications powered by Lithium-ion batteries such as flash LED drivers which are quite inefficient if not driven by a buck-boost converter [10].

Second design presented in this research provides a cost effective and fully integrated alternative to a fixed frequency PWM controller. The technique is based on a hysteretic converter which resolves the various issues such as wide frequency variation, poor load regulation and large output ripple associated with state of the hysteretic converters.

Although the above two fully integrated controllers save external compensation, the on board LC filter is inevitable due to lack of technology capable of fabricating high power on-chip inductors and high density capacitors. Therefore pushing the converter switching frequency high is the only viable solution to achieve smaller size of passive components. As a matter of fact, the converter switching frequency is rapidly advancing and has surpassed several MHz in the last couple of years. With the present availability of 6MHz-8MHz converter in the market [2]-[3], it will not be surprising to see above 10MHz converter in the near future. Following the latest market trend, third and final design addresses the limitations with high frequency operation of existing control topologies by proposing a 10MHz continuous time PWM controller based on ultra low power and highly integrated time based proportional-integral-derivative (PID) compensator.

### 1.2 Thesis Organization

This thesis is organized as follows: Chapter 2 provides an overview of switching dc-dc converter.

Chapter 3 starts with an introduction of buck-boost converter and challenges associated with the existing designs. A buck-boost converter based on constant ON/OFF time fractional-N digital control is presented in this chapter and design details are discussed. The chapter is concluded with measurement results of the prototype build to demonstrate the proposed technique.

Chapter 4 gives insight of a hysteretic dc-dc converter and analyzes its behavior under different conditions. The various conditions for stable operation of a hysteretic converter are studied. The benefits and drawbacks of both voltage and current mode hysteretic converters are discussed. A hybrid controller comprising of both voltage and current mode is proposed with a scheme for regulating the switching frequency to get the fixed frequency operation.

Chapter 5 introduces the concept of time based PWM controller using time domain signal processing. A proportional-integral-derivative (PID) compensator is realized in time domain using voltage controlled oscillators (VCO) and voltage controlled delay lines (VCDL). Detailed design procedure of a 10MHz buck converter is presented and various design parameters are calculated. Issues with the proposed technique are also discussed with the possible solutions.

Even though the techniques presented in Chapter 4 and 5 were implemented with a buck converter, their application is not limited and can be employed with any type of converter (boost or buck-boost). The designs were demonstrated only for continuous conduction mode (CCM). The standard PFM (pulse frequency modulation) mode can also be implemented with these controllers under discontinuous conduction mode (DCM) to achieve higher efficiency at light load.

## CHAPTER 2. AN OVERVIEW OF SWITCHING DC-DC CONVERTER

### 2.1 Linear vs. Switching Converter

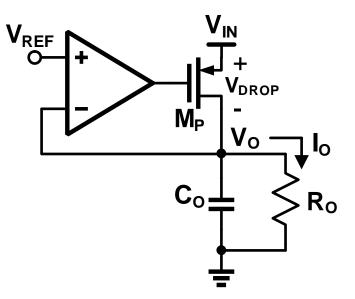

It is a well known fact that switching converters (or regulators) offer superior efficiency over wide range of input and output voltages therefore always preferred over linear regulators. Since a linear regulator, as shown in Fig. 2.1, regulates the output voltage by dropping extra voltage across the pass transistor  $(M_P)$ , it suffers from poor efficiency.

Figure 2.1: A linear regulator

When linear regulators are operated at higher current, the drop-out power is dissipated into heat and requires bulky heat sink. A switching converter on the other hand, by virtue of its operation, does not require a heat sink and despite using external inductor it offers a compact power solution.

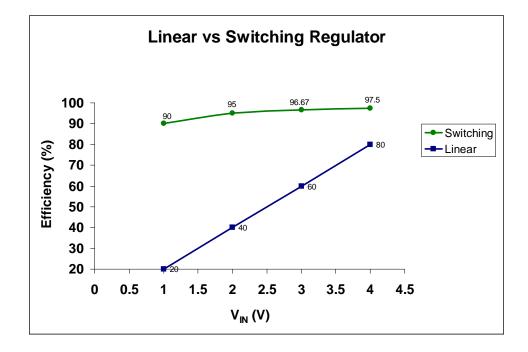

Figure 2.2: Efficiency comparison of switching and linear regulators

Fig. 2.2 shows the efficiency comparison of switching converter with a linear regulator when both are operated at 5V input while output is varied from 1V to 4V at load current of 1A. The difference is quite obvious and it could be noticed that at 1V, 80% of the total power is lost in the linear regulator while switching converter maintains an efficiency of above 90% throughout the entire range. Since the linear regulator efficiency is improved at higher output to input voltage ratio (due to less drop-out voltage), they might be preferred if regulated output voltage is close to input but application is quite limited.

### 2.2 Switching DC-DC Converter

A PWM based dc-dc converter works on the averaging concept of a variable width square pulse or PWM signal. This pulse when passed through a high Q low pass LC filter, all the ac harmonics are suppressed leaving only the the average dc voltage at the output . The output voltage can be regulated simply by controlling the width of the square pulse.

Figure 2.3: Switching action of a dc-dc converter

As shown in Fig. 2.3, the width of square wave can be controlled with the switches  $S_P$  and  $S_N$ . Assuming that the  $V_{SW}$  is at  $V_{IN}$  when switch  $S_P$  is ON,  $S_N$  is OFF and 0 when  $S_N$  is ON,  $S_P$  is OFF then the output voltage  $V_{OUT}$  can be expressed as:

$$V_{OUT} = DV_{IN} \tag{2.1}$$

where D is the duty cycle (a measure of pulse width) expressed as:

$$D = \frac{T_{ON}}{T_{ON} + T_{OFF}} = \frac{T_{ON}}{T_{SW}}$$

(2.2)

and  $T_{SW}$  is the clock period,  $T_{ON}$  is the ON time and  $T_{OFF}$  is the OFF time of the square pulse.

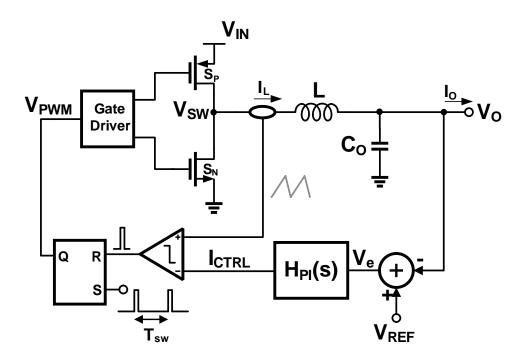

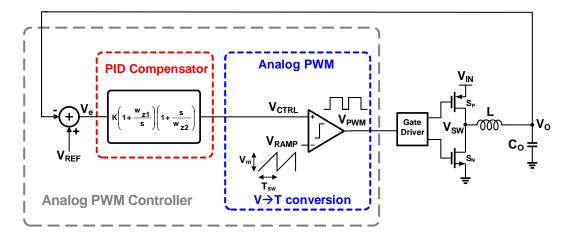

From eq. 2.1, it can be understood that in order to get the constant  $V_{OUT}$ under varying  $V_{IN}$ , D must be changed accordingly. This is usually accomplished by the PWM feedback loop which controls the duty cycle to regulate the output voltage under variable operating conditions. Fig. 2.4 shows the block diagram of a dc-dc converter based on analog PWM control.

Figure 2.4: A PWM controlled switching dc-dc converter

The output voltage  $V_O$  is compared with a fixed reference voltage,  $V_{REF}$ . The resulting error voltage, Ve, is passed through a PID compensator which generates the control voltage,  $V_{CTRL}$ . The PWM signal is generated by comparing  $V_{CTRL}$

with a fixed frequency ramp signal,  $V_{RAMP}$  as shown in Fig. 2.5 and controls the ON/OFF time of power MOSFET switches,  $S_P$  and  $S_N$ .

Figure 2.5: A pulse width modulated signal

### 2.3 Types of DC-DC Converters

Based on input to output conversion ratio, dc-dc converters are mainly classified into three categories.

(1) Buck (Step - Down) Converter: output voltage is always less than or equal to input voltage.

(2) Boost (Step - Up) Converter: output voltage is always higher or equal to input voltage

(3) Buck – Boost Converter: combines the features of both buck and boost hence output voltage could be either equal, lower or higher than the input voltage.

Fig. 2.6 shows the different converters along with their input-output voltage and current relationship with duty cycle.

All these three converters operate on the switching principle where output

Figure 2.6: Different classes of switching dc-dc converters

voltage is controlled by changing the duty cycle. The main difference lies in the power stage where switches are configured differently. In case of synchronous converters, the buck and boost can be used interchangeably by swapping the in-put/output voltages.

### 2.4 Switching Converter Control Techniques

The two most widely used control techniques in switching converters are (1) PWM Control and (2) Hysteretic Control. The main difference is that the PWM control is linear and operates with a fixed frequency as shown in Fig. 2.4.

A hysteretic control on the other hand is non-linear control and does not need any clock as it relies on self oscillations. The feedback loop is much simpler and does not require any compensation but it suffers from wide variation in switching frequency. The details about hysteretic control technique are discussed in Chapter 4.

### 2.5 Voltage Mode vs. Current Mode PWM Control

Depending upon how feedback loop of a dc-dc converter is closed they can be classified into two categories, (1) voltage mode control (VMC) and (2) current mode control (CMC). The buck converter shown in Fig. 2.4 is essentially a VMC converter as it uses only voltage information in the feedback. A current mode converter on the other hand employs both current and voltage information.

Figure 2.7: A current mode controlled dc-dc converter

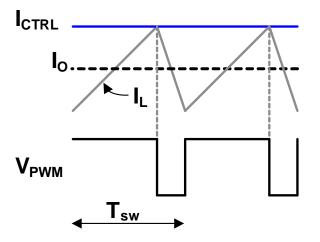

As shown in Fig. 2.7, it has two feedback loops. Unlike an external PWM ramp signal used in voltage mode, the current mode converter uses inductor current,  $I_L$  as a ramp. The peak of this current is compared with a control current

which is generated from error signal processed through a compensator. The PWM signal is set at every edge of the clock period,  $T_{SW}$  and allows the inductor current to ramp up as seen from Fig. 2.8.

Figure 2.8: Pulse width modulation in a peak current mode converter

As soon as this current crosses the control current, the PWM signal is reset. Since feedback loop limits the peak of inductor current, it is called as peak current mode control (in a valley current mode current the valley limited). The current limiting action actually forces the inductor to behave like a constant current source and kills the resonance action of LC filter. The complex LC poles are therefore converted into a single real pole which is only due to the output capacitor,  $C_O$  and load resistor,  $R_O$  and requires only one zero for the loop compensation. A proportional-integral (PI) compensator is therefore used instead of PID which greatly reduces the complexity of control circuitry. The feed-forward action of current loop also offers much better response to line transients as compared to a voltage mode control where line suppression relies on the voltage feedback loop. However, the subharmonic oscillation due limiting only one side of the current (peak or valley) needs to be corrected by ramp compensation. A current mode converter is also quite vulnerable to any noise at the switching node,  $V_{SW}$  and may cause false reset of the PWM signal or even cause unwanted oscillations [8], [9].

### 2.6 Efficiency of A Switching DC-DC Converter

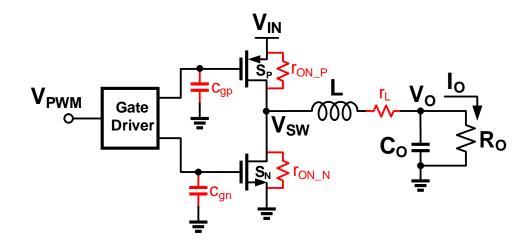

The efficiency of an ideal dc-dc converter is 100% due to the fact that both inductor and capacitor used as output LC filter are lossless. However in practical scenario this is not true and the eq. 2.1 is no longer valid due to losses associated with the power switches and inductor dc resistance (DCR) as shown in Fig. 2.9.

Figure 2.9: Different loss components associated with a dc-dc converter

The relationship between input and output voltages under loss is redefined as:

$$V_{OUT} = DV_{IN} - V_{loss} \tag{2.3}$$

Where  $V_{loss}$  is the voltage drop in the power stage due to losses. Therefore in order to keep the output voltage constant, the duty ratio D must be increased proportionally as loss goes higher. The current drawn from the input supply is expressed as:

$$I_{IN} = DI_O \tag{2.4}$$

Since input current drawn from the supply is proportional to the duty ratio, it could be observed that if losses in the power stage are higher then for the same output power the current drawn from the input supply increases thereby reducing the efficiency of the converter. The efficiency of a dc-dc converter is defined by the expression:

$$\eta = \frac{P_O}{P_{IN}} = \frac{P_{IN} - P_{loss}}{P_{IN}} \tag{2.5}$$

Where  $P_O$  is the delivered output power ,  $P_{IN}$  is the supplied input power and  $P_{loss}$  is the power loss.

The total power loss consists of following components:

$$P_{LOSS} = P_{cond} + P_{sw} + P_{dead} + P_{gate} + P_q \tag{2.6}$$

The conduction loss,  $P_{cond}$  is mainly caused by the resistive losses such as ON resistance of the switches  $(r_{ON_P} \text{ and } r_{ON_N})$  and DCR of the inductor  $(r_L)$  as shown in Fig. 2.9. The conduction loss can be expressed as:

$$P_{cond} = I_O^2 (r_{P_{-}ON}D + r_{N_{-}ON}(1-D) + r_L)$$

(2.7)

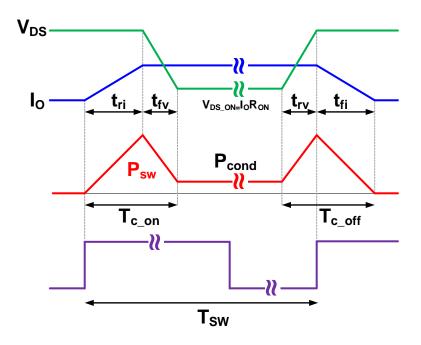

The switching loss,  $P_{sw}$  is usually associated with the switching behavior of MOSFET switches [6] which depends upon various factors such as, parasitic junction capacitance, drain current and voltage across its terminals (Vgs and Vds). The presence of gate resistance and finite gate capacitance causes rise/fall time in

turning ON and OFF the MOSFET. Due to this finite rise/fall time, the MOS-FET exhibits high ON resistance and causes switching loss in the converter. The switching characteristic of a MOSFET is shown in Fig. 2.10. Faster the MOSFET is turned ON or OFF, lesser is the switching loss. The switching loss,  $P_{sw}$  is defined by:

Figure 2.10: Hard switching losses  $(P_{sw})$  in a dc-dc converter

$$P_{sw} = \frac{1}{2} V_{IN} I_O(t_{c\_on} + t_{c\_off}) F_{SW}$$

(2.8)

Where  $t_{c_on}$  and  $t_{c_off}$  are the turn-on and turn-off times of the MOSFETs and  $F_{SW}$  is the switching frequency.

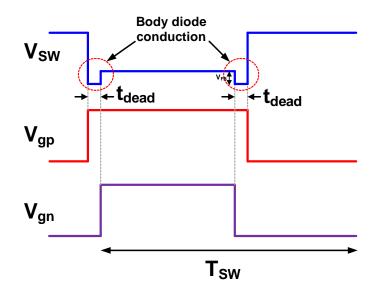

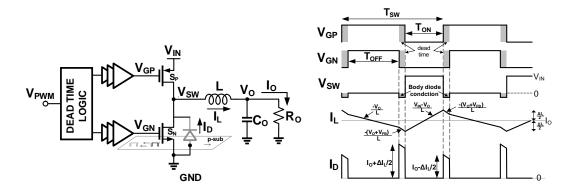

The dead time loss  $P_{dead}$  is due to non-overlap time between top and bottom switches as shown in Fig. 2.11. This dead time  $(t_{dead})$  is needed in order to avoid short circuit due to simultaneous conduction of top and bottom switches. During this dead time, both top and bottom switches are OFF hence the conduction takes

Figure 2.11: Dead time switching losses  $(P_{dead})$  due to body diode conduction

place through body diode of the bottom MOSFET  $(S_N)$ . The loss due to dead time is defined by:

$$P_{dead} = 2V_{FB}I_O t_{dead}F_{SW} \tag{2.9}$$

Where  $V_{FB}$  is the forward bias voltage of the body diode which is  $0.7V \sim 0.8V$ in most of the cases.

The gate switching losses are usually associated with the parasitic gate capacitors ( $c_{gp}$  and  $c_{gn}$ ) of the MOSFET switches and expressed as:

$$P_{gate} = (c_{gp} + c_{gn}) V_{IN}^2 F_{SW}$$

(2.10)

The quiescent loss  $P_q$  is the controller power.

It could be observed from the above equations that both hard switching  $(P_{sw})$  and conduction loss increases with the load current while the gate drive loss is fixed and independent of the load current. At lighter load current, conduction

and switching losses are negligible and gate drive loss starts dominating. When load current is much less compared to the gate switching losses, the converter is quite often operated in the PFM mode where switching frequency is scaled down with the load current to reduce losses. Dynamic FET sizing [7] is another effective technique to reduce the gate switching losses .

### 2.7 Control Loop Dynamics of DC-DC Converter

Transfer function of the LC filter of dc-dc converter shown in Fig. 2.4 is expressed as:

$$H_{LC}(s) = \frac{1}{LC_O^2 s + \frac{L}{R_O}s + 1}$$

(2.11)

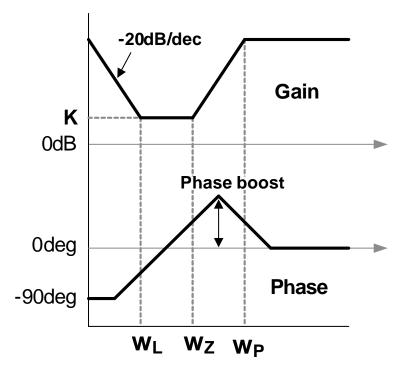

Which exhibits a pair of complex poles causing  $\approx 180^{\circ}$  phase shift around resonance frequency ( $w_O = \frac{1}{\sqrt{LC_O}}$ ) and making the loop unstable. The loop can be stabilized by simply using an integrator which provides the dominant pole compensation and pushes the complex poles out of the unity gain bandwidth (UGB). Although high dc gain of the integrator provides good voltage regulation but this type of compensation limits the loop bandwidth and degrades the transient performance of the converter. For better transient response a proportional-integralderivative (PID) compensator is used in a voltage mode PWM controller. A PID compensator is defined by the following transfer function [4]:

$$H_{PID}(s) = K \frac{\left(1 + \frac{w_L}{s}\right) \left(1 + \frac{s}{w_z}\right)}{1 + \frac{s}{w_p}}$$

(2.12)

The integral term amplifies the error voltage at dc in order to regulate the output voltage around  $V_{REF}$  while the two zeros ( $w_L$  and  $w_Z$ ) provide phase boosting to inhibit the effect of complex poles due to LC filter and provide a sufficient

phase margin around the crossover frequency.  $w_p$  is a high frequency pole used to suppress the high frequency noise due to switching and kept outside the UGB. The overall loop transfer function of a compensated buck converter can be expressed as [4]:

$$T(s) = \frac{V_{IN}}{V_m} H_{PID}(s) H_{LC}(s)$$

(2.13)

Where,  $\frac{V_{LN}}{V_m} = G_{PWM}$  is the gain of PWM modulator and power MOSFET stage. The bode plot of a PID compensator is shown in Fig. 2.12. The location of two zeros ( $w_L$  and  $w_Z$ ) is chosen such that enough phase boost is obtained to suppress the resonance due to LC filter and K is adjusted to get the desired crossover frequency. The detailed design of a PID compensator is discussed in Chapter 5.

Figure 2.12: Bode plot of the PID compensator

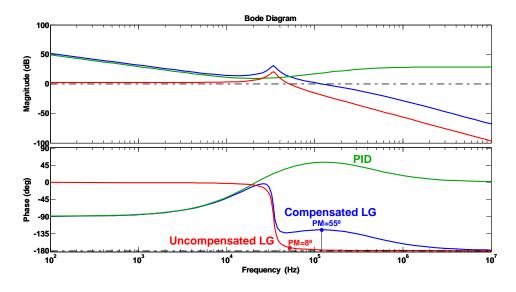

Simulated loop gain and phase response of a an uncompensated and compensated buck converter is shown in Fig. 2.13. The uncompensated loop has phase margin of only  $8^{\circ}$  and therefore unstable.

Figure 2.13: Bode plot of an uncompensated and compensated buck converter

### 2.8 Switching Noise Caused by DC-DC Converter

Just like any other switching circuit, the dc-dc converter has tendency to produce switching noise. There are mainly three types of noise generated by switching converter.

### 2.8.1 Substrate Injection

The substrate noise is caused by the body diode conduction of NMOS switch during dead time. During dead time, the current flows from ground (GND) to the inductor through body diode which is formed between the drain terminal of bottom switch  $(S_N)$  and p-substrate as shown in Fig. 2.14.

Figure 2.14: Substrate noise injection due to body diode conduction

This negative current injection disturbs the substrate potential (which is connected to GND) causing substrate noise. This noise may propagate through the substrate causing issue for the neighboring noise sensitive circuits. To prevent this noise from propagation, the bottom switch should be surrounded by enough substrate contacts connected to GND. This provides a local low resistive path to the substrate noise and prevents it from propagating further. An isolated p-well (in case of deep n-well process) also helps in preventing the substrate noise by completely isolating the body diode of bottom switch from the chip substrate.

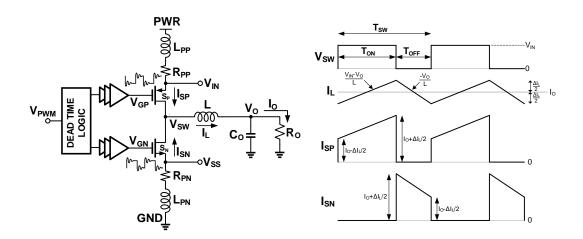

#### 2.8.2 Supply and Ground Bounce

The switching action of  $V_{PWM}$  causes  $S_P$  to connect to the internal supply voltage,  $V_{IN}$  during ON time and  $S_N$  to connect to internal ground, VSS during OFF time causing a switching current drawn from the supply, PWR and ground GND as shown in Fig. 2.15.

Considering the fast turn ON/OFF time of the switches, the finite parasitic inductances ( $L_{PP}$  and  $L_{PN}$ ) associated with power and ground causes large  $L_{dt}^{di}$

Figure 2.15: Supply and Ground noise in a DC-DC converter

noise in  $V_{IN}$  and  $V_{SS}$ . These parasitics inductances, when coupled with parasitic capacitance, also produce resonance and may even cause breakdown of the switches if amplitude of the ringing (due to resonance) is large. Another issue cause by this switching noise is electromagnetic interference (EMI). The problem could be suppressed by reducing the parasitic inductances which is mainly due to the bond wires and board traces. Putting decoupling capacitors between  $V_{IN}$  and  $V_{SS}$  also damps the resonance and helps in reducing noise.

NOTE: In case of a boost converter, the switching action takes place between output and ground so the noise generated in  $V_{IN}$  is not significant.

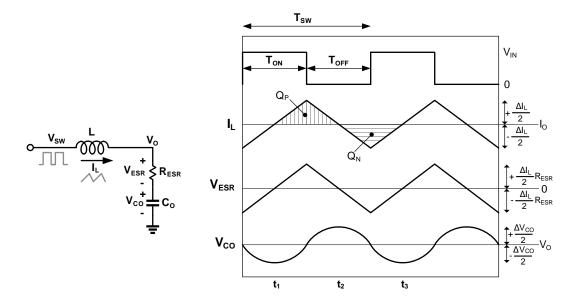

#### 2.8.3 Output Ripple

The finite bandwidth of the output LC filter and capacitor's ESR does not completely filters out the high frequency noise of PWM switching node,  $V_{SW}$  and appears as ripple in the output voltage. This ripple consists of two components, capacitive ripple and ESR ripple as shown in Fig. 2.16.

Figure 2.16: Output voltage ripple of a buck converter

If  $\Delta V_{CO}$  is the capacitor ripple voltage then, output voltage ripple can be expressed as:

$$\Delta V_O(t) = \Delta V_{ESR}(t) + \Delta V_{CO}(t) \tag{2.14}$$

In case of small ESR, the output ripple is mostly dominated by the capacitive component, and pk-pk ripple can be found by charge transfer theorem. The total positive charge stored in the inductor during time  $t_1 - t_2$  is simply the area under triangle,  $Q_P$  i.e.

$$Q_P = \frac{1}{2} \left(\frac{1}{2} T_{SW}\right) \left(\frac{\Delta I_L}{2}\right) = \frac{1}{8F_{SW}} \Delta I_L \tag{2.15}$$

The change in capacitor voltage due to this charge can be given as (using Q = CV):

$$\Delta V_{CO} = \frac{1}{C_O} \frac{1}{8F_{SW}} \Delta I_L \tag{2.16}$$

Substituting inductor ripple current,  $\Delta I_L = \frac{V_{IN} - VO}{L} DT_{SW}$ , the output ripple voltage can be expressed as:

$$\Delta V_O = \frac{V_{IN} D(1 - D)}{8F_{SW}^2 L C_O}$$

(2.17)

Which is the expression for output ripple voltage in case of small ESR.

In case of large ESR, the output ripple is dominated by  $\Delta V_{ESR}$  and can be expressed as:

$$\Delta V_O = \Delta I_L R_{ESR} = \frac{V_{IN} D(1-D)}{F_{SW} L} R_{ESR}$$

(2.18)

Which shows that the output voltage ripple can be controlled by properly choosing  $F_{SW}$ , L and  $C_O$ . Capacitor with low ESR also helps in reducing the output ripple.

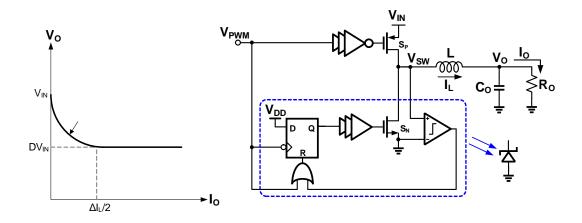

## 2.9 Discontinuous Conduction Mode (DCM)

In a switching dc-dc converter, the direction of inductor current is always positive i.e. towards output if we assume zero inductor ripple current. However, in reality the inductor ripple current, can not be ignored as it may cause the reversal of inductor current when load current is low. Since the inductor ripple current is given by  $\Delta I_L = \frac{V_{IN}-V_O}{L}DT_{SW}$ , the valley of inductor current hits 0 when load current goes to  $\Delta I_L/2$  as shown in Fig. 2.17.

If the converter is operated in continuous conduction mode (CCM), i.e the current is always flowing through the inductor, further reduction in load current

Figure 2.17: Inductor current valley hitting zero in case of light load

causes output capacitor to discharge through bottom switch and reduces the efficiency. In order to prevent this, the current through inductor should be cut-off as soon as the ripple valley hits zero. This could be achieved by detecting the zero crossing voltage at  $V_{SW}$ , which indicates the change of current direction, and turning the bottom switch OFF. The implementation for DCM operation is shown in Fig. 2.18.

Figure 2.18: Implementation of DCM in a buck converter

The condition at which the converter enters DCM can be derived as follows: The valley of inductor ripple current hits zero when  $I_O = \frac{\Delta I_L}{2}$ , i.e.

$$I_O = \frac{1}{2} \frac{V_{IN} - V_O}{L} DT_{SW}$$

(2.19)

Assuming,  $R_O$  is the load resistor then  $I_O = \frac{V_O}{R_O}$ , the above expression can be written as:

$$\frac{V_O}{R_O} = \frac{V_{IN} - V_O}{2L} DT_{SW} \tag{2.20}$$

or

$$V_O = D(V_{IN} - V_O) \frac{R_O T_{SW}}{2L}$$

(2.21)

Term  $\frac{2L}{R_O T_{SW}}$  is defined as  $K_{crit}$  which marks the boundary condition for DCM [4]. The converter remains in CCM as long as  $\frac{2L}{R_O T_{SW}} > K_{crit}$  and output voltage is expressed as  $V_O = DV_{IN}$ . However in DCM the output voltage keeps rising with reduction in load current and expressed as:

$$V_O = \frac{2}{1 + \sqrt{1 + \frac{4K}{D^2}}} \tag{2.22}$$

where  $K = \frac{2L}{R_O T_{SW}}$  and valid for  $K < K_{crit}$

Therefore in DCM, the feedback control should reduce the duty cycle with reducing load current to regulate the output voltage otherwise output voltage will eventually saturate to  $V_{IN}$  as shown in Fig. 2.18.

Usually, the converter is operated in PFM mode in DCM where switching frequency is reduced with load. This helps in maintaining the output regulation when duty cycle is saturated to its minimum value and also reduces the gate switching losses associated with the top and bottom switches.

NOTE: In a non-synchronous converter, the DCM operation is automatic due the bottom diode as it goes reverse biased when for negative inductor current and cuts-off the conduction. The DCM implementation in Fig. 2.18 actually emulates an active diode.

# CHAPTER 3. DIGITAL CONSTANT ON/OFF TIME DELTA-SIGMA FRACTIONAL-N CONTROL FOR BUCK-BOOST CONVERTER

This chapter presents an all-digital Buck-Boost converter that obviates the need for a high resolution DPWM and external compensation capacitor while maintaining high efficiency over a wide input range. We further leverage the highly digital architecture to achieve seamless transitioning between the modes of operation reliably under all operating conditions.

The chapter is organized as follows. Section 3.1 gives an introduction to buckboost dc-dc converter and discusses trade-offs with the existing designs. The concept of constant ON/OFF time is demonstrated in Section 3.2. The proposed architecture is introduced in Section 3.3. Section 3.4 discusses the design of fractional-N controller. The measurement results are shown in Section 3.5.

## 3.1 Introduction to Buck-Boost Converter

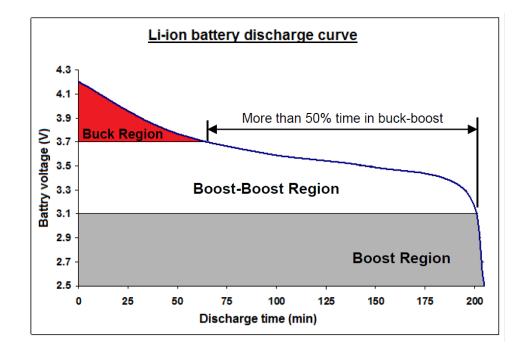

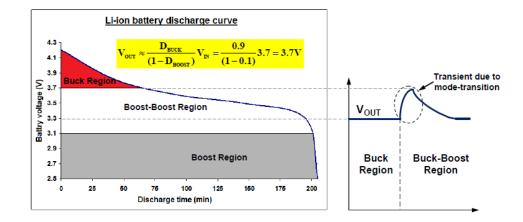

A typical Li-ion battery output voltage, as shown in Fig. 3.1, is at 5.5V when fully charged and drops to 2.7V when fully discharged. Therefore, a buck converter fails to regulate the output at 3.3V over the entire range of battery voltage and using only boost converter on the other hand would be inefficient.

A conventional buck-boost converter [4], [10] shown in Fig. 3.2, implemented using a single duty cycle control, is highly inefficient due to higher average inductor current.

Figure 3.1: Discharging profile of a Li-ion battery

Figure 3.2: Conventional single-mode Buck-Boost converter.

Such type of converter operates in both Buck and Boost modes even when the input voltage is large (or small) enough to operate only in the Buck (or Boost) mode. The impact of such an operation on the converter efficiency can be best understood by referring to the output voltage,  $V_{OUT}$ , and inductor current  $I_L$  in the expressions shown below.

$$V_{OUT} = \frac{D}{1-D} V_{in}$$

and  $I_L = \frac{1}{1-D} I_O$  (3.1)

Since the inductor current is stepped up, the efficiency degrades with increasing duty cycle. For instance, if  $V_{IN} = V_{OUT}$  then the desired duty cycle according to above equation should be, D = 0.5. The corresponding inductor current is 2x of the output load current,  $I_O$ , thereby increasing the conduction losses (as expressed in eq. 2.7 of Chapter 2) by 4 times. This causes a significant drop in the efficiency.

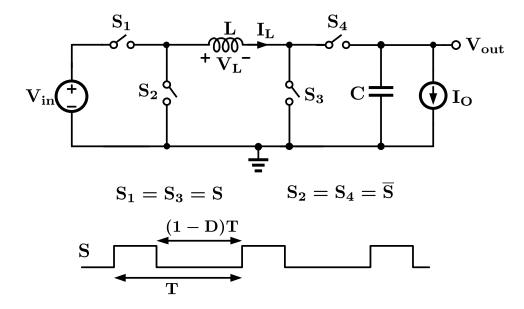

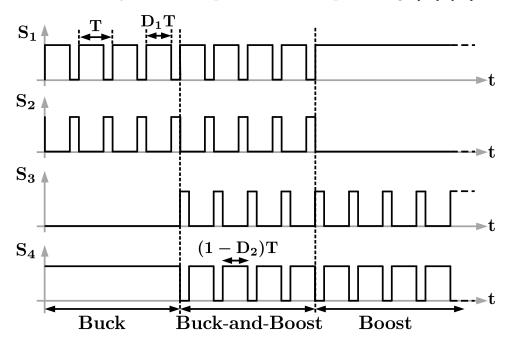

The higher inductor current problem is resolved by independently controlling buck and boost switches (tri-mode operation) as shown in Fig. 3.3 and activating buck-boost mode only when the input is around output voltage [11], [10].

Figure 3.3: Tri-mode converter timing diagram.

Assuming that buck and boost duty cycles are controlled independently, the

Figure 3.4: Overshoot during mode transition in a tri-mode buck-boost converter

eq. 3.1 can be written for a tri-mode buck-boost converter as below:

$$V_{out} = \frac{D_1}{1 - D_2} V_{in}$$

and  $I_L = \frac{1}{1 - D_2} I_O$  (3.2)

Where  $D_1$  is the duty cycle of buck switches (S<sub>1</sub> and S<sub>2</sub>) and  $D_2$  is the duty cycle of boost switches (S<sub>3</sub> and S<sub>4</sub>). A close observation of eq. 3.2 indicates that condition  $V_{IN} = V_{OUT}$  can still be met by limiting  $D_1$  and  $D_2$  to their maximum and minimum values respectively. For instance if  $D_1 = 0.9$  and  $D_2 = 0.1$  then  $V_{OUT}$  becomes equal to  $V_{IN}$  while keeping the inductor current  $\approx I_O$  and reducing the conduction losses. Even though this technique greatly improves the efficiency, there exists a dead zone between boundaries of the operating modes where converter's behavior becomes non-linear and switching is unpredictable [12]. Since the maximum buck duty cycle at the boundary is larger than the required for making smooth transition, it causes a large overshoot in the output voltage (3.4). This overshoot and settling becomes even worse in case of only integral compensated loop due to sluggish response [10].

Therefore ensuring smooth transition between different modes of operation

in tri-mode buck-boost converter becomes challenging. The solutions proposed in [10], [13] address mode transition issue, however the analog nature of the controller makes it susceptible to operating conditions and the controller also requires external compensation capacitor.

This chapter presents an all-digital Buck-Boost converter that obviates the need for a high resolution DPWM and external compensation capacitor while maintaining high efficiency over a wide input range [14]. We further leverage the highly digital architecture to achieve seamless transition between the modes of operation reliably under all operating conditions.

Unlike the conventional PWM method, the proposed converter uses constant ON/OFF time to regulate the output voltage. The next section discusses how a constant ON/OFF time technique helps in minimizing the overall inductor ripple current and leads to the design of proposed Fractional-N digital buck-boost controller.

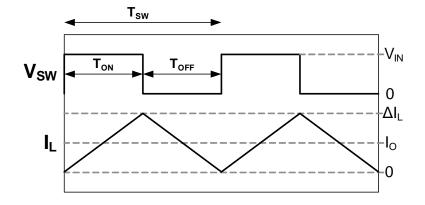

## 3.2 Constant ON/OFF Time Operation

Considering a standard buck converter, the inductor ripple current during ON time  $(T_{ON})$  can be expressed as:

$$\Delta I_{LON} = \frac{V_{IN} - V_{OUT}}{L} T_{ON} \tag{3.3}$$

Where  $V_{IN}$  is the input voltage,  $V_{OUT}$  is the output voltage and L is the inductor value. Inductor ripple current during OFF time  $(T_{OFF})$  is given by

$$\Delta I_{L_OFF} = \frac{V_{OUT}}{L} T_{OFF} \tag{3.4}$$

If converter duty cycle is fixed at 50% and operated at 10MHz ( $T_{ON} = T_{OFF} = 50$ ns), assuming  $L = 1\mu H$  and  $V_{OUT}$  is regulated at 3.3V, the inductor ripple current during ON and OFF time can be calculated as:

$$\Delta I_{L_{ON}} = \Delta I_{L_{OFF}} = \frac{3.3}{1\mu} 50n = 165mA \tag{3.5}$$

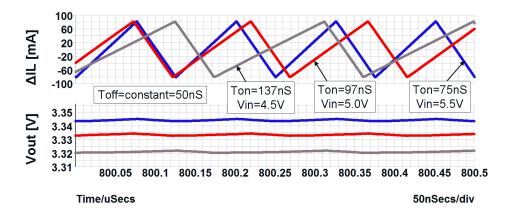

If the required duty cycle is more than 50%, simply making the ON time proportional to  $V_{IN}$  while keeping the OFF time constant time can still regulate  $V_{OUT}$ . Although this would make the switching frequency proportional to  $V_{IN}$ , the voltage across inductor also decreases inversely with ON time making Voltage-Time product constant. Hence inductor ripple current remains constant. This scenario is illustrated in Fig. 3.5 where  $V_{OUT}$  is regulated at 3.3V by making the ON time inversely proportional to  $V_{IN}$  while OFF time is fixed at 50ns.

Figure 3.5: Inductor ripple current and output voltage of a buck converter for constant OFF time (variable ON time).

A similar argument applies for duty cycle less than 50%, where ON time can be fixed at 50ns and OFF time is varied proportional to  $V_{IN}$  for regulating the output voltage. Since inductor ripple current and ESR of the capacitor govern output voltage ripple, as long as switching frequency is significantly higher than LC cutoff, the output voltage ripple still remains lower.

Since regulating the output voltage with only ON time would again require a high resolution scheme similar to that of PWM. Therefore we exploit the benefit of lower inductor ripple current of constant ON/OFF time technique in the proposed converter by using only two duty cycles as discussed next.

#### **3.3** Proposed Architecture

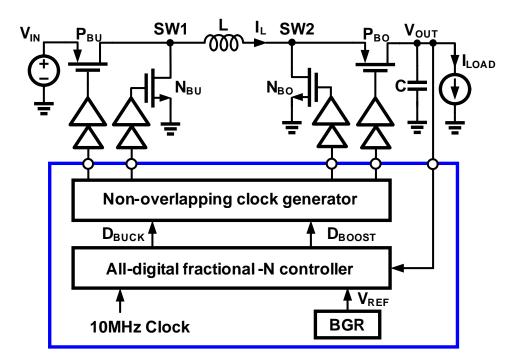

The block diagram of the proposed digitally controlled Buck-Boost converter [14] is shown in Fig. 3.6. Power-FETs,  $P_{BU}$ ,  $N_{BU}$ ,  $P_{BO}$  and  $N_{BO}$  are controlled by two independent control signals,  $D_{BUCK}$  and  $D_{BOOST}$ .

Figure 3.6: Proposed digital Buck-Boost converter

Unlike in a conventional controller, the power-FETs are operated in only two well-defined duty cycles of 50% and 100% or 50% and 0% by keeping either

ON or OFF time constant. Based upon the number (N) of 50% duty cycles, the entire input voltage region is divided into 11 pre-defined states (ST1 to ST11) and stored in a look-up table (LUT) shown in Fig. 3.7. The output is regulated by dithering between the two adjacent states. Since the power-FETs are either ON/OFF for a fixed period of time in every clock cycle, high-resolution digital PWM is not needed. The fixed 50% and 100% (or 0%) duty cycles also makes it possible to operate the converter at much higher frequency (10 MHz) as compared to conventional PWM.

|               | Operating<br>States | Control Code | Fraction<br>N:1  |

|---------------|---------------------|--------------|------------------|

|               |                     |              | 50%Buck:100%Buck |

|               | → ST1               | 0001         | 5:1              |

| Buck          | ST2                 | 0010         | 4:1              |

| Mode          | ST3                 | 0011         | 3:1              |

|               | ST4                 | 0100         | 2:1              |

| $\rightarrow$ | → ST5               | 0101         | 1:1              |

| Buck-         |                     |              | 50%Buck:50%Boost |

| Boost         | ST6                 | 0110         | 1:1              |

| Mode          |                     |              | 50%Boost:0%Boost |

|               | → ST7               | 0111         | 1:1              |

| Boost 1       | ST8                 | 1000         | 2:1              |

| Mode          | ST9                 | 1001         | 3:1              |

|               | ST10                | 1010         | 4:1              |

|               | → ST11              | 1011         | 5:1              |

Figure 3.7: Lookup table for control mapping

Depending upon whether  $V_{IN}$  is higher, equal or lower than  $V_{OUT}$ , the converter automatically switches between modes of operations, as discussed below.

#### 3.3.1 Buck Mode and Boost Mode

The converter operates in buck-mode if  $V_{IN}$  is significantly higher than  $V_{OUT}$ . During this mode,  $D_{BOOST}$  is always 0% and  $D_{BUCK}$  outputs either 50% or 100% duty cycle of a 10MHz clock. Number of 100% buck cycle is always kept one while number of 50% cycles (N) is varied depending upon  $V_{IN}$ . N varies from 1 to 5 making total of five states (ST1 to ST5) in the buck mode.

Similarly when  $V_{IN}$  falls much below  $V_{OUT}$ , the converter operates in boost mode. During boost-mode,  $D_{BUCK}$  is always 100% and  $D_{BOOST}$  outputs the control signal which is one cycle of 0% boost and N cycles of 50% boost. The integer N is varied from 1 to 5 again making a total of five states (ST7 to ST11).

#### 3.3.2 Buck-Boost Mode

If  $V_{IN}$  falls between any value for which either buck or boost mode fails to regulate  $V_{OUT}$  then converter goes into buck-boost mode. The last state of buck (ST5) and first state of boost (ST7) mark the boundaries of the buck-boost region. Only one state (ST6) corresponding to buck-boost is stored in the LUT where both  $D_{BUCK}$  and  $D_{BOOST}$  switch between 50% buck and 50% boost duty cycles respectively every alternate clock period. For any other input voltage in this mode, the output voltage is regulated by dithering between states ST5 and ST6 or ST6 and ST7 depending upon whether  $V_{IN}$  is higher or lower than  $V_{OUT}$ .

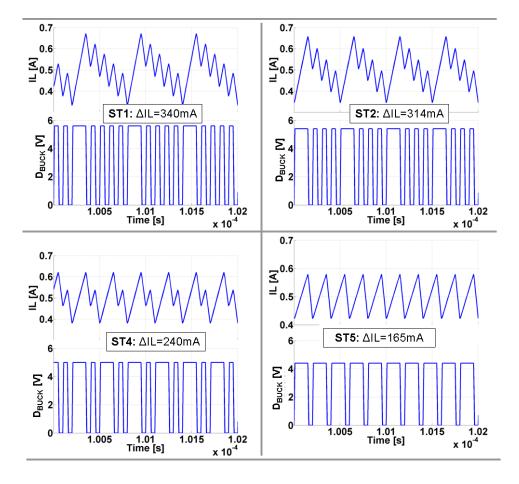

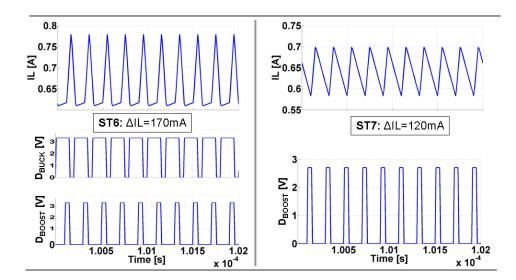

The inductor current profile in various states (ST1-ST5) of buck mode is shown in Fig. 3.8. The average inductor current remains same as load current which is 500mA while maximum peak-to-peak ripple current is 340mA and occurs in state ST1. It should be noted that a fixed frequency PWM converter for the same  $\frac{V_{OUT}}{V_{IN}}$  would require L of  $2\mu H$  in order to achieve the same ripple current. This shows 2X reduction in L by using the proposed constant ON/OFF time method.

Figure 3.8: Profile of inductor current in different states of buck-mode

The inductor currents for buck-boost state (ST6) and boost state (ST7) are shown in Fig. 3.9. The ripple current in both ST6 and ST7 remains low but the average inductor current increases to 650mA due to 1 : 1 boost operation. However, this increase in average current is still 70% lower as compared to a single duty cycle controlled buck-boost converter.

Figure 3.9: Profile of inductor current in buck-boost and boost states

## 3.4 Fractional-N Controller Design

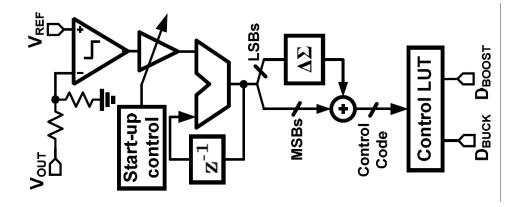

The proposed digital Fractional-N controller is shown in Fig. 3.10. The controller is composed of a comparator, an accumulator, and look-up table (LUT) that outputs  $D_{BUCK}$  and  $D_{BOOST}$ . The comparator detects the sign of the voltage error between the scaled output voltage and the reference voltage ( $V_{REF}$ ) and drives 18-bit digital accumulator. Because of the hard non-linearity introduced by the comparator, the steady state of the converter is a bounded limit cycle that manifests itself as output voltage dithering [20]. To attenuate the resulting output ripple, the lower 7 least significant bits (LSBs) in the accumulator output are dropped. A 1*st*-order digital delta-sigma ( $\Delta\Sigma$ ) modulator truncates the 11 most significant bits (MSBs) to 4 bits which dither between two adjacent states of LUT. This 11-bit to 4-bit conversion greatly simplifies the implementation of fractional-N control circuit.

The LC low-pass filter, following the power stage, suppresses the high fre-

Figure 3.10: Digital Fractional-N controller implemented the proposed buck-boost converter

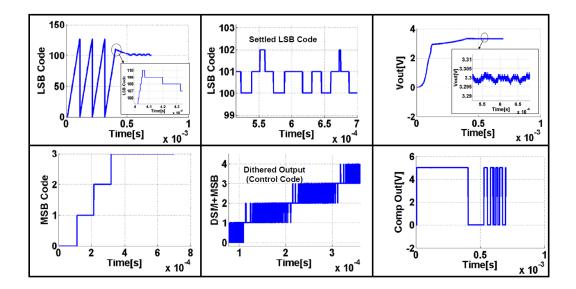

quency quantization error introduced in the fractional-N control and generates a constant DC output voltage. A start-up control circuit increases the loop gain on power up to improve the turn-on time of the converter. The loop gain is reduced as soon as first negative edge of comparator output (Comp Out) occurs indicating that  $V_{OUT}$  had risen up to 3.3V. Once the output is settled, the LSB code toggles between +/-1 LSB. The various control signals and output voltage are shown in Fig. 3.11. For the ease of reading, the control codes are shown in decimal instead of binary in the plot.

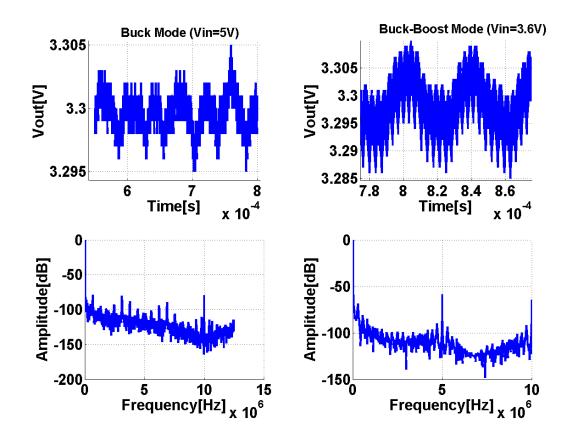

The use of higher switching clock frequency and N:1 dither pattern ensures lower fractional tone at the output that remains well below 50dB and peak to peak ripple remains within 10mV. The output voltage for buck and buck-boost modes of operation with their corresponding frequency spectrum is shown in Fig. 3.12. The amplitude in frequency spectrum is normalized to 3.3V.

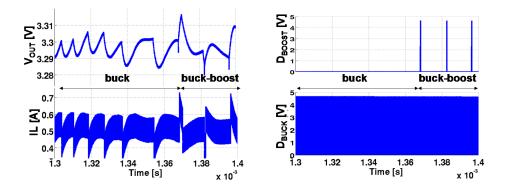

The proposed Fractional-N control also enables seamless transition between modes. The voltage ripple in the output voltage is only 20mV when converter switches from buck mode to buck-boost as shown in Fig. 3.13.

Figure 3.11: Control signals and output voltage of the proposed controller

### 3.5 Experimental Results

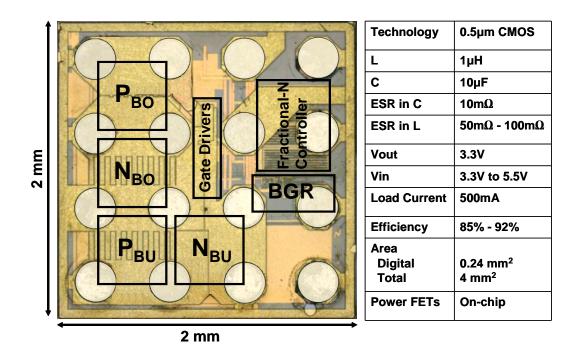

The proposed Buck-Boost DC-DC converter was fabricated in 500nm CMOS process and packaged in a 4x4 micro SMD package. The die size is  $4mm^2$  as shown in Fig. 3.14. Using an off-chip  $1\mu H$  inductor and a  $10\mu F$  capacitor the prototype operates at 10MHz clock frequency and regulates the output voltage to 3.3V.

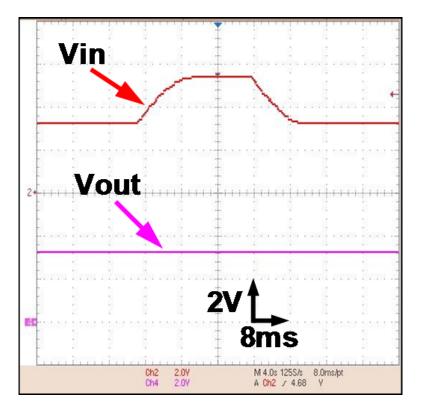

The output voltage, measured by slowly varying the input voltage from 3.3V to 5.5V, shown in Fig. 3.15. illustrates robust regulation immune to any modetransition transients present in conventional analog PWM-controlled buck-boost converters.

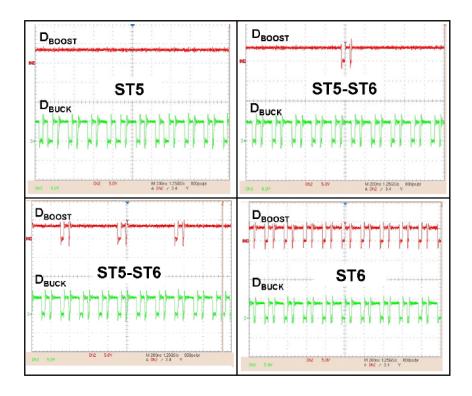

Fig. 3.16 shows the measured switching profile in different operating states. It could be observed that the number of boost cycles is 0 in ST5 (buck mode) and dithers between between ST5 and ST6 as  $V_{IN}$  decreases.

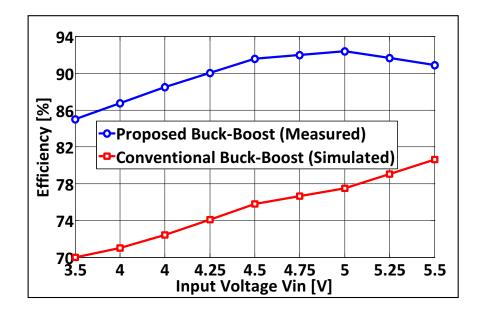

The efficiency plot is shown in Fig. 3.17. The converter achieves efficiency

Figure 3.12: Output voltage and spectrum plot of the proposed converter in buck and buck-boost modes

Figure 3.13: Output waveforms of the proposed converter during buck to buckboost mode transition.

of 85% - 92%. The reduction in efficiency at lower input voltage is mainly due to increased ON resistance of power switches.

Figure 3.14: Die photo of the proposed digital buck-boost converter

Figure 3.15: Measured  $V_{IN}$  versus  $V_{OUT}$

Figure 3.16: Measured switching profile in different operating states

Figure 3.17: Measured efficiency versus input voltage

# CHAPTER 4. FIXED FREQUENCY HYBRID VOLTAGE AND CURRENT MODE HYSTERETIC BUCK CONVERTER

This chapter discusses the design of a hybrid voltage and current-mode hysteretic control which overcomes the issues associated with conventional hysyteretic converters such as wide frequency variation, large output ripple and poor voltage regulation. The chapter is organized as follows. Sections 4.1 and 4.2 give an introduction to voltage and current mode hysteretic dc-dc converters and discuss their advantages and drawbacks. The proposed hybrid hysteretic control is discussed in Section 4.3 along with its design details. The chapter is concluded with the measurement results discussed in Section 4.4.

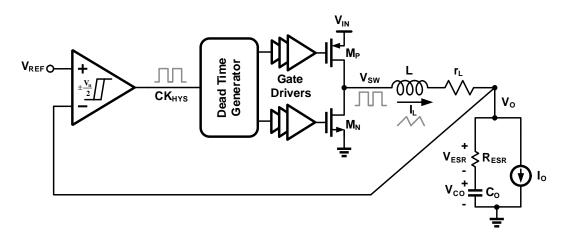

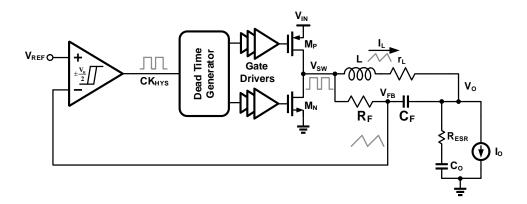

#### 4.1 A Voltage mode Hysteretic DC-DC Converter

Fig. 4.1 shows the simplified circuit of a conventional voltage mode hysteretic dc-dc converter [21]. The main advantage of the converter is its simplicity as it requires only a comparator in the feedback control and no additional compensation circuit is needed. The ability to respond faster (because of no sampling and compensation loop delays) to a load transient makes the converter an attractive choice over PWM based converters for applications that require stringent transient response such as powering microprocessors, solid state driver and RF power amplifiers. The output voltage of a hysteretic converter is regulated in the same manner as of PWM converter by changing the ON time (duty cycle) of the switching clock

and expressed as:

$$V_O = D V_{IN} \tag{4.1}$$

where D is the duty cycle.

Figure 4.1: A voltage mode hysteretic converter.

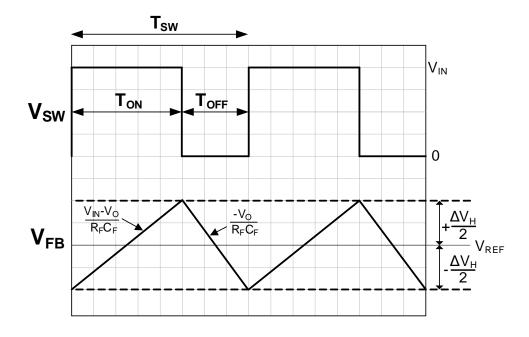

The switching behavior of the hysteretic converter is shown in Fig. 4.2. Unlike a PWM based converter which uses a fixed frequency switching clock, a hysteretic converter does not require any clock. A closer look at Fig. 4.1 indicates that a hysteretic converter resembles an RC relaxation oscillator where RC filter is replaced by an LC filter. Since it relies on self oscillation, the switching frequency depends on various circuit parameters and given by [25]

$$F_{SW} = \frac{V_{IN}D(1-D)R_{ESR}}{\Delta V_H L} \tag{4.2}$$

where L is the inductor value,  $R_{ESR}$  is the equivalent series resistance of the output capacitor,  $C_O$ , and  $\Delta V_H$  is the hysteresis of the comparator.

Figure 4.2: Switching behavior of a hysteretic converter.

### 4.1.1 Stability of a Hysteretic DC-DC Switching Converter

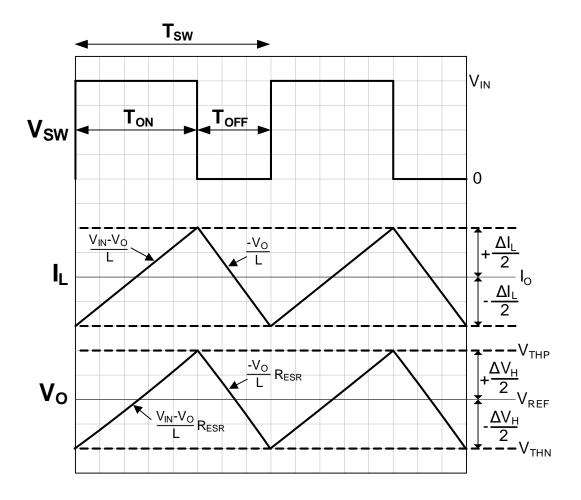

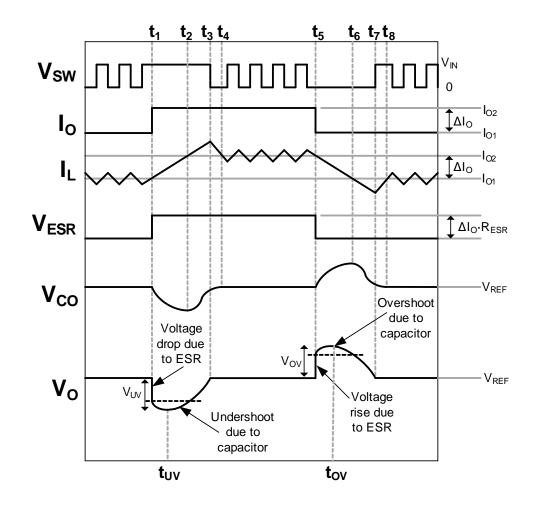

Since operation of a hysteretic converter strongly relies on the output ripple (sometimes also called ripple converter), it becomes important to analyze the ripple and how different circuit parameters affect its behavior. Referring again to Fig. 4.1, the output voltage consists of two components: capacitor voltage,  $V_{CO}$  and ESR voltage  $V_{ESR}$  as shown in Fig. 4.3. If  $\Delta V_{CO}$  is the capacitor ripple voltage then,

output voltage ripple can be expressed as:

$$\Delta V_{OV}(t) = V_{ESR}(t) + \Delta V_{CO}(t) \tag{4.3}$$

Voltage across ESR is given by

$$V_{ESR}(t) = \Delta I_L(t) R_{ESR} \tag{4.4}$$

$I_L(t)$  is the inductor ripple current given by

$$\Delta I_L(t) = \Delta I_L(0) + \frac{V_L}{L}t \tag{4.5}$$

where  $\frac{V_L}{L}$  is the inductor current slope  $(V_L = V_{IN} - V_O \text{ during } T_{ON} \text{ and}$  $V_L = -V_O \text{ during } T_{OFF}$ ). Substituting eq. 4.5 in eq. 4.4, we get

$$V_{ESR}(t) = \left(\Delta I_L(0) + \frac{V_L}{L}t\right) R_{ESR}$$

(4.6)

The capacitor ripple voltage can be expressed as:

$$\Delta V_{CO}(t) = \frac{1}{C_O} \int \left( \Delta I_L(0) + \frac{V_L}{L} t \right) dt$$

(4.7)

Substituting eq. 4.7, after integrating, and eq. 4.6 into eq. 4.3, we get

$$\Delta V_O(t) = \Delta I_L(0) R_{ESR} + \left(\frac{V_L}{L} R_{ESR} + \frac{\Delta I_L(0)}{C_O}\right) t + \frac{1}{2} \frac{V_L}{LC_O} t^2$$

(4.8)

which is the expression for output ripple voltage in the presence of ESR. The condition for ripple peak/valley can be obtained by differentiating eq. 4.8 w.r.t. time and equating to 0, which gives

$$t_{peak,valley} = -\frac{\Delta I_L(0)}{V_L} L - R_{ESR} C_O \tag{4.9}$$

where  $t_{peak}$  and  $t_{valley}$  are measured with reference to falling and rising edge of the PWM signal, respectively.

Figure 4.3: Ripple of a hysteretic converter.

Since ripple peak will occur during  $T_{OFF}$  (due to phase lag) and  $V_L = -V_O$ ,  $\Delta I_L(0) = \frac{1}{2} \frac{V_O}{L} T_{OFF}$  during OFF time, eq. 4.9 can be re-written for peak as:

$$t_{peak} = \frac{1}{2}T_{OFF} - R_{ESR}C_O \tag{4.10}$$

Similarly ripple valley will occur during  $T_{ON}$  and  $V_L = V_{IN} - V_O$ ,  $\Delta I_L(0) = \frac{1}{2} \frac{V_{IN} - V_O}{L} T_{ON}$  during ON time, eq. 4.9 can be re-written for valley as:

$$t_{valley} = \frac{1}{2}T_{ON} - R_{ESR}C_O \tag{4.11}$$

In order to bound the output ripple between hysteresis window, both  $t_{peak}$ and  $t_{valley}$  should be zero i.e. t=0 in eq. 4.8 will make the ripple voltage same as voltage across ESR which is in-phase with the inductor ripple current and bound it within the hysteresis window (assuming no delay in the comparator). From eq. 4.10, the condition for stable operation during  $T_{ON}$  i.e.  $t_{peak} = 0$  will be

$$\frac{1}{2}T_{OFF} \leq R_{ESR}C_O \quad \text{or} \quad \frac{1}{2}(1-D)T_{SW} \leq R_{ESR}C_O \tag{4.12}$$

and from eq. 4.11, the condition for stable operation during  $T_{OFF}$  i.e.  $t_{valley} = 0$  will be

$$\frac{1}{2}T_{ON} \le R_{ESR}C_O \quad \text{or} \quad \frac{1}{2}DT_{SW} \le R_{ESR}C_O \tag{4.13}$$

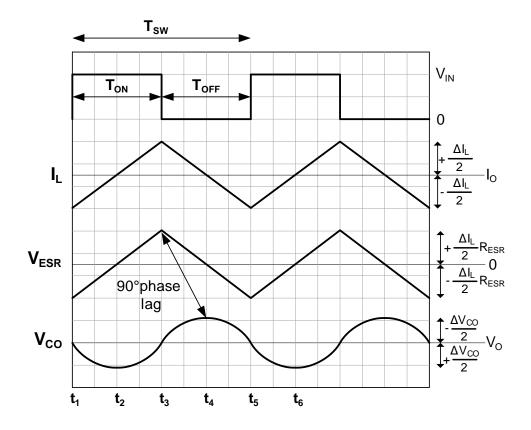

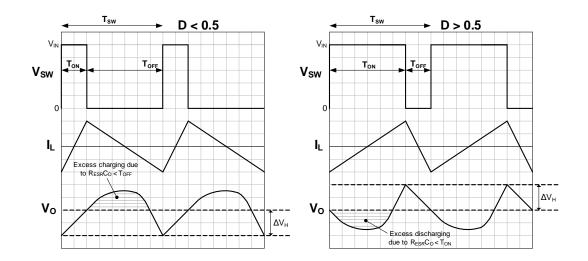

It is observed from eq. 4.12 and eq. 4.13 that the RC time constant should be more than half of the ON or OFF time for stable operation[23]. If this condition is not met then ripple will no longer be bounded between the hysteresis window and the converter becomes uncontrollable. It should also be noticed that if these conditions are satisfied only for D = 0.5 then no peaks are observed for higher duty cycle but it causes a valley in the output and vice versa for the lower duty cycle as shown in Fig. 4.4. The converter under such condition behaves like a single bound hysteretic converter and introduces dc error in the output voltage. Therefore ideal condition for stable operation across entire range of duty cycle (D = 0 to D = 1)is

$$\frac{1}{2}T_{sw} \le R_{ESR}C_O \tag{4.14}$$

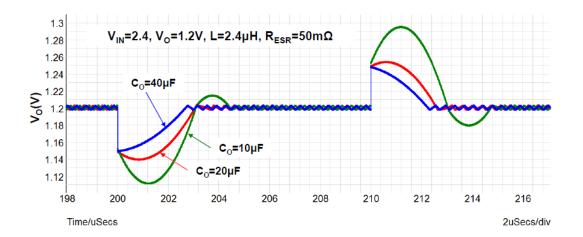

Equation 4.14 shows that either a large ESR or large output capacitor is required for stable operation of a hysteretic converter. For instance, if the converter is designed to operate at switching frequency of 1MHz with  $C_O = 10\mu F$ , the required ESR would be  $50m\Omega$ . Even though large ESR ensures stability, it drastically affects the transient response as discussed next.

Figure 4.4: Offset in the output ripple due to lower  $R_{ESR}C_O$ .

## 4.1.2 Transient Response of a Hysteretic DC-DC Switching Converter

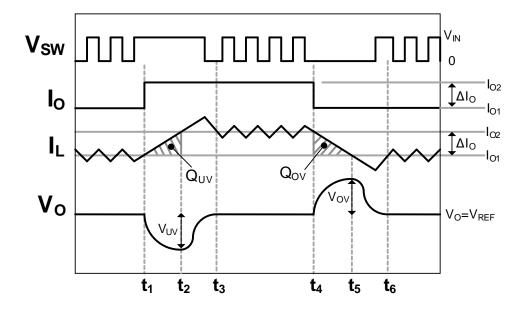

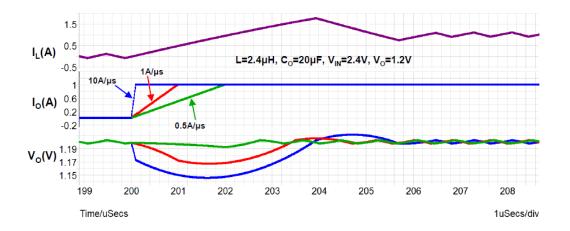

In order to understand the transient behavior of a hysteretic converter, lets first analyze the transient response of an ideal switching converter and then see how it gets affected by various circuit parameters of a hysteretic converter. Fig. 4.5 shows the load transient response of an ideal converter [24] depicting the behavior of output voltage,  $V_O$  and inductor current,  $I_L$  under a sudden change in the output load current,  $I_O$ . Suppose that the output voltage is initially regulated at  $V_{REF}$  and current load step of  $\Delta I_O$  is applied at  $t = t_1$ . Since we have assumed an ideal converter, it responds quickly to the perturbation applied at the output and keeps the switch  $M_P$  ON until the output voltage is recovered. Due to the slow rate of change of inductor current, the extra current due to change in load is drawn from the output capacitor  $C_O$  between the time duration  $t_1 - t_2$  until the inductor current reaches to the final value of  $I_O$  i.e.  $I_{O2}$ . This slow rate of change in the inductor current causes an undershoot  $V_{UV}$  in the output voltage whose value depends upon the size of the capacitor and how quickly the inductor current is recovered, therefore it is a function of inductor current slope. If  $V_{IN}$  is the input voltage and L is the inductor value then change in the inductor current is given by

Figure 4.5: Transient response of an ideal buck dc-dc converter.

$$\Delta I_O = \frac{V_{IN} - V_O}{L} \Delta t \qquad \text{where } \Delta t = t_2 - t_1 \tag{4.15}$$

or

$$\Delta t = \frac{\Delta I_O}{V_{IN} - V_O} L$$

(4.16)

The average charge,  $Q_{UV}$  stored in the inductor between  $t_1 - t_2$  is given by area under the triangle as:

$$Q_{UV} = -\frac{1}{2}\Delta t \Delta I_O \tag{4.17}$$

Substituting  $\Delta t$  from eq. 4.16, we get

$$Q_{UV} = -\frac{1}{2} \frac{\Delta I_O^2}{V_{IN} - V_O} L$$

(4.18)

Since charge stored in the inductor should be transferred to capacitor  $C_O$ , the change in voltage across  $C_O$  will be