### AN ABSTRACT OF THE DISSERTATION OF

<u>Jinjin He</u> for the degree of <u>Doctor of Philosophy</u> in <u>Electrical and Computer Engineering</u> presented on <u>April 19, 2010</u>.

Title: Efficient Decoder Design for Error Correction Codes

Abstract approved:

Huaping Liu

Zhongfeng Wang

Error correction codes (ECCs) have been widely used in communication systems and storage devices. Nowadays, the rapid development of integrated circuit technologies makes feasible the implementation of powerful ECCs such as turbo code and low-density paritycheck (LDPC) code. However, these high-performance codes require complex decoding algorithms, resulting in large hardware area and high power consumption. Furthermore, some of these decoders require an iterative decoding process, which leads to a long decoding latency. Therefore, low-complexity, low-power and high-speed very-large-scale integration (VLSI) architecture design for the ECC decoder is of great importance. This dissertation focuses on efficient VLSI implementation for the decoders of convolutional codes and two advanced coding schemes based on convolutional code: trellis-coded modulation (TCM) and convolutional turbo code (CTC).

The first part of this dissertation is dedicated to low-complexity, low-power decoders design for a 4-dimensional, 8-ary phase-shift keying (4-D 8PSK) TCM system. We propose a low-complexity architecture for the transition-metric unit (TMU) to reduce the hardware area without performance loss. Then, a power-efficient scheme by applying T-algorithm on branch metrics (BMs) is proposed for the Viterbi decoder (VD) embedded in the 4-D 8PSK TCM decoder. Unlike the conventional T-algorithm, the proposed scheme does not affect the clock speed of the decoder. Finally, a hybrid T-algorithm is developed by applying T-algorithm on both BMs and path metrics (PMs), which reduces significantly more computations than the conventional T-algorithm applied on PMs.

The VLSI design for VDs has been an active research area for decades. In the second part of the dissertation, we extend our research to a more general topic of VDs, where novel architectures are explored to efficiently reduce the power consumption, while still maintaining a high decoding speed and a low decoding latency.

CTCs are constructed from parallel convolutional encoding of the same message in different sequences and have the error-correcting capability near the Shannon bound. Practical decoding schemes normally require an iterative decoding process employing the soft-in soft-out (SISO) decoder. The third part of this dissertation is focused on the SISO decoder design for double-binary (DB) CTCs. We propose a low-complexity, memoryreduced architecture by partitioning BMs into two independent portions: information metrics and parity metrics. Furthermore, high-speed recursion architectures for logarithm domain maximum *a posteriori* probability (log-MAP) algorithm are proposed to increase the decoding speed by algorithmic approximation and bit-level optimization. ©Copyright by Jinjin He April 19, 2010 All Rights Reserved Efficient Decoder Design for Error Correction Codes

by

Jinjin He

# A DISSERTATION

submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Presented April 19, 2010 Commencement June 2010 Doctor of Philosophy dissertation of Jinjin He presented on April 19, 2010

APPROVED:

Co-Major Professor, representing Electrical and Computer Engineering

Director of the School of Electrical Engineering and Computer Science

Dean of the Graduate School

I understand that my dissertation will become part of the permanent collection of Oregon State University libraries. My signature below authorizes release of my dissertation to any reader upon request.

Jinjin He, Author

# ACKNOWLEDGEMENTS

First, I would like to express my sincere gratitude to my advisors, Prof. Huaping Liu

at Oregon State University and Dr. Zhongfeng Wang at Broadcom Corporation for their invaluable advice, incessant guidance, continuous encouragement, and financial support throughout my Ph.D. career at Oregon State University. Their broad knowledge, rigorous working attitude and eagerness for new technology are always my model to follow. I am also very grateful to their understanding and caring to my study and life. I can not finish my dissertation successfully without their help.

I am deeply indebted to Dr. Bella Bose, Dr. Ben Lee, Dr. Patrick Chiang, Dr. Kagan Tumer and Dr. Thomas Schmidt for their great efforts and significant amount of time to serve on my Ph.D. committee.

I would like to thank all my friends and colleagues at Oregon State University for their friendships and support. My special thanks go to Dr. Zhiqiang Cui, Dr. Qingwei Li, Lupin Chen and Ruiqing Ye for many useful discussions and help.

Finally, I would like to express my deepest love and appreciation to my parents and my husband, to whom this dissertation is dedicated, for their constant encouragement, support and unconditional love.

# TABLE OF CONTENTS

|    |                                     | Ī                                                                                                                                     | Page                              |

|----|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| 1. | INTI                                | RODUCTION                                                                                                                             | 1                                 |

|    | 1.1.                                | Overview                                                                                                                              | 1                                 |

|    | 1.2.                                | Summary of Contributions                                                                                                              | 2                                 |

|    |                                     | <ul> <li>1.2.1 A low-complexity TMU for a 4-dimensional TCM decoder</li> <li>1.2.2 The <i>T</i>-algorithm on branch metrics</li></ul> | $2 \\ 3 \\ 3 \\ 4 \\ 4 \\ 4 \\ 5$ |

|    | 1.3.                                | Organization of the Dissertation                                                                                                      | 5                                 |

| 2. | ERR<br>2.1.<br>2.2.<br>2.3.<br>2.4. | OR CORRECTION CODES                                                                                                                   | 7<br>8<br>12<br>16<br>21          |

| 3. | AN I                                | EFFICIENT VLSI ARCHITECTURE FOR THE 4-D TCM DECODER .                                                                                 | 22                                |

|    | 3.1.                                | System Overview                                                                                                                       | 22                                |

|    | 3.2.                                | Encoder Design                                                                                                                        | 23                                |

|    | 3.3.                                | Decoder Design.3.3.1 Literature review3.3.2 Low-complexity TMU design3.3.3 T-algorithm on BMs                                         | 26<br>27<br>30<br>37              |

|    |                                     | 3.3.4 Hybrid $T$ -algorithm                                                                                                           | 44                                |

# TABLE OF CONTENTS (Continued)

|    |      |                                                             | Page                         |

|----|------|-------------------------------------------------------------|------------------------------|

|    | 3.4. | An FPGA implementation for the decoder                      | 47                           |

|    | 3.5. | Conclusion                                                  | 49                           |

| 4. | LOW  | -POWER VITERBI DECODER DESIGN                               | 50                           |

|    | 4.1. | A High-Speed Low-power Viterbi Decoders for High-Rate Codes | 50                           |

|    |      | <ul> <li>4.1.1 Literature review</li></ul>                  | $50 \\ 51 \\ 54 \\ 63 \\ 65$ |

|    | 4.2. | Optimal Memory Organization for Viterbi Decoders            | 67                           |

|    |      | <ul> <li>4.2.1 Literature review</li></ul>                  | 68<br>71<br>74<br>75<br>76   |

|    | 4.3. | Conclusion                                                  | 78                           |

| 5. |      | I-SPEED MEMORY-REDUCED SISO DESIGN FOR DUO-BINARY TUF<br>E  | 2BO<br>80                    |

|    | 5.1. | literature Review                                           | 80                           |

|    | 5.2. | System Overview                                             | 82                           |

|    | 5.3. | Memory-Reduced SISO Decoder                                 | 87                           |

|    |      | <ul> <li>5.3.1 Analysis of branch metrics</li></ul>         | 87<br>88<br>92<br>93<br>94   |

# TABLE OF CONTENTS (Continued)

|    |      | 1 age                                            |

|----|------|--------------------------------------------------|

|    | 5.4. | High-speed Architecture for TL log-MAP algorithm |

|    |      | 5.4.1 Proposed Scheme-I                          |

|    |      | 5.4.2 Proposed Scheme-II                         |

|    |      | 5.4.3 Implementation result                      |

|    | 5.5. | Conclusion                                       |

| 6. | CON  | CLUSIONS AND FUTURE WORK 106                     |

|    | 6.1. | Conclusions                                      |

|    | 6.2. | Future Work 108                                  |

| BI | BLIO | GRAPHY 110                                       |

| AF | PENI | DIX                                              |

# Page

# LIST OF TABLES

| Tab | <u>ole</u>                                                 | Page |

|-----|------------------------------------------------------------|------|

| 2.1 | Rate 1/2 maximum free distance codes                       | 10   |

| 3.1 | Grouping of the candidates for BM 0000                     | 34   |

| 3.2 | Grouping of the candidates for BM 0001                     | 36   |

| 3.3 | Grouping of the candidates for BM 1000                     | 37   |

| 3.4 | Grouping of the candidates for BM 1001                     | 38   |

| 3.5 | Computational complexity comparision for $RM=11/12$ case   | 38   |

| 3.6 | Computational complexity comparision for all cases         | 39   |

| 3.7 | Synthesis results for TMU                                  | 39   |

| 3.8 | Synthesis results for ACSU with several schemes            | 43   |

| 3.9 | Synthesis results for TCM decoder                          | 48   |

| 4.1 | Synthesis results of pre-computation scheme                | 63   |

| 4.2 | Truth table of 64-to-6 priority encoder                    | 64   |

| 4.3 | Truth table of 4-to-2 priority encoder                     | 65   |

| 4.4 | Power Estimation results                                   | 67   |

| 4.5 | Decoding latency and the implementation complexity for SMU | 77   |

| 5.1 | Summary of the computational overhead                      | 93   |

| 5.2 | Summary of the memory size                                 | 95   |

| 5.3 | Comparison for several architectures                       | 104  |

| AI  | $2 \times 8$ PSK signal set partitioning                   | 118  |

| AII | $4 \times 8$ PSK signal set partitioning                   | 119  |

# EFFICIENT DECODER DESIGN FOR ERROR CORRECTION CODES

# 1. INTRODUCTION

## 1.1. Overview

Error correction codes (ECCs) have been widely used in a variety of modern telecommunication and electronic systems [1]. Historically, very-large-scale integration (VLSI) technique plays an important role for the application of ECCs. In the mid-20th century, two powerful ECCs – Reed-Solomon codes [2] and low-density parity-check (LDPC) codes [3]– were discovered, both of which require very complicated decoding algorithms. However, at that time, no hardware was capable of handling such complex computations. Consequently, these codes have been forgotten for a long time. With the rapid development of VLSI technology later last century, implementation of very complex algorithms becomes feasible. Thus, these codes were rediscovered in the late 1990s [1]. Since then, the VLSI architecture design for the decoders of ECCs has become a hot research area.

Our research focuses on efficient VLSI architecture design and implementation for the decoders of convolutional codes, trellis coded modulation and convolutional turbo codes.

Convolutional code is one of the two major groups of ECCs, for which the Viterbi algorithm is known to be the optimal decoding method. Therefore, Viterbi decoders are widely used in modern communication systems and storage systems. Research on Viterbi decoder architectures has focused on the add-compare-select unit (ACSU) and survivor memory unit (SMU) [4]. ACSU is the bottleneck for high-speed implementations and SMU is the key unit in determining the overall power consumptions.

Trellis coded modulation, (TCM) which typically uses high-rate convolutional codes, is a modulation scheme that allows efficient transmission of information over band-limited channels. In the literature, very few papers have dealt with the implementation issues of TCM decoders. The transition metric unit (TMU) and the Viterbi decoder are the two major modules in a TCM decoder.

Convolutional turbo code (CTC) is a high-performance code that could approach the Shannon bound in theory. However, the iterative decoding for CTCs requires a large amount of memories to store intermediate results. Therefore, memory-reduced architectures for CTC decoders are of great interest. On the other hand, high-speed recursion architecture design is very important for CTC decoders since it is the bottleneck for highspeed implementation. Extensive work has been done on efficient recursion architectures with sub-optimal decoding methods [5–7].

In this dissertation, we address various VLSI design issues and develop efficient approaches to reduce the memory requirement, lower the computational complexity/power consumption, and increase the decoding speed of the decoders for the aforementioned ECCs.

### **1.2.** Summary of Contributions

The main contributions of this dissertation are summarized as follows:

### 1.2.1 A low-complexity TMU for a 4-dimensional TCM decoder

The main difference between the trellis diagrams of a TCM system and a normal convolutional coded system is that, in the former, there are parallel paths between state transitions, which extend from one state and end at the same state. Therefore, before performing Viterbi decoding, a transition metric unit (TMU) is used to find the optimal paths among each group of the parallel paths as the branch metrics (BMs). Theoretically, the BM for a soft-decision VD in multi-dimensional TCM is represented as the sum of the Euclidian distance from each dimension of the signal sets [8]. In a multi-dimensional TCM decoder, the TMU could be very complex. We propose a new architecture for TMU, which reduces the computational complexity to about 1/3 of an existing low-complexity architecture presented in [9] while the bit-error-rate (BER) performance is not compromised [10].

#### 1.2.2 The *T*-algorithm on branch metrics

TCM typically employs high-rate convolutional codes. Unlike low-rate codes (e.g., 1/2, 1/3) that have 2 incoming paths for each state, high-rate convolutional codes generate many paths in state transitions. When applying Viterbi decoding on these codes, more branch metrics (BMs) are involved. Motivated by the conventional *T*-algorithm, we found that eliminating redundant additions is an effective way to reduce computational complexity. Therefore, the *T*-algorithm could be applied on BMs, instead of on path metrics (PMs) [11]. Compared with conventional *T*-algorithm on PMs, which will significantly reduce the clock speed due to a maximum/minimum value searching in the add-compare-select (ACS) loop, the proposed *T*-algorithm on BMs removes the searching operation from the feed-back loop so that the clock speed is not affected.

### 1.2.3 The hybrid *T*-algorithm

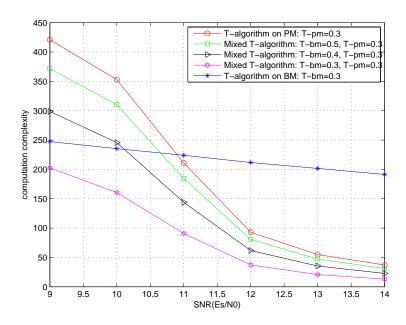

The proposed T-algorithm on BMs not only provides an alternative to the conventional T-algorithm on PMs, but also gives insights leading to techniques that can further reduce computations. Based on this, we develop a hybrid T-algorithm for VD by applying T-algorithm on both BMs and PMs [11]. Simulation results show that computations can be reduced by as much as 50% from the conventional T-algorithm applied on PMs.

# 1.2.4 A high-speed, low-power Viterbi decoder for high-rate convolutional codes

As we mentioned in Section 1.2.2, conventional T-algorithm on PMs suffers from a decreased clock speed. There have been several papers that suggest using the estimated value, instead of finding the accurate one, during each cycle to overcome the speed drawback of conventional T-algorithm. However, these schemes suffer from a significant performance loss when applied on high-rate convolutional codes. Thus we propose a precomputation architecture to speed up the decoding process with no performance loss from the conventional T-algorithm, at the expense of a small computation overhead [12]. ASIC synthesis and power estimation of the complete VD have verified the low-power property of the proposed architecture [13].

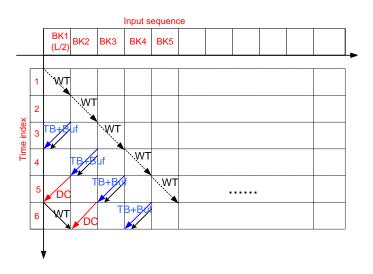

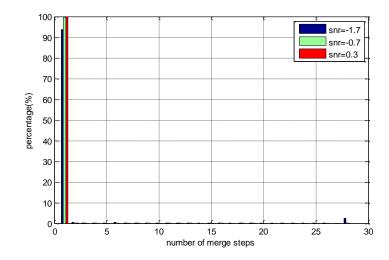

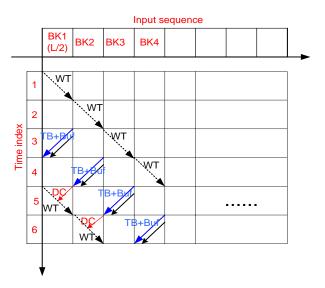

### 1.2.5 Optimal memory organization for Viterbi decoders

In the Viterbi decoder, the SMU is the most power-consuming module. For low power applications, a trace-back approach (TBA) is usually employed in SMU. However, TBA suffers long latency and low throughput. Employing multiple memory banks could resolve the throughput issue to a great extent at the cost of a higher power consumption. We present two efficient schemes to improve the latency issue of conventional TBA by exploiting the pre-trace-back method [14]. We also adopt a buffer-based TBA method to reduce memory access times, thus reducing power consumption significantly. Simulation results show that the proposed decoding schemes cause either zero or negligible performance loss.

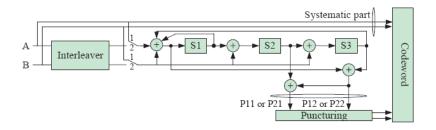

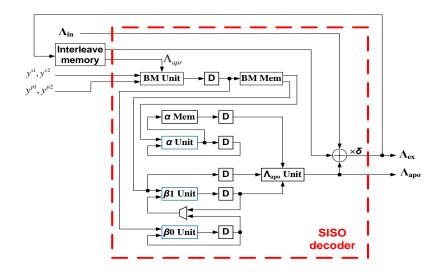

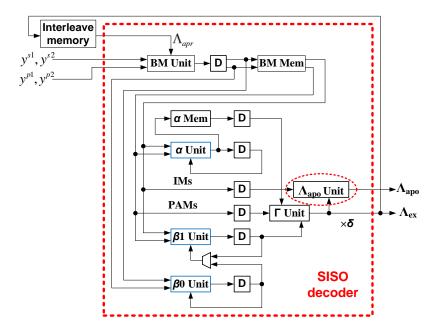

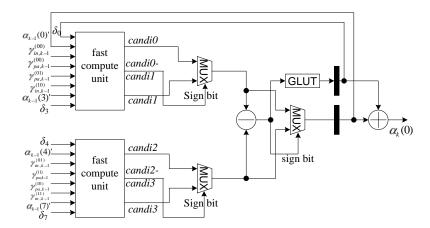

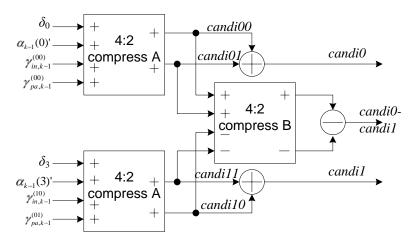

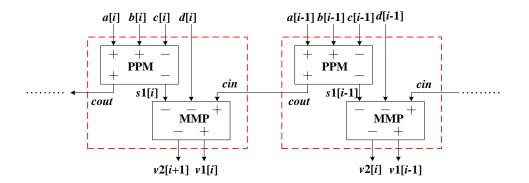

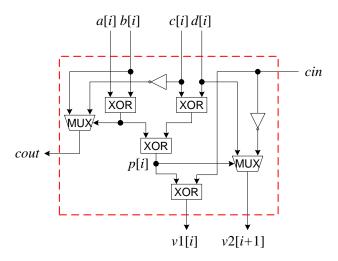

# 1.2.6 A low-complexity, memory-reduced SISO decoder for double-binary turbo code

When extending CTCs from single-binary (SB) to double-binary (DB), the number of BMs increases exponentially. Therefore, in a soft-in soft-out (SISO) decoder for a DB CTC, BMs, rather than the forward metrics, become the dominant factor in determining the overall memory size. We propose a memory-reduced method by decomposing each BM into an information metric and a parity metric, reducing the memory size for BMs by half. Then the MAP algorithm is modified accordingly. The modified MAP algorithm reveals that the extrinsic values exchanged between SISO decoders are only related to the forward metrics, the backward metrics, and the parity metrics. Therefore, unnecessary computation can be removed from the decoder. We thus develop an architecture based on BM partitioning and the modified MAP algorithm, a promising solution for low-power implementation [15].

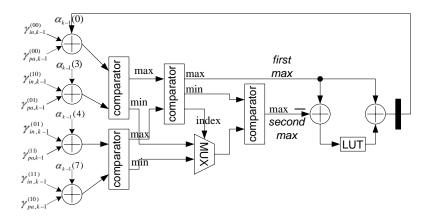

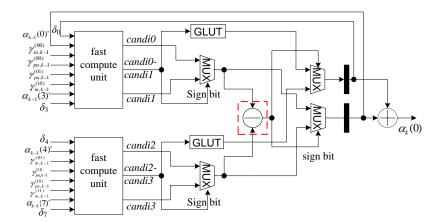

# 1.2.7 A high-speed recursion architecture for log-MAP and TL-log-MAP algorithms

As the number of paths reaching each state is increased from 2 to 4, the length of the critical path as well as the computational complexity is increased drastically. A simplified algorithm [16] proposes to find the two largest values within all the candidates first. Then the log-MAP algorithm is applied to the two largest value only, rather than to all candidates. When this two-largest (TL) log-MAP algorithm is employed for DB CTCs, simulation result shows that it has no observable performance loss compared with log-MAP algorithm. However, a straightforward implementation of the TL log-MAP algorithm will dramatically reduce the decoding speed due to the sorting process to determine the two largest candidates. We propose two high-speed recursion architectures for TL log-MAP algorithm [17], where the decoding speed is improved by 50% through algorithmic approximation and bit-level optimization with negligible BER performance loss.

### **1.3.** Organization of the Dissertation

This dissertation is outlined as follows.

Chapter 2 reviews some important information theory backgrounds for convolutional

codes, trellis coded modulation, and convolutional turbo codes.

Chapter 3 focuses on the high-speed low-complexity VLSI architecture design for a 4-D 8PSK TCM codec. We first give the system overview. Then the encoder design is discussed. After that, the proposed low-complexity TMU, the T-algorithm on branch metrics and the hybrid T-algorithm are presented in the decoder design section.

In Chapter 4, we discuss the low-power implementation for Viterbi decoders. We first present the high-speed, low-power VD design. Then a general optimization for memory organization in Viterbi decoders is discussed.

Chapter 5 is dedicated to the high-speed, memory-reduced VLSI design for doublebinary CTCs.

Chapter 6 gives a brief conclusion and some potential future research topics.

### 2. ERROR CORRECTION CODES

Error correction codes (ECC) are employed in most electronics devices that people use everyday. For example, the International Standard Book Number (ISBN) system identifies every book with a ten-digit number, such as 7-5053-7048-0, where the first nine digits are the actual number and the tenth is a redundant number derived from a mathematical formula based on the first nine. If a single one of the digits is changed, as in a misprint when ordering a book, a simple check verifies that something is wrong. In brief, the idea of ECC is to add redundant information to the message in a controlled way. When error occurs during the transmission of the coded data, the receiver can recover the original message by exploiting the redundant information. For binary data transmissions, a theoretical way to evaluate an ECC's performance is to measure the minimum Hamming distance between all the possible codewords (coded data), where Hamming distance is the number of positions at which the corresponding symbols are different between two codewords. For example, the Hamming distance between codewords "010" and "100" is 2. The minimum Hamming distance of an ECC is also defined as the "minimum free distance". The larger the minimum free distance, the better the bit-error-rate (BER) performance, or the stronger the error-correcting capability.

The two basic groups of ECCs are block codes and convolutional codes [18]. Advanced codes such as Reed-Solomon codes [2] and LDPC codes [3] belong to the category of block codes, while CTCs [19] are based on convolutional codes. This dissertation is focusing on VLSI architecture design for decoding convolutional codes and two convolutionalcode-based schemes: TCM and CTC. This chapter briefly summarizes the background information that is required for development in later chapters.

### 2.1. Convolutional Codes

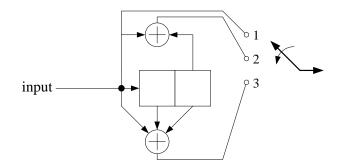

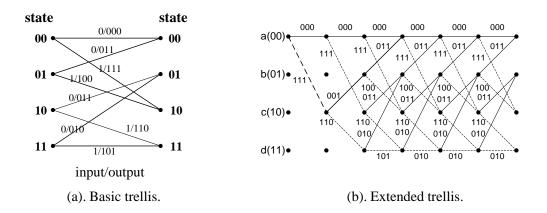

Convolutional codes are adopted in many modern communication standards. Unlike block codes, whose codewords only depend on the current input, the output of convolutional codes depend on both current and past data bits sent to the encoder. In other words, convolutional codes are codes with memories, where a parameter called constraint length K is used to represent the length of convolved memory. The encoder for a convolutional code with a constraint length of K contains K - 1 delay elements. Just as other ECCs, the code rate of the convolutional codes is defined as the number of input bits over the number of output bits. An example of a rate-1/3 convolutional code encoder is shown in Fig. 2.1, where the constraint length K equals 3. For convenience of analysis, convolutional codes are commonly described in the form of a trellis diagram. The trellis diagram of the code shown in Fig. 2.1 is given in Fig. 2.2, where the nodes in a column are the 4 states represented by the delay elements in the encoder<sup>1</sup>. The basic trellis diagram shown in Fig. 2.2(a) describes the state transition based on different input data, while the extended trellis in Fig. 2.2(b) helps illustrate the encoding process: the encoded sequence is a path traveling through the extended trellis from time slot 0 to time slot n.

In 1968, Heller derived an upper bound on the minimum free distance of a rate-1/n convolutional code. It is given by [20]

$$d_{free} \le \min_{l \ge 1} \lfloor \frac{2^{l-1}}{2^l - 1} (K + l - 1)n \rfloor$$

(2.1)

where  $\lfloor \cdot \rfloor$  denotes the floor function. Eq. (2.1) reveals that the longer the constraint length K, the better the performance. Table 2.1 lists the optimal rate-1/2 convolutional codes with different constraint lengths. These codes were obtained by computer search and are optimal in the sense that, for a given constraint length, they have the largest possible  $d_{free}$ .

$<sup>^{1}</sup>$ In this dissertation, the input and output data of the encoders are assumed to be binary, unless explicitly stated otherwise

FIGURE 2.1: Encoder for a rate-1/3 convolutional code.

FIGURE 2.2: Trellis diagram of a rate-1/3 convolutional code.

Although the minimum free distance of the listed optimal codes do not always match the theoretical upper bound in Eq. (2.1), both of them show the trend that increasing the constraint length does improve the performance.

In some practical applications, there is a need to employ high-rate convolutional codes (*i.e.*, rates of (n-1)/n, n = 2, 3, 4...). The trellis for such high-rate codes has  $2^{(n-1)}$  branches that enter each state. Consequently, there are  $2^{(n-1)}$  metric computations per state and many comparisons for selecting the best path. The implementation of the decoder of a high-rate code can be very complex. An alternative way to design a high-rate

| Constraint length K | Generators in octal |     | $d_{free}$ | Upper bound on $d_{free}$ |

|---------------------|---------------------|-----|------------|---------------------------|

| 3                   | 5                   | 7   | 5          | 5                         |

| 4                   | 15                  | 17  | 6          | 6                         |

| 5                   | 23                  | 35  | 7          | 8                         |

| 6                   | 53                  | 75  | 8          | 8                         |

| 7                   | 133                 | 171 | 10         | 10                        |

| 8                   | 247                 | 371 | 10         | 11                        |

| 9                   | 561                 | 753 | 12         | 12                        |

TABLE 2.1: Rate 1/2 maximum free distance codes

convolutional code is to delete some of the coded bits. The deletion of selected coded bits at the output of a convolutional encoder is called puncturing, and the resulting code is called a punctured convolutional code. Punctured convolutional codes are widely used for constructing high-rate CTC.

For decoding convolutional codes, the Viterbi algorithm [21] is known as the optimal decoding method in the sense of maximum likelihood sequence detection (MLSD). By exploiting the extended trellis, the Viterbi algorithm implements the maximum likelihood algorithm with a drastically reduced computational complexity. Consider the extended trellis shown in Fig. 2.2(b): the MLSD compares the received sequence with all the possible paths traveling through the trellis, where the differences between the received one and the candidate paths are calculated. The candidate path with the minimum difference is selected as the decoded sequence. In the Viterbi algorithm, the path difference is defined as the path metric (PM) and is derived from accumulating the branch metrics (BMs) on the PMs in previous time slot. A BM represents the difference between an input codeword and the transition branch connecting the states of adjacent time slots. Note that in Fig. 2.2(b), at each time slot, all the paths will reach one of the 4 states. Therefore, for each state, the

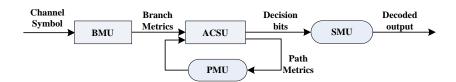

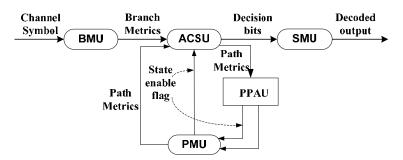

Viterbi algorithm compares all the incoming paths. The optimal one with minimum PM is kept and others are discarded. It is easy to prove that the maximum likelihood path would not be any of the discarded one. A Viterbi decoder typically contains 4 modules as shown in Fig. 2.3:

- branch metric unit (BMU) converts received symbols into branch metrics for ACSU;

- add-compare-select unit (ACSU) recursively updates new path metrics for each state;

- survivor memory unit (SMU) stores the selected path for each state;

- path metrics unit (PMU) buffers path metrics generated by ACSU.

FIGURE 2.3: Block diagram of a Viterbi decoder.

There are two types of Viterbi decoders: hard Viterbi decoder and soft Viterbi decoder. In hard Viterbi decoder, the input is hard-decision binary codewords from the demodulation module, and the BMs are Hamming distances between codewords associated to the states transition lines in the trellis diagram and an input codeword. Soft Viterbi decoder directly takes the received symbols as the input, and the BMs are the Euclidean distance between the received symbols and constellation points. Soft Viterbi decoding gains about 2 dB over the hard decoding scheme in an additive white Gaussian noise (AWGN) channel.

From the discussion above, we know the Viterbi algorithm requires the computation of  $2^{(K-1)} \times 2^{(n-1)}$  metrics each cycle, among which only  $2^{(K-1)}$  would be stored. Also,  $2^{K-1}$  surviving sequences are saved, each of which is about 6K long. The computational burden and the storage requirement for the Viterbi decoder make it impractical to decode convolutional codes with a very large constraint length. Other non-optimal, low-complexity decoding algorithms for convolutional codes include sequential decoding, stack algorithm, and feedback decoding. Interested readers can refer to [20] for details.

### 2.2. Trellis Coded Modulation

When ECCs are employed in a system, the data rate for the information bits is reduced. Generally, there exist two possibilities to compensate for the rate loss: increasing the modulation rate if the channel bandwidth allows, or enlarging the signal set of the modulation system if the channel is band-limited. The latter approach leads to the use of nonbinary modulation [22]. However, given a fixed signal power, increasing the constellation size usually leads to an increasing of bit-error rate (BER) because of the smaller spacing between signal points. Therefore, performance improvement gained by encoding is counteracted by the performance loss in the modulation stage. Moreover, in the traditional communication systems, encoding and modulation are treated as two independent processes, and increasing the Hamming distance at the encoding stage does not guarantee a larger Euclidian distance at the modulation stage (Euclidian distance is the distance between two constellation points; just as the Hamming distance, a larger Euclidian distance indicates a better BER performance).

The coded modulation scheme is proposed by G. Ungerboeck [22], which gains noise immunity over uncoded transmission without expanding the signal bandwidth or increasing the transmission power. The encoding process will directly increase the Euclidian distance rather than the Hamming distance. Ungerboeck concentrated his efforts on finding trellis-based signaling schemes that use signal sets of size  $2^{m+1}$  for transmission of m bits per modulation interval. The following is an example to illustrate the increase of the Euclidian distance.

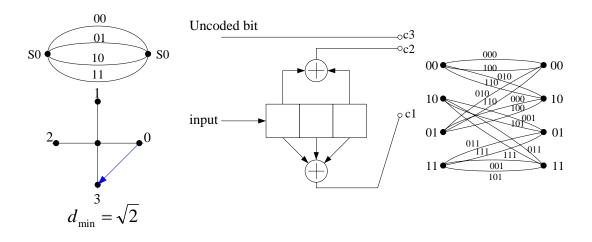

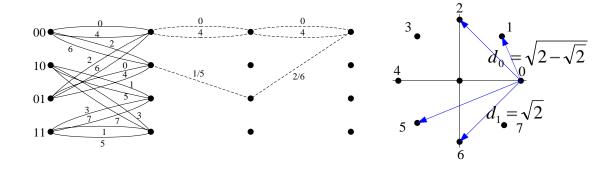

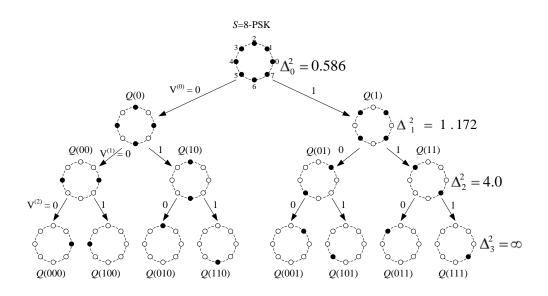

Consider a sequence of uncoded data modulated using quadrature phase-shift keying (QPSK). Every 2 bits are grouped together as (2,2) block code and modulated into 1 signal symbol. The minimum squared Euclidian distance (MSED) between QPSK signal points is  $2E_s$ , where  $E_s$  is the energy per symbol. For convenience of calculation,  $E_s$  is normalized as 1. In trellis-coded modulation, rate-1/2 convolutional encoding is performed only on 1-bit of the original 2. Then, the 2-bit coded data, together with another uncoded bit are modulated into 8 phase-shift keying (8PSK) signals. Fig. 2.4 shows the trellis diagram of the code. Because of the uncoded bit, the transitions in the trellis diagram occur in pairs of two parallel paths. The distance property of the example is illustrated in Fig. 2.5. For any unparallel path, the minimum free squared Euclidean (MFSE)  $d_{free}^2$  distance is defined as the MSED between any two signal paths in the trellis that diverge in one state and re-merge in the same state after more than one transition. In the example,  $d_{free}^2 = d_1^2 + d_0^2 + d_1^2 = 4.585$ . The MSED between two parallel paths in this example is 4. Therefore, compared with the uncoded QPSK system, TCM increases the MSED from 2 to 4!

From the above example, it is clear that the methodology of mapping codewords to constellation points is essential to TCM. This process is called partitioning of the constellation by Ungerboeck. A systematic approach for this partitioning is developed in [8], which is based on three heuristic rules:

- Use all subsets with equal frequency in the trellis;

- Transitions originating from the same state or merging into the same state in the trellis are assigned subsets that are separated by the largest Euclidean distance;

- Parallel state transitions (when they occur) are assigned signal points separated by the largest Euclidean distance. Parallel transitions in the trellis are characteristic of

FIGURE 2.4: An example of TCM based on convolutional encoding.

FIGURE 2.5: Free distance of the TCM.

TCM that contains one or more uncoded information bits.

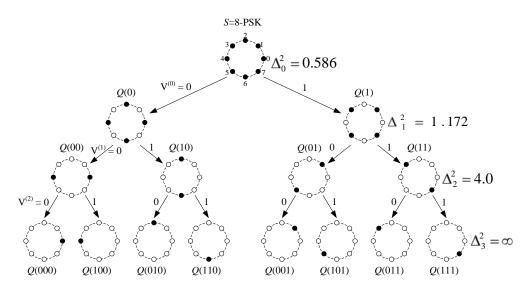

The partitioning of the 8PSK signals is shown in Fig. 2.6. For the TCM system illustrated in Fig. 2.4, the coded bits select one of the four signal subsets at level 2 in Fig. 2.6, and the uncoded bit selects one of the constellation points in a subset.

Later on, Ungerboeck extended TCM schemes to multi-dimensional constellations, which further improves the BER performance [23]. The use of multidimensional modula-

FIGURE 2.6: Partitioning of 8PSK signal.

tions has several advantages over traditional one-dimensional TCM:

- Flexibility in achieving a variety of fractional information rates;

- Codes are partially or completely transparent to discrete phase rotations of the signal set;

- Suitability for use as inner codes in a concatenated coding system

- Higher decoder speeds resulting from the high rate codes used (rate k/(k+1) with k up to 15).

Partitioning of the multi-dimensional signal sets follows the same rules discussed above, though the process is more complex. Multi-dimensional partitioning for two common modulations:  $2\times8$ -PSK and  $4\times8$ -PSK is discussed in *Appendix*. The method can be further applied to higher dimensions. Interested readers can refer to [23] for more information. A more general encoder system of TCM is shown in Fig. 2.7, which consists of three principal sections: a differential encoder, a binary convolutional encoder, and a multidimensional mapper. During the transmission, the signal phase may be rotated by the channel, and the rotation may lead to a wrong decision in demodulation. Differential decoding is a commonly used method to overcome the phase rotation. In a TCM system, differential encoding is only applied to several important bits. Then a subset is chosen from the constellation points through convolutional encoding and the uncoded data chose one point in the subset by the mapper.

FIGURE 2.7: A general encoder system for TCM.

Decoding for a TCM system is based on the Viterbi algorithm since convolutional codes are involved. There are two general methods: "brute-force" method [9] and a simpler approach based on "auxiliary trellis" [8]. The first one is straightforward but has a high complexity; thus, it is rarely used in practice. The second one employed a "auxiliary trellis" to perform a low-complexity computation for finding the best path among all the parallel paths first. Then a regular Viterbi algorithm is used to further decode the signal. Details of "auxiliary trellis" will be discussed in Chapter 3.

# 2.3. Turbo Codes

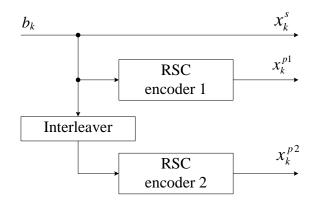

Turbo codes have been considered as one of the most significant technology breakthroughs in the information theory in 1990s, because they are the first practical codes to closely approach the Shannon bound. The code was first introduced by Berrou, Glavieus and Thitimajshima in 1993 in their paper: "Near Shannon Limit Error-correcting Coding and Decoding: Turbo-codes", published in the Proceeding of IEEE International conference on Communications [19]. The encoder of a convolutional turbo code (CTC) is illustrated in Fig. 2.8, where two recursive systematic convolutional (RSC) encoders work in parallel. One encoder encodes the original message and the other works on the permutated message sequence.

FIGURE 2.8: Turbo encoder structure.

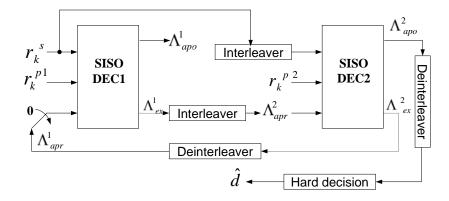

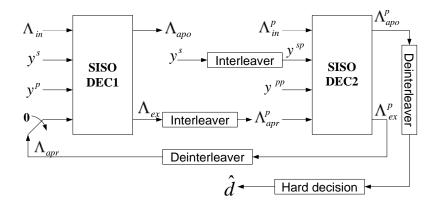

The CTC decoder is built in a similar way as the encoder, where two basic decoders are interconnected in series as shown in Fig. 2.9. Optimal decoding algorithm for CTC requires iterative decoding, where the soft information of the received sequence is passed from a previous decoding iteration to the current iteration. Therefore, DEC1 and DEC2 should be capable of generating the soft outputs, which represent the probability of a bit being '1' or '0' as expressed in Eq. (2.2). Since the conventional Viterbi decoder is unable to calculate the probability value, it can not be directly used in DEC1 or DEC2. The soft-input soft-output (SISO) decoder employs the modified BCJR algorithm, which is also known as the maximum *a posteriori* probability (MAP) algorithm.

The MAP algorithm can be summarized as follows. Assume the output of the

FIGURE 2.9: Turbo decoder structure.

Gaussian memoryless channel is a sequence  $R_1^N = R_1 \cdots R_k \cdots R_N$ , where k is the time index and  $1 \le k \le N$ . The MAP algorithm evaluates the probability of each bit to be 1 or 0 under the condition of the received sequence  $R_1^N$ . When decoding a specific bit at time slot k, the process turns out to be simplified if we take advantage of the trellis structure. Again, considering the trellis diagram shown in Fig. 2.2 (a), we use m' to represent the state at time slot k-1 and m for state at time slot k. Thus, the probability of the bit to be 1 equals  $\sum_{m} \sum_{m'} \Pr\{S_k = m\} \Pr\{S_{k-1} = m'\} \Pr\{d_k = 1, S_k = m, S_{k-1} = m'\}$ .  $\Pr\{S_k = m\}$ is called the backward state metric, which represents the probability that the state at time slot k to be m and is related to received symbols  $R_{k+1}^N$ .  $Pr\{S_{k-1} = m'\}$  is known as the forward state metric, which represents the probability that the state at time slot k-1 to be m' and is related to received symbols  $R_1^{k-1}$ .  $Pr\{d_k = 1, S_k = m, S_{k-1} = m'\}$  is the probability the previous state being m' and current state being m under the condition that the current received symbol is  $R_k$  and the decoded bit is 1. In the iterative decoding, the soft input will contain another portion called the *a priori likelihood ratio*, which comes from the soft output of the last decoding iteration. The mathematic expression of the MAP algorithm is given in Eq. (2.2)

$$\lambda(d_k) = \frac{p(d_k = 1)}{p(d_k = 0)} = \frac{\sum_{m} \sum_{m'} \gamma_1(R_k, m', m) \alpha_{k-1}(m') \beta_k(m)}{\sum_{m} \sum_{m'} \gamma_0(R_k, m', m) \alpha_{k-1}(m') \beta_k(m)},$$

(2.2)

where  $\gamma$ ,  $\alpha$  and  $\beta$  are the branch metrics, forward state metrics and backward state metrics respectively, and are defined through Eq. (2.3) to Eq. (2.5), where i = 0, 1.

$$\gamma_i(R_k, m', m) = p(R_k/d_k = i, S_k = m, S_{k-1} = m') \cdot q(d_k = i/S_k = m, S_{k-1} = m') \cdot \pi(S_k = m/S_{k-1} = m');$$

(2.3)

$$\alpha_k(m) = \sum_{m'} \gamma_i(R_k, m', m) \alpha_{k-1}(m');$$

(2.4)

$$\beta_k(m') = \sum_m \gamma_i(R_{k+1}, m', m)\beta_{k+1}(m).$$

(2.5)

In Eq. (2.3),  $p(\cdot/\cdot)$  is the transition probability of the channel,  $q(\cdot/\cdot)$  is the *a priori* likelihood ratio, and  $\pi(\cdot/\cdot)$  is a fixed probability derived from the trellis diagram. Usually the input at the encoder is a random data sequence with even probability of 1 and 0. Therefore, for most of the cases,  $\pi(\cdot/\cdot)$  is a constant for all existing transition lines in the trellis and can be removed from the equation.

For simplicity of hardware implementation, log-MAP algorithm is used in practical design, where all the computation is transformed into logarithm domain. Therefore, branch metrics, forward state metrics, and backward state metrics should be re-defined as Eq. (2.6) to Eq. (2.10), and the multiplication operations are converted to addition operations in the new algorithm. According to Fig. 2.9, current  $\Lambda_{apr}$  in Eq. (2.6) is  $\Lambda_{ex}$ from previous decoding process after interleaving or de-interleaving.

$$\gamma_i(R_k, m', m) = \log(p(R_k/d_k = i, S_k = m, S_{k-1} = m')) + \Lambda_{apr}(k);$$

(2.6)

$$\alpha_k(m) = \log(\sum_{m'} \exp(\gamma_i(R_k, m', m) + \alpha_{k-1}(m')));$$

(2.7)

$$\beta_k(m') = \log(\sum_m \exp(\gamma_i(R_{k+1}, m', m) + \beta_{k+1}(m)));$$

(2.8)

$$\Lambda_{apo}(k) = \log(\sum_{m} \sum_{m'} \exp(\gamma_1(R_k, m', m) + \alpha_{k-1}(m') + \beta_k(m))) - \log(\sum_{m} \sum_{m'} \exp(\gamma_0(R_k, m', m) + \alpha_{k-1}(m') + \beta_k(m))); \quad (2.9)$$

$$\Lambda_{ex}(k) = \Lambda_{apo}(k) - \Lambda_{apr}(k).$$

(2.10)

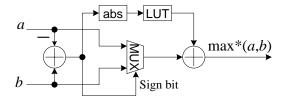

The first CTC only considers the single binary input. As a result, there are only two paths merging into one state. Mathematically, Eq. (2.7) and Eq. (2.8) can be treated as the same class of equation:  $S = \log(\exp(a) + \exp(b))$ . Note that,

$$S = \log(\exp(a) + \exp(b))$$

(2.11)

=  $\log(\exp(\max(a, b)) \cdot (1 + \exp(-|a - b|)))$

=  $\max(a, b) + \log(1 + \exp(-|a - b|)).$

When the second term of Eq. (2.12) is ignored, the calculation for  $\alpha$  reduces to the conventional Viterbi algorithm, and the computation for  $\beta$  can be treated as a backward Viterbi process. The simplified log-MAP is also known as the MAX-log-MAP algorithm, which leads to lower computational complexity, but with some performance loss. We can also maintain the high performance of log-MAP scheme by implementing  $\log(1+\exp(-|a-b|))$  as a look-up-table (LUT).

In 2005, the inventor of the basic single-binary turbo codes, Claude Berrou, proposed the turbo codes based on multiple-input convolutional codes [24]. These codes offer several advantages over classical single binary CTC:

• Better convergence of the iterative process;

- Larger minimum distance;

- Less puncturing for a given rate;

- Higher throughput and lower latency;

- More robust decoder.

Recently, double-binary (DB) CTC has attracted significant research interest and has been adopted in wireless communication standards such as digital video broad-castingreturn channel over satellite and terrestrial (DVB-RCS and DVB-RCT) [25] and WiMAX [26]. The decoding process for DB CTC is similar to the conventional binary CTC, though it requires more computational efforts. Details about decoding DB CTC will be introduced in Chapter 5.

# 2.4. Conclusion

In this chapter, we have reviewed the background information of convolutional codes, TCM system, and turbo codes. The decoding algorithm for each scheme is introduced. This information is the basis for the readers to understand the materials in the following chapters.

# 3. AN EFFICIENT VLSI ARCHITECTURE FOR THE 4-D TCM DECODER

#### 3.1. System Overview

TCM techniques have been employed in communication systems emphasizing on the bandwidth efficiency. For example, the 4-dimentional (4-D) 8PSK TCM system studied in our research is considered by National Aeronautics and Space Administration (NASA) for space data transmission [27].

The convolutional encoder and constellation mapper for the 4-D 8PSK TCM system are specified in [27]:

- Size of the constellation: M = 8 phase states (8PSK);

- Number of signal set constituent is 4 (4-D);

- Number of states for the trellis encoder is 64;

- Rate of the convolutional encoder used for the construction of the trellis is 3/4;

- Rate of modulation:  $\operatorname{Rm}=m/(m+1)$ , m=8, 9, 10 or 11.

- Efficiency of the modulation:

- $R_{eff} = 2.0$  bits per channel-symbol (Rm=8/9);

- $R_{eff} = 2.25$  bits per channel-symbol (Rm=9/10);

- $R_{eff} = 2.5$  bits per channel-symbol (Rm=10/11);

- $-R_{eff} = 2.75$  bits per channel-symbol (Rm=11/12);

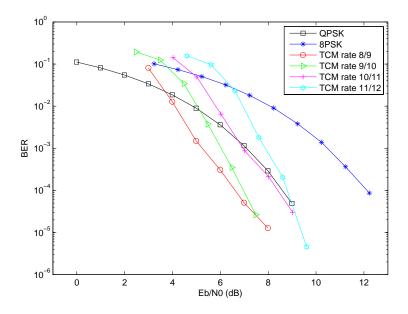

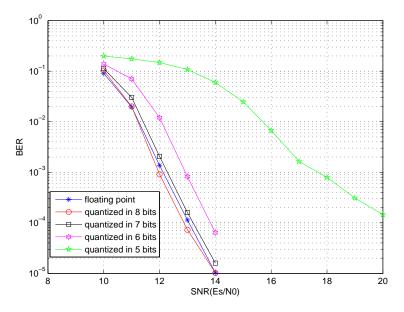

The TCM system was modeled in Matlab and the BER performance is simulated as shown in Fig. 3.1. From the figure, we can observe that, near the BER of  $10^{-4}$ , with the same modulation efficiency of 2 bits/symbol, the 4-D 8PSK TCM (Rm=8/9) achieve 2 dB gain over the uncoded QPSK system. Compared with 8PSK signal which transmit 3 bits/symbol, the TCM system with a modulation rate of 11/12 gains 3 dB at the cost of a very small loss of modulation efficiency.

FIGURE 3.1: BER performance of the 4-D 8PSK TCM system.

## 3.2. Encoder Design

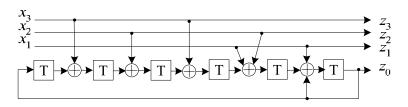

Regardless of the modulation rate, the 4-D 8PSK TCM encoder uses the same convolutional code shown in Fig. 3.2, while the constellation mapper varies from case to case, which is shown through Eq. (3.1) to Eq. (3.4). A complete understanding of partitioning multi-dimensional constellation points requires extensive mathematic background, which is beyond the scope of this dissertation. Interested readers may refer to the *Appendix* or [8] for more information.

FIGURE 3.2: Rate-3/4 convolutional encoder.

$$R_{eff} = 2.0$$

bits/T, Rm=8/9:

$$\begin{pmatrix} Z_{0} \\ Z_{1} \\ Z_{2} \\ Z_{3} \end{pmatrix} = \begin{cases} (4x^{(8)} + 2^{(5)} + x^{(1)}) \begin{pmatrix} 1 \\ 1 \\ 1 \\ 1 \end{pmatrix} + 4 \begin{pmatrix} 0 \\ x^{(7)} \\ x^{(6)} \\ x^{(7)} + x^{(6)} + x^{(4)} \end{pmatrix} \\ + 2 \begin{pmatrix} 0 \\ x^{(3)} \\ x^{(2)} \\ x^{(3)} + x^{(2)} + x^{(0)} \end{pmatrix} \end{cases} (mod8), \qquad (3.1)$$

$R_{eff} = 2.25$  bits/T, Rm=9/10:

$$\begin{pmatrix} Z_{0} \\ Z_{1} \\ Z_{2} \\ Z_{3} \end{pmatrix} = \begin{cases} (4x^{(9)} + 2^{(6)} + x^{(2)}) \begin{pmatrix} 1 \\ 1 \\ 1 \\ 1 \end{pmatrix} + 4 \begin{pmatrix} 0 \\ x^{(8)} \\ x^{(7)} \\ x^{(8)} + x^{(7)} + x^{(5)} \end{pmatrix} \\ + 2 \begin{pmatrix} 0 \\ x^{(4)} \\ x^{(3)} \\ x^{(4)} + x^{(3)} + x^{(1)} \end{pmatrix} + \begin{pmatrix} 0 \\ x^{(0)} \\ 0 \\ x^{(0)} \end{pmatrix} \} (mod8), \qquad (3.2)$$

$$\begin{pmatrix} Z_{0} \\ Z_{1} \\ Z_{2} \\ Z_{3} \end{pmatrix} = \begin{cases} \left(4x^{(10)} + 2^{(7)} + x^{(3)}\right) \begin{pmatrix} 1 \\ 1 \\ 1 \\ 1 \\ 1 \end{pmatrix} + 4 \begin{pmatrix} 0 \\ x^{(9)} \\ x^{(8)} \\ x^{(9)} + x^{(8)} + x^{(6)} \end{pmatrix} \\ + 2 \begin{pmatrix} 0 \\ x^{(5)} \\ x^{(4)} \\ x^{(5)} + x^{(4)} + x^{(2)} \end{pmatrix} + \begin{pmatrix} 0 \\ x^{(1)} \\ x^{(0)} \\ x^{(1)} + x^{(0)} \end{pmatrix} \right\} (mod8), \quad (3.3)$$

$$R_{eff} = 2.75 \text{ bits/T, Rm} = 11/12:$$

$$Z_{0} \\ Z_{1} \\ Z_{2} \\ Z_{3} \end{pmatrix} = \begin{cases} \left(4x^{(11)} + 2^{(8)} + x^{(4)}\right) \begin{pmatrix} 1 \\ 1 \\ 1 \\ 1 \\ 1 \end{pmatrix} + 4 \begin{pmatrix} 0 \\ x^{(10)} \\ x^{(9)} \\ x^{(10)} + x^{(9)} + x^{(7)} \end{pmatrix} \\ + 2 \begin{pmatrix} 0 \\ x^{(6)} \\ x^{(5)} \\ x^{(5)} + x^{(5)} + x^{(3)} \end{pmatrix} + \begin{pmatrix} 0 \\ x^{(2)} \\ x^{(1)} \\ x^{(2)} + x^{(1)} + x^{(0)} \end{pmatrix} \right\} (mod8), \quad (3.4)$$

$R_{\rm eff} = 2.5 \ {\rm bits}/{\rm T} \ {\rm Bm} = 10/11$

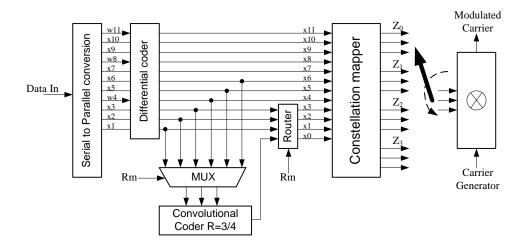

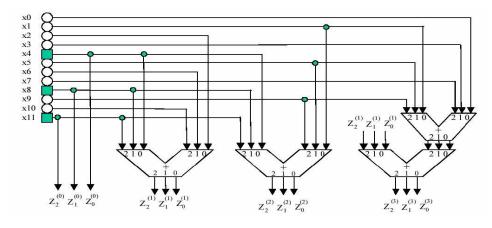

We can design 4 different constellation mappers and enable the right one according to its modulation rate. However, this approach is very inefficient in terms of hardware area. By carefully examining the common features of these mapping equations, we have developed a universal encoder architecture shown in Fig. 3.3, where the router block takes 4 bits input and outputs 4 bits in a proper order based on the given data rate, and the MUX maps the proper data to the input of the convolutional encoder. This architecture only requires one single constellation mapper to implement Eq. (3.4). The structure of the mapper is shown in Fig. 3.4.

FIGURE 3.3: Encoder of the 4-D 8PSK TCM system.

FIGURE 3.4: Constellation mapper.

# 3.3. Decoder Design

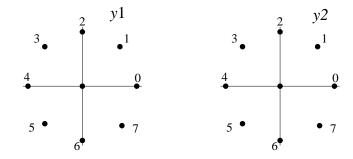

Before providing the details of decoder design, it is necessary to evaluate the influence from signal quantization. Fig. 3.5 shows the simulation results with various quantization levels for the 4-D 8PSK TCM signal with a modulation rate of 11/12. The signal-to-noise ratios (SNRs) to achieve a BER of  $10^{-4}$  for the floating-point case, 8-bit quantization, 7-bit quantization, and 6-bit quantization are 12.88 dB, 13.05 dB, 13.20 dB and 13.82 dB, respectively. In principle, on the premise of an acceptable performance, the length of bits for the signal quantization should be as small as possible. The 7-bit quantization is adopted in our design, since the performance loss is less than 0.5 dB compared with the floating-point case. When the frond-end analog-to-digital converter (ADC) can not provide so many bits per symbol, a 6-bit quantization is still usable. Quantization with fewer than 6 bits should not be considered due to its poor performance as shown in Fig. 3.5.

FIGURE 3.5: Influence of the signal quantization.

#### 3.3.1 Literature review

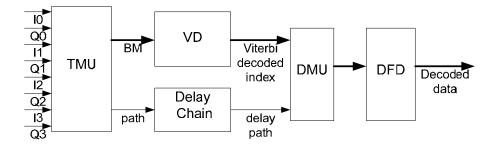

The block diagram of the decoder for 4-D 8PSK TCM signal is shown in Fig. 3.6, where the delay chain is used to buffer the paths associated with each BM generated by the TMU. The "path" refers to the 12 bits of information from the 4 dimensions of 8PSK signals. Since there are only 16 BMs [9] in this case, using a 4-bit index is more

efficient than using the 12-bit path information inside the VD. When the VD outputs the decoded index, the corresponding path will be sent to the de-mapping unit (DMU) and differential decoder (DFD) for further processing. Implementation of the DMU and DFD is straightforward; the most challenging and hardware-consuming parts are the TMU and VD.

FIGURE 3.6: 4-D 8PSK TCM decoder diagram.

Parallel paths in trellis transition distinguish TCM schemes with conventional convolutional encoding. The TMU is used to find the optimal path among all the parallel ones as the BM to the Viterbi decoder. As indicated in Fig. 3.3, for any encoded sequence "x3x2x1x0", there are 256 different 4-D 8PSK signal groups (combinations of x11 - x4) which indicate 256 parallel paths for each state transition in the trellis diagram. Therefore, each BM has 256 candidates. A straightforward implementation of TMU leads to very high computational complexity, which is even higher than that of the ACSU in the Viterbi decoder. The structure of the auxiliary trellis has been presented in [9] to remove the redundant operations in TMU by sharing intermediate results among all the BM candidates. However, the computational complexity is still considerably high. A new architecture is proposed in this chapter to further remove the redundant computations.

For VD implementation, research efforts have focused on ACSU and SMU. ACSU implementation is critical because the feedback loop makes it the bottleneck for high speed applications. Additionally, as the constraint length K increases, the number of

states and computation in the ACSU increase exponentially. Several algorithms such as *M*-algorithm [28] and *T*-algorithm [29], [30] have been proposed to reduce the computation in ACSU. In the M-algorithm, this is achieved by keeping M optimal states and purging the rest. In the T-algorithm, a threshold T is set and the difference between each PM and the optimal one is calculated. The algorithm compares the differences with T; only the states with a difference less than T survive and are used for the calculation in the next cycle. Both methods have the potential for significant power savings. In practical implementation, however, T-algorithm is more popular than M-algorithm for two reasons: 1) it can adaptively adjust the number of purged states according to run-time channel conditions and 2) it has lower computational complexity since T-algorithm only needs to find out the optimal PM (maximum or minimum value, depending on different implementations), while *M*-algorithm involves a sorting process for  $2^{(k-1)}$  values. However, T-algorithm still requires the search of the optimal PM in the ACS loop. The extra comparison operation will affect the clock speed of the entire design. Although it is possible to implement a fully parallel structure for the comparison operation, it will cause a significant hardware overhead. Recently, several novel VLSI architectures are proposed to remove or to reduce the loop latency with reasonable hardware overhead. For example, in [31], instead of finding the exact optimal PM, an estimated value is obtained. Then, a compensation scheme outside the loop is used to adjust the estimated optimal PM.

There are two basic schemes for SMU implementation: the register-exchange (RE) scheme [32] and the trace-back (TB) scheme [33]. Because of the maximum likelihood (ML) path searching in SMU, VD usually causes a decoding latency proportional to the constraint length K. The RE scheme is well suited for low-latency, high-speed applications, while the TB scheme consumes less power. Although there exists extensive work on reducing the latency of the TB scheme [4, 34–36], none of them could achieve the latency of the RE scheme even at the expense of a huge power consumption overhead. Another

advantage of using RE scheme is that T-algorithm on PM can be efficiently exploited in RE design. Thus, the RE scheme is adopted in our design.

The algorithms discussed above are general solutions for VDs. TCM schemes usually employ high-rate codes (e.g., the rate-3/4 codes in our case), and the unique properties of high-rate codes can be exploited to construct more efficient architectures for the corresponding VD.

# 3.3.2 Low-complexity TMU design

There are two common ways to design TMU: 1) ROM based approach, and 2) arithmetic (on-line) computation based solution. In order to reduce hardware as well as to pipeline the computation unit for high clock speeds, the second approach is adopted in our design. Exploiting the auxiliary trellis [9], we design two efficient methods to reduce the computational complexity.

## A. Simplified computation of Euclidian metrics

Given a received 8PSK symbol  $(I_r, Q_r)$  and a target constellation point A:  $(I_s, Q_s)$  $(s = 0, 1, 2, \dots, 7 \text{ for 8 PSK signals})$ , the Euclidian distance is computed as:

$$d_s = (I_r - I_s)^2 + (Q_r - Q_s)^2$$

=  $(I_r^2 + I_s^2 + Q_r^2 + Q_s^2) - 2I_r I_s - 2Q_r Q_s.$  (3.5)

Note that for all  $d_s$ ,  $(I_r^2 + I_s^2 + Q_r^2 + Q_s^2)$  remains the same. Finding the minimum of  $(d_0, d_1, d_2, ..., d_7)$  (the closest constellation point to the received signal) is equivalent to finding the maximum of  $(I_r I_0 + Q_r Q_0, I_r I_1 + Q_r Q_1, I_r I_2 + Q_r Q_2, ..., I_r I_7 + Q_r Q_7)$ . Thus, we only need to consider the following distance:

$$d'_s = I_r I_s + Q_r Q_s. aga{3.6}$$

Furthermore, because all the possible constellation points are equally spaced on a circle with the phase of  $s\pi/4$ , s = 0, 1, 2...7, it has been found in [9] that  $I_s$  and  $Q_s$  satisfy the following conditions

$$I_s = -I_{(s+4)mod8}$$

$$Q_s = -Q_{(s+4)mod8}.$$

Hence, only four sets of Eq. (3.6) need to be calculated. The Euclidean metrics  $C_i$  (i = 0, 1, 2, 3) are computed as

$$C_{0} = |d'_{0}| = |I_{r}|$$

$$C_{1} = |d'_{1}| = |(I_{r} + Q_{r}) \times 0.707|$$

$$C_{2} = |d'_{2}| = |Q_{r}|$$

$$C_{3} = |d'_{3}| = |(Q_{r} - I_{r}) \times 0.707|.$$

(3.7)

It is clear from Eq. (3.7) that only 2 multiplications are required.

## B. Sharing of branch metric computations

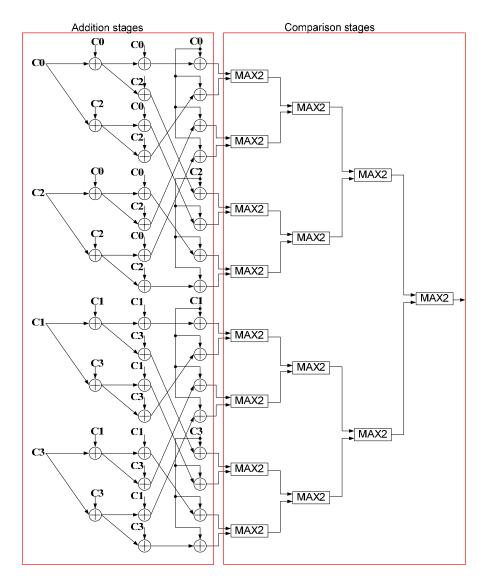

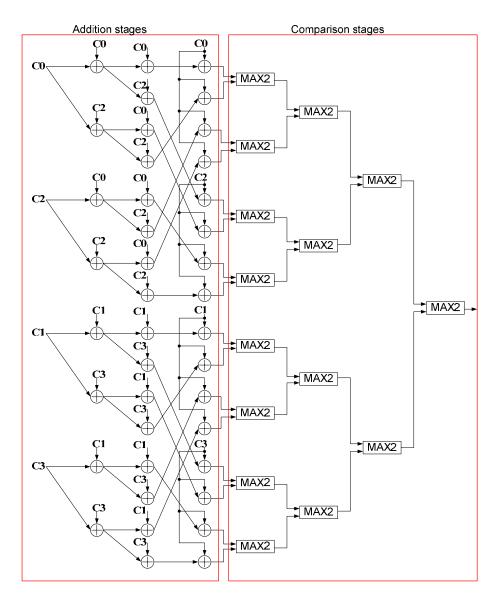

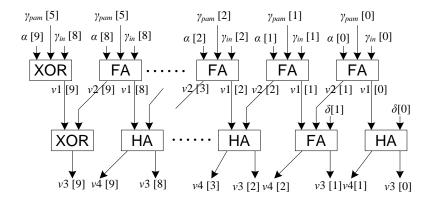

In the 4-D 8PSK TCM decoder, 16 BMs are selected from 4096 (*i.e.*, 8<sup>4</sup>) candidates every cycle. From Fig. 1, the 16 BMs are related to the 16 combinations of  $x_3, x_2, x_1$ and  $x_0$ . Let BM 0000 denote the BM related to  $(x_3, x_2, x_1, x_0) = (0, 0, 0, 0)$ ; BM 0001 denote the BM related to  $(x_3, x_2, x_1, x_0) = (0, 0, 0, 1)$ , and so on. Each candidate is the sum of the 4 Euclidian metrics of the received signal set  $(Z_0, Z_1, Z_2, Z_3)$ . By applying the above simplified Euclidian metrics to BMs, the number of candidates is reduced from 4096 to 256 (*i.e.*, 4096/16), since the number of Euclidian metrics from each signal set is reduced by half. Now each BM is selected among only 16, rather than 256, candidates. A straightforward implementation requires 3 serial addition stages to compute the candidates and several comparison steps to find the BMs. Since the results at each addition stage can be shared for further computation, using auxiliary trellis [9] can eliminate redundant additions. Fig. 3.7 is an example that illustrates the process of computing BM 0000. From the left to the right,  $C_i$  (i = 0, 1, 2, 3) in each step denote the Euclidean metrics of the received symbols from  $Z_0, Z_1, Z_2$  and  $Z_3$ , respectively. The same rule applies to all equations and figures in the rest of the Chapter. The 16 candidates for BM 0000 are: $C_0 + C_0 + C_0 + C_0, C_1 + C_1 + C_1, C_0 + C_0 + C_2 + C_2, C_1 + C_1 + C_3, C_0 + C_2 + C_0 + C_2, C_1 + C_3 + C_1 + C_3, C_0 + C_2 + C_2 + C_0, C_1 + C_3 + C_3 + C_1, C_2 + C_2 + C_2 + C_2 + C_2 + C_2, C_3 + C_3 + C_3 + C_3, C_2 + C_2 + C_0 + C_2 + C_0, C_3 + C_1 + C_3 + C_1, C_2 + C_0 + C_0 + C_2 + C_0 + C_1 + C_1 + C_2 + C_3 + C_3 + C_3 + C_3 + C_1 + C_1 + C_1 + C_2 + C_3 + C_3 + C_3 + C_3 + C_1 + C_1 + C_3 + C_3 + C_1 + C_3 + C_1 + C_3 + C_1 + C_2 + C_3 + C_3 + C_3 + C_3 + C_1 + C_1 + C_3 + C_1 + C_3 + C_1 + C_3 + C_1 + C_2 + C_3 + C_3 + C_3 + C_3 + C_1 + C_1 + C_3 + C_1 + C_3 + C_1 + C_3 + C_1 + C_3 + C_1 + C_2 + C_0 + C_2 + C_2 + C_0 +$

By using the auxiliary trellis, the total number of additions is reduced from 768  $(i.e., 3 \times 16 \times 16)$  with the straightforward implementation to 336  $(i.e., 4^2 + 4^3 + 4^4)$ . However, the number of comparisons remains the same. In this work, we propose a new approach that further reduces the number of additions by half. In addition, about 2/3 of the comparisons are removed.

The key idea of the improvement is as follows. Let us again take BM 0000 as an example. In the auxiliary trellis approach as shown in Fig. 3.7, to compute each candidate branch metric, 3 serial addition stages are performed to compute 16 candidates in parallel. Then, one survival BM is chosen from the 16 candidates. A careful examination of the added Euclidian distances reveals that in the last addition stage, there are only 4 different values to be added onto the 16 candidates as indicated in Table 3.1.

This property can be exploited to reduce the number of additions in the last stage by rearranging the calculation flow in Fig. 3.7. In the proposed approach, the 16 candidates are divided at the end of the second addition stage into 4 groups, which is represented by  $G_k, k = 0, 1, 2, 3$ , in Table 3.1. The 4 candidates in each group are supposed to add the same Euclidian metric of  $Z_3$  later. Before the last addition operation, one survival candidate is chosen from each group. Then in the last addition stage, only 4 additions, instead of 16, are required. Based on the two-step comparison method, an algorithmic strength reduction scheme is introduced, which significantly reduces the needed comparisons. As

FIGURE 3.7: An example of auxiliary trellis to simplify the BM calculation.

|       | $Z_0$          | $Z_1$ | $Z_2$ | $Z_3$ |       | $Z_0$ | $Z_1$ | $Z_2$          | $Z_3$ |       |       |   |

|-------|----------------|-------|-------|-------|-------|-------|-------|----------------|-------|-------|-------|---|

|       | $C_0$          | $C_0$ | $C_0$ |       |       |       | $C_1$ | $C_1$          |       |       |       |   |

| C     | $C_0$          | $C_2$ | $C_2$ | C     | C     | C     | C     | C              | $C_1$ | $C_3$ | $C_3$ | C |

| $G_1$ | $C_0$<br>$C_2$ | $C_2$ | $C_0$ | $C_0$ | $G_2$ | $C_3$ | $C_3$ | $C_3$<br>$C_1$ | $C_1$ |       |       |   |

|       |                | $C_0$ |       |       |       | $C_3$ | $C_1$ | $C_3$          |       |       |       |   |

|       | $C_0$          | $C_0$ | $C_2$ |       |       | $C_1$ | $C_1$ | $C_3$          |       |       |       |   |

| C     | $C_0$          | $C_2$ | $C_0$ | $C_2$ | C     | a     | $G_4$ | $C_1$          | $C_3$ | $C_1$ | C     |   |

| $G_3$ | $C_2$          | $C_2$ | $C_2$ |       | G4    | $C_3$ | $C_3$ | $C_1$<br>$C_3$ | $C_3$ |       |       |   |

|       | $C_2$          | $C_0$ | $C_0$ |       |       | $C_3$ | $C_1$ | $C_1$          |       |       |       |   |

TABLE 3.1: Grouping of the candidates for BM 0000

shown in Fig. 3.8, the computation procedure is rearranged: two serial comparison operations are inserted between the second and the third addition operations. Furthermore, the survival candidates after the comparison step 1 can be shared by 4 BM computations (*i.e.*, BM 0000, BM 0001, BM 1000 and BM 1001 share the same survival candidates, as listed in Table 3.1 through Table 3.4).

The other 12 BMs have the same property and can be categorized into 3 clusters; in each cluster, 4 BMs share the survivor candidates after the comparison step 1. The total number of additions of the proposed architecture is  $4^2 + 4^3$  from the first two addition stages plus  $4 \times 16$  from the third addition stage. Meanwhile, the comparison operations are also reduced. The computational complexities of the 3 methods are summarized in Table 3.5.

The same structure can be extended to the cases of Rm = 10/11 and Rm = 9/10, in which the same method could be employed. For the case of Rm = 8/9, since there are only two candidates for each BM, the structure based on the conventional auxiliary trellis [9] is as efficient as the proposed approach. A detailed comparison of computational

FIGURE 3.8: Computation of BM 0000 using the proposed 2-step comparison method.

|       | $Z_0$           | $Z_1$          | $Z_2$ | $Z_3$ |            | $Z_0$ | $Z_1$ | $Z_2$          | $Z_3$ |   |

|-------|-----------------|----------------|-------|-------|------------|-------|-------|----------------|-------|---|

|       | $C_0$           | $C_0$          | $C_0$ |       |            |       | $C_1$ | $C_1$          |       |   |

| C     | $C_0$           | $C_2$          | $C_2$ | a     |            | $C_1$ | $C_3$ | $C_3$          | C     |   |

| $G_1$ | $C_2$           | $C_2$<br>$C_2$ | $C_0$ | $C_1$ | $G_2$      | $C_3$ | $C_3$ | $C_3$<br>$C_1$ | $C_2$ |   |

|       | $C_2$           | $C_0$          | $C_2$ |       |            | $C_3$ | $C_1$ | $C_3$          |       |   |

|       | $C_0$           | $C_0$          | $C_2$ |       |            | $C_1$ | $C_1$ | $C_3$          |       |   |

| C     | $C_0$           | $C_2$          | $C_0$ | a     | G          | C     | $C_1$ | $C_3$          | $C_1$ | C |

| $G_3$ | $C_0$<br>$C_2$  | $C_2$          | $C_2$ | $C_3$ | $C_3  G_4$ | $C_3$ | $C_3$ | $C_1$<br>$C_3$ | $C_0$ |   |

|       | $C_2  C_0  C_0$ |                | $C_3$ | $C_1$ | $C_1$      |       |       |                |       |   |

TABLE 3.2: Grouping of the candidates for BM 0001

complexity is provided in Table 3.6.

# C. FPGA implementation result

In our design, the decoders for four different modulation rates are integrated into a reconfigurable 4-D 8PSK TCM decoders. The entire design is first modeled in Matlab for performance simulation and finite wordlength analysis. As we analyzed before, quantization of 7 bits is a good choice for maintaining an acceptable BER performance. Therefore, the 4-D 8PSK TCM decoder with 7-bit quantized input is implemented with Verilog HDL, simulated in Modelsim and synthesized using Xilinx Virtex-4 FPGA (XC4VLX160). The TMUs with both the conventional auxiliary trellis structure and the proposed 2-step comparison architecture are implemented. Both TMUs are designed to have the capability to deal with 4 different modulation rates. In addition, 3 pipeline stages are used for both cases to increase the clock speed. Synthesis results are shown in Table 3.7, where the utilization of the device on FPGA is also shown in percentage.

Although we concluded above that the proposed architecture could reduce the computational complexity by 67%, due to the similar number of registers used for pipelining

|       | $Z_0$          | $Z_1$ | $Z_2$ | $Z_3$ |            | $Z_0$          | $Z_1$          | $Z_2$          | $Z_3$      |       |       |                |          |

|-------|----------------|-------|-------|-------|------------|----------------|----------------|----------------|------------|-------|-------|----------------|----------|

|       | $C_0$          | $C_0$ | $C_0$ |       |            | $C_1$          | $C_1$          | $C_1$          |            |       |       |                |          |

| C     | $C_0$          | $C_2$ | $C_2$ |       |            | $C_1$          | $C_3$          | $C_3$          | a          |       |       |                |          |

| $G_1$ | $C_2$          | $C_2$ | $C_0$ |       | $C_2$      | $\mathbb{C}_2$ | $\mathbb{C}_2$ | $\mathbb{C}_2$ | $C_2  G_2$ | $C_3$ | $C_3$ | $C_3$<br>$C_1$ | $\cup_3$ |

|       | $C_2$          | $C_0$ | $C_2$ |       |            |                |                | $C_3$          |            |       |       |                |          |

|       | $C_0$          | $C_0$ | $C_2$ |       |            | $C_1$          | $C_1$          | $C_3$          |            |       |       |                |          |

| C     | $C_0$          | $C_2$ | $C_0$ | a     | C          | a a            | $C_1$          | $C_3$          | $C_1$      | C     |       |                |          |

| $G_3$ | $C_0$<br>$C_2$ | $C_2$ | $C_2$ | $C_0$ | $C_0  G_4$ | $C_3$          | $C_3$          | $C_1$<br>$C_3$ | $C_1$      |       |       |                |          |

|       | $C_2$          | $C_0$ | $C_0$ |       |            | $C_3$          | $C_1$          | $C_1$          |            |       |       |                |          |

TABLE 3.3: Grouping of the candidates for BM 1000

the circuits for both cases, Table 3.7 only shows half of the hardware reduction.

## 3.3.3 *T*-algorithm on BMs

# A. Applying T-algorithm to BMs

In the 4-D 8PSK TCM system, signals with different modulation rates use the same convolutional code as shown in Fig. 3.2.

Unlike low-rate codes (e.g., 1/2, 1/3) that have 2 incoming paths for each state, high-rate convolutional codes generate many more paths in state transitions (8 in the our case due to 3 input bits). When applying Viterbi decoding on these codes, more BMs are involved (16 in the above case because of the 4 output bits), which increase the computational complexity of the decoder. For example, the computational complexity of the Viterbi decoder for decoding the rate-3/4 convolutional code employed in this 4D TCM system is equivalent to the Viterbi decoder for a rate-1/2 convolutional code with 256 states. Therefore, it is necessary to use some low-power scheme in the design. Motivated by the conventional *T*-algorithm, we found that eliminating redundant additions is an

TABLE 3.4: Grouping of the candidates for BM 1001

|       | $Z_0$ | $Z_1$ | $Z_2$ | $Z_3$ |             | $Z_0$ | $Z_1$ | $Z_2$          | $Z_3$ |       |

|-------|-------|-------|-------|-------|-------------|-------|-------|----------------|-------|-------|

|       | $C_0$ | $C_0$ | $C_0$ |       |             | $C_1$ | $C_1$ | $C_1$          |       |       |

| C     | $C_0$ | $C_2$ | $C_2$ | $C_3$ | $C_3$ $G_2$ | $C_1$ | $C_3$ | $C_3$          | C     |       |

| $G_1$ | $C_2$ | $C_2$ | $C_0$ |       |             | $C_3$ | $C_3$ | $G_2$          | $C_3$ | $C_3$ |

|       | $C_2$ | $C_0$ | $C_2$ |       |             |       |       | $C_3$          |       |       |

|       | $C_0$ | $C_0$ | $C_2$ |       |             | $C_1$ | $C_1$ | $C_3$          |       |       |

| C     | $C_0$ | $C_2$ | $C_0$ | $C_1$ | a           | $C_1$ | $C_3$ | $C_1$          | C     |       |

| $G_3$ | $C_2$ | $C_2$ | $C_2$ |       | $C_1  G_4$  | $C_3$ | $C_3$ | $C_1$<br>$C_3$ | $C_2$ |       |

|       | $C_2$ | $C_0$ | $C_0$ |       |             | $C_3$ | $C_1$ | $C_1$          |       |       |

TABLE 3.5: Computational complexity comparison for RM=11/12 case

| Methods           | Additions | Comparisons |

|-------------------|-----------|-------------|

| Straightforward   | 768       | 240         |

| Auxiliary trellis | 336       | 240         |

| 2-step comparison | 144       | 96          |

effective way to reduce computational complexity. In our case, since the number of BMs is so large, BMs also play a very important role in determining the overall complexity. Since PMs and BMs are evenly distributed in ACSU calculations, purging a BM is equivalent to purging 4 PMs in terms of equivalent number of additions being eliminated. Therefore, the T-algorithm could be applied on BMs, instead of PMs. The process is the same as in the conventional T-algorithm applied on PMs: first, finding the optimal BM - the maximum value of all 16 BMs in our case - and setting up a threshold; then, comparing the difference between each BM and the maximum value. If the difference is larger than the threshold, the corresponding BM is purged, which means that in the ACSU, the additions involving

| Rm                |             | 8/9 | 9/10 | 10/11 | 11/12 |

|-------------------|-------------|-----|------|-------|-------|

| Straightforward   | Additions   | 96  | 192  | 384   | 768   |

| implement         | Comparisons | 16  | 48   | 112   | 240   |

| Conventional      | Additions   | 56  | 112  | 208   | 336   |

| auxiliary trellis | Comparisons | 16  | 48   | 112   | 240   |

| Proposed 2-step   | Additions   | 56  | 80   | 112   | 144   |

| comparison        | Comparisons | 16  | 32   | 64    | 96    |

TABLE 3.6: Computational complexity comparision for all cases

TABLE 3.7: Synthesis results for TMU

| Xc4vlx160-12ff1148 Virtex 4, speed scale 12 $$ |             |                 |  |  |  |

|------------------------------------------------|-------------|-----------------|--|--|--|

|                                                | Number of   | Number of       |  |  |  |

|                                                | 4-input LUT | Slice Flip-flop |  |  |  |

| Auxiliary trellis                              | 14686(10%)  | 3939(2%)        |  |  |  |

| 2-step comparison                              | 7912(5%)    | 1280(0%)        |  |  |  |

the purged BMs are not performed.

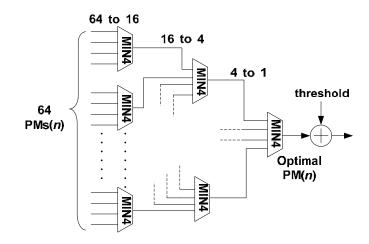

The benefit of applying *T*-algorithm on BMs is obvious. In our case, finding the maximum value of 16 BMs is more efficient than searching for the maximum value of 64 PMs, not only because the number of BMs is less than the number of PMs, but also due to the fact that each BM is the sum of the Euclidian metrics from 4 signal sets. The maximum value of BMs is equivalent to the sum of the maximum Euclidian metrics from each signal set. Finding 4 maximum values and then adding them is much more convenient than finding the maximum value of 16 arbitrary data. Additionally, the processes of finding the maximum value of BMs and calculating 16 BMs could take place in parallel, since the maximum BM is derived directly from the Euclidian metrics. This property can be

explored to eliminate the latency caused by the process of calculating the maximum value in a normal case which needs to obtain the values of all BMs first.

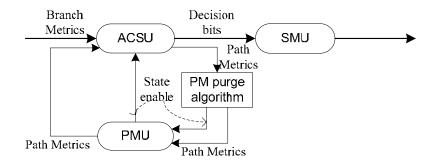

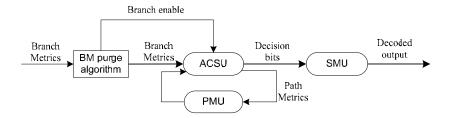

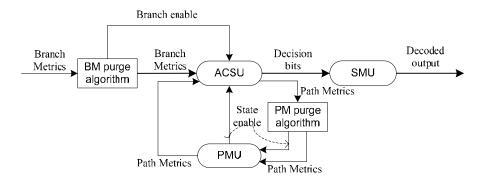

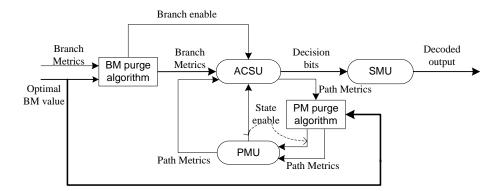

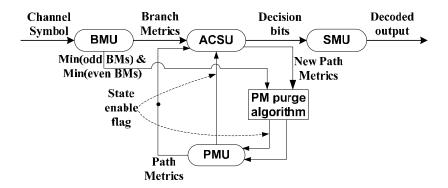

A more important advantage of the proposed method is the improvement of clock speed. The computation of the BMs is a feed-forward process that can be theoretically pipelined to achieve a clock speed as high as needed, and there is no additional process or calculation in the ACS loop. Comparing Fig. 2.3, Fig. 3.9 and Fig. 3.10, it is seen that the VD with T-algorithm applied on BMs maintain almost the same clock speed as the regular VD in Fig. 2.3.

FIGURE 3.9: Functional diagram of a Viterbi decoder with T-algorithm on PM.

FIGURE 3.10: Functional diagram of a Viterbi decoder with T-algorithm on BM.

We have pointed out in Section 3.3.1 that conventional T-algorithm applied on PM could perform well for the RE scheme. When a state is purged in ACSU, the corresponding registers in SMU are not updated; thus, the power consumption is reduced. Generally, the scheme can be implemented by clock gating. For T-algorithm on BMs, when the BMs

involved for calculating a new PM are all purged and the PM can not get a valid value, the corresponding state can be treated as "purged". Again, the registers associated with the "purged" state will not be updated in the SMU.

#### B. Simulation results

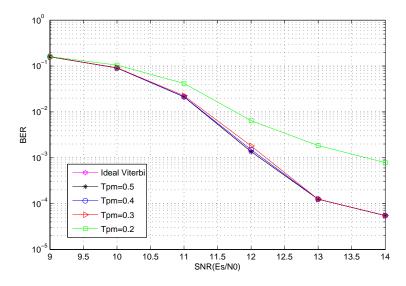

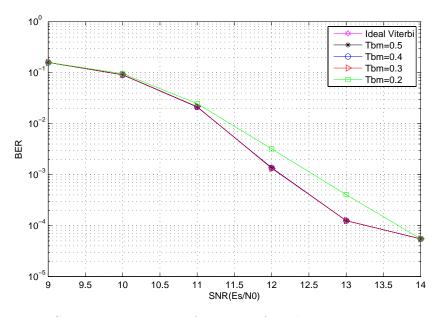

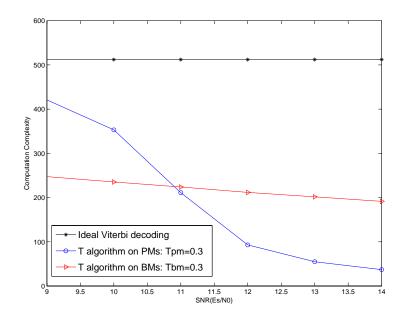

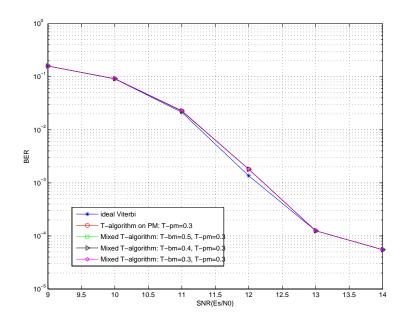

It is necessary to examine the BER performance and computational complexity of the conventional VD with T-algorithm applied on PMs and the proposed VD with T-algorithm applied on BMs. Fig. 3.11 and Fig. 3.12 show the BER performance of these two methods for the case of Rm=11/12. When the threshold drops to below 0.3, a dramatic performance loss for both cases is observed; at a threshold of 0.3, the BER performance of the proposed scheme is slightly better than that of the conventional scheme with T-algorithm applied on PMs.

FIGURE 3.11: BER performance of T-algorithm on PMs.

The corresponding average computational complexity for the case with a threshold of 0.3 is shown in Fig. 3.13. The average computational complexity refers to the number of additions in each cycle. For a regular Viterbi decoder, the computational complexity is

FIGURE 3.12: BER performance of T-algorithm on BMs.

64 (number of states)  $\times$  8 (number of input BMs per state) = 512. From the simulation result shown in Fig. 3.13, we observe that, as the SNR changes, the number of purged computation changes accordingly in the case of *T*-algorithm on PMs, whereas for the case of *T*-algorithm on BMs, the number of purged computation remains almost the same regardless of the channel condition. The performance of *T*-algorithm on BMs behaviors more like the conventional *M*-algorithm, rather than a *T*-algorithm. Therefore, when SNR is low, the computational complexity of the proposed scheme is lower than that of the conventional scheme. In the high-SNR region, however, the conventional scheme has a lower complexity than the proposed one. Although the proposed *T*-algorithm on BMs can not save as many computations as the conventional *T*-algorithm on PMs in the high SNR region, it still has the advantages of lower complexity, higher throughput, and better BER performance.

## C. FPGA implementation result

FIGURE 3.13: Computational complexities of T-algorithm on PMs and BMs.

Since the new scheme is proposed only for ACSU in VD, it can be combined with any type of SMU. To demonstrate the improvements of the proposed T-algorithm on BMs, ACSUs with different algorithms are synthesized. The results are shown in Table 3.8.

| Xc4vlx160-12ff1148 Virtex 4, speed scale 12 |             |                 |                                      |  |  |

|---------------------------------------------|-------------|-----------------|--------------------------------------|--|--|

|                                             | Number of   | Number of       | Max clock                            |  |  |

|                                             | 4-input LUT | Slice Flip-flop | $\operatorname{speed}(\mathrm{MHz})$ |  |  |

| Full trellis                                | 18522(13%)  | 576(0%)         | 103.8                                |  |  |

| T-algorithm on PMs                          | 23326(17%)  | 576(0%)         | 42.5                                 |  |  |

| T-algorithm on BMs                          | 18626(13%)  | 576(0%)         | 102.1                                |  |  |

TABLE 3.8: Synthesis results for ACSU with several schemes

In Table 3.8, "Full trellis" refers to the conventional Viterbi algorithm without any state-reducing scheme, T-algorithm on PMs is the conventional T-algorithm in [31],

and T-algorithm on BMs is the first proposed scheme. Compared with the "Full trellis" case, T-algorithm on BMs requires a slightly more hardware, while the conventional T-algorithm on PMs leads to about 30% hardware overhead. Also, the the proposed T-algorithm on BMs can keep nearly the same clock speed as the "Full trellis" VD, which is more than twice of that for VD employing T-algorithm on PMs.

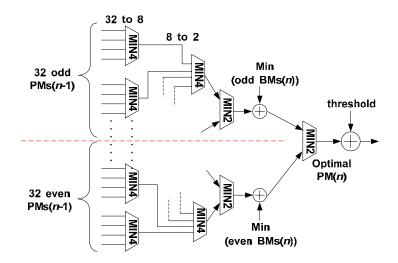

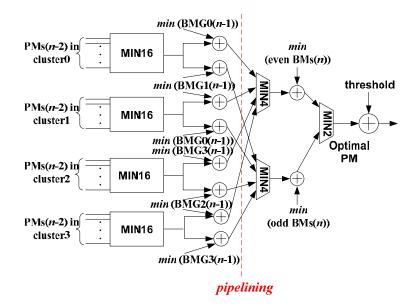

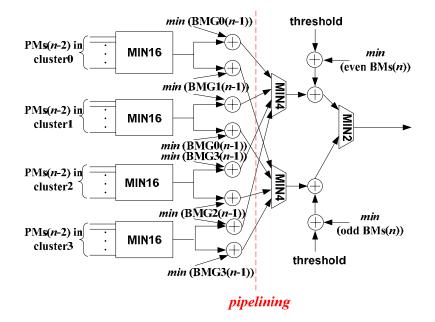

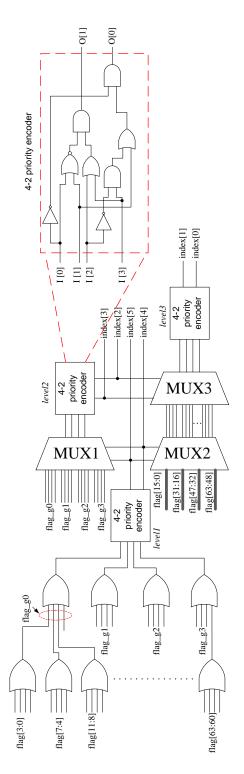

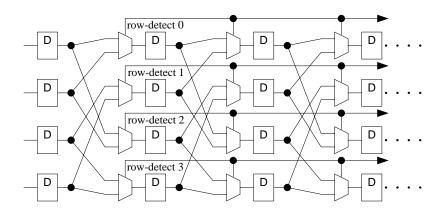

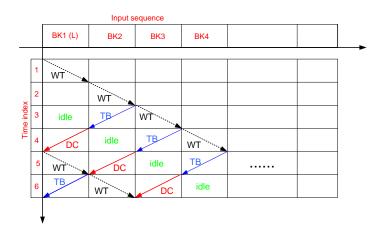

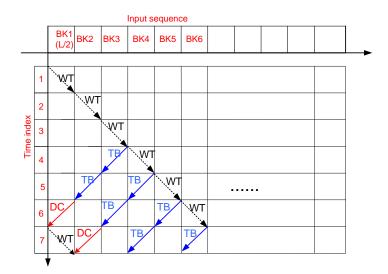

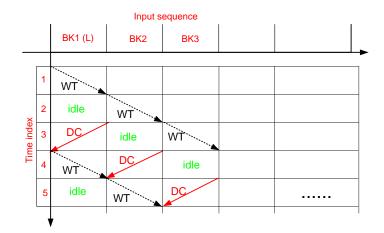

# 3.3.4 Hybrid *T*-algorithm