#### AN ABSTRACT OF THE THESIS OF

James D. Davidson for the degree of Master of Science in Electrical and Computer Engineering presented on October 1, 1991. Title: Capacitance-Voltage Analysis, SPICE Modeling, and Aging Studies of AC Thin Film Electroluminescent Devices.

Abstract approved: Signature redacted for privacy.

Dr. John F. Wager

Alternating-current thin-film electroluminescent (ACTFEL) devices are metal-insulator-semiconductor-insulator-metal (MISIM) structures which emit light under high field, pulsed excitation. One aspect of ACTFEL operation that is not well understood is the aging of such devices with operating time. One of the primary goals of this thesis is to characterize the kinetics of ACTFEL aging and to determine the associated activation energy which is then used as an aid in identifying the physical mechanism responsible for aging. Toward this end a new method, the capacitance-voltage (C-V) technique, for electrical characterization of ACTFEL devices is developed and refined. The threshold voltage ,V<sub>th</sub>, total capacitance C<sub>tot</sub>, and the insulator capacitance, C<sub>ins</sub>, as well as some information about the relative interface state density are

available from C-V analysis.

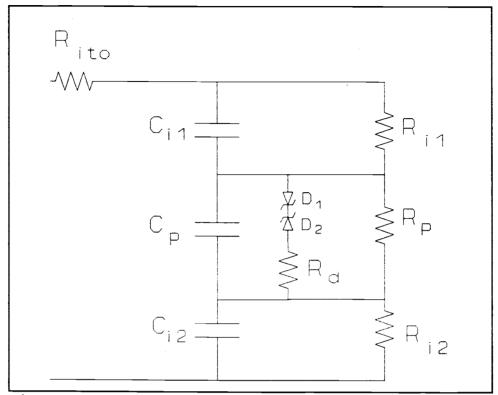

SPICE simulation and a discrete ACTFEL model are used to verify and refine the C-V technique. The heart of the SPICE model is the standard ACTFEL circuit model which consists of three capacitors representing the phosphor and two insulator layers and a pair of back-to-back Zener diodes which account for conduction in the phosphor above threshold. Model enhancements are the inclusion of five resistances which account for 1) the resistance of the transparent conducting layer, R<sub>ito</sub>, 2) and 3) the bulk insulator resistances,  $R_{i1}$  and  $R_{i2}$ , 4) the phosphor layer bulk resistance,  $R_{\rm p}$ , and 5) a diode resistance,  $R_{\rm d}$ , which is in series with the back-to-back Zener diodes and is termed a hot electron resistor since it is associated with the emission of electrons from interface trap states. refined SPICE equivalent circuit is found to give good agreement with experimental C-V curves and with C-V curves generated using a discrete ACTFEL model which is built using discrete capacitors and Zener diodes.

Aging experiments are conducted using the C-V technique to monitor the threshold voltage as a function of aging time over a temperature range of -50 °C to 80 °C. An incubation period, in which the threshold voltage is constant, occurs for temperatures below 20 °C but no incubation period is observed for temperatures above 20 °C. After the incubation period, if any exists, the threshold

voltage increases logarithmically with time to a saturated value which is temperature-dependent; logarithmic and saturated aging are collectively referred to as constituting short-term aging. Short-term aging is characterized by Ctot, Cins, and phosphor threshold voltage which are independent of aging time, rigid shifts in the C-V transition to higher threshold voltages with aging time, and decreases in the conduction and polarization charges with aging time. A kinetic analysis of the variable-temperature ACTFEL aging characteristics results in an activation energy of 0.2 eV. Such experimental observations lead to a model for ACTFEL aging in which conduction electrons are trapped in deep level, fixed charge states which arise from atomic rearrangement at the interface. This trapped charge reduces the polarization charge with a corresponding increase in the threshold voltage.

# Capacitance-Voltage Analysis, SPICE Modeling, and Aging Studies of AC Thin-Film Electroluminescent Devices

by

James D. Davidson

A THESIS

submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Master of Science

Completed October 1, 1991

Commencement June 1992

| Α                     | P | P | R            | 0 | 7.7 | Έ | n  | • |

|-----------------------|---|---|--------------|---|-----|---|----|---|

| $\boldsymbol{\Gamma}$ |   | 1 | $\mathbf{r}$ |   | v   |   | IJ | • |

# Redacted for Privacy

|                                                                                                    |      | ļ    | Neuau    | ieu ii | <i>J</i> I I I | ivacy  |       |        |      |         |      |

|----------------------------------------------------------------------------------------------------|------|------|----------|--------|----------------|--------|-------|--------|------|---------|------|

| Associate Professor of Electrical and Computer Engineering in charge of major Redacted for Privacy |      |      |          |        |                |        |       |        |      |         |      |

| Head                                                                                               | of   | Dep  | artment  | of     | Elect          | trical | and   | Comput | er E | ngineer | ing  |

|                                                                                                    |      |      |          |        |                |        |       |        |      |         |      |

|                                                                                                    |      |      | Redacte  | ed for | Privad         | СУ     |       |        |      |         |      |

| Dean                                                                                               | of   | Grad | duatte s | choo   | V              |        |       |        |      |         |      |

|                                                                                                    |      |      |          |        |                |        |       |        |      |         |      |

|                                                                                                    |      |      |          |        |                |        |       |        |      |         |      |

| Date                                                                                               | the  | sis  | is pre   | sent   | ed             | 0ct    | ober  | 1, 199 | 1    |         |      |

| typed                                                                                              | l by |      |          |        | Ja             | mes D  | . Dav | idson_ |      |         | ···· |

## TABLE OF CONTENTS

| CHAPTER 1 - INTRODUCTION                                       | 1  |

|----------------------------------------------------------------|----|

| CHAPTER 2 - LITERATURE REVIEW OF ACTFEL DEVICES                | 4  |

| 2.1 HISTORY AND BACKGROUND                                     | 4  |

| 2.2 DEVICE DESCRIPTION                                         |    |

| 2.3 PHYSICS OF DEVICE OPERATION                                | 5  |

| 2.3.1 - introduction                                           | 7  |

| 2.3.2 - simplified energy band diagrams of ACTFEL devices      | 7  |

| 2.3.3 - analysis techniques                                    | 11 |

| 2.4 SUMMARY                                                    | 15 |

| CHAPTER 3 - THE C-V TECHNIQUE AND SPICE MODELING               | 17 |

| 3.1 INTRODUCTION                                               | 17 |

| 3.2 THE SPICE CIRCUIT MODEL                                    | 17 |

| 3.3 THE C-V TECHNIQUE                                          | 20 |

| 3.4 PARAMETER EXTRACTION                                       | 24 |

| 3.5 VERIFICATION OF THE ACCURACY OF THE C-V TECHNIQUE          | 27 |

| 3.6 SPICE SIMULATIONS                                          | 30 |

| 3.6.1 - introduction                                           | 30 |

| 3.6.2 - charge, capacitance, and threshold voltage variations  | 32 |

| 3.6.3 - C-V curve variations                                   | 36 |

| 3.7 SUMMARY                                                    | 44 |

| CHAPTER 4 - ACTFEL AGING INSTABILITY ANALYSIS                  | 46 |

| 4.1 INTRODUCTION                                               | 46 |

| 4.2 EXPERIMENTAL TECHNIQUE                                     | 47 |

| 4.2.1 - experiment description                                 | 47 |

| 4.2.2 - initial conditions                                     | 48 |

| 4.3 AGING RESULTS                                              | 50 |

| 4.4 ACTIVATION ENERGY EXTRACTION                               | 59 |

| 4.4.1 - Arrhenius analysis                                     | 59 |

| 4.4.2 - activation energy from aging kinetics                  | 60 |

| 4.5 AGING ELECTROSTATICS                                       | 65 |

| 4.6 PHYSICAL MECHANISMS OF AGING                               | 70 |

| 4.7 SUMMARY                                                    | 76 |

| CHAPTER 5 - CONCLUSIONS AND RECOMMENDATIONS<br>FOR FUTURE WORK | 78 |

| BIBLIOGRAPHY                                                   | 82 |

# LIST OF FIGURES

| Figur         | <u>es</u>                                                                                                               | <u>Page</u> |

|---------------|-------------------------------------------------------------------------------------------------------------------------|-------------|

| 1-1.          | A possible three-color ACTFEL process.                                                                                  | 2           |

| 2-1.          | Typical ACTFEL structure and dimensions.                                                                                | 6           |

| 2-2.          | Virgin energy band diagram of ACTFEL device.                                                                            | 8           |

| 2-3.          | ACTFEL energy band diagram during positive bias.                                                                        | 10          |

| 2-4.          | ACTFEL energy band diagram after positive bias.                                                                         | 10          |

| 2-5.          | ACTFEL energy band diagram during negative bias.                                                                        | 10          |

| 2-6.          | ACTFEL energy band diagram after negative bias.                                                                         | 10          |

| 2-7.          | Typical Q-V measurement circuit.                                                                                        | 12          |

| 2-8.          | Typical Q-V measurement result.                                                                                         | 13          |

| 2-9.          | The I-V measurement circuit.                                                                                            | 14          |

| 3-1.          | Simple SPICE equivalent circuit.                                                                                        | 18          |

| 3-2.          | Enhanced SPICE equivalent circuit model.                                                                                | 19          |

| 3-3.          | Measurement circuit for C-V analysis.                                                                                   | 20          |

| 3-4.          | Standard driving waveform. RT - rise time, FT - fall time, PW - pulse width, and $V_{\rm m}$ - maximum driving voltage. | 21          |

| 3 <b>-</b> 5. | A labeled C-V curve showing capacitances, threshold voltages, and standard terminology.                                 | 23          |

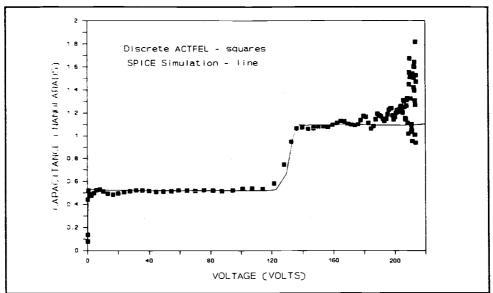

| 3-6.          | Comparison of SPICE C-V simulations with the discrete component ACTFEL device.                                          | 28          |

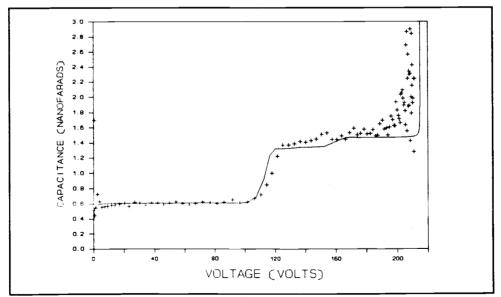

| 3-7.          | SPICE C-V simulation compared to data from a real ACTFEL device.                                                        | 29          |

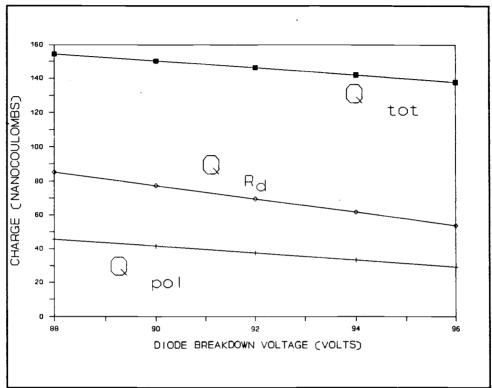

| 3-8.          | SPICE simulated charge versus diode breakdown voltage, BV.                                                              | 33          |

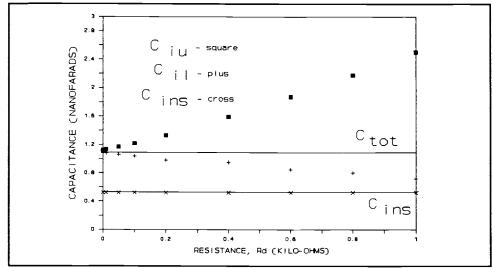

| 3-9.          | SPICE simulated capacitance versus resistance, R <sub>d</sub> .                                                         | 34          |

| 3-10          | SPICE simulated capacitance versus resistance, R <sub>ito</sub> .                                                       | 34          |

| 3-11. | SPICE simulated threshold voltage, $V_{\text{th2}}$ , versus resistance, $R_{\text{d}}$ .                                                                                        | 35         |  |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--|

| 3-12. | SPICE simulated threshold voltage, $V_{\text{th2}}$ , versus diode breakdown voltage, BV.                                                                                        | 35         |  |

| 3-13. | SPICE simulated threshold voltage, $V_{\text{th2}}$ , versus resistance, $R_{\text{p}}$ .                                                                                        | 36         |  |

| 3-14. | C-V curves for parametric variations of $R_{ito}$ . $R_{ito} = 0$ , 30, and 100 ohms. Arrows indicate an increasing value for $R_{ito}$ .                                        | 38         |  |

| 3-15. | Circuit used to examine the capacitance step observed in C-V curves in the conduction region.                                                                                    | 38         |  |

| 3-16. | C-V curves for parametric variation of $R_i$ .<br>$R_i = 10k$ , $100k$ , $10^6$ , and $10^{14}$ ohms. Arrows indicate an increasing value for $R_i$ .                            | 40         |  |

| 3-17. | C-V curve for parametric variation of $R_p$ . $R_p = 10k$ , $100k$ , $2x10^6$ , and $10^7$ ohms. Arrows indicate an increasing value for $R_p$ .                                 | 40         |  |

| 3-18. | C-V curves for parametric variations of BV. BV = 88, 90, 92, 94, and 96 volts. Arrow indicate an increasing value for BV.                                                        | 41         |  |

| 3-19. | C-V curves for parametric variations of $R_d$ . $R_d = 0$ , 50, 100, 200, and 1000 ohms. Arrows indicate an increasing value for $R_d$ .                                         | 41         |  |

| 4-1.  | Block diagram of the aging experimental setup.                                                                                                                                   | 48         |  |

| 4-2.  | Initial room temperature threshold voltages, $V_{\rm th2}$ , for glass 7-26-90-15 and adjusted threshold voltages at which the aging experiments begin.                          | 49         |  |

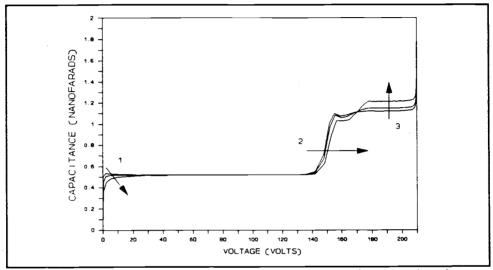

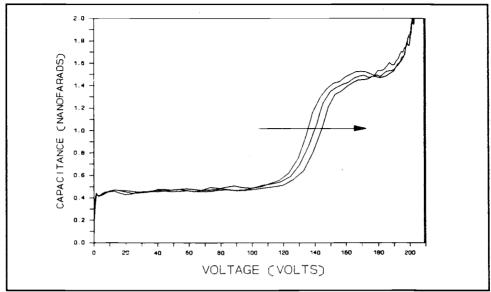

| 4-3.  | Family of C-V curves for the 60 °C experiment with aging times of 1 second, 20 minutes, and 9.5 hours. Arrow indicates the direction of threshold voltage shift with aging time. | 5 <b>1</b> |  |

| 4-4.  | Threshold voltage, $V_{\text{th2}}$ , for all temperatures as a function of aging time.                                                                                          | 51         |  |

|       |                                                                                                                                                                                  |            |  |

| 4-5.  | Threshold voltage, $V_{\text{th2}}$ , for all temperatures as a function of the <u>natural logarithm</u> of aging time. | 52 |

|-------|-------------------------------------------------------------------------------------------------------------------------|----|

| 4-6.  | Threshold voltage, $V_{\text{th2}}$ , as a function of aging time at a temperature of -50 °C.                           | 52 |

| 4-7.  | Threshold voltage, $V_{\text{th2}}$ , as a function of aging time at a temperature of -10 °C.                           | 53 |

| 4-8.  | Threshold voltage, $V_{\text{th2}}$ , as a function of aging time at a temperature of 0 °C.                             | 53 |

| 4-9.  | Threshold voltage, $V_{\text{th2}}$ , as a function of aging time at a temperature of 20 °C.                            | 54 |

| 4-10. | Threshold voltage, $V_{\text{th2}}$ , as a function of aging time at a temperature of 60 °C.                            | 54 |

| 4-11. | Threshold voltage, $V_{\text{th2}}$ , as a function of aging time at a temperature of 80 °C.                            | 55 |

| 4-12. | Temperature dependence of the $-50$ °C dot threshold voltage, $V_{\rm th2}$ , after the aging experiment was completed. | 58 |

| 4-13. | Initial and final threshold voltages, $V_{\text{th2}}$ , for all aging samples as a function of temperature.            | 58 |

| 4-14. | Normalized shift in threshold voltage, $V_{\rm th2}$ , as a function of aging time at a temperature of -50 °C.          | 61 |

| 4-15. | Normalized shift in threshold voltage, $V_{\text{th2}}$ , as a function of aging time at a temperature of -10 °C.       | 62 |

| 4-16. | Normalized shift in threshold voltage, $V_{\text{th2}}$ , as a function of aging time at a temperature of 0 °C.         | 62 |

| 4-17. | Normalized shift in threshold voltage, V <sub>th2</sub> , as a function of aging time at a temperature of 20 °C         | 63 |

- 4-18. Normalized shift in threshold voltage,  $V_{\rm th2}$ , 63 as a function of aging time at a temperature of 60 °C.

- 4-19. Normalized shift in threshold voltage,  $V_{\rm th2}$ , as a function of aging time at a temperature of 80 °C.

- 4-20. Arrhenius plot of the aging experiment data. 64

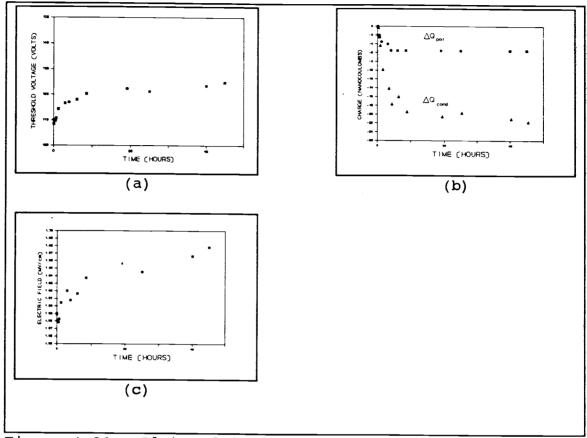

- 4-21. Plots of (a) threshold voltage,  $V_{\rm th1}$ , (b) charge 69  $Q_{\rm pol}$  and  $Q_{\rm cond}$ , and (c) phosphor electric field as a function of aging time for glass 7-26-90-15 dot 3.

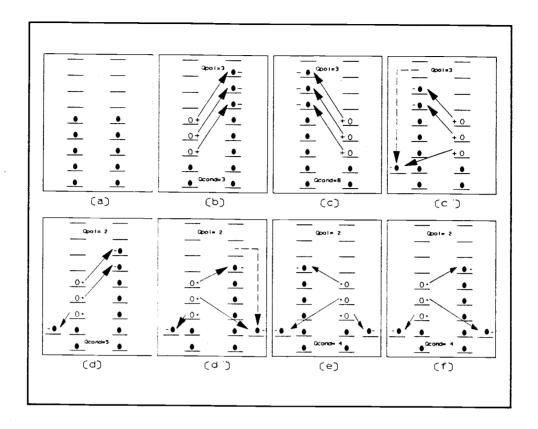

- 4-22. Idealized electron transport and trapping 71 sequence for an ACTFEL device with symmetric interfaces. (a) equilibrium; charge neutrality exists, (b) negative bias; no trapping, (c') maintain positive bias; no trapping, (c') maintain positive bias; trap 1 electron, (d) negative bias; no trapping, (d') maintain negative bias; trap 1 electron, (e) positive bias; no further trapping, (f) negative bias; no further trapping.

#### LIST OF TABLES

| <u>Table</u> | <u>s</u>                                                                                       | <u>Page</u> |

|--------------|------------------------------------------------------------------------------------------------|-------------|

| 3-1.         | A summary of nominal circuit component values and their range of variation for SPICE modeling. | 31          |

| 3-2.         | Summary of the effect of parameter variations on C-V curves.                                   | 43          |

| 4-1.         | Summary of temperature-dependent rate constants, intercepts, and correlation of fit.           | 65          |

| 4-2.         | The Arrhenius straight line fit parameters.                                                    | 65          |

| 4-3.         | Estimated migration energies for nearest-                                                      | 74          |

Capacitance-Voltage Analysis, SPICE Modeling, and Aging Studies of AC Thin-Film Electroluminescent Devices.

#### CHAPTER 1 - INTRODUCTION

Alternating-current thin-film electroluminescent (ACTFEL) devices are currently used for monochrome flat panel display applications. The ultimate goal of this technology is to have displays with full color, grey scale, long operating lifetime, and to meet high definition television (HDTV) standards. These goals are believed to be achievable<sup>1,2</sup>.

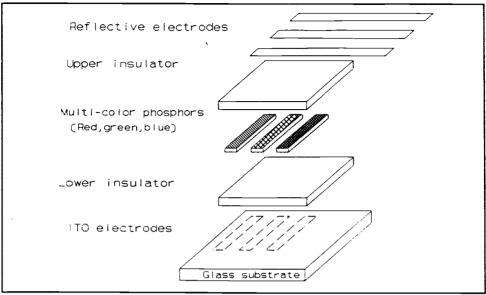

To meet these goals, ACTFEL process technology needs to be developed so that red, green, and blue ACTFEL phosphors may be patterned onto glass substrates in matrix-addressable patterns. Currently a two-color, red/green display has been designed. The prototype of the two-color display was unveiled at the Society for Information Display (SID) conference in 1991. A possible configuration for a three-color display is shown in Fig. 1-1.

Addressing circuitry must also be developed that meets the criteria for HDTV. The 40-inch diagonal size for HDTV may present some production problems since no defects are allowable. As a further consideration, brightness must be stable and controllable over the rated lifetime.

Aging instabilities which affect panel brightness are a poorly understood phenomenon that currently is circumvented by pre-aging ACTFEL panels prior to commercial usage.

Figure 1-1. A possible three-color ACTFEL process.

The purpose of the work described in this thesis is to understand the nature of the aging instability by relating shifts in the threshold voltage to changes associated with the aging process. To this end we have developed and refined a capacitance-voltage (C-V) technique for the electrical characterization of ACTFEL devices and have used the C-V technique to monitor the threshold voltage shift during aging. The refinements of the C-V technique consist of optimization of the current limiting resistor used in the data acquisition circuit and optimization of the digital sampling period which increases the signal-to-noise ratio of the C-V measurement system. Additionally, a simple equivalent circuit for the ACTFEL in conjunction with SPICE

modeling is used for verification and refinement of the C-V technique as well as for further exploration of the basic device physics of ACTFEL performance.

Once the C-V technique is refined, it is used to track the threshold voltage shift as a function of aging time and as a function of temperature. Subsequently, the aging kinetics are modeled and Arrhenius analysis is used to deduce an activation energy for the aging process of 0.2 eV. The aging mechanism associated with this activation energy is believed to be due to atomic migration at the interfaces.

In Chapter 2 a discussion of the current understanding of ACTFEL device physics and operation is provided. The C-V technique and SPICE modeling are presented in Chapter 3. Chapter 4 consists of an examination of aging instabilities and an analysis of the aging kinetics. Conclusions and recommendations for further work are given in Chapter 5. It should be noted that some of the work described in this thesis has been previously published or submitted for publication<sup>3,4,5,6,7</sup>.

CHAPTER 2 - LITERATURE REVIEW OF ACTFEL DEVICES

2.1 HISTORY AND BACKGROUND

The use of high electric fields to produce light from phosphor powders was first discovered in the early 1900's. However, not until the advent of thin-film technology has this phenomenon been useable for display technology. ACTFEL devices with long-term stability were first introduced in 1974 by Inoguchi<sup>8</sup>. These devices have matured from laboratory experiments to commercial mass production of 18-inch diagonal, monochrome displays. Additional research is necessary to understand all the phenomena associated with ACTFEL devices.

Degradation of light output with operating time limits the useful lifetime of production devices. Currently ACTFEL devices show an initial rapid change in light output followed by very small changes over the rest of the expected lifetime. The cause of the initial change in light output is the focus of the work in this thesis.

Much research is centered on developing full color capability. The future of ACTFEL flat panel displays holds much promise since the ability to generate the three primary colors has been demonstrated in several laboratories<sup>9,10,11</sup>. The major technical problems impeding the development of full color ACTFEL display technology are attainment of a blue phosphor with sufficient luminescent

intensity and proper chromaticity and the integration of a three color system onto a single substrate. Recently, two-color (red/green) displays have been demonstrated<sup>12</sup>. A demonstration of three-color ACTFEL display is expected from Planar Systems by 1993<sup>13</sup>.

#### 2.2 DEVICE DESCRIPTION

ACTFEL devices are built using low temperature processing methods. The low temperature is needed to protect the ITO conducting layer and the glass substrate. Currently, production ACTFEL devices are built using either sputtering, evaporation, or atomic layer epitaxy (ALE) 14.

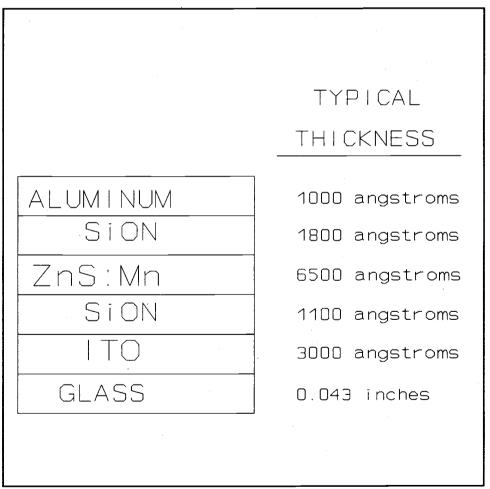

The ACTFEL structure is shown in Fig. 2-1. The devices tested in this thesis use the materials and thicknesses shown in Fig. 2-1. The glass substrate is 7059 Corning glass which is covered with a transparent layer of indium-tin-oxide (ITO). The insulator layers are sputtered silicon-oxy-nitride and the phosphor layer is evaporated zinc sulfide doped with manganese (Mn). The ACTFEL device is annealed before Al deposition at 450 °C for 60 minutes. The aluminum layer is then applied by evaporation. The sputtered insulator layers are amorphous and the ZnS layer is polycrystalline in nature.

Other material systems are also used for ACTFEL fabrication. Some insulators which have been used include

Y<sub>2</sub>O<sub>3</sub>, Al<sub>2</sub>O<sub>3</sub>, Ta<sub>2</sub>O<sub>5</sub>, Al<sub>2</sub>O<sub>3</sub>-TiO<sub>2</sub>, and, Si<sub>3</sub>N<sub>4</sub><sup>15-19</sup>. ZnS:Mn, which emits a yellow luminescence characteristic of the Mn dopant, is the most common monochrome display phosphor. CaS and SrS are phosphors that use rare-earth dopants to produce primary colors. Some of the most notable rare-earth dopants include europium (Eu), terbium (Tb) and cerium (Ce) which are used to produce red, green, and blue-green light, respectively.

Figure 2-1. Typical ACTFEL structure and dimensions.

#### 2.3 PHYSICS OF DEVICE OPERATION

#### 2.3.1 - introduction

Various authors have described the operation of ACTFEL devices, including Sahni<sup>20</sup>, Mach<sup>21</sup> and Inoguchi<sup>8</sup>. In the following section simplified energy band diagrams for virgin and aged devices are examined in order to provide an understanding of how ACTFEL devices operate. This is followed by a brief description of the various techniques used to characterize ACTFEL devices. The physical phenomena observed by using these characterization methods are discussed along with limitations of each particular technique.

# 2.3.2 - simplified energy band diagrams of ACTFEL devices

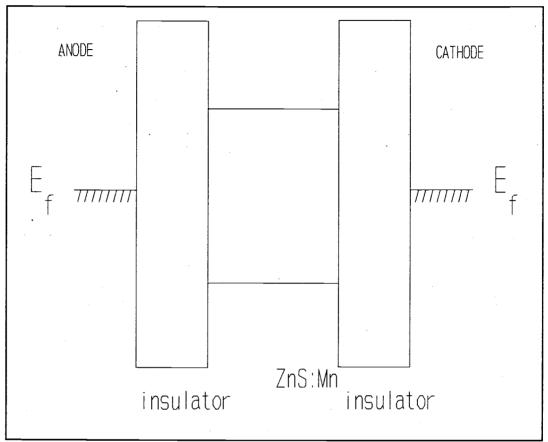

The band gap of ZnS is 3.68 eV and the band gap of the SiON insulators is about 5.8 eV. The ACTFEL structure is assumed to be homogeneous for each region. The nature of the ZnS-SiON interface is not completely known. However, it is generally accepted that the interface regions are depleted of sulfur and that a large number of interface states exist ( $\approx 10^{13}/\mathrm{cm}^3$ ). To understand the operation of the ACTFEL device under an alternating voltage waveform, simplified band diagrams as shown in Figs. 2-2 through 2-6 are used. In these diagrams the interface is modeled as ideal.

Figure 2-2. Virgin energy band diagram of ACTFEL device.

Under a symmetric bipolar voltage waveform there is a tilting of the energy band diagram from the virgin state and a build-up of polarization charge at the ZnS-SiON interfaces. The virgin state is considered to be that state where the internal polarization charge is identically zero. The virgin state energy band diagram is shown in Fig. 2-2. The effect of positive and negative biasing is explained as follows.

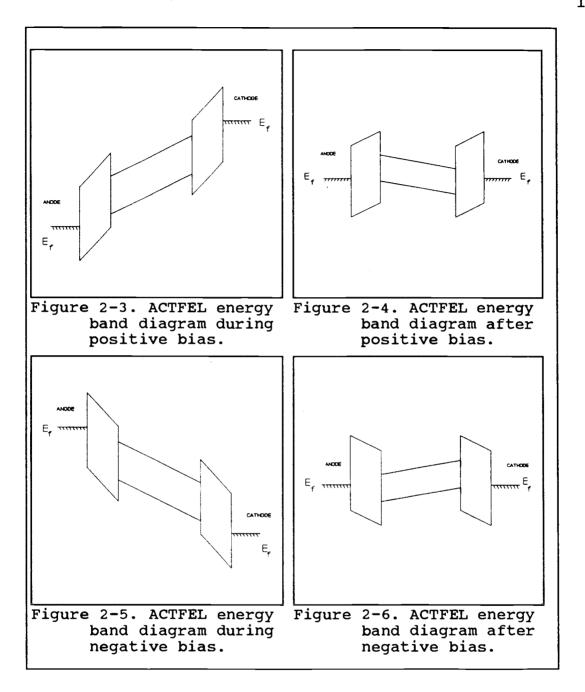

Assume that positive biasing of the device occurs at the anode. Under this bias the energy band diagram is as shown in Fig. 2-3. Electric potential is dropped across each region until the ZnS-SiON interface starts to tunnelemit electrons. When electron conduction occurs across the ZnS layer, the ZnS electric field is effectively clamped due to an abundance of tunnel-injected electrons from interface states. As positive bias is further increased the electric potential is dropped across the SiON insulators. Tunnel-injected electrons transit the ZnS region under the applied field, are trapped at the cathodic interface, and set up an opposing electric potential. When the positive bias returns to zero, the external electric potential goes to zero, but the internal electric field in the ZnS due to electron trapping at the cathode interface remains, and is referred to as the internal polarization The energy band diagram, as shown in Fig. 2-4, results after the polarization charge is transferred during the positive bias, and after the external voltage goes to zero. The polarization charge is assumed to remain constant during the delay time between alternating pulses which is typically, at a frequency of 1000 Hertz, of the order of 0.5 milliseconds.

During the subsequent opposite polarity pulse the internal polarization field aids the external electric field causing electrons to tunnel from interface trap states at a lower external bias magnitude than for the

previous polarity pulse. This results in an increase in the internal charge transferred and a concomitant increase in the polarization field. This process repeats until a steady state is reached at which time the magnitude of the internal polarization charge for each voltage pulse is the same. Figures 2-5 and 2-6 show the energy band diagram during and after, respectively, the negative bias waveform.

#### 2.3.3 - analysis techniques

The methods typically used to characterize ACTFEL device operation are the charge-voltage (Q-V), luminance-voltage (L-V), also called brightness-voltage (B-V), and current-voltage (I-V) methods. All three methods may be used to define a threshold voltage. Q-V also may be used to determine total and insulator capacitance, and the conduction and polarization charges. L-V is a production tool used to set panel brightness and grey scale and to monitor luminance shift with operating time. I-V is the only technique that directly attempts to determine the internal operation of ACTFEL devices. In this thesis a new method is developed, the capacitance-voltage (C-V) technique, which is discussed in Chapter 3.

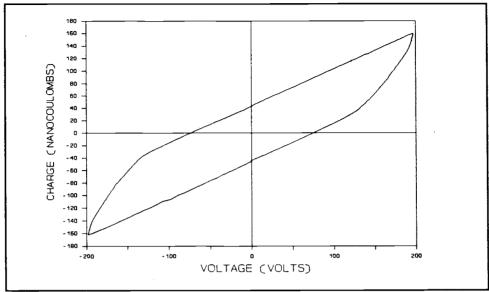

The Q-V technique<sup>22</sup> employs the Sawyer-Tower method for determining charge as shown in Fig. 2-7.  $Q_{pol}$ ,  $Q_{tot}$ ,  $Q_{cond}$  and the threshold voltage are determined directly from the Q-V curves.  $C_{tot}$  and  $C_{ins}$  are determined from the slope of the Q-V curve before and after the threshold voltage. Figure 2-8 shows an ideal Q-V waveform. Through experimentation it is found that this technique is

sensitive to the type and quality of the sense capacitor,  $C_{\rm sense}$ , used in the circuit. The dissipation of  $C_{\rm sense}$  must be very small to ensure that significant charge does not leak from  $C_{\rm sense}$  during the long delay time associated with using a pulsed voltage waveform. Also  $C_{\rm sense}$  is generally 100 times the total capacitance of the ACTFEL device to ensure the voltage change across  $C_{\rm sense}$  is small compared to the voltage across the ACTFEL device. A modification of this method gives the charge-time (Q-t) waveform which is a plot of the charge accumulated on  $C_{\rm sense}$  as a function of time. Again, these charge techniques are sensitive to the type of sense capacitor used in the test circuit.

Figure 2-7. Typical Q-V measurement circuit.

Figure 2-8. Typical Q-V measurement result.

Another widely used characterization method is the L-V technique. The L-V method<sup>23</sup> measures the light output as a function of applied bias. The peak of the voltage waveform is ramped from zero volts to 40 volts above the threshold voltage and the luminance is monitored.

Light output is a function of many factors such as,

1) the transmission through each layer, 2) the doping

concentration, and 3) viewing angle. Since many factors

affect luminance, it is extremely difficult to relate

changes in brightness to changes in the electronic nature

of the ACTFEL structure. However, luminance versus applied

voltage is the final criterion for the determination of how

well an ACTFEL device operates.

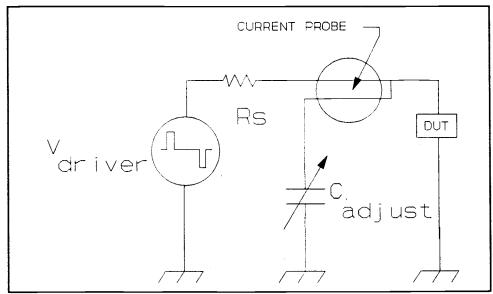

The I-V technique<sup>22</sup> attempts to measure the conduction

current through ACTFEL devices by the use of a capacitor bridge. This technique is susceptible to measurement errors since the ACTFEL device can not strictly be modeled as a capacitor when electron conduction occurs at and above the threshold voltage. The I-V test circuit is shown in Fig. 2-9.

Figure 2-9. The I-V measurement circuit.

The I-V measurement system is calibrated by nulling the current through the ACTFEL device, using a variable capacitor, while the device is operated at a sub-threshold voltage. The ACTFEL device is then operated above threshold and the conduction current through the ZnS layer is determined by multiplying the measured current by the ratio  $\frac{(C_{ins} + C_p)}{C_{ins}}$ , where  $C_{ins}$  is the capacitance due to both insulating layers and  $C_p$  is the phosphor layer

capacitance of the device. Most measurement error occurs at the initiation of conduction and before field clamping takes place. The reason is explained as follows.

Before conduction the bridge circuit is balanced. After initiation of conduction the ACTFEL device capacitance increases due to conduction through the ZnS layer. Once field clamping occurs then the ACTFEL capacitance is fixed at C<sub>ins</sub>. Between the subthreshold and field clamping regimes, as described in Chapter 3, the capacitance is transitory and is not accurately modelled by the given equations. This results in an error when calculating conduction current. Several authors have provided methods to decrease the error in conduction current calculations<sup>24,25</sup>.

#### 2.4 SUMMARY

ACTFEL devices show a promising future. Full color capability and grey scale should soon be available in smaller display sizes. Problems associated with aging instabilities and color technology integration are surmountable.

There are currently three methods of characterizing ACTFEL devices; Q-V, L-V, and I-V. A fourth method, the C-V technique, is discussed in Chapter 3. Each of the four characterization methods is simple to implement and the

results are easy to understand. However, improvements to the basic characterization techniques need to be made in order to increase the accuracy and information that may be obtained.

# CHAPTER 3 - THE C-V TECHNIQUE AND SPICE MODELING 3.1 INTRODUCTION

Electrical characterization of ACTFEL devices is usually accomplished by charge-voltage (Q-V), luminance-voltage (L-V), or current-voltage (I-V) analysis. We have recently described<sup>3</sup> the C-V technique as an alternative method for ACTFEL electrical characterization. Our goal for the work described herein is to show that the C-V technique, in conjunction with SPICE modeling using a simple equivalent circuit, provides a powerful means of probing ACTFEL device physics.

The SPICE model for the ACTFEL structure is discussed in Section 3.2. The C-V technique and driving waveform are discussed in Section 3.3 of this chapter. Section 3.4 examines how values are obtained for the enhanced SPICE model parameters. Section 3.5 compares C-V curves obtained from SPICE simulation, an ideal discrete ACTFEL device, and real ACTFEL devices. Parametric variations of selected SPICE model elements are examined in Section 3.6. Section 3.7 is a summary of the chapter.

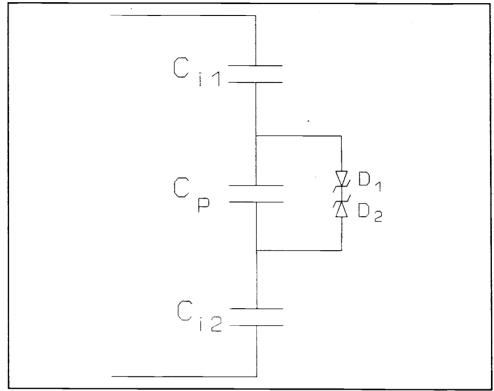

### 3.2 THE SPICE CIRCUIT MODEL

The simple equivalent circuit for SPICE simulation of the ACTFEL device  $^{26}$  is shown in Fig. 3-1.  $C_{i1}$  and  $C_{i2}$  are the insulator capacitances and  $C_{p}$  is the phosphor

Figure 3-1. Simple SPICE equivalent circuit model.

capacitance. The phosphor capacitance is shunted by two back-to-back Zener diodes. These diodes are characterized by only one parameter, the breakdown voltage, BV, beyond which conduction occurs. These circuit components constitute what is termed an ideal circuit model for the ACTFEL device.

This circuit provides a general description of ACTFEL device operation. In order to more completely describe the electrical characteristics of ACTFEL devices, five additional resistors are added to the ideal equivalent circuit to obtain the SPICE equivalent circuit of Fig. 3-2.

Figure 3-2. Enhanced SPICE equivalent circuit model.

$R_{i1}$ ,  $R_{i2}$ , and  $R_p$  represent the parallel shunt resistances of the respective insulator or phosphor layers which are associated with dc leakage through these layers.  $R_{ito}$  is a lumped resistance accounting for the non-zero series resistance of the ITO electrode.  $R_d$  is used to model tunneling from interface states which limits the current flow during conduction in the ZnS layer.  $R_d$  is denoted the diode resistor or is alternately referred to as a hot electron resistor. The effects on C-V curves due to parametric variations of these resistances are discussed in Section 3.6.3 of this chapter.

#### 3.3 THE C-V TECHNIQUE

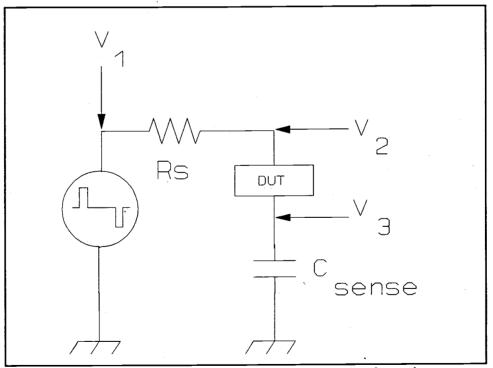

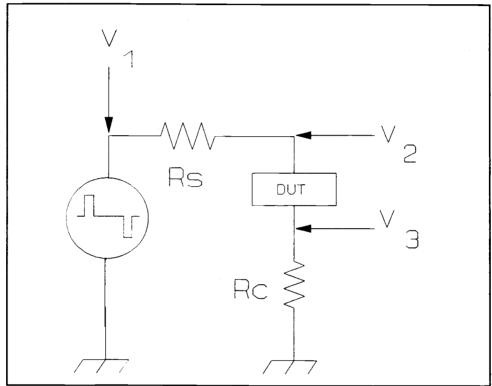

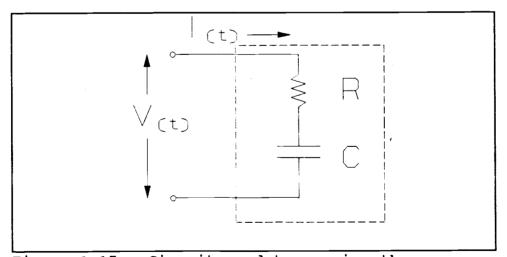

C-V analysis is accomplished using the circuit shown in Fig. 3-3. An arbitrary waveform generator (Wavetek model 275) in conjunction with a high-voltage operational

Figure 3-3. Measurement circuit for C-V analysis.

amplifier (Apex PA-85) generates the small duty cycle bipolar pulse waveform which drives a series resistor,  $R_{\rm g}$ , the ACTFEL device, and a current sense resistor,  $R_{\rm c}$ , as shown in Fig. 3-3.  $R_{\rm s}$  is chosen to be large, typically 1200 ohms. This ensures that the driving waveform does not destroy the ACTFEL device because the current is limited by  $R_{\rm s}$ .  $R_{\rm c}$  is chosen to be about 10 ohms so that the voltage

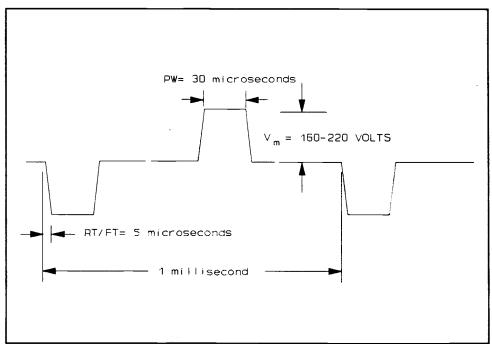

drop across  $R_c$  is negligible. The three voltages indicated in Fig. 3-3 ( $V_1$ ,  $V_2$ , and  $V_3$ ) correspond to the driver, the ACTFEL device, and the current sense voltages, respectively. The standard waveform employed is shown in Fig. 3-4. The waveform consists of symmetric, bipolar pulses of trapezoidal shape with  $5\mu s$  rise and fall times and a pulse width of  $30\mu s$  where rise and fall times are defined as the time between 0 % and 100 % of the maximum amplitude and the pulse width is defined as the duration during which the pulse is at its maximum amplitude. The frequency of the waveform is 1000 Hertz. This waveform is

Figure 3-4. Standard driving waveform. RT - rise time, FT - fall time, PW - pulse width, and  $V_{\rm m}$  - maximum driving voltage.

typical of driving waveforms used for commercial ACTFEL drivers with the exception of frequency, which is usually 60 Hz. Note that standard definitions of rise time, fall time, and pulse width are not used for the waveform definition.

The measurement is performed in the following manner. Voltages  $V_2(t)$  and  $V_3(t)$  are obtained using a Tektronix model 7854 digitizing oscilloscope with high input impedance probes. A 100 point average of the respective voltages, an oscilloscope time base setting of 2  $\mu$ s per division, and 128 points per waveform give best results. The calculation of C-V curves then proceeds as follows.

Referring to the circuit shown in Fig. 3-3, the current through the ACTFEL device is obtained from the voltage across the sense resistor,  $R_{\rm c}$ ,

$$I(t) = \frac{V_3(t)}{R_C}$$

(3-1)

The capacitance is equal to the current divided by the derivative of the voltage across the ACTFEL device, so that the C-V curve is obtained as

$$C(V_2 - V_3) \triangleq \frac{I(t)}{d[V_2(t) - V_3(t)]/dt}$$

(3-2)

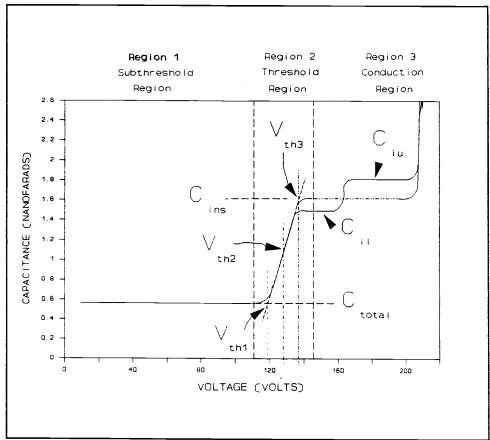

The resulting C-V curve is labelled as shown in Fig. 3-5.

Figure 3-5. A labeled C-V curve showing capacitances, threshold voltages, and standard terminology.

The labels are required to explain changes in the C-V curves due to aging or other causes. The curve is divided into three voltage regions denoted subthreshold, threshold, and conduction. Also, three threshold voltages are distinguished as follows:

- 1)  $V_{th1}$ , the onset of conduction,

- 2)  $V_{\text{th3}}$ , the field clamping voltage, and

- 3)  $V_{\text{th2}}$ , the Q-V threshold voltage.

Two constant capacitance regimes,  $C_{\rm tot}$  and  $C_{\rm ins}$  are also labeled. These refer to the pre-breakdown capacitance,

$C_{

m tot}$ , which corresponds to the total capacitance of the ACTFEL structure prior to breakdown and the insulator capacitance,  $C_{

m ins}$ , which is the capacitance due exclusively to the insulator layers after breakdown when the phosphor capacitance is shunted by conduction through the phosphor.

Under certain conditions, described in Section 3.6.3,  $C_{\rm ins}$  splits into what is called an upper insulator capacitance,  $C_{\rm iu}$ , and a lower insulator capacitance,  $C_{\rm il}$ . This condition is due to non-field clamping conduction. Field clamping requires that two conditions be met.

- 1) the  ${\rm C}_{\rm ins}$  value is flat after breakdown, and

- C<sub>ins</sub> is the expected insulator capacitance as determined by Eqn. 3-3.

#### 3.4 PARAMETER EXTRACTION

In this section simple methods for determining SPICE model parameter values are discussed. These methods are used to obtain nominal values for the ACTFEL devices tested. Part of SPICE analysis is to determine how variations from nominal values affect charge, capacitance, and threshold voltage. The parameter values used in the SPICE model are estimated in accordance with the following considerations.  $C_{i1}$ ,  $C_{i2}$ , and  $C_p$  are calculated as parallel plate capacitors,

$$C = \epsilon * \frac{A}{d} \tag{3-3}$$

where  $\epsilon$  is the permittivity of the respective layer, **A** is the area, and **d** is the thickness of the layer.

$V_{th1}$  and  $V_{th3}$  are obtained graphically by drawing a straight line through the most linear portion of the C-V transition to the points at which this line intersects an extension of  $C_{tot}$  or  $C_{ins}$ , respectively.  $V_{th2}$  is obtained as the average of  $V_{th1}$  and  $V_{th3}$ .  $V_{th2}$  is found to correspond well with the threshold voltage obtained from Q-V analysis. This external threshold voltage may be used to estimate an internal diode breakdown voltage using the following equation;  $BV = V_{pol} + V$

$V \frac{ext}{p} = \frac{\mathcal{Q}_{ext}}{C_p}$  where  $\mathcal{Q}_{ext}$  is the charge accumulated on the device up to  $V_{th1}$  and  $C_p$  is the phosphor layer capacitance. By adding the polarization voltage,  $V_{pol}$ , and  $V \frac{ext}{p}$  a value for BV is obtained. The evaluated range of BV for C-V curve variations is 88 to 96 volts.

R<sub>i</sub> values are determined by the quality of the insulators. SiON insulators, processed similar to the

devices used in this work, evaluated using a corona discharge method at the David Sarnoff Research Center, are found to have a very high resistivity,  $^{27}$  on the order of  $10^{15}$ - $10^{16}$   $\Omega$ -cm. Using this value it is possible to determine the resistance of the SiON layers. The resistance is calculated using the simple bulk resistance method,

$$R = \rho \, \frac{L}{A} \tag{3-6}$$

where  $\rho$  is the resistivity of the material, L is the length, and A is the area. The insulator resistivity could range from  $10^{12}$  to  $10^{17}$   $\Omega$ -cm which would give corresponding resistance variations from  $2.5 \times 10^8$  to  $2.5 \times 10^{13}$  ohms.

$R_{\rm ito}$  is determined by evaluating the sheet resistance per square of the ITO layer and determining the number of squares associated with the contact regions. The resistance per square is 10 ohms. For the glass samples used,  $R_{\rm ito}$  has a value of approximately 30 ohms. Also, for reasonable process variations  $R_{\rm ito}$  is not expected to exceed 100 ohms.

$R_{\rm p}$  is estimated using a typical value for the bulk resistivity of polycrystalline  ${\rm ZnS^{28}}$ . The resistance is again calculated using the simple bulk resistance method in accordance with Eqn. (3-6). This yields a value of  $R_{\rm p}$  of order  $2\times10^6$  ohms. Parametric variations of  $R_{\rm p}$  are

evaluated over the range  $1 \times 10^4$  to  $1 \times 10^7$  ohms.

$R_{\rm d}$  is an internal parameter that is not easily evaluated. Generally  $R_{\rm d}$  is adjusted, as necessary, to fit SPICE C-V simulations to actual C-V curves. The nominal value of  $R_{\rm d}$  is 40 ohms and realistic limits of  $R_{\rm d}$  are approximately 20 to 200 ohms. Parametric variations of Rd are obtained from 0 to 1000 ohms in order to examine trends over a broad range.

#### 3.5 VERIFICATION OF THE ACCURACY OF THE C-V TECHNIQUE

The C-V technique accuracy is verified using three methods. First, SPICE simulation using nominal parameter values is used to determine the accuracy of the C-V equations discussed in Section 3.3. It is found that  $C_{\rm tot}$ ,  $C_{\rm ins}$ , and  $V_{\rm th}$  are easy to extract and that their values are as expected. Deviations from expected C-V curve results occur under certain parameter variations and are discussed in Section 3.6.

Second, SPICE C-V simulation curves are compared with the C-V curves of an ACTFEL device built from discrete components of the ideal model shown in Fig. 3-1. This is done to optimize the oscilloscope settings and  $R_{\rm g}$  value. It is found that good agreement is achieved using the oscilloscope settings and  $R_{\rm g}$  value previously described. Variations from these settings tend to increase the

observed noise in the C-V curve. The comparison of a SPICE simulated C-V curve to a discrete component C-V curve is shown in Fig. 3-6. For this simulation resistance values are set to their ideal values in the SPICE model (i.e.  $R_{ito}$ =30 ohms,  $R_{i1}$ =infinity,  $R_{i2}$ =infinity,  $R_{p}$ =infinity,  $R_{d}$ =0 ohms,  $C_{i1}$ =2.2 nF,  $C_{i2}$ =2.18 nF,  $C_{p}$ =0.987 nF, BV=92 volts).

Figure 3-6. Comparison of SPICE C-V simulations with the discrete component ACTFEL device.

Finally, once the C-V measurement system is optimized it is necessary to compare measured and simulated ACTFEL C-V curves. A comparison of a typical measured ACTFEL C-V curve with a SPICE simulation of the same ACTFEL device is shown in Fig. 3-7. The agreement between the experimental and simulated curve is reasonably good except for the threshold region and near the maximum applied voltage. The

maximum applied voltage region of the C-V curve is noisy because capacitance arises from a ratio of the measured current and the derivative of the voltage across the ACTFEL device; these signals are both very small near the maximum applied voltage which results in a small signal-to-noise ratio.

The threshold region of actual ACTFEL C-V curves cannot be fit using the enhanced ACTFEL model. A further modification of the ACTFEL model is required which involves adding another capacitance,  $C_d$ . This capacitor is added in series in the diode branch and is placed between  $R_d$  and  $D_2$ . In combination with  $R_d$  this capacitor causes a time delay which extends the width of the threshold region to actual ACTFEL device widths as shown in Fig. 3-7.

Figure 3-7. SPICE C-V simulation compared to data from a real ACTFEL device.

Please note that the need for this modification was recognized at the latter stages of the theses write-up and is not included in the SPICE-generated C-V variations that follow. Also, preliminary checks indicate that this capacitance does not affect C-V curves other than to adjust the width of the threshold region. The typical  $C_{\rm d}$  value is of the order 100 nF.

#### 3.6 SPICE SIMULATIONS

#### 3.6.1 - introduction

In general, the ACTFEL electrical characteristics of interest are displacement and conduction currents, capacitance values, and threshold voltage. Using SPICE modeling these currents, capacitances, and threshold voltages are examined. The conduction charge,  $Q_{\rm cond}$ , is found as the integral of conduction current through  $R_{\rm d}$ , I(Rd).  $Q_{\rm total}$  is the total charge, conduction and displacement, across the ACTFEL device and is evaluated as the integral of the total current through  $R_{\rm c}$ , I( $R_{\rm c}$ ). Analysis of the C-V curves provide  $C_{\rm tot}$ ,  $C_{\rm ins}$ , and  $V_{\rm th}$ . From evaluation of these parameters it is possible to show that variations in C-V curves are directly related to circuit parameters which represent specific layers of the ACTFEL structure.

SPICE simulation is used to examine trends that result

from parametric variations of  $R_{\rm ito}$ ,  $R_{\rm i1}$ ,  $R_{\rm i2}$ ,  $R_{\rm p}$ , and  $R_{\rm d}$  around nominal parameter values. Variations of  $R_{\rm g}$ , the current limiting resistor in the C-V setup, are not examined.  $R_{\rm g}$  is an external parameter that affects charge, capacitance, and threshold voltage; however, it is fixed at a value that causes little C-V curve variation. Table 3-1 shows circuit component values and ranges for SPICE modeling.

The nominal values are arrived at using a typical ACTFEL structure and process information supplied by Planar Systems and the methods described in Section 3.2.2. The ranges listed in Table 3-1 are for parameter variations that do not cause C-V curves to have unreasonable results.

Table 3-1. A summary of nominal circuit component values and their range of variation for SPICE modeling.

| Parameter        | Ideal Value      | Nominal Value          | Range                                 |  |

|------------------|------------------|------------------------|---------------------------------------|--|

| R <sub>ito</sub> | 0 ohms           | 30 ohms                | 0-100 ohms                            |  |

| R <sub>i</sub>   | infinite<br>ohms | 10 <sup>11</sup> ohms  | 10k-10 <sup>14</sup><br>ohms          |  |

| R <sub>p</sub>   | infinite<br>ohms | 2x10 <sup>6</sup> ohms | 10 <sup>4</sup> -10 <sup>7</sup> ohms |  |

| R <sub>d</sub>   | 0 ohms 40 ohms   |                        | 0-1000<br>ohms                        |  |

| R <sub>s</sub>   | 1200 ohms        | 1200 ohms              | not varied                            |  |

| BV               | 92 V             | 92 V                   | 88-96 V                               |  |

## 3.6.2 - charge, capacitance, and threshold voltage variations

The results of the parametric variation analysis are shown in Figs. 3-8 through 3-13. These trends are divided into three categories; charge, capacitance, and threshold voltage. Over the range of parameter variation many trends are evident.

Examining the charge trends first it is found that  $R_d$ ,  $R_p$ ,  $R_{ito}$  and  $R_i$  have little effect on  $Q_{total}$ ,  $Q_{pol}$ , or  $Q_{rd}$ ; since this is the case no plots of charge as a function of these parameters are provided. BV affects the charge and, as shown in Fig. 3-8, it is observed that BV causes a linear decrease in all charges with increasing BV. This is reasonable since the charge flowing is a function of the time during which the applied voltage is above threshold.

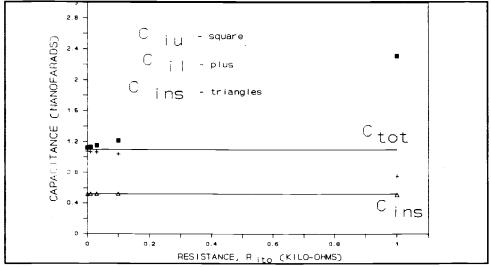

The capacitance trends are shown in Figs. 3-9 and 3-10 as a function of the parameters which displayed significant capacitance variation,  $R_{\rm d}$  and  $R_{\rm ito}$ , respectively. The first trend to observe is that there is no change in the total capacitance. The second is to observe there is a step change in the insulator capacitance in the conduction region of the C-V curve which depends upon  $R_{\rm d}$  and  $R_{\rm ito}$ . When the step occurs neither value of capacitance,  $C_{\rm iu}$  or  $C_{\rm il}$ , is the true insulator capacitance. This insulator capacitance step is due to modeling the ACTFEL device as a parametric capacitor specified by Eqn. (3-2); such a model

Figure 3-8. SPICE simulated charge versus diode breakdown voltage, BV.

does not adequately account for non-zero internal resistances present in the ACTFEL device. This effect is further explained later in this section. Parameter variations, for the ranges listed in Table 3-1, show that only  $R_d$ , causes a significant  $C_{ins}$  step as shown in Fig. 3-9.  $R_{ito}$  essentially causes the same step as  $R_d$ ; however,  $R_{ito}$  is not expected to exceed 100 ohms for standard devices and for this range the  $C_{ins}$  step is not significant. Increasing the value of  $R_d$  causes an increase in the separation of  $C_{i1}$  and  $C_{iu}$ .

Figure 3-9. SPICE simulated capacitance versus resistance,  $R_d$ .

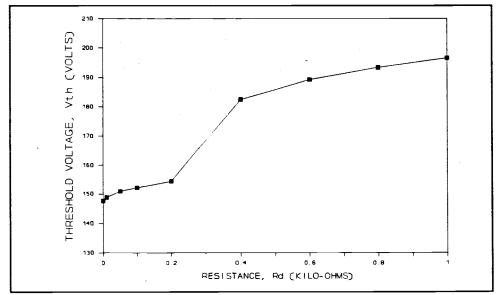

The threshold voltage is dramatically affected by  $R_{\rm d}$ , BV, and  $R_{\rm p}$ . These effects are shown in Figs. 3-11 through 3-13. Threshold voltage changes of over 30 volts are observed.

Figure 3-10. SPICE simulated capacitance versus resistance, R<sub>ito</sub>.

Figure 3-11. SPICE simulated threshold voltage,  $V_{\text{th2}}$ , versus resistance,  $R_{\text{d}}$ .

Figure 3-12. SPICE simulated threshold voltage,  $V_{\text{th2}}$ , versus diode breakdown voltage, BV.

Figure 3-13. SPICE simulated threshold voltage,  $V_{\text{th2}}$ , versus resistance,  $R_{\text{p}}$ .

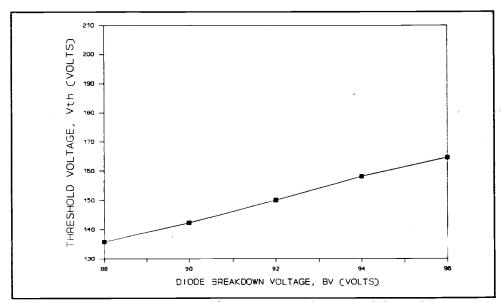

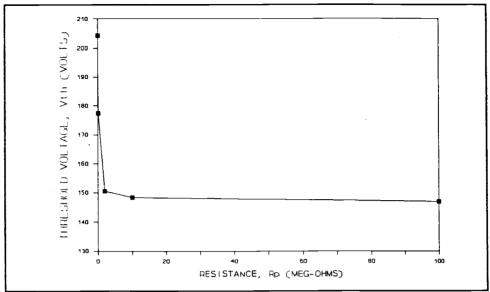

As shown in Fig. 3-11,  $R_d$  causes an increase in threshold voltage with increasing  $R_d$ . Increasing BV, as indicated in Fig. 3-12, results in a linear increase in threshold voltage over the BV range considered. Increasing  $R_p$  causes a decrease in threshold voltage as shown in Fig. 3-13, also  $R_p$  has no effect on threshold voltage for resistances larger than  $10^6$  ohms.

#### 3.6.3 - C-V curve variations

By examining C-V curves it is possible to relate changes in these curves to variations in specific model parameters which can then be directly related to the physical ACTFEL structure. These changes are examined as

follows. C-V changes due to single parameters are discussed first and then a summary of the changes observed in various C-V regions is provided with an explanation of how to interpret these C-V changes. Refer to Fig. 3-5 for explanation of the terms in the following discussion.

R<sub>ito</sub>, the ITO resistance, causes three effects as can be deduced from Fig. 3-14. The first effect is a simple RC time constant increase at low voltages in the subthreshold region. The second effect is a small change in the slope of the transition region while the third effect is an increase in the C<sub>ins</sub> step in the conduction region. The RC time constant effect is consistent with having a resistor in series with a capacitor which introduces a time delay in charging the capacitor. The third effect is explained by examining a simple series RC network as shown in Fig. 3-15.

An analysis of a simple RC series network shows why the capacitance step exists. The following equation for voltage is obtained from a Kirchoff voltage law analysis of the circuit shown in Fig. 3-15,

$$V(t) = i(t) *R + \frac{1}{C} \int i(t) dt$$

. (3-7)

Re-arranging this equation and solving for capacitance gives,

$$C = \frac{\int i(t) dt}{v(t) - i(t) R}$$

(3-8)

Without the resistor, the capacitance equation used in the C-V analysis, (3-2), is correct. However, the inclusion of a resistance leads to an additional term, i(t)R, which causes the calculated capacitance to be either larger or

Figure 3-14. C-V curves for parametric variations of  $R_{\rm ito}$ .  $R_{\rm ito}$  = 0, 30, and 100 ohms. Arrows indicate an increasing value for  $R_{\rm ito}$ .

Figure 3-15. Circuit used to examine the capacitance step observed in C-V curves in the conduction region.

smaller than that of the expected capacitance by a factor related to the direction of current flow and the magnitude of the resistance.

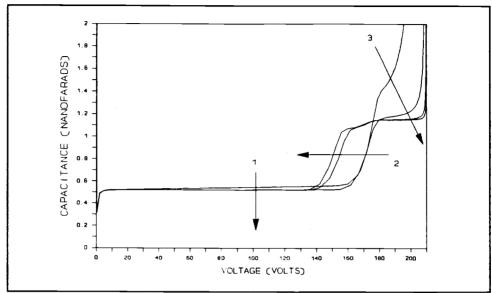

$R_{\rm i}$  variations cause three effects, as shown in Fig. 3-16. First, we observe a small slope in the subthreshold capacitance,  $C_{\rm tot}$ . Second, it is found that the threshold voltage shifts rigidly. The third effect is associated with changes in the nature of the insulator capacitance at high voltage in the conduction region. An examination of Fig. 3-17 indicates that  $R_{\rm p}$ , has only one noticeable effect. Increasing  $R_{\rm p}$  introduces a rigid shift in the threshold voltage to lower voltages.

Changing BV, as shown in Fig. 3-18, causes a rigid shift in the threshold voltage.

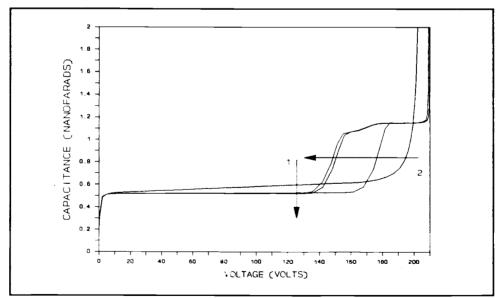

Fig. 3-19 shows that variations in  $R_d$  result in two effects. In the transition region we see that  $V_{th1}$  is fixed and  $V_{th3}$  moves to higher voltages with increasing  $R_d$ . This gives rise to a change in the slope of the capacitance in the transition region. This change in the slope of the transition region is also consistent with an increase in the density of interface states in the pre-clamping regime (threshold region of Fig.3-5). The second effect causes an increase in the difference between  $C_{i1}$  and  $C_{iu}$  in the conduction region with  $C_{i1}$  decreasing and  $C_{iu}$  increasing.

Figure 3-16. C-V curves for parametric variation of  $R_i$ .  $R_i$ =10k, 100k, 10<sup>6</sup>, and 10<sup>14</sup> ohms. Arrows indicate an increasing value for  $R_i$ .

Figure 3-17. C-V curves for parametric variation of  $R_{\rm p.}$ .  $R_{\rm p} = 10 \, \rm k, 100 \, k, 2 \, \rm x \, 10^6$ , and  $10^7$  ohms. Arrows indicate an increasing value for  $R_{\rm p.}$

Figure 3-18. C-V curves for parametric variation of BV. BV = 88, 90, 92, 94, and 96 volts. Arrows indicate an increasing value for BV.

Figure 3-19. C-V curves for parametric variations of  $R_d$ .  $R_d$  = 0, 50, 100, 200, and 1000 ohms. Arrow indicates an increasing value for  $R_d$ .

The changing slope of the capacitance transition in the threshold region of the C-V curves may be explained as follows.  $R_d$  affects the abruptness of the C-V threshold with smaller  $R_d$  yielding a more abrupt transition. Physically,  $R_d$  corresponds to a resistance associated with hot electron injection from interface traps. Thus,  $R_d$  is related to the characteristic time for electron emission from an interface trap such that we interpret a smearing out of the C-V transition as arising from traps having time constants of similar magnitude as the characteristic times of the driving waveform.

These changes in the C-V curves that have just been enumerated may be placed into five categories which are summarized in Table 3-2.

- 1) an RC time constant rise in the capacitance in the subthreshold region,

- a change of slope of the capacitance transition in the threshold region,

- a rigid threshold voltage shift in the threshold region,

- 4) a change in the difference between  $C_{i1}$  and  $C_{iu}$ , and

- 5) a change in the capacitance rise near  $V_{\rm m}$  in the conduction region.

$R_{\rm ito}$  is the only parameter that causes a change in the RC time constant rise. This effect is expected to be nearly undetectable for  $R_{\rm ito}$  less than 100 ohms. When  $R_{\rm ito}$  increases above 100 ohms then the effect is more apparent. The value of  $R_{\rm ito}$  may be evaluated from C-V analysis by

choosing the appropriate value for  $R_{\rm ito}$  in the SPICE simulation that provides agreement with the measured C-V curve.

Table 3-2. Summary of the effect of parameter variations on C-V curves.

|                  | C-V<br>curve<br>effect |                 |                                   |                                     |                                  |  |

|------------------|------------------------|-----------------|-----------------------------------|-------------------------------------|----------------------------------|--|

| Parameter        | RC<br>Rise             | Slope<br>Change | Rigid<br>V <sub>th</sub><br>shift | C <sub>il</sub> and C <sub>iu</sub> | Insulator<br>capacitance<br>rise |  |

| R <sub>s</sub>   | no                     | no              | no                                | no                                  | no                               |  |

| R <sub>ito</sub> | yes                    | yes             | no                                | yes                                 | no                               |  |

| R <sub>i</sub>   | no                     | no              | yes                               | no                                  | yes                              |  |

| R <sub>p</sub>   | no                     | no              | yes                               | no                                  | no                               |  |

| R <sub>d</sub>   | no                     | yes             | no                                | yes                                 | no                               |  |

| BV               | no                     | no              | yes                               | no                                  | no                               |  |

$R_{\rm d}$  and  $R_{\rm ito}$  are the only parameters that cause a noticeable change in the slope of the capacitance transition in the threshold region.  $R_{\rm d}$  and  $R_{\rm ito}$  effects are easily distinguishable since any change in the capacitance of the sub-threshold region indicates that  $R_{\rm ito}$  has changed. If there is only a change in the slope in the threshold region then  $R_{\rm d}$  is the parameter that has changed.

$\mathbf{R}_{\mathrm{p}},~\mathbf{R}_{\mathrm{i}},~\mathrm{and}~\mathrm{BV}$  all cause rigid shifts in threshold

voltage. Assuming insulators of high quality,  $R_i$  can be eliminated as a possible cause of rigid shifts in  $V_{\rm th}$ .  $R_{\rm p}$  and BV changes are not separable for reasonable values of  $R_{\rm p}$  and BV. For  $R_{\rm p}$  less than  $1 \times 10^5$  ohms; however, it is possible to separate  $R_{\rm p}$  from BV effects.

$R_{\rm i}$  variations yield small changes in the capacitance rise in the conduction region. However, since the insulators employed in this study are found to be of high quality, only  $R_{\rm i}$  values of unrealistic magnitudes give rise to such changes.

#### 3.7 SUMMARY

In this chapter the utility of SPICE modeling in conjunction with an equivalent circuit model of the ACTFEL device for the interpretation of C-V curves is demonstrated. It is shown that simple methods may be used to give reasonably accurate SPICE circuit element parameters. Comparison of measured ACTFEL C-V results with SPICE simulations show good agreement, thereby reenforcing the viability of parameters used in the model. Changes in C-V curves are interpretable in terms of SPICE circuit parameters which in turn are related to specific layers of the ACTFEL structure. In this manner, the C-V technique is a useful aid for ACTFEL diagnostics and may be well suited to quality control and lifetime monitoring. It is believed that C-V analysis and SPICE modeling provide new device

physics insight into the nature of ACTFEL operation and are useful methods for exploring ACTFEL aging instabilities.

# CHAPTER 4 - ACTFEL AGING INSTABILITY ANALYSIS 4.1 INTRODUCTION

The electronic nature of semiconductor devices is controlled, to a large extent, by the intrinsic and extrinsic doping of the material either in the bulk or at interfaces between different materials. Doping may consist of an addition of impurities or defects to the host material due to processing steps. These impurities or defects form sites at which electrons may be sourced and trapped. The sites are characterized by their specific energies in the energy band.

Whether or not traps are stable in energy and physical location determines the aging characteristics of a device. A measure of the activation energy associated with aging provides the link between device behavior and the microscopic identity of the process giving rise to aging and, thus, aids in understanding the nature of the aging process.

In this chapter the shift in the C-V threshold voltage with short-term aging time and as a function of temperature is measured. The short-term aging kinetics are then analyzed and an activation energy for the initial aging process is deduced. Based on the magnitude of the measured short-term activation energy, a discussion of possible atomic mechanisms responsible for aging and how they occur is provided.

#### 4.2 EXPERIMENTAL TECHNIQUE

#### 4.2.1 - experiment description

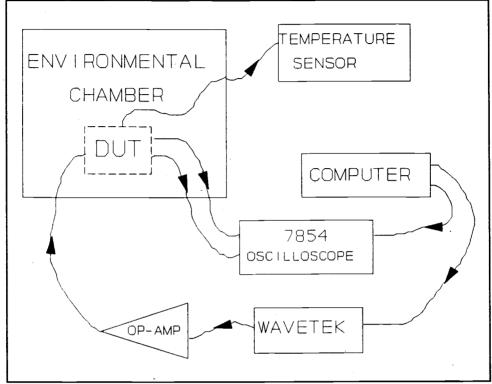

The aging experiment consists of monitoring the C-V threshold voltage, V<sub>th2</sub>, with aging time and as a function The experiment is performed using a single of temperature. glass substrate, provided by Planar Systems, that has 10 aluminum dots. Aging occurs over a temperature range of -50 °C to 80 °C. The aging duration is 45 hours using the standard waveform described in Section 3.3 with a voltage amplitude of 210 volts. Temperature is controlled using a Blue-M environmental furnace. Thermocouples located in the Threshold furnace near the sample record the temperature. voltage sampling is performed automatically with a computercontrolled system using the C-V analysis technique described in Chapter 3. The threshold voltage is obtained graphically from the C-V curves generated. Over the aging duration 56 threshold voltages are determined. Threshold voltage sampling occurs more rapidly during the rapid initial aging and then slows down as the sample approaches its saturated threshold voltage.

Fig. 4-1 shows a block diagram of the ACTFEL aging measurement system. The following equipment is used for this aging experiment.

- 1) OMEGA microprocessor thermometer model HH22,

- 2) BLUE-M environmental chamber,

- 3) Wavetek arbitrary waveform generator model 275,

- 4) APEX operational amplifier model PA-85,

- 5) Tektronix 7854 digitizing oscilloscope, and

- 6) IBM 286 compatible computer with GPIB capability,

Figure 4-1. Block diagram of the aging experimental setup.

#### 4.2.2 - initial conditions

The ACTFEL sample consists of 10 dots on a 2x2 inch glass substrate which is processed using Planar Systems standard process. A dot consists of a 1/4 inch diameter aluminum circle. The standard Planar Systems process is described in Section 2.2.

The Planar Systems ACTFEL device needs a slow warm-up to full operating voltage to ensure self-healing of defects that otherwise could cause burn-out. A room temperature

warm-up of the 10 dots is employed which starts at 10 volts and goes to 210 volts in 3 volt steps which occur every three seconds. This yields a warm-up time of approximately 35 minutes. Threshold voltage is then determined for each dot and is found to vary from 126 to 114 volts. As necessary, each sample dot is pre-aged to obtain  $V_{\rm th2} = 125$  volts, to within 2 percent; this insures that all of the dots are initialized in the same manner.

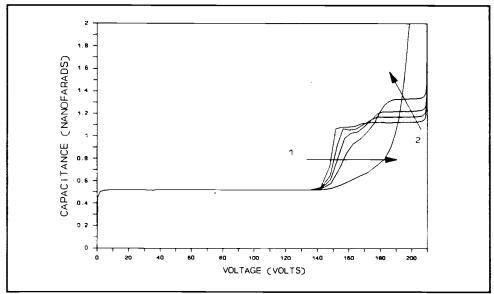

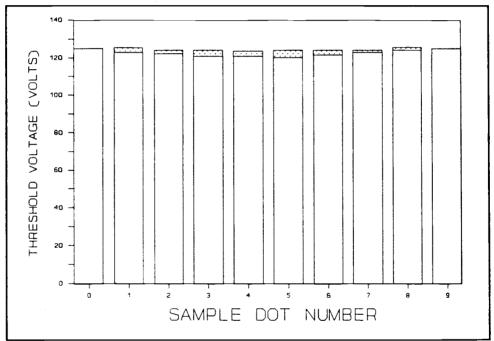

Figure 4-2. Initial room temperature threshold voltages, V<sub>th2</sub>, for glass 7-26-90-15 and adjusted threshold voltages at which the aging experiments begin.

Figure 4-2 shows the initial threshold voltage after the warm-up procedure and the subsequent adjusted threshold at which the aging experiment begins. It is generally assumed that processing yields consistent thickness and

composition in each layer and so variations in the threshold voltage are attributed to differing trap densities and energies. By forcing each dot to have the same adjusted threshold voltage, it is believed they are initialized in the same manner and that the aging results of each dot can be directly compared. The time necessary to adjust the initial threshold voltage is a maximum of 100 seconds. It is also suspected that some aging may occur due to temperature alone, independent of the application of a voltage waveform; because of this, the aging experiments are performed at the low temperatures first so as to introduce as little shift due to temperature as possible.

#### 4.3 AGING RESULTS

The results of ACTFEL aging experiments using glass number 7-26-90-15 are shown in Figs. 4-4 through 4-11 for the following temperatures: -50 °C, -10 °C, 0 °C, 20 °C, 60 °C, and, 80 °C. A characteristic family of C-V curves and the shift in threshold voltage for each temperature are shown and discussed below.

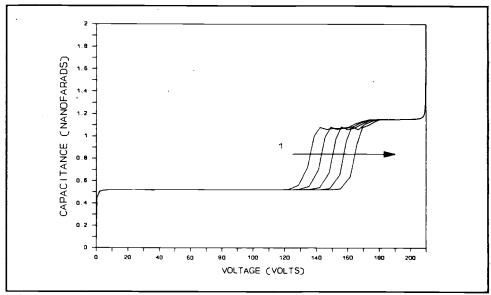

The family of selected C-V curves shown in Fig. 4-3 are for the 60 °C experiment. These C-V curves show characteristics typical of all aging experiments at various temperatures. In general, it is observed that the threshold voltage shifts rigidly with operating time and  $C_{\rm tot}$  and  $C_{\rm ins}$  remain essentially constant to within experimental error.

Figure 4-3. Family of C-V curves for the 60 °C experiment with aging times of 1 second, 20 minutes, 9.5 hours. Arrow indicates direction of threshold voltage shift with aging time.

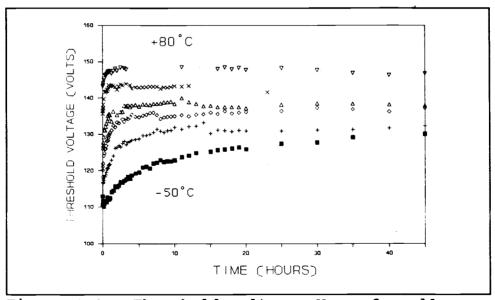

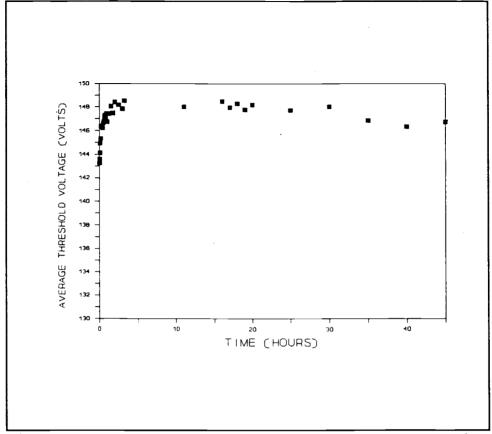

Figure 4-4. Threshold voltage,  $V_{\text{th2}}$ , for all temperatures as a function of aging time.

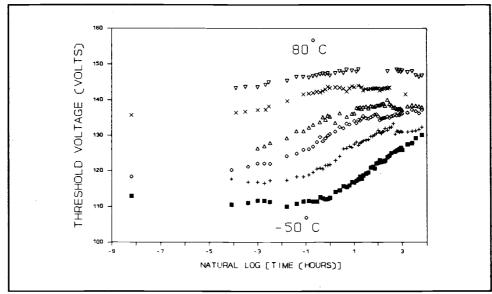

Figure 4-5. Threshold voltage, V<sub>th2</sub>, for all temperatures as a function of the <u>natural logarithm</u> of aging time.

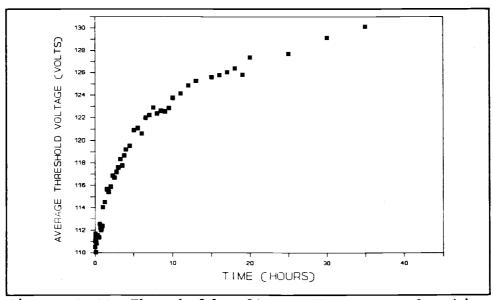

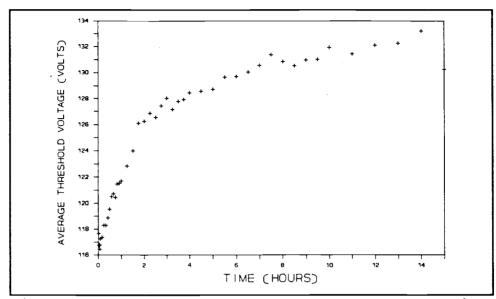

Figure 4-6. Threshold voltage,  $V_{\text{th2}}$ , as a function of aging time at a temperature of -50 °C.

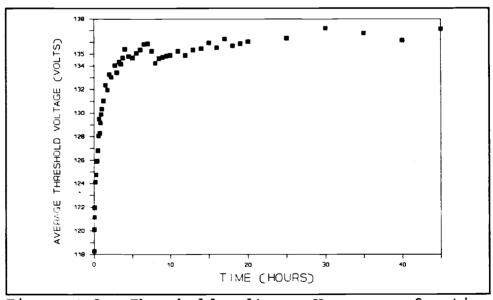

Figure 4-7. Threshold voltage,  $V_{\text{th2}}$ , as a function of aging time at a temperature of -10°C.

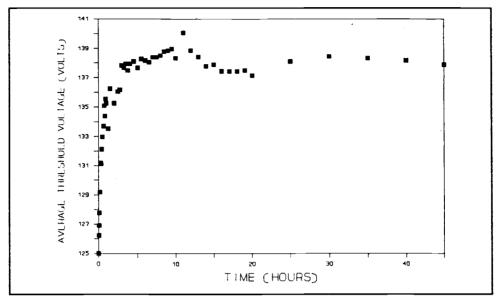

Figure 4-8. Threshold voltage,  $V_{\text{th2}}$ , as a function of aging time at a temperature of 0 °C.

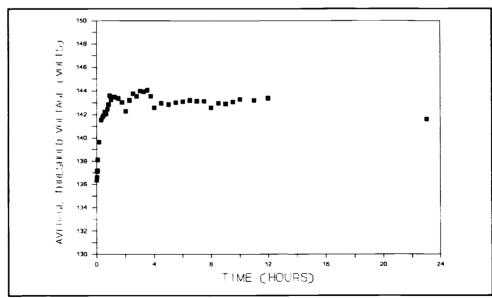

Figure 4-9. Threshold voltage,  $V_{\text{th2}}$ , as a function of aging time at a temperature of 20 °C.

Figure 4-10. Threshold voltage,  $V_{\rm th2}$ , as a function of aging time at a temperature of 60 °C.

Figure 4-11. Threshold voltage, V<sub>th2</sub>, as a function of aging time at a temperature of 80 °C.

The characteristics of the threshold voltage shifts are discussed as follows. As can be observed from Figs. 4-4 and 4-5, the aging characteristics can be classified into four regimes:

- 1) incubation period,

- logarithmic aging,

- 3) saturation, and

- 4) long-term aging.

At lower temperatures there is an incubation period, in which the threshold voltage is essentially constant. This

incubation period lasts one hour at the lowest temperature (-50 °C) and eventually disappears at and above room temperature (20 °C). The incubation period is followed by a period in which the threshold voltage increases logarithmically with aging time. Next, the threshold voltage approaches a saturated value which is temperaturedependent. The logarithmic and saturation regimes are collectively referred to as constituting the short-term aging regime, which is of primary importance in this thesis. As expected, the aging rate increases as temperature increases. At higher temperatures (60 °C and 80 °C) the aging occurs so rapidly that only a very small window of time exists during which the threshold voltage depends exponentially on time. Since the analysis of the short-term aging kinetics depends exclusively on the exponential period, where the change in threshold voltage is linear with respect to the natural logarithm of time, this window must be selected carefully in order to avoid an analysis which includes long-term aging mechanisms and which could result in negative activation energy.

Finally, the last aging regime is denoted long-term aging in which the threshold voltage decreases slowly with increasing aging time. Previous room-temperature aging experiments over an aging period of 65 hours show a tendency for the threshold voltage to subsequently decrease slightly after about 50 hours of aging. This decrease is on the

order of a few volts over this 15 hour period. This effect is not observed in the 45 hour experiments until the temperature exceeds about 60 °C. Thus, choosing an aging time of 45 hours is nearly optimal for the analysis of the primary mechanism of ACTFEL aging. However, termination of the experiment at 45 hours precludes analysis of the mechanism of long-term aging.

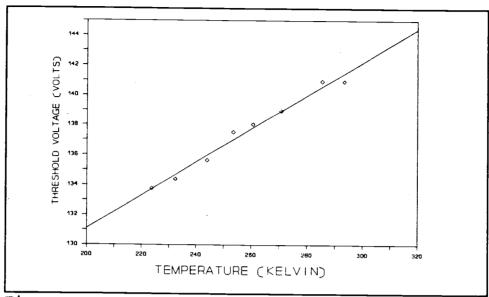

During the aging experiment it is observed that the initial threshold voltage for each dot is not necessarily the same as for the pre-aged, room temperature, threshold voltage. Figure 4-12 shows the temperature dependence of the -50 °C dot. This data is obtained after the temperature experiment is completed. The ramping of temperature took less than one hour so little aging occurred during the acquisition of this data. The graph clearly shows a linear dependence of the threshold voltage on temperature. By plotting the initial and final threshold voltage for the aging data at each temperature, as shown in Fig. 4-13, a similar linear dependence with temperature is observed.

The cause of the temperature dependence of the threshold voltage is uncertain. The temperature dependence of the insulator capacitance was checked, using a HP4280A 1MHz capacitance meter, from 20 °C to 95 °C and found to vary only 4 percent. This small variation in the dielectric constant is insufficient to explain the observed threshold voltage temperature-dependence.

Figure 4-12. Temperature dependence of the -50 °C dot threshold voltage, V<sub>th2</sub>, after the aging experiment was completed.

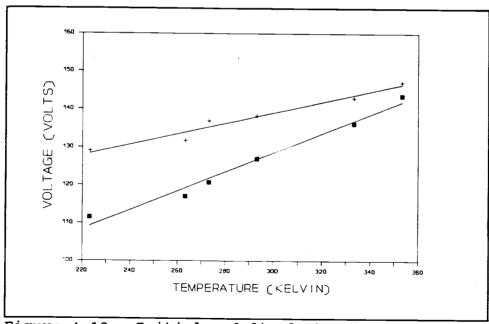

Figure 4-13. Initial and final threshold voltages,  $V_{\text{th2}}$ , for all aging samples as a function of temperature.

#### 4.4 ACTIVATION ENERGY EXTRACTION

#### 4.4.1 - Arrhenius analysis

Arrhenius proposed that, over a limited range of temperature, the rate constant,  $\alpha$ , of a process depends exponentially on temperature as

$$\alpha = \mathbf{A} \exp\left(\frac{-E_a}{k_B T}\right) \tag{4-1}$$

where  $\bf A$  is a pre-exponential factor,  $\bf E_a$  is the activation energy, and  $\bf k_B$  is the Boltzmann constant. Writing (4-1) in logarithmic form gives

$$\ln (\alpha) = -\frac{E_a}{k_B T} + \ln (A) \qquad (4-2)$$

which yields a straight line when the logarithm of the rate constant,  $\alpha$ , is plotted against the reciprocal of the absolute temperature. The slope of this line gives the activation energy whereas the intercept is related to the pre-exponential factor.

Not all experimental results give rise to a rate constant with simple exponential Arrhenius behavior. Specifically, if the incubation and long-term aging periods are temporarily ignored, ACTFEL aging experiments show an increase in the threshold voltage which depends logarithmically on the aging time and a subsequent threshold voltage saturation. Further, there is a temperature-dependence on the threshold voltage that is relatively

independent of aging and which needs to be taken into account. The following equation is found to fit the ACTFEL aging data in the logarithmic and saturation regions and to account for the temperature-dependence of the threshold voltage;

$$\Delta V_{th}(t) = \Delta V \frac{SAT}{th}(T) \left[ 1 - \exp(-\alpha t) \right]$$

(4-3)

where  $\Delta$  V<sub>th</sub>(t) is the measured change in threshold voltage which is evaluated from the experimental aging data,  $\Delta V \frac{SAT}{th}(T)$  is the difference between the saturation threshold voltage and the initial threshold voltage, and  $\alpha$  is the rate constant characteristic of the ACTFEL aging process. Equation (4-3) can be rearranged to yield

$$\alpha t = \ln \left[1 - \frac{\Delta V_{th}(t)}{\Delta V_{th}^{SAT}(T)}\right]$$

(4-4)

Therefore, a plot of the right hand side of (4-4) versus time should result in a linear relationship in time, the slope of which corresponds to the rate constant,  $\alpha$ . If  $\alpha$  is extracted for each temperature and plotted versus the inverse of the absolute temperature, the slope of such a plot yields the activation energy for ACTFEL aging.

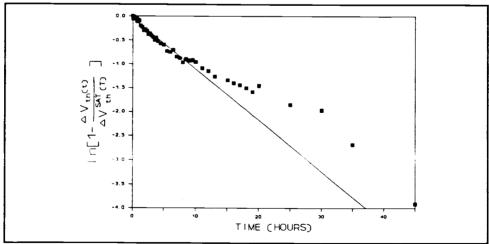

### 4.4.2 - activation energy from aging kinetics

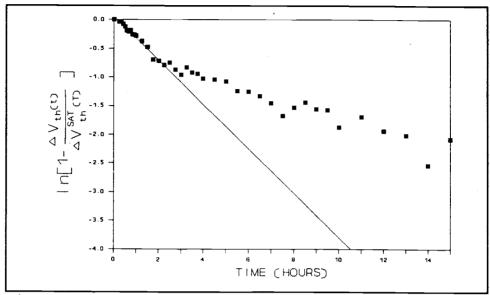

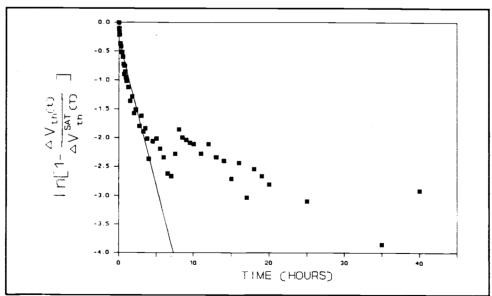

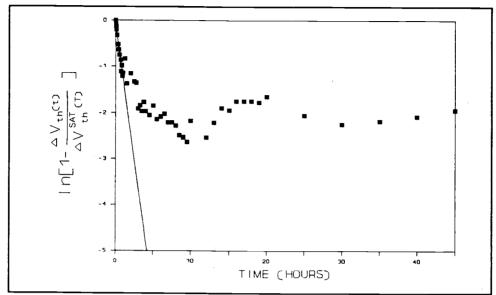

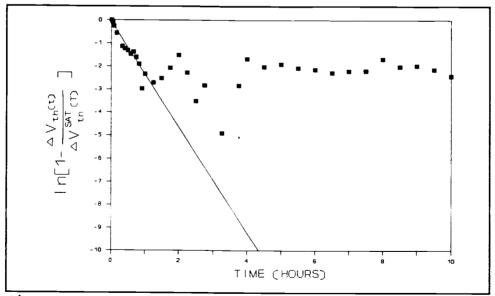

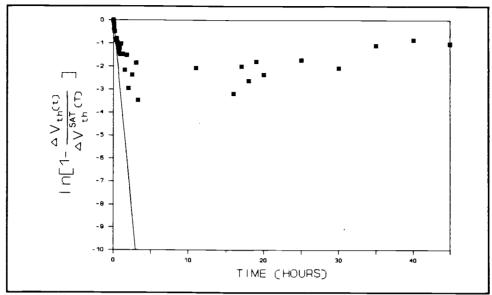

Each of the six sets of data shown in Figs. 4-5 through 4-10 is plotted according to Eqn. (4-4) and these normalized

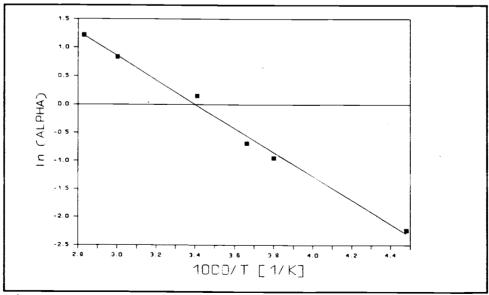

threshold voltage difference curves are given in Figs. 4-14  $\Delta V_{th}^{SAT}(T)$  is found for every temperature through 4-19. from the experimental data and the rate constant,  $\alpha$ , is determined from best fit of the linear region of the normalized plots of the change in the threshold voltage as shown in Figs. 4-14 through 4-19. The correlation of fit,  $R^2$ , of the linear portion of the curve to  $\alpha$  varied from 0.87 to 0.98 with an average fit of 0.92, as is summarized in Table 4-1. The rate constant for each temperature is then plotted as a function of inverse absolute temperature to obtain an Arrhenius plot as shown in Fig. 4-20. of the experimental data yields the straight line shown in Fig. 4-20 from which the parameters summarized in Table 4-2 are extracted. The slope of this line, which corresponds to the threshold voltage activation energy, has a value of approximately 0.2 eV.

Figure 4-14. Normalized shift in threshold voltage, V<sub>th2</sub>, as a function of aging time at a temperature of -50 °C.

Figure 4-15. Normalized shift in threshold voltage, V<sub>th2</sub>, as a function of aging time at a temperature of -10 °C.

Figure 4-16. Normalized shift in threshold voltage, V<sub>th2</sub>, as a function of aging time at a temperature of 0 °C.

Figure 4-17. Normalized shift in threshold voltage, V<sub>th2</sub>, as a function of aging time at a temperature of 20 °C.

Figure 4-18. Normalized shift in threshold voltage, V<sub>th2</sub>, as a function of aging time at a temperature of 60 °C.

Figure 4-19. Normalized shift in threshold voltage, V<sub>th2</sub>, as a function of aging time at a temperature of 80 °C.

Figure 4-20. Arrhenius plot of the aging experiment data.

Table 4-1. Summary of temperature-dependent rate constants, intercepts, and correlation of fit.

| Temperature<br>(°C) | Rate<br>Constant | Intercept $\ln [1 - \frac{{}^{\Delta V}{th}^{(t)}}{{}^{\Delta V} \frac{SAT}{th}^{(T)}}]$ | R <sup>2</sup><br>Fit |

|---------------------|------------------|------------------------------------------------------------------------------------------|-----------------------|

| -50                 | -0.1067          | -0.0405                                                                                  | 0.9689                |

| -10                 | -0.3870          | 0.0714                                                                                   | 0.9782                |