#### AN ABSTRACT OF THE DISSERTATION OF

Pavan Kumar Hanumolu for the degree of <u>Doctor of Philosophy</u> in <u>Electrical and Computer Engineering</u> presented on <u>August 21, 2006</u>. Title: Design Techniques for Clocking High Performance Signaling Systems.

Abstract approved: \_

Un-Ku Moon

Scaling of CMOS technology has progressed relentlessly for the past several decades. In order for this unprecedented scaling to benefit the performance of large digital systems, the communication bandwidth between integrated circuits (ICs) must scale accordingly. However, interconnect technology does not scale as aggressively, making communication between chips the major bottleneck in overall system performance. In addition, supply voltage scaling, increasing device leakage, and increased noise make existing signaling circuits inefficient and difficult to scale.

In this thesis, both analog and digital enhancement techniques to mitigate scaling related issues and improve the performance of building blocks used in highspeed signaling systems are discussed. A digital-to-phase converter (DPC) with a resolution better than 100 femto-second resolution, a hybrid analog/digital clock and data recovery (CDR) architecture that improves the tracking range of traditional CDRs by an order of magnitude, and a digital CDR architecture that obviates the need for the charge pump and the large area occupying loop filter, while achieving error-free operation are presented. Measured results obtained from the prototype chips are presented to illustrate the proposed design techniques. <sup>©</sup>Copyright by Pavan Kumar Hanumolu August 21, 2006 All Rights Reserved

# Design Techniques for Clocking High Performance Signaling Systems

by

Pavan Kumar Hanumolu

## A DISSERTATION

submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Presented August 21, 2006 Commencement June 2007 Doctor of Philosophy dissertation of <u>Pavan Kumar Hanumolu</u> presented on August 21, 2006

APPROVED:

Major Professor, representing Electrical and Computer Engineering

Director of the School of Electrical Engineering and Computer Science

Dean of the Graduate School

I understand that my dissertation will become part of the permanent collection of Oregon State University libraries. My signature below authorizes release of my dissertation to any reader upon request.

Pavan Kumar Hanumolu, Author

#### ACKNOWLEDGMENTS

Pursuing a doctoral degree is like venturing into a long journey imbued with both intellectual spirit and capricious blend of uncertainties. I for one have thoroughly enjoyed this thrill-a-minute endeavor for all of the last five years. At the end of it all, I feel that there is as much pleasure in the journey as there is in reaching the destination. For that, I would like to thank all the people who made at times turbulent journey a pleasant experience and helped me reach the summit which looked hopelessly insurmountable at various stages.

First and foremost, I am deeply indebted to my peerless advisor Professor Un-Ku Moon, for giving me the golden opportunity of being part of his group when I knew little about circuits. He gave me the freedom and provided all the means, financial and otherwise, to pursue my own ideas and showed seemingly unlimited patience when I frequently digressed into other areas of his research. He is also a circuit designer of transcendental brilliance and I greatly benefited from his expertise. He will be a role model that I will look up to as I start my career in academia.

Professor Gu-Yeon Wei of Harvard University unselfishly agreed to be my coadvisor despite being 3000 miles away and generously shared his vast knowledge on links design. Gu masterfully explained the nitty-gritty of my own designs with consummate ease and frequently improved them by way of suggesting changes that were certainly beyond my scope of thinking. He also laboriously edited my papers and presentations and trained me on how to give good talks. I am grateful for his tutelage and look forward to the continued friendship and collaboration.

Randy Mooney of Intel Circuit Research Labs introduced me to serial links and then provided both financial and intellectual support for all of my research on this topic. In spite of his busy schedules, he always found time to listen to my ideas, good and mostly bad, and provided invaluable feedback. He gave me the best advice regardless of the consequences for him. I am deeply indebted to him for his generosity, kindness, and guidance. I also greatly benefited from the interactions with all the members of his research team, past and present: Ganesh Balamurugan, Bryan Casper, David Johnson, James Jaussi, Joe Kennedy, Mozghan Mansuri, Aaron Martin, and Frank O'mahoney. In particular, Aaron, Bryan, and David answered all my questions very patiently when I first started this work. I am grateful for all their help. I would also like to thank Matt Haycock and Shekar Borkar for constant encouragement and support.

I am indebted to the mighty Professor Temes for his invaluable advice on both technical and personal matters. He has been a source of inspiration all along and I feel fortunate and honored to have had the opportunity to interact with him. I would be remiss if I do not mention how thoroughly I enjoyed his stories that were generously filled with humor, wit, and inspiration. I also appreciate the kindness of Professor Temes and Ibi for inviting me to their home for excellent dinners.

Professor Mayaram rigorously edited my writing and taught me technical writing style by example. He also provided unconditional help and precious advice through out my graduate study and I am deeply grateful to him for that.

I would also like to thank Professor Solomon Yim for serving on my committee. Thanks are also due to Merrick Brownlee, Rob Gregoire, and Sunwoo Kwon for reading my thesis and providing feedback.

Andy, Clara, Josh, Morgan, Nancy, and Sarah worked relentlessly to put bureaucracy at bay and made sure the much needed checks came in on time. Ferne has a next to impossible and often thankless job of assisting all the ECE graduate students. But, she some how tactfully manages to help everybody with unlimited patience, grace, and cordiality. I am also grateful to Manfred Dittrich for his help with my test setup preparations. Thank you for all your help and friendship.

My tenure as a graduate student in Corvallis would'nt have been as enjoyable and as fulfilling without the support of my beloved friends. I am not eloquent enough to adequately express my true feelings of joy and gratitude for their friendship. Nevertheless, I would like to acknowledge them. Gil-cho Ahn taught me not to take anything for granted, particularly good things in life. Matt Brown, José Silva, and José Ceballos showed great concern for my well-being, much more than a good friend could or should ask for. Merrick Brownlee, Volodymyr Kratyuk (a.k.a Vova), and Todd Shechter often performed wizardry with computers and saved me from insanity! Min Gyu Kim showed me the value of simplicity both in circuit design and in life. Arun Rao did the best favor I could ask of him by introducing me to Professor Moon and Dong-Young Chang made me feel at home when I first came to Corvallis. Thank you all for your unconditional support at all times.

Daily coffee breaks and weekly dinner meetings at *Bombs Away* with my best buddies Amy Doty, Erik Geissenhainer, Christopher Hanken, Wonseok Huang, Celia Hung, Min Gyu Kim, Sunwoo Kwon, Jim Le, Nema Talebbeydokhti, and Eric Vernon served as perfect tools for stress relief. You made bad times seem not that bad and work seem less work. Thank you for your friendship.

I also greatly enjoyed the good company and camaraderie of Anurag, David B., Dave G., Emma, Gowtham, Jack, Jake, James, Josh, Jipeng, Kerem, Kyehyung, Martin, Nag, Nishanth, Peter, Rob, Robert, Ruopong, Sasidhar, Tawfiq, Ting, Thuy, Wonseok, Xuesheng, Younjae, and Zhenyong. If I inadvertently forgot anybody, I ask you as a good friend to forgive my ungratefulness! I will forever cherish the good times we all had together.

The *couples* Charlie/Meridith, Jose/Marcella, Min Gyu/Suk-Hyeon, Matt/Melinda, and Vova/Miroslava invited me for sumptuous dinners on numerous occasions, something, as a starving graduate student, I always longed for.

I am grateful to Samsung Electronics and National Semiconductor for providing the fabrication of my test chips. In particular, I would like to thank Sang-Hyeon Lee, Amjad Obeidat, Kim Yeow Wong, and Bijoy Chatterjee for their herculean efforts to make the fabrication possible.

Finally, but immensely, I would like to thank my parents for teaching me the true value of education and continued learning. My deepest gratitude belongs to them for their sacrifice, love, and support. I would also to thank my brother for his love and friendship. This thesis for all its worth is dedicated to them.

# TABLE OF CONTENTS

Page

| 1. | INT | RODUCTION                                    | 1  |

|----|-----|----------------------------------------------|----|

|    | 1.1 | Channel Loss                                 | 2  |

|    | 1.2 | Clock Jitter                                 | 5  |

|    | 1.3 | Thesis Organization                          | 6  |

| 2. | PER | RFORMANCE ANALYSIS METHODS FOR SERIAL LINKS  | 8  |

|    | 2.1 | Worst Case ISI Analysis                      | 9  |

|    | 2.2 | Analysis of Clock Jitter                     | 11 |

|    | 2.3 | Receiver Clock Jitter                        | 13 |

|    | 2.4 | Transmitter Clock Jitter                     | 18 |

|    | 2.5 | Transmitter Jitter and Receiver Jitter       | 22 |

|    | 2.6 | Summary                                      | 23 |

| 3. | HIG | H RESOLUTION DIGITAL-TO-PHASE CONVERTERS     | 25 |

|    | 3.1 | Proposed Architecture                        | 30 |

|    | 3.2 | Phase Filter Implementation                  | 34 |

|    | 3.3 | Circuit Design                               | 40 |

|    | 3.4 | Experimental Results                         | 48 |

|    | 3.5 | Summary                                      | 53 |

| 4. |     | YBRID ANALOG/DIGITAL CLOCK AND DATA RECOVERY | 55 |

|    | 4.1 | Proposed Architecture                        | 63 |

|    | 4.2 | Circuit Design                               | 70 |

# TABLE OF CONTENTS (Continued)

|    |      |                                        | Pa  | age |

|----|------|----------------------------------------|-----|-----|

|    | 4.3  | Experimental Results                   |     | 89  |

|    | 4.4  | Summary                                |     | 91  |

| 5. | A D  | IGITAL CLOCK AND DATA RECOVERY CIRCUIT |     | 93  |

|    | 5.1  | Digital CDR                            |     | 94  |

|    | 5.2  | Proposed Architecture                  |     | 96  |

|    | 5.3  | Linear Analysis                        |     | 97  |

|    | 5.4  | Circuit Design                         | ••• | 99  |

|    | 5.5  | Experimental Results                   |     | 101 |

|    | 5.6  | Summary                                | ••• | 102 |

| 6. | COI  | NCLUSIONS                              |     | 105 |

| BI | BLIO | GRAPHY                                 |     | 107 |

#### LIST OF FIGURES

| Fig | ure                                                                                                                                                                                          | Page   |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| 1.1 | A typical serial link block diagram                                                                                                                                                          | . 2    |

| 1.2 | Loss of a 20" (server) and 6" (desktop) FR4 traces with two connectors                                                                                                                       | . 3    |

| 1.3 | 2.5Gbps eye diagram                                                                                                                                                                          | . 3    |

| 1.4 | 5Gbps eye diagram                                                                                                                                                                            | . 4    |

| 1.5 | Equalized 5Gbps eye diagrams: (a) Attenuating low-frequency<br>(b) Boost high-frequency.                                                                                                     |        |

| 1.6 | Effect of clock jitter in serial links                                                                                                                                                       | . 5    |

| 1.7 | Receive equalized 5Gbps eye diagram with transmitter PLL jitte                                                                                                                               | r. 6   |

| 2.1 | Pulse response with the corresponding ISI terms                                                                                                                                              | . 10   |

| 2.2 | 3Gbps pulse response.                                                                                                                                                                        | . 11   |

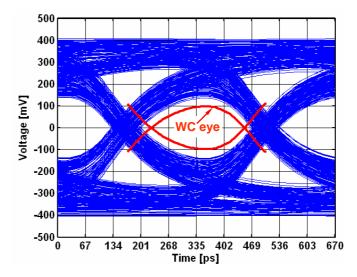

| 2.3 | 3Gbps simulated and worst case eye diagrams                                                                                                                                                  | . 12   |

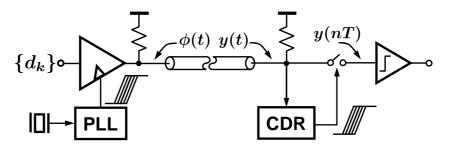

| 2.4 | Serial link model with transmitter and receiver clock jitter                                                                                                                                 | . 12   |

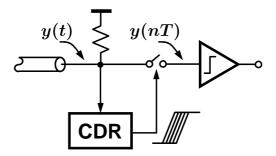

| 2.5 | Receiver with recovered clock jitter.                                                                                                                                                        | . 13   |

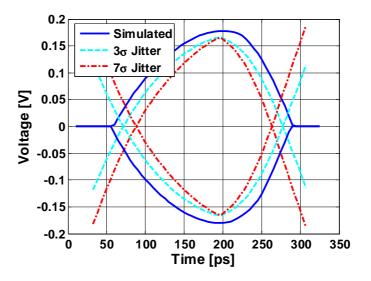

| 2.6 | Eye diagrams with receiver clock jitter                                                                                                                                                      | . 16   |

| 2.7 | Transmitter with PLL clock jitter.                                                                                                                                                           | . 18   |

| 2.8 | Eye diagrams with transmitter PLL clock jitter                                                                                                                                               | . 21   |

| 2.9 | Eye diagrams with transmitter PLL clock and recovered clock jitte                                                                                                                            | er. 24 |

| 3.1 | A typical source-synchronous interface.                                                                                                                                                      | . 25   |

| 3.2 | DPC using phase selection.                                                                                                                                                                   | . 26   |

| 3.3 | DPC using phase selection and interpolation                                                                                                                                                  | . 27   |

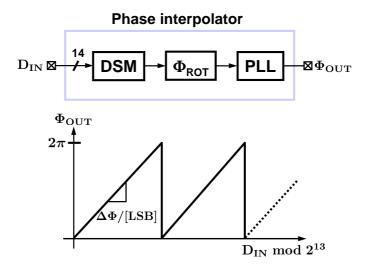

| 3.4 | Phase interpolator: (a) Operation (b) Model                                                                                                                                                  | . 28   |

| 3.5 | Analysis of the phase interpolator linearity. The solid line repre-<br>sents the transfer function with $\frac{\Delta T}{RC} = 0.5$ and dashed lines with $\frac{\Delta T}{RC} = 1, 1.5, 2.$ | . 29   |

| Figu | lire                                                                      | Pag | ge |

|------|---------------------------------------------------------------------------|-----|----|

| 3.6  | Proposed DPC architecture.                                                |     | 30 |

| 3.7  | Phasor diagram to illustrate DPC operation                                | ••• | 32 |

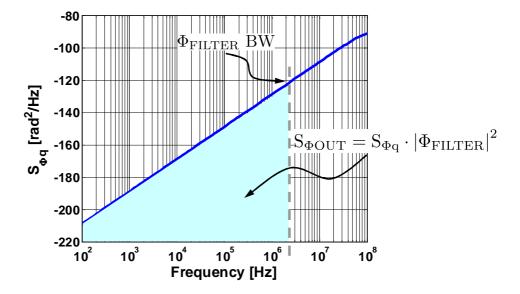

| 3.8  | Frequency domain view of the phase noise due to DSM noise shaping.        |     | 33 |

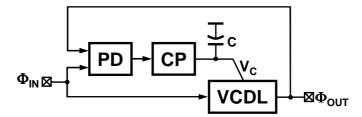

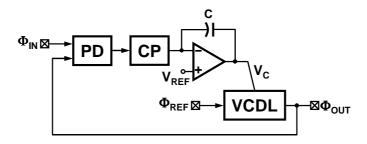

| 3.9  | Conventional delay locked loop                                            |     | 35 |

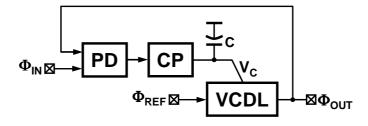

| 3.10 | Modified DLL with low-pass transfer function                              |     | 35 |

| 3.11 | Small-signal model of the modified DLL                                    |     | 36 |

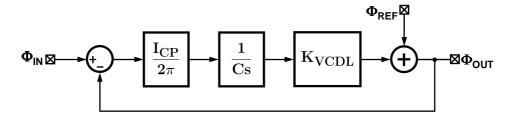

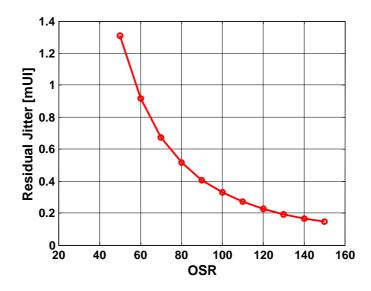

| 3.12 | Residual jitter vs. over sampling ratio for a first-order DLL             | ••• | 37 |

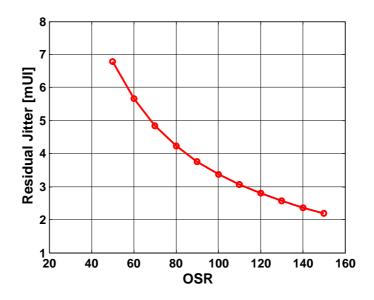

| 3.13 | Low-pass DLL with an active loop filter                                   | ••• | 38 |

| 3.14 | Residual jitter vs. over sampling ratio for a second-order DLL.           | ••• | 39 |

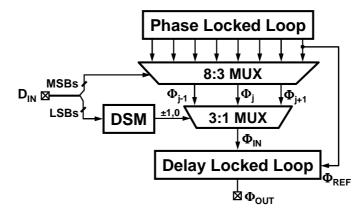

| 3.15 | Complete DPC architecture.                                                | • • | 39 |

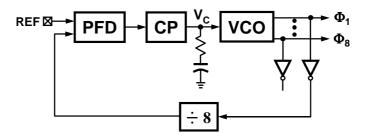

| 3.16 | Phase-locked loop that provides 8-phases                                  | • • | 40 |

| 3.17 | A 4-stage ring oscillator and the delay cell                              |     | 41 |

| 3.18 | Implemented delay-locked loop with active loop filter                     |     | 42 |

| 3.19 | Timing diagram illustrating a <i>stuck at minimum delay fault</i>         |     | 43 |

| 3.20 | DLL lock range.                                                           | • • | 43 |

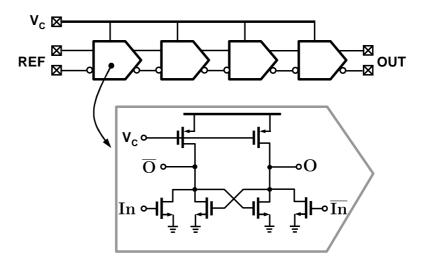

| 3.21 | Phase-only detector with differential outputs                             | ••• | 44 |

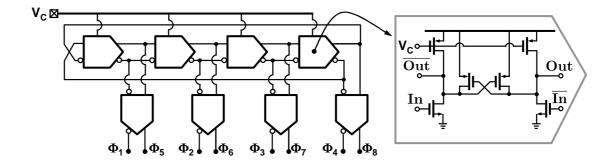

| 3.22 | A four stage delay line along with the delay cell                         | • • | 45 |

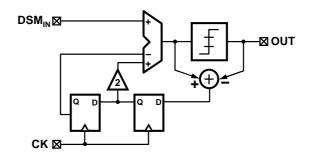

| 3.23 | An error feedback delta-sigma modulator                                   |     | 46 |

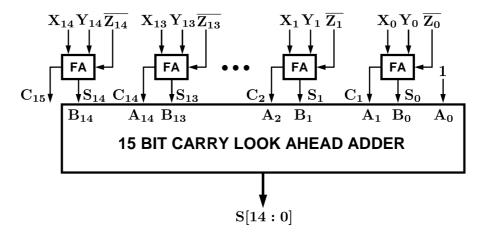

| 3.24 | 15-bit, 3-input adder to implement $\mathbf{X} + \mathbf{Y} - \mathbf{Z}$ |     | 46 |

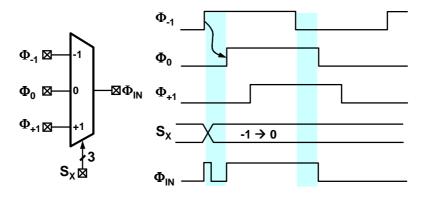

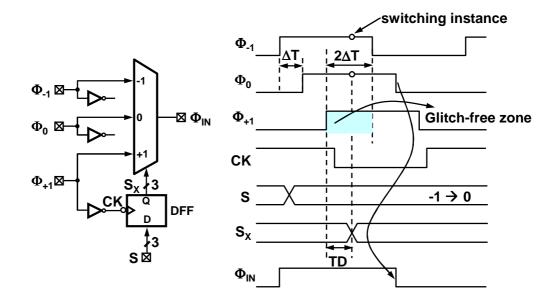

| 3.25 | Illustration of glitches during phase switching                           |     | 47 |

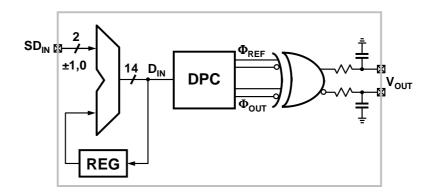

| 3.26 | Glitch-free switching scheme and the associated timing diagram.           | •   | 48 |

| 3.27 | Block diagram of the DPC prototype test chip                              | ••  | 49 |

| Figu | ure                                                                                                                                                                  | Pa  | ge |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----|

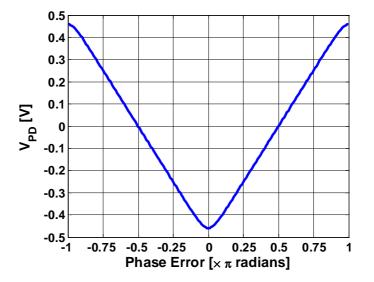

| 3.28 | Simulated XOR transfer function.                                                                                                                                     |     | 49 |

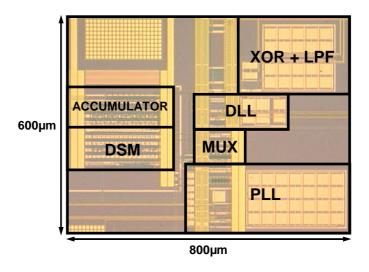

| 3.29 | DPC chip micrograph.                                                                                                                                                 | • • | 50 |

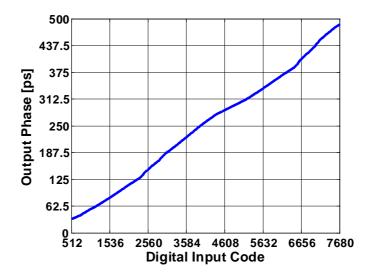

| 3.30 | Measured transfer function of the DPC operating at 1GHz                                                                                                              |     | 51 |

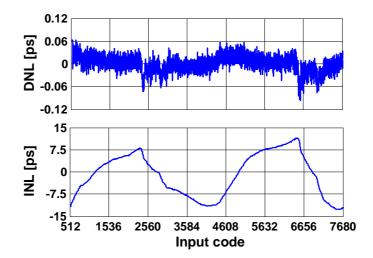

| 3.31 | Measure DNL/INL of the DPC                                                                                                                                           | ••• | 51 |

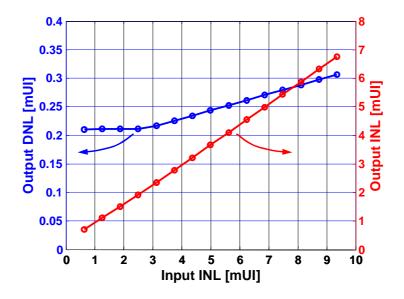

| 3.32 | Effect of the multi-phase generator INL on DPC linearity                                                                                                             | • • | 52 |

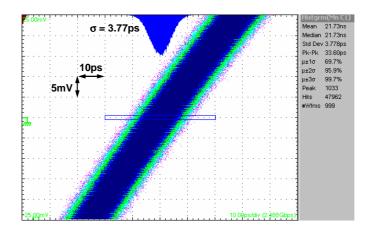

| 3.33 | PLL clock jitter at 1GHz.                                                                                                                                            |     | 52 |

| 3.34 | DPC clock jitter at 1GHz.                                                                                                                                            | • • | 53 |

| 4.1  | Serial signaling system with <i>embedded clock</i>                                                                                                                   |     | 55 |

| 4.2  | Dual-loop CDR.                                                                                                                                                       |     | 56 |

| 4.3  | A representative phase interpolator transfer function                                                                                                                |     | 57 |

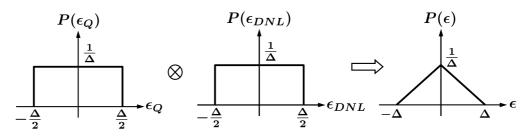

| 4.4  | Calculation of phase error distribution of a phase interpolator<br>with uniformly distributed DNL with a range of $\pm \frac{\Delta}{2}$                             |     | 58 |

| 4.5  | CDR with phase averaging phase interpolator                                                                                                                          |     | 60 |

| 4.6  | Illustration of phase averaging in the Larsson CDR                                                                                                                   |     | 61 |

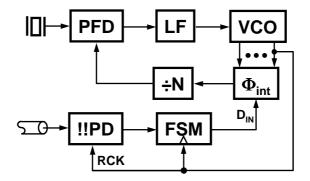

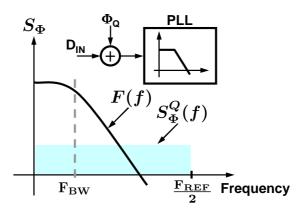

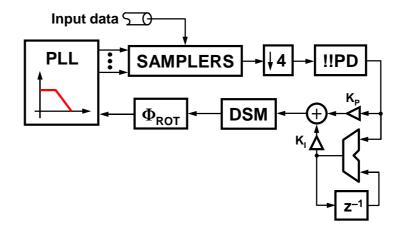

| 4.7  | Proposed CDR architecture.                                                                                                                                           | • • | 63 |

| 4.8  | Phase interpolator transfer characteristics                                                                                                                          |     | 68 |

| 4.9  | Block diagram of the CDR used for stability analysis                                                                                                                 |     | 69 |

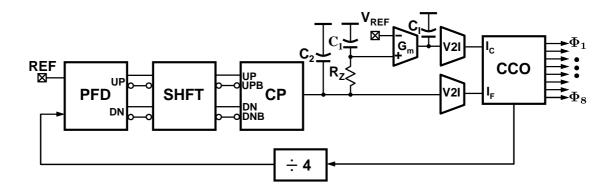

| 4.10 | Split-tuned PLL.                                                                                                                                                     | • • | 71 |

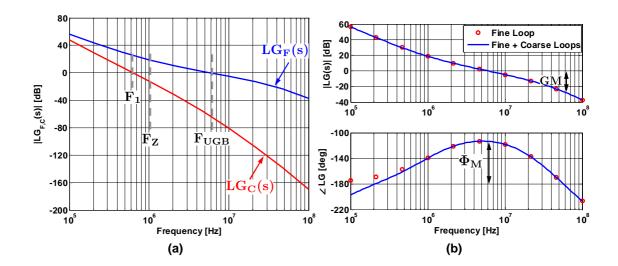

| 4.11 | PLL stability analysis: (a) Coarse and fine loop gain magnitude<br>response (b) Gain and phase margin of fine and sum of the coarse<br>and the fine loops of the PLL | 9   | 73 |

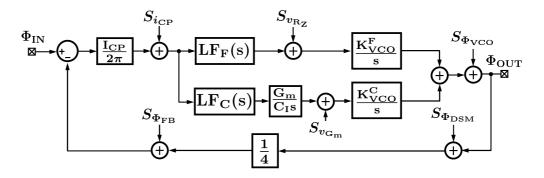

| 4.12 | Small-signal noise model of the PLL including the DSM noise                                                                                                          |     | 75 |

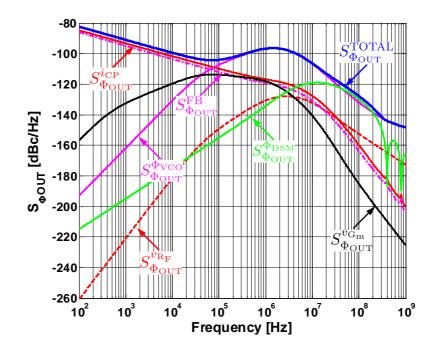

| 4.13 | Simulation illustrating the contribution of individual noise sources to the overall output phase noise.                                                              |     | 77 |

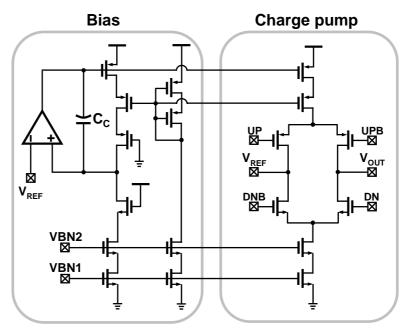

| 4.14 | Replica biased charge pump with improved current matching                                                                                                            |     | 78 |

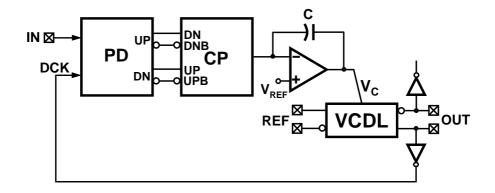

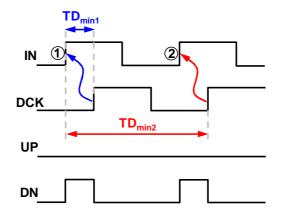

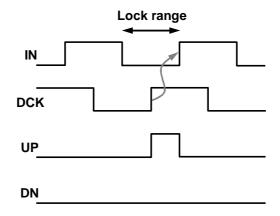

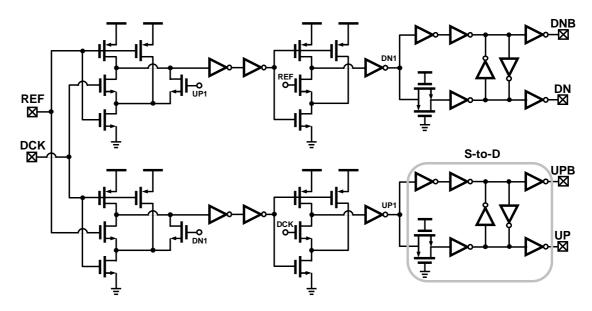

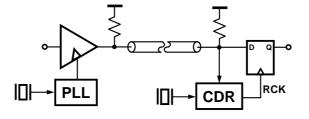

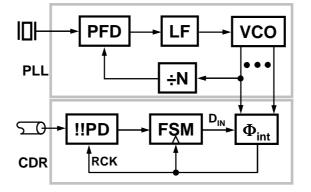

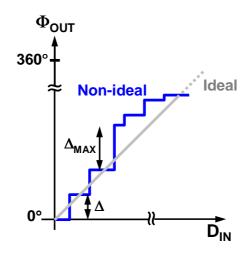

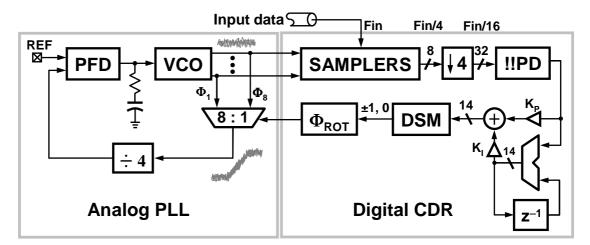

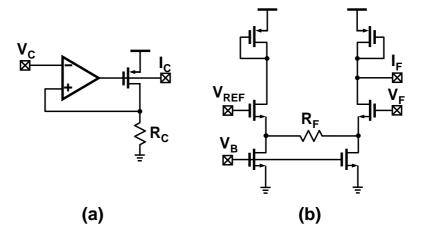

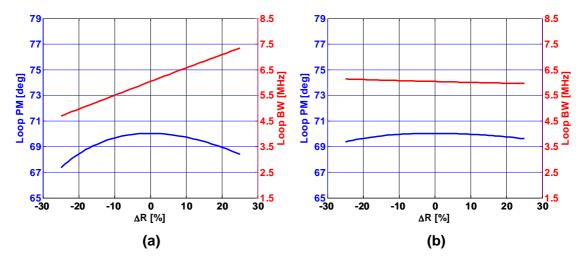

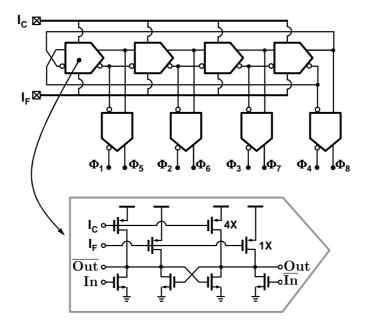

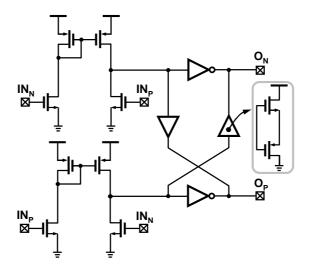

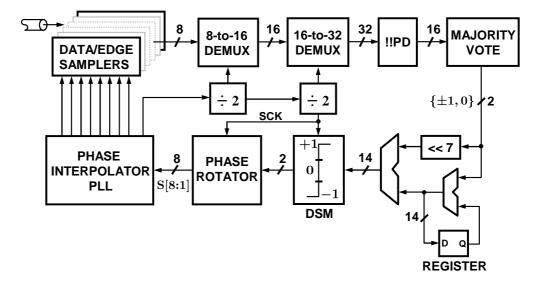

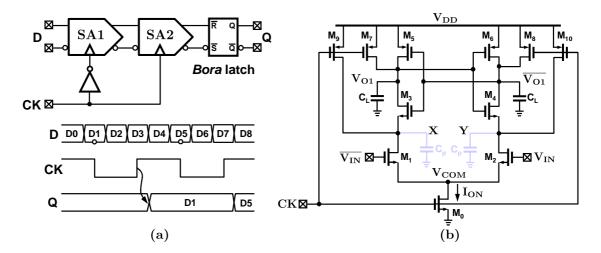

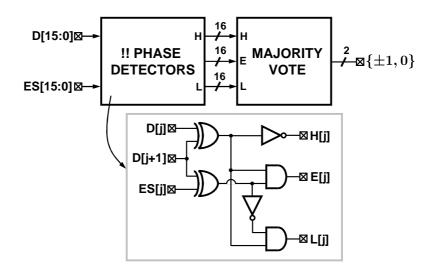

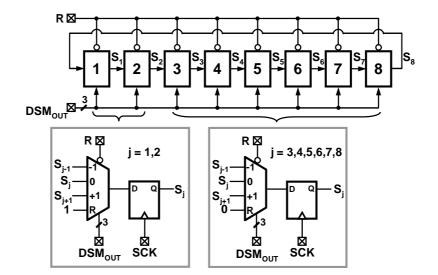

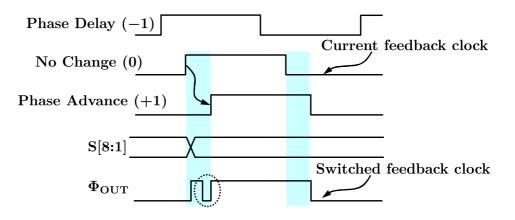

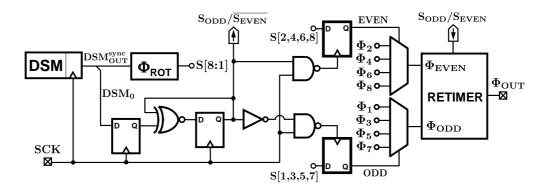

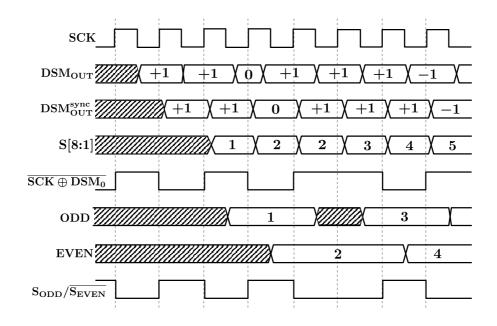

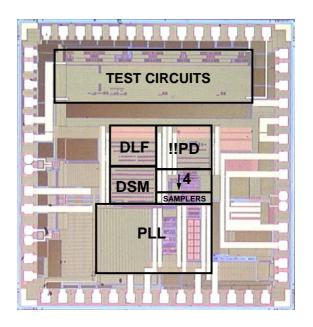

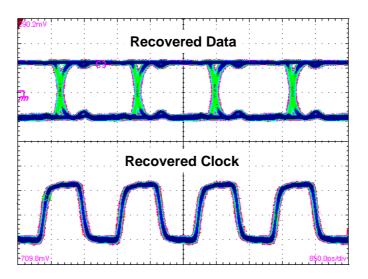

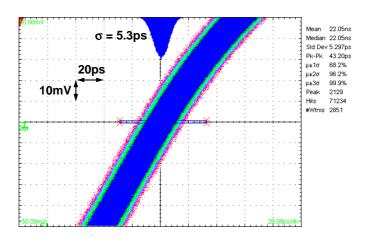

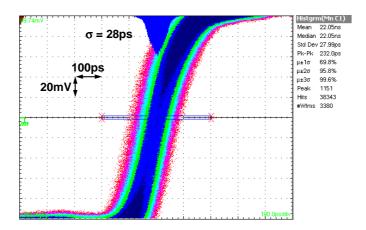

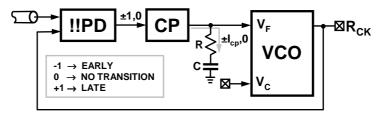

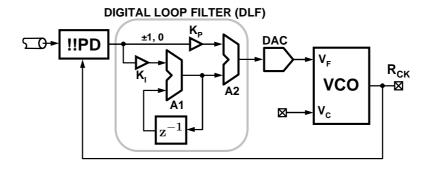

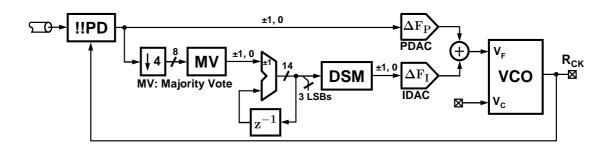

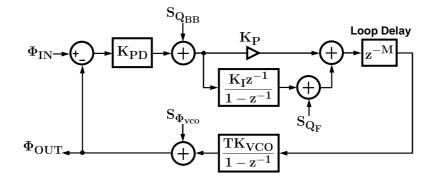

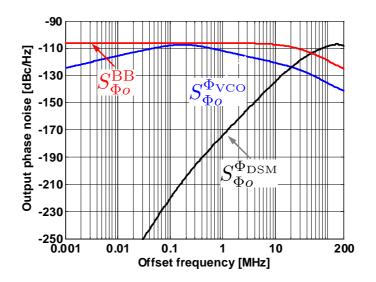

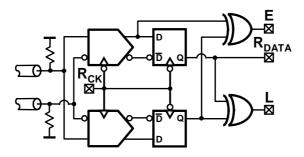

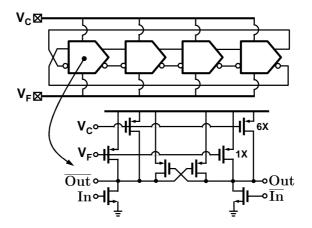

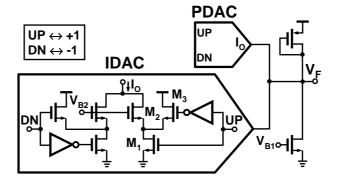

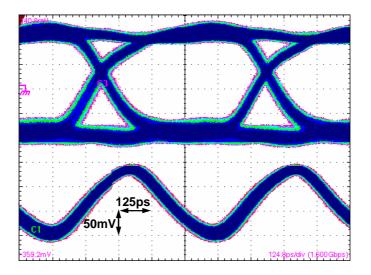

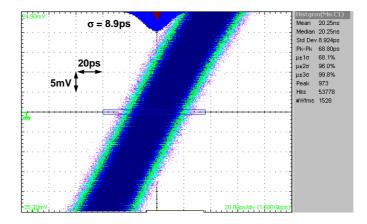

Figure 4.15 V2I circuits: (a) Coarse V2I (b) Fine V2I.... 79 4.16 Effect of filter resistance variation : (a) With out V2Is. (b) With V2Is..... 80 4.17 Split-tuned current controlled oscillator..... 81 4.18 VCO buffer that provides nominally 50% duty cycle. ..... 82 83 4.19 CDR block diagram. 4.20 (a) Two stage front-end sampler circuit and the associated timing diagram (b) Sense-amplifier (SA) schematic..... 84 4.21 Bang-bang phase detection circuitry. ..... 86 4.22 Circular shift register to implement phase rotator..... 86 4.23 Illustration of phase glitches..... 87 4.24 Phase switching control circuit.  $DSM_0$  represents the **0** output of the 3-bit wide  $(\pm 1, 0)$  one hot DSM output..... 88 4.25 Timing diagrams for glitch-free phase switching..... 88 4.26 Die photo..... 90 4.27 Recovered quarter-rate 500Mbps data and 500MHz clock..... 90 91 4.28 PLL jitter when operating at 500MHz. 4.29Recovered clock jitter. 91 Conventional analog CDR. 93 5.15.2A digital CDR obtained by a *s*-to-*z* transformation. ..... 955.3Proposed all-digital CDR..... 96 Linearized CDR model..... 985.45.5Output phase noise contribution from individual noise sources  $(\sigma_i = 7.5ps, \Delta F_P = 4MHz, \Delta F_I = 12MHz, M=3, T = 625ps).$ 99

#### 5.6Data recovery and phase detection circuit..... 100

Page

| Figure |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Page |     |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|

| 5.7    | 4-stage VCO employing split-tuned delay cell                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      | 100 |

| 5.8    | DACs to generate fine control voltage $V_F$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | • •  | 101 |

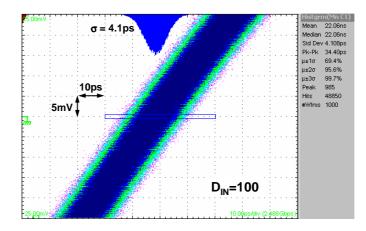

| 5.9    | Recovered data and clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | •••  | 102 |

| 5.10   | Recovered clock jitter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      | 102 |

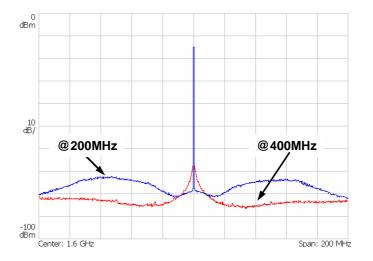

| 5.11   | Recovered clock spectrum. (DSM clocked at 200MHz and 400MHz and 4 | Hz)  | 103 |

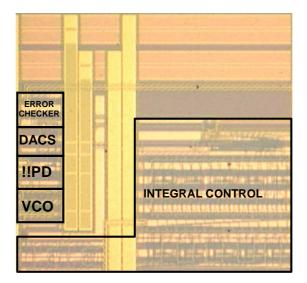

| 5.12   | Chip micrograph                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      | 103 |

## LIST OF TABLES

| Table |                                                                                                    | Page  |  |

|-------|----------------------------------------------------------------------------------------------------|-------|--|

| 3.1   | Mapping between output phase $\Phi_{OUT}$ and coarse phases $\Phi_{j-1}$ , $\Phi_j$ , $\Phi_{j+1}$ |       |  |

| 3.2   | DPC Performance Summary                                                                            | . 54  |  |

| 4.1   | PLL loop parameters                                                                                | . 74  |  |

| 4.2   | Performance Summary                                                                                | . 92  |  |

| 5.1   | Digital CDR Performance Summary                                                                    | . 104 |  |

# DESIGN TECHNIQUES FOR CLOCKING HIGH PERFORMANCE SIGNALING SYSTEMS

#### CHAPTER 1. INTRODUCTION

Recent advances in integrated circuit(IC) fabrication technology coupled with innovative circuit and architectural techniques led to the design of high performance digital systems. Complex systems are built by combining several ICs consisting of millions of transistors operating at multi-gigahertz frequency. These systems require efficient communication between multiple chips for proper functioning of the whole system. However, the off-chip bandwidth scales [1] at a much lower rate compared to the on-chip bandwidth [2], thus making the communication link - also referred to as serial link - between chips the major bottleneck for the overall performance. For example, present day microprocessors run at several gigahertz clock rates, while the speed of the front-side bus is limited to less than a gigahertz. Due to these reasons, there is a great research interest to reduce the gap between the on-chip and off-chip bandwidth.

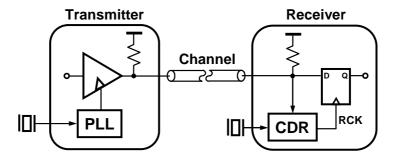

A representative block diagram of a typical serial link is shown in Fig. 1.1. It consists of a transmitter, a channel and a receiver. Dedicated circuits designed for high-speed operation are used in transmitter and receiver to transmit and receive the data respectively. The medium of transmission is called the channel which in the ideal case is simply a wire representing a short circuit. The main issues in the design of these high-speed serial links can be broadly classified into two main categories, namely, channel related and circuit related. First, as the data

Figure 1.1: A typical serial link block diagram.

rates increase the channel behaves as a lossy transmission line, thereby, severely degrading the transmitted data symbols. Second, as the bit-periods shrink, circuit related issues such as limited transmitter and receiver bandwidth and clock jitter will ultimately limit the performance of the overall serial link. In the following sections, both of these issues are elaborated.

#### 1.1 Channel Loss

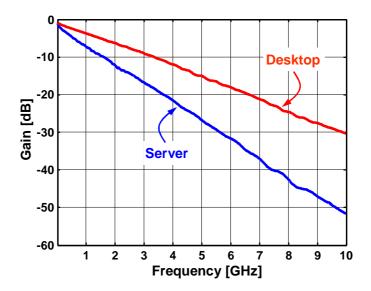

There are several types of channels used in high-speed interconnects, primarily based on the target application. These include short well-controlled copper traces on a printed circuit board (PCB) and coaxial cables used in local-area networks (LAN). The dominant sources of loss in these channels are skin effect and dielectric loss [3]. To illustrate this, the loss of a 20" differential micro-strip line on a FR4 board with two connectors - referred to as *server channel* - and a 6" differential micro-strip line on the same FR4 board indicated as *desktop channel* is shown in Fig. 1.2. The frequency dependent channel loss manifests itself as *Inter Symbol Interference* (ISI) which severely degrades both the timing and voltage margins of the received data. This degradation can be best viewed by plotting the

Figure 1.2: Loss of a 20" (server) and 6" (desktop) FR4 traces with two connectors.

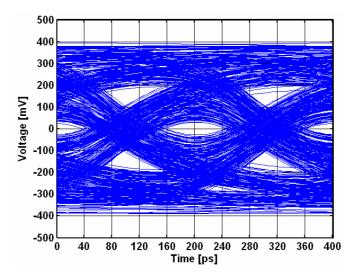

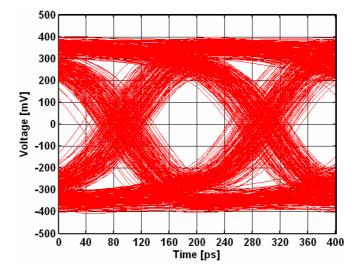

eye diagram. The eye diagram is generated by taking the time-domain signal and overlapping the traces for a certain number of bits. For example, the eye diagram at the receive end of the *server* channel with a span of two bit periods obtained by transmitting 1500 pseudo-random bits ( $\pm 1$ ) at 2.5Gbps is shown in Fig. 1.3. It

Figure 1.3: 2.5Gbps eye diagram.

can be seen from this eye diagram that even though ISI introduces both voltage and timing noise, there is still considerable margin, as indicated by the shaded rectangle, to recover the data. In fact, there is about  $\pm 100$ mV and  $\pm 100$ ps of voltage and timing margin respectively. However, as the data rates increase beyond 2.5Gbps, the channel loss increases further and ISI causes complete closure of the eye. This is demonstrated by the 5Gbps eye diagram shown in Fig. 1.4. Clearly, there is little margin to recover the data and this results in large number of bit errors. Since bit errors are unacceptable, techniques that mitigate ISI and *open the eye* are needed. The frequency shaping filters that flatten the channel

Figure 1.4: 5Gbps eye diagram.

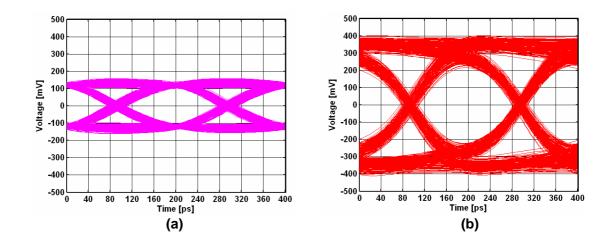

response till Nyquist frequency are called equalizers. These equalizers reduce ISI and can increase the achievable data rates tremendously. The equalized 5Gbps eye diagrams obtained by attenuating the low-frequency content and boosting the high-frequency energy are shown in Fig. 1.5(a) and Fig. 1.5(b) respectively. Even though boosting high frequency seems to be clearly superior method, several implementation issues make this choice less clear. A more detailed analysis of these equalizers including several circuit architectures obtained during the initial phase

Figure 1.5: Equalized 5Gbps eye diagrams: (a) Attenuating low-frequency (b) Boost high-frequency.

of this research are presented in [4]. The focus of the rest of this dissertation is circuits that enable low-jitter clock and data recovery.

#### 1.2 Clock Jitter

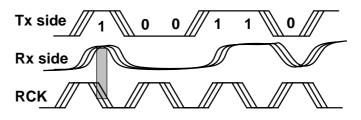

Clock jitter – defined as the uncertainty in the zero-crossings – distorts both the transmitted data and recovered data and severely affects the bit error rate (BER) of the link. Reducing the BER is the primary motivation to design lowjitter clocks. The effect of clock jitter in serial links in depicted in Fig. 2.4. The

Figure 1.6: Effect of clock jitter in serial links

jitter of the phase locked loop (PLL) directly modulates the transmitted data and

the jitter on the recovered clock (RCK) results in sub-optimal sampling of the incoming data, both of which result in degraded BER. In order to provide a better view of the effect of jitter, a simulated 5Gbps eye diagram with transmitter clock jitter is shown in Fig. 1.7. Comparing this to the eye diagram generated with *jitter free* PLL in Fig. 1.5(b), the degradation in both the timing and voltage margin is self evident. In view of these detrimental effects of clock jitter, the focus of this

Figure 1.7: Receive equalized 5Gbps eye diagram with transmitter PLL jitter.

research is to both develop analytical models that enable quick margin analysis in the presence of clock jitter and to investigate and invent new circuit architectures that enable low-jitter clock recovery.

### **1.3** Thesis Organization

Since the focus of this dissertation is techniques to realize low-jitter clocking schemes, Chapter 2 presents an analysis of the effect of clock jitter in high-speed links. This analysis provides expressions to estimate voltage and timing margin degradation due to ISI, transmitter and receiver clock jitter.

Chapter 3 discusses the design of digital to phase converters which are the most important building blocks of source synchronous interfaces. After a brief review of the drawbacks of the existing solutions, a new architecture that achieves sub-picosecond resolution is presented.

A mixed analog/digital clock and data recovery architecture that achieves very high phase and frequency resolution is presented in Chapter 4. This architecture also provides very wide tracking range making it suitable for systems with spread-spectrum clocking.

Chapter 5 discusses a digital clock and data recovery circuit, in which analog blocks such as charge-pump and loop filter are replaced with digital counterparts. Despite it simplicity, this circuit achieves performance comparable to an analog clock and data recovery circuit.

# CHAPTER 2. PERFORMANCE ANALYSIS METHODS FOR SERIAL LINKS

As increasing data rates follow technology scaling, limited timing accuracy that is bound by the unavoidable use of phase- and/or delay-locked loops (PLLs/DLLs) can significantly degrade link performance. Furthermore, due to the need for integration of clock generators such as phase-locked loops (PLLs) in large digital chips, clock jitter is dominated by power supply and substrate noise, both of which do not scale with technology. As data rates increase, bit periods become shorter and the performance of most multi-gigabit links will be limited by clock jitter. Therefore, it is important to analyze the effects of clock jitter on these high speed serial links. In view of these issues, we need an approach to thoroughly analyze the impact of PLL clock jitter on serial links to identify and understand weaknesses, to verify robustness, and to shed light on new techniques to overcome these problems. In the design phase, transceiver systems typically rely on time-domain simulations involving a long sequence of random data and the performance of serial links is often evaluated using eye diagrams of the received data.

There are two problems with this traditional design approach. First, simulation time becomes prohibitively long to evaluate a near worst-case eye diagram. For example, for a serial link with an expected bit error rate (BER) of  $10^{-12}$ , the input random sequence should be at least  $10^{12}$  bits long, and preferably, many times longer in order to get an accurate statistical measure. Second, it is difficult to properly simulate these serial links with time-domain jitter contributions coming from clock sources at both ends (receiver and transmitter) of the link. In

practice, several simplifying assumptions are made regarding the effect of clock jitter on the receive eye diagram. Using these assumptions, the eye diagram generated without clock jitter is modified to obtain an eye diagram with clock jitter. One common way to do this is by closing either side of the eye horizontally by the amount of peak clock jitter. While this method can be helpful in evaluating the effects of jitter at the receiver end, we will show in the following sections that this is an overly optimistic approximation of noise margin degradation for transmitter jitter. In the following sections, an analytical method to incorporate time-domain clock jitter into the design of high speed serial links is presented. This analysis is based on the assumption that jitter is small compared to the clock period. This assumption is valid for well-designed PLLs.

#### 2.1 Worst Case ISI Analysis

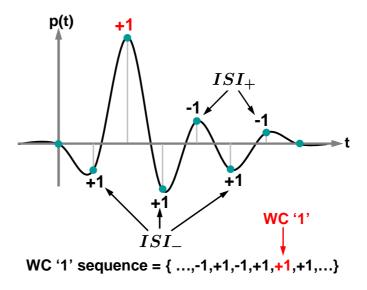

Non-return-to-zero (NRZ) pulses are commonly used as basis functions for discrete data transmission. The response of the channel to the NRZ pulse is defined as the pulse response and is traditionally used to analyze and model the effects of a channel on data transmission and also in the design of equalizers in the case of channels with large attenuation at the frequency of interest. The pulse response is obtained simply by convolving the channel impulse response with the transmitted pulse. A conceptual pulse response along with ISI terms are shown in Fig. 2.1. Since the pulse response is completely deterministic, we can find the sequence of bits that maximizes the ISI. In other words, we can determine the worst case eye closure for a given channel response and data rate. Based on the observation that the total ISI is maximized when negative ISI terms ( $ISI_{-}$ ) are multiplied with +1 and the positive ISI terms ( $ISI_{-}$ ) with -1, the worst-case ISI distortion (positive

Figure 2.1: Pulse response with the corresponding ISI terms.

pulse example is illustrated) is given in Eq. (2.1) [5]:

Worstcase ISI noise =

$$\sum |ISI_{+}| + \sum |ISI_{-}|$$

=

$$\sum ISI_{+} - \sum ISI_{-}$$

=

$$\sum_{k=-\infty}^{\infty} y(t-kT)|_{y(t-kT)>0, k\neq 0}$$

$$-\sum_{k=-\infty}^{\infty} y(t-kT)|_{y(t-kT)<0, k\neq 0}$$

(2.1)

"Worstcase ISI noise" denotes the maximum ISI distortion experienced by the transmitted pulse. Note we can easily determine the data sequence that causes the worst-case noise and this process is also illustrated in Fig. 2.1. The time-reversal inherent in the convolution can be accounted for by simply reading the sequence from right to left.

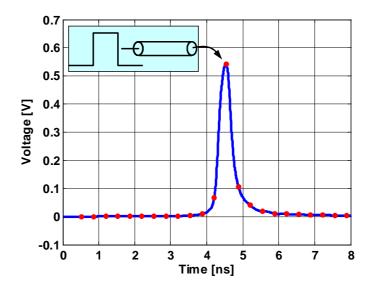

As an example, this analysis is used to calculate the worst case ISI eye diagram for the *server* channel at 3Gbps data rate. The 3Gbps pulse response is shown in Fig. 2.2. The pulse response indicates significant pre and post cursor ISI

Figure 2.2: 3Gbps pulse response.

terms. These ISI terms reduce the voltage margin at the receiver as illustrated by the receive eye diagram in Fig. 2.3. This eye diagram is the result of long transient simulations in which about 2000 random data bits are transmitted across the channel. Also shown in the figure is the worst case (WC) eye obtained by the analysis described above. This figure illustrates that the simulated eye diagram approaches the worst case eye only with very long data streams.

#### 2.2 Analysis of Clock Jitter

Even though the pulse response is very useful for characterizing the ISI, we will find that it is very difficult to analyze the effects of PLL jitter (especially transmitter jitter) because a pulse is created by two adjacent edges with jitter. Consider the serial link model shown in Fig. 2.4. Qualitatively, jitter in the transmit PLL modulates the width of the transmitted NRZ data pulse. This modulation

Figure 2.3: 3Gbps simulated and worst case eye diagrams.

being random, the pulse response of the system displays a level of random variation in accordance with the jitter. This makes the usage of standard deterministic methods difficult. In the case of receiver sampling jitter, several approaches to estimate the signal-to-noise ratio (SNR) loss due to jitter have been proposed [6]. However, it is difficult to translate SNR loss to a reduction of the noise-margin or degradation of the bit error rate (BER) in the case of serial links. To circumvent these problems we need a unifying analysis to accommodate both the transmitter and receiver sampling jitter to calculate the worst-case noise margin degradations. The following analysis and discussions are formulated in the context of a two-level

Figure 2.4: Serial link model with transmitter and receiver clock jitter.

(single-bit-per-symbol) NRZ transceiver system, as this is the most common modulation scheme used in serial links today. Some recent implementations employ four-level NRZ signaling (i.e., PAM-4) which doubles the bits-per-symbol rate. While our analysis and conclusions can easily be transferred to this and a variety of other signaling systems, we stay with the common two-level (binary) NRZ signaling scheme to focus our investigations on how PLL jitter impacts transceiver performance.

#### 2.3 Receiver Clock Jitter

The block diagram used to analyze the clock jitter in the receiver is shown in Fig. 2.5. The sequence of bits (symbols) communicated to the receiver by the transmitter can be considered equally likely and independent of each other. We denote these bits by an independent and identically distributed (i.i.d.) sequence  $\{d_k\}$ . The transmitter produces an output pulse corresponding to data bit  $d_k$ and the variation in the pulse width is determined by the transmitter clock jitter generated by a PLL. We begin our analysis by focusing on the effects of jitter on the

Figure 2.5: Receiver with recovered clock jitter.

receiver end and assume that the transmitter clock is *jitter free*. Later sections will consider the effects of jitter only at the transmitter and the combination of jitter on both transmit and receive clocks. This means that the pulses corresponding to all data bits have equal width. With this assumption, the transmitted pulse train  $\phi(t)$ , in terms of the data bit sequence  $\{d_k\}$ , can be written as [7]

$$\phi(t) = \sum_{k=-\infty}^{\infty} (d[kT] - d[kT - T]) \cdot u(t - kT), \qquad (2.2)$$

where T is equal to the bit period and u(t) is the unit step function such that u(t) = 0 for  $t \le 0$  and u(t) = 1 for t > 0. The output of the channel, y(t), can be evaluated by convolving the input pulse train with the channel impulse response h(t)

$$y(t) = \left[\sum_{k=-\infty}^{\infty} (d[kT] - d[kT - T]) \cdot u(t - kT)\right] \otimes h(t)$$

$$= \sum_{k=-\infty}^{\infty} \left[ (d[kT] - d[kT - T]) \cdot s(t - kT) \right], \qquad (2.3)$$

where  $s(t) = u(t) \otimes h(t)$  is the step response of the channel. A clock and data recovery circuit or a PLL locked to a source-synchronous clock generates a receiver clock phase that is aligned with the incoming data such that the voltage margin (and/or timing margin) is maximized at the input of the detector. But due to various noise sources (intrinsic device and power supply noise), the receiver clock has jitter associated with each of its edges. This jitter is denoted by the jitter sequence  $\{j_{rx}\}$  such that  $j_{rx}[n]$  is the jitter associated with the  $n^{th}$  sampling edge. Note that we have not yet made any assumptions regarding the properties of the  $\{j_{rx}\}$  sequence. With this framework, we can write the sampled channel output as

$$y(nT) = \sum_{k=-\infty}^{\infty} \left[ (d[kT] - d[kT - T]) \cdot s(nT - kT + j_{rx}[nT]) \right].$$

(2.4)

The sampled step response can be approximated with a first-order Taylor series expansion. For practical/realistic channels with finite bandwidths, it is reasonable to assume that the first derivative of the step response exists. It is reasonable to assume that this first-order approximation is valid for the case when  $j_{rx}[n]$  is very small compared to the bit period T. Therefore, an approximate sampled channel step response can be written as

$$s(nT - kT + j_{rx}[nT]) \approx s(nT - kT) + j_{rx}[nT] \cdot \left. \frac{ds(t)}{dt} \right|_{t=nT-kT}$$

$$= s(nT - kT) + j_{rx}[nT] \cdot h(nT - kT). \quad (2.5)$$

Using Eq. (2.5) in Eq. (2.4), we can rewrite the sampled channel output as

$$y(nT) \approx \sum_{k=-\infty}^{\infty} \left[ (d[kT] - d[kT - T]) \cdot s(nT - kT) \right] + \sum_{k=-\infty}^{\infty} \left[ (d[kT] - d[kT - T]) \cdot h(nT - kT) \right] \cdot j_{rx}[nT] = (d[nT] - d[nT - T]) \otimes s[nT] + \left[ (d[nT] - d[nT - T]) \otimes h[nT] \right] \cdot j_{rx}[nT].$$

(2.6)

And rewriting the expression with just the n index,

$$y[n] = a[n] \otimes s[n] + (a[n] \otimes h[n]) \cdot j_{rx}[n], \text{ where } a[n] = d[n] - d[n-1](2.7)$$

The intermediate sequence a[n] is introduced for notational brevity. The first term in Eq. (2.7) is the channel output obtained by sampling the continuoustime channel output with an ideal clock (i.e., no jitter) while the second term represents the equivalent *voltage* noise due to sampling jitter. Qualitatively, the second term in the first-order Taylor series translates the timing jitter into voltage noise depending on the slope of the step response at that instant. This explicit separation of the jitter noise from the signal in Eq. (2.7) enables us to evaluate the worst-case distortion due to ISI and the clock jitter independently. It is important to note that since all practical channels used in multi giga-bit serial links are significantly bandwidth limited, the step response of the channel rises/falls quite slowly. This slow rise/fall translates to high accuracy of the first-order Taylor series. In the case of distortion introduced by clock jitter, the worst-case condition can be evaluated by observing the effect of jitter due to the worst-case ISI data pattern as illustrated in Fig. 2.1. The corresponding jitter noise can be evaluated using the second term of Eq. (2.7),  $(a[n] \otimes h[n]) \cdot j_{rx}[n]$ , by

Receiver Jitter Noise =

$$(\hat{a}[n] \otimes h[n]) \cdot max(j_{rx}[n]),$$

(2.8)

where  $\hat{a}[n]$  is the worst-case/peak ISI distortion data sequence derived using Eq. (2.1).

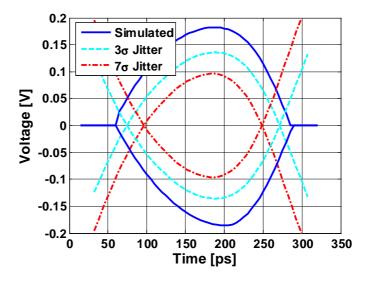

Figure 2.6: Eye diagrams with receiver clock jitter.

The simulation results that demonstrate the noise margin degradation due to the receiver clock jitter are presented next. The simulated eye diagram with 30k data bits and 5ps rms ( $\sigma$ ) jitter is shown in Fig. 2.6. Note that the eye is still wide-open since only a limited amount of data bits are used in the simulation. We now evaluate the receiver eye based on the analysis presented in the preceding section. First, the worst-case ISI data pattern is calculated using Eq. (2.1) and

the jitter noise generated due to this data pattern is calculated using Eq. (2.8). The worst-case eye is then obtained by subtracting the jitter noise from the worstcase ISI eye. The calculated worst-case eye diagrams using  $3\sigma$  and  $7\sigma$  amounts of peak jitter are shown in Fig. 2.6. The noise margin degradation is minimal at the center of the eye and maximum near the zero-crossing. This makes intuitive sense because the center of the eye is reasonably flat (slope is zero) and hence any jitter at the optimal sampling point only results in a small voltage margin degradation. However, due to the larger slope at the edges, jitter translates to a larger voltage margin degradation at the edge of the eye. Also, notice that even with 30k data bits, the simulated eye is not close to the calculated worst-case eye with  $3\sigma$  jitter. This reinforces the fact that it is generally very difficult to find the absolute worst-case margin from time-domain simulations. For this reason, timedomain simulation is seldom used to estimate BER in practice. Commonly used methods incorporate the effects of jitter into the worst-case ISI eye by shifting the ISI eye edges horizontally towards the center of the eye by the peak jitter amount. Even though this method results in a worst-case eye, it provides little insight and is not applicable to the transmitter jitter.

In the case of severely ISI-limited channels, equalization is used to recover some of the high frequency content lost through the channel. An equalizer is typically a filter which inverts the channel response so that the overall response is essentially flat in the band of interest (up to the Nyquist rate of the data), thus reducing the effects of ISI. In serial links employing equalizers, the detector input is simply the sampled channel output convolved with the filter with impulse response W. This is given by

$$y_{eq}[n] = a[n] \otimes s[n] \otimes W[n] + \{(a[n] \otimes h[n]) \cdot j_{rx}[n]\} \otimes W[n].$$

$$(2.9)$$

The worst-case jitter noise and ISI data patterns can be calculated in a similar way as shown earlier in the case without equalization.

#### 2.4 Transmitter Clock Jitter

The block diagram used to analyze the clock jitter in the transmitter is shown in Fig. 2.7. The transmitter clock determines the pulse width of the transmitted bit or symbol. With transmitter clock jitter, the pulse width of the transmitted data bit can be viewed as being modulated by the jitter. This causes degradation of the noise margin at the detector input for the following reasons. First, the transmitter clock jitter causes sub-optimal sampling at the receiver due to the limited tracking bandwidth of the timing-recovery loop. Second, in the case of equalized serial links, the transmitter jitter degrades the equalizer performance. This is because the equalizers are normally optimized for a specific pulse response. Even in the case of adaptive equalizers, the high frequency content of the jitter cannot be tracked due to typically large time constants of the adaptation algorithms [8]. We will now

Figure 2.7: Transmitter with PLL clock jitter.

show that the transmit jitter can be analyzed in a similar framework as shown for receiver sampling clock jitter previously in Section 2.3. Consider Eq. (2.3) repeated below for convenience:

$$y(t) = \left[\sum_{k=-\infty}^{\infty} (d[kT] - d[kT - T]) \cdot u(t - kT)\right] \otimes h(t)$$

$$= \sum_{k=-\infty}^{\infty} \left[ (d[kT] - d[kT - T]) \cdot s(t - kT) \right].$$

In this equation, the sampling instant kT determines the pulse width of the  $k^{th}$  transmitted data pulse/bit. The jitter in the transmitter can be included in the above equation by defining a jitter sequence  $\{j_{tx}\}$  such that  $j_{tx}[k]$  is the jitter associated with the  $k^{th}$  clock edge:

$$y(t) = \left[\sum_{k=-\infty}^{\infty} (d[kT] - d[kT - T]) \cdot u(t - kT - j_{tx}[kT])\right] \otimes h(t)$$

=

$$\sum_{k=-\infty}^{\infty} \left[ (d[kT] - d[kT - T]) \cdot s(t - kT - j_{tx}[kT]) \right].$$

(2.10)

Again, a first-order Taylor series expansion can be used if  $j_{tx}[k] \ll T$ , and the approximate channel output can be written as

$$y(t) \approx \sum_{k=-\infty}^{\infty} \left[ (d[kT] - d[kT - T]) \cdot s(t - kT) \right] \\ + \sum_{k=-\infty}^{\infty} \left[ (d[kT] - d[kT - T]) \cdot h(t - kT) \cdot j_{tx}[kT]) \right].$$

(2.11)

In order to estimate the effects of transmitter clock jitter alone, let us assume for now that the receiver sampling clock is jitter free. In this case, the sampled channel output can be written as

$$y(nT) = \sum_{k=-\infty}^{\infty} \left[ (d[kT] - d[kT - T]) \cdot s(nT - kT) \right] + \sum_{k=-\infty}^{\infty} \left[ (d[kT] - d[kT - T]) \cdot h(nT - kT) \cdot j_{tx}[kT]) \right] = \sum_{k=-\infty}^{\infty} \left[ a[kT] \cdot s(nT - kT) \right] + \sum_{k=-\infty}^{\infty} \left[ (a[kT] \cdot j_{tx}[kT]) \cdot h(nT - kT) \right].$$

(2.12)

And rewriting this first-order approximated output expression with just the n index,

$$y[n] = a[n] \otimes s[n] + (a[n] \cdot j_{tx}[n]) \otimes h[n].$$

(2.13)

Unlike the receiver sampling jitter of Eq. (2.7), the transmitted data difference sequence a[n] is first modulated by the transmitter jitter sequence  $j_{tx}[n]$  and then the resulting sequence is convolved with the channel's impulse response h[n].

Once again, the peak ISI distortion inherent in the first convolution term in Eq. (2.13) can be calculated using Eq. (2.1). However, the peak distortion due to the transmitter jitter noise is different from that of the receiver sampling jitter. Intuitively, we expect the transmit jitter to be filtered by the channel in some fashion and the second term in Eq. (2.13) reinforces our intuition. Due to the modulation of a[n] by the jitter sequence  $j_{tx}[n]$ , we can evaluate the peak distortion due to the transmitter clock jitter, i.e., the peak distortion of the second term  $(a[n] \cdot j_{tx}[n]) \otimes h[n]$ , by

Transmit Jitter Noise =

$$(|\hat{a}[n]| \cdot max(j_{tx}[n])) \otimes |h[n]|,$$

(2.14)

where  $\hat{a}[n]$  is the worst-case/peak ISI distortion data sequence derived using Eq. (2.1). It is interesting to note that the peak distortion due to the transmitter clock jitter noise can be potentially greater than that of the receiver sampling jitter for the similar amounts of receiver  $(j_{rx})$  and transmitter  $(j_{tx})$  jitter.

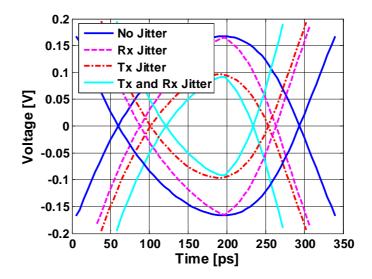

Similar to the receiver sampling jitter case, the simulated and calculated worst-case eye diagrams with the transmitter jitter are shown in Fig. 2.8. Again, the simulated eye is not close to the calculated worst-case eye even with  $3\sigma$  jitter. It is interesting to note that the noise margin degradation due to transmitter jitter is severe all across the eye unlike the receiver jitter case, where degradation is minimal at the center of the eye and maximum near the zero-crossing. This is consistent with Eq. (2.15) which showed that the jitter is shaped along with the data symbols by the band-limited channel. As in the analysis of the receiver

Figure 2.8: Eye diagrams with transmitter PLL clock jitter.

sampling jitter with receiver equalizer, the transmitter's clock jitter analysis can also be extended to the serial link with receive equalizer. The input to the detector, with the receive equalizer, is simply the convolution of the raw channel output and the FIR equalizer:

$$y_{eq}[n] = \{a[n] \otimes s[n] + (a[n] \cdot j_{tx}[n]) \otimes h[n]\} \otimes W[n]$$

$$= a[n] \otimes s[n] \otimes W[n] + (a[n] \cdot j_{tx}[n]) \otimes h[n] \otimes W[n].$$

(2.15)

Equalization is also sometimes used on the transmit side, and this is often referred to as transmit pre-emphasis. Transmit pre-emphasis shapes the transmitted pulse so as to make the channel response flat up to the Nyquist rate of the data. Even though this type of equalization is transmit power limited [9], it is commonly applied [10], [11] because of its relative simplicity in comparison to building a more extensive receive equalizer. The jitter analysis for serial links with transmit equalizer/pre-emphasis directly follows from Eqs. (2.7) and (2.13) with a corresponding equalized/pre-emphasized data sequence  $\{d_k\}$ .

## 2.5 Transmitter Jitter and Receiver Jitter

We analyzed transmitter jitter and receiver sampling jitter independently until now. This was done to demonstrate the effect of each of the jitter terms independently. Because both effects of jitter typically appear together in a serial link, we now summarize how the above analysis can be extended to include both the transmitter and receiver jitter. Equation (2.10) defines the channel output with transmitter jitter and Eq. (2.4) was derived to consider receive sampling jitter. Combining the results of Eqs. (2.10) and (2.4), we can re-write the sampled channel output which incorporates both of the jitter terms:

$$y(nT) = \sum_{k=-\infty}^{\infty} \left[ (d[kT] - d[kT - T]) \cdot s(nT - kT + j_{rx}[nT] - j_{tx}[kT]) \right]. \quad (2.16)$$

Once again, we can approximate the step response using a first-order Taylor series approximation for two variables (i.e. when  $j_{tx}[k] \ll T$  and  $j_{rx}[k] \ll T$ ):

$$s(nT - kT + j_{rx}[nT] - j_{tx}[kT]) \approx s(nT - kT)$$

$$+ j_{rx}[nT] \cdot \frac{ds(t)}{dt}\Big|_{t=nT-kT} - j_{tx}[kT] \cdot \frac{ds(t)}{dt}\Big|_{t=nT-kT}$$

$$= s(nT - kT)$$

$$+ j_{rx}[nT] \cdot h(nT - kT)$$

$$+ j_{tx}[kT] \cdot h(nT - kT). \qquad (2.17)$$

Putting Eqs. (2.16) and (2.17) together, we can write the channel output as

$$y[n] \approx a[n] \otimes s[n] + (a[n] \otimes h[n]) \cdot j_{rx}[n] + (a[n] \cdot j_{tx}[n]) \otimes h[n].$$

(2.18)

Since we did not use any specific properties of the jitter sequence, Eq. (2.18) is valid for any jitter sequences  $j_{tx}[n]$  and  $j_{rx}[n]$ . The correlation between  $j_{tx}[n]$  and  $j_{rx}[n]$ , if any, is determined by the clocking scheme and the system. By defining the jitter sequences accordingly, the trade-offs between various clocking schemes (e.g. mesochronous, source synchronous, and embedded clocking [3]) can be analyzed using Eq. (2.18).

The properties of the individual jitter sequence depend on the type of clock source used and the system architecture of the serial link. In most situations, it would be reasonable to assume for the worst case that the transmitter and the receiver jitter properties are uncorrelated. However, any amount of observed correlation between the transmit and receive jitter would result in an overall improvement of the system. The calculated eye-diagram incorporating both the transmitter and receiver jitter is shown in Fig. 2.9. Eye diagrams calculated using zero jitter (i.e., only worst-case ISI), transmitter jitter alone, and receiver jitter alone are also shown. It is clear that the transmitter and receiver jitter degrade both the voltage margin and the timing margin. However, the transmitter jitter has a more adverse affect on both the voltage and timing margins.

## 2.6 Summary

The analysis and net effects of receiver and transmitter clock jitter on highspeed serial links are presented in this chapter. In particular, the effect of transmitter clock jitter and receiver sampling jitter on the worst-case ISI condition is analyzed. Based on the linear time-invariant assumptions of the channel and using the first-order Taylor series approximation, analytical expressions representing the detector input for various conditions are derived. Interestingly, this analysis shows

Figure 2.9: Eye diagrams with transmitter PLL clock and recovered clock jitter.

that the transmitter jitter has more deleterious effect on the link performance compared to receiver jitter. The noise due to jitter was decoupled from the expression of the channel output without jitter. This enables efficient calculation of the noise margin degradation due to jitter. Mathematical expressions useful for calculating the receive and transmit jitter degradations are summarized. Behavioral simulations indicate a good match between the calculation and simulation. This analysis enables efficient calculation of the worst-case margin without indulging in prohibitively long simulations.

# CHAPTER 3. HIGH RESOLUTION DIGITAL-TO-PHASE CONVERTERS

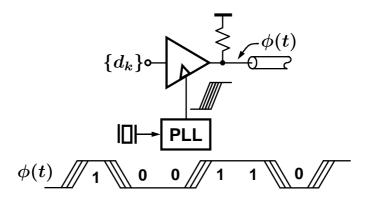

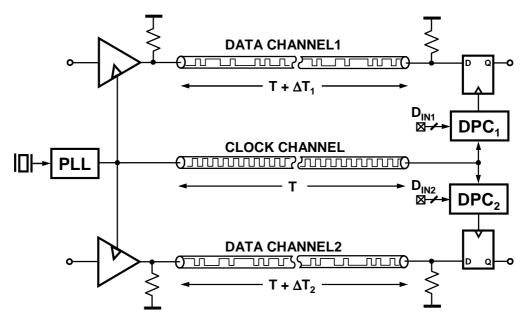

Source-synchronous interfaces are a class of point-to-point links that are widely used in microprocessors and communication switches. A simplified block diagram of a typical source-synchronous interface is shown in Fig. 3.1. In this

Figure 3.1: A typical source-synchronous interface.

system, a clock is transmitted along with the data on a separate channel to the receiver. In order to reduce the overhead of an extra channel, the clock channel is shared among multiple data channels. The clock edges are synchronized with the data transitions at the transmitter. If the data and clock transmission lines are perfectly matched, the time of flight of the data and the clock are equal and as a result, clock and data remain synchronized at the receiver as well. However, as data rates increase to multi-gigabit range, it is uneconomical to match the time of

flight of clock and data to pico-second accuracy. This mismatch results in a skew between the clock and data at the receiver causing sub-optimal sampling of the incoming data. In order to improve the timing margin by reducing the skew between the received clock and data, a method to introduce a controlled phase shift on the clock is needed. The focus of the rest of the chapter is the implementation of circuits that provide a means to introduce such a programmable phase shift. A digital to phase converter (DPC) is one such circuit block that is often used to introduce a phase shift whose amount is controlled by an input digital word  $D_{IN}$ . It is important to note that the resolution of the DPC is of paramount importance as this determines the residual skew between the clock and data which in turn directly affects the bit-error-rate (BER) of the link. Even though the design of the DPC is presented in the context of source-synchronous interfaces, it is worth mentioning that there are several other applications for digital to phase converters in measurement instrumentation and the techniques developed here can be directly applied in those applications.

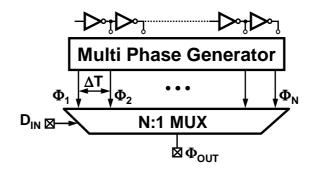

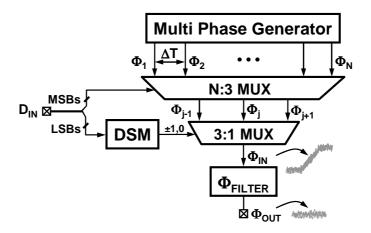

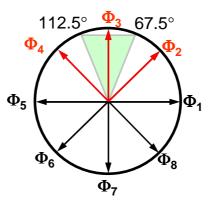

Before we present the proposed DPC architecture it is instructive to review the disadvantages of existing architectures. One of the earliest implementations of the DPC is shown in Fig. 3.2 [12]. It consists of a multi phase generator which

Figure 3.2: DPC using phase selection.

provides N clock phases separated by a delay of  $\Delta T$ . These multiple phases ( $\Phi_1$  to

$\Phi_{\rm N}$ ) are typically generated through a chain of inverters whose delay is precisely adjusted to  $\Delta T$  by a feedback loop. An N-to-1 mux is used to select one of the N phases based on the input digital word D<sub>IN</sub>, thereby introducing a phase shift in steps of  $\Delta T$  on the output. There are several drawbacks with this approach. First, the resolution  $\Delta T$  is limited by the minimum delay of the inverter in a given process. Second, since  $\Delta T$  is equal to a fraction of the clock period  $(\frac{T_{\rm period}}{N})$ the resolution scales directly with the frequency, thereby degrading it at a lower operating frequency. Finally, the phase selection process introduces unwanted discrete phase jumps in the output phase. Despite its simplicity, due to these performance limiting factors, the use of this DPC is very limited in multi-giga bit interfaces.

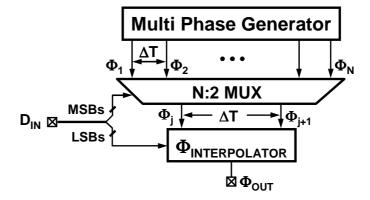

A more commonly used DPC architecture that overcomes some of these drawbacks is depicted in Fig. 3.3 [13], [14], [15]. This architecture combines the phase

Figure 3.3: DPC using phase selection and interpolation.

selecting multiplexer with a phase interpolator. The most significant bits (MSBs) of the input digital word are used to select two adjacent phases,  $\Phi_{j}$ ,  $\Phi_{j+1}$ , from the N phases using an N:2 multiplexer (mux). These two phases are interpolated by a phase interpolator controlled by the least significant bits (LSBs) to generate the required output phase  $\Phi_{OUT}$ . As a result of phase interpolation, the resolution of

this DPC is not limited by the minimum inverter delay. However, the effectiveness of the interpolation depends largely on the input rise time, phase separation  $\Delta T$ , and the interpolator output time constant.

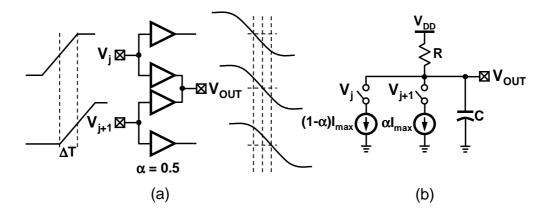

Figure 3.4: Phase interpolator: (a) Operation (b) Model.

Consider the conceptual phase interpolator block diagram and its model shown in Fig. 3.4. The output voltage of the phase interpolator can be written as [16]:

$$V_{OUT}(t) = V_{DD} + (1 - \alpha) \cdot R \cdot I_{max} \cdot \left\{ \frac{t}{\tau_r} \cdot u(t) + \left[ 1 - \frac{t}{\tau_r} \right] \cdot u(t - \tau_r) \right\} \cdot \left( e^{-\frac{t}{RC}} - 1 \right) + \alpha \cdot R \cdot I_{max} \cdot \frac{t - \Delta T}{\tau_r} \cdot u(t - \Delta T) \cdot \left( e^{-\frac{t - \Delta T}{RC}} - 1 \right) + \alpha \cdot R \cdot I_{max} \cdot \left[ 1 - \frac{t - \Delta T}{\tau_r} \right] \cdot u(t - \Delta T - \tau_r) \cdot \left( e^{-\frac{t - \Delta T}{RC}} - 1 \right), \quad (3.1)$$

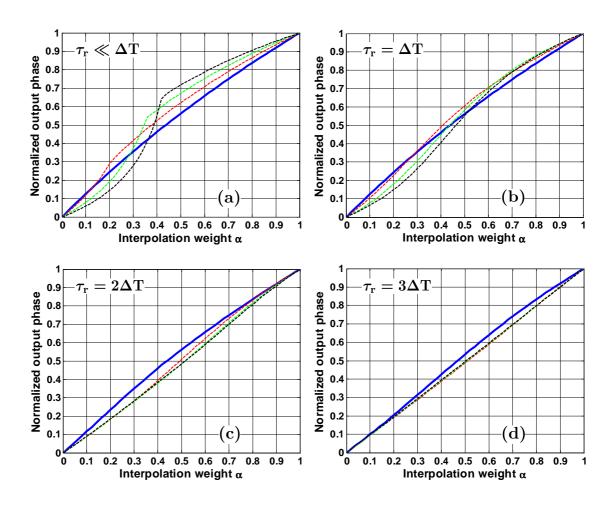

where  $\alpha$  is the interpolation weight,  $I_{max}$  is the maximum bias current,  $\tau_r$  is the rise time of the input signal, and  $\Delta T$  is the phase spacing between the input signals. Eq. (3.1) shows that the interpolator delay depends not only on  $\alpha$  but also on the interpolator output time constant (RC), rise time of the inputs, and the time difference between the inputs. This dependence is illustrated in Fig. 3.5, in which the interpolator transfer function ( $\alpha$ -to-output phase) is plotted for varying values of  $\Delta T$  and  $\tau_r$ . All the time parameters,  $\Delta T$ ,  $\tau_r$ , and output phase are normalized

Figure 3.5: Analysis of the phase interpolator linearity. The solid line represents the transfer function with  $\frac{\Delta T}{RC} = 0.5$  and dashed lines with  $\frac{\Delta T}{RC} = 1, 1.5, 2$ .

to the output RC time constant. The output phase is referenced to the delay when the interpolation weight is zero as expressed by

Normalized output phase at

$$\alpha 1 = \frac{T_D|_{\alpha=\alpha 1} - T_D|_{\alpha=0}}{RC}$$

, (3.2)