### AN ABSTRACT OF THE THESIS OF

Kyle M. Webb for the degree of <u>Master of Science</u> in

<u>Electrical and Computer Engineering</u> presented on <u>June 27, 2005</u>.

Title: <u>A Test Fixture and Deembedding Procedure for</u>

High-Frequency Substrate Characterization

Abstract approved:

Terri Fiez

Karti Mayaram

At frequencies exceeding 1-2 GHz, the substrate network models used in substrate coupling simulation must account for the reactive nature of the substrate. Unlike at low frequencies, where the purely resistive substrate models can be validated through DC resistance measurements, these high-frequency models, comprising reactive components, must be validated through high-frequency network analyzer measurements. Accurately obtaining such measurements requires careful design of both a measurement test fixture as well as a measurement deembedding procedure.

A test fixture has been fabricated and a deembedding procedure designed to enable high-frequency (up to 20 GHz) network parameter measurements of a silicon substrate. A test chip, containing a variety of substrate test structures has been fabricated in a 0.35  $\mu$ m CMOS process on a heavily-doped substrate. The design of the test fixture, test chip, and deembedding procedure has been validated through extensive simulations in HFSS. Measurements have been made on the test chips mounted in the test fixture. The performance of the test fixture and measurement deembedding procedure has been evaluated, and suggestions for future improvements in this area are presented. ©Copyright by Kyle M. Webb June 27, 2005 All Rights Reserved A Test Fixture and Deembedding Procedure for High-Frequency Substrate Characterization

by

Kyle M. Webb

A Thesis

submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Master of Science

Completed June 27, 2005 Commencement June 2006 Master of Science thesis of Kyle M. Webb presented on June 27, 2005

APPROVED:

Co-Major Professor, representing Electrical and Computer Engineering

Co-Major Professor, representing Electrical and Computer Engineering

Director of the School of Electrical Engineering and Computer Science

Dean of the Graduate School

I understand that my thesis will become part of the permanent collection of Oregon State University libraries. My signature below authorizes release of my thesis to any reader upon request.

Kyle M. Webb, Author

#### ACKNOWLEDGMENT

First, I'd like to express thanks to my advisors, Dr. Terri Fiez and Dr. Karti Mayaram, for supporting this research and providing guidance along the way. Thanks also to Dr. Andreas Weisshaar and Dr. David Hackleman for serving on my thesis committee.

Many people have taken time over the past couple of years to discuss and suggest solutions to problems encountered in this research. Among them are Dr. Raghu Settaluri, and Dr. Andreas Weisshaar. Thanks to Dr. Leonard Hayden from Cascade Microtech for all of his help and for the ideas he contributed to this work.

This research involved a great deal of time working with various simulation tools. Thanks to Mike Phillips for his help with HFSS, and to Scott Hazenboom for his help with ADS Momentum. Thanks also to Dr. Chenggang Xu for help with his EPIC substrate simulation tool.

Thanks to Martin Held for helping with the release of the test chip for fabrication at MOSIS. Thanks also to the all of the other students in the substrate coupling research group with whom I've worked over the past couple of years.

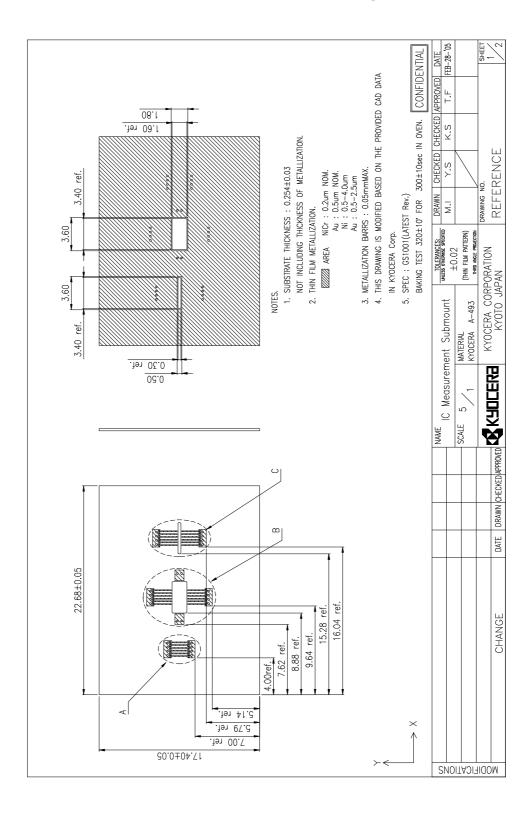

The test fixture assemblies were fabricated by Kyocera. I'd like to thank Matt Driscoll and Jim Shaver of Kyocera for their support of this work.

Finally, I'd like to thank the Design Validation Division of Agilent Technologies, for allowing me to take a leave of absence from my job and return to school, and for their financial support of my education.

# TABLE OF CONTENTS

| 1 | INTI | RODUCTION                                       | 1  |

|---|------|-------------------------------------------------|----|

|   | 1.1  | Background and Motivation                       | 1  |

|   | 1.2  | Thesis Outline                                  | 5  |

| 2 | AN ( | OVERVIEW OF PRIOR WORK                          | 6  |

| 3 | TES  | T FIXTURE DESIGN                                | 9  |

|   | 3.1  | Off-Chip Probing                                | 9  |

|   | 3.2  | Deembedding Theory                              | 11 |

|   |      | 3.2.1 Series Impedances                         | 11 |

|   |      | 3.2.2 Shunt Admittances                         | 12 |

|   |      | 3.2.3 Series Two-Port Test Fixture Sections     | 14 |

|   | 3.3  | Test Fixture Assembly                           | 15 |

|   |      | 3.3.1 The Test Chip and On-Chip Test Structures | 16 |

|   |      | 3.3.2 The Ceramic Substrate                     | 19 |

| 4 | A FO | DUR-STEP DEEMBEDDING PROCEDURE                  | 23 |

|   | 4.1  | Test Fixture Model                              | 24 |

|   | 4.2  | Step One: Micro-Strip Transmission Lines        | 25 |

|   | 4.3  | Step Two: Bondwires                             | 26 |

|   | 4.4  | Step Three: On-Chip Traces                      | 27 |

|   |      | 4.4.1 Chain Parameter Factorization             | 29 |

|   | 4.5  | Step Four: Shunt Admittances                    | 31 |

| 5 | SIM  | ULATION                                         | 34 |

# TABLE OF CONTENTS (Continued)

|    | 5.1  | Probe-to-Probe Test Fixture Simulations         | 35 |

|----|------|-------------------------------------------------|----|

|    |      | 5.1.1 Simulations of a 1 K $\Omega$ Resistor    | 38 |

|    | 5.2  | Simulations of On-Chip Test structures          | 43 |

| 6  | MEA  | SUREMENTS                                       | 52 |

|    | 6.1  | Test Setup                                      | 52 |

|    | 6.2  | Initial Measurements                            | 52 |

|    | 6.3  | Revised Simulations                             | 57 |

|    |      | 6.3.1 Correlation with Measurements             | 57 |

|    |      | 6.3.2 Simulations of Test Fixture Modifications | 60 |

| 7  | CON  | CLUSION AND SUGGESTIONS FOR FUTURE WORK         | 64 |

|    | 7.1  | Conclusion                                      | 64 |

|    | 7.2  | Suggestions for Future Work                     | 65 |

| BI | BLIO | GRAPHY                                          | 67 |

| Ał | PPEN | DICES                                           | 69 |

|    | APP  | ENDIX A Test Fixture Mechanical Drawings        | 71 |

|    | APP  | ENDIX B Matlab Deembedding Code                 | 73 |

|    | APP  | ENDIX C Test Fixture Photomicrographs           | 79 |

# LIST OF FIGURES

| Figur | <u>e</u>                                                                                                     | Page |

|-------|--------------------------------------------------------------------------------------------------------------|------|

| 1.1   | Low-frequency resistive substrate network model                                                              | . 4  |

| 1.2   | High-frequency substrate network model.                                                                      |      |

| 1.3   | The substrate as a two-port network                                                                          | . 4  |

| 2.1   | Test structures used for previous measurements at OSU                                                        |      |

| 3.1   | Preliminary test fixture concept                                                                             | . 1( |

| 3.2   | Parasitic impedance in series with the network being measured                                                | . 12 |

| 3.3   | An example of parasitic shunt admittances associated with the test fixture.                                  | . 13 |

| 3.4   | Pi-network representation of the substrate network and the parasitic test fixture admittances which shunt it | . 14 |

| 3.5   | Chain parameter representation of test fixture parasitics appearing in series with the substrate network.    | . 15 |

| 3.6   | Test fixture assembly                                                                                        | . 16 |

| 3.7   | Die photo of the test chip, showing four test structures and two deembedding structures                      | . 18 |

| 3.8   | Close-up view of the die mounted in the cavity                                                               | . 20 |

| 3.9   | Transmission line characterization structures                                                                | . 21 |

| 3.10  | Bondwire characterization structures.                                                                        | . 21 |

| 4.1   | Test fixture model used for deembedding                                                                      | . 24 |

| 4.2   | Model of the network corresponding to the data after step one of the deembedding procedure                   | . 25 |

| 4.3   | Model of the network corresponding to the data after step two of the deembedding procedure                   | . 27 |

| 4.4   | Dimensions of the through trace and trace segments                                                           | . 28 |

| 4.5   | Model of the network corresponding to the data after step three of<br>the deembedding procedure.             | . 32 |

| 5.1   | HFSS structure for the simulation of a 1 K $\Omega$ resistor embedded in the test fixture.                   | . 30 |

# LIST OF FIGURES (Continued)

Figure

| 5.2  | Reference networks for the (a) first and (b) second deembedding steps.                                                                                                                                   | 39 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5.3  | Simulated S-parameters for a 1 K $\Omega$ resistor embedded in the test fixture. (a) S <sub>11</sub> , (b) S <sub>21</sub>                                                                               | 40 |

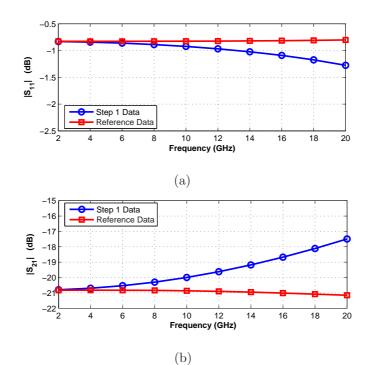

| 5.4  | Simulated S-parameters for a 1 K $\Omega$ resistor following the first deembedding step. (a) S <sub>11</sub> after step 1. (b) S <sub>21</sub> after step 1                                              | 41 |

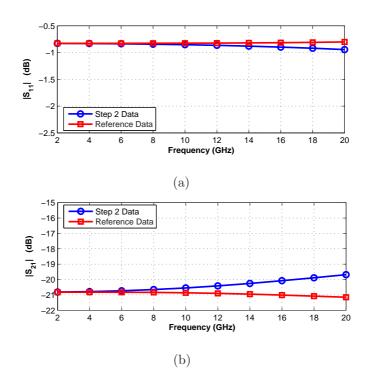

| 5.5  | Simulated S-parameters for a 1 K $\Omega$ resistor following the second deembedding step. (a) S <sub>11</sub> after step 2. (b) S <sub>21</sub> after step 2                                             | 42 |

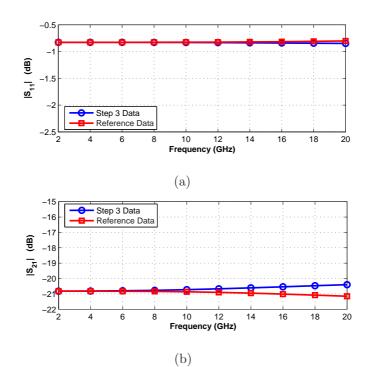

| 5.6  | Simulated S-parameters for a 1 K $\Omega$ resistor following the third deembedding step. (a) S <sub>11</sub> after step 3. (b) S <sub>21</sub> after step 3                                              | 43 |

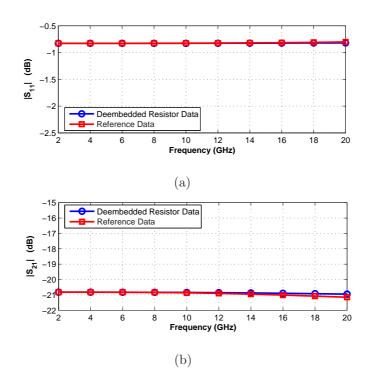

| 5.7  | Simulated S-parameters for a 1 K $\Omega$ resistor following the final deembedding step. (a) S <sub>11</sub> after step 4. (b) S <sub>21</sub> after step 4                                              | 44 |

| 5.8  | Simulated deembedded self and mutual admittances for the 1 K $\Omega$ resistor. (a) Self conductance, (b) self susceptance, (c) mutual conductance, and (d) mutual susceptance.                          | 45 |

| 5.9  | Three-layer substrate used for simulation                                                                                                                                                                | 46 |

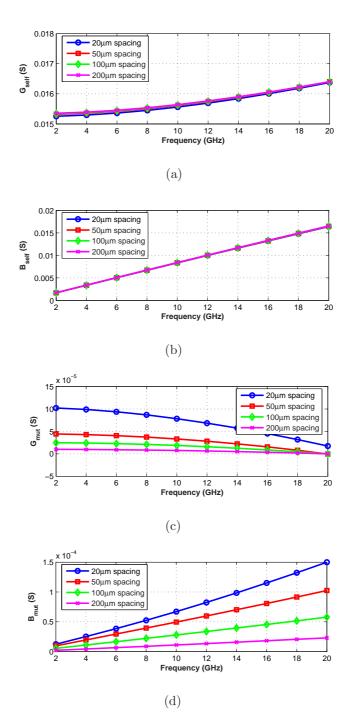

| 5.10 | Simulated deembedded self and mutual admittances for a pair of $10\mu m \ge 10\mu m$ substrate contacts. (a) Self conductance, (b) self susceptance, (c) mutual conductance, and (d) mutual susceptance  | 47 |

| 5.11 | Simulated deembedded self and mutual admittances for a pair of $60\mu m \ge 60\mu m$ substrate contacts. (a) Self conductance, (b) self susceptance, (c) mutual conductance, and (d) mutual susceptance  | 48 |

| 5.12 | Simulated deembedded self and mutual admittances for a pair of $10\mu m \ge 60\mu m$ substrate contacts. (a) Self conductance, (b) self susceptance, (c) mutual conductance, and (d) mutual susceptance  | 49 |

| 5.13 | Simulated deembedded self and mutual admittances for a pair of $50\mu m \ge 100\mu m$ substrate contacts. (a) Self conductance, (b) self susceptance, (c) mutual conductance, and (d) mutual susceptance | 50 |

|      |                                                                                                                                                                                                          |    |

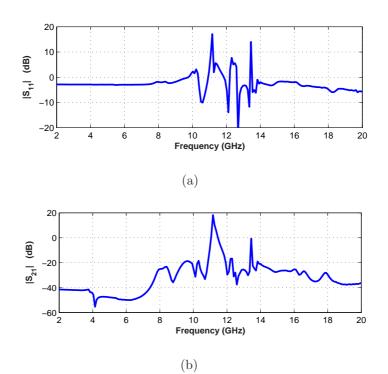

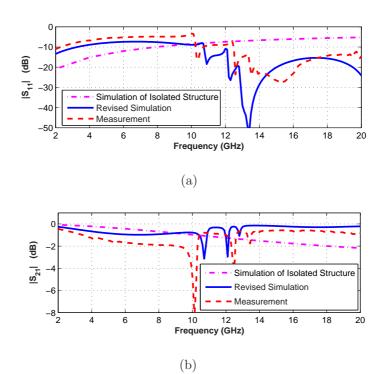

6.1 S-parameters from the initial measurements, showing the failure of the measurement and deembedding procedure. (a)  $S_{11}$ , (b)  $S_{21}$ . . . . . 53

# LIST OF FIGURES (Continued)

| <u>e</u>                                                                                                                                                                                                                                                                                                                                                                                    | Page                                                                                                                                                                                                                                             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

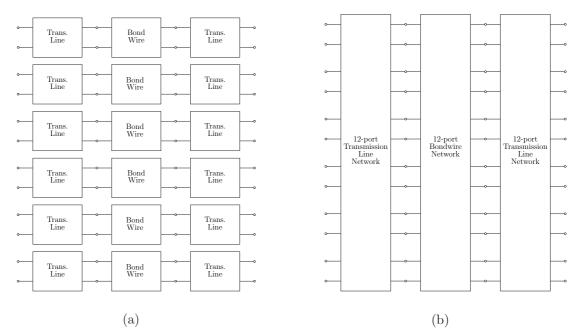

| (a) The deembedding procedure assumes that the transmission lines<br>and bondwires can be modeled as isolated two-port networks. (b) A<br>more realistic model accounts for coupling, and treats the traces and<br>bondwires as 12-port networks                                                                                                                                            |                                                                                                                                                                                                                                                  |

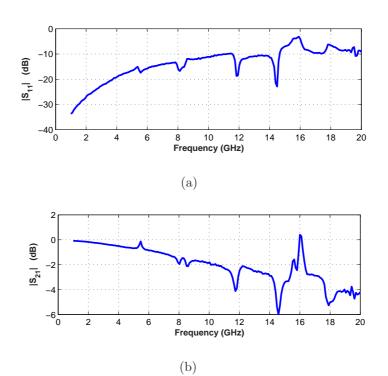

| S-parameters for the on-chip through trace deembedded from measurements taken after removing all other bondwires. (a) $S_{11}$ , (b) $S_{21}$ .                                                                                                                                                                                                                                             | . 56                                                                                                                                                                                                                                             |

| Revised HFSS structure for the simulation of the bondwire charac-<br>terization structure.                                                                                                                                                                                                                                                                                                  | . 58                                                                                                                                                                                                                                             |

| S-parameters from the initial simulations, revised simulations, and measurements for the outer-most bondwire of the bondwire characterization structure. (a) $S_{11}$ , (b) $S_{21}$                                                                                                                                                                                                        | . 59                                                                                                                                                                                                                                             |

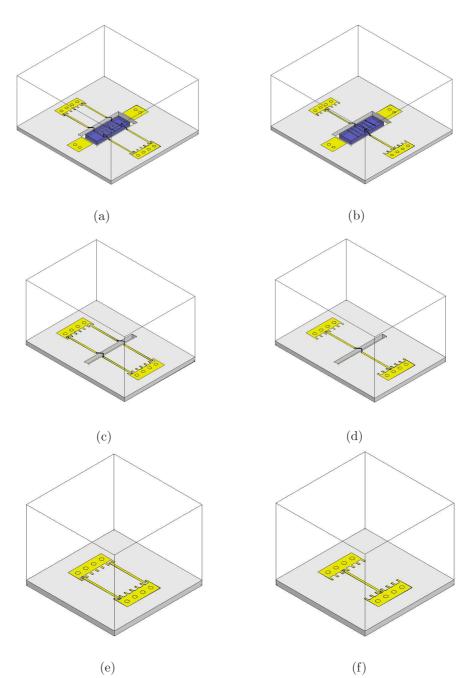

| HFSS structures for the simulation and deembedding of a 1 K $\Omega$ resistor embedded in the modified test fixture. Structure for the simulation of (a) on-chip through trace and 1 K $\Omega$ resistor, (b) on-chip empty structure, (c) outer bondwires, (d) inner bondwire, (e) outer transmission line traces, and (f) inner transmission line trace                                   |                                                                                                                                                                                                                                                  |

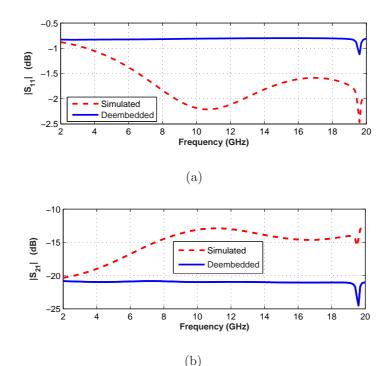

| Simulated and deembedded S-parameters for a 1 K $\Omega$ resistor embedded in the modified test fixture. (a) $S_{11}$ , (b) $S_{21}$                                                                                                                                                                                                                                                        | . 63                                                                                                                                                                                                                                             |

| Modified test fixture structures for (a) measurement of the on-chip<br>through structure and a 10 $\mu$ m x 10 $\mu$ m substrate structure, and<br>(b) measurement of the on-chip empty structure. The bondwire and<br>transmission line characterization structures on each substrate would<br>have traces and bondwires removed to match the test chip measure-<br>ment structures shown. |                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                             | (a) The deembedding procedure assumes that the transmission lines<br>and bondwires can be modeled as isolated two-port networks. (b) A<br>more realistic model accounts for coupling, and treats the traces and<br>bondwires as 12-port networks |

# LIST OF TABLES

| <u>Table</u> |                                            | Page |

|--------------|--------------------------------------------|------|

| 3.1          | Dimensions of the on-chip test structures. | . 17 |

# LIST OF APPENDIX FIGURES

| Figure Pag                                                                | e |

|---------------------------------------------------------------------------|---|

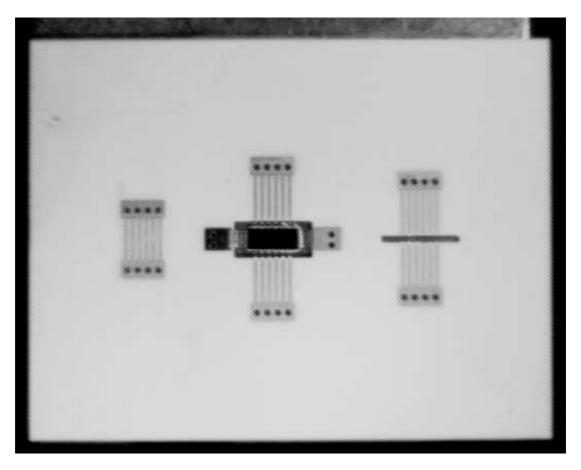

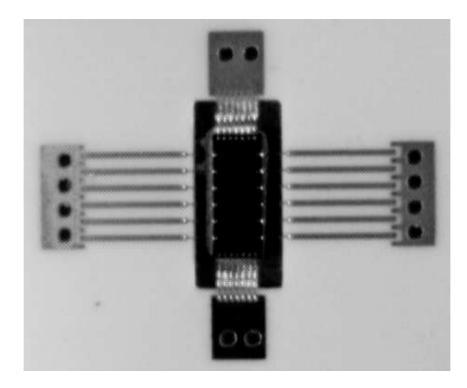

| C-1 Photomicrograph of the complete test fixture                          | 9 |

| C-2 Photomicrograph of the test chip mounted in the test fixture 8        | 0 |

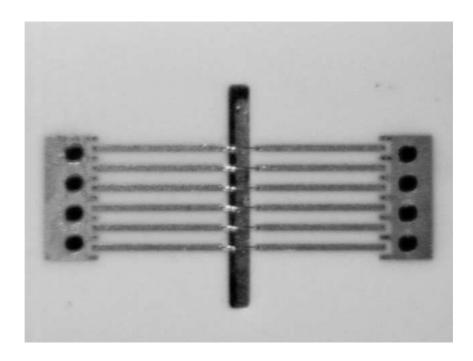

| C-3 Photomicrograph of the bondwire characterization structure 8          | 0 |

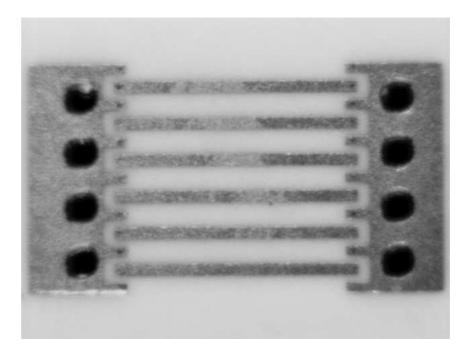

| C-4 Photomicrograph of the transmission line characterization structure 8 | 1 |

# A Test Fixture and Deembedding Procedure for High-Frequency Substrate Characterization

## 1. INTRODUCTION

### 1.1. Background and Motivation

With the exploding market for portable electronic devices, such as cell phones, PDAs, and digital music players, comes a drive toward making those products smaller, less expensive, and more power efficient. These goals can be accomplished, in part, by higher levels of integration. That is, integrating more and more functionality on single integrated circuits (ICs). Often this means the integration of sensitive analog circuitry, such as the front end of wireless transceiver, with a high-speed, noisy digital signal processing block, all on a single IC.

With sensitive analog blocks and noisy digital blocks fabricated on a common silicon substrate, noise coupling from the digital to analog circuitry becomes a concern. This coupling can occur through several interdependent paths, including the power supplies, interconnect and package parasitics, and through the silicon substrate itself [1], [2].

The Silencer! tool developed at Oregon State University enables mixedsignal circuit designers to predict, through simulation, the coupling that will occur between analog and digital blocks in a circuit layout [3]. Given a circuit layout in a specified IC process, Silencer! extracts an equivalent substrate network to model the coupling between regions of the layout, which are specified by the circuit designer. The extracted equivalent substrate network consists of resistive pi-networks connecting all pairs of specified substrate contacts. This resistive substrate network is then inserted into the circuit netlist, enabling the inclusion of substrate coupling effects in circuit simulation.

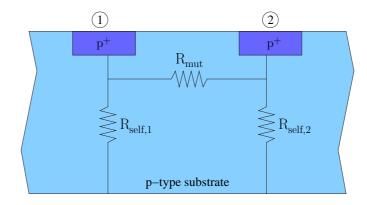

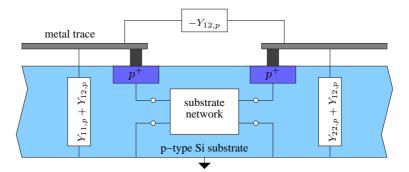

It has been shown that for lower frequencies, below roughly 1-2 GHz, the substrate can be adequately modeled as purely resistive [4]. At these frequencies, the extracted substrate network connecting two p+ substrate contacts is shown in Figure 1.1.

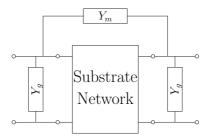

FIGURE 1.1. Low-frequency resistive substrate network model.

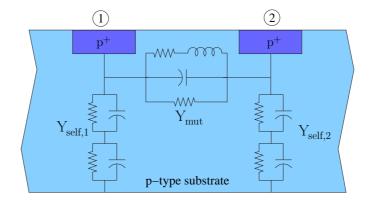

In this pi-network,  $R_{mut}$  represents the mutual resistance between the two substrate contacts, while  $R_{self,1}$  and  $R_{self,2}$  represent the self resistances of each contact to the back side of the die. While the resistive network is adequate at lower frequencies, at higher frequencies, in excess of 2 GHz, it becomes necessary to account for the dielectric nature of the substrate. At these higher frequencies, a more accurate equivalent substrate network would include both resistive and reactive components [5], [6], as shown in Figure 1.2 [7].

Similar to the low frequency model, the high frequency model is a pinetwork, with self and mutual resistances being replaced by self and mutual admittances. For both models a common node at the backside of the substrate is assumed. This is a valid assumption for heavily-doped logic processes, fabricated

FIGURE 1.2. High-frequency substrate network model.

on very low resistivity substrates, and for any die which is conductively bonded to a package ground plane.

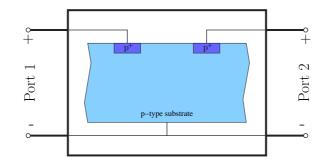

The extraction of a substrate network from an IC layout is accomplished by the use of models developed for the given IC process. These models are formulae, which compute the network component values based on the geometries of the substrate contacts in question. When developing and refining these models, it is essential to have the means to validate them through physical measurements. At lower frequencies the resistive models can be validated through DC resistance measurements made on test structures laid out in a die. These test structures consist of pairs of  $p^+$  substrate contacts of various dimensions and spacings. DC resistance measurements can then be made whereby the values of  $R_{self}$  and  $R_{mut}$ can be determined. Figure 1.3 shows that the pairs of substrate contacts can be thought of as two-port networks, which can be characterized by any set of network parameters, such as open-circuit impedance parameters (Z-parameters) or short-circuit admittance parameters (Y-parameters).

The two-port network itself comprises the silicon substrate surrounding the two p+ contacts. The backside serves as a common reference node for both

FIGURE 1.3. The substrate as a two-port network.

ports. The potential at port 1 is defined as the potential between contact 1 and the equi-potential backside of the substrate, and the potential at port 2 is defined similarly. Z- or Y-parameters for the resistive two-port substrate network can be extracted by DC measurements. At frequencies exceeding 2 GHz, where the two-port network begins to look reactive, DC measurements no longer suffice, and it becomes necessary to characterize the two-port substrate network as a function of frequency. At the higher frequencies, which are of interest here, the two-port network is best characterized with S-parameters measured with a network analyzer.

Conceivably, the process of characterizing the low-frequency, resistive twoport substrate network with DC measurements, could be extended to network analyzer measurements which characterize the two-port substrate network over a range of higher frequencies. The ability to accurately take such measurements would represent a valuable step in the development of substrate models, which will enable accurate simulation of high-frequency substrate coupling effects in integrated circuits.

#### 1.2. Thesis Outline

This thesis details the design of test structures, a test fixture, and a measurement methodology for the characterization of the two-port substrate network, connecting pairs of  $p^+$  substrate contacts, at frequencies up to 20 GHz. Chapter 2 provides an overview of prior works and efforts to make high-frequency substrate coupling measurements. Chapter 3 describes the design of the test fixture used to make the high frequency network parameter measurements of the substrate network, as well as the design of the test chip, on which the test structures are fabricated. Also discussed in Chapter 3 is the network theory and measurement methodology that enables the extraction of data from network parameter measurements, which may be dominated by test fixture parasitics. This data extraction process is known as deembedding. A four-step deembedding procedure developed for the substrate network measurements taken with this test fixture is detailed in Chapter 4. The test fixture design, including the on-chip test structures, along with the deembedding procedure were validated through extensive simulations. These simulations are the topic of Chapter 5. Measurement results are presented in Chapter 6, and finally, conclusions and suggestions for future work are offered in Chapter 7.

### 2. AN OVERVIEW OF PRIOR WORK

Previous works have attempted to characterize the two-port substrate network between pairs of substrate contacts with varying degrees of success. These can be separated into two categories: those which directly measure the network parameters of the substrate [5], [8], and those which characterize the substrate indirectly, by sensing and amplifying coupled signals [9], [10].

A direct measurement method, if feasible, is preferred, because it eliminates the uncertainty and additional calibration requirements associated with the onchip circuitry used in an indirect measurement scheme. Substrate characterization through direct network analyzer measurements is the focus of this work.

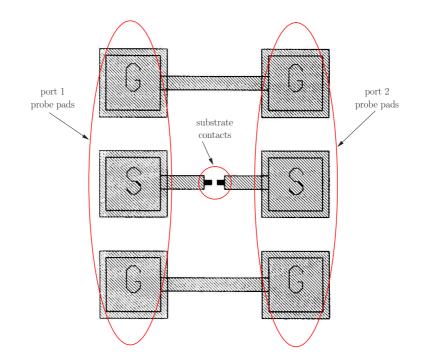

Direct measurements, such as [5] and [8], as well as previous measurement attempts made at Oregon State University, have all been similar in that each was performed by probing specially designed on-chip test structures with 50 $\Omega$  RF micro-probes connected to a network analyzer. In each case probe pads were laid out on a test chip to allow for on-chip probing with the ground-signal-ground (G-S-G) micro-probes. Previous attempts at measurements of this kind at Oregon State University utilized test structures like those shown in Figure 2.1.

In the case of the test structures of Figure 2.1, as well as some of those used in [5] the probe ground leads connect only to each other through metal traces on the test chip; they make no connection to the silicon substrate. The probe ground leads are the point of connection between the measurement system ground of the network analyzer and the reference ground of the two-port network under test. As far as the measurement is concerned, the probe grounds *are* the two-port reference ground. So, in the case of the test structures of Figure 2.1, the reference node of the substrate network being measured becomes the metal ground traces on top of

FIGURE 2.1. Test structures used for previous measurements at OSU.

the chip. As explained in Chapter 1, it is desirable to have the back side of the die serve as the reference node for the two-port substrate network.

In other similar works, such as [8] the probe ground pads connect to the substrate with  $p^+$  substrate contacts. In that case the ports of the substrate network are defined between the  $p^+$  substrate contacts being excited and those connected to the probe ground leads.

Measurements of the test structures of Figure 2.1 failed to yield meaningful data, because they were dominated by interactions with the probe station chuck on which the die being tested was situated. This effect was also alluded to in [5]. In that work, however, the problem was eliminated by separating the die from the chuck with a sufficiently thick piece of glass. It was found that the effects of interaction with the probe station chuck could not be eliminated from the measurements on the test structures of Figure 2.1, regardless of the spacing from

the chuck. It is believed that interactions with the chuck are exacerbated by the fact that the backside of the die is not grounded and that the substrate is not directly connected to the probe and measurement system ground.

The circuit models presented in [7], and used by Silencer! [3] for substrate coupling simulation, assume that the reference node for the two-port substrate network is the backside of the die. For accurate high-frequency measurements, as well as measurements which will correlate to the models used in simulation, it is therefore essential to make a good low-impedance connection between the probe grounds and the backside of the die. To the author's best knowledge, this is something that has not been done in previous work.

#### 3. TEST FIXTURE DESIGN

#### 3.1. Off-Chip Probing

Because the backside of the die is the reference node of the two-port substrate network, it is essential to make a low-impedance connection between the probe grounds and the grounded backside of the die. Actually, it is essential to make either a low-impedance connection, or a connection whose impedance can be accurately characterized.

The use of on-chip probing means that the probe grounds are by necessity on the top surface of the substrate. It would therefore be desirable to connect the probe ground pads on the topside of the die to the metallized backside with the use of vias directly through the entire substrate. Unfortunately, this is not an option in a standard IC process.

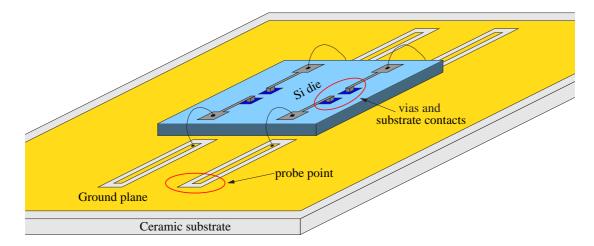

Another possible method, and the one pursued here, for making the connection between the probe and two-port grounds, is to move the probe points off-chip. By conductively bonding the test chip to a ground plane on some sort of substrate (e.g. PCB or ceramic), the probe grounds can be made to connect directly to the same ground plane, to which the backside of the die is attached. This scheme is illustrated in Figure 3.1.

This conceptual drawing shows the test chip, with test structures similar to those in Figure 2.1, attached to a ground plane on a ceramic substrate. The test structures are still probed with the same 50  $\Omega$  G-S-G micro-probes, but now the probe points have been moved off-chip. This allows an intimate connection, via the ground plane, between the ground of the two-port substrate network and the ground of the measurement system. The probes would connect to the on-chip

FIGURE 3.1. Preliminary test fixture concept.

test structures through off-chip transmission lines, bondwires, and on-chip metal traces.

While the problem of making a low-impedance ground connection is solved by the setup of Figure 3.1, another problem is introduced. By moving the probe points off-chip, and further away from the actual on-chip test structures, which are the subject of the measurements, significant test fixture parasitics are introduced into the circuit being measured. These parasitics can, in fact, dominate the measurements, obscuring the desired network parameters of the substrate network. A procedure is needed which allows for the characterization of test fixture parasitics and the removal of their effects from the measurements. This procedure is known as deembedding. Because the process of deembedding, and the ability to do so accurately, played a central role in the design of the test fixture, the theory behind deembedding will be discussed briefly in the following section, prior to further discussion of the test fixture itself.

### 3.2. Deembedding Theory

Deembedding is the process of characterizing the parasitics of the test fixture in terms of series impedances, shunt admittances, or a set of any convenient two-port network parameters, then using these parameters to remove the test fixture effects from the measurements. This process allows the obscured network parameters of the device-under-test, in this case the substrate network, to be extracted from the measured data. When developing a deembedding procedure, it is first necessary to develop an equivalent circuit model for the test fixture. This is done by decomposing the test fixture into smaller sections, which appear in series or shunt with the substrate network, and which, through either direct or indirect measurements, can be isolated and characterized.

Sections of the test fixture and the parameters that characterize them, fall into three categories: series impedances, shunt admittances, and more complex sections characterized by general network parameters, appearing in series with the substrate network.

#### 3.2.1. Series Impedances

Parts of the test fixture may present impedances, which appear in series with the network being measured. Simple examples of this may be contact resistance of the probe, the impedance of a metal trace leading to the network being measured, or the series impedance presented by a bondwire. Figure 3.2 illustrates how these impedances appear in the test setup. Note that this network, like all other networks considered here, is assumed to be symmetric.

The measured network parameters of the entire two-port network of Figure 3.2 can be expressed in terms of impedance parameters as

FIGURE 3.2. Parasitic impedance in series with the network being measured.

$$\mathbf{Z}_{m} = \begin{bmatrix} Z_{11,m} & Z_{12,m} \\ Z_{21,m} & Z_{22,m} \end{bmatrix}$$

(3.1)

The measured impedance parameters,  $\mathbf{Z}_m$ , can equivalently be expressed in terms of the series impedance, Z, and the impedance parameters of the substrate network,  $\mathbf{Z}_{sub}$ .

$$\mathbf{Z}_{m} = \begin{bmatrix} Z_{11,sub} + Z & Z_{12,sub} \\ Z_{21,sub} & Z_{22,sub} + Z \end{bmatrix}$$

(3.2)

From (3.2) it is clear that extracting the Z-parameters for the substrate network is simply a matter of determining the value of the series impedance, Z, and subtracting that from  $Z_{11,m}$  and  $Z_{22,m}$ . Or, equivalently,

$$\mathbf{Z}_{sub} = \mathbf{Z}_m - \begin{bmatrix} Z & 0\\ 0 & Z \end{bmatrix}$$

(3.3)

If portions of the test fixture can be modeled as lumped series impedances, and those impedances can be measured, then their effects can be removed from the measured network parameters using Eq. (3.3).

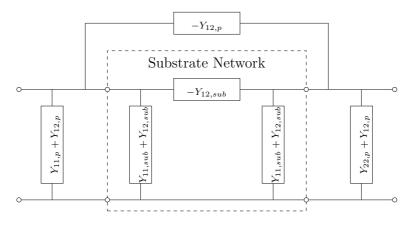

### 3.2.2. Shunt Admittances

The second category of test fixture parasitics, whose effects can be removed from the measured data, consists of shunt admittances. These are admittances that appear in parallel with the substrate network, either shunting its ports to ground or one port to the other. Figure 3.3 illustrates a physical example of the origin of such admittances. Metal traces, with vias down to the  $p^+$  substrate

FIGURE 3.3. An example of parasitic shunt admittances associated with the test fixture.

contacts, have parasitic admittances to ground and across the gap between the substrate contacts. The measured admittance parameters, resulting from both the substrate network and the parasitic admittances, are

$$\mathbf{Y}_{m} = \begin{bmatrix} Y_{11,m} & Y_{12,m} \\ Y_{21,m} & Y_{22,m} \end{bmatrix}$$

(3.4)

The substrate network can similarly be characterized in terms of its Ymatrix,  $\mathbf{Y}_{sub}$ . A symmetric two-port network can be represented as a pi-network, described by its Y-parameters, so the parallel combination of the substrate network and the shunt admittances of the test fixture can be drawn as the network of Figure 3.4. Figure 3.4 shows that the measured admittance parameters can be expressed in terms of the admittance parameters of the substrate network,  $\mathbf{Y}_{sub}$ , and the admittance parameters which characterize the shunt admittances of the test fixture,  $\mathbf{Y}_p$ .

FIGURE 3.4. Pi-network representation of the substrate network and the parasitic test fixture admittances which shunt it.

$$\mathbf{Y}_{m} = \begin{bmatrix} Y_{11,sub} & Y_{12,sub} \\ Y_{21,sub} & Y_{22,sub} \end{bmatrix} + \begin{bmatrix} Y_{11,p} & Y_{12,p} \\ Y_{21,p} & Y_{22,p} \end{bmatrix} = \begin{bmatrix} Y_{11,sub} + Y_{11,p} & Y_{12,sub} + Y_{12,p} \\ Y_{21,sub} + Y_{21,p} & Y_{22,sub} + Y_{22,p} \end{bmatrix}$$

(3.5)

If the Y-parameters of the parasitic shunt admittances are known, then, according to (3.5), the Y-parameters for the substrate network can be extracted from the measurements by a simple Y-matrix subtraction.

$$\mathbf{Y}_{sub} = \mathbf{Y}_m - \mathbf{Y}_p \tag{3.6}$$

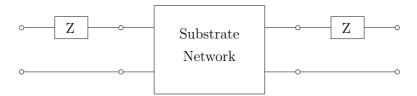

### 3.2.3. Series Two-Port Test Fixture Sections

The third, and most general, category of test fixture parasitics are those which appear in series with the substrate network-under-test, and which are best characterized by any type of two-port network parameters. Typical examples of test fixture sections which would fall into this category are sections of trace, either on-chip or off, which lead from the probes toward the test structure, and are not adequately characterized by lumped impedances or admittances. These sections may be treated as two-port networks and characterized by their chain parameters. This scenario is illustrated in Figure 3.5.

FIGURE 3.5. Chain parameter representation of test fixture parasitics appearing in series with the substrate network.

The chain parameters of a cascade of series-connected two-port networks are given by the product of the chain parameters of the individual two-ports. So the chain parameters of the network of of Figure 3.5 would be

$$\mathbf{T}_{m} = \mathbf{T}_{p} \cdot \mathbf{T}_{sub} \cdot \mathbf{T}_{p} \tag{3.7}$$

$$\mathbf{T}_{m} = \begin{bmatrix} A_{p} & B_{p} \\ C_{p} & D_{p} \end{bmatrix} \begin{bmatrix} A_{sub} & B_{sub} \\ C_{sub} & D_{sub} \end{bmatrix} \begin{bmatrix} A_{p} & B_{p} \\ C_{p} & D_{p} \end{bmatrix}$$

(3.8)

If the chain parameters describing the series section of test fixture parasitics,  $\mathbf{T}_p$ , are known, then their effects on the measurement may be eliminated by simply right and left multiplying the measured chain parameters by the matrix inverse of the chain parameters for the parasitics,  $\mathbf{T}_p^{-1}$ .

$$\mathbf{T}_{sub} = \mathbf{T}_p^{-1} \cdot \mathbf{T}_m \cdot \mathbf{T}_p^{-1} \tag{3.9}$$

#### 3.3. Test Fixture Assembly

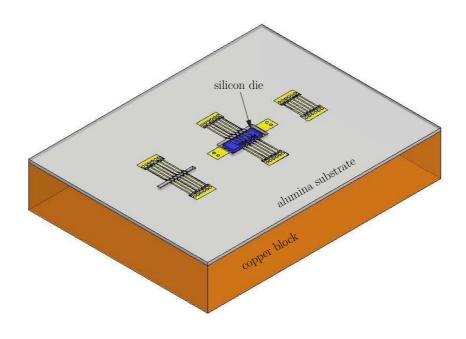

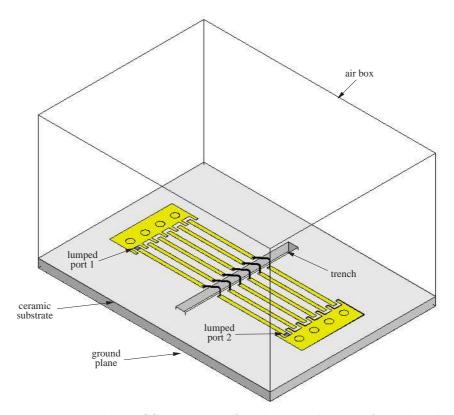

A test fixture was designed to enable high-frequency network parameter measurements of two-port substrate network test structures fabricated on a test chip. The test fixture shown in Figure 3.6 comprises three main components: the silicon die, on which the test structures are fabricated, a thin ceramic substrate, with thin film traces on one side and a ground plane on the other, and a solid copper block.

FIGURE 3.6. Test fixture assembly.

#### 3.3.1. The Test Chip and On-Chip Test Structures

A test chip was designed and fabricated through MOSIS using a 0.35  $\mu$ m TSMC process. The chip is roughly 2 mm x 5 mm and contains four sub-dice, which were singulated after receiving the larger die from MOSIS. Each of the smaller sub-dice is roughly 1 mm x 2 mm, and contains four substrate test structures and two structures to be used for deembedding. Four sub-dice, each with four distinct test structures, yield a total of 16 unique test structures. Each test structure consists of a pair of  $p^+$  substrate contacts. The size of the substrate

| Test Structure | Contact Size                 | Spacing          |

|----------------|------------------------------|------------------|

| 1              | $10 \ \mu m \ge 10 \ \mu m$  | $20~\mu{\rm m}$  |

| 2              | $60 \ \mu m \ge 60 \ \mu m$  | $20~\mu{\rm m}$  |

| 3              | $10 \ \mu m \ge 60 \ \mu m$  | $20~\mu{ m m}$   |

| 4              | $50 \ \mu m \ge 100 \ \mu m$ | $20~\mu{ m m}$   |

| 5              | $10 \ \mu m \ge 10 \ \mu m$  | $50~\mu{ m m}$   |

| 6              | $60 \ \mu m \ge 60 \ \mu m$  | $50~\mu{ m m}$   |

| 7              | $10 \ \mu m \ge 60 \ \mu m$  | $50~\mu{ m m}$   |

| 8              | $50 \ \mu m \ge 100 \ \mu m$ | $50~\mu{ m m}$   |

| 9              | $10 \ \mu m \ge 10 \ \mu m$  | $100~\mu{\rm m}$ |

| 10             | $60 \ \mu m \ge 60 \ \mu m$  | 100 $\mu m$      |

| 11             | $10 \ \mu m \ge 60 \ \mu m$  | $100 \ \mu m$    |

| 12             | $50 \ \mu m \ge 100 \ \mu m$ | $100 \ \mu m$    |

| 13             | $10 \ \mu m \ge 10 \ \mu m$  | $200~\mu{\rm m}$ |

| 14             | $60 \ \mu m \ge 60 \ \mu m$  | $200~\mu{\rm m}$ |

| 15             | $10 \ \mu m \ge 60 \ \mu m$  | $200~\mu{\rm m}$ |

| 16             | $50 \ \mu m \ge 100 \ \mu m$ | $200~\mu{\rm m}$ |

TABLE 3.1. Dimensions of the on-chip test structures.

contacts, and the distance that separates them, is varied from one contact to the next. Each sub-die has four different-sized contacts, all at a single spacing. Table 3.1 lists the dimensions of all 16 test structures.

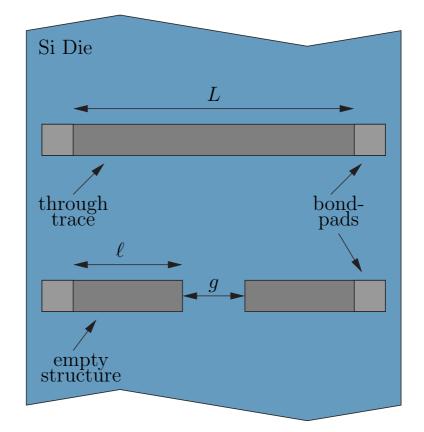

Top metal traces (metal-4), 60  $\mu$ m wide, run straight in from the bond pads at each edge of the die to the substrate contacts, where they make contact to the  $p^+$  diffusions with vias. A photograph of one of the sub-dice is shown in Figure 3.7.

| 10 μm x 10 μm                |

|------------------------------|

| $60 \ \mu m \ge 60 \ \mu m$  |

|                              |

| substrate<br>contacts        |

| $10 \ \mu m \ge 60 \ \mu m$  |

|                              |

| bond<br>pads<br>empty        |

| $50 \ \mu m \ge 100 \ \mu m$ |

| ······                       |

| through                      |

| and the second second        |

|                              |

FIGURE 3.7. Die photo of the test chip, showing four test structures and two deembedding structures.

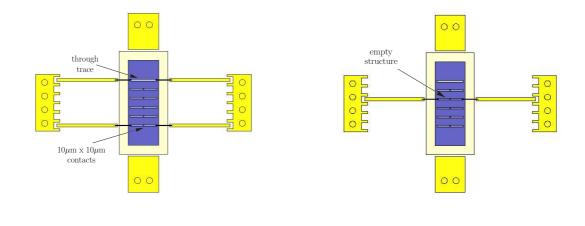

Note that along with the four test structures the layout includes an empty structure, which contains identical metal traces to the other structures, but no substrate contacts, and a through structure, which is simply a 60  $\mu$ m-wide metal-4

trace running straight across the die. These two structures are used for deembedding, and their function is described in Sections 4.4 and 4.5.

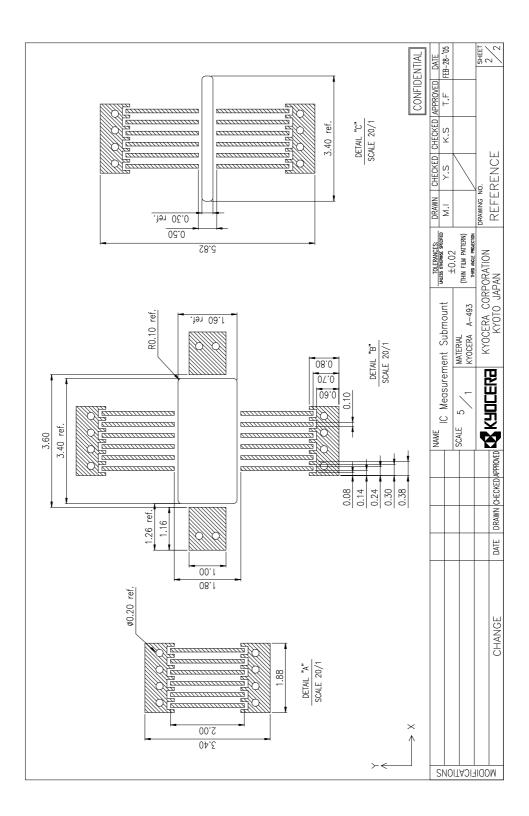

### 3.3.2. The Ceramic Substrate

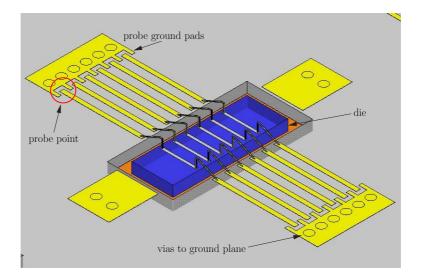

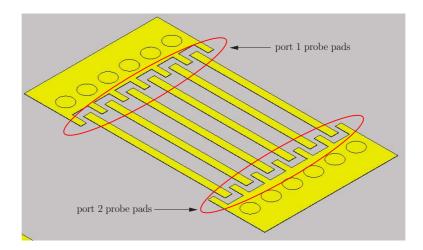

The ceramic substrate is 0.010" (254  $\mu$ m) thick, and is made of alumina (Al<sub>2</sub>O<sub>3</sub>). A solid metal ground plane covers the bottom side of the substrate. A thin-film circuit consisting of probe pads and transmission lines is fabricated on the top side. The probe ground pads on the top side connect to the back side ground plane through vias.

The alumina substrate contains a cutout, which is sized to be slightly larger than the die. The substrate is soldered onto the copper block, which then becomes the ground plane for the substrate. Attaching the substrate to the copper block transforms the cutout to a cavity, the bottom of which is the exposed ground plane of the copper block. The die is conductively bonded to the copper block inside the cavity. The die and the ceramic substrate are roughly the same thickness, so the surface of the die lies flush with the surface of the ceramic. A closer view of the die, mounted in the cavity, is provided by Figure 3.8.

The test structures on the die connect, via metal-4 traces, to bond pads on the edge of the die (see Figure 3.7). These bond pads are wire-bonded to transmission lines on the top side of the ceramic. The transmission lines lead away from the die to the probe pads. There, they become the signal pads for the G-S-G probes, and are interdigitated with the probe ground pads. The probe ground pads connect directly to the backside ground plane through nearby vias.

The transmission lines, which are probed with the 50  $\Omega$  G-S-G microprobes, are 100  $\mu$ m wide. The dimensions of the traces were dictated by the

FIGURE 3.8. Close-up view of the die mounted in the cavity.

dimensions of the probes, whose leads are on a 150  $\mu$ m pitch, and by metal-tometal spacing requirements. Given these constraints, 100 $\mu$ m-wide traces, were the widest allowable. This width provides a characteristic impedance of approximately 70  $\Omega$ , presenting a mismatch to the the 50  $\Omega$  probes. This is not a concern, because the characteristics of the traces will be calibrated out as part of the deembedding process.

Along with the cavity and the traces for mounting and making connections to the die, the ceramic substrate contains two sets of deembedding structures, which are used for test fixture characterization. The first, shown in Figure 3.9, is a set of transmission lines identical to those which connect to each side of the die. Unlike the transmission lines connecting to the die, these lines have probe pads on both ends. This allows them to be probed and characterized with two-port network analyzer measurements. Once characterized, their network parameters can be used in the deembedding process.

FIGURE 3.9. Transmission line characterization structures.

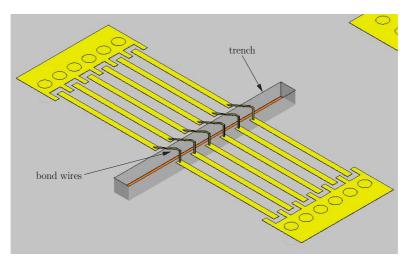

The second set of deembedding structures, shown in Figure 3.10, comprises two sets of probe pads and transmission lines, identical to those which connect to the die. The two sets of transmission lines are separated by a trench. The trench,

FIGURE 3.10. Bondwire characterization structures.

like the cavity in which the die is mounted, is formed by a cutout in the ceramic substrate. The trench is sized so that its narrow dimension is the same as the gap which surrounds the die in the cavity. Transmission lines on opposite sides of the trench connect via bondwires, which span the trench. These bondwires are intended to be identical to those which connect the transmission lines to the bond pads on the die. These structures enable the characterization of the bondwires by allowing them to be probed and measured with the network analyzer. The network parameters of the bondwires measured here can then be used later in the deembedding process.

Both the transmission line and bondwire characterization structures comprise six sets of adjacent traces, similar to those which connect to the chip. The proximity of neighboring traces and bondwires will result in different traces and bondwires having different two-port parameters depending on their location in the group. The traces and bondwires on the outside of the group will be characterized by different two-port parameters than those which characterize the traces and bondwires located one in from the outside, whose two-port parameters will in turn differ from those characterizing the inner-most traces or bondwires. Due to the symmetry of the six-trace-wide structures, they can be completely characterized with three sets of two-port parameters. These structures will allow bondwires and transmission lines to be characterized more accurately than would be possible if the bondwire and transmission line characterization structures consisted only of single traces and bondwires.

The bondwire characterization structures of Figure 3.10 make clear the motivation for mounting the die in a cavity, such that its surface is flush with the surface of the ceramic. Were the die to be mounted on top of a ground plane on the topside of the substrate, as shown in the preliminary conceptual drawing of Figure 3.1, then it would be much more difficult to accurately replicate, for the purpose of characterization, both the length and configuration of the bondwires that make contact to the die.

## 4. A FOUR-STEP DEEMBEDDING PROCEDURE

The first step in the design of a deembedding procedure is to develop a model that adequately describes the important parasitics of the test fixture surrounding the network being measured. The model may consist of lumped impedances and admittances, along with two-port blocks, characterized by twoport network parameters. Once a model has been established, the next step is to design a set of deembedding test structures, along with a measurement procedure that allows the impedance, admittance, and the two-port network parameter values, that characterize the model, to be obtained.

The simplest and most frequently used deembedding procedure for on-chip measurements is Y-parameter subtraction. The Y-parameter subtraction scheme assumes that the test fixture can be adequately modeled as admittances that shunt the network under test, as in Figures 3.3 and 3.4. The parasitic shunt admittances are measured from an empty structure, which is a test structure that does not contain the network under test. The measured Y-matrix of the empty structure is subtracted from the measured Y-matrix of a full test structure, yielding the deembedded two-port parameters for the network under test. For certain test fixtures, networks under test, and measurement frequency ranges, simple Y-parameter subtraction may provide suitable deembedding accuracy.

Recognizing the limits of the simple test fixture model associated with Y-parameter subtraction, particularly at higher frequencies, other more rigorous deembedding procedures have been developed [11–15]. These deembedding schemes are based on test fixture models that more accurately account for the most significant parasitics.

## 4.1. Test Fixture Model

Prior to taking any measurements the network analyzer will be calibrated to the probe tips in a separate calibration procedure. All parts of the test fixture between the 50  $\Omega$  probe tips and the substrate contacts become part of the measurement, and therefore must be accounted for in the equivalent circuit model for the test fixture.

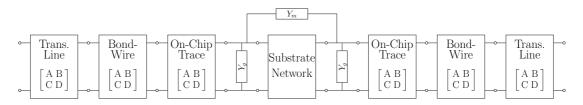

The test fixture between the probe tips and the substrate contacts consists of three main components: the micro-strip transmission lines on the ceramic substrate, the bondwires connecting those lines to the on-chip traces, and the on-chip traces themselves. An equivalent test fixture circuit model, which accounts for these components is given in Figure 4.1.

FIGURE 4.1. Test fixture model used for deembedding.

Three of the blocks, the micro-strip transmission lines, the bondwires, and the on-chip sections of trace, are treated as series-connected two-port networks, and are characterized using their chain parameters. The final section of the test fixture model comprises the admittances that shunt the substrate network to ground,  $Y_g$ , and from port to port,  $Y_m$ . This block is characterized using its admittance matrix. In the center of the model is the substrate network which will ultimately be described with any desired set of two-port network parameters. The network parameters of the substrate will be extracted from the measured data as the effects of the other blocks are stripped away in four steps.

## 4.2. Step One: Micro-Strip Transmission Lines

The outer-most block in the model comprises the micro-strip transmission lines, which lead from the probe pads to the bondwires. The transmission line block is characterized by its chain parameters. Network analyzer measurements taken on the micro-strip transmission lines of Figure 3.9 yield S-parameters for the lines, which can be converted into the corresponding chain parameters. Once the chain parameters are known, it is a simple matter to remove the effects of the transmission lines from the measured data, as described in Section 3.2.3. Simply left- and right-multiply the measured chain parameter matrix,  $\mathbf{T}_m$ , by the inverse chain parameter matrix of the micro-strip lines,  $\mathbf{T}_{tl}^{-1}$ .

$$\mathbf{T}_1 = \mathbf{T}_{tl}^{-1} \cdot \mathbf{T}_m \cdot \mathbf{T}_{tl}^{-1} \tag{4.1}$$

The result,  $\mathbf{T}_1$ , is the chain parameter matrix for the substrate coupling measurement following the first deembedding step. The subscript denotes the number of deembedding steps the data has undergone, incrementally increasing with each successive step, as more and more of the test fixture effects are peeled away. Figure 4.2 shows a model of the physical network corresponding to the measured data after the first deembedding step.

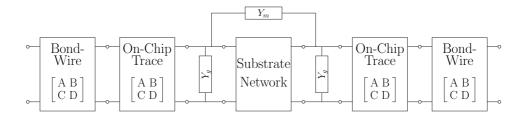

FIGURE 4.2. Model of the network corresponding to the data after step one of the deembedding procedure.

## 4.3. Step Two: Bondwires

The next block of test fixture parasitics to be removed, according to Figure 4.2, is that of the bondwires. Bondwires tend to look primarily inductive, and in many applications they are adequately modeled as lumped inductances. Simulations, however, demonstrated that in this case treating the bondwires as simple lumped inductances introduces unacceptable errors into the deembedding process. If they are to be modeled with simple lumped elements, a CLC pi-network is more appropriate. Equivalently, the bondwires can be characterized in terms of general two-port parameters.

Network analyzer measurements taken on the structures of Figure 3.10 yield a set of S-parameters. These S-parameters describe a network including not only the bondwire, but also the series sections of the transmission line connected to each port of the bondwire. Written in terms of chain parameters, the measured network parameters of the bondwire characterization structure can be expressed as

$$\mathbf{T}_{bw,m} = \mathbf{T}_{tl} \cdot \mathbf{T}_{bw} \cdot \mathbf{T}_{tl} \tag{4.2}$$

Clearly, the chain parameters for the bondwires can be extracted by applying the first deembedding step to the measured data.

$$\mathbf{T}_{bw} = \mathbf{T}_{tl}^{-1} \cdot \mathbf{T}_{bw,m} \cdot \mathbf{T}_{tl}^{-1} \tag{4.3}$$

Now that the bondwire chain parameters have been deembedded, the second deembedding step is completed by left- and right-multiplying the data from step one,  $\mathbf{T}_1$ , by the inverse of the bondwire chain parameter matrix,  $\mathbf{T}_{bw}^{-1}$ .

$$\mathbf{T}_2 = \mathbf{T}_{bw}^{-1} \cdot \mathbf{T}_1 \cdot \mathbf{T}_{bw}^{-1} \tag{4.4}$$

The data that results from this second deembedding step,  $\mathbf{T}_2$ , corresponds to the physical network modeled by Figure 4.3.

FIGURE 4.3. Model of the network corresponding to the data after step two of the deembedding procedure.

## 4.4. Step Three: On-Chip Traces

The third deembedding step involves removal of the effects due to the onchip traces. Again, the first step in this process will be taking measurements of deembedding structures, that will allow the network parameters for these traces to be obtained. Along with the four substrate coupling test structures on each chip, are two structures dedicated solely for the purpose of deembedding. One of these, as shown in figure 3.7, is a through trace, spanning the width of the die. Network analyzer measurements of the through structure yield S-parameters, which are then converted to chain parameters. These chain parameters correspond to a network consisting of not only the on-chip through trace, but also the bondwires and micro-strip transmission lines. These chain parameters can be expressed as

$$\mathbf{T}_{thru,m} = \mathbf{T}_{tl} \cdot \mathbf{T}_{bw} \cdot \mathbf{T}_{thru} \cdot \mathbf{T}_{bw} \cdot \mathbf{T}_{tl}$$

$$(4.5)$$

The chain matrix for the on-chip through trace alone can be retrieved from the measured chain parameters,  $\mathbf{T}_{thru,m}$ , by passing the data through deembedding steps one and two. First, the effects of the micro-strip lines are removed.

$$\mathbf{T}_{thru,1} = \mathbf{T}_{tl}^{-1} \cdot \mathbf{T}_{thru,m} \cdot \mathbf{T}_{tl}^{-1}$$

(4.6)

Then, the bondwire effects are stripped away, yielding the chain parameters for the through trace.

$$\mathbf{T}_{thru} = \mathbf{T}_{bw}^{-1} \cdot \mathbf{T}_{thru,1} \cdot \mathbf{T}_{bw}^{-1} \tag{4.7}$$

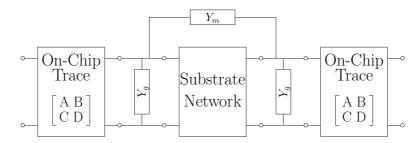

This chain matrix,  $\mathbf{T}_{thru}$ , applies to the entire length of the through trace that spans the die. What is needed to proceed with the deembedding process, however, is the chain parameter matrix for only the short sections of trace leading up to the substrate contacts. Figure 4.4 shows the dimensions of both the through trace and the shorter segments of the trace leading to the substrate contacts.

FIGURE 4.4. Dimensions of the through trace and trace segments.

The deembedded chain matrix,  $\mathbf{T}_{thru}$ , represents a trace of length L. A procedure is therefore needed to convert  $\mathbf{T}_{thru}$  into a set of chain parameters describing a trace of length  $\ell$ . This will be accomplished through a procedure that will be referred to as chain parameter factorization.

## 4.4.1. Chain Parameter Factorization

Given a trace of length L with chain matrix,  $\mathbf{T}_L$ , there exists a chain matrix,  $\mathbf{T}_{\frac{L}{2}}$ , such that

$$\mathbf{T}_L = \mathbf{T}_{\frac{L}{2}} \cdot \mathbf{T}_{\frac{L}{2}} \tag{4.8}$$

where  $\mathbf{T}_{\frac{L}{2}}$  is the chain matrix for a trace of length  $\frac{L}{2}$ . This chain matrix can in turn be factored into the product of two identical chain matrices representing traces of length  $\frac{L}{4}$ .

$$\mathbf{T}_{L} = \mathbf{T}_{\frac{L}{4}} \cdot \mathbf{T}_{\frac{L}{4}} \cdot \mathbf{T}_{\frac{L}{4}} \cdot \mathbf{T}_{\frac{L}{4}}$$

(4.9)

This factorization procedure could be carried out n times, resulting in the chain matrix for a trace of length  $\frac{L}{2^n}$ .

The length of the through trace in Figure 4.4 is L, the length of the shorter trace segments are  $\ell$ , and the length of the gap between the trace segments is g. The ratio of the length of the gap, g, to the length of a shorter segment,  $\ell$ , may then be expressed as

$$\frac{g}{\ell} = \frac{g}{\frac{L-g}{2}} = \frac{m}{k} \tag{4.10}$$

where m and k are the smallest integers satisfying the equation. The required number of successive factorizations of the chain parameters of the trace of length, L, is then given by

$$n = \log_2(m + 2k) \tag{4.11}$$

Following the *n* successive factorizations, the resulting chain parameters,  $\mathbf{T}_{\frac{L}{2^n}}$ , represent a trace of length  $\frac{L}{2^n}$ , or, equivalently, length  $\frac{\ell}{k}$ . They can then be used to obtain the chain matrix of the shorter segment of trace of length  $\ell$ .

$$\mathbf{T}_{\ell} = \mathbf{T}_{\frac{L}{2^n}}^k \tag{4.12}$$

The procedure just described is useful only if a method is available that allows the chain parameters for a given length of trace to be factored into chain parameters for a trace of half that length. The method used for this factorization makes use of the fact that the on-chip trace is a network that is both symmetric and reciprocal. Symmetry of the on-chip trace implies that

$$A_{thru} = D_{thru} \tag{4.13}$$

and the reciprocal nature of the network implies that

$$|\mathbf{T}_{thru}| = A_{thru} \cdot D_{thru} - B_{thru} \cdot C_{thru} = 1$$

(4.14)

which says that the determinant of the chain matrix is unity [16]. Using these properties, it is possible to express the chain parameters for the full through trace, of length L, in terms of the chain parameters of halved sections of trace, of length  $\frac{L}{2}$ .

$$\mathbf{T}_{thru} = \begin{bmatrix} A_{\frac{L}{2}} & B_{\frac{L}{2}} \\ C_{\frac{L}{2}} & D_{\frac{L}{2}} \end{bmatrix} \cdot \begin{bmatrix} A_{\frac{L}{2}} & B_{\frac{L}{2}} \\ C_{\frac{L}{2}} & D_{\frac{L}{2}} \end{bmatrix}$$

(4.15)

$$\mathbf{T}_{thru} = \begin{bmatrix} 2A_{\frac{L}{2}}^2 - 1 & 2A_{\frac{L}{2}}B_{\frac{L}{2}} \\ 2C_{\frac{L}{2}}D_{\frac{L}{2}} & 2D_{\frac{L}{2}}^2 - 1 \end{bmatrix}$$

(4.16)

What's shown in (4.16) is a set of four equations, which can be solved for the chain parameters of the halved trace sections as follows:

$$A_{\frac{L}{2}} = \sqrt{\frac{A_{thru} + 1}{2}} = D_{\frac{L}{2}}$$

(4.17)

$$D_{\frac{L}{2}} = \sqrt{\frac{D_{thru} + 1}{2}} = A_{\frac{L}{2}}$$

(4.18)

$$B_{\frac{L}{2}} = \frac{B_{thru}}{2A_{\frac{L}{2}}} \tag{4.19}$$

$$C_{\frac{L}{2}} = \frac{C_{thru}}{2D_{\frac{L}{2}}}$$

(4.20)

This factorization process is carried out n times, where n is given by (4.11), resulting in the chain parameters for a trace of length  $\frac{L}{2^n}$ ,  $\mathbf{T}_{\frac{L}{2^n}}$ . The chain parameters for the length- $\ell$  section of trace,  $\mathbf{T}_t$ , are then given by a cascade of  $k \mathbf{T}_{\frac{L}{2^n}}$ matrices, as described by (4.12).

$$\mathbf{T}_t = \mathbf{T}_{\frac{L}{2^n}}^k \tag{4.21}$$

The third deembedding step, the removal of the effects of the on-chip trace segments, can now be completed. Simply left- and right-multiply the chain parameters of (4.4),  $\mathbf{T}_2$ , which describe the network of Figure 4.3, by the inverse of the chain matrix of the on-chip trace segments,  $\mathbf{T}_t^{-1}$ .

$$\mathbf{T}_3 = \mathbf{T}_t^{-1} \cdot \mathbf{T}_2 \cdot \mathbf{T}_t^{-1} \tag{4.22}$$

Figure 4.5 shows the physical network, which corresponds to the data resulting from this third deembedding step.

# 4.5. Step Four: Shunt Admittances

As evident from Figure 4.5, the final parasitic test fixture elements remaining are the admittances shunting the substrate network. The value of these admittances can be obtained through a measurement of the empty structure. Shown in the chip layout of Figure 3.7, the empty structure is identical to the full

FIGURE 4.5. Model of the network corresponding to the data after step three of the deembedding procedure.

test structures, except that it contains no  $p^+$  substrate contacts. The length, g, of the gap between the traces of the empty structure (Figure 4.4) is identical to that of all other structures, but the traces do not via down to make contact with the substrate.

Measurements of the empty structure can be used to obtain the values of the parasitic admittances,  $Y_g$  and  $Y_m$ . Once the values of these admittances are determined, the corresponding Y-matrix can be subtracted from the Y-matrix resulting from the third deembedding step,  $\mathbf{Y}_3$ . This step, described in Section 3.2.2, is referred to as Y-parameter subtraction. It often represents the extent of the deembedding performed when taking on-chip measurements, and is the deembedding procedure used when measurements were taken on the test structures shown in Figure 2.1.

The admittance values needed to complete the deembedding are described by what will be referred to as the Y-parameters of the empty structure,  $\mathbf{Y}_e$ . The empty structure is, however, surrounded by the same parasitics that surround the full test structures. The Y-matrix of the empty structure,  $\mathbf{Y}_e$ , will therefore have to be deembedded from the measured data using deembedding steps one through three. The measured chain parameters for the empty structure,  $\mathbf{T}_{e,m}$ , can be expressed as

$$\mathbf{T}_{e,m} = \mathbf{T}_{tl} \cdot \mathbf{T}_{bw} \cdot \mathbf{T}_t \cdot \mathbf{T}_e \cdot \mathbf{T}_t \cdot \mathbf{T}_{bw} \cdot \mathbf{T}_{tl}$$

(4.23)

First, the effects of the micro-strip transmission lines are removed.

$$\mathbf{T}_{e,1} = \mathbf{T}_{tl}^{-1} \cdot \mathbf{T}_{e,m} \cdot \mathbf{T}_{tl}^{-1} \tag{4.24}$$

Then, the bondwire effects are stripped away, yielding the chain parameters for the entire on-chip portion of the empty structure.

$$\mathbf{T}_{e,2} = \mathbf{T}_{bw}^{-1} \cdot \mathbf{T}_{e,1} \cdot \mathbf{T}_{bw}^{-1} \tag{4.25}$$

In the third step, the effects of the on-chip trace segments are eliminated, yielding the chain parameters of the empty structure.

$$\mathbf{T}_e = \mathbf{T}_t^{-1} \cdot \mathbf{T}_{e,2} \cdot \mathbf{T}_t^{-1} \tag{4.26}$$

The resulting chain parameters,  $\mathbf{T}_e$ , are then converted to the Y-matrix,  $\mathbf{Y}_e$ , representing the admittances that shunt the substrate network as shown in Figure 4.5.

The fourth, and final, step of the deembedding procedure is completed by subtracting the Y-parameters of the empty structure from the Y-parameters resulting from step three.

$$\mathbf{Y}_{sub} = \mathbf{Y}_3 - \mathbf{Y}_e \tag{4.27}$$

The resulting Y-parameters,  $\mathbf{Y}_{sub}$ , correspond to the substrate network itself, with the effects of all test fixture parasitics eliminated from the data.

#### 5. SIMULATION

Extensive simulations greatly aided the design of the test fixture, the onchip test structures, and the four-step deembedding procedure. Two categories of simulations were performed, each using a different simulator. The first group of simulations included the entire test fixture, from probe tip to probe tip, and was performed using Ansoft's HFSS (High Frequency Structure Simulator), a threedimensional, electromagnetic field solver [17]. In order to ease memory requirements, the model for the silicon chip was greatly simplified in these simulations. The simplified model does not account for the behavior of the lossy silicon substrate or of the actual substrate networks themselves. The purpose of this first group of simulations was to enable the design and validation of the physical test fixture, including the on-chip interconnects, as well as the equivalent circuit model and step-by-step deembedding procedure outlined in Chapter 4.

The second category of simulations included the substrate test structures fabricated in a heavily-doped silicon substrate from a TSMC 0.35  $\mu$ m process. These simulations, which included only the on-chip substrate contacts surrounded by the heavily-doped substrate, were performed in EPIC (Extraction of Parasitics in Integrated Circuits), a Green's Function-based substrate simulator [18]. The test fixture, as well as the on-chip interconnects, were excluded from these simulations. The objective of these simulations was to obtain network parameter data for the substrate networks defined by the pairs of substrate contacts of Table 3.1.

This two-part simulation plan allowed for design and validation of both the on-chip and off-chip portions of the test fixture, without exceeding the memory available for simulation. It also provided simulated two-port substrate network parameters that can be compared to the data obtained from measurements.

## 5.1. Probe-to-Probe Test Fixture Simulations

The purpose of the first group of simulations was the design of the test fixture, including the on-chip interconnects, as well as the development of the test fixture model and the deembedding plan. The model used for these simulations includes the entire test fixture, but substitutes a greatly simplified model for the silicon substrate.

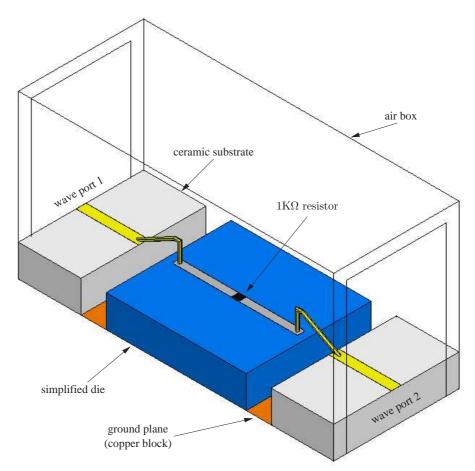

The real test chip is fabricated in a heavily-doped substrate, with a lowresistivity bulk. For the purposes of simulation the substrate can be modeled as having three discrete layers, each with a different resistivity. This substrate model will be discussed in Section 5.2, which covers the simulation of the on-chip test structures. The finite-element mesh generated by HFSS for such a substrate model becomes quite dense, resulting in prohibitively large memory requirements when included in the model of the entire test fixture. Memory requirements for this first set of simulations were eased by replacing the model for the silicon substrate with a uniform block of lossless dielectric, whose dielectric constant was arbitrarily chosen to be that of silicon dioxide. Because the substrate is modeled as a lossless dielectric, it is not possible to include, as the networks under test, the actual substrate contacts and substrate networks in these full test fixture simulations. Instead, the substrate network was replaced with a variety of other simple networks such as transmission lines, resistors, and capacitors. Figure 5.1 shows the 3-D HFSS structure used for the simulation of a test fixture containing a 1 K $\Omega$ , 60  $\mu$ m x 60  $\mu$ m resistor.

The structure shown is a cut-away section of the full test fixture. It is kept as small as possible to limit the memory and time requirements for the simulation, while still being large enough to allow the simulator to arrive at an accurate

FIGURE 5.1. HFSS structure for the simulation of a 1 K $\Omega$  resistor embedded in the test fixture.

solution. Any volume of material added to the structure will be included in the finite-element mesh, and will increase the amount of memory required for the simulation. All unnecessary material, such as the full thickness of the copper block, has therefore been excluded from the simulation. The structure is surrounded by an air-box, which defines the volume over which the electromagnetic fields will be calculated. Stimuli are applied to the network through wave ports, which are defined by rectangles at the ends of the structure and the ends of the micro-strip traces. Two-port network parameter measurements were simulated for the full test structure, containing the network under test, and for each of the on- and off-chip deembedding structures described in Chapter 3. The results of these simulations represent the complete set of data that will be obtained from actual network analyzer measurements on the physical test fixture. Simulated data is stored as S-parameters in Touchstone-formatted files, as it will be for measured data. The S-parameter files from the simulated measurements are fed into a Matlab program, which performs the deembedding and outputs network parameters for the substrate network, or, in the case of these simulations, a resistor.

Simulation facilitates the test fixture and deembedding procedure design by allowing the simulation ports to be placed at various points in the test fixture, yielding network parameters for isolated test fixture sections. For example, the accuracy of the first step of the deembedding procedure, elimination of the effects of the micro-strip transmission lines, can be evaluated by submitting the network parameters obtained from a simulation of the complete structure in Figure 5.1, to the first deembedding step, and comparing the resulting network parameters to those obtained from a simulation with the micro-strip lines removed from the structure.

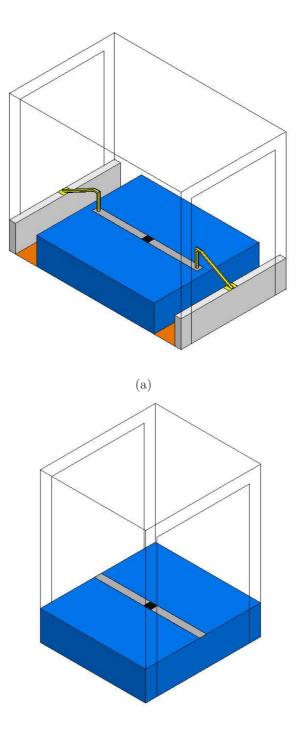

In other words, the structure of Figure 5.1 is simulated and the effects of the micro-strip lines are stripped from the simulation by the first deembedding step. The resulting data is then compared to the network parameters obtained from a simulation of the structure shown in Figure 5.2(a). This structure serves as the reference network for the validation of the first deembedding step, and sets the standard by which the accuracy of this part of the deembedding process is judged. Similarly, the second step of deembedding can be evaluated by comparing the resulting network parameters to those obtained from simulation of the structure shown in Figure 5.2(b).

Discrepancies between the deembedded data and the data from the simulation of the corresponding reference network indicate problems either with the test fixture model (Figure 4.1), the deembedding procedure, or both. Discrepancies due to errors in the model can be remedied by either changing the model to more accurately reflect the test fixture, or by altering the test fixture design to better match the model. As the model becomes more complex, more measurements and perhaps additional deembedding test structures may be needed in order to obtain the parameters that characterize that model. For this reason, it is often preferable to alter the test fixture to conform to the simplest possible model.

#### 5.1.1. Simulations of a 1 K $\Omega$ Resistor

HFSS simulations of simple networks embedded in the test fixture, such as the 1 K $\Omega$  resistor of Figure 5.1, shaped the design of the test fixture and deembedding plan. This section will present the simulated S-parameters for that 1 K $\Omega$  resistor as the data progresses through each successive deembedding step.

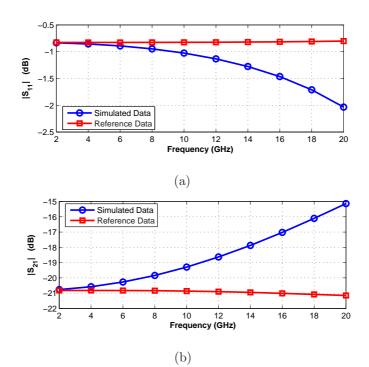

Figure 5.3 shows the S-parameters resulting from simulation of the structure of Figure 5.1. These results represent the S-parameters that would be obtained from measurements taken of the 1 K $\Omega$  resistor embedded in the test fixture. Also plotted are the reference S-parameters for the resistor. The reference Sparameters, available due to the fact that these are simulations, represent the end goal of the deembedding procedure, and the standard by which its effectiveness will be judged.

(b)

FIGURE 5.2. Reference networks for the (a) first and (b) second deembedding steps.

FIGURE 5.3. Simulated S-parameters for a 1 K $\Omega$  resistor embedded in the test fixture. (a) S<sub>11</sub>, (b) S<sub>21</sub>.

While the simulated data agree quite well with the reference S-parameters at 2 GHz, as the frequency increases and the parasitic effects of the test fixture become important, the simulated data diverge from the reference S-parameters. Note that the reference S-parameters are about what would be expected for an electrically small 1 K $\Omega$  resistor:  $S_{21} \approx -21$  dB and  $S_{11} \approx -0.8$  dB. Because the resistor is electrically small, even at 20 GHz, its S-parameters remain relatively constant over the frequency range.

Figures 5.4 through 5.7 show how the simulated S-parameters evolve throughout the deembedding procedure. The effectiveness of the deembedding procedure is illustrated as, with each successive deembedding step, the Sparameters converge to the reference S-parameters. The S-parameters following

FIGURE 5.4. Simulated S-parameters for a 1 K $\Omega$  resistor following the first deembedding step. (a) S<sub>11</sub> after step 1. (b) S<sub>21</sub> after step 1.

the final deembedding step (Figure 5.7) show very good agreement with the refernce S-parameters.

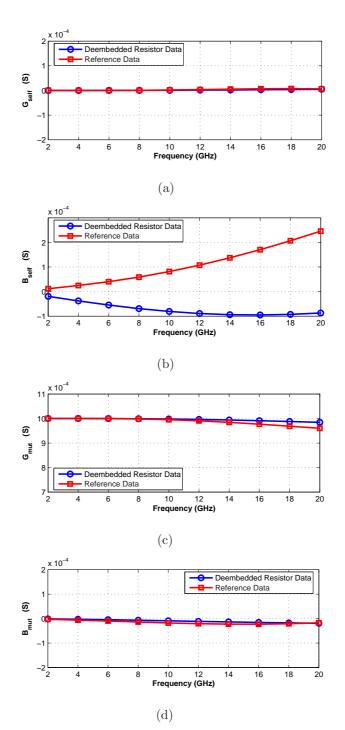

The data in Figures 5.3 through 5.7 are presented in terms of S-parameters, because these are the two-port parameters directly obtained from network analyzer measurements, both real and simulated. However, it is the Y-parameters, and the corresponding self and mutual admittances, that are of most interest when developing and evaluating a model such as that of Figure 1.2. The deembedded self admittance,  $Y_{self}$ , and mutual admittance,  $Y_{mut}$ , for the resistor of Figure 5.1 are plotted in Figure 5.8.

FIGURE 5.5. Simulated S-parameters for a 1 K $\Omega$  resistor following the second deembedding step. (a) S<sub>11</sub> after step 2. (b) S<sub>21</sub> after step 2.

Self admittance is the admittance of the shunt branches of an equivalent pi-network, and mutual admittance is the admittance of the series branch. These admittances can be expressed in terms of Y-parameters as follows:

$$Y_{self} = Y_{11} + Y_{21} \tag{5.1}$$

$$Y_{mut} = -Y_{21} (5.2)$$

The 1 K $\Omega$ , 60  $\mu$ m x 60  $\mu$ m resistor is electrically small over this frequency range, so it can be expected that its equivalent pi-network would essentially be a resistor, perhaps with some small amount of capacitive susceptance in the shunt legs. Since the resistor is placed on a lossless dielectric substrate, the self conductance should be zero. Additionally, it can be expected that the mutual conductance would decrease slightly from its low frequency value of 1 mS, due to the

FIGURE 5.6. Simulated S-parameters for a 1 K $\Omega$  resistor following the third deembedding step. (a) S<sub>11</sub> after step 3. (b) S<sub>21</sub> after step 3.

skin effect. These expectations are borne out in the plots of Figure 5.8. While there appears to be a significant discrepancy between the reference and deembedded self susceptance,  $B_{self}$ , note that the self susceptance of the reference network corresponds to a shunt capacitance of less than 2 fF, so it is not a large error.

## 5.2. Simulations of On-Chip Test structures

The second category of simulations, which were performed in EPIC, included only the on-chip substrate contacts and the heavily-doped silicon substrate that surrounds them. Neither the on-chip interconnects, nor off-chip test fixture were included. For these simulations, the simplified substrate model of Section 5.1

FIGURE 5.7. Simulated S-parameters for a 1 K $\Omega$  resistor following the final deembedding step. (a) S<sub>11</sub> after step 4. (b) S<sub>21</sub> after step 4.

was replaced with a more accurate model of the heavily-doped silicon substrate, on which the test chip is fabricated.

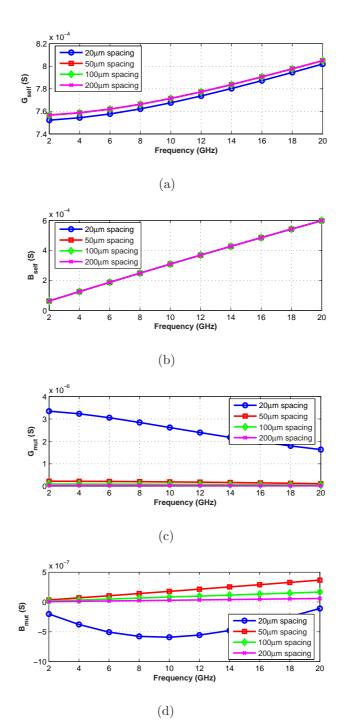

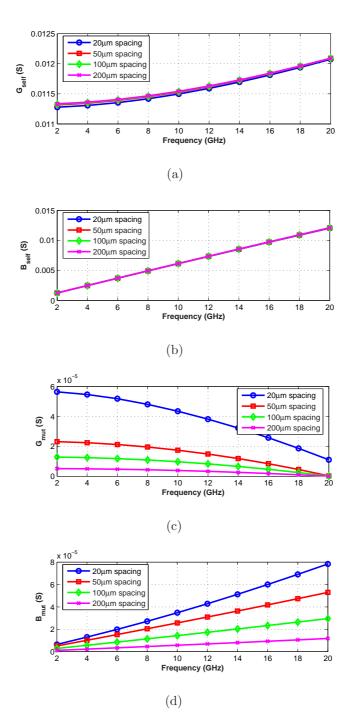

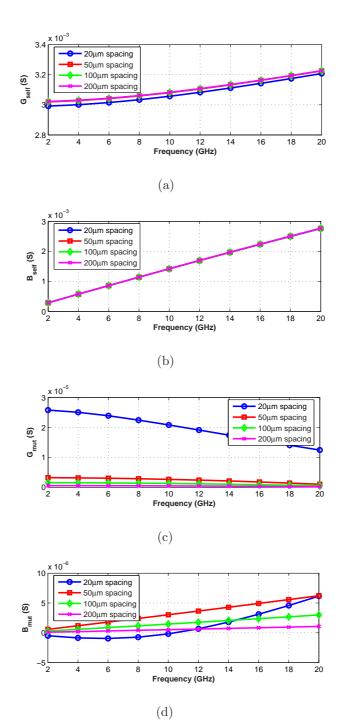

The heavily-doped substrate used in the TSMC 0.35  $\mu$ m logic process can be modeled as comprising three discrete layers, as illustrated in Figure 5.9 [19]. This substrate profile is typical of substrates used for mixed-signal systems on chip, which may contain large, noisy digital blocks, along with sensitive analog circuitry. The bulk layer is a 245  $\mu$ m-thick heavily-doped layer. This low-resistivity layer aids latchup prevention in the digital circuitry. The 4  $\mu$ m-thick epitaxial layer has a higher resistivity of 10  $\Omega$ ·cm, and serves to provide some degree of isolation between circuits on the chip. The top layer is the 1  $\mu$ m-thick, 2  $\Omega$ ·cm channel stop