#### AN ABSTRACT OF THE THESIS OF

| Mehran G. Aminzadeh for the degree of <u>Doctor of Philosophy</u> in |

|----------------------------------------------------------------------|

| Electrical and Computer Engineering presented on April 25, 1988.     |

| Title: Recombination and Generation Lifetime Characterization of     |

| p/p Epitaxial silicon Wafers                                         |

| Abstract approved: Redacted for privacy                              |

| Professor Leonard Forbes                                             |

The refresh times of all dynamic charge storage devices, best characterized by the generation lifetime at room temperature and the recombination lifetime at higher device operating temperatures (T>70°C), strongly influence the efficient and successful operation of dynamic charge storage devices such as DRAM's and CCD's. Both recombination and generation lifetime characteristics of p/p<sup>+</sup> epitaxial silicon wafers are investigated. Extremely high generation lifetimes on the order of 20-30 msec are observed on p-type epitaxial layers which are correlated by DLTS measurements where no significant trap levels with concentrations higher than  $3x10^{11}$  cm<sup>-3</sup> are observed.

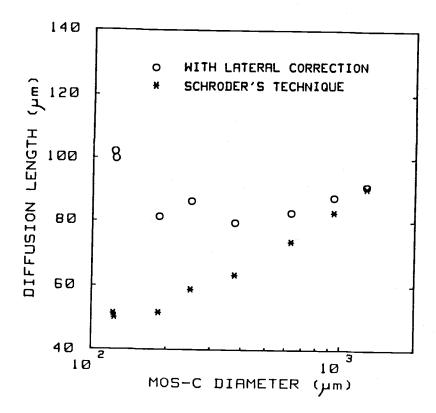

Schroder's [1] simple technique for the determination of recombination lifetimes of materials using a pulsed MOS capacitor technique at elevated temperatures ignores the lateral quasi-neutral bulk generation for short base width devices such as thin epitaxial layers. Consequently, calculations using Schroder's technique indicate that the recombination lifetime of a given material is a function of MOS capacitor diameter. A simple one dimensional approach

was developed [2] for the measurement of recombination lifetimes in which quasi-neutral bulk generation in the lateral area of MOS capacitors and the time dependence of the width of space-charge region are taken into consideration for short-base-width devices.

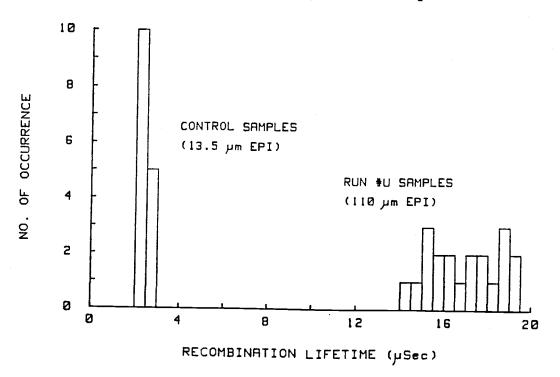

The apparent recombination lifetime of thin p-type epitaxial layers were limited to 2  $\mu$ sec by the lower lifetime of the epitaxial layer - p<sup>+</sup> substrate interface. Investigation of wafers with various epitaxial layer thickness revealed that the actual recombination lifetime of the bulk epitaxial material is an order of magnitude higher than the apparent values. Precipitates at the epitaxial layer - substrate interface were suspected as the main limiting factor causing a localized degradation of recombination lifetimes at the epitaxial layer - substrate interface in p/p<sup>+</sup> epitaxial wafers. Application of an intrinsic gettering cycle and CMOS simulation heat treatments suggests up to three fold improvement of apparent recombination lifetimes.

# Recombination and Generation Lifetime Characterization of p/p Epitaxial Silicon Wafers

by

Mehran G. Aminzadeh

#### A THESIS

submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of Doctor of Philosophy

Completed April 25,1988

Commencement June 1988

APPROVED:

# Redacted for privacy

| Professor of Electrical and Computer Engineering in charge of major Redacted for privacy |

|------------------------------------------------------------------------------------------|

| Head of department of Electrical and Computer Engineering                                |

|                                                                                          |

|                                                                                          |

|                                                                                          |

| Redacted for privacy                                                                     |

| Dean of Graduate School                                                                  |

|                                                                                          |

|                                                                                          |

|                                                                                          |

|                                                                                          |

| Date thesis is presented: <u>April 25, 1988</u>                                          |

|                                                                                          |

| Typed by researcher for: Mehran G. Aminzadeh                                             |

|                                                                                          |

## <sup>C</sup> Copyright by Mehran G. Aminzadeh April 25, 1988

All Rights Reserved

#### ACKNOWLEDGEMENT

I express my sincere appreciation to professor Len. Forbes for his guidance, and support during this investigation. I am grateful to Dr. John Wager and Dr. Steve Goodnick for their timely and critical review of this manuscript and helpful discussions. Also to be thanked is Dr. Babak Sabi for his continuous encouragement and his helpful discussions.

The author is grateful to Dr. Howard Mollenkopf, Dr. Witawat Wijaranakula, and Dr. Albert Derheimer of SEH America, Inc. for their valuable discussions and support throughout this investigation.

This work was sponsored in part by SEH America, Inc. and the Intel Research Council.

## TABLE OF CONTENTS

|   |     |                                                                                              | Page |

|---|-----|----------------------------------------------------------------------------------------------|------|

| I | נאנ | PRODUCTION                                                                                   | 1    |

| п | BAC | KGROUND AND LIFETIME MEASUREMENT TECHNIQUES                                                  | 6    |

|   | A.  | RECOMBINATION-GENERATION PROCESS                                                             | 7    |

|   |     | 1. Recombination versus generation lifetime                                                  | 9    |

|   |     | 2. Generation lifetime measurement techniques                                                | 13   |

|   |     | 3. Generation lifetime using pulsed MOS capacitor                                            | 16   |

|   |     | 4. Maximum possible recombination-generation lifetimes in silicon                            | 23   |

|   | в.  | RECOMBINATION LIFETIME                                                                       | 27   |

|   |     | 1. Recombination lifetime measurement techniques                                             | 27   |

|   |     | 2. Recombination lifetime of short base width devices using pulsed MOS capacitance technique | 29   |

|   | c.  | DEEP LEVEL TRANSIENT SPECTROSCOPY (DLTS)                                                     | 34   |

|   |     | 1. Capacitance DLTS                                                                          | 34   |

|   |     | 2. Application of DLTS to MOS relaxation transients                                          | 40   |

|   | D.  | EFFECTS OF INTRINSIC GETTERING ON LIFETIME                                                   | 43   |

| ш | EX  | PERIMENTAL SETUP AND PROCEDURE                                                               | 48   |

|   | A.  | MOS CAPACITOR AND LIFETIMES                                                                  | 52   |

|   |     | 1. Fabrication of MOS capacitors                                                             | 52   |

|   |     | 2. C-V characterization setup and procedure                                                  | 54   |

|   |     | 3. Generation lifetime setup and procedure                                                   | 56   |

|   |     | 4. Recombination lifetime setup                                                              | 60   |

#### TABLE OF CONTENTS — Continued

|    |    |                                                                 | Page |

|----|----|-----------------------------------------------------------------|------|

| ш  | EX | PERIMENTAL PROCEDURE AND SETUP (continued)                      |      |

|    | в. | SCHOTTKY BARRIER DIODES AND DLTS                                | 60   |

|    |    | 1. Fabrication of Schottky diodes                               | 60   |

|    |    | 2. DLTS setup                                                   | 62   |

|    |    | 3. Majority carrier DLTS and optical DLTS                       | 62   |

| IV | RE | SULTS AND DISCUSSION (I)                                        | 64   |

|    | A. | C-V CHARACTERIZATION OF MOS CAPACITORS                          | 64   |

|    | в. | GENERATION LIFETIME                                             | 73   |

|    |    | 1. Surface generation effects of high quality silicon materials | 75   |

|    |    | 2. Generation lifetimes of p/p epitaxial wafers                 | 80   |

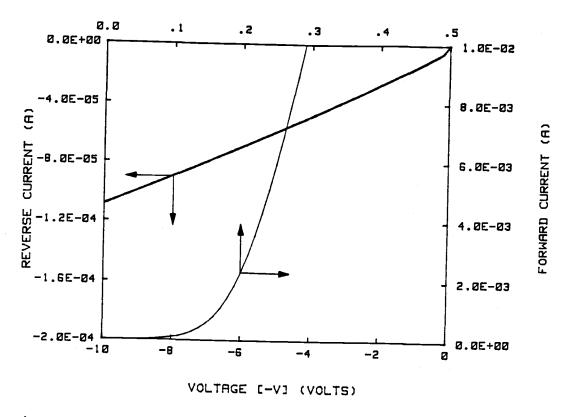

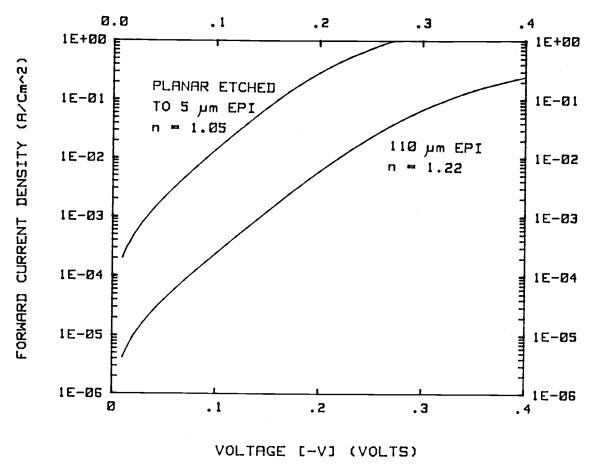

|    | c. | CHARACTERIZATION OF SCHOTTKY DIODES                             | 83   |

|    |    | 1. I-V characteristics                                          | 83   |

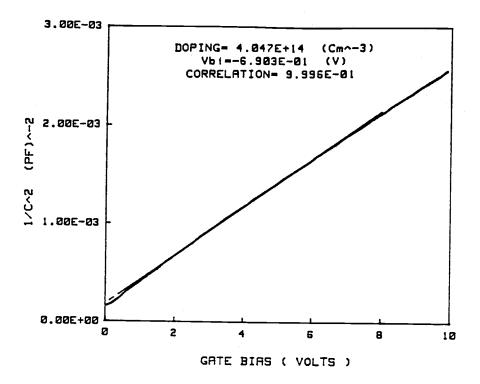

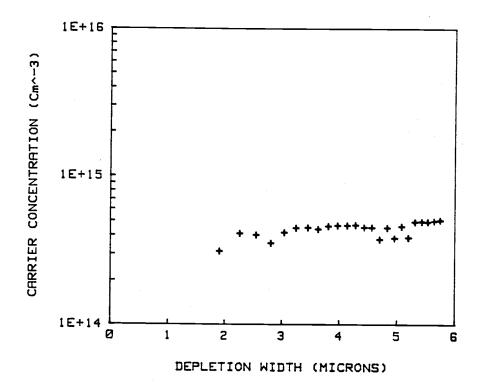

|    |    | 2. C-V characteristics                                          | 89   |

|    | D. | DEEP LEVEL TRANSIENT SPECTROSCOPY                               | 92   |

|    |    | 1. Majority carrier DLTS of p/p epitaxial wafers                | 92   |

|    |    | 2. Optical DLTS of p/p <sup>+</sup> epitaxial wafers            | 95   |

|    |    | 3. Trap levels of a Fe implanted sample as an illustration      | 98   |

## TABLE OF CONTENTS — Continued

|                                                                                                                     | Page  |

|---------------------------------------------------------------------------------------------------------------------|-------|

| V RESULTS AND DISCUSSION (II)                                                                                       | . 103 |

| A. RECOMBINATION LIFETIME OF p/p EPITAXIAL WAFERS                                                                   | . 103 |

| <ol> <li>Recombination lifetime of short base width devices<br/>using the pulsed MOS capacitor technique</li> </ol> | . 103 |

| <ol> <li>Recombination lifetime 13.5 μm</li> <li>p/p epitaxial control wafers</li> </ol>                            | . 109 |

| 3. Epitaxial layer - p <sup>+</sup> substrate interface generation                                                  | . 111 |

| 4. Temperature dependence of diffusion process                                                                      | . 117 |

| 5. Possible source of epi-layer - p <sup>+</sup> substrate interface current                                        | . 123 |

| 6. Effects of intrinsic gettering and heat treatments on $\tau_{\rm r}$                                             | . 126 |

| 7. Suggestions for improving $\tau_r$ in thin p/p epitaxial silicon                                                 | . 129 |

| VI CONCLUSIONS AND SUGGESTIONS FOR FUTURE WORK                                                                      | . 132 |

| VII REFERENCES                                                                                                      | . 137 |

| VIII APPENDICES                                                                                                     | 144   |

#### LIST OF FIGURES

| <u>Figun</u> | <u>Title</u>                                                                                                                                                                                               | <u>Page</u> |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 1            | Generation within the space charge region corresponding to inverse SRH recombination process for p-type Si                                                                                                 | 9           |

| 2            | Diffusion process from the bulk at elevated temperatures dominates the generation within the space charge region                                                                                           | 11          |

| 3            | Schematic representation of the pulsed MOS capacitor. indicating four carrier generation mechanism involved in relaxation to equilibrium                                                                   | 17          |

| 4            | a) Pulsed MOS capacitor C-t response, and b) Zerbst plot .                                                                                                                                                 | 21          |

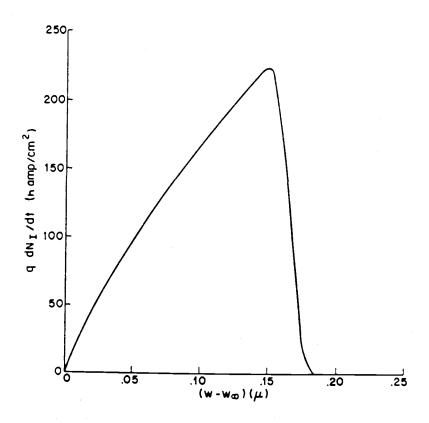

| 5            | Rate of change of inversion layer density per area versus W-W $_{\rm f}$ , after Collins and Churchill [22]                                                                                                | 22          |

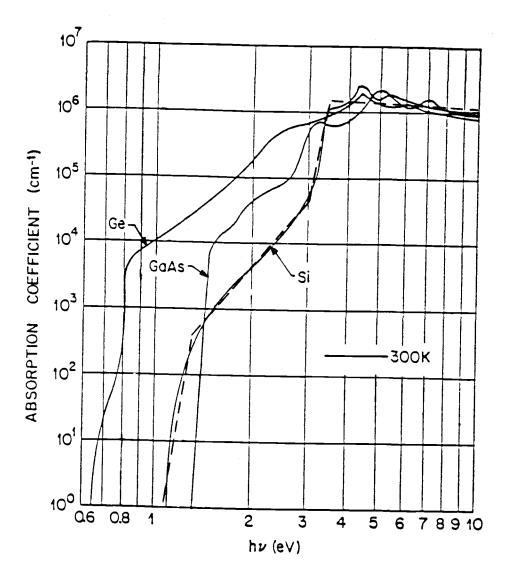

| 6            | Measured absorption coefficient for pure Ge, Si, and GaAs, after S.M. Sze [25]                                                                                                                             | 25          |

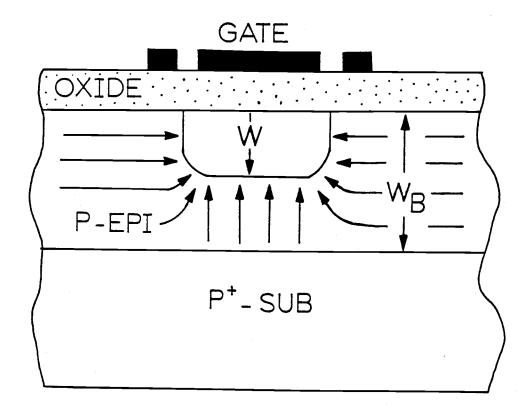

| 7            | Cross sectional view of a short base width device on p/p epitaxial silicon                                                                                                                                 | 31          |

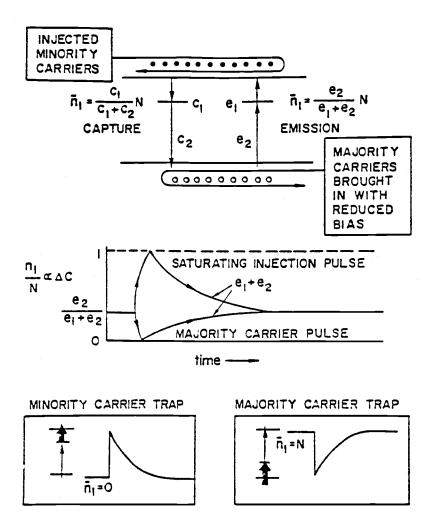

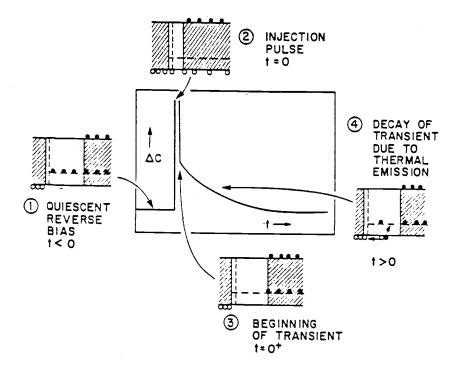

| 8            | Schematic diagram of the emission and capture process for an arbitrary trap level and capacitance transient of that trap in p-type material, after D.V. Lang [41]                                          | 35          |

| 9            | Pulse sequence which is used to produce a capacitance transient for a) minority carrier trap and b) majority carrier trap for a p-n junction, after D.V. Lang [43]                                         | 36          |

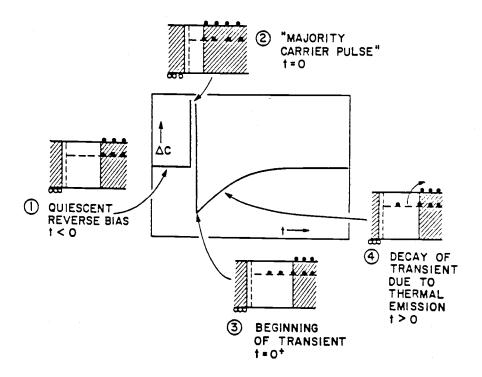

| 10           | Schematic representation of various temperatures which corresponds to DLTS signal resulting from a double boxcar integrator, after D.V. Lang [41]                                                          | 38          |

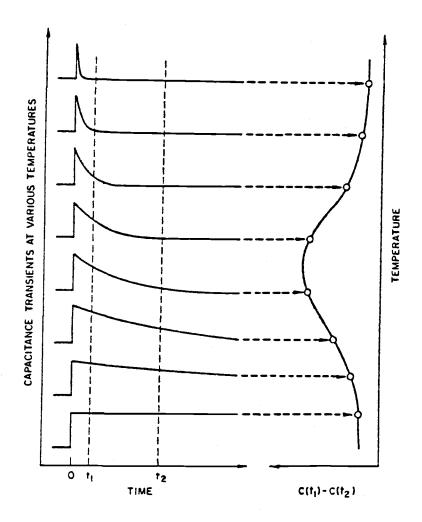

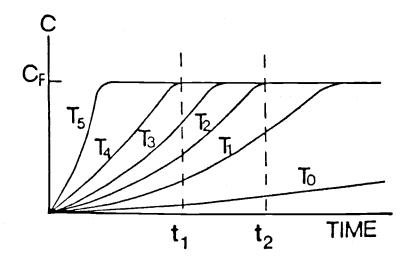

| 11           | a) Schematic representation of C-t response of a MOS capacitor at various temperatures. b) Illustrates how an application of DLTS results in a peak corresponding to retention time, t2, after Pearce [46] | 41          |

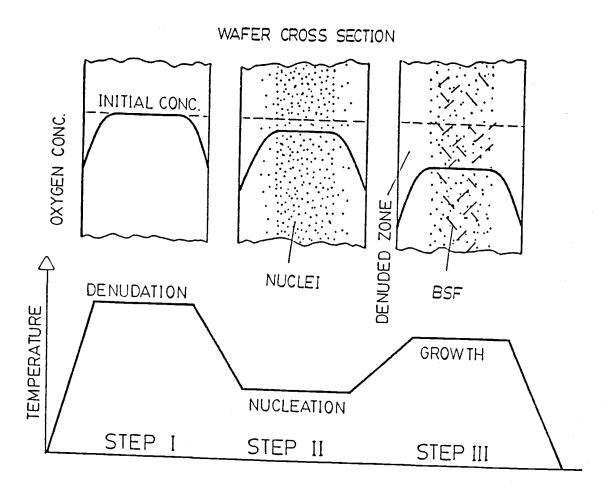

| 12           | The fundamental heat treatment steps for intrinsic gettering, after W. Wijaranakula [54]                                                                                                                   | 45          |

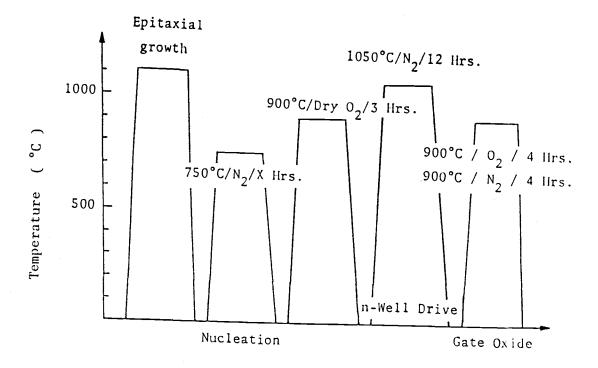

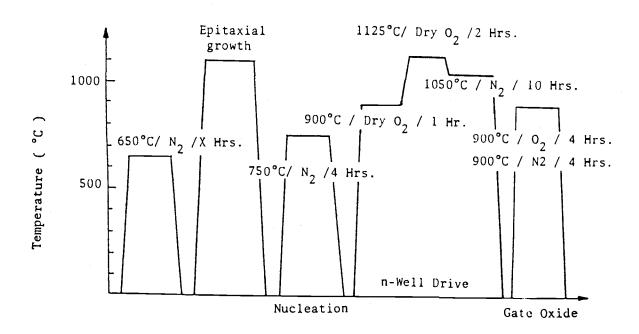

| 13           | Nucleation and heat treatment cycles of intrinsic gettering and CMOS simulations                                                                                                                           | 50          |

| Figun | <u>Title</u>                                                                                                                                                                   | <u>Page</u> |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

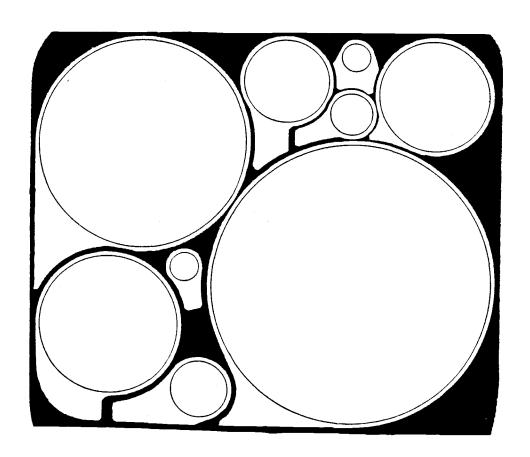

| 14    | Mask set of various size diameters ranging from 123 $\mu$ m to 1272 $\mu$ m with a 6 $\mu$ m guard ring spacing, after W.I. Sze [68]                                           | 51          |

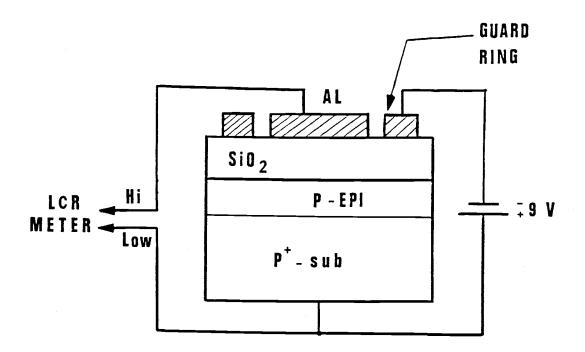

| 15    | Cross section of an MOS test capacitor                                                                                                                                         | 52          |

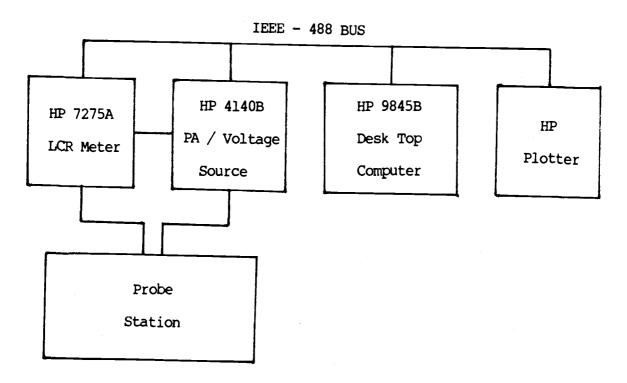

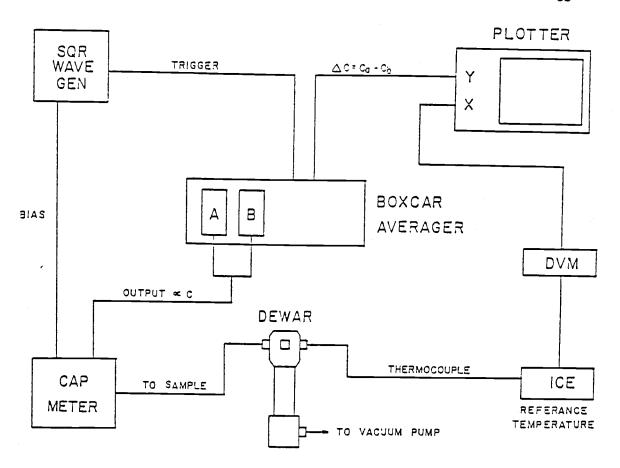

| 16    | Block diagram of the device characterization setup                                                                                                                             |             |

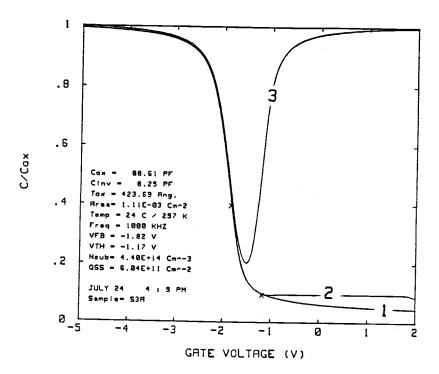

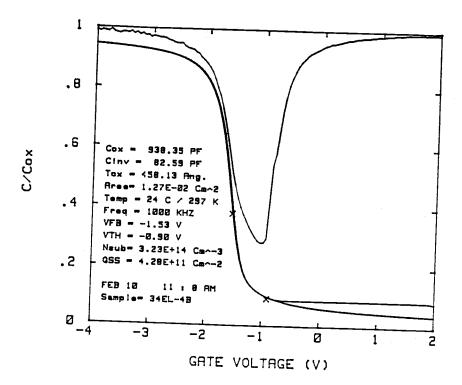

| 17    | Typical C-V characteristics of a p-type MOS capacitor                                                                                                                          | 55          |

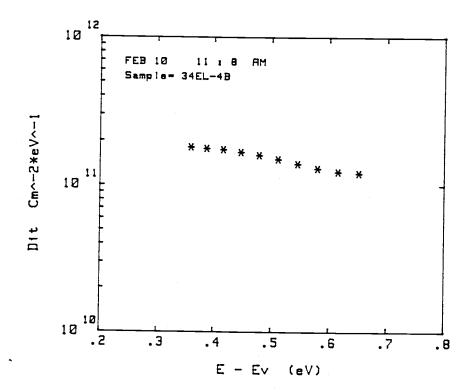

| 18    | Typical Si-SiO <sub>2</sub> density of interface traps (Dits) distribution within the silicon band gap                                                                         |             |

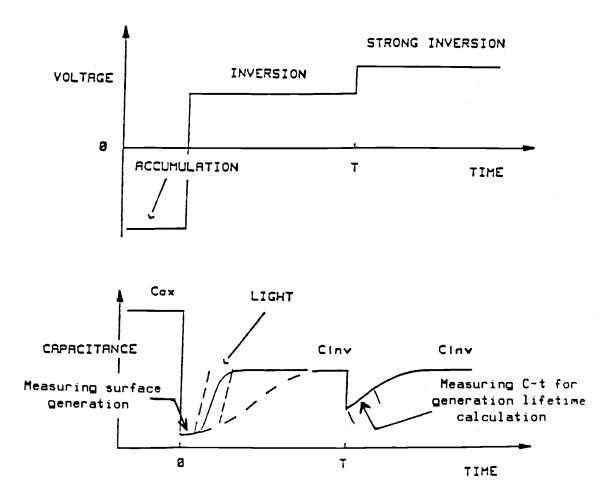

| 19    | Schematic diagram of the modified voltage steps and C-t transient response for faster $\tau_{\rm g}$ evaluation                                                                | 57          |

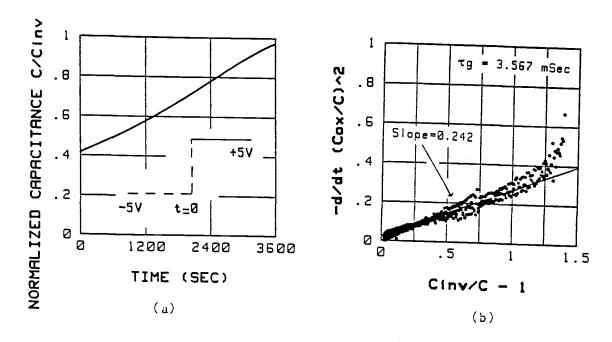

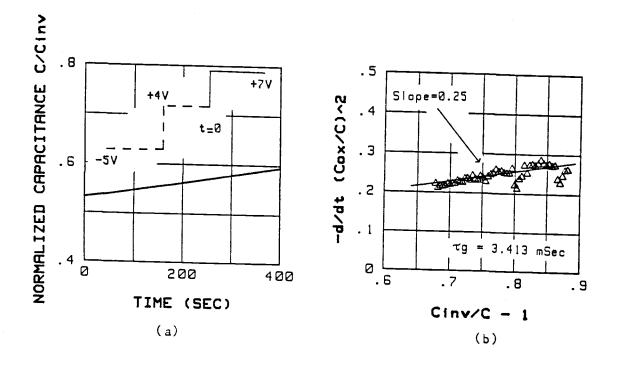

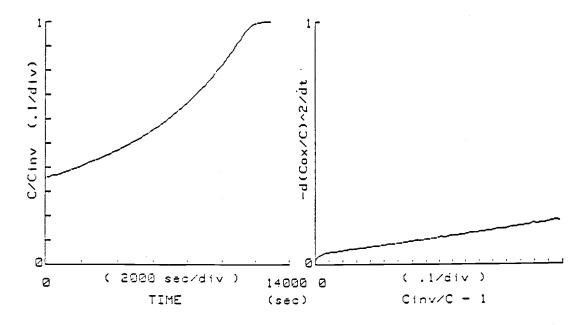

| 20    | a) C-t response of a typical MOS capacitor, b) Zerbst plot of part a)                                                                                                          | 58          |

| 21    | a) Partial C-t response of the same device as fig. 20 using two voltage steps, b) Zerbst plot of part a)                                                                       | 58          |

| 22    | Schematic diagram of the DLTS setup                                                                                                                                            | 63          |

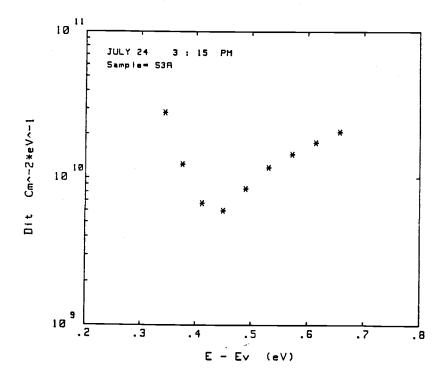

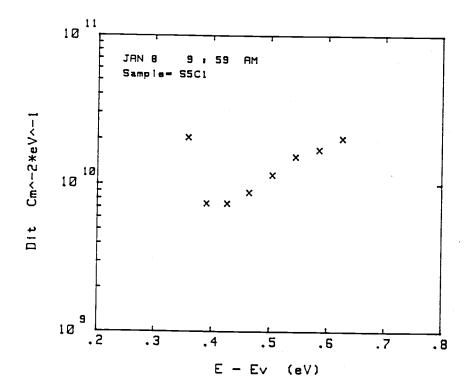

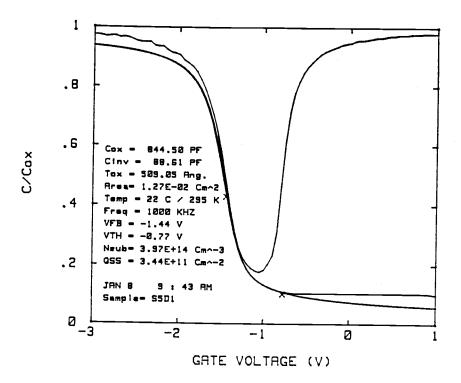

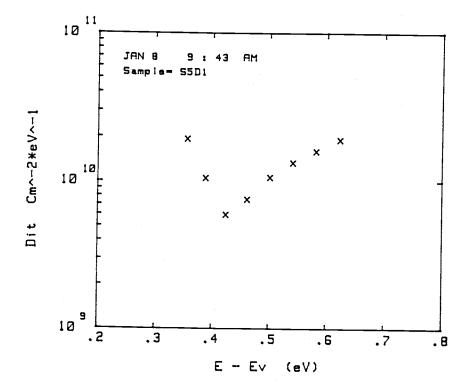

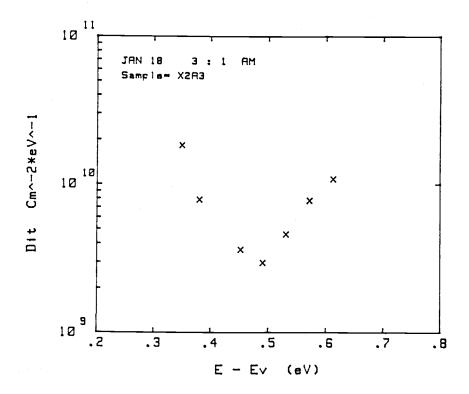

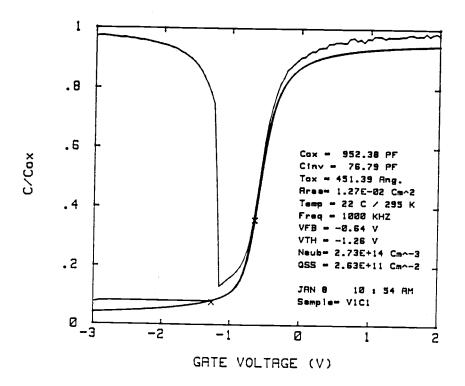

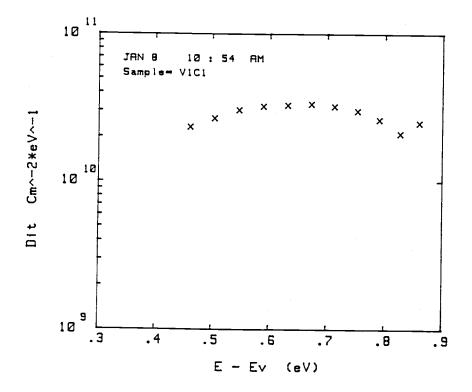

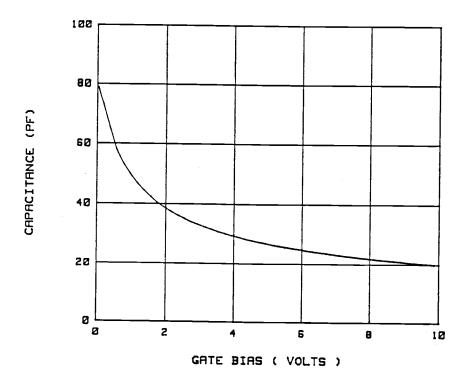

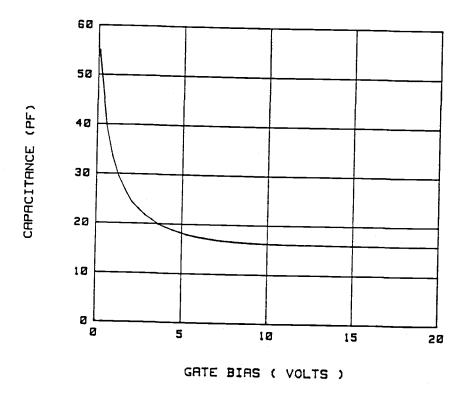

| 23    | a) High frequency and quasi-static C-V plots of a p/p <sup>+</sup> epitaxial wafer without post-metalization anneal, b) distribution of density of interface traps of fig. 23a | 65          |

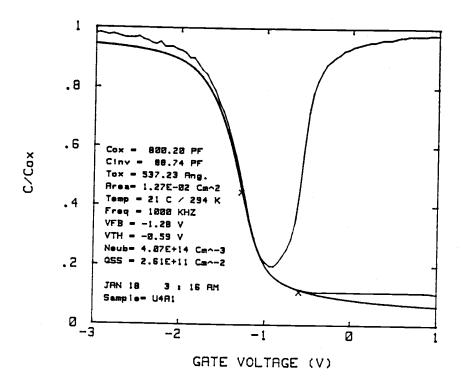

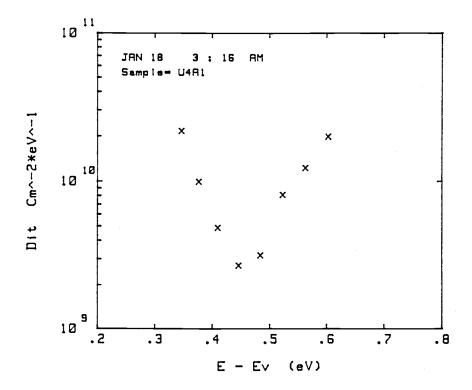

| 24    | a) High frequency and quasi-static C-V plots of a 6 $\mu$ m p/p epitaxial layer, b) distribution of density of interface traps of fig. 24a)                                    | 68          |

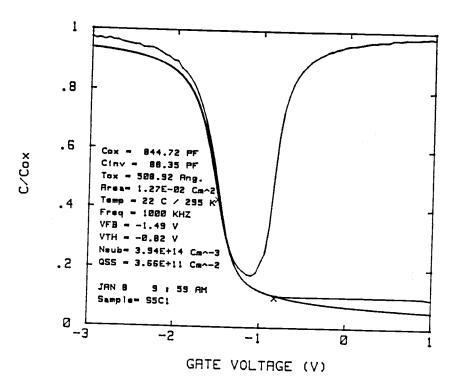

| 25    | a) High frequency and quasi-static C-V plots of a 13.5 $\mu$ m p/p epitaxial layer, b) distribution of density of interface traps of fig. 25a)                                 | 69          |

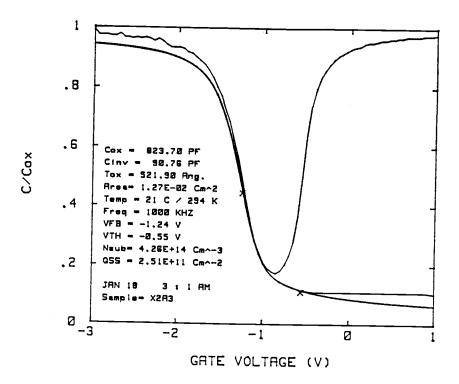

| 26    | a) High frequency and quasi-static C-V plots of a 70 $\mu$ m p/p epitaxial layer, b) distribution of density of interface traps of fig. 26a)                                   | 70          |

| 27    | a) High frequency and quasi-static C-V plots of a 110 $\mu$ m p/p epitaxial layer, b) distribution of density of interface traps of fig. 27a)                                  | 71          |

|       | a) High frequency and quasi-static C-V plots of a 50 $\mu$ m N/N epitaxial layer, b) distribution of density of interface traps of fig. 28a)                                   |             |

| Figur | <u>Title</u>                                                                                                                                       | <u>Page</u> |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 29    | Typical C-t response of an MOS capacitor at T=22°C using an accumulation-depletion voltage step                                                    | 73          |

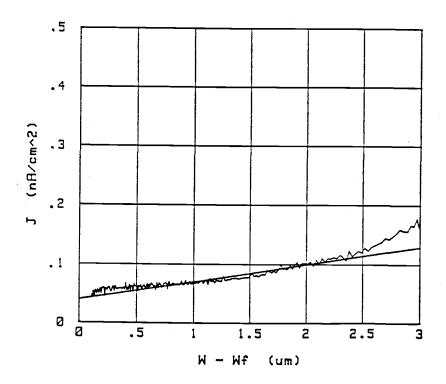

| 30    | a) Typical C-t response of an MOS capacitor at T=22°C using a modified voltage step, b) its Zerbst plot plotted in terms of J vs. W-W <sub>f</sub> | 74          |

| 31    | Typical C-t and Zerbst plot of a p/p epitaxial wafer, after W.I Sze [68]                                                                           | 77          |

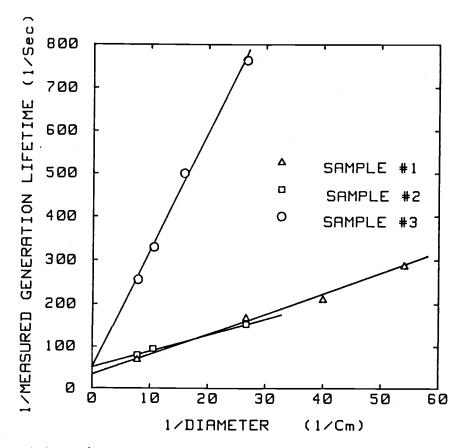

| 32    | Reciprocal of measured generation lifetime versus reciprocal MOS capacitor diameter                                                                | 78          |

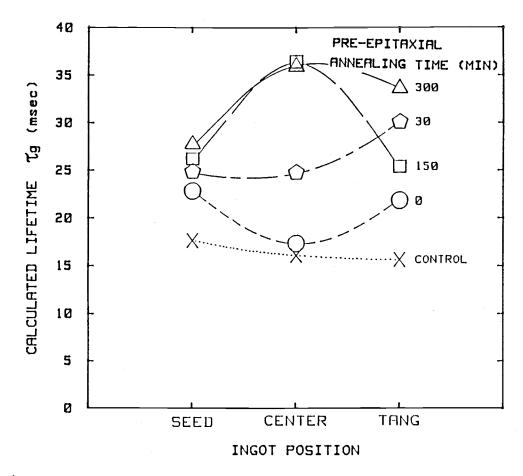

| 33    | Calculated generation lifetime vs. position in ingot for various pre-epitaxial annealing times, after W.I. Sze [68]                                | 81          |

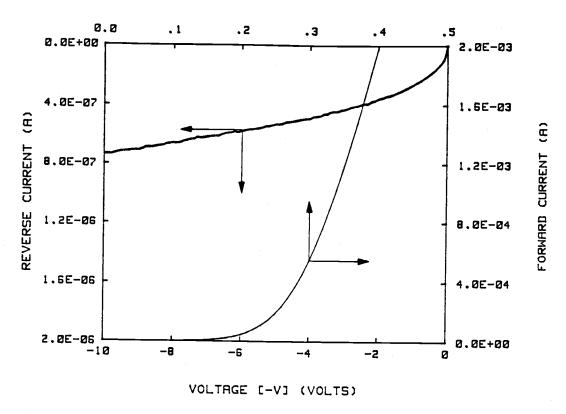

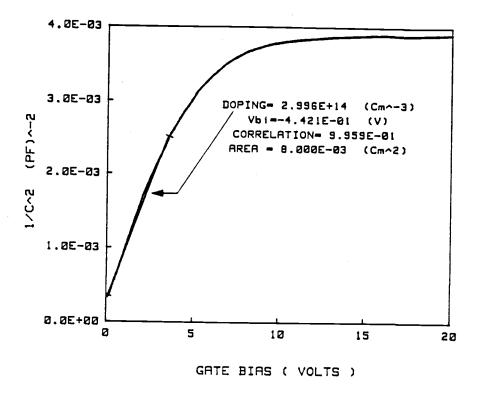

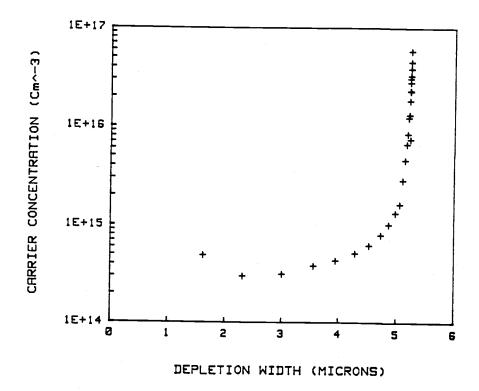

| 34    | a) I-V , b) C-V , c) $1/c^2$ - V, and d) free carrier profile of 110 $\mu$ m thick epi Schottky diode                                              | 84          |

| 35    | a) I-V , b) C-V , c) $1/c^2$ - V, and d) free carrier profile of 13.5 $\mu m$ epi (control) Schottky diode                                         | 86          |

| 36    | Plot of ideality factor of Schottky diodes                                                                                                         | 88          |

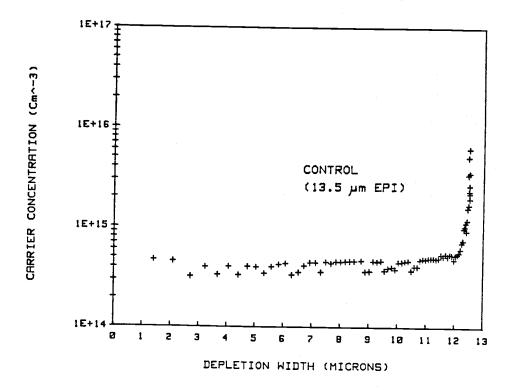

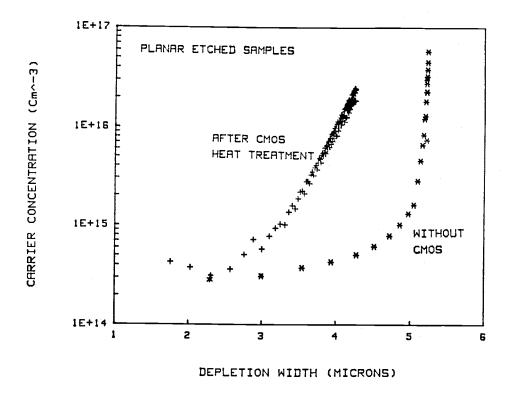

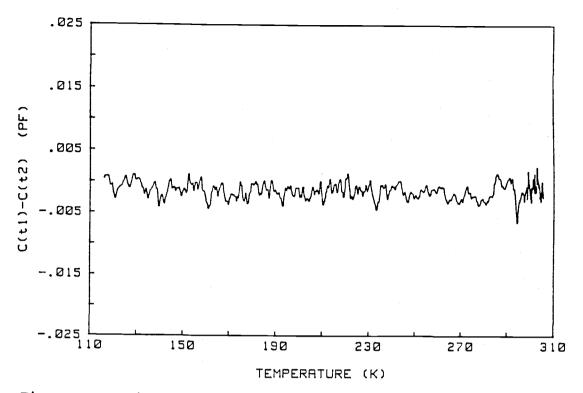

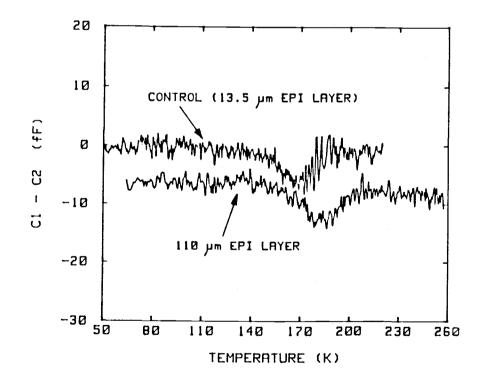

| 37    | a) carrier profile of control sample, b) carrier profile of planar etched samples with and without the CMOS cycle .                                | 90          |

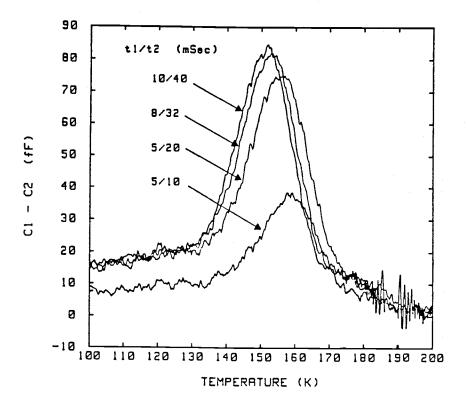

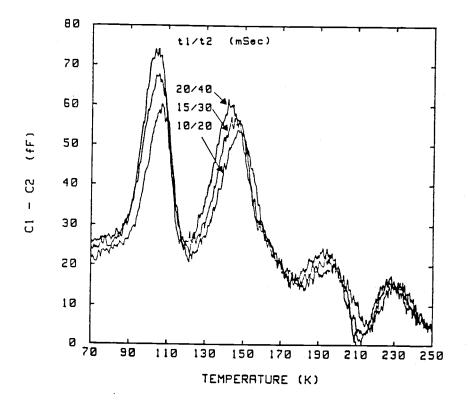

| 38    | Typical majority carrier DLTS spectra of a 13.5 $\mu m$ epitaxial layer Schottky diode                                                             | 93          |

| 39    | Majority carrier DLTS spectra of a control and 110 $\mu m$ epitaxial layers showing an extremely small and broad peak                              | 93          |

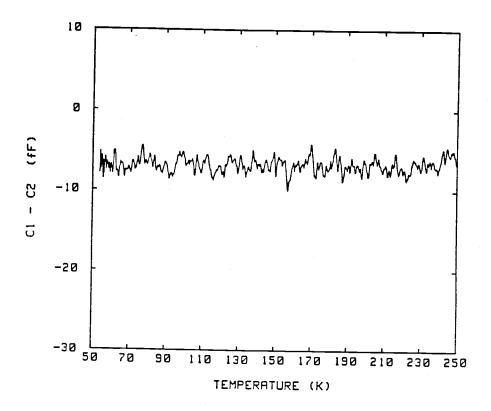

| 40    | Optical DLTS signal of a 110 $\mu$ m epi-layer diode                                                                                               | 96          |

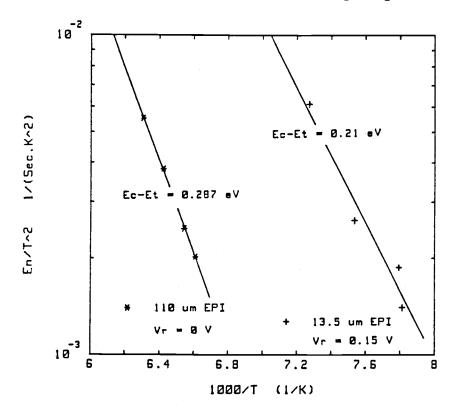

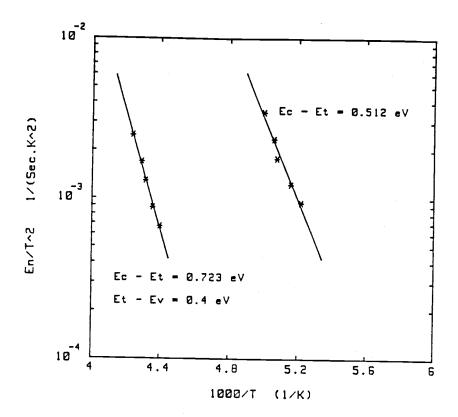

| 41    | Arrhenius plot of the 110 $\mu m$ epi-layer diode biased at 0 V and a 13.5 $\mu m$ control epi-layer diode reversed biased at 0.15 V               | 96          |

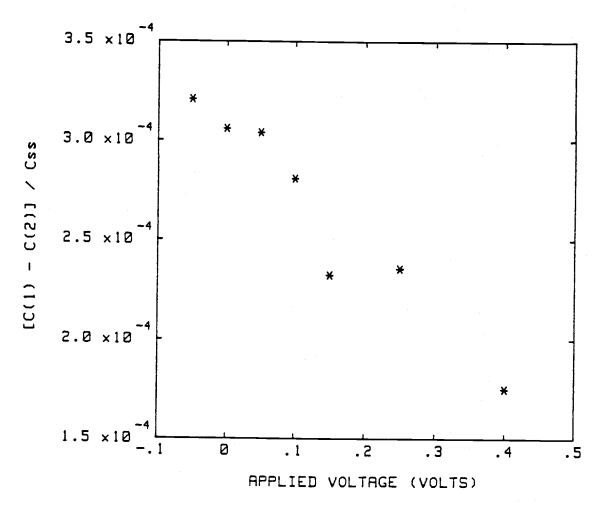

| 42    | $\delta$ C/C as a function of applied reverse bias on the control Schottky diode                                                                   | 97          |

| 43    | Majority carrier DLTS spectra of a Fe implanted Schottky diode                                                                                     | 99          |

| rigur | <u>Title</u>                                                                                                                                               | <u>Page</u> |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

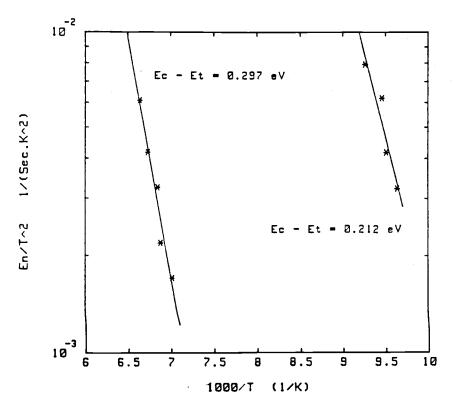

| 44    | Optical DLTS spectra of a Fe implanted Schottky diode                                                                                                      | 99          |

| 45    | Arrhenius plot of a Fe implanted Schottky diode showing the donor levels detected by optical DLTS                                                          | 100         |

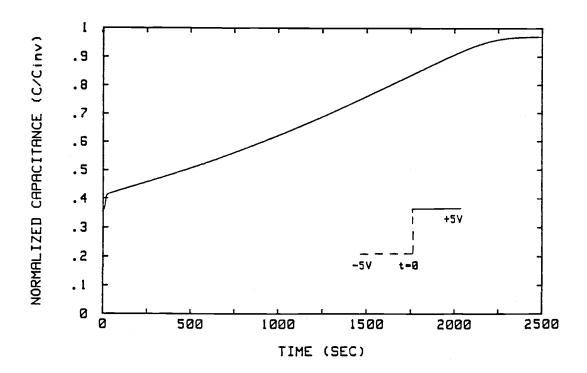

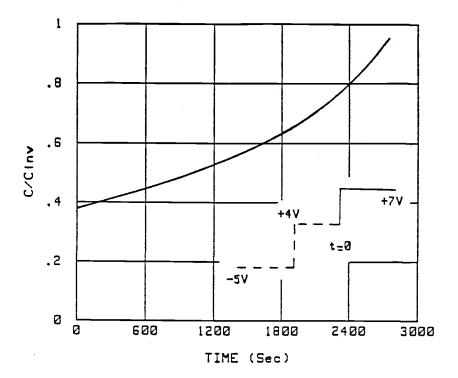

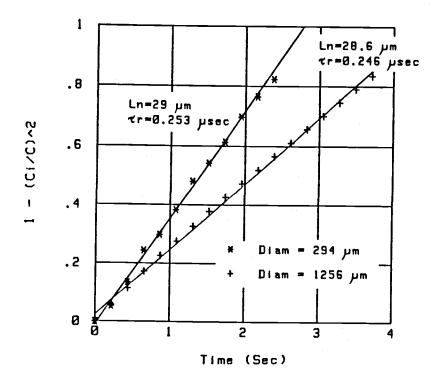

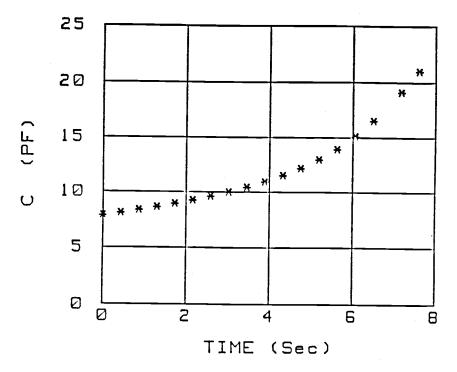

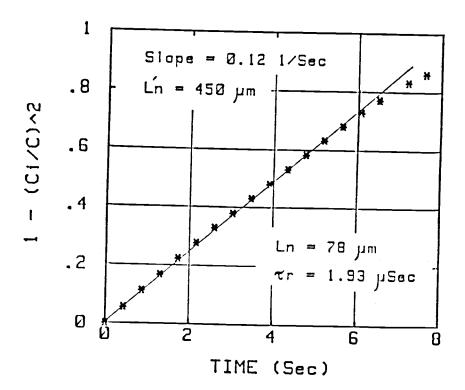

| 46    | 1 - (C <sub>i</sub> /C) <sup>2</sup> versus time plot of p-type polished wafers for different diameters measured at T=55°C                                 | 104         |

| 47    | a) C-t transient response of a MOS capacitor on p/p epitaxial layer measured at T=70°C. b) 1 - (C;/C) versus time calculated from C-t response shown in a) | 105         |

| 48    | The calculated diffusion length versus device diameter. The technique with lateral bulk correction versus Schroder's technique                             | 106         |

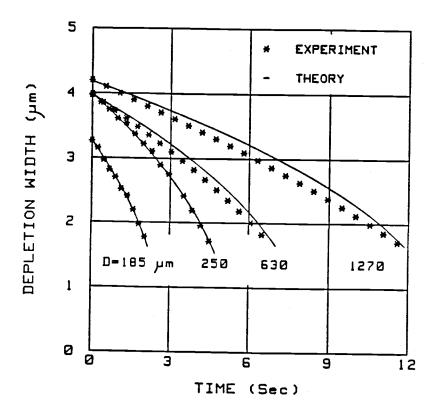

| 49    | Depletion width versus response time of MOS capacitors of different size devices on the same sample (T=70°C)                                               | 107         |

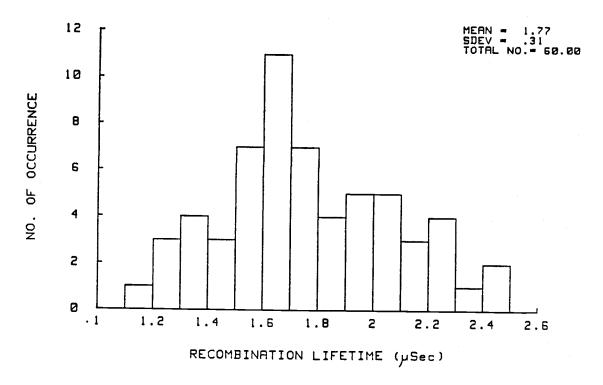

| 50    | Histogram of apparent recombination lifetime data on a 40 $\Omega$ -cm control 13.5 $\mu$ m epitaxial sample                                               | 110         |

| 51    | Histogram of apparent recombination lifetime of a control and a 110 $\mu m$ epi-layer with 35 $\Omega$ -cm resistivity                                     | 110         |

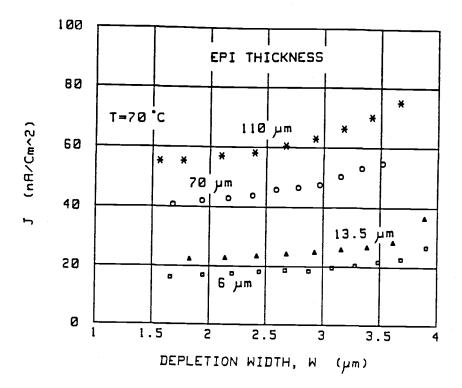

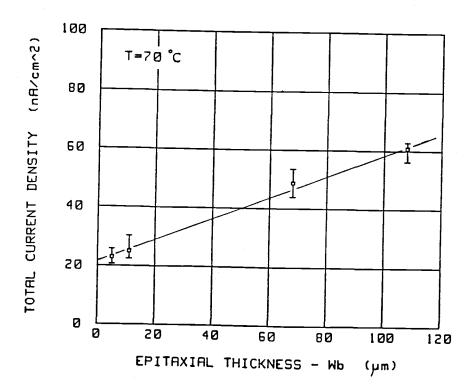

| 52    | Current density versus depletion width for different epitaxial thicknesses measured at T=70°C                                                              | 115         |

| 53    | Current density as a function of epitaxial thickness at T=70°C                                                                                             | 115         |

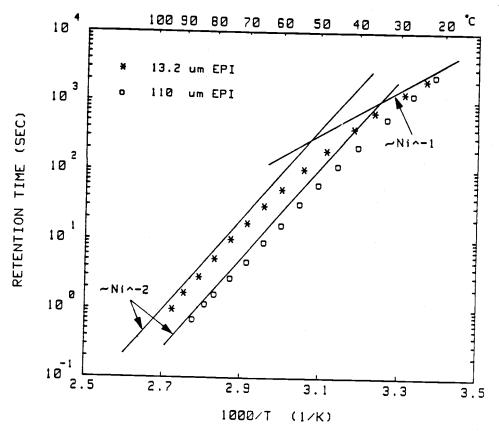

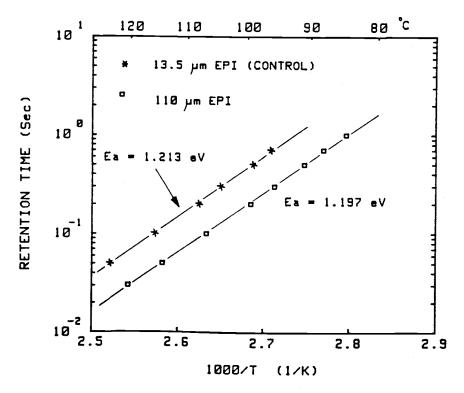

| 54    | Retention time of C-t transient response as a function of inverse temperature for a control and 110 $\mu m$ epi-layer                                      | 118         |

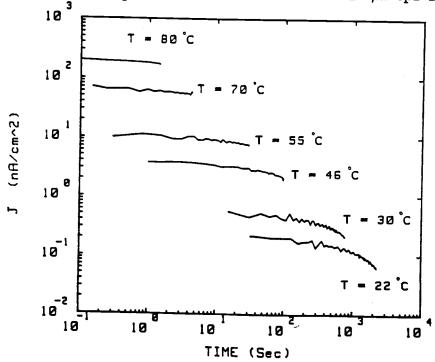

| 55    | Current density as a function of transient response time for various temperatures                                                                          | 118         |

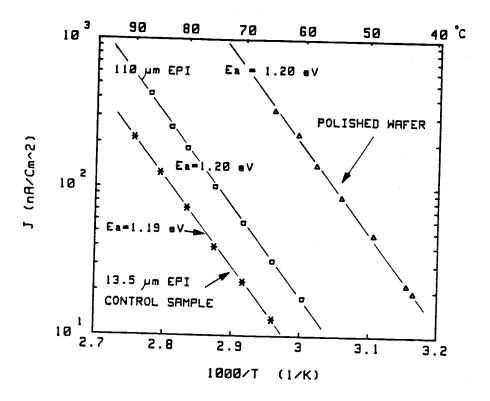

| 56    | Current density as function of inverse temperature                                                                                                         | 119         |

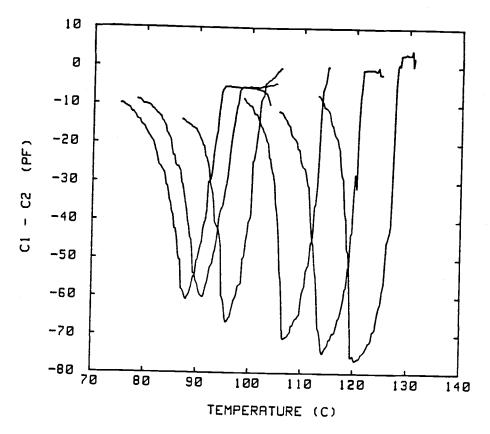

| 57    | a) DLTS signal of a 110 $\mu$ m epi-layer MOS capacitor<br>b) Retention times obtained from<br>figure 57a) for the temperature range of 80 to 130°C        | 121         |

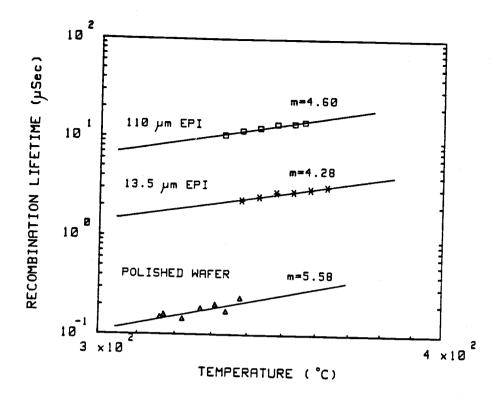

| 58    | Temperature dependence of recombination lifetimes                                                                                                          |             |

| <u>Figur</u> | <u>Title</u>                                                                                                                      | <u>Page</u> |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------|-------------|

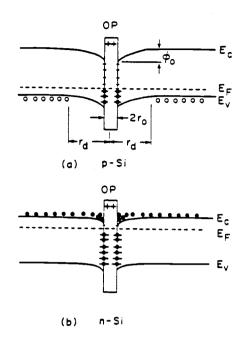

| 59           | A model for oxide precipitates in n- and p-type silicon wafers, after Hwang et al. [62]                                           | 125         |

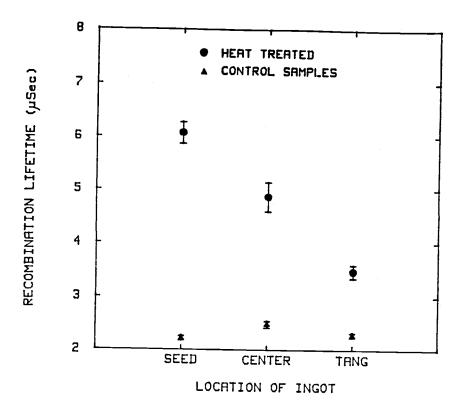

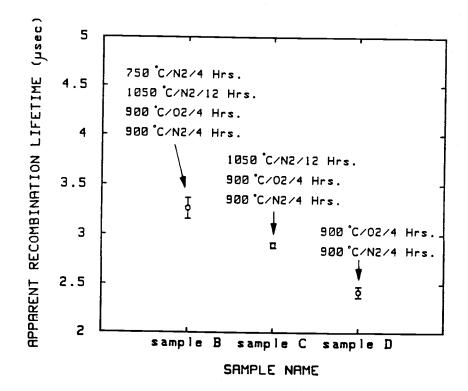

| 60           | Apparent recombination lifetime versus location of ingot for control and heat treated samples                                     | 127         |

| 61           | Apparent recombination lifetime of 13.5 $\mu m$ epi-layers after each heat treatment step of a two atep intrinsic gettering cycle | 127         |

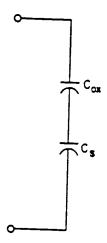

| 62           | High frequency equivalent circuit of an MOS capacitor                                                                             | 145         |

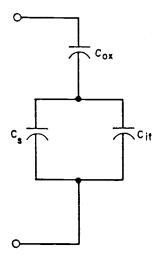

| 63           | Low frequency equivalent circuit of an MOS capacitor                                                                              | 147         |

## LIST OF TABLES

| <u>Table</u> | <u>Title</u>                                                                             | <u>Page</u> |

|--------------|------------------------------------------------------------------------------------------|-------------|

| 1            | Common minority carrier recombination lifetime measurement techniques                    | 28          |

| 2            | A summary of main wafers used for lifetime and DLTS study                                | 49          |

| 3            | Summary of heat treatments for three samples used for the generation lifetime comparison | 78          |

| 4            | Summary of measured generation lifetimes                                                 | 82          |

| 5            | Summary of measured generation and recombination lifetimes                               | 114         |

# RECOMBINATION AND GENERATION LIFETIME CHARACTERIZATION OF p/p + EPITAXIAL SILICON WAFERS

#### I. INTRODUCTION

Since the invention of integrated circuits the technology trends have always been focused on size and especially toward faster speeds of electronic devices. With the recent development of 32 microprocessors, clearly the issue of speed remains the main goal of the future electronic industry. These systems clearly require large amounts of information stored in dynamic memories, commonly used in various electronic devices, to be handled more efficiently. refresh time, which is the minimum time interval required for refreshing a dynamic storage device without loss of information, very important in dynamic memories. The advantages of simple operation and small geometry of dynamic memories have to compromised with intelligent and expensive circuits to refresh the memory circuits. Refreshing of memory circuits is a time consuming process causing a loss of computing time, so it is desired to have very long refresh times to increase computing time and have faster circuits. Imperfections or defects present in silicon material, best characterized by carrier lifetimes, strongly influence the refresh time of dynamic memories.

Prior to the invention of field-effect transistors, most semiconductor devices were minority carrier operated. The gain of bipolar transistors and their switching times are dependent on minority carrier transport across the base. The leakage current of

p-n junctions is also dependent on minority carrier lifetime. Solar cells rely on efficient transport of minority carriers. Although metal oxide semiconductor (MOS) devices and Schottky diodes are majority carrier devices, the minority carrier lifetime plays an important role in the leakage current of these devices. The refresh time of dynamic random access memories (DRAM's) and efficient operation of charge coupled devices (CCD's) are also strongly dependent on lifetime of the material.

In recent years, a thin layer of lightly doped silicon deposited on a heavily doped substrate by a chemical vapor deposition process known as epitaxial deposition has attracted advanced bipolar and MOS technologies. Epitaxial silicon offers an improved active layer quality, free from the defects normally observed in bulk Czochralski silicon, and results in increase in yield and device performance. Epitaxial silicon wafers have superior lifetimes since a heavily doped substrate limits the diffusion current collected by a space charge region in the lightly doped layer. Naturally, dynamic charge storage devices such as DRAM's and CCD's benefit by substituting the initial material from polished wafers to epitaxial wafers. However, technology trends are constantly pushing toward reduced impurities in the material or higher generation and recombination lifetimes. It is necessary to establish an understanding for the material limitations of epitaxial silicon by means of electrical characterization for very large scale integration (VISI) and ultra large scale integration (ULSI) applications.

The main goal of this study is characterization of generation and recombination lifetimes of  $p/p^+$  epitaxial wafers and a basic

understanding of factors which limit the lifetimes in epitaxial material. It is shown that surfaces and interfaces are primarily responsible for generating minority carriers causing a significant reduction in apparent or measured generation and recombination lifetimes. Deep level Transient spectroscopy (DLTS) measurements indicates no significant deep levels present in the p-type epitaxial layers and proper accounting of surface generation using modified Zerbst technique [3] reveals extremely long actual lifetimes for the p-type epitaxial layer. From the study of epitaxial wafers with various epitaxial thicknesses the epi-layer - substrate interface is identified as a source of generation of a significant number of minority carriers causing low apparent recombination lifetimes. In addition, properties of recombination lifetime of p/p+ epitaxial wafers such as temperature dependence of  $au_{r}$  and possible sources causing the reduction of apparent lifetimes are investigated in this work.

The generation lifetime in silicon is determined from the thermal emission rate of generated carriers within a space charge of a device due to the trap levels present within the bandgap. The generation lifetime measured at room temperature, is very sensitive to the energy of impurities or defects within the silicon bandgap. The generation lifetime samples a volume limited to the space charge region which is usually of the order of a few microns from the surface. This measurement is commonly used for characterization of a material or process. In contrast, the recombination lifetime is relatively insensitive to the position of energy levels of impurities or defects. The depth sampled by the recombination lifetime is a

material property and is typically tens to hundreds of microns. At elevated temperatures (60-100°C) or higher which is a more realistic representative of device operating conditions, the diffusion process, characterized by a recombination lifetime, dominates over the generation within the space charge region. In contrast to various reports in the literature on generation lifetimes, recombination lifetimes are seldom reported in the evaluation of epitaxial wafers. Although, as a first order evaluation of the material quality the properties of the active region of a device are of main concern, the effects of recombination lifetime in any dynamic charge storage device especially at normal device operating temperatures is inevitable. The current understanding of lifetime limitations, especially recombination lifetime on epitaxial wafers, is very limited.

Even though generation and recombination lifetimes in silicon are inverse processes, the physical conditions under which they apply are quite different, resulting in values which differ by a large amount. The pulsed MOS capacitor technique or its variations have been well established for generation lifetime measurements. On the other hand, numerous techniques are available to characterize the recombination lifetime of a material or a device. The photoconductive decay method, surface photo voltage, reverse recovery technique, open circuit voltage decay, pulse MOS capacitor, and admittance techniques are some of many existing techniques for recombination lifetime evaluation. When one wishes to study lifetime it appears logical to adapt the measurement technique and test structure similar to the device and application.

A brief review of available lifetime measurement techniques and effects of oxygen precipitation behavior and intrinsic gettering on lifetimes is discussed in the next chapter. In order to appropriately evaluate the lifetimes on high quality epitaxial wafers the existing lifetime techniques have been replaced or modified (Chapter II and The measurement technique and test structures used in this study were kept simple to avoid complications or introduction of secondary defects. MOS capacitors for investigation of generation and recombination lifetime properties of p/p epitaxial silicon wafers and Schottky barrier diodes for deep level transient spectroscopy (DLTS) measurements were fabricated. The test capacitors and Schottky diodes were fully characterized to meet the acceptance criteria prior to further lifetime or DLTS study as described in Chapter IV. recombination lifetime characterization is discussed separately in Chapter V. The main emphasis in this study is the recombination lifetime properties of starting p/p<sup>+</sup> silicon material identification of factors limiting lifetime values. Contribution of interface between p<sup>+</sup>-substrate and the lightly doped epitaxial layer is examined by recombination lifetime measurements. For the first time, the size dependence of the test structures and effects of epitaxial thickness on the recombination lifetime of p-type epitaxial material has been studied.

## II. BACKGROUND AND LIFETIME MEASUREMENT TECHNIQUES

The continuous trend towards smaller geometry and higher performance of semiconductor devices demands improved process control and more importantly, starting material free from defects and imperfections. The lifetime in semiconductors is a measure of material quality. Generation lifetime characterizes the active region of a device while recombination lifetime which is different in principle, is a measure of the bulk property of a material. Various techniques have been used to characterize lifetimes prior or subsequent to high temperature processing during device fabrication. The work described herein is mainly restricted to evaluation of p/p<sup>†</sup> epitaxial silicon wafers used as starting material for many technologies such as CMOS or bipolar.

In this chapter, the theoretical background used for the measurements and characterization in the following chapters is developed. The first section deals with the general recombination - generation processes in semiconductors, the generation lifetime measurment techniques, the Zerbst formulation for evaluation of generation lifetime using pulsed MOS capacitors, and a discussion of the maximum possible recombination and generation lifetimes in silicon. Assessment of the recombination lifetime using the pulsed MOS (Metal Oxide Semiconductor) capacitor technique is discussed in the second section, followed by a brief development of the Deep Level Transient Spectroscopy (DLTS) technique. In addition, a brief discussion on effects of intrinsic gettering on lifetimes are

described in the last section.

#### A. RECOMBINATION - GENERATION PROCESSES

There are three main recombination - generation mechanisms in semiconductors namely, the Shockley-Read-Hall (SRH), radiative, and Auger. The recombination rate R for minority carrier electrons in a p-type semiconductor depends on the number of excess carriers  $\delta n$  which can be written as [4]

$$R = A(\delta n) + B(\delta n)^{2} + C(\delta n)^{3}$$

(1)

where A, B, C are constants which depend on the individual process. The recombination lifetime,  $\tau_{r'}$  is defined to be the number of excess carriers divided by the recombination rate  $(\delta n/R)$

$$1/\tau_{r} = A + B(\delta n) + C(\delta n)^{2} = 1/\tau_{srh} + 1/\tau_{rad} + 1/\tau_{Auger}$$

(2)

In a SRH process, recombination is completed via intermediate energy levels within the bandgap which act as "stepping stones" [5] in the transition of electrons and holes between the conduction and valence bands. Radiative recombination is a band to band process; therefore, both electrons and holes must be present simultaneously for the recombination to take place. Thus the radiative recombination is inversely proportional to the number of excess carriers,  $\delta n$ . In Auger recombination, energy is given to a third carrier (either an electron or a hole) and the lifetime is inversely dependent on  $(\delta n)^2$ .

The Auger process is most important at high temperatures [6] and only under high level injection conditions. Radiative recombination is normally the dominating process in the direct band gap semiconductors like GaAs. SRH recombination is the dominant recombination-generation process in indirect bandgap semiconductors such as silicon. Generation of carriers at room temperature is due to the inverse SRH process shown in Fig. 1. Since both electron and hole emission processes must take place to complete the inverse SRH process, intermediate trap levels located around the midgap are the most effective recombination-generation centers within the bandgap. Trap levels close to the valence or conduction bands are inefficient recombination-generation centers since the probability of either an electron emission or hole emission is very low.

The free carrier lifetime in a semiconductor is the time required for the free carrier concentration in the bulk semiconductor to return to thermal equilibrium after a disturbance from equilibrium has occurred. When the system is driven out of equilibrium both the majority and minority carrier concentrations changes from their thermal equilibrium values. Depending on the reduction or increase of the carrier concentration after a transient, equilibrium will be reached by generation or recombination process, respectively. If the minority carriers dominate the majority carriers in establishing the return to equilibrium, then the lifetime is determined by the lifetime of the minority carriers. At room temperature, the minority carriers actually determine the lifetime of silicon wafers by a thermal emission process which is sensitive to the position of the energy level of defects or impurities present in the material. The

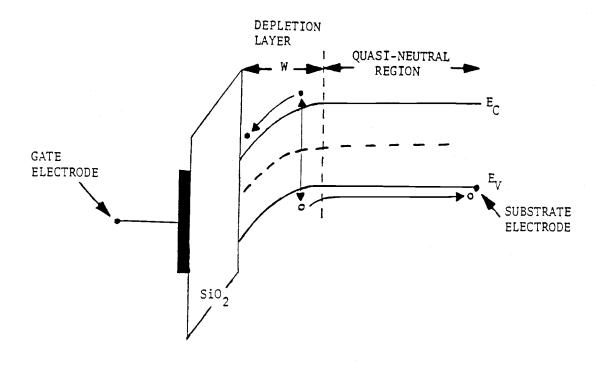

Figure 1) Generation within the space charge region corresponding to inverse SRH recombination process for p-type silicon.

term lifetime implies that an entity ceases to exit. However, in the generation process carriers are being continuously generated instead of being destroyed. It may seem surprising that this process is described by a lifetime, but none the less it is described as a generation lifetime and is a very useful parameter in device behavior.

## 1. Recombination vs. generation lifetime

Of the three main recombination - generation processes discussed in Section A1, the Shockley - Read - Hall process is the dominant

process in silicon. From the theory of the SRH process [7], the recombination rate of electron - hole pairs is given by

$$R = \frac{(pn - n_i^2)}{\tau_{po}(n + n1) + \tau_{no}(p + p1)}$$

(3)

$$\tau_{\text{no}} = 1/(\sigma_{\text{n}} v_{\text{th}} N_{\text{T}})$$

,  $\tau_{\text{po}} = 1/(\sigma_{\text{p}} v_{\text{th}} N_{\text{T}})$  (4)

where nl and pl are the number of electrons and holes in conduction and valence bands when the Fermi level coincides with trap energy, n and p are free carrier concentrations of electrons and holes,  $\tau_{\rm no}$  and  $\tau_{\rm po}$  are the electron and hole lifetimes respectively,  $n_{\rm i}$  is the intrinsic carrier concentration,  $v_{\rm th}$  is the carrier thermal velocity,  $\sigma_{\rm n}$  and  $\sigma_{\rm p}$  are electron and hole capture cross sections, and  $N_{\rm T}$  is the trap concentration. In the following, the recombination and generation lifetimes,  $\tau_{\rm r}$  and  $\tau_{\rm g}$  are discussed using the pulsed MOS capacitor technique within the SRH framework.

At elevated temperatures diffusion from the bulk silicon is the dominant process in relaxation to equilibrium in pulsed MOS capacitors. The reason is simply because the diffusion process (shown in Fig. 2 is a function of the number of minority carriers ( or  $\alpha$   $n_i^{\ 2}$ ) while the generation within the space charge region (Fig. 1) is proportional to  $n_i$ . The diffusion process is characterized by a diffusion length or a recombination lifetime,  $\tau_r$ . For quasi - neutral bulk generation (diffusion process) in a pulsed MOS capacitor the minority carrier concentration changes significantly, but the majority carrier concentration changes by a negligible amount. In general, the concentration of electrons under the non-equilibrium

Figure 2) Diffusion from the bulk at elevated temperature dominates the generation within the space charge region.

condition is given by  $n=n_0^-\delta n$  and for holes by  $p=p_0^-\delta p$ , where  $n_0$  and  $p_0$  are the equilibrium concentration of electrons and holes and  $\delta n$  and  $\delta p$  are the deficient concentrations due to the pulsed condition. The number of reduced carriers is assumed to be the same  $(\delta n=\delta p)$  when the number of deep level traps is much smaller than majority carrier concentration. The concentration of majority carriers does not change significantly, therefore,  $p=p_0$  and for a p-type sample  $p_0>>\delta n, n_0$ . Furthermore, for the pulsed capacitance condition, the free carrier electron concentration becomes negligible (n=0). Therefore, the recombination rate using Eqn. (3) results in

$$R \approx \frac{-p_0 \delta n}{\tau_{po}(n_0 - \delta n + n1) + \tau_{po}(p_0 + p1)} .$$

(5)

For trap centers whose energy level is close to  $E_i$ ,  $p_o>>pl,nl$  so the recombination rate reduces to

$$R \approx \frac{-\delta n}{\tau_{no}} = -(\frac{n_i^2}{N_a})\frac{1}{\tau_{no}} = -(\frac{n_i^2}{N_a})\frac{1}{\tau_r}$$

(6)

The negative sign in Eqn. (6) indicates a generation process due to quasi - neutral bulk generation (diffusion). Consequently, the recombination lifetime of the material is equal to the minority carrier (electron) lifetime  $(\tau_r = \tau_{ro})$ .

For evaluation of the generation lifetime,  $\tau_{\rm g}$ , consider Eqn. (3) with the concentration of electrons, n, and holes, p, to be essentially zero within the space charge region. Writing n1 and p1 in term of the trap energy level, Eqn. (3) becomes

$$R = \frac{-n_{i}}{\tau_{po} \exp[-(E_{i}-E_{T})/KT] + \tau_{no} \exp[-(E_{T}-E_{i})/KT]} = \frac{-n_{i}}{\tau_{q}} .$$

(7)

The generation lifetime,  $\tau_{g'}$  defined in Eqn. (7) can be written as [4]

$$\tau_{\rm g} = 2\tau_{\rm r} \left(\sigma_{\rm n}/\sigma_{\rm p}\right)^{0.5} \cos \left[ \left(E_{\rm T}-E_{\rm i}\right)/{\rm KT} + \ln \left(\sigma_{\rm n}/\sigma_{\rm p}\right)^{0.5} \right] . \tag{8}$$

Equation (8) clearly shows that the generation lifetime is a strong function of the location of the trap level and also depends on the capture cross section of electrons and holes. Note that  $\tau_{\rm q}$  can be

much larger than  $\tau_{\rm r}$  (= $\tau_{\rm no}$ ) if the trap energy level is not at the midgap or if the electron capture cross sections are much larger than holes.

The volume sampled by the recombination lifetime is quite different than the generation lifetime. For the recombination lifetime the sampled volume is determined by the minority carrier diffusion length, which is a material property. However, in the generation lifetime the sampled volume is limited by the space charge region. In high-quality silicon materials the minority carrier diffusion length is normally greater than 50 or 100  $\mu \rm m$  while the depletion region sampled in  $\tau_{\rm g}$  measurements is on order of a few microns. The generation lifetime is an important parameter in charge coupled devices, and in establishing the refresh time of dynamic RAM's. The recombination lifetime is an important factor in determining the switching time of bipolar devices, the leakage current of p-n junctions, and I²L devices in bipolar technology.  $\tau_{\rm r}$  is also very important at normal operating temperatures for any dynamic charge storage device.

## 2. Generation lifetime measurement techniques

Many papers have been published dealing with the non-equilibrium pulsing a MOS capacitor from accumulation to deep depletion. The capacitance-time (C-t) transient technique involving a voltage step applied to a metal-insulator-semiconductor structure was introduced by Zerbst [3] and was further analyzed in more detail by Heiman [8]. The generation lifetime of the material is obtained from a time

derivative of the C-t response. Inversion to deep depletion pulsing was investigated by Hofstein [9]. Later Schroder [10,11] identified a significant component of C-t transient current due to lateral surface effects or lateral surface generation velocity, resulting in a reduction of the effective or measured generation lifetime. Zerbst technique and a simple model developed by Schroder which incorporates the surface effects are discussed in detail in the next section. Pierret [12,13] has described and refined a technique using a linear voltage ramp to maintain a constant capacitance for measurement of the generation lifetime,  $au_{\mathbf{q}}$ . This method permits direct evaluation of  $au_{q}$  from the slope of a plot of various applied voltage ramp rates versus the measured depletion layer width. Contrary to the time derivative calculation of the C-t response required for  $au_{

m q}$  evaluation in the Zerbst technique, Pierret's procedure provides a simple means for the evaluation of  $\tau_{_{\mathrm{Cl}}}$ . However, the experimental setup for this procedure is more complex compared to the Zerbst technique and it suffers from the breakdown in thin oxides due to the high voltages required during the voltage ramp. Lin [14] introduced a double-sweep C-V technique for determination of the generation rates and the doping concentration in non-uniform doping profile devices.

The retention time, defined as the time for return to the inversion capacitance after application of a voltage step, is extremely long [15] in high quality silicon materials. Care must be taken in the interpretation of the results [16]. Numerous modifications to the original Zerbst technique have been reported [15,17,18,19] to reduce the measurement time of generation lifetimes.

It has been shown that by pulsing from inversion to deep depletion and taking the C-t data over a small portion of transient response,  $au_{_{\mathbf{Q}}}$  can be evaluated in much shorter times without any information loss. This is discussed in detail in Chapter III. Recently, Keller [18] reported a rapid measurement based on establishing intermediate capacitance values by means of voltage pulses and calculating the time derivative in an identical fashion to the Zerbst technique, but only for short times. This method is similar to that discussed and used for the  $\tau_{\rm q}$  measurement in Chapter III [15], except various voltage pulses are employed rather than a single voltage step. Although this method may be more complex for routine evaluations,  $\tau_{\rm cr}$ values can be obtained in about 10% of the total retention times. Fahrner et al. [19] investigated a technique which involves an increase in the measurement temperature to speed up the measurements. As pointed out by Schroder [11], for high quality silicon wafers the quasi-neutral bulk generation starts to become important at lower temperatures when compared to the space charge generation. Therefore, while increasing the temperature may reduce the measurement time, the accuracy of  $\tau_{\rm g}$  using such a technique is questionable. Furthermore, they assumed that the bulk generation is independent of the depletion layer thickness. This assumption does not hold for short base width devices [2] namely  $p/p^+$  epitaxial wafers used in this study. Recently, Radzimski et al. [20] reported analysis of MOS capacitor Ct data that enables a plot of the generation lifetime as a function of depletion layer width which is useful for non-uniform lifetime characterization.

## 3. Generation lifetime using a pulsed MOS capacitor

The MOS capacitor is the most widely used structure for assessing the Si-SiO<sub>2</sub> interface and the quality of the bulk silicon. Measurements of the generation lifetime is possible by operating the MOS capacitor in a non-equilibrium mode (known as a pulsed MOS capacitor) introduced by Zerbst [3]. The Zerbst technique or its various modifications [15,17,18,19] have been commonly used for generation lifetime measurement. The generation lifetime is a very important parameter in monitoring deep level defects caused by interstitial or substitutional impurities in silicon which cause a degradation in performance of DRAM's and CCD's.

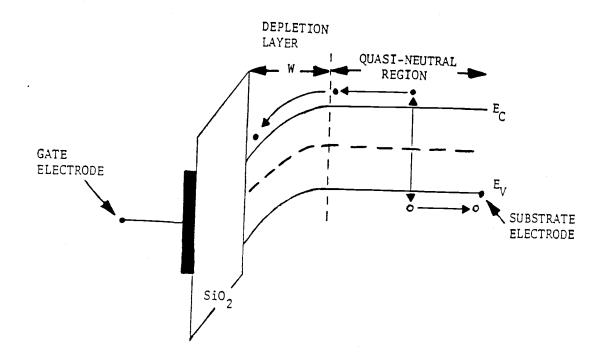

In the pulsed MOS capacitor measurement, the capacitor is pulsed from an accumulation to a deep depletion while monitoring the capacitance as a function time. The observed transient in the gate voltage results from formation of a deep depletion layer under the gate electrode causing the capacitor to be in a non - equilibrium condition. The gate voltage is kept at a fixed value until the capacitance returns to its equilibrium or inversion capacitance, Figure 3 shows four processes contributing to relaxation to equilibrium: 1) generation of carriers within the space charge region with a generation lifetime,  $\tau_{q'}$  2) surface generation, S, of the surface under the gate , 3) lateral surface generation,  $S_0$ , from the surface of depletion region, and 4) diffusion process from the bulk silicon characterized by a recombination lifetime,  $\tau_{\rm r}$ . The diffusion contribution is normally negligible at room temperature (diffusion at elevated temperatures is discussed in section B).

Figure 3) Schematic representation of a pulsed MOS capacitor showing the four carrier generation mechanisms involved in relaxation to equilibrium.

In the pulsed MOS capacitor technique, the surface generation, S, is a maximum immediately after the transition from accumulation to deep depletion. Because the surface under the gate electrode quickly becomes inverted while the lateral surface remains depleted immediately after the pulse. Once an inversion layer is formed, traps at the SiO<sub>2</sub> - Si interface become filled, thereby, reducing surface generation under the gate electrode. After the gate bias transient, S decreases rapidly while the lateral surface generation remains constant. As time progresses, the depletion width contracts and an equilibrium inversion layer is eventually formed. The period in which the capacitance relaxes back to C<sub>inv</sub> is known as retention time.

The Zerbst's relation, commonly used for the evaluation of  $au_{m{q}'}$

is derived here. From Gauss's law, the oxide field is proportional to the net charge per unit area [21]

$$C_{ox}[V_{g} - \phi_{s}(t)] = q[N_{I}(t) + \int_{0}^{W(t)} N(x) d(x)]$$

(9)

where  $\phi_{\rm S}(t)$  is the instantaneous band bending, W(t) is the depletion width, N<sub>I</sub>(t) is the instantaneous inversion layer density, N(x) is the doping density at position x, and C<sub>ox</sub> the oxide capacitance in F/cm<sup>2</sup>. Differentiating Eqn. (9) with respect to time for a constant gate voltage after the pulse and assuming uniform doping concentration results in

$$\frac{dN_{I}}{dt} = -\frac{C_{OX}}{q} \frac{d\phi_{S}}{dt} - N_{a} \frac{dW}{dt} . \qquad (10)$$

The space charge layer, in terms of the measured capacitance, is given by:

$$W(t) = \epsilon_{si} \text{ Area } [1/C(t) - 1/C_{ox}]$$

(11)

where C(t) is the measured high frequency capacitance, and  $\epsilon_{\rm si}$  the permittivity of silicon. Neglecting the voltage drop across the inversion layer [21], the rate of change of the band bending becomes

$$d\phi_{s}/dt = q/\epsilon_{si} W(t) N_{a} dW/dt$$

(12)

and with the use of Eqn. (10,11, and 12) the rate of change of the inversion layer density becomes

$$\frac{dN_{I}}{dt} = -\frac{c_{ox}}{c(t)}N_{a} \epsilon_{si} \frac{d}{dt} \left(\frac{1}{c(t)} - \frac{1}{c_{ox}}\right) = -\frac{N_{a}}{2} \frac{\epsilon_{si}}{\epsilon_{ox}} T_{ox} \frac{d}{dt} \left(\frac{c_{ox}}{c(t)}\right)^{2}. (13)$$

Equation (13) is a general relation between the rate of change of the inversion layer density and the rate of change of depletion layer width. Zerbst's analysis assumes that the rate of change of the inversion layer density or generation rate is linearly proportional to the depletion layer width,

$$dN_{I}/dt = n_{i}/\tau_{q} (W - W_{f})$$

(14)

where  $W_{\rm f}$  is the final (equilibrium) depletion width. The rate  $n_{\rm i}/\tau_{\rm g}$  is the value used in the steady state analysis of reverse biased p-n junctions. Schroder and Nathanson [10] have shown that the rate of change of inversion layer density, taking the surface generation and the extended space charge region into account, gives

$$dN_{I}/dt = n_{i}/\tau_{g} (W - W_{f}) + n_{i} S A_{G}/A + n_{i} S_{O} (W - W_{f}) P/A$$

(15)

where  $A_{\mathbb{C}}$  is the area of the gate, A is the area of the gate plus the lateral surface area shown in Fig. 3, P is the perimeter of the gate, and  $W_{\mathbf{f}}$  is the final depletion width. For simplicity, Schroder assumes that the lateral and longitudinal width of the space charge regions are the same. This is a fairly good first order approximation. For a circular gate of diameter D, Eqn. (15) simplifies to

$$\frac{dN_{I}}{dt} \approx n_{i} (W - Wf) \left[ \frac{1}{\tau_{g}} - \frac{4S}{D} + \frac{4S_{o}}{D} \right] + n_{i} S$$

(16)

for  $t>0^+$  on the C-t curve, S is much smaller than  $S_0$ , so the (4S/D) term in Eqn. (16) may be neglected. Using the Eqn. (13 and 16) we obtain

$$-\frac{d}{dt} \left[ \frac{c_{ox}}{c(t)} \right]^2 = 2 \frac{n_i}{N_a} \left[ \frac{c_{ox}}{c_{inv}} \left( \frac{c_{inv}}{c_{ox}} - 1 \right) \frac{1}{\tau'} + \frac{\epsilon_{ox}}{\epsilon_{si}} \frac{s}{T_{ox}} \right]$$

(17)

where  $\tau'_{g}$  is the effective generation lifetime defined by

$$1/\tau'_{g} = 1/\tau_{g} + 4S_{o}/D$$

(18)

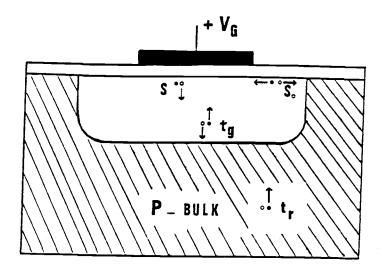

Equation (17) is the Zerbst relation which relates the capacitance from the C-t curve to the generation lifetime and surface generation velocity. If the left hand side of Eqn. (17) is plotted versus  $C_{\rm inv}/C_{\rm ox}$  - 1, the slope of the linear portion of this plot is inversely proportional to the effective generation lifetime and the intercept to an average surface generation velocity, S. By plotting the transient capacitance as shown in Fig. 4, the bulk generation may be separated from surface generation and diffusion from the bulk silicon. The Zerbst plot is equivalent to a plot of current density, J, versus the depletion layer change, W-W<sub>f</sub>. The following relations show how current density, J, and W-W<sub>f</sub> are related to C(t) data.

$$J = -q \frac{N_a}{2} \frac{\epsilon_{si}}{\epsilon_{ox}} T_{ox} \frac{d}{dt} \left[ \frac{c_{ox}}{c(t)} \right]^2$$

(19)

Figure 4 a) Pulsed MOS capacitor C-t response, and b) Zerbst plot. The slope of linear portion of such a plot results in the generation lifetime and its intercept in an average surface generation velocity.

$$W - W_{f} = (1/C - 1/C_{inv}) \epsilon_{o} \epsilon_{si} Area .$$

(1)

Collins and Churchill [22] have shown that the Eqn. (14) is not completely adequate for the non-equilibrium analysis of pulsed MOS capacitors since the rate is taken from a steady state analysis. Their exact analysis reveals that the generation region is initially

linearly dependent on W-W<sub>f</sub>, but as time progresses it becomes smaller than W<sub>f</sub>. Figure 5 is a plot of J versus W-W<sub>f</sub> (or a Zerbst plot) showing that  $q \, dN_{\rm I}/dt$  drops faster as W-W<sub>f</sub> reaches zero. Collins's explanation for a more rapid drop of  $dN_{\rm I}/dt$  is that mobile carriers encroach the depletion layer at small W-W<sub>f</sub>. In general, a Zerbst plot provides an approximate straight line, provided that the doping profile is uniform and the time interval for the measurement capacitance is chosen appropriately for evaluation of time derivative of  $d/dt \, \left( c_{\rm OX}/C(t) \right)^2$ .

Although, theoretically it is possible to extract the generation lifetime from the linear portion of the Zerbst plot, even when there is significant bulk diffusion or surface generation, in reality the

Figure 5) Rate of change of inversion layer density per area versus  $W-W_{\mbox{\it f}}$ , after Collins et al. [22].

interpretation of the transient response in such a case is cumbersome. To examine the bulk generation lifetime of a device, the surface generation S, and especially the lateral surface generation,  $S_{\rm O}$ , must be minimized (Eqn. (18)). It was demonstrated [9] that the surface generation can be reduced significantly if instead of an accumulation-inversion voltage pulse, an inversion to strong inversion voltage pulse is used. With this technique the contribution of interface traps is minimized by pulsing from inversion to stronger inversion since the majority of interface traps have already been filled throughout the pulse, resulting in smaller surface generation contribution.

### 4. Maximum possible generation - recombination lifetimes in silicon

The recombination and generation lifetimes of pure silicon, completely free of defects and impurities provide an upper limit of what may be expected for a high-quality material. For a perfect silicon sample without any deep levels, the dominant process of recombination is via the radiative process. The maximum possible lifetime for the doping densities used in this study is approximated in the following using the radiative process. The Van Roosbroeck-Shockley relation [23] states that the rate of optical generation of electron - hole pairs equals the radiative recombination rate at equilibrium. Therefore, the emission rate at a frequency v in an interval dv is given by

where P(v) is the probability per unit time of absorbing a photon of energy hv, and  $\Omega(v)d(v)$  is the density of photons. From Planck's radiation law [24] the density of photons is written as

$$\Omega(v) dv = 8\pi v^2 (n/c)^3 \left[ \exp(hv/KT) - 1 \right]^{-1} dv$$

(22)

The absorption probability is equal to inverse of mean lifetime  $\tau\left(\mathbf{v}\right)$  of the photon

$$P(v) = 1/\tau(v) \tag{23}$$

Since the mean lifetime is proportional to the mean free path,  $1/\alpha(v)$ , and the velocity of photon Eqn. (21) becomes

$$R(v)d(v) = \frac{8\pi v^2 n^3 dv}{c^3 \left[ \exp(hv/KT) - 1 \right]} . \tag{24}$$

The total number of recombinations per second per unit volume becomes

$$R = \frac{8\pi n^2}{c^2 h^3} \int \frac{\alpha (hv)^2 d(hv)}{\exp (hv/kT) - 1} .$$

(25)

In order to estimate the integral in Eqn. (25) the absorption coefficient as a function of frequency, hv, must be known. Since only an order of magnitude of maximum lifetime is of interest, a simple approach was considered for evaluation of Eqn. (25) as follows. The

Figure 6) Measured absorption coefficient for pure Ge, Si, and GaAs, after S.M. Sze [25].

absorption coefficient curve of silicon as a function of hv was broken into four sections and a power law fit was made to each section. Figure 6 shows the measured absorption coefficients for pure Ge, Si, GaAs, and the simple power law fit for Si. Using this approximation for  $\alpha(hv)$ , the integral of Eqn. (25) was evaluated numerically using Simpson's rule in the range of 1.1 eV to 10 eV at room temperature which resulted in a recombination rate of about

$1 \times 10^5$  cm<sup>-3</sup>sec<sup>-1</sup>. For a doped silicon sample the maximum generation or recombination lifetime is given by [26]

$$\tau = n_i^2 / (R N_a) \tag{26}$$

where  $N_a$  is the doping concentration of the p-type material. For the doping density of the epitaxial layer used in this study  $(3-5x10^{14} \text{ cm}^{-3})$ , the maximum generation or recombination lifetime was calculated to be about 0.45 sec. A recombination lifetime of 0.47 sec has been calculated by Dumke [27] for spontaneous radiative recombination of silicon for a doping density of  $10^{15} \text{ cm}^{-3}$ . Blakemore [26] and Pankove [28] have reported 0.3 sec and 0.5 sec lifetimes for ideal silicon with concentrations of  $10^{15} \text{ cm}^{-3}$ .

This is an extreme upper limit of the lifetime expected in silicon material. In reality, either deep level traps or surface effects would dominate the radiative recombination process resulting in orders of magnitude lower measured lifetimes.

#### B. RECOMBINATION LIFETIME

Different recombination mechanisms were briefly discussed in Section A. In this section, subsequent to the recombination lifetime measurement techniques, evaluation of the recombination lifetime using the pulsed MOS capacitor technique is discussed.

## 1. Recombination lifetime measurement techniques

A comprehensive review of recombination mechanisms is given by Bruevich [29] with a summary of electron and hole capture cross sections and recombination lifetime values for various impurities in silicon and germanium. As mentioned in the previous chapter, numerous measurement methods for evaluation of the minority carrier recombination lifetime,  $\tau_{r'}$  exist and only a brief introduction is given here.

Table 1. gives a summary of some common minority carrier recombination lifetime measurement techniques. The reverse recovery time method [30,31] and open circuit voltage decay are measured on a p-n junction diode structures. Injection level and trapping problems are fairly common for these techniques. Use of a p-n junction is avoided in this work to eliminate the possibility of introducing another impurity. Optical methods on bulk material such as the photoconductive decay measurement [32,33,34] and the surface photovoltage technique [35] are also common. Proper optical setup of these measurements could be rather involved. In the photoconductivity

| Method                              | test<br>structure                            | measurement<br>parameter   | disadvantage                                                                 | Ease of<br>measurement       | Ref.    |

|-------------------------------------|----------------------------------------------|----------------------------|------------------------------------------------------------------------------|------------------------------|---------|

| Reverse<br>recovery<br>time         | pn<br>Junction                               | I-t                        | Injection level<br>& trapping<br>problems                                    | simple                       | [30,31] |

| Open<br>circuit<br>voltage<br>decay | pn<br>Junction                               | voltage<br>decay           |                                                                              |                              |         |

| Photo<br>conduct-<br>ivity<br>decay | bulk<br>material                             | conductance<br>decay       | DC light must<br>saturate traps<br>or injection<br>problems occur            | involved<br>optical<br>setup | [32-34] |

| Surface<br>photo<br>voltage         | capacitance<br>probe or<br>Schottky<br>diode | voltage<br>vs.<br>1/α      | voltage & 1/a<br>may have<br>non-linear<br>relation                          | complex<br>setup             | [35]    |

| Pulsed<br>MOS<br>capacit-<br>ance   | MOS<br>capacitor                             | capacitance<br>vs.<br>time | elevated temp.,<br>two dimensional<br>effects for short<br>base width device | simple                       | [1,2]   |

Table 1. Common minority carrier (recombination) lifetime measurement techniques.

decay technique, the recombination lifetime is evaluated from the conductance decay and in the surface photovoltage technique from a plot of the voltage versus inverse absorption coefficient  $(1/\alpha)$ . Also, the small signal admittance method is used on pn junctions and npn or pnp transistors for measurement of the diffusion length and surface recombination velocity in thin semiconductor layers [36,37]. In addition, from the amplitude or phase shift of the frequency dependence of the short-circuit photocurrent in a Schottky contact illuminated by intensity modulated light, the minority carrier lifetime,  $\tau_{\rm r}$ , can be evaluated [38]. Recently, Spirito et al. [39]

reported a conductivity modulated technique using a lateral pn diode for  $au_{r}$  profile in thin epitaxial layers. Schröder et al. showed that  $\tau_{

m r}$  and hence the diffusion length of a material may also be obtained by using a pulsed MOS capacitor at elevated temperatures. Even though an MOS capacitor is a zero injection device and the recombination of carriers does not take place,  $\tau_{

m r}$  is evaluated from the quasi-neutral bulk generation (or diffusion process) which is the dominant mechanism in C-t relaxation to equilibrium at elevated This technique uses the same MOS capacitor test temperatures. structure and measurement setup as the Zerbst method for the  $\tau_{\alpha}$ measurements; therefore, it is more favorable than other techniques. The pair of  $au_{ extsf{q}}$  and  $au_{ extsf{r}}$  values using the pulsed MOS capacitor technique reflect both near surface (active region of a device) and bulk properties of the substrate using a common test structure and processing conditions. The recombination lifetime measurement technique used in this study [2] is a modification of Schroder's method accounting for lateral and time dependent quasi-neutral bulk generation for short base width devices. This is discussed in detail in next section and Chapter III.

# Recombination lifetime of short base width devices using pulsed MOS capacitance technique

Schroder et al. [1] have described a simple method for the determination of the recombination lifetime on silicon wafers using the pulsed MOS capacitor technique at elevated temperatures of 70 - 100°C. This technique relies on the dominance of the quasi-neutral

bulk generation (diffusion current) over the space charge and surface generation at elevated temperatures. The technique is summarized in the following. The rate of change of the space charge region W(t) in a pulsed MOS capacitor is given by [3,8]

$$\left(1 + \frac{\epsilon_{\text{ox}}}{\epsilon_{\text{si}}} \frac{W}{T_{\text{ox}}}\right) \frac{dW}{dt} + \frac{1}{N_{\text{a}}} \frac{J_{\text{total}}}{q} = 0$$

(27)

where  $\epsilon_{\rm ox}$  and  $\epsilon_{\rm s}$  are the dielectric constants of oxide and silicon,  $T_{\rm ox}$  the oxide thickness,  $N_{\rm a}$  the doping concentration,  $J_{\rm total}$  the total current density contributing to relaxation to equilibrium and q the charge of the electron. At elevated temperatures, quasi-neutral bulk generation dominates and a plot of  $1-(C_{\rm i}/C)^2$  versus time gives a straight line [1]. The slope is related to an effective diffusion length,  $L'_{\rm n}$  as follows:

Slope =

$$\left(\frac{C_{\underline{i}}}{C_{ox}}\right)^2 \left(\frac{n_{\underline{i}}}{N_a}\right)^2 \left(\frac{\epsilon_{ox}}{\epsilon_s}\right) \left(\frac{2}{T_{ox}}\right) \left(\frac{D_n}{L_n'}\right)$$

(28)

where  $C_i$  is the initial capacitance after the pulse,  $C_{ox}$  the oxide capacitance,  $n_i$  the intrinsic concentration at the measured temperature,  $D_n$  the diffusion coefficient of electrons (for a p-type sample).

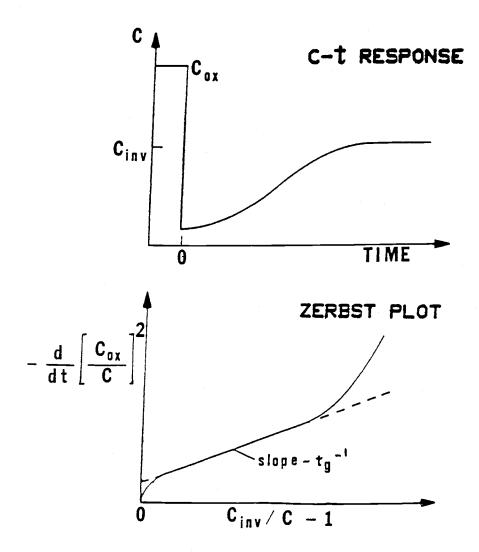

Schroder's technique of measuring the recombination lifetime works well for long base width polished silicon wafers, but it is shown below that it is not appropriate for short base width samples. This simple approach ignores the lateral quasi-bulk generation and

Figure 7) Cross sectional view of a short base width device on p/p<sup>+</sup> epitaxial silicon. Minority carriers generated within one diffusion length in the lateral direction contribute to the lateral current. The volume of generated carriers (diffusion) under the gate is limited by the epitaxial thickness and the time-dependent space charge width.

the time dependence of the width of the space charge region, W, in short base width devices. Consequently, calculations using Schroder's technique indicate that the recombination lifetime is a function of device diameter. These factors are discussed in the following. Figure 7 shows a cross section of a  $p/p^+$  epitaxial wafer where a quasi- neutral bulk current is generated one diffusion length away from the depletion region edge laterally and is bounded by the epitaxial thickness. This can be best treated as a two dimensional problem (assuming a uniform recombination lifetime within the

epitaxial layer). However, for simplicity a simple one dimensional approach is proposed [2] in which bulk generation in the lateral area of the device is taken into consideration, resulting in a fairly uniform recombination lifetime which is independent of device diameter for short base width devices.

The total current contributing in the relaxation to equilibrium due to quasi-neutral bulk generation in a pulsed MOS capacitor at elevated temperatures for a circular structure may be approximated by simply adding the lateral current contribution to the bulk diffusion under the space charge region as follows

$$J_{\text{total}} = q \frac{n_i^2}{N_a} \frac{D_n}{L_n^2} (W_B - W(t)) + q \frac{n_i^2}{N_a} \frac{D_n}{L_n} (\frac{4W_B}{D})$$

(29)

where  $W_B$  is the base width, W(t) the depletion region width,  $I_n$  the diffusion length, and D the device diameter. The first term in Eqn. (29) is due to the carriers generated within region defined by the epitaxial layer -  $p^+$  substrate interface and the edge of the depletion region under the gate electrode. The time dependence of W is included in this term. The second term is the lateral current component, assuming the minority carriers are generated within one diffusion length,  $I_n$ , from the space charge edge. The term  $(4W_B/D)$  in Eqn. (29) is a correction factor which results from normalizing the cross sectional area of the lateral current component  $(\pi DW_B)$  to the area of the MOS capacitor  $(\pi D^2/4)$ . Due to the  $p/p^+$  built in field, generation at this interface is normally assumed to be zero  $(S_{pp+}=0)$ . If this generation is not zero, the recombination lifetime assuming

no interface generation would be an apparent rather than the actual lifetime of the epi-layer. Substituting Eqn. (29) in (27) results in the following solution:

$$(1 - \frac{\epsilon_{\text{ox}}}{\epsilon_{\text{si}}} \frac{U}{T_{\text{ox}}}) \ln \left| \frac{W_{i}^{+U}}{W^{+U}} \right| + \frac{\epsilon_{\text{ox}}}{\epsilon_{\text{si}}} \frac{1}{T_{\text{ox}}} (W_{i}^{-W}) = -(\frac{n_{i}^{2}}{N_{a}^{2}} \frac{D_{n}}{L_{n}^{2}}) t$$

$$U = -W_{B} (1 + 4L_{N}/D)$$

(30)

where  $W_i$  is the initial depletion width just after the voltage pulse. Equation (30) predicts how the depletion region changes as a function of time for a pulsed MOS capacitor at elevated temperatures. All of the parameters in Eqn. (30) can be measured or evaluated for a given transient response except for the diffusion length,  $L_n$ , which may be found as follows. The initial and final values of the space charge region  $W_i$  and  $W_f$  and the final time (retention time),  $t_f$ , may be obtained from the C-t response at elevated temperatures. All of the capacitor parameters in addition to its diameter size are substituted into Eqn. (30) and  $L_h$  is solved iteratively using the secant method. Subsequently, the value of  $L_h$  is substituted back in Eqn. (30) and a W-t plot is created for comparison to the measured transient response (this is shown later).

# C. DEEP LEVEL TRANSIENT SPECTROSCOPY (DLIS)

#### 1. Capacitance DLTS

Capacitance DLTS is a transient technique [41] which is used for characterization of trap levels present within the bandgap of a semiconductor. The capacitance transient technique [42] is widely used for studying traps within the depletion region of a Schottky barrier or a p-n junction diode. Analysis using DLTS normally allows evaluation of the trap type (majority or minority carrier trap), energy level of the trap, capture cross section, and the trap concentration.

Figure 8 [41] is a schematic diagram of emission and capture process of an arbitrary trap in a p-type material. el, e2, cl, and c2 represent the electron emission, hole emission, electron capture, and hole capture, respectively. The observable traps are within the depletion region of the device. Therefore, the capture rates are zero since the concentration of electrons and holes are essentially zero in the space charge region. Thus, all deep levels act as traps since the recombination cannot occur in the space charge region. The simple rate equation of Fig. 8 shows the transient to be an exponential function of time with a rate el + e2. Normally one of these rates dominates. An increase in trapped minority carriers causes an increase in the junction capacitance. Thus, the capacitance transient is always positive for a minority carrier trap while a majority carrier has a negative capacitance transient. Figure 9 [41]

Figure 8) Schematic diagram of the emission and capture processes for an arbitrary trap level and capacitance transient of that trap in p-type material, after D.V. Lang [41].

indicates the capacitance transient and the required pulse sequence used to produce the transient for a) minority carrier trap and b) majority carrier trap in a p-n<sup>+</sup> junction diode. Band bending is omitted for simplicity.

The emission rate of a trapped carrier is determined by Boltzmann statistics and is an exponential function of the lattice temperature, T, and the activation energy of the trap,  $E_A$ . For a p-

Figure 9) Pulse sequence which is used to produce a capacitance transient for a) minority carrier trap and b) majority carrier trap for a pn junction, after D.V. Lang [43].

type semiconductor the emission rate of electrons,  $\boldsymbol{e}_{n^{\prime}}$  is given by

$$e_n = \sigma_n v_{th} N_C \exp (-E_A/KT)$$

(31)

where K is Boltzmann constant,  $\sigma_{\rm n}$  is the minority carrier capture cross section,  $v_{\rm th}$  is the electron thermal velocity, and  $N_{\rm C}$  is the effective density of states of conduction band. The activation energy is defined as the energy separation between the conduction band and the trap level. A semi-log plot of emission rate normalized by the square of the temperature  $(T^2)$  versus the inverse temperature is called an Arrhenius plot. The product of thermal velocity and density of states in Eqn. (31) has a temperature dependence of  $T^2$ . Therefore, the reason for division by  $T^2$  in the Arrhenius plots is to remove the temperature dependence of the pre-exponential term. In general, the capture cross section is also temperature dependent, and care must be taken when interpreting deep levels with known strong temperature dependent of capture cross sections. The activation energy of a trap can be obtained from the slope of this plot and the capture cross section from the intercept.

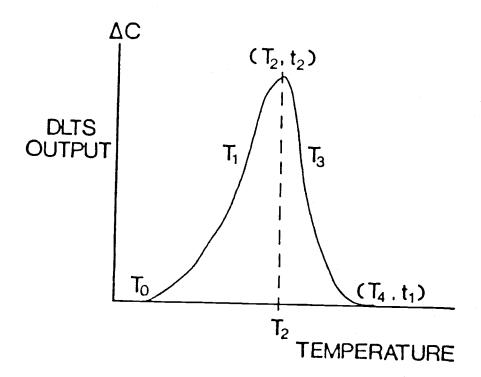

One way of analyzing the exponential capacitance is by sampling the transient at two different times  $t_1$ , and  $t_2$  using a boxcar integrator. Figure 10 [41] shows a schematic diagram of how a capacitance transient changes as a function of temperature. On the right hand side of Fig. 10, the DLTS signal is shown which results from the difference between the capacitance at time  $t_1$  and  $t_2$  plotted as a function of temperature. The normalized capacitance change (normalized DLTS signal) at these two times is written as

Figure 10) Schematic representation of various temperatures which corresponds to DLTS signal resulting from a double boxcar integrator, after D.V. Lang [41].

$$S(T) = (C(t_1) - C(t_2))/\delta C(0)$$

(32)

Where  $\delta C(0)$  is the capacitance change at the beginning of the pulse (t=0). For an exponential transient the normalized DLTS signal is  $S(T) = \exp(-t_1/\tau_C) - \exp(-t_2/\tau_C)$ . Where,  $\tau_C$ , is the time constant defined as the reciprocal of the sum of electron and hole emission rates ( $\tau_C = 1/(e_n + e_p)$ ). The maximum DLTS signal occurs when

$$\tau_{c} = (t_2 - t_1) / \ln(t_2 / t_1)$$

(33)

Since  $t_1$  and  $t_2$  are fixed parameters of the boxcar integrator the corresponding  $\tau_{\rm C}$  or emission rate can be calculated using Eqn. (33). The emission rate corresponding to a peak in the DLTS thermal scan gives a single data point for an Arrhenius plot. The thermal DLTS scan must be repeated for various time constants,  $\tau_{\rm C}$ , or the emission rates by changing the rate window  $t_1$  and  $t_2$  to be able to obtain an adequate Arrhenius plot for evaluation of the activation energy and capture cross section of a trap. The concentration of a trap is related to the DLTS peak height by the following relation [41]