#### AN ABSTRACT OF THE THESIS OF

<u>Jaewon Yoo</u> for the degree of <u>Master of Science</u> in <u>Electrical and Computer Engineering</u> presented on <u>June 4, 2008</u>.

Title: <u>Side Channel Attack Resistant Elliptic Curves Cryptosystem on Multi-cores for Power Efficiency</u>

| Abstract approved: |         |  |  |

|--------------------|---------|--|--|

| 11                 | Ben Lee |  |  |

The Advent of multi-cores allows programs to be executed much faster than before. Cryptoalgorithms use long-bit words thus parallelizing these operations on multi-cores will achieve significant performance improvement. However, not all long-bit word operations in cryptosystems are suitable for parallel execution on multi-cores. In particular, long-bit words used in Elliptic Curves Cryptography (ECC) do not efficiently divide by the system word size. This causes some of the cores to be idle, which makes it vulnerable for attackers to guess how many operations occurred and thus what field size is being used.

Multiplication is the most important part of public key cryptosystems. Long-bit word multiplication operations are needed for encryption and decryption. J. Fan et al. proposed using Montgomery multiplication on multi-cores using  $GF(2^{256})$  [25, 26], which is suitable for computer systems with 16-bit or 32-bit word size. Fan's Montgomery multiplication is suitable for most RSA. However, in ECC, some GFs will cause idle cores. For example, suppose  $GF(2^{131})$  is used (which is one of the recommended word size by NIST) on a quad-core with a 32-bit word size, which requires  $\lceil 132/32 \rceil = 5$  iterations with the last iteration requiring just a 3-bit operation. This cause three of the cores to be idle during this time causing needless power consumption. The most general and the easiest way to make side channel attacks difficult is to insert dummy in-

structions to cover the idle processors. However, dummy instructions result in extra workloads that lead to performance degradation and increases in power consumption.

In this thesis, we will present a multiplier adjuster technique to improve the execution time and the power consumption for the last unbalanced iteration. By appropriately applying dummy instructions between point-addition and point-doubling operations, a balanced point operation can be achieved in ECC. The performance and power-efficiency of the proposed method on multi-cores are analyzed for each GF used in ECC.

©Copyright by Jaewon Yoo June 4, 2008 All Rights Reserved

# Side Channel Attack Resistant Elliptic Curves Cryptosystem on Multi-cores for Power Efficiency

by Jaewon Yoo

#### A THESIS

submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Master of Science

Presented June 4, 2008 Commencement June 2009

| Master of Science thesis of <u>Jaewon Yoo</u> presented on <u>June 4, 2008</u>                                                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                 |

|                                                                                                                                                                                 |

| APPROVED:                                                                                                                                                                       |

|                                                                                                                                                                                 |

|                                                                                                                                                                                 |

| Major Professor, representing Electrical and Computer Engineering                                                                                                               |

|                                                                                                                                                                                 |

|                                                                                                                                                                                 |

| Director of the School of Electrical Engineering and Computer Science                                                                                                           |

|                                                                                                                                                                                 |

|                                                                                                                                                                                 |

| Dean of the Graduate School                                                                                                                                                     |

|                                                                                                                                                                                 |

|                                                                                                                                                                                 |

|                                                                                                                                                                                 |

|                                                                                                                                                                                 |

|                                                                                                                                                                                 |

| I understand that my thesis will become part of the permanent collection of Oregon State University libraries. My signature below authorizes release of my thesis to any reader |

| upon request.                                                                                                                                                                   |

|                                                                                                                                                                                 |

| Jaewon Yoo, Author                                                                                                                                                              |

#### **ACKNOWLEDGEMENTS**

Thanks God!

I wish to express my gratitude to Professor Ben Lee, my advisor, for his encouragement, insightful guidance and patience throughout my MS degree at OSU.

I also want to extend great appreciation to Professor Huaiping Liu, Traylor Roger, and John A. Nairn for their serving in my graduate committee.

I want to thank my country Korea, Korean Air Forces, and Defense Security Command for giving chance to study and fully supporting me in USA. In Specially, DSC and  $2^{nd}$  Service Department for patience about my studies for the last two years.

Finally, I express my deepest appreciation and love to my father, Youngkun Yoo, and my mother, Yangsun Oh, who have been encouraging, caring, and praying for my whole life. I also express my thanks to my God parent, Hubert and Maris Böwer, and his family. In special, I would like to express my deepest gratitude to my wife, Hyeking Jeon who has shown endless patience and love. She supported me fully with victimizing her important period in her life. I thank very much my daughter, Siyeon Yoo for well-breeding with health and happiness.

Thanks Everybody Jaewon Yoo

## TABLE OF CONTENTS

|                                                 | <u>Page</u> |

|-------------------------------------------------|-------------|

| 1 Introduction                                  | 1           |

| 2 Cryptography                                  | 4           |

| 2.1 Symmetric Key Cryptography                  | 4           |

| 2.2 Public Key Cryptography                     | 5           |

| 2.3 Hybrid Cryptography                         | 6           |

| 2.4 Example of Crypto-algorithm                 | 7           |

| 2.4.1 Data Encryption Scheme (DES)              | 7           |

| 2.4.2 Rivest, Sharmir, and Adleman (RSA) Scheme | 10          |

| 2.4.3 Elliptic Curve Cryptography (ECC)         | 13          |

| 3 Background                                    | 16          |

| 3.1 Mathematic Tools Used in Cryptosystem       | 16          |

| 3.1.1 Fundamental Mathematical Operation        | 16          |

| 3.1.2 Addition Chain                            | 22          |

| 3.1.3 Montgomery's Method                       | 25          |

| 3.1.4 Chinese Reminder Theorem (CRT)            | 26          |

| 3.1.5 Euclid's Algorithm                        | 27          |

| 3.1.6 Projective Coordinate                     | 28          |

| 3.2 Power Model                                 | 29          |

| 3.2.1 Power Reduction of Circuit Level          | 31          |

| 3.2.2 Power Reduction of Architectural Level    | 31          |

| 3.2.3 Power Reduction of Software Level         | 32          |

# TABLE OF CONTENTS (Continued)

|                                                       | <u>Page</u> |

|-------------------------------------------------------|-------------|

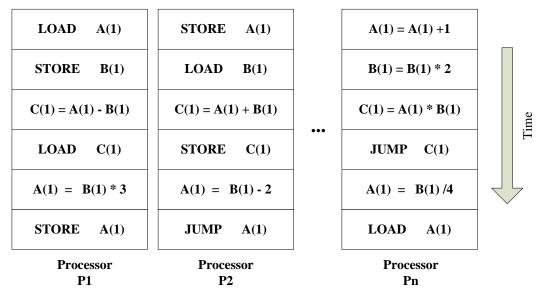

| 3.3 Parallel Computing Architectures                  | 32          |

| 3.3.1 Single Instruction, Single Data (SISD)          | 34          |

| 3.3.2 Single Instruction, Multiple Data (SIMD)        | 34          |

| 3.3.3 Multiple Instruction, Single Data (MISD)        | 35          |

| 3.3.4 Multiple Instruction, Multiple Data (MIMD)      | 36          |

| 4 Side Channel Attack (SCA)                           | 37          |

| 4.1 SCA Methods                                       | 37          |

| 4.1.1 Timing Analysis                                 | 37          |

| 4.1.2 Power Analysis                                  | 38          |

| 4.1.3 Mircro-architecture Analysis                    | 39          |

| 4.2 SCA Countermeasures                               | 40          |

| 4.2.1 CM for Timing Analysis                          | 41          |

| 4.2.2 CM for Power Analysis                           | 42          |

| 4.2.3 CM for Mircro-architecture Analysis             | 44          |

| 5 Related Work                                        | 46          |

| 5.1 Montgomery Multiplication on Mutli-cores          | 46          |

| 5.2 Montgomery Multiplication in $GF(2^k)$            | 48          |

| 5.3 Projective Coordinates in $GF(2^k)$               | 48          |

| 6 The Proposed Method                                 | 51          |

| 6.1 Parallel Implementation of modular multiplication | 54          |

| 6.2 Inserting Dummy Instruction                       | 58          |

| 6.3 Multiplier Adjuster                               | 60          |

# TABLE OF CONTENTS (Continued)

|                             | <u>Page</u> |

|-----------------------------|-------------|

| 7 Simulation Study & Result | 62          |

| 7.1 Simulation Environment  | 62          |

| 7.2 SESC API                | 64          |

| 7.3 Simulation Methods      | 67          |

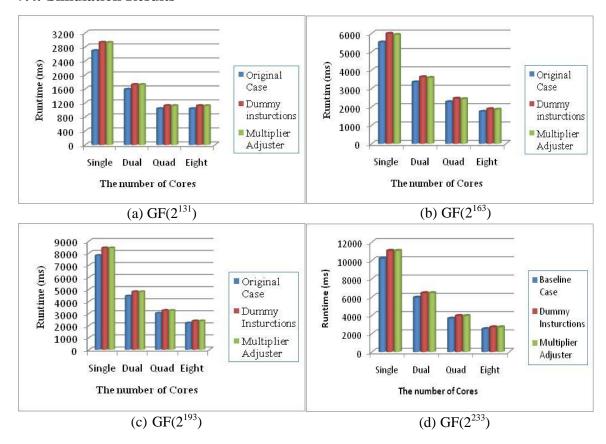

| 7.4 Simulation Results      | 68          |

| 8 Future work & Conclusion  | 72          |

| Bibliography                | 73          |

## LIST OF FIGURES

| <u>Figure</u>                                                                    | <u>Page</u> |

|----------------------------------------------------------------------------------|-------------|

| 1. Symmetric Key Cryptosystem.                                                   | 5           |

| 2. Public Key Cryptosystem                                                       | 6           |

| 3. Hybrid Cryptosystem                                                           | 7           |

| 4. Architecture of DES                                                           | 8           |

| 5. E-table and Example of bits extension                                         | 10          |

| 6. S-box Substitution.                                                           | 10          |

| 7. RSA Scheme                                                                    | 12          |

| 8. Operations in Elliptic Curves over $GF(p)$ and $GF(2^m)$                      | 13          |

| 9. ECC ElGamal Scheme                                                            | 15          |

| 10. Example of Addition in Group $Z_{15}$ and Multiplication in Group $Z_{11}^*$ | 17          |

| 11. Arithmetic Operations of Polynomial Bases.                                   | 19          |

| 12. Binary AD Algorithm.                                                         | 23          |

| 13. Binary SM Algorithm                                                          | 24          |

| 14. MM Algorithm and Example                                                     | 26          |

| 15. Flow of SISD                                                                 | 34          |

| 16. Flow of SIMD                                                                 | 34          |

| 17. Flow of MISD                                                                 | 35          |

| 18. Flow of MIMD                                                                 | 36          |

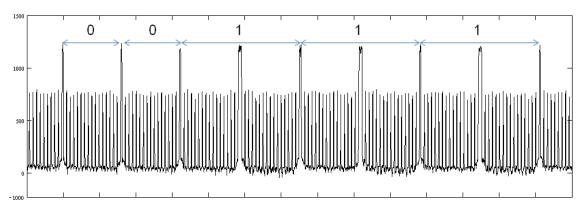

| 19. Power Analysis in RSA                                                        | 39          |

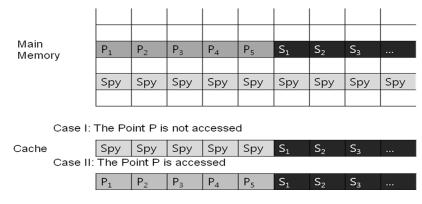

| 20. Cache Analysis                                                               | 40          |

| 21. Dummy Instruction in AD Algorithm                                            | 41          |

| 22. Random instruction in AD Algorithm                                           | 41          |

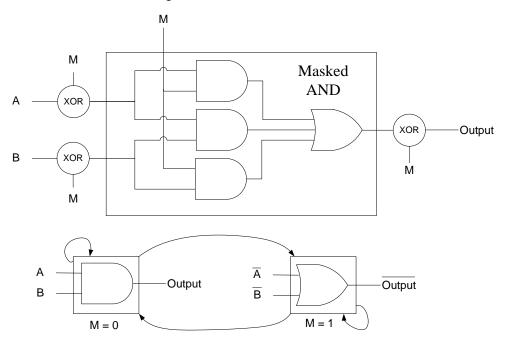

| 23. Masked Gates                                                                 | 42          |

# LIST OF FIGURES (Continued)

| <u>Figure</u>                                                          | <u>Page</u> |

|------------------------------------------------------------------------|-------------|

| 24. MM in <i>GF</i> (2 <sup>n</sup> )                                  | 44          |

| 25. Radix-2 <sup>w</sup> ( <i>n</i> -bit) MM                           | 47          |

| 26. Fan's MM on Multi-cores                                            | 48          |

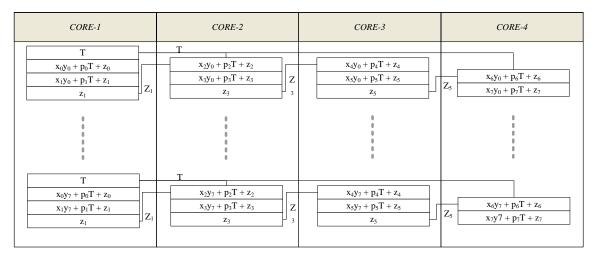

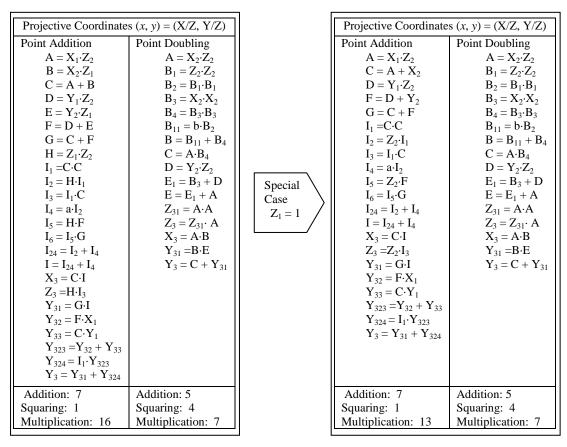

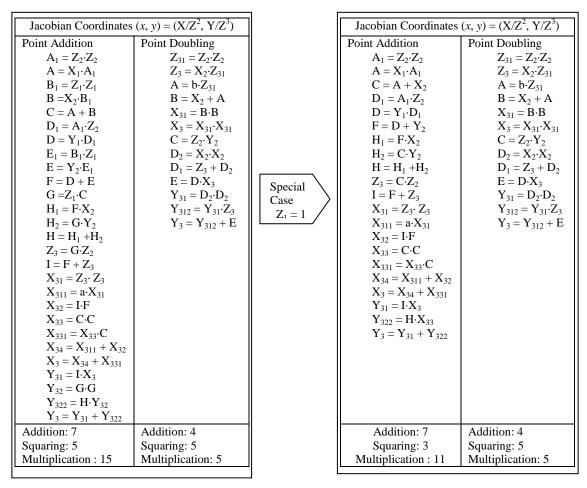

| 27. Projective Coordinates and Mixed Coordinates with Affine Systems   | 49          |

| 28. Jacobian Coordinates and Mixed Coordinates with Affine Systems     | 50          |

| 29. Difference of Elliptic Curve PA and PD                             | 52          |

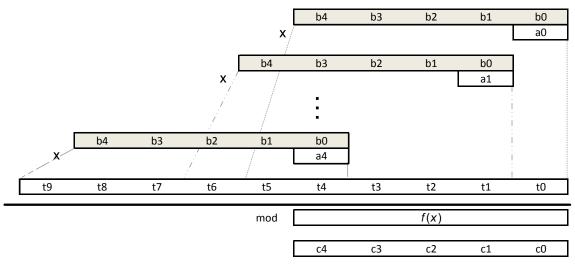

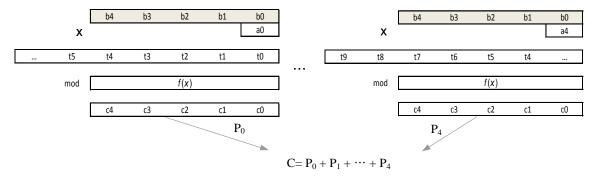

| 30. Multiplication over $GF(2^{131})$ for Word Size 32 bits            | 53          |

| 31. Charateristics of <i>GF</i> s                                      | 53          |

| 32. Original Code – poly_mul( ) & poly_div( )                          | 54          |

| 33. Original Code – poly_mul_partial()                                 | 55          |

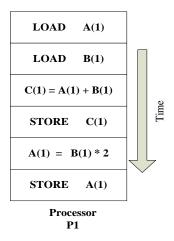

| 34. Conventional MM operation                                          | 55          |

| 35. Parallelizing MM operation                                         | 56          |

| 36. Data Structure – SUB                                               | 56          |

| 37. Modified Code – poly_mul()                                         | 57          |

| 38. Modified Code – poly_sub()                                         | 57          |

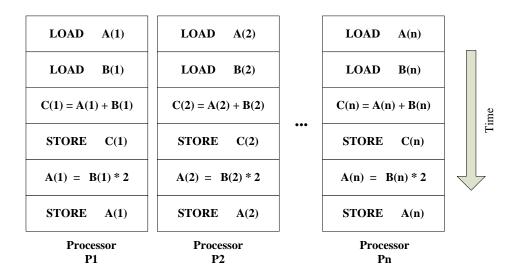

| 39. Low-level Dummy inserting over $GF(2^{131})$ for word size 32 bits | 58          |

| 40. High-level Dummy inserting                                         | 59          |

| 41. Modified Code – Jpoly_edbl()                                       | 60          |

| 42. Multiplier Adjuster                                                | 61          |

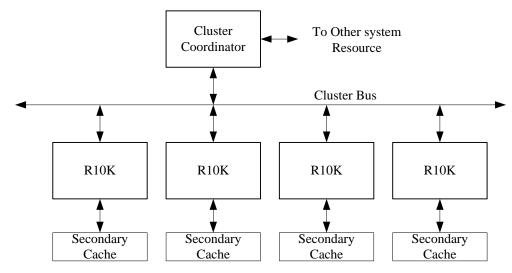

| 43. MIPS 10K Multiprocessor Configuration using Cluster Bus            | 63          |

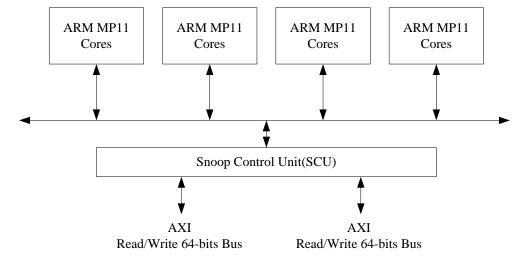

| 44. ARM 11MP Processor Configuration                                   | 63          |

| 45. Configuration File in SESC (sesc.conf)                             | 64          |

| 46. Typical Thread Program                                             | 65          |

# LIST OF FIGURES (Continued)

| <u>Figure</u>                           | <u>Page</u> |

|-----------------------------------------|-------------|

| 47. SESC Version of Threading Program   | 66          |

| 48. Performance of <i>GF</i> s          | 68          |

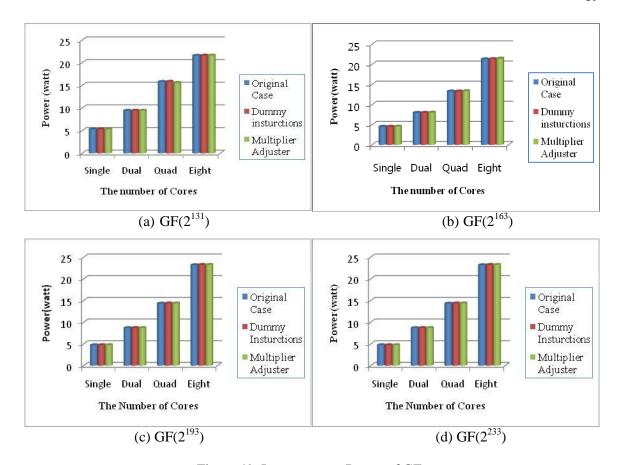

| 49. Instantaneous Power of <i>GF</i> s  | 69          |

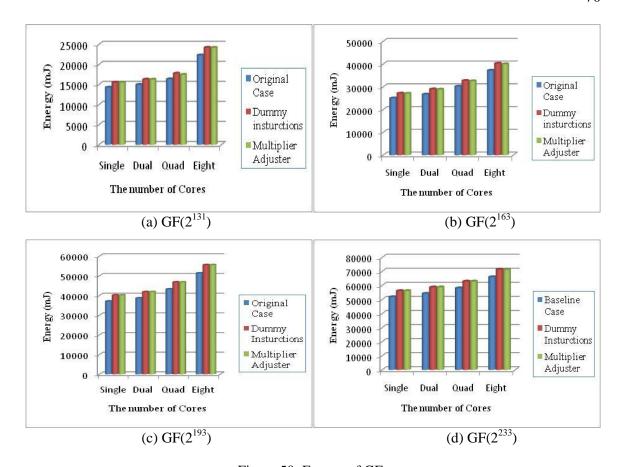

| 50. Energy of <i>GF</i> s               | 70          |

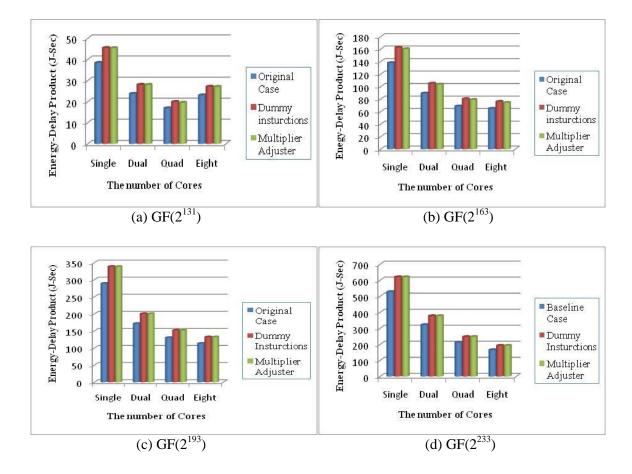

| 51. Energy-Delay Product of <i>GF</i> s | 71          |

## LIST OF TABLES

| <u>Table</u>                                                          | <u>Page</u> |

|-----------------------------------------------------------------------|-------------|

| 1. Multiplication modulo 8 and Occurrences                            | 16          |

| 2. Multiplication mod $f(x)$ where $f(x) = x^3 + x + 1$               | 21          |

| 3. Relationship between Affine Coordinates and Projective Coordinates | 29          |

| 4. The number of field operations on each coordinates systems         | 67          |

### Side Channel Attack Resistant Elliptic Curves Cryptosystem on Multi-cores for Power Efficiency

#### 1. Introduction

Information security has always been an important challenge in our society. Information processing, especially in governments and businesses, requires systems to be secure. Protection of critical information has usually been accomplished using *cryptography*. Cryptography is the science of hiding data from eavesdroppers. On the other hand, eavesdroppers want to find data from systems that use cryptography, which is known as *cryptanalysis* or *attack*. Cryptography and cryptanalysis have an antagonistic relationship. One side hides data, while the other side attacks it. In the age of computers, cryptography has been integrated into computer systems. Accordingly, attacks have been accomplished by observing the computer system.

A cryptosystem is also referred to as a *cipher*. For example, one of the well-known crypto-algorithms can be found in Roman Emperor Caesar's letters for his staff generals. Caesar encrypted his orders by shifting the letters some fixed number of positions further down the alphabet so that only the generals who knew the number of shifts could understand them. In the Second World War, German's used a cipher called Enigma to hide messages from the allied forces. With the advent of the Internet, the importance of privacy and security of personal information has increased. Therefore, people began to use various crypto-algorithms in their computers, hand-held devices, smart cards, etc.

The efforts to hide information have also attracted the efforts to break the cryptosystem. The essence of cryptosystems has traditionally been considered as a kind of a mathematical problem. Making a crypto-algorithm impossible to break is the key to security. Even mathematically immune crypto-algorithms have vulnerability in practical devices, i.e., real computer systems. Ideally, a cryptosystem generates an output with two inputs: *plaintext* and *key*. However, real systems have other inputs and output, such as voltage, current, power consumption and electromagnetic emission. These parameters have been ignored in traditional cryptosystems. However, the concept of a *side channel* has been recently introduced to include physical characteristics of cryptosystems. A side channel is another source of information about the plaintext and key. The cryptosystem can be broken using this side channel information, which is called a *Side-Channel Attack* (SCA). One general method of SCA is performing power and timing analysis, since different operations of a cryptosystem generate different power consumption and execution time characteristics.

In traditional cryptosystems, the fastest cipher was considered the best cipher. However, in 1996, the vulnerability of cryptosystems to SCAs was exposed by Kocher [14] who extracted

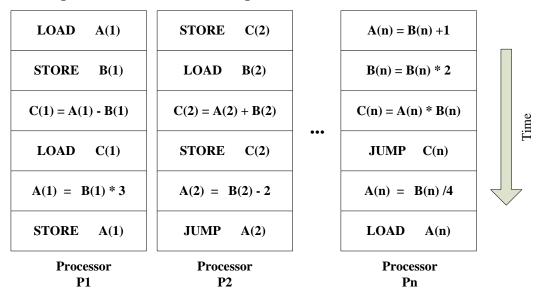

the key value by monitoring the execution time of a cipher. Since then protection from SCA has become one of the major issue in the design of cryptosystems. The general techniques for protecting against SCAs involve masking at the gate-level, inserting dummy instructions, and using regular behaving algorithms [16, 19, 37]. However, most of these research efforts have been performed on a single-core processor. A multi-core processor is a single-chip multiprocessor that contains two or more processors have been attached for enhanced performance, reduced power consumption, and more efficient simultaneous processing of multiple tasks. Multi-core set-up is somewhat comparable to having multiple, separate processors installed in the same computer, but because the two processors are actually merged into the same chip, the connection between them is faster. Ideally, e.g. a dual-core processor is nearly twice as powerful as a single-core processor, and quad-core is four times better than single-core. However, multi-core processors present new software challenges that must be overcome to fully take advantage of processing capabilities to get twice the performance or even more than a single-core processor. Conventional programs do not take into account the capability of multiprocessing, especially in personnel computers or mobile computing devices. Software developers thought that parallel programming is only needed in large companies that require parallel data processing. Thus, small programs, including cryptography programs, used in PCs or mobile devices have been designed for single-core systems.

With the advent of multi-cores, a number of parallel multiplication algorithms have been developed [25, 26]. However, crypto-algorithms use long keywords, e.g., one of the key sizes in ECC is 163-bit. This requires a 163-bit multiplication on multi-cores, which causes uneven distribution of the load. For example, consider an eight-core system with 32-bit processors. Then, 163-bit divided by 32-bit generates six iterations that can be distributed across the cores. However, this causes two of the cores to be completely idle making it vulnerable to SCAs. Therefore, this thesis analyzes the performance and power characteristics of running crypto-algorithms on multi-cores, and develops methodologies to improve the energy-delay product and at the same time protect from SCAs. We proposed arranging the main operation of crypto-algorithm to make it balanced and inserted dummy instructions to fill the gap which is for not accessed data in normal operations. Also, to reduce the overhead from the dummy instructions, we applied a *multip-lier adjuster* for the last iteration in a multiplication operation. Rearrangement of the operation and dummy instructions increased runtime by 7.5% and the energy-delay product (EDP) by 1.5%

on average. This increase reduced to at most a 1.1% and 2.7% overhead for runtime and EDP, respectively.

The thesis organized as follows: Section 2 presents a brief review of some typical cryptosystems with examples: *Data Standard Encryption* (DES), *Rivest-Shamir-Adleman Scheme* (RSA), *Elliptic Curves Cryptography* (ECC). Section 3 presents the background on mathematical tools used in cryptosystems that include *Galois Field* (GF), basic operations in GF, the addition chain and multiplication algorithm. Then a Power model and parallel methods are reviewed. Section 4 introduces the Side channel attack method and defense techniques. In Section 5, related works for this thesis that include multiplication operations on a multi core and projective coordinates. Section 6 shows the proposed method of parallelizing multiplication, inserting dummy instruction and using multiplier adjuster. Section 7 shows the simulation environment, simulation methods, and results for the proposed method. Finally, conclusions are drawn in Section 8.

#### 2. Cryptography

According to Wikipedia, *Cryptography* is the practice and study of hiding information. Until recently, cryptography almost referred exclusively to *encryption*, which is the process of converting ordinary information, called *plaintext*, into meaningless garbage information, called *ciphertext*. Decryption is the reverse process that converts ciphertext to plaintext. The pair of algorithms that performs this encryption and decryption is called a *cipher*, or cryptosystem. The detailed operations of cryptosystems are controlled by both the algorithm and a parameter called a *key*. This is a secret key for a specific message exchange context, and is ideally known only to the communicants.

Cryptosystems can be divided into three groups depending on the types of keys: *Symmetric key* cryptosystem, *public key* (also known as asymmetric key) cryptosystems, and *hybrid* cryptosystems. The first method uses the same key for both encryption and decryption. The second method uses different keys for encryption and decryption. The last method uses the combination of the previous two cryptographic schemes.

The following subsections describe the characteristics of the three algorithms.

#### 2.1. Symmetric Key Cryptography

Until the 1970s, all ciphers were based on *Symmetric Key Cryptography (SKC*). The basic idea was simple – a cipher generates a ciphertext based on an input message and the key. Then, the delivered ciphertext with the same key recovers the original message.

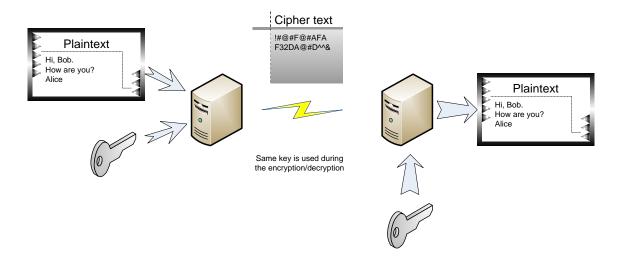

Figure 1 illustrates an example SKC. Suppose Alice wants to communicate securely with Bob. First, Alice and Bob have to meet and share a key to use in the cipher. Then, Alice generates a ciphertext with the message and the shared key and sends it to Bob. When Bob receives the ciphertext, Alice's message is reproduced with the shared key.

Figure 1: Symmetric Key Cryptosystem

#### 2.2. Public Key Cryptography

In SKC, anyone who wants to communicate must share the same key in a secure way; e.g., face-to-face or through a trusted courier. Furthermore, frequent key exchanges are usually required to maintain secure communications. In addition, each user who wants to perform cryptography must have keys for all other users, which makes key management and distribution a major problem. Before World War II, this was not a big problem because only a few people in Government agencies and the military used SKC. Therefore, key management and distribution was not an issue.

However, with advances in technology, the need for secure communication in our society has become essential. Therefore, key management and distribution has become a major challenge for researchers. In order to reduce the side effects of using symmetric keys, Diffie and Hellman introduced the concept of *public key cryptography* (*PKC*) in 1976 [12]. The concept of public key is to use two different keys during encryption and decryption, called a *public key* and a *private key*. Thus, a user who wants to use this scheme needs to notify to others his public key.

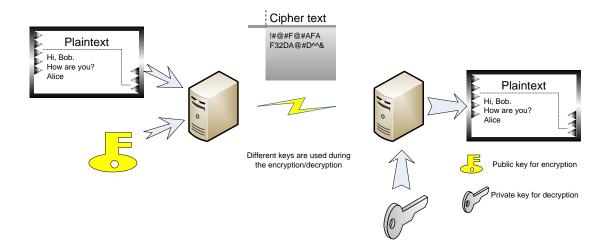

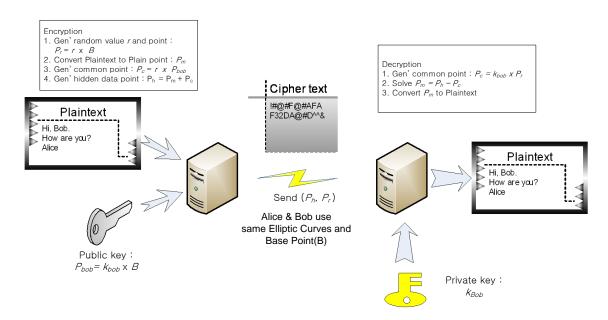

Figure 2 shows an example where Alice wants to send a message to Bob using PKC. Alice first acquires Bob's public key. Then, the message is encrypted to ciphertext using the obtained key and sent to Bob. When Bob receives the ciphertext, it is decrypted to plaintext using Bob's own private key.

Figure 2: Public Key Cryptosystem

#### 2.3. Hybrid Cryptosystem

Both SKC and PKC have advantages and disadvantages. SKC has a high security level and is easy to implement, but key distribution and management is a problem. PKC solves the aforementioned issue in SKC, but has a big shortcoming – the level of security for PKC compared with SKC of the same key size is lower. *Hybrid Cryptosystems* have been introduced to overcome this weakness by implementing key distribution/management as in PKC and encryption/decryption process based on SKC.

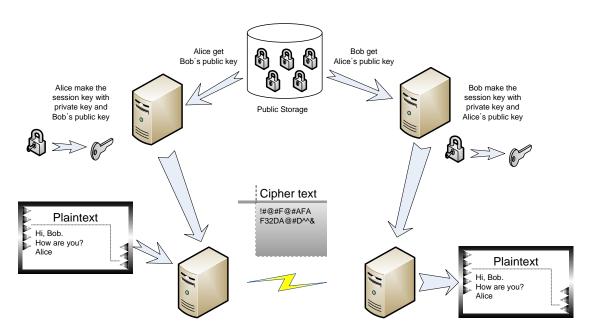

Figure 3 shows an example of a hybrid scheme. First, Alice and Bob generate their own key, called a *session key*, using the PKC scheme. They then exploit the session key with the SKC scheme.

Each user, Alice and Bob, has his or her own private key as same as we saw in the PKC. They need a secret key to operate the system. The secret key must be shared by two parties, i.e., Alice and Bob. However, the secret key is created by the PKC. This key which is created by PKC is called a *session key* in contrast with the normal secret key. Alice gets Bob's public key and then mixes it up with her own private key. Bob also performs the same process with Alice's public key. These key is ideally the same:  $K_{pri\_alice} * (K_{pri\_bob} * Base) = K_{pri\_bob} * (K_{pri\_alice} * Base)$  where  $K_{pri\_alice}$  and  $K_{pri\_bob}$  are their own private key, Base and \* are the shared information and operation, i.e., Base is basic point and \* is scalar multiplication in ECC.

Figure 3: Hybrid Cryptosystem

#### 2.4. Example of Crypto-algorithm

There have been many cryptographic algorithms developed since humans started hiding information. After WWII, most cryptographic applications have been developed for computing environments. This section overviews three modern crypto-algorithms; *Data Encryption Standard* (*DES*), *Rivest-Shamir-Adleman* (*RSA*) scheme, and *Elliptic Curve Cryptography* (*ECC*).

DES is a typical SKC system, while RSA and ECC represent PKC systems.

#### 2.4.1. Data Encryption Scheme (DES)

A team at IBM proposed the DES algorithm [1] in 1975 as a response to the government's needs for secured protection of classified and other sensitive information. DES was adopted in 1977 and became the most widely used encryption scheme. In DES, data is encrypted in 64-bit blocks using a 56-bit key. A plaintext is first divided into 64-bit blocks, and then the blocks are changed bit-by-bit using permutation and substitution, based on subkeys produced from the 56-bit key.

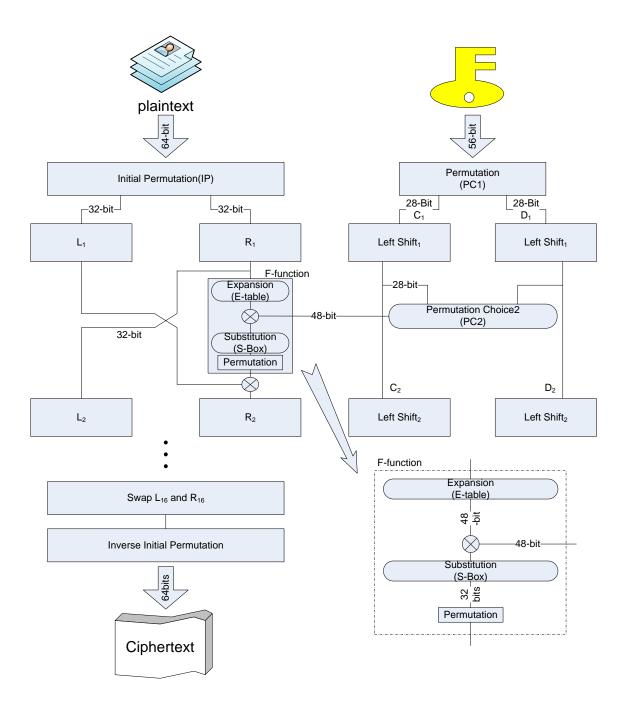

The overall architecture of DES is shown in Figure 4, which accepts a 64-bit block of *plaintext* and a 56-bit *key*. The processing of the plaintext proceeds in three phases; Initial Permutation (IP), 16-Round processing, and Inverse IP. The right-hand portion of Figure 4 shows the way in which the 56-bit key is used. Initially, the 56-bit key is passed through a permutation function, which changes the position of the bits. Then, for each of the 16 rounds, a 48-bit *subkey*

or *roundkey*  $K_i$  is produced by the combination of a left circular shift and a permutation [2, 10, 11]. Based on this, each round obtains a different subkey.

Figure 4: Architecture of DES

Figure 4 also shows the internal structure of a single round. The left  $(L_{i-1})$  and right  $(R_{i-1})$  halves of each 64-bit intermediate value are treated as separate 32-bit quantities. The processing requirement for each round i can be summarized as the following formulas:

$$L_i = R_{i-1}$$

$$R_i = L_{i-1} \oplus F(R_{i-1}, K_i)$$

where the subkey  $K_i$  is 48 bits and  $L_{i-1}$  and  $R_{i-1}$  are 32-bit inputs.  $R_{i-1}$  is then expanded to 48 bits by a predefined extended permutation table (E-table). The extended 48 bits are mixed with the subkey by exclusive-OR and substituted with 32 bits by S-box. Finally, by passing the permutation table, the substituted 32 bit positions are changed into the next  $L_i$  after an exclusive-OR operation with  $L_{i-1}$

The 48-bit subkey is produced by using the 56-bit key as an input and then applying Permuted Choice 1 (PC1), circular left shift (LS), and Permuted Choice 2 (PC2).  $C_{i-1}$  and  $D_{i-1}$  are 28 bits of the left and right sides of the 56-bit key. PC2 chooses 48 bits as a subkey with  $C_i$ = $LS(C_{i-1})$  and  $D_i$ = $LS(D_{i-1})$ . Afterwards,  $C_i$  and  $D_i$  are used as the inputs for the next round processing.

Simply DES gets a 64-bit data, and then divides it into two parts. One of them is extended using E-table and mixed with the subkey. After this, it is reduced by S-box, and finally its bit position is interchanged. This process repeats 16 times in DES machine.

Suppose we have a simple permutation table such as '2 5 7 8 4 6 3 1', which numbers represent the bit position, instead of a real permutation table since real permutation tables require at least 32 bits. Any input character in the American Standard Code for Information Interchange (ASCII) format can be changed by the permutation table. For examples, the letter 'A' (0100 0001)<sub>2</sub> is changed to 'È' (1001 0000)<sub>2</sub>. IP, IP-1, PC and PC2 have the same concept of this simple example. The Extended table(E-table) is also similar to the permutation tables. Figure 5 shows the real E-table and an example in DES. As shown in the Figure, there are extra bits such as the 4<sup>th</sup>, 5<sup>th</sup> and 32<sup>nd</sup> positions.

Figure 5: E-table and Example of bits extension

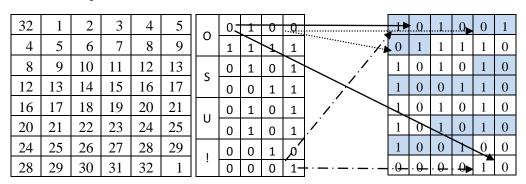

Using the table, the 4 letter word "OSU!", viz., O(0100 1111)<sub>2</sub>, S(0101 0011)<sub>2</sub>, U(0101 0101)<sub>2</sub>, and !(0010 0001)<sub>2</sub>, is changed to a 48 bit chunk. The extended data chunk is shortened by the Substitution Box. S-box operations are described in Figure 6.

Figure 6: S –box Substitution

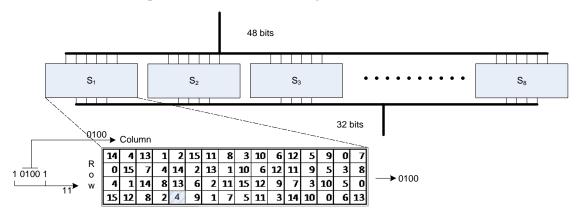

S-Box consists of eight substitution tables. The extended 48-bit chunk is divided by 8 and distributed to each substitution table;  $S_1$ ,  $S_2$ , ...,  $S_7$ , and  $S_8$ . The distributed 6 bit chunk is used to choose the substitute data. The 1<sup>st</sup> and 6<sup>th</sup> bit are used to select a row and the 2<sup>nd</sup> to 5<sup>th</sup> bit are used to select a column as shown in Figure 6. In our example, the first 6 bit chunk (101001)<sub>2</sub> from Figure 5 selects (11)<sub>2</sub> as a row and (0100)<sub>2</sub> as a column.

#### 2.4.2. Rivest, Shamir, and Adleman (RSA) Scheme

In 1976, Diffie and Hellman demonstrated the concept of an algorithm where two parties can communicate without sharing the key [3, 12]. The first implementation of the algorithm was proposed by Rivest, Shamir, and Adleman (RSA) at MIT in 1977. The RSA scheme is a block cipher, and the plaintext and ciphertext are integers between 0 and *n*-1 for some *n*.

RSA relies on the difficulty of factoring some number and modular operations based on the following equations:

$$C = M^e \bmod n \tag{2.1}$$

$$M = C^d \bmod n = (M^e)^d \bmod n, \tag{2.2}$$

where C is ciphertext, M is plaintext, n is the product of the two prime numbers, and e and d are the public key and the private key, respectively. How e, d, and n are chosen will be discussed shortly.

For example, suppose Alice wants to communicate with Bob. Bob first generates the RSA key pair  $(e_{Bob}, d_{Bob})$ . Alice obtains Bob's public key,  $e_{Bob}$ , and encrypts the message M using the obtained key  $e_{Bob}$  and modulus n. When Bob receives the ciphertext C, the message is decrypted using the private key  $d_{Bob}$  and modulus n.

Before performing encryption and decryption, the RSA algorithm requires a setup operation to choose e, d, and n, which is done using the following steps:

- 1. Choose two distinct prime numbers p and q

- 2. Compute n = pq

- 3. Compute Euler's totient function of  $n: \phi(n) = (p-1)(q-1)$

- 4. Select the public key  $e_{Bob}$  such that  $gcd(e_{Bob}, \phi(n))=1$

- 5. If  $e_{Bob} < 1$  or  $e_{Bob} > \phi(n)$ , return to step 4.

- 6. Compute  $d_{Bob} = e_{Bob}^{-1} \pmod{\phi(n)}$  using extended Euclid's algorithm.

The security of RSA comes from the difficulty of solving the *Discrete Logarithm Problem* (DLP). In other words, RSA relies on the difficulty of factoring some numbers, which requires multiplication and squaring. Euler's totient function  $\phi(n)$  is defined as the number of integers less than n which are relative prime to n. For example,  $\phi(6) = 2$  since 1 and 5 are relative prime to 6. Also  $\phi(9) = 6$  since 1, 2,4,5,7, and 8 are relative prime to 9.

The equation of step 6 above can be represented as  $e_{Bob}d_{Bob} = 1 \pmod{\phi(n)}$  by multiplying the  $e_{Bob}$  for both sides. Since GCD( $e_{Bob}$ ,  $\phi(n)$ ) = 1 by step 4, GCD( $e_{Bob}$ ,  $\phi(n)$ ) can be represented as the following equation by Extended Euclid's algorithm which is described in the background work.

$$e_{Bob}x + \phi(n)y = 1 \pmod{\phi(n)} \tag{2.3}$$

The x and  $d_{Bob}$  are identical since  $\phi(n)y$  (mod  $\phi(n)$ ) = 0. The  $d_{Bob}$  is the multiplicative inverse of  $e_{Bob}$  (mod  $\phi(n)$ ). Extended Euclid's algorithm is used in finding out x and y from the equation (2.3).

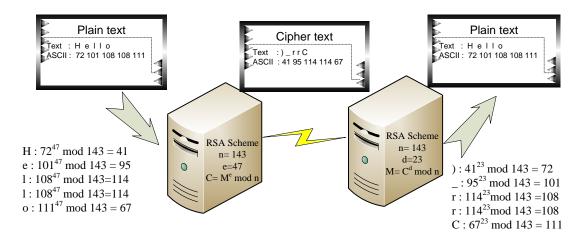

Figure 7: RSA Scheme

Figure 7 shows the RSA scheme. Suppose the encryption process of the sentence "Hello" is performed by RSA. The n is set to 143. Since we choose p = 11 and q = 13, as a result  $\phi(n)$  will be set to 120. The encryption key and decryption key are 47 and 23, respectively. The first letter 'H' in our example can be represented '72' in ASCII. The number 72 is converted to 41 by RSA algorithm;  $41 = 72^{47} \mod 143$ . The same method applied to the other letters. The decryption process is also similar to the encryption process. The encrypted letter '41' is recovered to '72' by the equation;  $72 = 41^{23} \mod 143$ . The processes of other encrypted letters are identical.

#### 2.4.3. Elliptic Curve Cryptography (ECC)

| $GF(p)\supset d, e$                     | $GF(2^m)\supset c, e$                       |

|-----------------------------------------|---------------------------------------------|

| $a,b,c = 0;p>3;4d^3+27e^2\neq0$         | a=1;b,d=0;e≠0                               |

| O + O = O                               | O + O = O                                   |

| (x,y) + O = (x,y)                       | (x,y) + O = (x,y)                           |

| (x,y) + (x,-y) = O                      | (x,y) + (x,x+y) = O                         |

| Addition over GF( <i>p</i> )            | Addition over GF(2 <sup>m</sup> )           |

| $(x_1,y_1) + (x_2,y_2) = (x_3, y_3)$    | $(x_1,y_1) + (x_2,y_2) = (x_3, y_3)$        |

| $\lambda = (y_2 - y_1)(x_2 - x_1)^{-1}$ | $\lambda = (y_2 - y_1)(x_2 - x_1)^{-1}$     |

| $x_3 = \lambda^2 - x_1 - x_2$           | $x_3 = \lambda^2 + \lambda + x_1 + x_2 + c$ |

| $y_3 = \lambda(x_1 - x_3) - y_1$        | $y_3 = \lambda(x_1 + x_3) + x_3 + y_1$      |

| Doubling over GF(p)                     | Doubling over GF(2 <sup>m</sup> )           |

| $(x_1,y_1) + (x_1,y_1) = (x_3, y_3)$    | $(x_1,y_1) + (x_1,y_1) = (x_3, y_3)$        |

| $\lambda = (3x_1^2 + d)(2y_1)^{-1}$     | $\lambda = x_1 + (y_1)(x_1)^{-1}$           |

| $x_3 = \lambda^2 - 2x_1$                | $x_3 = \lambda^2 + \lambda + c$             |

| $y_3 = \lambda(x_1 - x_3) - y_1$        | $y_3 = \lambda(x_1 + x_3) + x_3 + y_1$      |

Figure 8: Operations in Elliptic curves over GF(p) and  $GF(2^m)$

ECC was introduced by Neal Koblitz and Victor S. Millerin in 1985 [6]. ECC relies on the difficulty of performing algebra on an elliptic curve. ECC offers an equal level of security with smaller key sizes than RSA. Thus, the computational requirement is reduced. The security from ECC comes from the difficulty in solving the *Elliptic Curve* DLP (ECDLP) modular random number p. An arbitrary number  $n \pmod{p}$  has the same result with  $n \times n \times \cdots \times n \pmod{p}$ , i.e.,  $x \pmod{p}$  times multiplication in RSA. Also, arithmetic operation of random point  $dP(mod\ p)$  has similar

results with the RSA case. Scalar multiplication of d times point P, dP, gives the identical output as  $P + P + \cdots + P$ , d times addition in ECC.

In fact, elliptic curves are not ellipses. They are named so because they are described by cubic equations, similar to those used for calculating the circumference of ellipses. In general, cubic equations for elliptic curves take the form

$$y^{2} + axy + by = x^{3} + cx^{2} + dx + e$$

where a, b, c, d, and e are real numbers that satisfy some simple conditions. Also included in the definition of any elliptic curve is a single element denoted as O, called the *point at infinity* or the *zero point*, which is the sum of three points on an elliptic curve that lie on a straight line [2].

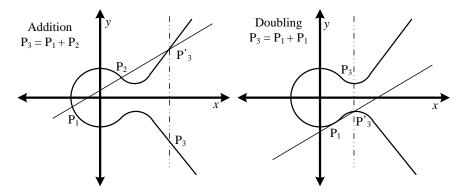

There are two major types of elliptic curves in real cryptosystems; *Galois Field (GF)* in prime number p, GF(p), and GF in  $2^m$ ,  $GF(2^m)$ . The coefficients of an elliptic curve change depending on the types. They also have different doubling and addition equations. Figure 8 shows the difference of operations between the two types.

As we see in Figure 8, the addition of two points on an elliptic curve always lies somewhere on the curve. Even though the third point as a sum of two points also lie on the elliptic curve, the point addition is not as simple as adding the coordinates of the points. The third point  $P_3$  is defined as follows. A certain point  $P_3$  in Figure 8 will be met by the straight line - it can be created by two given points - and elliptic curve whether the two points are different or not.  $P_3$  is reflected across the x-axis. The reflected point also lies on the elliptic curve. This reflected point is  $P_3$  which is the result point of the addition  $P_1$  and  $P_2$ . The difference of GF(p) and  $GF(2^m)$  comes from distinct algebra operation from each field as we saw in the mathematical section. We will briefly review the Addition and Doubling operations over GF(p).

On the elliptic curves, O plays a role of  $Addition\ Identity$ , which acts similar to 0 in general algebra. Since an elliptic curve is symmetric about the x-axis, when we add two distinct points which have the same x value, it does not satisfy the summation sentence as we discussed without  $Addition\ Identity\ O$ . When we add two distinct points with different x values on elliptic curves, the third point will be on the curve. With two points, we can create a linear equation and then find out the third point by interception with the elliptic curves and the lines. Also, in the case of doubling, we can use the tangent of a line by differentiation of the elliptic curves. The same rule also applies to elliptic curves over  $GF(2^m)$ . For more detail, see [30].

Figure 9: ECC ElGamal Scheme

There are several applications using elliptic curves, but this paper discusses a simple application -the ElGamal scheme in Figure 9. Assume that someone who wants to send a message m has to convert the message into point  $P_m$  over the Elliptic curve. The plain point  $P_m$  will be encrypted and then decrypted. Each user chooses an arbitrary number k less than n and one point P=kG, where k and P are used as a private key and a public key, respectively. Using these keys, plain point  $P_m$  can be encrypted as

$$C_m = (rG, P_m + rP_{rcv}),$$

where r is a random number chosen by the sender and  $P_{rcv}$  is the other party's public key. Then, the other party can decrypt the ciphertext  $C_m$  to the point  $P_m$  by subtracting a common value from:

$$P_{\rm m} = P_{\rm m} + rP_{\rm rev} - k_{\rm rev} rG$$

(using  $rP_{\rm rev} = rk_{\rm rev}G$ ).

Then, the extracted  $P_m$  is converted into the message that was originally sent by sender.

### 3. Background

This section presents a brief overview of the background information necessary to understand the rest of the thesis. First, some mathematical concepts used in cryptosystems are introduced. Then, some basic information on power models are discussed. Finally, methodologies for parallel computing are summarized. For a detailed treatment of these topics, readers are referred to the following: Cryptography [2, 10, 11], Power Model [17], and Side Channel Attack [14, 15]

#### 3.1. Mathematical Concepts Used in Cryptosystem

Cryptosystems cannot be explained without mathematics. Cryptographers often evaluate the security of ciphers by observing their mathematical functions. The fundamental mathematical operations in cryptography consist of addition, subtraction, multiplication, and division with reminder. Using these four mathematical operations, a cryptosystem can change a plaintext into a cipher text and vice versa.

#### 3.1.1. Fundamental Mathematical Operations

Humans use the base-10 number system. However, base-10 is not efficient for computer arithmetic operations, since computers use the base-2 number system. Therefore, a cryptosystem also uses the base-2 number system. However, the number of occurrences of the nonzero integer is not uniform in modular multiplication using the binary system. For example, the results of performing modular multiplications on 3-bit data (i.e., mod 8) are shown in Table 1. As can be seen, there are only four occurrences of 3, but twelve occurrences of 4. Uneven number format is shown to be cryptographically weaker than a uniformly distributed number format [2]. In contrast, *polynomial base* (PB) provides a uniform number format, i.e., the frequency of occurrence of any number is the same.

010(2) 100(4) Mult 001(1) 011(3) 101(5) 110(6) 111(7) 001(1) 001(1) 010(2) 011(3) 100(4) 101(5) 110(6) 111(7) 010(2) 010(2) 100(4) 110(6) 000(0) 010(2) 100(4) 110(6) 011(3) 010(2) 101(5) 011(3) 110(6) 001(1) 100(4) 111(7) 100(4) 000(0) 000(0) 100(4) 000(0) 100(4) 100(4) 100(4) 101(5) 101(5) 010(2) 111(7) 100(4) 001(1) 110(6) 011(3) 010(2) 110(6) 110(6) 100(4) 000(0) 110(6) 100(4) 010(2) 111(7) 111(7) 110(6) 101(5) 100(4) 011(3) 010(2) 001(1)

Table 1: Multiplication modulo 8 and Occurrences

| Integer    | 1 | 2 | 3 | 4  | 5 | 6 | 7 |

|------------|---|---|---|----|---|---|---|

| Occurences | 4 | 8 | 4 | 12 | 4 | 8 | 4 |

A polynomial is a sum of different powers of a variable. For example,

$$x^4 + x^2 + 1 \tag{3.1}$$

$$x^3 + x + 1 (3.2)$$

are polynomials in x. The polynomials (3.1) and (3.2) can be represented in binary format  $(10101)_2$  and  $(1011)_2$ , respectively. A polynomial is not set to any particular constant, i.e., x is not defined. Thus, four operations in PB, i.e., addition, subtraction, multiplication and division, are different from conventional algebra. Before discussing the PB operations, the concepts of fields and group will first be reviewed. This will be followed by a discussion on addition, subtraction, multiplication, and division operations in PB.

#### **Group and Fields**

A group is a set of numbers with a set of custom-defined arithmetic operations. The unique rules for arithmetic in groups are the source of the hard problems necessary for cryptographic security. In general, two groups used in cryptosystems are  $Z_n$ , the additive group of integers modulo a number n, and  $Z_p^*$ , the multiplicative group of integers modulo a prime number p.

The group  $Z_n$  operations use only the integers from 0 to (n-1). Its basic operation is addition, which ends by reducing the result modulo n, i.e., taking the integer remainder when the result is divided by n. One very important feature of arithmetic in a group is that all calculations give numbers that are in the group, which is called closure. The modular reduction by n ensures that all additions result in numbers between 0 and (n-1).

| mod 11 = 6    |

|---------------|

| $\mod 11 = 5$ |

| $\mod 11 = 1$ |

| 1             |

Figure 10: Example of Addition in Group  $Z_{15}$  and Multiplication in Group  $Z_{11}^*$

The multiplicative group  $Z_p^*$  uses only the integers between 1 and (p-1) and its basic operation is multiplication. A multiplication ends by taking the remainder of a division by a prime number p, which ensures closure.

Figure 10 shows some example additions and multiplications in group  $Z_{15}$  and group  $Z_{11}^*$ . The additive group  $Z_{15}$  uses integers from 0 to 14. If two arbitrary numbers a and b belong to  $Z_{15}$ , the result c of its addition also belongs to group  $Z_{15}$ , i.e., (a + b) mod 15 = c. The multiplicative

group  $Z_{11}^*$  uses integers from 1 to 10. A multiplication in  $Z_{11}^*$  finishes by taking the remainder after the result is divided by 11.

An arithmetic operation is said to be *commutative* if the order of its arguments is insignificant. With ordinary numbers, addition and multiplication are commutative operations; e.g., (2\*9) = (9\*2) and (2+9) = (9+2). However, subtraction and division are not commutative, e.g.,  $(2-9) \neq (9-2)$  and  $(2/9) \neq (9/2)$ .

A group is called *Abelian* if its main operation is commutative. Thus, an additive group is Abelian if (a + b) = (b + a) for all elements a and b in the group. A multiplicative group is Abelian if (a \* b) = (b \* a) for all elements a and b in the group. The additive group  $Z_n$  and the multiplicative group  $Z_p^*$  are both Abelian groups.

A *field* is a set of elements with two custom-defined arithmetic operations; most commonly, addition and multiplication. The elements of the field are an additive Abelian group, and the non-zero elements of the field are a multiplicative Abelian group. This means that all elements of the field have an additive inverse, and all non-zero elements have a multiplicative inverse. As is true for groups, other operations can be defined in a field, using its two main operations. A field is called *finite* if it has a finite number of elements. The most commonly used finite fields or *Galois fields* in cryptography are GF(p) (where p is a prime number) and  $GF(2^n)$  [28].

#### Field of GF(p)

The GF(p) field consists of numbers from 0 to (p-1). Its operations are addition and multiplication, which are defined for the groups  $Z_n$  and  $Z_p^*$ , respectively, and all calculations end with reduction modulo p. The restriction that p be a prime number is necessary so that all non-zero elements have a multiplicative inverse. As with  $Z_n$  and  $Z_p^*$ , other operations in GF(p) (such as division, subtraction, and exponentiation) are derived from the definitions of addition and multiplication.

#### Field of $GF(2^n)$

The  $GF(2^n)$  field is attractive for implementation due to their carry-free arithmetic, and the availability of different equivalent representations of the field, which can be implemented and optimized in hardware [28, 29]. There are several ways to describe arithmetic in  $GF(2^n)$ . Polynomial basis (PB) and optimal normal basis (ONB) are typical  $GF(2^n)$  representation methods. Our proposed method is based on PB, therefore, only the PB representation will be reviewed in this thesis.

A cryptosystem uses various GF sizes. For example, ECC usually uses  $GF(2^{131})$ ,  $GF(2^{163})$ ,  $GF(2^{193})$ , and  $GF(2^{233})$ , whereas RSA uses  $GF(2^{1024})$ ,  $GF(2^{2048})$  and  $GF(2^{3072})$ . In order to improve security, the field size will become bigger in future.

#### **Polynomial Bases Representation**

$GF(2^n)$  has  $2^n$  elements, which are polynomials of degree less than n, with coefficients in  $GF(2^n)$ , i.e.,  $\{a_{n-1}x^{n-1} + a_{n-2}x^{n-2} + ... + a_2x^2 + a_1x + a_0 \mid a_i = 0 \text{ or } 1\}$ . These elements can be written in vector form as  $(a_{n-1} \dots a_1 \ a_0)$ . The main operations in  $GF(2^n)$  are addition and multiplication. Some computations involve an *irreducible* polynomial  $f(x) = x^n + f_{n-1}x^{n-1} + f_{n-2}x^{n-2} + ... + f_2x^2 + f_1x + f_0$ , where each  $f_i$  is in  $GF(2^n)$ . The polynomial f(x) cannot be factored into two polynomials over  $GF(2^n)$ , each of degree less than n. The irreducible polynomial takes the same role as a prime number in the GF(p). The basic arithmetic operations of polynomial bases are shown in Figure 11:

#### Addition/Subtraction

$$(c_{n-1} \dots c_1 c_0) = (a_{n-1} \dots a_1 a_0) \pm (b_{n-1} \dots b_1 b_0),$$

where  $c_i = a_i \text{ xor } b_i, \ 0 \le i \le n-1$

Division/Modular operation

$$(a_{n-1} \dots a_1 a_0) = (q_{n-k} \dots q_0) \times (b_{k-1} \dots b_1 b_0) + (r_{k-2} \dots r_0)$$

where  $(q_{n-k} \dots q_0)$  is the quotient,  $(r_{k-2} \dots r_0)$  is the reminder  $(n \ge k)$

$$(a_{n-1} \dots a_1 a_0) \div (b_{k-1} \dots b_1 b_0) = (q_{n-k} \dots q_0)$$

$(a_{n-1} \dots a_1 a_0) \mod (b_{k-1} \dots b_1 b_0) = (r_{k-2} \dots r_0)$

#### Modular Multiplication

$$(r_{n-1} \dots r_1 r_0) = (a_{n-1} \dots a_1 a_0) \times (b_{n-1} \dots b_1 b_0) \mod f(x),$$

where

$$a_i$$

,  $b_i$  and  $r_i$  (0  $\leq i \leq n-1$ ) is the remainder modulo  $f(x)$

#### Additive Identity/Inverse

$$(a_{n-1} \dots a_1 a_0) + 0 = (a_{n-1} \dots a_1 a_0) \mod f(x)$$

0 is called an *additive identity*

if

$$(a_{n-1} \dots a_1 a_0) + (b_{n-1} \dots b_1 b_0) = 0 \mod f(x)$$

then

$(b_{n-1} \dots b_1 b_0)$  is an additive inverse of  $(a_{n-1} \dots a_1 a_0)$

#### Multiplicative Identity/Inverse

$$(a_{n-1} \dots a_1 a_0) \times 1 = (a_{n-1} \dots a_1 a_0) \mod f(x)$$

1 is called a multiplicative identity

if

$$(a_{n-1} \dots a_1 a_0) \times (b_{n-1} \dots b_1 b_0) = 1 \mod f(x)$$

then

$(b_{n-1} \dots b_1 b_0)$  is a multiplicative inverse of  $(a_{n-1} \dots a_1 a_0)$

Figure 11: Arithmetic Operations of Polynomial Bases

In order to illustrate PB arithmetic operations, consider the following two polynomial representations

$$x^4 + x^2 + 1$$

$(a_4 a_3 a_2 a_1 a_0) = (1 \ 0 \ 1 \ 0 \ 1)$  (3.3)

$$x^3 + x^2 + x + 1$$

$(b_4 b_3 b_2 b_1 b_0) = (0 \ 1 \ 1 \ 11),$  (3.4)

where both are elements of  $GF(2^5)$ . The result of performing addition according to Figure 11 is as follows:

$$c_4 = a_4 \text{ xor } b_4 = 1 \text{ xor } 0 = 1$$

$c_3 = a_3 \text{ xor } b_3 = 0 \text{ xor } 1 = 1$   $c_2 = a_2 \text{ xor } b_2 = 1 \text{ xor } 1 = 0$   $c_1 = a_1 \text{ xor } b_1 = 0 \text{ xor } 1 = 1$   $c_0 = a_0 \text{ xor } b_0 = 1 \text{ xor } 1 = 0$   $(1 \ 1 \ 0 \ 1 \ 0)$   $x^4 + x^3 + x$

Thus, PB representation  $x^4 + x^3 + x$  is the addition of (3.3) and (3.4). In PB representation, subtraction also provides the same results. Multiplication is more difficult than addition/subtraction. The following illustrates the multiplication of the above two polynomials, i.e.,  $(x^4 + x^2 + 1) \times (x^3 + x^2 + x + 1) \mod (x^5 + x^3 + 1)$ :

$$x^{4} \times (x^{3} + x^{2} + x + 1) = x^{7} + x^{6} + x^{5} + x^{4}$$

$$x^{2} \times (x^{3} + x^{2} + x + 1) = x^{5} + x^{4} + x^{3} + x^{2}$$

$$1 \times (x^{3} + x^{2} + x + 1) = x^{3} + x^{2} + x + 1$$

$$(x^{7} + x^{6} + x + 1) \times x^{2} \times (10100101) \times (3.5)$$

$$- (x^{5} + x^{3} + 1) \times x^{2} \times (10100100) \times (3.6)$$

$$- (x^{6} + x^{5} + x^{2} + x + 1) \times x \times (10100101) \times (3.7)$$

$$- (x^{5} + x^{3} + 1) \times x \times (1010010) \times (3.8)$$

$$- (x^{5} + x^{4} + x^{2} + 1) \times (00110101) \times (3.9)$$

$$- (x^{5} + x^{3} + 1) \times (101001) \times (3.10)$$

$$- (x^{5} + x^{3} + 1) \times (101001) \times (3.10)$$

$$- (x^{5} + x^{3} + x^{2} + 1) \times (101001) \times (3.10)$$

Multiplication is simply a shift and Exclusive-OR as shown in (3.5). However, since multiplication increases the size of the exponent, we need to shorten it to fit into a  $GF(2^5)$  word size, i.e., 5 bits. To prevent word size overflow, a modular operation is performed using an irreducible polynomial  $x^5 + x^3 + 1$ , which is one of the irreducible polynomials in  $GF(2^5)$  that has been arbitrarily chosen. The division and modular operation involves a series of shift and Exclusive-OR operations as shown in (3.6) to (3.11) until the reminder becomes an element of  $GF(2^5)$ . The quotients bits are generated from operations (3.6), (3,8) and (3.10), i.e.,  $x^2 + x + 1$ . The last reminder is the result of modular operation, which is  $x^4 + x^3 + x^2$ .

The benefit of PB is a uniformly distributed number format system. Back to the 3-bit system, we already saw the binary format is unevenly distributed as shown in Table 1. Consider the same bit system using PB format where irreducible polynomial is  $x^3 + x + 1$ . The results of multiplication mod f(x) are shown as Table 2.

Table 2: Multiplication mod f(x) where  $f(x) = x^3 + x + 1$

| Mult       | 001(1) | 010(2) | 011(3) | 100(4) | 101(5) | 110(6) | 111(7) |  |

|------------|--------|--------|--------|--------|--------|--------|--------|--|

| 001(1)     | 001(1) | 010(2) | 011(3) | 100(4) | 101(5) | 110(6) | 111(7) |  |

| 010(2)     | 010(2) | 100(4) | 110(6) | 011(3) | 001(1) | 111(4) | 101(5) |  |

| 011(3)     | 011(3) | 110(6) | 101(5) | 111(7) | 100(4) | 001(1) | 010(2) |  |

| 100(4)     | 100(4) | 011(3) | 111(7) | 110(6) | 010(2) | 101(5) | 001(1) |  |

| 101(5)     | 101(5) | 001(1) | 100(4) | 010(2) | 111(7) | 011(3) | 110(6) |  |

| 110(6)     | 110(6) | 111(7) | 001(1) | 101(5) | 011(3) | 010(2) | 100(4) |  |

| 111(7)     | 111(7) | 101(5) | 010(2) | 001(1) | 110(6) | 100(4) | 011(3) |  |

|            |        |        |        |        |        |        |        |  |

| Integer    | 1      | 2      | 3      | 4      | 5      | 6      | 7      |  |

| Occurences | . 7    | 7      | 7      | 7      | 7      | 7      | 7      |  |

#### 3.1.2. Addition Chain

Multiplication is one of the big issues in Cryptography. In particular, efficient algorithms for group exponentiation have received much attention due to their role in the cryptosystem. Suppose we want to evaluate  $M^n$  for given arbitrary numbers M and n. The computation of  $M^n$  is an n-multiplication operation, i.e., the result is equals to M multiplied n times. However, computation cost is expensive because a cryptosystem uses a large number n to increase security. For example, RSA typically uses a 1024-bit number for n. Many mathematicians have tried to find a solution that requires a less number of multiplications, and  $Addition\ Chain$  is one of the solutions. Interestingly, Addition Chain is not new. Knuth found material that existed in around 200 B.C. related to the addition chain problem [30]. Indian and Arabic works in the  $10^{th}$  and  $11^{th}$  century also mentioned the problem.

An addition chain is a sequence of integers

$$a_0 \qquad a_1 \qquad a_2 \qquad \dots \qquad a_n$$

starting from  $a_0$ =1 and ending with  $a_r = n$  in such a way that any  $a_k$  is the sum of two earlier integers  $a_i$  and  $a_i$  in the chain, i.e.,

$$a_k = a_i + a_i$$

for  $0 < i, j < k$

For example, the computation of  $M^{15}$  can be done in two ways as shown below.

As we see from the above result, (3.12) needs 15 multiplications but (3.13) needs just 6 multiplications. Using the Addition Chain is almost two times more efficient than performing multiplications sequentially. In the following subsections, we will show the Binary Addition Chain as an example of performing addition, and then discuss exponentiation.

#### **Binary Addition Chain**

The Binary Addition Chain is also called the *Addition-and-Doubling* (AD) *Algorithm*. Suppose we want to compute the encrypted point  $S = dP \pmod{f(x)}$ , where d is an n-bit key value, i.e.,  $d = (d_{n-1}, d_{n-2}, \ldots, d_0)_2$ , P is a given plain point, and f(x) is the irreducible polynomial in GF. A modular f(x) operation is a protection from word size overflow. Figure 12 shows the steps of AD, which processes the bits of d from MSB to LSB.

```

if d_{n-1} = 1 then S = P else S = 0

for i from n-2 to 0 {

S = S + S \pmod{f(x)}

if d_i = 1 then S = S + P \pmod{f(x)}

}

return S

```

Figure 12: Binary AD Algorithm

Suppose we want to compute 15 (*d*) times *P* by using Addition Chain ignoring modular operation since the results from Point Addition and Point Doubling are already optimized by modular operation. 15 can be expressed as a binary  $(01111)_2$  in  $GF(2^5)$ . Since the MSB is 0, the initial value *S* is set to *O*. The following operations are then performed.

| $(0\ 1\ 1\ 1\ 1)$ | S = O   | //S = S + S | 1 <sup>st</sup> iteration |

|-------------------|---------|-------------|---------------------------|

| $\uparrow$        | S = P   | //S = S + P |                           |

| (0 1 1 1 1)       | S = 2P  | //S = S + S | 2 <sup>nd</sup> iteration |

| <b>↑</b>          | S = 3P  | //S = S + P |                           |

| (0 1 1 1 1)       | S = 6P  | //S = S + S | 3 <sup>rd</sup> iteration |

| <b>↑</b>          | S = 7P  | //S = S + P |                           |

| (0 1 1 1 1)       | S = 14P | //S = S + S | 4 <sup>th</sup> iteration |

| <b>↑</b>          | S = 15P | //S = S + P |                           |

As a result, we obtain S = 15P in  $GF(2^5)$ . The scalar multiplication using the Addition Chain takes 8 additions compared to 15 additions without it. Using the AD method, the *n*-bit Addition Chain requires *n*-1 doubling (i.e., S + S) operations, and the number of S + P operations is equal to the number of 1's in *d* (except MSB). In our example, we need 4 doubling and 4 addition operations. This Addition Chain is the one of main operations in the ECC scheme and is also the main source to get the private key. The method to get the private key will be discussed in a later section.

#### **Binary Exponentiation**

Binary exponentiation uses an algorithm similar to AD called *Squaring-and-Multiplication* (SM), where doubling changes to squaring and addition changes to multiplication. Figure 13 shows the algorithm for binary exponentiation:

```

if d_{n-1} = 1 then S = P else S = 1

for i from n-2 to 0 {

S = S \times S \pmod{f(x)}

if d_i = 1 then S = S \times P \pmod{f(x)}

}

return S

```

Figure 13: Binary SM Algorithm

For example, suppose we want to compute  $10^{15}$ , P is set to  $10 (01010)_2$ , d is set to  $15 (01111)_2$ , and modular f(x) is set to  $32 (100101)_2$ . Since the MSB of d is 0, the initial value S is set to 1.

```

1<sup>st</sup> iteration

(0\ 1\ 1\ 1\ 1)

S = (11100)

// S = S \times S \pmod{f(x)}

1

S = (01100)

// S = S \times P \pmod{f(x)}

2<sup>nd</sup> iteration

(0\ 1\ 1\ 1\ 1)

S = (10100)

// S = S \times S \pmod{f(x)}

// S = S \times P \pmod{f(x)}

\uparrow

S = (11010)

3<sup>rd</sup> iteration

// S = S \times S \pmod{f(x)}

(01111)

S = (00011)

// S = S \times P \pmod{f(x)}

1

S = (111110)

(0\ 1\ 1\ 1\ 1)

// S = S \times S \pmod{f(x)}

4<sup>th</sup> iteration

S = (10011)

// S = S \times P \pmod{f(x)}

S = (11011)

```

As a result we obtain  $10^{15}$  in  $GF(2^5)$ . The binary exponentiation using the addition chain takes 8 multiplications compared to 15 multiplications without it. Using the SM method, we can see that the *n*-bit addition chain needs *n*-1 squaring and the number of  $S \times P$  operations equal to the number of 1's in *d* (except MSB). The SM method is the main operation of RSA and also the target algorithm to get a private key.

#### 3.1.3. Montgomery's Method

In 1985, P. L. Montgomery proposed a new modular multiplication algorithm without requiring division by n [24]. *Montgomery Multiplication* (MM) exploits additions and divisions by a power of 2, i.e., shift right or left. This method replaces division by n with division by  $r = 2^k$ , where  $2^k$  is greater than n, GCD(r, r) should be *one* (1) and the inverse of r is less than r. Using this method, computer systems can easily implement the modular divide operation since  $r = 2^k$  involves simple shifting operations.

MM is used to compute  $Z = A \cdot B \cdot r^{-1} \pmod{n}$ , where A and B are the n-residues of a and b with respect to r and  $r^{-1}$  is the inverse of r in modulus n, i.e.,  $A = a \cdot r \pmod{n}$ ,  $B = b \cdot r \pmod{n}$ . Since r is chosen as a power of 2, r and n should be relative prime. In addition, we need  $n^{-1}$  in such a way that  $r \cdot r^{-1} - n \cdot n^{-1} = 1$ . Montgomery found the following equation, where m is set to  $t \cdot (-n^{-1} \pmod{r})$  mod r:

$$(t + m \cdot n)/r = \{t + n \cdot [t \cdot (-n^{-1} \bmod r) \bmod r]\}/r$$

$$= (t + n \cdot t \cdot n^{-1})/r$$

$$= t \cdot r^{-1} \bmod n$$

Using this equation, we can divide by r instead of by n. For example, suppose we want to compute  $a \cdot b$  using MM. First, a and b changed to A and B, respectively, and the result of  $A \cdot B$  is given as

$$A \cdot B = (a \cdot r) (b \cdot r) r^{-1} \mod n$$

=  $a \cdot b \cdot r \mod n$

Then, we obtain the result by using one more MM with 1, i.e.,

$$(a \cdot b \cdot r \bmod n) \cdot 1 = (a \cdot b \cdot r) \cdot r^{-1} \bmod n$$

=  $(a \cdot b) \bmod n$

Figure 14 shows the MM algorithm and example.

```

a = 5, b = 3, n = 7, r = 2^4

Input: a, b

r^{-1}r - n^{-1}n = 1, thus n^{-1} = 9, r^{-1} = 4

Output : a \cdot b \cdot r \mod n

A = a * r \mod n = 5 * 16 \mod 7 = 3

n^{-1} \& r^{-1} are pre computed.

B = b * r \mod n = 3 * 16 \mod 7 = 6

Function: MMmult(A,B)

MM(A, B)

t = A*B

t = A * B = 18

m = t * n^{-1} \mod r = 18 * 9 \mod 16 = 2

m = t * n^{-1} \mod r

u = (t + m * n) / r = (18 + 2*7) / 16 = 2

u = (t+m*n)/r

MM(u,1)

if u \ge n then return u–n

t = u * 1 = 2

else return u

m = t * n^{-1} \mod r = 2 * 9 \mod 16 = 2

u = (t + m * n) / r = (2 + 2*7) / 16 = 1

```

Figure 14: MM Algorithm and Example

Consider the case:  $5 \times 3 \mod 7$ . It is easily computed with a result of 1. However the operation  $\pmod{7}$  is not easy to computer as mentioned. Consider the r as  $2^4$ , we can get  $n^{-1}$  as a 9 and  $r^{-1}$  as a 4 by using the Extended Euclid's algorithm, which are discussed in a later section. Then input value 5(a) and 3(b) are changed n-residues 3(A) and 6(B), respectively. Using A and B, MM(A, B) computed the  $a \times b \times r^{-1} \mod n$  as a result 2. Actually, our purpose is not the computation of  $a \times b \times r^{-1} \mod n$ , but  $a \times b \mod n$ . To change  $a \times b \times r^{-1} \mod n$  into  $a \times b \mod n$ , one more MM is required with the result of MM(A, B) and 1 as an input. As shown in figure 14, the second MM(2, 1) shows the same value with  $5 \times 3 \mod 7$ .

MM needs pre-computations of  $n^{-1}$  and  $r^{-1}$ , and the changing processes of input values are also needed. Finally, one more MM is required to get a correct value. Even though MM needs pre and post processing, it is better than conventional modular multiplication in the case of cryptosystems where a large number of modular multiplications are required.

#### 3.1.4. Chinese Reminder Theorem (CRT)

CRT was discovered by a Chinese mathematician, Sun Tse, in the 1<sup>st</sup> century [10]. The basic theorem is simple. Let  $m_1$  and  $m_2$  be relatively prime integers. Given  $x_1$  less than  $m_1$  and  $x_2$  less than  $m_2$ , there exists a unique integer X less than  $m_1 \cdot m_2$  such that

```

X = x_1 \mod m_1

X = x_2 \mod m_2

X = x_1 + m_1 \cdot [(x_2 - x_1) \cdot m_1^{-1} \mod m_2]

```

This method is useful in reducing an *n*-bit modular exponentiation into two half size modular exponentiations with CRT processing.

#### 3.1.5. Euclid's Algorithm

Greatest Common Divisor of a and b, denoted as GCD (a, b), is the largest positive integer that divides both a and b. There are two general ways to determine the GCD. The first method is factoring each number a and b to find the common factor. For example, if a = 1728 and b = 135, then GCD can be found as

$$1728 = 2^63^2$$

,  $135=3^35 =$  GCD(1728, 135) =  $3^2 = 9$

Since a and b have the same factor of  $3^2$ , GCD is 9. However, factoring large numbers is not easy. Therefore, Euclid's Algorithm is used to determine the GCD of large numbers. For any integer a and b, a is greater than or equal to b, if not, switch a and b. The first step is to divide a by b, hence represent a in the following equation:

$$a = q_1 b + r_1 \tag{3.14}$$

where  $q_1$  is the quotient and  $r_1$  is the reminder. If  $r_1 = 0$ , then GCD is b. If not, then continue in the following form until the reminder is zero.

$$a = q_1b + r_1$$

$r_2 = q_4r_3 + r_4$  :  $b = q_2r_1 + r_2$   $r_3 = q_5r_4 + r_5$   $r_{k-2} = q_kr_{k-1} + r_k$  :  $r_{k-1} = q_{k+1}r_k$

Then the GCD  $(a, b) = r_k$ . Euclid's algorithm has the following important characteristics. If one of a or b is not zero, then there exist integers x and y such that ax + by = GCD(a, b).

The process of finding x and y is called Extended Euclid's algorithm. Suppose we start by dividing by b into a, that is  $a = q_1b + r_1$ , then proceed as above in Euclid's algorithm. We will get the successive quotients, i.e.,  $q_1, q_2, ..., q_{k+1}$ . The x and y can be found by the following equations:

$$x_i = -q_{i-1}x_{i-1} + x_{i-2}, \ x_0 = 0, \ x_1 = 1 \text{ for } (2 < j < k+1)$$

(3.15)

$$y_i = -q_{i-1}y_{i-1} + y_{i-2}, \ y_0 = 1, \ y_1 = 0 \text{ for } (2 < j < k+1)$$

(3.16)

The  $x_{k+1}$  and  $y_{k+1}$  are what we want to find. Suppose we want to find out GCD (1180, 482) and x and y in the equation  $1180 \times x + 482 \times y = GCD$  (1180, 482) by extended Euclid's algorithm. The process of finding the GCD (1182, 482) is like below:

$$1182 = 2 \times 482 + 216$$

$50 = 3 \times 16 + 2$

$482 = 2 \times 216 + 50$   $16 = 8 \times 2$

$216 = 4 \times 50 + 16$

Thus, we can find out the GCD (1180, 482) =  $r_k$  = 2, and then we can also get the quotients  $q_1$  = 2,  $q_2$  = 2,  $q_3$  = 4,  $q_4$  = 3 and  $q_5$  = 8. By using these quotients, we can find out the x and y. The following processes show the way of finding x and y.

$$x_0 = 0$$

$y_0 = 1$

$x_1 = 1$   $y_1 = 0$

$x_2 = -2x_1 + x_0 = -2$   $y_2 = -2y_1 + y_0 = 1$

$x_3 = -2x_2 + x_1 = 5$   $y_3 = -2y_2 + y_1 = -2$

$x_4 = -4x_3 + x_2 = -22$   $y_4 = -4y_3 + y_2 = 9$

$x_5 = -3x_4 + x_3 = 71$   $y_5 = -3y_4 + y_3 = -29$

The 71 and -29 are what we want. Extended Euclid's algorithm is useful to find *the multiplicative inverse*.

To find the multiplicative inverse of 11111 (mod 12345) as an example, Let us analyze the definition of the multiplicative inverse, i.e., the multiplicative inverse x is defined as the multiplicative identity 1 multiplied by 11111 as in equation (3.17).

$$11111x = 1 \pmod{12345} = 12345y' + 1 \tag{3.17}$$

$$11111x + 12345y = 1 = GCD (11111, 12345),$$

Substitute  $y = -y'$  (3.18)

from equation (3.18), we can get the quotients  $q_1 = 1$ ,  $q_2 = 9$ ,  $q_3 = 246$ ,  $q_4 = 1$ , and  $q_5 = 4$  by Euclid's algorithm. Then, we can find the number x = 2471 as the multiplicative inverse by Extended Euclid's algorithm. To verify it, we substitute x with 247. Then we can check it with following equation (3.19);

$$11111 \times 2471 = 27455281 = 2224 \times 12345 + 1 = 1 \pmod{12345}$$

(3.19)

#### 3.1.6. Projective Coordinate

The projective coordinate is used to eliminate the need for performing division. Affine coordinate in ECC as shown in the Cryptography section requires a division operation, i.e., computing  $\lambda$  requires one division in both GF(p) and  $GF(2^m)$ . In computer systems, a division operation needs more clock cycles than a multiplication operation [28]. Affine coordinate (x, y) can be represented as a projective (Jacobian style) coordinate (X, Y, Z), where  $(x, y) = (X/Z^2, Y/Z^3)$ . A point doubling and a point addition are transformed as shown in Table 3.

Table 3: Relationship between Affine Coordinates and Projective Coordinates [30,43]

| $y^{2} + xy = x^{3} + ax^{2} + b$ over $GF(2^{m})$ , $b \neq 0$ | Affine Coordinates( $x$ , $y$ )                                                                                                                                   | Projective Coordinates( $X, Y, Z$ )                                                                                                                                                                                                                                                                             |  |  |

|-----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Point Addition                                                  | $(x_1, y_1) + (x_2, y_2) = (x_3, y_3)$ $\lambda = (y_2 - y_1)(x_2 - x_1)^{-1}$ $x_3 = \lambda^2 + \lambda + x_1 + x_2 + c$ $y_3 = \lambda(x_1 + x_3) + x_3 + y_1$ | $(X_{1},Y_{1},Z_{1}) + (X_{2},Y_{2},Z_{2}) = (X_{3}, Y_{3}, Z_{3})$ $A = X_{1}Z_{2}^{2}$ $B = X_{2}Z_{1}^{2}$ $C = A + B$ $D = Y_{1}Z_{3}^{3}$ $E = Y_{2}Z_{1}^{3}$ $F = D + E$ $G = Z_{1}C$ $H = FX_{2} + GY_{2}$ $Z_{3} = GZ_{2}$ $I = F + Z_{3}$ $X_{3} = aZ_{3}^{2} + IF + C^{3}$ $Y_{3} = IX_{3} + HG^{2}$ |  |  |

| Point Doubling                                                  | $(x_1, y_1) + (x_1, y_1) = (x_3, y_3)$ $\lambda = x_1 + (y_1)(x_1)^{-1}$ $x_3 = \lambda^2 + \lambda + c$ $y_3 = \lambda(x_1 + x_3) + x_3 + y_1$                   | $(X_{1},Y_{1},Z_{1}) + (X_{1},Y_{1},Z_{1}) = (X_{3}, Y_{3}, Z_{3})$ $Z_{3} = X_{1}Z_{1}^{2}$ $A = bZ_{1}^{2}$ $B = X_{1} + A$ $X_{3} = B^{4}$ $C = Z_{1}Y_{1}$ $D = Z_{3} + X_{1}^{2} + C$ $E = DX_{3}$ $Y_{3} = X_{1}^{4}Z_{3} + E$                                                                            |  |  |

A division operation in Affine Coordinates does not appear in Projective Coordinates. Instead of division operations, Projective Coordinates need more multiplication than Affine Coordinates, i.e., Point Doubling needs 12 multiplications in Projective Coordinates while it needs only 2 multiplications in Affine Coordinates. Thus, the appropriateness of using projective coordinates is determined by user. Furthermore, a division operation is needed to change Projective Coordinates into Affine Coordinates.

## 3.2. Power Model

Most of our electric appliances like TVs, game cubes and computers, consume power from power outlets and lots of hand-held devices also use a battery as a power source. This means that power consumption rates are one of the performance standards, which makes limiting power consumption a critical issue for embedded systems. A cryptosystem requires numerous computations,

which means lots of 0-to-1 or 1-to-0 transitions at the gate-level. These gates usually consist of one or more complementary metal-oxide semiconductor (CMOS) logic circuits.

The dominant equation for the CMOS power model is given by

$$P = ACV^2 f + tAVI_{\text{short}} f + VI_{\text{leak}}$$

(3.20)

The first term measures the dynamic power consumption, which is proportional to the frequency f, the active gates A, the capacitance C, and the square of voltage  $V^2$ . The second terms are related to short-circuit power, which varies with short circuit current  $I_{\text{short}}$ , and instantaneous time t. The last term,  $VI_{\text{leak}}$ , shows the leakage power by Ohm's law. However, the second and third terms are less significant than the first term in most CMOS circuits.

P is defined as the consumption at a discrete point in time while *energy E* is defined as the power dissipation during the execution time D, as shown in the equation:

$$E = P_{avg} \cdot D \tag{3.21}$$

As we know, power uses watts units (W), and energy uses Jules (J = W/s). Even if a processor operates at low power, its energy can be greater than or equal to the energy used when operating at high power. Another example, a single core can finish a job in time 2t using power p while a dual core takes time t using power 2p. The energy between the single and dual core will be the same even though the performance of dual core is better than that of the single core. Energy or instantaneous power, as a measure of efficiency, is not suitable for evaluating the system. Therefore, evaluating the power-performance of a system based only on instantaneous power or energy is not sufficient. Thus, researchers use a new method for power-performance, the *energy-delay product* [18]:

$$EDP = E \cdot D \text{ (J-sec)}$$

(3.22)

By using *Energy-Delay product* (EDP), the above example of comparison with single core and dual core can be meaningful. The EDP of the single core is  $(2t)^2 \cdot p$  while that of the dual core is  $t^2 \cdot 2p$ . Thus, dual-core is twice as good as a single core. Notice that smaller EDP means better power-performance efficiency.

There are several ways to improve performance-power efficiency in mobile devices. Research on power reduction consists of techniques at the circuit level, architectural level and software level. We will briefly discuss these methods in the following subsections. For more detail, refer to [17].

#### 3.2.1. Power Reduction at the Circuit Level