#### AN ABSTRACT OF THE THESIS OF

<u>Zhangxiang Hu</u> for the degree of <u>Master of Science</u> in <u>Computer Science</u> presented on June 3, 2015.

| Γitle: RANDOM AC     | CESS MACHINE IN | SECURE MULTI    | -PARTY COMPUTA | ATION |

|----------------------|-----------------|-----------------|----------------|-------|

|                      |                 |                 |                |       |

| Abstract approved: _ |                 |                 |                |       |

| arastract approved.  |                 | Michael J. Rosu | lek            |       |

Secure multi-party computation (MPC) is a conceptual framework in cryptography. It allows distrusting parties engage in a protocol to perform a computational task while still maintain some secure properties. Most existing approaches are required to interpret functions as a boolean circuit. With the recent state-of-art circuit garbling scheme, the performance are significantly improved. However, boolean circuit still has its limitations in practical usage, especially when the input data size is enormous.

In this thesis, we focus on another technique in MPC which is called random-access machines (RAM program). We first describe a zero-knowledge proof system in which a prover holds a large dataset M and can repeatedly prove NP relations about that dataset. This system achieves sublinear amortized cost. Second, we present the first practical protocols for evaluating RAM programs with security against malicious adversaries. The extra overhead of obtaining malicious security for RAM programs is minimal and does not grow with the running time of the program.

©Copyright by Zhangxiang Hu June 3, 2015 All Rights Reserved

# RANDOM ACCESS MACHINE IN SECURE MULTI-PARTY COMPUTATION

by

Zhangxiang Hu

#### A THESIS

submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Master of Science

Presented June 3, 2015 Commencement June 2016

| Master of Science thesis of Zhangxiang Hu presented on June 3, 2015.                                                                                                                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| APPROVED:                                                                                                                                                                                     |

| Major Professor, representing Computer Science                                                                                                                                                |

| Director of the School of Electrical Engineering and Computer Science                                                                                                                         |

| Dean of the Graduate School                                                                                                                                                                   |

|                                                                                                                                                                                               |

|                                                                                                                                                                                               |

| I understand that my thesis will become port of the normanent collection of Oregon                                                                                                            |

| I understand that my thesis will become part of the permanent collection of Oregon State University libraries. My signature below authorizes release of my thesis to any reader upon request. |

| Zhangxiang Hu, Author                                                                                                                                                                         |

#### ACKNOWLEDGEMENTS

Great thanks go to my advisor Mike Rosulek for his advising during my studies, this thesis would never possible without him. He inspired me a lot on ethics both in academia and research, and gave a lot of insightful comments on technical writings in cryptography. It is my honor to be his student.

I am grateful to the my thesis committee members, Attila Altay Yavuz, Amir Nayyeri, Rakesh Bobba and Mike Pavol for their helpful feedback on this thesis. Also thanks to my collaborators and co-authors, Arash Afshar and Payman Mohassel.

Finally but most importantly, I would like to thank my family for their great support in my life, especially my wife Xueni Guo who undertook the unpredictable journey to USA, she means the whole world to me.

# TABLE OF CONTENTS

|   |     |                                                                                                             | Page         |

|---|-----|-------------------------------------------------------------------------------------------------------------|--------------|

| 1 | Int | roduction                                                                                                   | 1            |

|   | 1.1 | Security Concerns  1.1.1 Adversary                                                                          | . 2          |

|   | 1.2 | Our contribution                                                                                            | . 5          |

| 2 | Pre | eliminary                                                                                                   | 7            |

|   | 2.1 | Basic Notation                                                                                              | . 7          |

|   | 2.2 | Hash Function and Strongly Universal Hashing                                                                | . 8          |

|   | 2.3 | Garbled Circuit and Garbling Scheme  2.3.1 Garbled Circuit  2.3.2 Oblivious Transfer  2.3.3 Garbling Scheme | . 8<br>. 10  |

|   | 2.4 | Oblivious RAM                                                                                               | . 13         |

|   | 2.5 | Commitment and Zero-knowledge proof                                                                         | . 15         |

| 3 | Zei | ro-Knowledge Proofs by using Oblivious RAM program                                                          | 18           |

|   |     | Introduction                                                                                                | . 19         |

|   | 0.2 | 3.2.1 Authenticated Array                                                                                   | . 19<br>. 20 |

|   | 3.3 | Protocol overview                                                                                           |              |

|   | 3.4 | Additional Notation and Helper Routines                                                                     | . 25         |

|   | 3.5 | Detailed protocol                                                                                           | . 29         |

|   | 3.6 | Security proof                                                                                              | . 31         |

# TABLE OF CONTENTS (Continued)

|   |       |           |                                           | Page |

|---|-------|-----------|-------------------------------------------|------|

| 4 | RA    | AM Progr  | am with Malicious Security                | 35   |

|   | 4.1   | Introduc  | etion                                     | . 35 |

|   |       | 4.1.1     | Our contribution                          | . 37 |

|   | 4.2   | Prelimin  | aries                                     | . 39 |

|   |       |           | Garbling Scheme                           |      |

|   | 4.3   | Batching  | g Protocol                                | . 41 |

|   |       | 4.3.1     | High-level Overview                       | . 41 |

|   |       | 4.3.2     | Detailed Protocol Description             |      |

|   |       |           | Efficiency and Parameter Analysis         |      |

|   |       |           | Security Proof                            |      |

|   |       |           | Optimizations                             |      |

|   | 4.4   |           | ng Cut-and-choose Protocol                |      |

|   |       |           | High-level Overview                       |      |

|   |       |           | Detailed Protocol Description             |      |

|   |       |           | Security Proof                            |      |

|   |       |           | Integrating Cheating Recovery             |      |

| 5 | Co    | onclusion |                                           | 72   |

| В | iblio | graphy    |                                           | 73   |

| A | pper  | ndices    |                                           | 80   |

|   | A     | Streamin  | ng Cut-and-choose Protocol Efficiency     | . 81 |

|   | В     | Concrete  | e Bounds for Batch Preprocessing Protocol | . 85 |

# LIST OF FIGURES

| Figure |                                                                                                                             | Page |

|--------|-----------------------------------------------------------------------------------------------------------------------------|------|

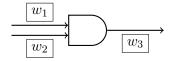

| 2.1    | And gate                                                                                                                    | 9    |

| 2.2    | 1-out-of-2 oblivious transfer functionality $\mathcal{F}_{ot}$                                                              | 10   |

| 2.3    | Ideal functionality $\mathcal{F}_{\sf otc}$ for committing oblivious transfer                                               | 11   |

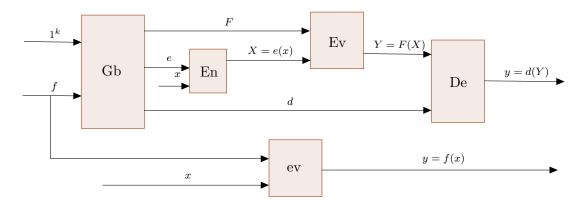

| 2.4    | Description of garbling scheme                                                                                              | 12   |

| 2.5    | Ideal functionality $\mathcal{F}_{com}$ for commitment                                                                      | 16   |

| 2.6    | XOR-homomorphic commitment functionality $\mathcal{F}_{xcom}$                                                               | 16   |

| 2.7    | Ideal functionality $\mathcal{F}^{\mathcal{R}}_{ZK}$ for zero-knowledge proofs of NP-relation $\mathcal{R}$                 | . 17 |

| 3.1    | Ideal functionality $\mathcal{F}_{Aut}$ for authenticated array access                                                      | 20   |

| 3.2    | Ideal functionality $\mathcal{F}_{\sf cpfe}$ for committing private function evaluation                                     | 20   |

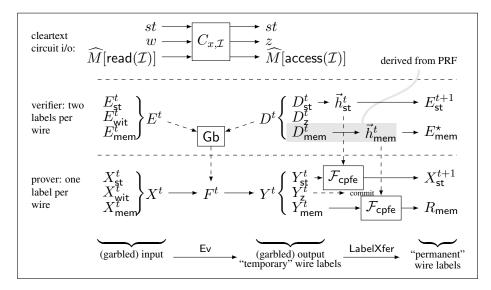

| 3.3    | Summary of variables and notation used in the protocol                                                                      | 27   |

| 3.4    | Ideal functionality $\mathcal{F}_{init}$ for initializing an ORAM program along with wire labels                            | 29   |

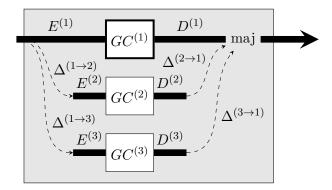

| 4.1    | Illustration of $MkBucket(\mathcal{B} = \{1, 2, 3\}, hd = 1)$                                                               | 44   |

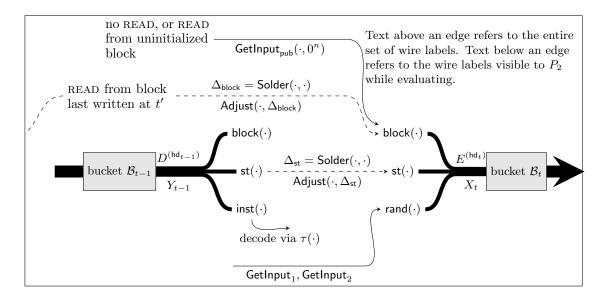

| 4.2    | Overview of soldering and evaluation steps performed in the online phase.                                                   | 45   |

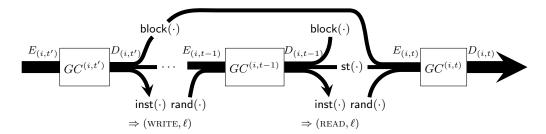

| 4.3    | Wire-label reuse within a single thread $i$ , in the streaming cut-and-choose protocol                                      | 58   |

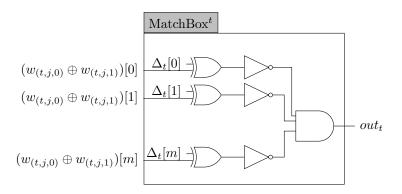

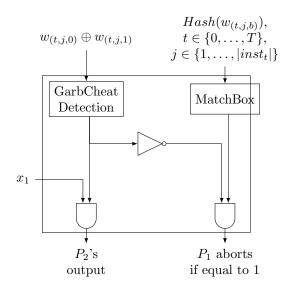

| 4.4    | Cheating recovery component 1: MatchBox. Where $\Delta_t[i]$ denotes the <i>i</i> th bit of $\Delta_t$ and $m =  \Delta_t $ | 70   |

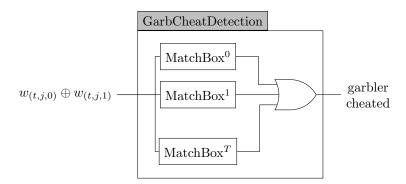

| 4.5    | Cheating Recovery component 1: Garbler Cheating Detection                                                                   | 70   |

| 4.6    | Final Circuit                                                                                                               | 71   |

# LIST OF TABLES

| <u>Table</u> |                              |      |      |  |  |  |  |  | Pa | age |

|--------------|------------------------------|------|------|--|--|--|--|--|----|-----|

| 2.1          | Garbled table for AND gate . | <br> | <br> |  |  |  |  |  |    | 9   |

# LIST OF APPENDIX TABLES

| Table |                                                                      | Page |

|-------|----------------------------------------------------------------------|------|

| A.1   | Comparison of "overhead" of naive implementation with streaming cut- |      |

|       | and-choose approach                                                  | . 84 |

#### Chapter 1: Introduction

The concept of secure two-party computation in the presence of semi-honest adversary was introduced by Yao in [55]. It allows two parties to jointly perform computations on their private inputs without leaking any information about their input beyond what is deducible from the output of computation. Namely, there are two parties Alice and Bob with their respective private input x and y, and they wish to cooperatively evaluate a polynomial-time computable function  $f(x,y) = (f_1(x,y), f_2(x,y))$  such that Alice receives output  $f_1(x,y)$  and Bob receives output  $f_2(x,y)$ . Besides the output, they should learn no useful information about the other parties' private input. A more general case is multi-party computation (MPC) rather than two parties. There are many situations in the real world that can take advantage of multi-party computation. For example, in electronic voting, voters want to choose a new president but are unwilling to reveal who they voted for. Another common situation is an auction, all parties want to find out the highest bidder but they do not want let others know their pricing strategy.

A naive way to achieve this is to find a trusted third party to gather all inputs, do the computation and announce the results to all parties. In the real world, a trusted third party can be a lawyer, a well-known company or government. However, sometimes it is hard to find a trusted third party, so we want a good "strategy" that can simulate the trusted party and perform the computation. Normally, a good "strategy" must achieve some security properties such as correctness, privacy, authenticity etc.

In cryptography, such strategy is called protocol. It implements the functionality of a trusted third party: performing the computation while still keeping the privacy of each party's input. Originating from the works [55, 16], there are significant improvements in designing and implementing a practical secure computation protocol. These techniques are mostly restricted to functions represented as boolean or arithmetic circuits. However, the conversion to circuit may lead to a huge blowup both in circuit size and running time. In addition, in the real world, the majority of applications we encounter in practice are more efficiently captured using random-access machine (RAM) programs that allow constant-time memory lookup. For example, to search an element in a large database,

efficient programs such as binary search can run in sub-linear time in the size of data. To convert it to a circuit, there are known polynomial transformations between RAM programs, Turing Machines and circuits. Given a RAM program with running time T, we can convert it to a Turing machine with running time  $O(T^3)$  [10]; and such Turing machine can be transformed to a circuit of size  $O(T^3 \log T)$  [44]. Therefore, by converting a RAM program to a circuit, it incurs an expensive time lose.

An variant of RAM program is oblivious RAM (ORAM). ORAM is a secure implementation of RAM program computation. It was first introduced by Goldreich and Ostrovsky [18] to protect software from illegitimate duplication. Different from the regular RAM program, an ORAM program can hide the information of both data and access pattern. In section 2.4, we present more details about ORAM programs.

# 1.1 Security Concerns

In this section, we introduce some fundamental notions in cryptography.

# 1.1.1 Adversary

To model security, we first need to model our adversary. That is, if a party is corrupted by an adversary, what can the adversary do when performing the computation? The security definition depends on the assumptions of adversary's ability. In general, there are two main adversary models that have been considered:

- **Semi-honest:** Also called "passive". In this model, the adversary follows the protocol correctly as an honest party, but tries to learn some unauthorized information from the transcript of messages it received during the computation.

- Malicious: Also called "active". In contrast to the semi-honest model, the malicious adversary can deviate arbitrarily from the protocol during the computation.

Usually, we prefer our protocol to protect against malicious adversaries. In this case, it guarantees that an attack to the protocol can succeed only with negligible probability. However, it also requires more cost and has less efficiency than semi-honest model.

Another important distinction of adversary in MPC is between adaptive and non-adaptive. An adaptive adversary allows to choose parties to be corrupted throughout the computation while a non-adaptive adversary allows to control arbitrary but fixed set of corrupted parties.

### 1.1.2 Ideal Functionality and Protocol

Functionality defines what a trusted third party can do for the computation. We usually refer it as in the ideal world, it describes what kind of computation task we want to achieve. The ideal functionality repeatedly receives inputs from all parties and sends back appropriate output values to them. It guarantees that all parties' outputs have the expected properties with respect to their inputs.

A functionality is called *reactive* if new input values are received and new output values are generated throughout the computation. <sup>1</sup> Otherwise a functionality is called *non-reactive* if it is just waiting for inputs from all parties and sends corresponding outputs back to them.

A protocol  $\pi$  for a functionality  $\mathcal{F}$  is an algorithm that consists of all parties exchanging information with each other to compute the same result as the functionality. A protocol with n participants is called an n-party protocol. We usually refer to protocols in the real world, it implements the task of a ideal functionality.

# 1.1.3 Security Analysis

To analyze the security of the protocol, we usually use  $real/ideal\ world$  paradigm, introduced by Goldreich, Micali, and Wigderson [16]. In this paradigm, the real world has all parties engage in a protocol while the ideal world has all parties simply send their input to a trusted third party (the functionality) who performs the computation. We say that the protocol securely implements the functionality if the real world is as secure as the ideal world. Namely, let  $\mathcal{S}$  be a simulator (usually is an algorithm) that takes whatever the adversary can see in the ideal world,  $\mathcal{S}$  simulates the view that the adversary sees in the real world. We use  $\text{view}_{\mathcal{S}}$  to denote the simulated real world view described by simulator  $\mathcal{S}$ , and use  $\text{view}_{\mathcal{R}}$  to denote the real view in the real world. If one can not

<sup>&</sup>lt;sup>1</sup>Even if the new inputs are chosen based on previous outputs.

efficiently distinguish between  $\mathsf{view}_{\mathcal{S}}$  and  $\mathsf{view}_{\mathcal{R}}$ , then the adversary learns nothing new from the protocol execution. In other words, if an adversary can attack the real world interaction, it can also attack the ideal world interaction and achieve the same effect.

In multi-party computation, all parties' inputs are chosen independent of other parties' input. In the ideal world, the trusted third party takes all parties' input, performs the computation and sends the corresponding result to each party. Whatever can be seen in the real world for each party must be also learned only from party's output in the ideal world. Both views should be computational indistinguishable. We will discuss more about indistinguishability in section 2.1.

The security described above is called *standalone security*. However, it only address the case that a single protocol execution is considered and it does not guarantee the security when a protocol instance may run concurrently with other protocols. Thus, we adopt the framework by Canetti [8] which is called *Universally Composable Security* or *UC-Security*. Here we only give a brief overview, and refer the reader to [8] for the full definition.

**Environments.** This framework uses the notion of an *external environment* to model contexts in which a protocol might be asked to execute. The environment interacts with all parties throughout the execution and tries to help the adversary. It sends some inputs to parties and receives outputs from them. Indeed, environment interacts with the protocol execution twice.

- First, it sends arbitrary inputs to the parties and to the adversary, and then it receives the outputs from the parties and the adversary.

- Second, the environment outputs a single bit, which indicates whether the environment thinks that it has interacted with the real protocol or with the ideal functionality.

**Dummy protocol.** An important protocol in this UC framework is called the *dummy* protocol, denoted by  $\pi_{dummy}$ , it prescribes the same behavior for each party as they would execute protocol  $\pi$  in the real world.

**Execution.** Let  $\mathcal{F}$  be a functionality,  $\pi$  be a protocol,  $\mathcal{A}$  be an adversary, and  $\mathcal{Z}$  be an environment, we define  $\mathsf{EXEC}(\mathcal{F}, \pi, \mathcal{A}, \mathcal{Z}, k)$  to be the random variable of the environment  $\mathcal{Z}$ 's output, it can be only 0 or 1. Here k is the secure parameter.

**Definition 1** ([48]). Let  $\mathcal{F}$  and  $\mathcal{G}$  be functionalities, and  $\pi$  be a protocol, we say  $\pi$  is a secure realization of  $\mathcal{F}$  in the  $\mathcal{G}$ -hybrid setting if for all PPT real-world adversaries  $\mathcal{A}$ , there exists another PPT adversary (called a simulator)  $\mathcal{S}$  such that for all PPT environments  $\mathcal{Z}$ , we have

$$Pr[\mathsf{EXEC}(\mathcal{G}, \pi, \mathcal{A}, \mathcal{Z}, k) = 1] \approx Pr[\mathsf{EXEC}(\mathcal{F}, \pi_{\mathsf{dummy}}, \mathcal{S}, \mathcal{Z}, k) = 1]$$

Here we refer  $\pi$  and  $\mathcal{G}$  as in the real world, while refer  $\pi_{\text{dummy}}$  and  $\mathcal{F}$  as in the ideal world. This definition implies that the real world is as secure as the ideal world. In other words, whatever an adversary can do to attack against  $\pi$  in the real world can also be done in the ideal world.

Now we come up with the fundamental result in the UC framework as follows:

**Theorem 2** ([8]). If  $\pi$  is a secure realization of  $\mathcal{F}$  in the  $\mathcal{G}$ -hybrid world, and  $\rho$  is a secure realization of  $\mathcal{G}$  in the  $\mathcal{H}$ -hybrid world, then  $\pi^{\rho}$  is a secure realization of  $\mathcal{F}$  in the  $\mathcal{H}$ -hybrid world, where  $\pi^{\rho}$  is the protocol  $\pi$  in which each external interface to an instance of  $\mathcal{G}$  is replaced with an instance of  $\rho$ .

In other words, if  $\mathcal{G}$  is a functionality in protocol  $\pi$ , we can always replace  $\mathcal{G}$  with its secure protocol  $\rho$  and vice versa.

#### 1.2 Our contribution

In this section, we present a brief overview about what are achieved in this thesis.

# 1.2.1 ORAM Application in Zero-knowledge Proof

In chapter 3, we present a practical application of ORAM in zero-knowledge proof. We describe a zero-knowledge proof system in which a prover holds a large dataset M and can repeatedly prove NP relations about that dataset. Each proof requires only constant number of rounds of interaction and has sublinear amortized cost in |M|. In addition,

the storage requirement between proofs for the verifier is constant. Our construction combines an Oblivious RAM and garbled circuits, but without using cryptographic operations inside the garbled circuits as in current garbled-RAM constructions, and thus has a high efficiency in communication/computation complexity.

This work represents joint work with Mike Rosulek from Oregon State University and Payman Mohassel from Yahoo Labs, and will appear in conference CRYPTO 2015.

# 1.2.2 RAM Program with Malicious Security

In chapter 4, we present the first practical protocols for evaluating RAM programs with security against malicious adversaries. Our RAM protocols achieve ratios matching the state of the art for circuit-based 2PC, the extra overhead of obtaining malicious security for RAM programs (beyond what is needed for circuits) is minimal and does not grow with the running time of the program. We introduce two protocols, which use different approaches for reusing wire labels. The first protocol uses ideas from the LEGO paradigm for 2PC [41, 13] and the second protocol directly reuses wire labels without soldering. We also show how to incorporate the input recovery technique of [32] for reducing the number of circuits by a factor of three.

This work represents joint work with Arash Afshar from University of Calgary, Payman Mohassel from Yahoo Labs and Mike Rosulek from Oregon State University, and is appeared in conference EUROCRYPT 2015 [1].

# Chapter 2: Preliminary

In this section, we introduce some basic notations and preliminary notions and definitions that used throughout this work.

#### 2.1 Basic Notation

Let  $\mathbb{N}$  denotes the set of natural numbers  $\{0,1,2,\ldots\}$  and let  $k \in \mathbb{N}$  be the security parameter. We say a function  $\epsilon : \mathbb{N} \to [0,1]$  is negligible if for any polynomial p, there exists a large enough k' such that for all k > k',  $\epsilon(k) < 1/p(k)$ . We say that a probability  $\Pr(k)$  is overwhelming if  $1 - \Pr(k)$  is a negligible function in k.

Let  $\mathcal{D}_0$  and  $\mathcal{D}_1$  be two discrete probability distributions. A **distinguisher**  $\mathcal{A}$  is a deterministic algorithm that outputs either 0 or 1. We define the bias of  $\mathcal{A}$  in distinguishing  $\mathcal{D}_0$  from  $\mathcal{D}_1$  as:

bias

$$(\mathcal{A}, \mathcal{D}_0, \mathcal{D}_1) = \left| \Pr[x \leftarrow \mathcal{D}_0 : \mathcal{A}(x) = 1] - \Pr[x \leftarrow \mathcal{D}_1 : \mathcal{A}(x) = 1] \right|$$

and define the statistical distance between distributions  $\mathcal{D}_0$  and  $\mathcal{D}_1$  as:

$$\Delta(\mathcal{D}_0,\mathcal{D}_1) = \max_{\mathcal{A}} \operatorname{bias}(\mathcal{A},\mathcal{D}_0,\mathcal{D}_1)$$

We say that two distributions  $\mathcal{D}_0$  and  $\mathcal{D}_1$  are computationally indistinguishable if for all polynomial-time distinguisher  $\mathcal{A}$ , the bias of  $\mathcal{A}$  in distinguishing  $\mathcal{D}_0$  from  $\mathcal{D}_1$ :

$$\Pr[x \leftarrow \mathcal{D}_0 : \mathcal{A}(x) = 1] - \Pr[x \leftarrow \mathcal{D}_1 : \mathcal{A}(x) = 1]$$

is negligible.

For an integer n, we define  $[n] = \{1, 2, \dots, n\}$ .

#### 2.2 Hash Function and Strongly Universal Hashing

A hash function  $h: \{0,1\}^* \mapsto \{0,1\}^n$  is any function that takes arbitrary-length input and has fixed length output. We say x, x' with  $x \neq x'$  are a collision under h if h(x) = h(x'). And h is collision resistant if for all PPT algorithms, the probability that we can find a collision in h is negligible.

A hash function family  $\mathcal{H}$  is a set of hash functions where each hash function in  $\mathcal{H}$  has the same output length. We also require the collision resistant property, in a hash function h which is chosen uniform randomly from the family. Notice that the difficulty of finding collisions now rests in the random choice of functions. Even an adversary can know every fact about  $\mathcal{H}$ , it still doesn't know which  $h \in \mathcal{H}$  it is going to be challenged to find a collision.

Let  $\mathcal{H}$  be a hash function family and each function  $h \in \mathcal{H}$  has the form  $h : A \mapsto B$ , then  $\mathcal{H}$  is strongly universal if for all distinct  $a, a' \in A$  and all (possibly equal)  $b, b' \in B$ ,

$$\Pr_{b \leftarrow \mathcal{H}}[h(a) = b \land h(a') = b'] = 1/|B|^2$$

One choice of strongly universal families is linear functions. In a finite field  $\mathbb{F}$ , define function  $f_{a,b}(x) \mapsto ax + b$ ,  $a, b \in \mathbb{F}$ , then the class of functions  $\{h_{a,b}|a, b \in \mathbb{F}\}$  is a strongly universal function family.

# 2.3 Garbled Circuit and Garbling Scheme

#### 2.3.1 Garbled Circuit

The first solution for secure two-party computation was also introduced by Yao [56]. The idea is by using the technique garbled circuits. Denote party  $P_1$  as the sender with input x and  $P_2$  as the receiver with input y. Let f to be the function that they wish to compute. For simplicity, we assume  $f_1(x,y) = f_2(x,y)$ . The first step is to express f as a boolean circuits  $C_f$ . Then  $P_1$  garble the circuit and sends it to  $P_2$ . Such circuit reveals nothing since it is encrypted.  $P_2$  evaluates the circuit based on input (x,y) to obtain the output f(x,y) and then announce the results. During the evaluation,  $P_2$  should only learn the output f(x,y). Other messages that  $P_1$  and  $P_2$  receive must leak no information.

Consider the evaluation of a circuit, a circuit is computed gate by gate, from the input wire to the output wire. Consider a fan-in to 2, and fan-out to 1 gate g in figure 2.1, the gate input wires  $w_1, w_2$  has value  $\alpha, \beta \in \{0, 1\}$ , then we can obtain the value  $g(\alpha, \beta)$  of gate output wire  $w_3$ . We keep doing this until all gates are evaluated. The value of circuit outputs wires are the output of circuit.

Figure 2.1: And gate

Next we show how to garble a circuit and how to evaluate it. Consider the same AND gate g with input wires  $w_1$ ,  $w_2$  and output wire  $w_3$ . The general idea of Yao's protocol is to generate two keys(also called wire labels) for each wire, and it does not reveal anything about the original wire values. For the AND gate g, we generate two random cryptographic keys  $k_i^0$  and  $k_i^1$  for wire  $w_i$ . Here  $k_i^0$  represents the value 0 and  $k_i^1$  represents the value 1. Notice that if one receives  $k_i^{\sigma}$ ,  $\sigma \in \{0,1\}$ , it can not tell  $\sigma$  is 0 or 1 since the keys have identical distribution. Now we have  $k_1^0$ ,  $k_1^1$  for input wire  $w_1$ ,  $k_2^0$ ,  $k_2^1$  for input wire  $w_2$  and  $k_3^0$ ,  $k_3^1$  for output wire  $w_3$ . Next we have the output value  $k_3^0$ ,  $k_3^1$  encrypted under the corresponding keys from the input wires. See the garbled table for AND gate g:

| Input wire $w_1$ | Input wire $w_2$ | Output wire $w_3$ | Encryption table                                                |

|------------------|------------------|-------------------|-----------------------------------------------------------------|

| $k_{1}^{0}$      | $k_2^0$          | $k_{3}^{0}$       | $\operatorname{Enc}_{k_1^0}(\operatorname{Enc}_{k_2^0}(k_3^0))$ |

| $k_1^0$          | $k_2^1$          | $k_3^0$           | $\operatorname{Enc}_{k_1^0}(\operatorname{Enc}_{k_2^1}(k_3^0))$ |

| $k_1^1$          | $k_2^0$          | $k_3^0$           | $\operatorname{Enc}_{k_1^1}(\operatorname{Enc}_{k_2^0}(k_3^0))$ |

| $k_1^1$          | $k_2^1$          | $k_3^1$           | $\operatorname{Enc}_{k_1^1}(\operatorname{Enc}_{k_2^1}(k_3^1))$ |

Table 2.1: Garbled table for AND gate

Here **Enc** is a private-key encryption scheme that is secure under *chosen plaintext* attacks. An example for **Enc** suggested in [34] is:

$$\mathbf{Enc}_k(x) = \langle r, f_k(r) \oplus x0^n \rangle$$

• On input  $(x_0, x_1)$  from party  $P_1$ , and input  $\sigma \in \{0, 1\}$  from  $P_2$ , sends delayed output  $x_{\sigma}$  to  $P_2$  and  $\bot$  to  $P_1$ .

Figure 2.2: 1-out-of-2 oblivious transfer functionality  $\mathcal{F}_{ot}$

where  $x \in \{0,1\}^n$ ,  $r \in_R \{0,1\}^n$ ,  $f_k : \{0,1\}^n \to \{0,1\}^{2n}$  for  $k \in \{0,1\}^n$  is a pseudorandom function. Now if we have two input wire keys, we can obtain the corresponding output wire key by decrypting the four entries in the garbled table. It is guaranteed that only one ciphertext can be decrypted correctly. Meanwhile, the original value of wire  $w_i$  is still hidden. This is because the fact that the evaluator does not know the key is associated with zero or one.

To securely evaluate function f,  $P_1$  generates the circuit  $C_f$  and sends her wire labels to  $P_2$  according to her input x. Now if  $P_2$  knows his corresponding wire labels, then  $P_2$  can evaluate the circuit. Notice that  $P_1$  has both wire labels and  $P_2$  has his own input value y. However,  $P_1$  does not know which wire label he should send to  $P_2$  since he can not know y. Thus, we need a technique to let  $P_2$  receives his corresponding wire labels.

#### 2.3.2 Oblivious Transfer

To solve the above problem, Robin introduced oblivious transfer (OT) in [46]. Generally speaking, a k-out-of-n OT is a protocol in which the sender has a list of n messages  $\{m_1, \dots, m_n\}$ , the receiver receives k of them without learning anything about other n-k messages. Also, the sender would have no idea about which k messages the receiver has received. Throughout this work, we will use 1-out-of-2 OT as defined in figure 2.2. In standard 1-out-of-2 OT, party  $P_1$  inputs two messages  $(x_0, x_1)$ , and party  $P_2$  has input  $\sigma$ . After running oblivious transfer, P receives  $x_{\sigma}$ .

Committing oblivious transfer The definition of committing oblivious transfer was first given by Kiraz and Schoenmakers [27]. It works the same as a standard OT except that the "committing" aspect allows party  $P_2$  to reveal  $(x_0, x_1)$  at a later time. The ideal functionality  $\mathcal{F}_{\text{otc}}$  is defined in Figure 2.3.

- Initialization:  $\mathcal{F}_{\text{otc}}$  takes private input  $(x_0, x_1, id)$  from party  $P_1$  and the private input  $\sigma \in \{0, 1\}$  from party  $P_2$ , then stores  $(x_0, x_1, id, \sigma)$  internally and output COMMITTED.

- Transfer: On command (TRANSFER, id) from  $P_1$ ,  $\mathcal{F}_{\sf otc}$  sends (TRANSFERRED,  $x_{\sigma}$ , id) to  $P_2$ .

- Open: On command (OPEN, id) from  $P_1$ ,  $\mathcal{F}_{otc}$  sends (OPENED,  $x_0, x_1, id$ ) to  $P_2$ .

Figure 2.3: Ideal functionality  $\mathcal{F}_{otc}$  for committing oblivious transfer.

# 2.3.3 Garbling Scheme

In section 2.3.1, we have a brief overview about how to use garbled circuit to implement two party secure computation. We have to interpret f as a circuit, and then garble such circuit and evaluate it. In this section, we present a high level abstraction of the garbled circuit from [5]. The abstraction formalize garbled circuits into a primitive which they call garbling scheme. Bellare  $et\ al.$  abstract versatile syntax and security definitions such that any garbled circuit satisfies their abstraction.

# 2.3.3.1 Syntax

A garbling scheme can be defined as a five-tuple algorithm:  $\mathcal{G} = (\mathsf{Gb}, \mathsf{En}, \mathsf{De}, \mathsf{Ev}, \mathsf{ev}).$  Denote  $f:\{0,1\}^n \to \{0,1\}^m$  to be the function that we want to evaluate, let x to be the original input and y = f(x) to be the final output. Then  $\mathsf{Gb}$  is a randomized algorithm that transform f into a new triple of functions (F,e,d). En is an algorithm that takes (e,x) as the input and outputs garbled input  $X = \mathsf{En}(e,x)$ . Ev takes input (F,X) and outputs the garbled output  $Y = \mathsf{Ev}(F,X)$ . De is an algorithm that transforms garbled output Y to the final output  $Y = \mathsf{De}(d,Y)$  and we have  $\mathsf{De}(d,Y) = \mathsf{ev}(f,x)$ . See figure 2.4 from [5]. Specifically, for a garbled circuit, we say  $\mathcal G$  is a circuit garbling scheme if  $\mathcal G$  as a circuit.

**Definition 3.** A garbling scheme  $\mathcal{G} = (\mathsf{Gb}, \mathsf{En}, \mathsf{De}, \mathsf{Ev}, \mathsf{ev})$  satisfies correctness if for all f and for all x, it holds the condition that

$$De(d, Ev(F, En(e, x))) = ev(f, x)$$

Figure 2.4: Description of garbling scheme

# 2.3.3.2 Security

In [5], the security of a garbling scheme can be abstracted into three properties: Privacy, Obliviousness and Authenticity. Let  $\Phi$  be the side information function that represents the information we expect to reveal for the garbling scheme.

1. **Privacy** For a simulation based privacy, it requires that whatever can be learned from (F, X, d) can also be learned by just knowing the final output y and side information function  $\Phi$ . More formally, we define privacy as follows.

**Definition 4.** A garbling scheme  $\mathcal{G} = (\mathsf{Gb}, \mathsf{En}, \mathsf{De}, \mathsf{Ev}, \mathsf{ev})$  satisfies privacy property if for every function f, input x, side information function  $\Phi$ , and for all PPT adversary  $\mathcal{A}$ , there exists a simulator  $\mathcal{S}$  such that the following difference:

$$\left|\Pr[\mathcal{A}(\mathcal{S}(1^k,y,\Phi(f))=1] - \Pr[\mathcal{A}(F,X,d)=1] : (F,e,d) = \mathsf{Gb}(1^k,f), X = \mathsf{En}(e,x)\right|$$

is negligible in  $k$ .

2. **Obliviousness**. Informally, obliviousness means when given Y = En(F, X) but not d, it does not leak any information about f, x, y beyond  $\Phi(f)$ .

**Definition 5.** A garbling scheme  $\mathcal{G} = (\mathsf{Gb}, \mathsf{En}, \mathsf{De}, \mathsf{Ev}, \mathsf{ev})$  satisfies obliviousness property if for every function f, input x, side information function  $\Phi$ , and for all

PPT adversary A, there exists a simulator S such that the following difference:

$$\left|\Pr[\mathcal{A}(\mathcal{S}(1^k,\Phi(f))=1] - \Pr[\mathcal{A}(F,X)=1] : (F,e,d) = \mathsf{Gb}(1^k,f), X = \mathsf{En}(e,x)\right|$$

is negligible in k.

3. Authenticity. Roughly speaking, authenticity means when given F and X, the adversary can not forge a valid Y such that  $Y \neq \text{Ev}(F, X)$  and  $d(Y) \neq \bot$ .

**Definition 6.** A garbling scheme  $\mathcal{G} = (\mathsf{Gb}, \mathsf{En}, \mathsf{De}, \mathsf{Ev}, \mathsf{ev})$  satisfies authenticity property if for every function f, input x, side information function  $\Phi$ , and for all PPT adversary  $\mathcal{A}$ , the following probability:

$$\Big|\Pr[\mathsf{De}(d,Y) \neq \bot, Y \neq \mathsf{Ev}(F,X) : (F,e,d) = \mathsf{Gb}(1^k,f), X = \mathsf{En}(e,x), Y = \mathcal{A}(F,X)]\Big|$$

is negligible in k.

#### 2.4 Oblivious RAM

Oblivious RAM (ORAM) programs were first introduced by Goldreich and Ostrovsky [18] to protect software from illegitimate duplication. This technique allows the CPU to hide all information about a RAM program, both the memory contents it accessed and its corresponding access patterns. In particular, if an adversary is eavesdropping the communication between the CPU and the memory, it can not tell what data the CPU is accessing and what memory the CPU is really trying to access. These information should look random to the adversary. The probability distribution of the access pattern must depend only on the input length rather than the input itself.

A more general application of ORAM is between a client with a limited memory and an untrusted server with a large memory. The client wants to store a large dataset on the server side and operate the data while still maintaining the privacy. An intuitive way is to encrypt the dataset before storing it to server. However, it still leaks the access pattern which contains significant sensitive information. Therefore, we use oblivious RAM program here to hide the information of both data and access pattern. Notice that an adversary can observe the physical locations that a client has accessed, but it

reveals nothing about the virtual memory and the physical access sequence should look random to the adversary.

In general, a ORAM program can be implemented as a circuit and running a ORAM program is identified as evaluating such corresponding deterministic next-instruction circuit  $\Pi$ . Assume that there is a ORAM program  $\Pi$  with its logical memory M. First we invoke a initialize function Initialize to encode the logical memory M into the physical memory array  $\widehat{M}$ :

$$(\widehat{M}, st) \leftarrow \mathsf{Initialize}(1^k, M)$$

At each evaluation step,  $\Pi$  checks its current ORAM state st, takes input of  $\Sigma$  and block where  $\Sigma$  is external input and block is the physical memory block data, outputs an instruction inst, next ORAM state and the corresponding data that is used for updating the memory block. The syntax of next-instruction circuit  $\Pi$  of a ORAM program is defined as follow:

$$(inst, st, block) \leftarrow \Pi(st, \Sigma, block)$$

The inst variable can only have one of the three forms: (READ, i), (WRITE, i), or (HALT, z). (READ, i) means the ORAM program to read data from block  $\widehat{M}[i]$  and assign it to block while (WRITE, i) means the ORAM program to write data block to the memory block  $\widehat{M}[i]$ . (HALT, z) indicates the ORAM program to terminate and output the final result z.

More formally, let  $\mathcal{I}$  denote the access sequence and  $r \leftarrow \{0,1\}^k$  be the external random input to the ORAM program, an execution of an ORAM program  $\Pi$  on input x with logical memory M is defined as follows:

```

\begin{split} & \underbrace{\operatorname{RAMEval}(\Pi,M,x)}_{\mathcal{I} := \, \emptyset, \, (\widehat{M},st) \leftarrow \operatorname{Initialize}(1^k,M)}_{\mathcal{I} := \, \emptyset, \, (\widehat{M},st) \leftarrow \operatorname{Initialize}(1^k,M)}_{(inst,st,block) := \, \Pi(st,x,\bot)} \\ & \text{do until inst has the form (halt,z):} \\ & block := [\operatorname{if} inst = (\operatorname{read},id) \operatorname{then} \widehat{M}[id] \operatorname{else} \bot] \\ & r \leftarrow \{0,1\}^k, \, (inst,st,block) := \Pi(st,r,block) \\ & \text{if } inst = (\operatorname{write},id) \operatorname{then} \, \widehat{M}[id] := block \\ & \mathcal{I} := \mathcal{I} \| inst \\ & \text{output } z \end{split}

```

The security definition of an ORAM program  $\Pi$  requires that the memory access sequence  $\mathcal{I}$  does not leak any information about the data set M or the input x. In other words, let  $\mathcal{I}(\Pi, M, x)$  be the random variable denotes the sequence of values taken by the *inst* variable in RAMEval $(\Pi, M, x)$ , then there exists a simulator  $\mathcal{S}$  such that, for all x and initially empty  $\widehat{M}$ , the output  $\mathcal{S}(1^k, z)$  is indistinguishable from  $\mathcal{I}(\Pi, M, x)$  where z is the final output of the RAM program on inputs x.

**Definition 7.** We say that  $\Pi$  is a **secure ORAM** if there exists an efficient simulator S such that, for all M, all  $(\widehat{M}, st) \leftarrow \text{Initialize}(1^k, M)$ , all x and z such that  $z = RAMEval(\Pi, M, x)$  and for all PPT A, the following difference:

$$\left| \Pr[\mathcal{A}(\mathcal{S}(1^k, z) = 1] - \Pr_r[\mathcal{A}(\mathcal{I}(\Pi, M, x)) = 1] \right|$$

is negligible in k.

# 2.5 Commitment and Zero-knowledge proof

#### 2.5.1 Commitment

The notion of commitment scheme is one of the most fundamental tool in cryptography. It allows one party to create a commitment c to a secret message m while still hiding the message from other parties, but later the party can choose to open the commitment and disclose m. It requires that the commitment must binding, which means once the commitment c is made, it is impossible to find another message m' such that m' and m has the same commitment c. The commitment functionality  $\mathcal{F}_{com}$  is defined in figure 2.5.

In addition to a standard commitment functionality  $\mathcal{F}_{com}$ , an XOR-homomorphic commitment scheme allows party  $P_1$  to disclose the XOR of two or more committed messages while keeps hiding the individual messages. The XOR-homomorphic commitment functionality  $\mathcal{F}_{xcom}$  is defined in figure 2.6.

Let  $\mathcal{M}$  denote the space of valid messages and the functionality is parameterized by an integer k.

- Commit: On input (COMMIT, m) from party  $P_1$  with  $m \in \mathcal{M}$  and  $m \in \{0, 1\}^k$ , if there is no value m already stored in memory, then  $\mathcal{F}_{\mathsf{com}}$  stores m internally and outputs COMMITTED to party  $P_2$ .

- Open: On input OPEN from  $P_1$ , if value m exists in memory, then  $\mathcal{F}_{\mathsf{com}}$  outputs (OPENED, m) to party  $P_2$ .

Figure 2.5: Ideal functionality  $\mathcal{F}_{\mathsf{com}}$  for commitment

The functionality is initialized with internal value i=1. It then repeatedly responds to commands as follows:

- On input (COMMIT, m) from  $P_1$ , store (i, m) internally, set i := i + 1 and output (COMMITTED, i) to both parties.

- On input (open, S) from  $P_1$ , where S is a set of integers, for each  $i \in S$  find  $(i, m_i)$  in memory. If for some i, no such  $m_i$  exists, send  $\bot$  to  $P_2$ . Otherwise, send  $(open, S, \bigoplus_{i \in S} m_i)$  to  $P_2$ .

Figure 2.6: XOR-homomorphic commitment functionality  $\mathcal{F}_{xcom}$ .

# 2.5.2 Zero-knowledge Proof

In zero-knowledge proof, a prover wants to convince a verifier that some NP statement x is true by using a valid witness w, and the verifier learns nothing except the validity of the statement. Typically, for any language  $\mathcal{L} \in \mathsf{NP}$  with some binary relation  $\mathcal{R}_{\mathcal{L}}$ , for all valid instances  $x \in \mathcal{L}$ , there exists a string w such that  $\mathcal{R}_{\mathcal{L}}(x,w) = 1$ . Otherwise, if  $x \notin \mathcal{L}$ , then for all string w we have  $\mathcal{R}_{\mathcal{L}}(x,w) = 0$ . The ideal functionality  $\mathcal{F}_{\mathsf{ZK}}^{\mathcal{R}}$  is defined in figure 2.7.

A zero-knowledge proof protocol must satisfy the following three properties:

- Completeness The prover can always convince the the verifier of true statements.

- Soundness False statement will not be accepted by the verifier, and the dishonest prover will be caught cheating with overwhelming probability.

- Zero-knowledge Roughly speaking, zero-knowledge means the verifier learns noth-

$\mathcal{F}_{\mathsf{ZK}}^{\mathcal{R}}$  is parametrized by a relation  $\mathcal{R}$ . It involves two parties: a prover P and a verifier V.

- Setup: On input (INIT, M) from P, if no previous INIT command has been given, then  $\mathcal{F}^{\mathcal{R}}_{\mathsf{ZK}}$  stores M internally.

- Proof: On input (Prove, sid, x, w) from P, if  $\mathcal{R}(M, x, w) = 1$ , output (Accept, sid, x) to V.

Figure 2.7: Ideal functionality  $\mathcal{F}^{\mathcal{R}}_{\mathsf{ZK}}$  for zero-knowledge proofs of NP-relation  $\mathcal{R}$

ing during the proof except that the statement is true. Formally, we require that there exists a efficient simulator S such that, for all PPT verifier, S can simulate all interactions of verifier with the prover.

# Chapter 3: Zero-Knowledge Proofs by using Oblivious RAM program

#### 3.1 Introduction

Since zero-knowledge proof plays such a important role in cryptography, there are many fundamental results show that for all languages in NP, there are zero-knowledge proofs, [12, 17, 23, 45]. However, it shows that they are too inefficient to be used in practical applications in the real world.

Besides these protocols of mainly theoretical interested, the recent work [49, 11, 7, 20] also introduce various protocols that are efficient enough for real world use. But all of their constructions were practical only for proving statements about certain algebraic structures such as proving knowledge of and relations for discrete logarithms, RSA public keys, and bilinear equations.

The recent work [24] combines zero-knowledge proof and garbled circuit and proposes a new approach that is suitable for general-purpose statements represented as boolean circuits. The general idea is to interpret the binary relation  $\mathcal{R}_{\mathcal{L}}$  as a function  $f_{\mathcal{R}}$  such that for some statement x,  $f_{\mathcal{R}}(w) = 1$  if w is a valid witness of x (which means  $\mathcal{R}_{\mathcal{L}}(x, w) = 1$ ) and otherwise  $f_{\mathcal{R}}(w) = 0$ . Then we can use Yao's garbled circuit technique to garble  $f_{\mathcal{R}}$  so both parties can evaluate the circuit. The security property of garbled circuit will guarantee the completeness, soundness and zero-knowledge requirements in zero-knowledge proofs.

In addition, a key observation here is that only the prover has input w to function  $f_{\mathcal{R}}$  while the verifier does not, which means there is no security needed for the verifier. Thus, some very efficient garbling schemes can be applied here. [29] shows that the number of ciphertexts we need for each gate in a garbled circuit can be reduced to 0,1, or 2. It significantly reduce the communication complexity and computational complexity, achieves a very practical use in the application world.

#### 3.1.1 Our results

Garbled circuit-based zero-knowledge proofs are very efficient and with the state-ofart circuit garbling technique [29, 30], zero-knowledge proofs can scale to statements of billions of gates. However, it still has limitations in some scenario. For example, a prover commits to a dataset S and wants to prove membership and non-membership statements x ( $x \in S$  and  $x \notin S$ ). Since garbled circuit is one time, we must construct a new circuit for each statement. Otherwise, the authenticity property of garbled circuit will not be guaranteed. This approach is so cumbersome and it becomes much worse when the dataset S is very large.

In our work, we introduce a new approach for zero-knowledge proof to address the problem that described above. We combines oblivious RAM and garbled circuit but without using cryptographic operations inside the garbled circuits as in current garbled-RAM constructions. It requires only a constant number of rounds of interaction. Also, in general we do not have to access the whole dataset, we only need the memory blocks that will be used in ORAM program. Therefore, the size of circuit ORAM is much smaller than [24].

Let  $\Pi$  be a oblivious RAM program and M is its corresponding memory blocks. For any statement x and witness w of the form  $\exists w : R(M,x,w) = 1$ , our solution is constant-round, and incurs online computation and communication cost that is linear in the running time of the RAM program, competitive with the best semi-honest 2PC for RAM programs [19], and hence sublinear in |M| for many applications of interest. Sublinear-time 2PC is not possible in general when expressing the NP relation as a boolean circuit. Furthermore, in our protocol the verifier maintains only constant storage space between multiple proofs.

#### 3.2 Preliminaries

# 3.2.1 Authenticated Array

An authenticated array allows one party to access all stored data and control over all modifications in the array, as the functionality  $\mathcal{F}_{Aut}$  is described in figure 3.1. A naive implementation is to let party to generate the array in the local storage. However, when the party V has minimal memory and it wants to store the array in some untrusted

party, then V need another way to guarantee the authenticity of such array. A simple solution is to use an *authenticated Merkle-tree*, with V storing only the root of the tree.

- Initialization: On input (INIT, N) from party V where  $N \in \mathbb{N}$ ,  $\mathcal{F}_{\mathsf{Aut}}$  initialize an array T of size N. For each T[i],  $i \in \{1, \ldots, N\}$ , set T[i] = 0.

- Update: On input (update, id, data) from party V, set T[id] = data and output (updated, id, data) to both parties.

- Open: On input (ACCESS, id) from party V, where  $id \in \{1, ..., N\}$ , send (ACCESSED, id, T[id]) to V.

Figure 3.1: Ideal functionality  $\mathcal{F}_{Aut}$  for authenticated array access.

#### 3.2.2 Committing Private Function Evaluation

Private function evaluation (PFE) takes input a function h from a sender and input x from a receiver, and gives output h(x) to the receiver. We define and use a committing variant of PFE in which the sender can later reveal the h that was used. The formal description is given in Figure 3.2. In addition, we also require that committing PFE supports a strongly universal class  $\mathcal{H}$  of functions.

$\mathcal{F}_{\mathsf{cpfe}}$  is parametrized by a class of functions  $\mathcal{H}$ , with each  $h \in \mathcal{H}$  having a common domain A.

- Evaluation: On input  $h \in \mathcal{H}$  from party V and input  $x \in A$  from party P, give output h(x) to party P. Remember h internally.

- Open: On input OPEN from party V, give output h to party P.

Figure 3.2: Ideal functionality  $\mathcal{F}_{\mathsf{cpfe}}$  for committing private function evaluation.

A feasible approach to implement  $\mathcal{F}_{\mathsf{cpfe}}$  is to use oblivious linear function evaluation (OLFE) [54]. Let  $\mathbb{F}$  be a finite field, then the class of functions of the form  $x \mapsto ax + b$  is strongly universal (with  $a, b \in \mathbb{F}$ ). OLFE takes input a, b from the sender and x from the receiver, and sends the output ax + b to the receiver.

# 3.2.3 Garbling Scheme

The garbling scheme we use in this work is slightly different from the standard garbling scheme in section 2.3.3. Recall that in the standard garbling scheme, we use X and Y to represent the real garbled input and garbled output respectively. When f is a circuit, to garble the circuit, we use E and D to represent the descriptions of input wire labels and output wire labels. So X is a subset of E and E is a subset of E. In other words, let E be a E array that represent a set of wire labels on E wire, For each wire E and E and E and E are two wire labels that encode false and true, respectively. For a truth value E, the corresponding wire labels are defined as E and E are two wire labels are defined as

Also, we have different security requirements in our protocol. Specifically, in zero-knowledge proof, we require the garbling scheme to satisfy *correctness* and *authenticity*. Since the circuit should only output 0 or 1 (depends on whether w is a valid witness) and verifier has no input, obliviousness and privacy are out of our consideration.

In addition to correctness and authenticity, we also require that the garbling scheme can be efficiently verified. That is, there exists an efficient algorithm  $\mathsf{Chk}$  which takes as input a boolean circuit, a garbled circuit F and input wire label description E such that:

$$\mathsf{Chk}(f, F, E) \to D \text{ or } \bot$$

For our work, we require a variant garbling scheme different from the standard one,

- $\mathsf{Gb}(1^k, f, E, D) \to F$ . Takes as input a boolean circuit f, descriptions of input wire labels E and output wire labels D, and outputs a garbled circuit F.

- $\text{En}(E,x) \to X = E|_x$ . Takes as input description of input wire labels E, a plaintext input x and outputs a garbled input X. In our schemes, encoding is always done via  $E|_x$ .

- $Ev(F,X) \to Y$ . Takes as input a garbled circuit F and a garbled input X and returns a garbled output Y.

$<sup>^{1}</sup>$ For each wire, E and D are wire labels includes both value 0 and 1, X and Y are wire labels only has value 0 or 1.

•  $\mathsf{Chk}(f, F, E) \to D$  or  $\bot$ . Takes as input a boolean circuit, a (purported) garbled circuit F and input wire label description E and outputs either D or an error indicator  $\bot$ .

and also has a different security requirements:

**Definition 8.** A garbling scheme satisfies correctness if:

1. For all circuits f, circuit-inputs x, and valid wire label descriptions E, D,

$$\mathsf{Chk}(f, F, E) = D \ whenever \ F \leftarrow \mathsf{Gb}(1^k, f, E, D)$$

2. For all circuits f, (possibly malicious) garbled circuits F and wire-label descriptions E,

$$\operatorname{Ev}(F, E|_x) = D|_{f(x)}$$

whenever  $\operatorname{Chk}(f, F, E) = D \neq \bot$

**Definition 9.** Let W denote the uniform distribution of  $m \times 2$  matrices as described above. A garbling scheme has **authenticity** if for every circuit f, circuit-input x, and PPT algorithm A, the following probability:

$$\Pr[\exists y \neq f(x), \tilde{D} = D|_y : E \leftarrow \mathcal{W}, F \leftarrow \mathsf{Gb}(1^k, f, E, D), \tilde{D} = \mathcal{A}(F, E|_x)]$$

is negligible in k.

#### 3.3 Protocol overview

Adapting to the ORAM setting, using constant rounds. We follow roughly the RAM-2PC paradigm of [19, 1], with some important differences. Let  $\Pi$  be an Oblivious RAM program with memory  $\widehat{M}$ , that implements  $R(M,x,\cdot)$ . We assume a trusted setup phase in which  $\Pi$ 's memory  $\widehat{M}$  and state st are initialized from M. The prover learns  $\widehat{M}$ , st, as well as a garbled encoding of these values (i.e., one wire label for each bit of memory & state); the verifier specifies the garbled encoding to be used (i.e., both wire labels for each bit). If we follow [19, 1] strictly, we would have both parties repeatedly evaluate the next-memory-access circuit of  $\Pi$ , updating memory  $\widehat{M}$ , until it halts. However, this would result in a protocol with one round of interaction for each memory access of  $\Pi$ .

<sup>&</sup>lt;sup>2</sup>We use M to refer to the logical RAM memory, and  $\widehat{M}$  to refer to the physical ORAM memory.

To see how to achieve the same effect in a constant number of rounds, imagine that when executing an ORAM program, the memory access pattern  $\mathcal{I}$  is known in advance. Then it is possible to express the entire computation in a single circuit. The circuit includes many copies of the RAM program's next-memory-access circuit, but is wired together under the assumption that the memory accesses will be  $\mathcal{I}$ . For example, if  $\mathcal{I}$  says that  $\Pi$  writes to some memory block at time 2, and later reads from the same memory block at time 10, then the memory-output wires of subcircuit copy #2 will be connected to the memory-input wires of subcircuit copy #10, and so on.

We can leverage this optimization in our setting because the prover knows all (plaintext) inputs to  $\Pi$ , including the contents of memory and the ORAM state. Hence, the prover can execute  $\Pi$  locally to determine the complete memory access pattern  $\mathcal{I}$ . Since  $\Pi$  is an oblivious RAM, its access pattern  $\mathcal{I}$  leaks no information about the inputs/memory/state, so the prover can safely send  $\mathcal{I}$  to the verifier. Using  $\mathcal{I}$ , the verifier constructs a *single* garbled circuit  $C_{x,\mathcal{I}}$  as described above. To prevent the prover from lying about the access pattern  $\mathcal{I}$ , the circuit recomputes the memory access pattern of  $\Pi$  and compares it to (hard-coded)  $\mathcal{I}$ .

Hence, this setting admits a constant-round solution based on ORAM, but avoiding tools like garbled RAM [38, 14] which incorporate expensive additional crypto circuitry into the garbled circuits.

Reusing M to perform many proofs. We follow the approach of [1], where the prover stores the ORAM memory and ORAM state encoded as wire labels from the various garbled circuits. The idea is that these wire labels can be reused directly as inputs to subsequent circuits, avoiding oblivious transfers for garbled circuit input. However, some modifications are required to adapt this idea to our setting.

After evaluating a garbled circuit, the prover holds a garbled output encoding of ORAM state & memory. The *authenticity* property of the garbling scheme guarantees that the prover knows at most one valid label per wire. As soon as the garbled circuit is opened, however, the prover learns both labels for each wire and authenticity is lost. The output wire labels are no longer useful for input to subsequent circuits, as the prover can now feed arbitrary garbled state/memory into subsequent garbled circuits. We need a mechanism to restore authenticity on all wire labels that may be later used (this includes the ORAM internal state as well as all memory locations that are read or written by the

garbled circuit).

Say the two wire labels on some output wire are  $y_0$  and  $y_1$ , and that the prover knows only  $y_b$ . Let us call  $y_0$  and  $y_1$  the temporary wire labels, since they will soon be discarded. The verifier chooses a random function h from a strongly universal hash family. Just before the garbled circuit is opened (clobbering wire-label authenticity), the parties perform a private function evaluation (PFE), where the prover gives  $y_b$ , the verifier gives h, and the prover learns  $h(y_b)$ . After the PFE, the garbled circuit can be opened, revealing  $y_0$  and  $y_1$ .

Define  $y'_0 = h(y_0)$  and  $y'_1 = h(y_1)$  to be the *permanent* wire labels for this wire. At the time of the PFE, the prover could not have guessed  $y_{1-b}$ , and so learned the output of h on some point that was not  $y_{1-b}$ . From strong universality of h, even if  $y_{1-b}$  is later revealed,  $y'_{1-b} = h(y_{1-b})$  is still random from the prover's point of view. Hence the PFE "transfers" the authenticity guarantee from the temporary wire labels  $y_0, y_1$  to the permanent ones  $y'_0, y'_1$ , preserving authenticity even after both of  $y_0, y_1$  are revealed. Hence,  $y'_0, y'_1$  are safe to use as input wire labels to subsequent garbled circuits.

For technical reasons, the PFE needs to be committing with respect to the input h (so that the verifier can later "open" the h that was used). We suggest two efficient instantiations of committing-PFE for strongly universal families: one based on oblivious linear function evaluation (OLFE) [54] and one based on the string-select variant of OT presented in [28].

Note that all the PFE instances can be run in parallel hence, maintaining the constant round complexity of the overall protocol.

Eliminating the verifier's storage requirement. As described so far, the verifier is required to keep track of two wire labels for each bit of  $\widehat{M}$ , at all times. We can decrease this burden somewhat by letting the verifier derive these wire labels from a PRF. Let s be a seed to a PRF. For simplicity, suppose a wire label encoding truth value b on the jth bit of the ith memory block, last accessed at time t, is chosen as  $\mathsf{PRF}(s,i||j||t||b)$ . In the actual protocol, the choice of wire labels is slightly more complicated.

Using this choice of wire labels, the verifier need only remember the last-access time of each block of  $\widehat{M}$ . However, this is still storage proportional to  $|\widehat{M}|$ . To reduce the storage even further, we "outsource" the maintenance of these last-access times to the prover. Let T[i] denote the last-access time of block i. We let the prover store the array

T authenticated by a Merkle tree for which the verifier remembers only the root node.<sup>3</sup>

Whenever the verifier is about to garble a circuit, he must be reminded of T[i] for each memory block i to be read by the RAM in its computation. We make the prover report each such T[i] to the verifier, authenticating each value via the Merkle tree. The ORAM circuit performs some reads & writes in  $\widehat{M}$ , so T and the Merkle tree are updated accordingly, for each memory block that was accessed. Note that all accesses to the Merkle tree are done at the same time (in parallel), and similarly for the updates at the end of the execution.

Overall, accessing/updating the authenticated array T adds polylogarithmic (in  $|\widehat{M}|$ ) communication/computation overhead and only a small constant number of rounds to the protocol. Instead of remembering two wire labels for each bit of  $\widehat{M}$ , the verifier need now remember only a PRF seed and the root of a Merkle tree.

# 3.4 Additional Notation and Helper Routines

**ORAM components:** Let  $\mathcal{I}$  be an ORAM memory access sequence. We define  $\operatorname{read}(\mathcal{I}) = \{i \mid (\operatorname{READ}, i) \in \mathcal{I}\}$ ,  $\operatorname{write}(\mathcal{I}) = \{i \mid (\operatorname{WRITE}, i) \in \mathcal{I}\}$ , and  $\operatorname{access}(\mathcal{I}) = \operatorname{read}(\mathcal{I}) \cup \operatorname{write}(\mathcal{I})$ ; i.e., the indices of blocks that are  $\operatorname{read/write/accessed}$  in  $\mathcal{I}$ . If  $S = \{s_1, \ldots, s_n\}$  is a set of memory-block indices, then we define  $M[S] = (M[s_1], \ldots, M[s_n])$ .

Let  $\Pi$  denote the next-instruction circuit of an ORAM. Given a zero-knowledge statement x and ORAM access sequence  $\mathcal{I}$ , we let circuit  $C_{x,\mathcal{I}}$  denote the following circuit:

$<sup>^{3}</sup>$ More generally, T can be stored in any authenticated data structure that provides small storage for the verifier.

```

\begin{split} & \frac{C_{x,\mathcal{I}}(st,w,\widehat{M}[\mathsf{read}(\mathcal{I})]):}{(inst,st,block) := \Pi(st,(x,w),\bot)} \\ & \text{for } i = 1 \text{ to } |\mathcal{I}| - 1: \\ & r \leftarrow \{0,1\}^k \\ & \text{if } \mathcal{I}[i] = (\text{READ},id) \text{ then:} \\ & (st,inst,\bot) \leftarrow \Pi(st,r,\widehat{M}[id]) \\ & \text{if } \mathcal{I}[i] = (\text{WRITE},id) \text{ then:} \\ & (st,inst,block) \leftarrow \Pi(\mathsf{st},r,\bot) \\ & \widehat{M}[id] = block \\ & \mathcal{I}' := \mathcal{I}'\|inst \\ & z := [\mathcal{I} \overset{?}{=} \mathcal{I}'] \\ & \text{return } (st,z,\widehat{M}[\mathsf{access}(\mathcal{I})]) \end{split}

```

As described in last section,  $C_{x,\mathcal{I}}$  is the circuit that will be garbled in the protocol. Note that both x and  $\mathcal{I}$  are hard-coded into  $C_{x,\mathcal{I}}$ . Also, the circuit verifies that  $\mathcal{I} = \mathcal{I}'$ , and this entails checking the correctness of the witness since the final element of  $\mathcal{I}$  is (HALT, TRUE).

Garbling notation: The circuit  $C_{x,\mathcal{I}}$  has 3 logical inputs and 3 logical outputs, and we must distinguish among them. When garbling the circuit via  $F \leftarrow \mathsf{Gb}(C_{x,\mathcal{I}}, E, D, 1^k)$ , we denote by E a description of input wire labels (i.e., two labels per wire) and D a description of output wire labels. We write  $E = E_{\mathsf{st}} \| E_{\mathsf{wit}} \| E_{\mathsf{mem}}$ , denoting the corresponding input wire labels for state, witness, and memory blocks, respectively. We define  $D = D_{\mathsf{st}} \| D_{\mathsf{z}} \| D_{\mathsf{mem}}$  similarly. When referring to a specific memory block i, we use notation  $E_{\mathsf{mem},i}$  and  $D_{\mathsf{mem},i}$ .

We use X to denote the prover's garbled input, and Y to denote the prover's garbled output (i.e., one label per wire). As above, we define  $X_{\mathsf{st}}$ ,  $X_{\mathsf{wit}}$ ,  $X_{\mathsf{mem}}$ ,  $Y_{\mathsf{st}}$ ,  $Y_{\mathsf{z}}$ ,  $Y_{\mathsf{mem}}$ . Finally, we have the prover maintain an array  $R_{\mathsf{mem}}$  at all times, containing the current wire labels for all of the ORAM memory  $\widehat{M}$ .

For an overview of the notation used in the protocol, see Figure 3.3.

**Temporary and permanent wire labels.** Recall from last section that the output wire labels of a circuit are "temporary" in the sense that their authenticity is lost when

Figure 3.3: Summary of variables and notation used in the protocol.

the garbled circuit is opened. We use PFE to transfer the authenticity property of these temporary wire labels to a different set of "permanent" wire labels.

We transfer authenticity with the LabelXfer subprotocol, where Y is a list of "temporary" wire labels (i.e., one label per wire), and  $\vec{h}$  is a list of elements from a strongly universal hash family  $\mathcal{H}$ .

Note that all instances of  $\mathcal{F}_{cpfe}$  are run in parallel and hence the protocol remains constant-round given that  $\mathcal{F}_{cpfe}$  is itself constant-round.

**Selecting wire labels.** Now let's consider how the verifier generates wire labels for the circuit. Recall from Section 3.3 that the verifier uses a PRF to generate wire labels corresponding to the ORAM memory, in order to reduce storage.

Since permanent wire labels are derived by applying strongly universal functions to

temporary wire labels, the verifier must also select strongly universal functions using the PRF to be able to reconstruct the choice of functions later.

Let s be the seed to a PRF. The verifier derives the *temporary* wire labels for a set S of memory block indices, last updated at time t, via the subroutine TempMemLabels. The verifier derives the choice of strongly universal functions via the subroutine GenH.

Finally, the verifier derives the *current*, *permanent* wire labels for a set S of memory block indices via the subprotocol PermMemLabels. Since each block may have been last accessed a different time, the authenticated array  $\mathcal{F}_{Aut}$  is referenced. For each block, the most recent temporary wire labels and strongly universal functions are reconstructed to derive the permanent wire labels.

```

func TempMemLabels(S, t):

D := \emptyset

for i \in S:

for j \in \{1, \dots, l\}, b \in \{0, 1\}:

\operatorname{prot} \operatorname{\mathsf{PermMemLabels}}(S):

D_i[j, b] = PRF(s, 0||i||j||t||b)

D := D \| D_i

for all i in S (in parallel):

return D

send (ACCESS, i) to \mathcal{F}_{\mathsf{Aut}}

receive t_i := T[i]

D_i := \mathsf{TempMemLabels}(\{i\}, t_i)

func GenH(S, t):

\vec{h} = \emptyset

\vec{h}_i := \mathsf{GenH}(\{i\}, t_i)

E_i := \vec{h}_i(D_i)

for i \in S:

for j \in \{1, ..., l\}:

E := E || E_i

\vec{h}_i[j] = \mathsf{PRF}(s, 1||i||j||t)

return E

\vec{h} := \vec{h} \| \vec{h}_i

return \vec{h}

```

When  $\vec{h}$  is an array of functions and D is a matrix of wire labels, the notation  $\vec{h}(D)$  refers to the matrix E whose entries are  $E[j,b] = \vec{h}[j](D[j,b])$ .

### 3.5 Detailed protocol

Now we present the full protocol  $\pi$ . We refer to the prover as P and the verifier as V. The setup phase uses the initialization functionality  $\mathcal{F}_{\mathsf{init}}$  defined in Figure 3.4.

- Initialize: On command (INIT, M) from P and (INIT,  $D_{\mathsf{st}}, D_{\mathsf{mem}}$ ), where M is logical ORAM memory, and  $D_{\mathsf{st}} \& D_{\mathsf{mem}}$  are wire label descriptions, run  $(st, \widehat{M}) \leftarrow \mathsf{Initialize}(1^k, M)$ . Give output  $(st, \widehat{M}, D_{\mathsf{st}}|_{st}, D_{\mathsf{mem}}|_{\widehat{M}})$  to P.

- Open: On command OPEN from V, give output  $(D_{st}, D_{mem})$  to P.

Figure 3.4: Ideal functionality  $\mathcal{F}_{init}$  for initializing an ORAM program along with wire labels.

**Setup:** On input M for prover P, let N denote the number of blocks in the ORAM encoding of M. Then both parties do the following:

1. V picks random wire label descriptions  $D_{\mathsf{st}}^0$  and computes

$$D_{\mathsf{mem}}^0 = \mathsf{TempMemLabels}([N], 0)$$

V also chooses a random PRF seed  $s \leftarrow \{0,1\}^k.$

- 2. P sends (INIT, M) to  $\mathcal{F}_{\mathsf{init}}$ ; V sends (INIT,  $D_{\mathsf{st}}^0, D_{\mathsf{mem}}^0$ ) to  $\mathcal{F}_{\mathsf{init}}$ . P receives output  $(st, \widehat{M}, Y_{\mathsf{st}}^0 = D_{\mathsf{st}}^0|_{st}, Y_{\mathsf{mem}}^0 = D_{\mathsf{mem}}^0|_{\widehat{M}})$ .

- 3. [Transfer wire-label authenticity]:<sup>4</sup>

- (a) V picks random vector  $\vec{h}_{\mathsf{st}}^0$  of strongly universal functions and sets  $E_{\mathsf{st}}^1 = \vec{h}_{\mathsf{st}}^0(D_{\mathsf{st}}^0)$ . The parties perform subprotocol LabelXfer $(Y_{\mathsf{st}}^0, \vec{h}_{\mathsf{st}}^0)$ , with P obtaining output  $\vec{h}_{\mathsf{st}}^0(Y_{\mathsf{st}}^0)$  which he stores as  $X_{\mathsf{st}}^1$ .

- (b) V picks vector  $\vec{h}_{\mathsf{mem}}^0 = \mathsf{GenH}([N], 0)$  and the parties perform subprotocol LabelXfer $(Y_{\mathsf{mem}}^0 \vec{h}_{\mathsf{mem}}^0)$ . P receives output  $\vec{h}_{\mathsf{mem}}^0(Y_{\mathsf{mem}}^0)$  which he stores as  $R_{\mathsf{mem}}$ .

- (c) V sends open to  $\mathcal{F}_{\mathsf{init}}$ , and P receives output  $(D^0_{\mathsf{st}}, D^0_{\mathsf{mem}})$ .

<sup>&</sup>lt;sup>4</sup>This step could be easily incorporated into  $\mathcal{F}_{init}$ , but is written separately so that the remainder of the protocol has no edge-cases involving t = 0.

4. P sends (INIT, N) to  $\mathcal{F}_{Aut}$  to initialize authenticated array T (with T[i] = 0 for all i).

**Proofs:** On input (x, w) for the prover, let this be the tth such proof. The parties do the following:

- 4. [ORAM Evaluation]:  $P \text{ runs } \mathcal{I} \leftarrow \mathsf{RAMEval}(\Pi, \widehat{M}, x, w, st)$ , then sends  $(x, \mathcal{I})$  to V. V aborts if  $\mathcal{I}$  is not an accepting access sequence. Note that RAMEval modifies  $\widehat{M}$  for the prover.

- 5. [Garbling the circuit]: V generates a garbled circuit as follows:

- (a) V chooses input wire labels to the circuit as follows:  $E_{\mathsf{wit}}^t$  are chosen randomly.  $E_{\mathsf{mem}}^t$  are chosen as  $E_{\mathsf{mem}}^t \leftarrow \mathsf{PermMemLabels}(\mathsf{read}(\mathcal{I}))$ . Recall that  $E_{\mathsf{st}}^t$  has been set previously.

- (b) V chooses output wire labels  $D_{\mathsf{z}}^t$  and  $D_{\mathsf{st}}^t$  randomly, and chooses  $D_{\mathsf{mem}}^t = \mathsf{TempMemLabels}(\mathsf{access}(\mathcal{I}), t)$ .

- (c) V sets  $E^t = E_{\mathsf{st}}^t \| E_{\mathsf{wit}}^t \| E_{\mathsf{mem}}^t$ , sets  $D^t = D_{\mathsf{st}}^t \| D_{\mathsf{z}}^t \| D_{\mathsf{mem}}^t$ , then invokes garbling algorithm  $F^t \leftarrow \mathsf{Gb}(1^k, C_{x,\mathcal{I}}, E^t, D^t)$ .

#### 6. [Evaluating garbled circuit]:

- (a) The parties invoke  $\mathcal{F}_{\text{otc}}$  with P giving input w and V giving input  $E_{\text{wit}}^t$ . P receives  $X_{\text{wit}}^t = E_{\text{wit}}^t|_w$ . Additionally, P finds  $X_{\text{st}}^t$  in its memory and sets  $X_{\text{mem}}^t = R_{\text{mem}}[\text{read}(\mathcal{I})]$ .

- (b) V sends  $F^t$  to P, and P evaluates the garbled circuit  $Y^t \leftarrow \mathsf{Ev}(F^t, X^t)$ .

- (c) P commits to  $Y_z^t$  (a single wire label) under  $\mathcal{F}_{\mathsf{com}}$

#### 7. [Transfer wire-label authenticity]:

- (a) V picks random vector  $\vec{h}_{\mathsf{st}}^t$  of strongly universal functions and sets  $E_{\mathsf{st}}^{t+1} = \vec{h}_{\mathsf{st}}^t(D_{\mathsf{st}}^t)$ . The parties perform subprotocol LabelXfer $(Y_{\mathsf{st}}^t, \vec{h}_{\mathsf{st}}^t)$ , with P obtaining output  $\vec{h}_{\mathsf{st}}^t(Y_{\mathsf{st}}^t)$  which he stores as  $X_{\mathsf{st}}^{t+1}$ .

- (b) V picks vector  $\vec{h}_{\mathsf{mem}}^t = \mathsf{GenH}(\mathsf{access}(\mathcal{I}), t)$  and the parties perform subprotocol LabelXfer $(Y_{\mathsf{mem}}^t, \vec{h}_{\mathsf{mem}}^t)$ . P receives output  $\vec{h}_{\mathsf{mem}}^t(Y_{\mathsf{mem}}^t)$  which he stores as  $R_{\mathsf{mem}}[\mathsf{access}(\mathcal{I})]$ .

#### 8. [Check garbled circuit]:

- (a) V sends OPEN to the  $\mathcal{F}_{otc}$ -instance from time t, and P receives output  $E_{wit}^t$ .

- (b) V sends OPEN to the PFE-instances used for the state wire labels in time t-1. The prover thus obtains  $\vec{h}_{\mathsf{st}}^{t-1}$  and sets  $E_{\mathsf{st}}^t = \vec{h}_{\mathsf{st}}^{t-1}(D_{\mathsf{st}}^{t-1})$ .

- (c) For each  $i \in \mathsf{read}(\mathcal{I})$ , verifier sends open to the PFE-instances used for memory block i in time T[i]. The prover thus obtains  $\vec{h}_{\mathsf{mem},i}^{T[i]}$  and sets  $E_{\mathsf{mem},i}^t = \vec{h}_{\mathsf{mem},i}^{T[i]}(D_{\mathsf{mem},i}^{T[i]})$ .

- (d) The verifier sets  $E^t = E_{\mathsf{st}}^t \| E_{\mathsf{wit}}^t \| E_{\mathsf{mem}}^t$  and runs  $D^t = \mathsf{Chk}(C_{x,\mathcal{I}}, F^t, E^t)$ . If the result is  $\bot$ , then V aborts. Otherwise, V opens his commitment to  $Y_{\mathsf{z}}^t$ .

- 9. [Check prover's output]: V checks whether  $Y_z^t = D_z^t|_{TRUE}$ . If not, then V aborts the protocol. Otherwise, V outputs (ACCEPT, t, x).

- 10. [Update T]: For all  $i \in \mathsf{access}(\mathcal{I})$  (in parallel), V sends (UPDATE, i, t) to  $\mathcal{F}_{\mathsf{Aut}}$ .

Other discussion. Our protocol is written in a hybrid model with access to various setup functionalities. In particular,  $\mathcal{F}_{cpfe}$  is a reactive functionality, and our protocol involves many  $(O(|\widehat{M}|))$  instances of  $\mathcal{F}_{cpfe}$  that remain "active" between ZK proofs. We have shown how the verifier's inputs to the  $\mathcal{F}_{cpfe}$  instances can be derived from a PRF, eliminating the need to explicitly store them. However, when these  $\mathcal{F}_{cpfe}$  instances are realized by concrete protocols, both parties are required to keep internal state between the PFE phase and opening phase. Hence, the verifier's random coins for the  $\mathcal{F}_{cpfe}$ -protocols should also be derived from a PRF. In that way, the verifier's entire view can be reconstructed as needed when it is time to OPEN each  $\mathcal{F}_{cpfe}$  instance.

# 3.6 Security proof

**Theorem 10.** The protocol  $\pi$  presented in Section 3.5 is a secure realization of the  $\mathcal{F}_{\mathsf{ZK}}^{\mathcal{R}}$  functionality.

*Proof.* We describe two simulators, depending on which party is corrupted.

Prover is corrupt: The primary role of the simulator in this case is to extract the witness from P. We construct the simulator in a sequence of hybrid interactions: