#### AN ABSTRACT OF THE DISSERTATION OF

<u>Jipeng Li</u> for the degree of <u>Doctor of Philosophy</u> in <u>Electrical and Computer</u> <u>Engineering</u> presented on <u>October 3, 2003</u>.

Title: Accuracy Enhancement Techniques in Low-Voltage High-Speed Pipelined

ADC Design

|                    | Redacted                                         | for privacy |  |

|--------------------|--------------------------------------------------|-------------|--|

| Abstract approved: | <del>-                                    </del> |             |  |

|                    |                                                  |             |  |

|                    | Un-K                                             | Tu Moon     |  |

Pipelined analog to digital converters (ADCs) are very important building blocks in many electronic systems such as high quality video systems, high performance digital communication systems and high speed data acquisition systems. The rapid development of these applications is driving the design of pipeline ADCs towards higher speed, higher dynamic range, lower power consumption and lower power supply voltage with the CMOS technology scaling. This trend poses great challenges to conventional pipelined ADC designs which rely on high-gain operational amplifiers (opamps) and well matched capacitors to achieve high accuracy.

In this thesis, two novel accuracy improvement techniques to overcome the accuracy limit set by analog building blocks (opamps and capacitors) in the context of low-voltage and high-speed pipelined ADC design are presented. One is the *time-shifted* correlated double sampling (CDS) technique which addresses the finite opamp gain effect and the other is the radix-based background digital calibration technique which can take care of both finite opamp gain and capacitor mismatch. These methods are simple, easy to implement and power efficient. The effectiveness of the proposed techniques is demonstrated in simulation as well as in experiment.

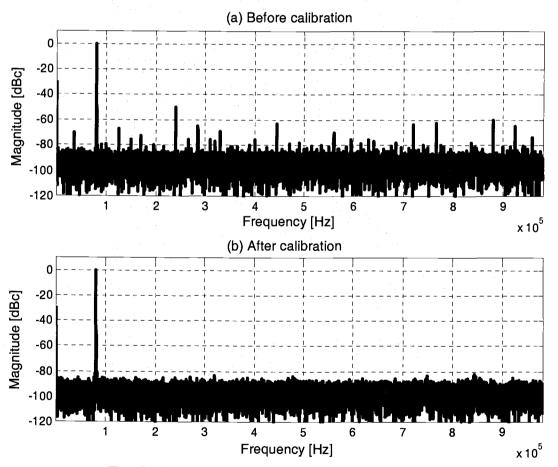

Two prototype ADCs have been designed and fabricated in 0.18µm CMOS technology as the experimental verification of the proposed techniques. The first ADC is a 1.8V 10-bit pipeline ADC which incorporated the time-shifted CDS technique to boost the effective gain of the amplifiers. Much better gain-bandwidth tradeoff in amplifier design is achieved with this gain boosting. Measurement results show total power consumption of 67mW at 1.8V when operating at 100MSPS. The SNR, SNDR and SFDR are 55dB, 54dB and 65dB respectively given a 1MHz input signal. The second one is a 0.9V 12-bit two-stage cyclic ADC which employed a novel correlation-based background calibration to enhance the linearity. The linearity limit set by the capacitor mismatches, finite opamp gain effects is exceeded. After calibration, the SFDR is improved by about 33dB and exceeds 80dB. The power consumption is 12mW from 0.9V supply when operating at 2MSPS.

©Copyright by Jipeng Li

October 3, 2003

All Rights Reserved

# Accuracy Enhancement Techniques in Low-Voltage High-Speed Pipelined ADC Design

by

Jipeng Li

### A DISSERTATION

submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Presented October 3, 2003 Commencement June 2004 Doctor of Philosophy dissertation of Jipeng Li presented on October 3, 2003

APPROVED:

Redacted for privacy

Major Professor, representing Electrical and Computer Engineering

Redacted for privacy

Director of the School of Electrical Engineering and Computer Science

Redacted for privacy

Dean of the Graduate School

I understand that my dissertation will become part of the permanent collection of Oregon State University libraries. My signature below authorizes release of my dissertation to any reader upon request.

Redacted for privacy

Jipeng Li, Author

#### **ACKNOWLEDGEMENTS**

I would like to thank Professor Un-Ku Moon, my advisor, for his encouragement and insightful guidance throughout my Ph.D. studies. I am also grateful to Professors Gábor C. Temes, Karti Mayaram and Terri Fiez for their helps in both research and academic matters. I would also like to acknowledge all members of my committee, for taking the time to serve on my defense.

I would like to thank Dr. Byung-Moo in National Semiconductor Corporation for the sponsorship of the prototype ADC fabrication. I appreciate the helps on chip layout from Mr. Yong-In Park in Texas Instruments Corporation. This work was supported by NSF center for Design of Analog and Digital Integrated Circuits (CDADIC) and partly by Analog Devices Corporation.

All my colleagues in the Analog Group have not hesitated to offer their help to me. First, I would like to thank Jose Silva. He has offered great help to me from the beginning of my research in school to the end of my study. I would also like to thank Dong-Young Chang, Cil-Cho Ahn, Xuesheng Wang and Pavan Hanumolu for helpful discussions.

Last, I would like to thank all my friends for their understanding, support and sharing happiness with me.

### TABLE OF CONTENTS

|    |            |                                         | <u>Page</u> |

|----|------------|-----------------------------------------|-------------|

| 1. | INTROD     | UCION                                   | 1           |

|    | 1.1 Backg  | ground                                  | 1           |

|    | 1.2 Motiv  | vation                                  | 2           |

|    |            | ng Methods                              |             |

|    |            |                                         |             |

|    | 1.4 Propo  | sed Approaches                          | 5           |

|    | 1.5 Thesis | s Organization                          | 6           |

| 2. | REVIEW     | OF PIPELINED ADC                        | 8           |

|    | 2.1 Pipeli | ned ADC Fundamentals                    | 8           |

|    | 2.2 Buildi | ing Block Design                        | 15          |

|    | 2.2.1      | Input Sample and Hold Circuit           | 15          |

|    | 2.2.2      | Multiplying Digital to Analog Converter | 18          |

|    | 2.2.3      | Sub-ADC                                 |             |

|    | 2.2.4      | Clock Generator and Clock Buffer        |             |

|    | 2.2.5      | Reference Buffer                        |             |

|    | 2.2.6      | Other Circuitry                         | 29          |

|    | 2.3 Impor  | tant Design Issues                      | 30          |

|    | 2.3.1      | MOS Switches                            | 30          |

|    | 2.3.2      | Noise                                   |             |

|    | 2.3.3      | Opamp Gain and Bandwidth                |             |

|    | 2.3.4      | Capacitor Mismatch                      |             |

|    | 2.3.5      | Charge Injection and Clock Feed-through | 38          |

|    | 2.4 Advar  | nced Design Techniques                  | 39          |

### TABLE OF CONTENTS (Continued)

|    | <u>Pa</u>                                                                                                                                      | age            |

|----|------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 3. | ACCURACY ENHANCEMENT TECHNIQUES                                                                                                                | 42             |

|    | 3.1 Analog Correction                                                                                                                          | 42             |

|    | 3.2 Digital Self-calibration                                                                                                                   | 47             |

|    | 3.3 Background Calibration                                                                                                                     | 49             |

| 4. | TIME-SHIFTED CDS TECHNIQUE                                                                                                                     | 54             |

|    | 4.1 Introduction                                                                                                                               |                |

|    | 4.2 Time-shifted CDS Technique                                                                                                                 | 55             |

|    | 4.3 Prototype Pipelined ADC Design                                                                                                             | 63             |

|    | 4.3.1 Opamp Design 4.3.2 Pseudo-differential MDAC Design 4.3.3 Double Sampling S/H Design 4.3.4 Comparator Design 4.3.5 Clock Generator Design | 65<br>67<br>68 |

|    | 4.4 Experimental Results                                                                                                                       | 71             |

|    | 4.5 Summary                                                                                                                                    | 75             |

| 5. | BACKGROUND DIGITAL CALIBRATION TECHNIQUE                                                                                                       | 76             |

|    | 5.1 Introduction                                                                                                                               | 76             |

|    | 5.2 Proposed Background Calibration                                                                                                            | 78             |

|    | 5.2.1 Radix-based Digital Self-calibration                                                                                                     | 84             |

# TABLE OF CONTENTS (Continued)

|    |            |                                                 | Page |

|----|------------|-------------------------------------------------|------|

|    | 5.2.4      | Overall Calibration Scheme                      | 94   |

|    | 5.2.5      | Simulation Results                              | 95   |

|    | 5.3 Protot | type Cyclic ADC Design                          | 98   |

|    | 5.3.1      | Low-voltage Pseudo-differential MDAC Using ORST | 78   |

|    | 5.3.2      | Low-voltage Opamp Design                        | 101  |

|    | 5.3.3      | Input Sampling Circuit                          | 103  |

|    | 5.3.4      | Low-voltage Comparator with Dither              | 104  |

|    | 5.3.5      | Pseudo-random Sequence Generator                |      |

|    | 5.4 Exper  | iments Results                                  | 107  |

|    | 5.5 Summ   | nary                                            | 112  |

| 6. | CONCLU     | USIONS                                          | 114  |

| ΒI | BLIOGRA    | PHY                                             | 115  |

### LIST OF FIGURES

| <u>Figu</u> | <u>Page</u>                                         |

|-------------|-----------------------------------------------------|

| 2.1         | A typical pipelined ADC                             |

| 2.2         | Effects of non-idealities in 1b/stage pipelined ADC |

| 2.3         | Mid-tread transfer curve with redundancy            |

| 2.4         | Digital correction algorithm                        |

| 2.5         | General structure of cyclic ADCs                    |

| 2.6         | Non-overlap and early falling clock scheme          |

| 2.7         | Charge redistribution S/H circuit                   |

| 2.8         | Capacitor flip-over S/H circuit                     |

| 2.9         | A 3-b switched-capacitor MDAC                       |

| 2.10        | Cascode opamp                                       |

| 2.11        | Two-stage opamp                                     |

| 2.12        | Structure of a typical sub-ADC                      |

| 2.13        | Capacitive coupled comparator module                |

| 2.14        | Static latched comparator                           |

| 2.15        | Dynamic latched comparator                          |

| 2.16        | Clock generator                                     |

| 2.17        | Clock buffer                                        |

| 2.18        | Reference buffer 28                                 |

# LIST OF FIGURES (Continued)

| <u>Figu</u> | <u>Pag</u>                                                       | <u>;e</u> |

|-------------|------------------------------------------------------------------|-----------|

| 2.19        | MOS switches                                                     | 0         |

| 2.20        | Conceptual bootstrapped switch                                   | 1         |

| 2.21        | Implementation of bootstrapped switch                            | 32        |

| 2.22        | Dynamic range, power and speed trade-off                         | 9         |

| 3.1         | Ratio independent multiplication                                 | ŀ3        |

| 3.2         | Capacitor error averaging                                        | 14        |

| 3.3         | Capacitor trimming                                               | .5        |

| 3.4         | Transfer curve of 1b MDAC                                        | ١7        |

| 3.5         | Queue based ADC architecture                                     | 51        |

| 3.6         | Timing of queue based calibration                                | 51        |

| 3.7         | Background calibration of capacitor mismatch using correlation   | 53        |

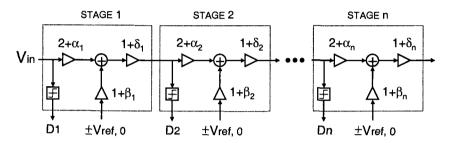

| 4.1         | 1.5-bit-per-stage pipelined ADC                                  | 55        |

| 4.2         | Typical 1.5-bit-per-stage MDAC                                   | 6         |

| 4.3         | Proposed pipelined ADC architecture                              | 57        |

| 4.4         | Proposed MDAC architecture                                       | 8         |

| 4.5         | Pipelined ADC employing conventional CDS technique               | 51        |

| 4.6         | Pipelined ADC applying time-shifted CDS to the first five stages | i2        |

| 4.7         | Pipelined ADC without any gain error correction                  | 2         |

# LIST OF FIGURES (Continued)

| <u>Figu</u> | <u>Page</u>                                                                 |

|-------------|-----------------------------------------------------------------------------|

| 4.8         | Proposed pipelined ADC applying time-shifted CDS to the first six stages 63 |

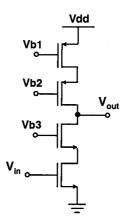

| 4.9         | CMOS cascode inverter                                                       |

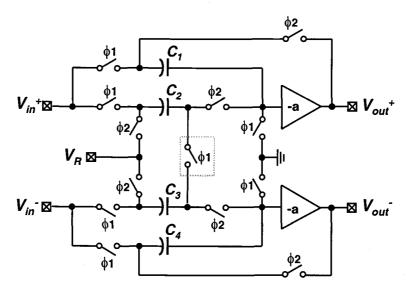

| 4.10        | Proposed pseudo-differential MDAC                                           |

| 4.11        | Double sampling front S/H circuit                                           |

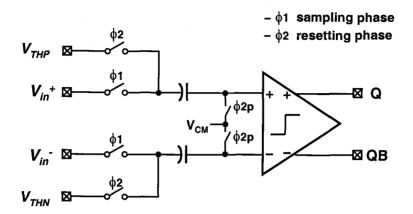

| 4.12        | Capacitive coupling comparator                                              |

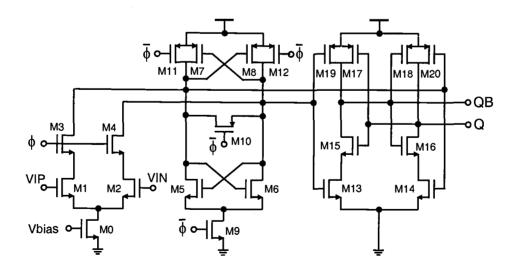

| 4.13        | High-speed latched comparator                                               |

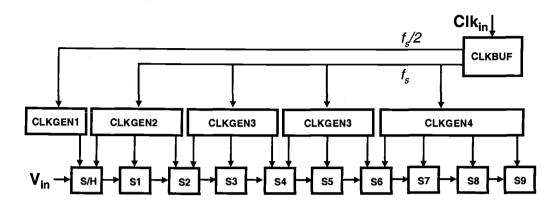

| 4.14        | Distributed clock generator                                                 |

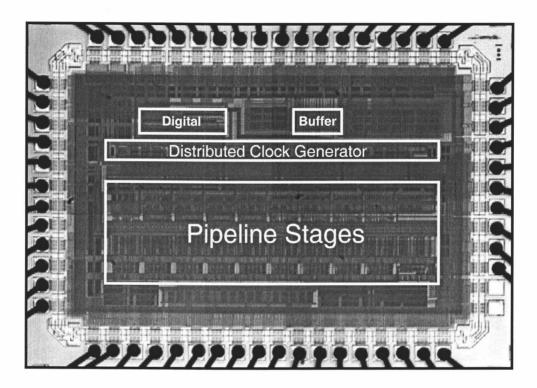

| 4.15        | Die photo of prototype pipelined ADC71                                      |

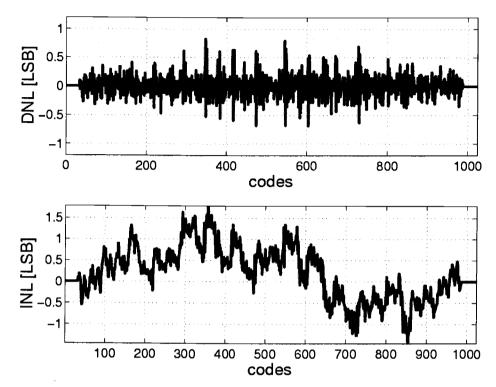

| 4.16        | Measured DNL and INL                                                        |

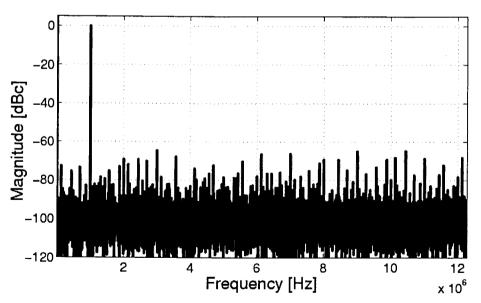

| 4.17        | Measured ADC output spectrum at 100MSPS                                     |

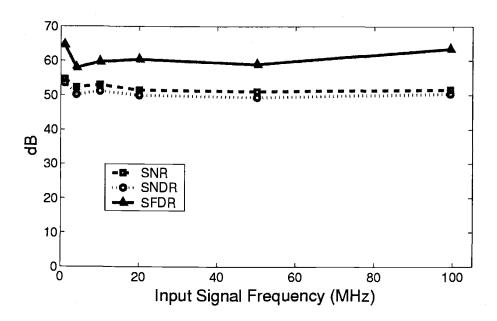

| 4.18        | Dynamic measurements vs. input frequency                                    |

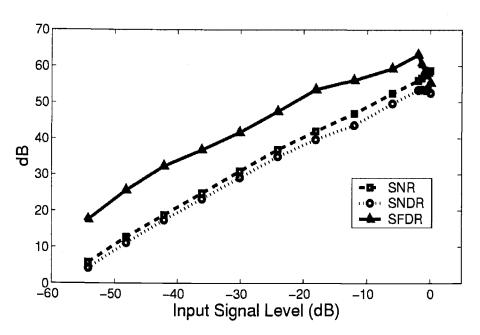

| 4.19        | Dynamic measurements vs. input amplitude                                    |

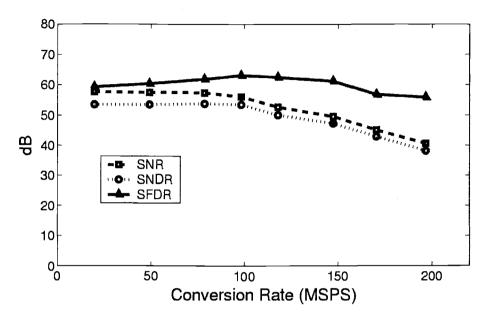

| 4.20        | Dynamic measurements vs. conversion rate                                    |

| 5.1         | Functional diagram of a non-ideal pipelined ADC (1.5b/stage)                |

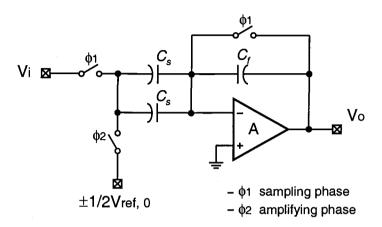

| 5.2         | Non-capacitor-flip-over MDAC                                                |

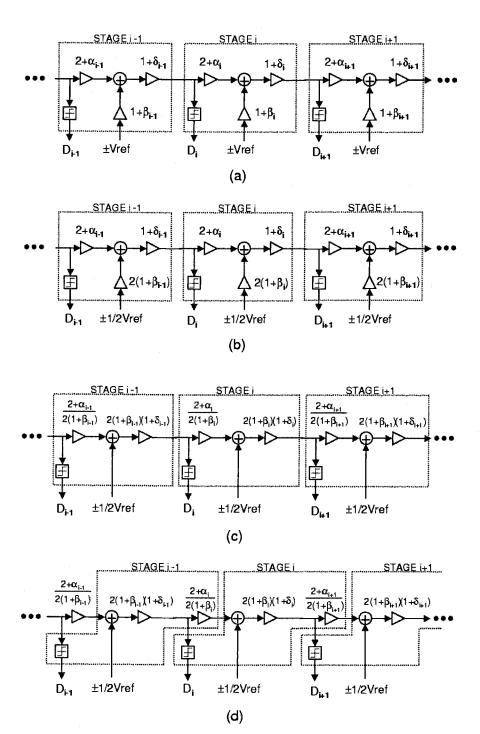

| 5.3         | Equivalent transformation of a pipelined ADC                                |

| 5.4         | Background equivalent radix extraction scheme 1                             |

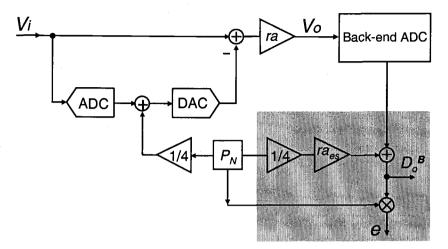

| 5.5         | Background equivalent radix extraction scheme 2                             |

# LIST OF FIGURES (Continued)

| <u>Figu</u> | <u>re</u>                                    | Page |

|-------------|----------------------------------------------|------|

| 5.6         | Interference in the radix error detection    | 90   |

| 5.7         | Two-channel ADC architecture                 | . 91 |

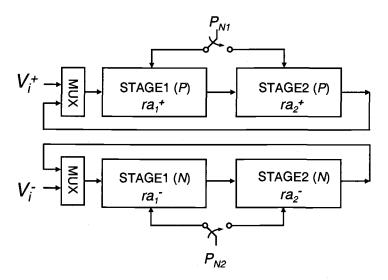

| 5.8         | Overall ADC with proposed calibration scheme | . 94 |

| 5.9         | Two-stage cyclic ADC with calibration        | 96   |

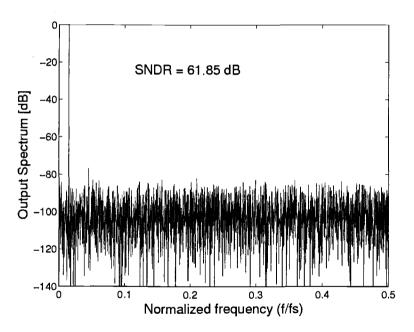

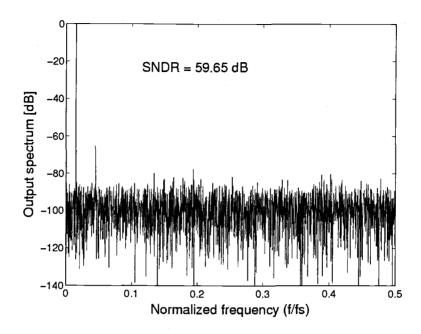

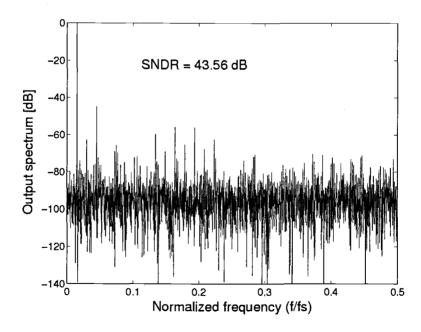

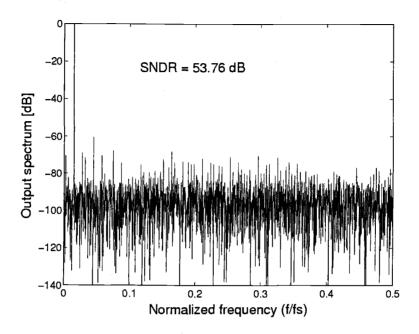

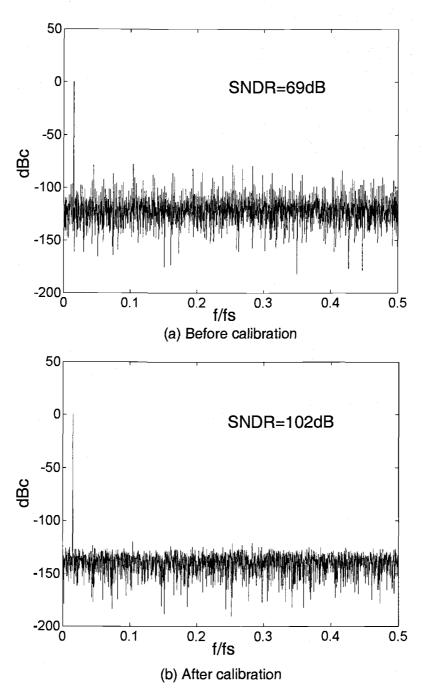

| 5.10        | Simulated output spectrum                    | . 97 |

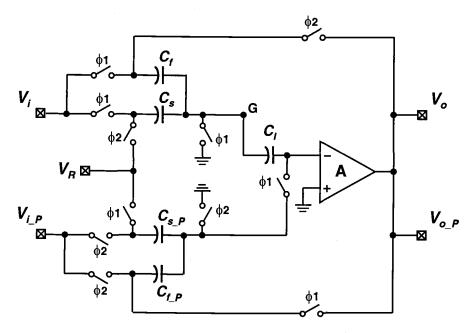

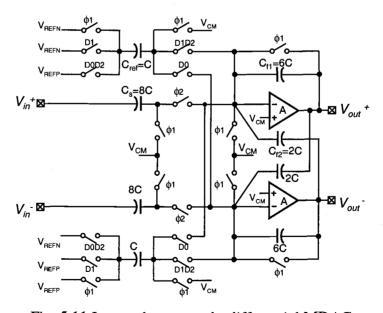

| 5.11        | Low-voltage pseudo-differential MDAC         | 98   |

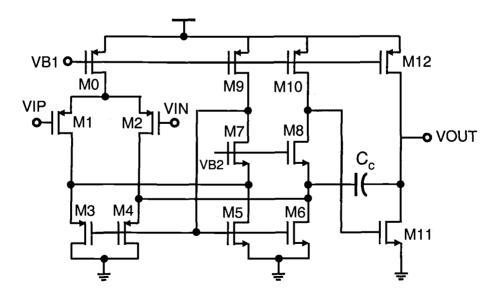

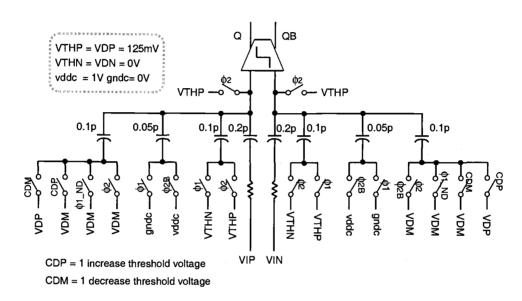

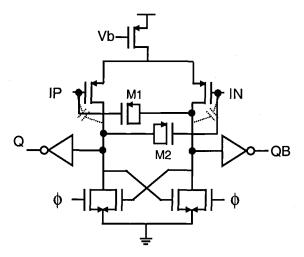

| 5.12        | Two-stage opamp with cascode compensation    | 102  |

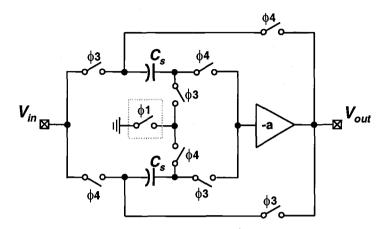

| 5.13        | Passive input sampling branch                | 103  |

| 5.14        | Low-voltage comparator module with dither    | 105  |

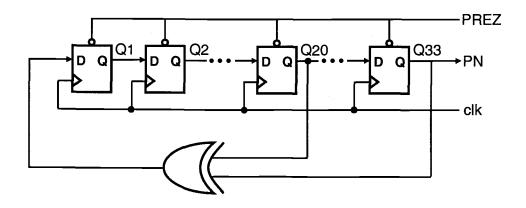

| 5.15        | Simple static comparator                     | 106  |

| 5.16        | Pseudo-random sequence generator             | 106  |

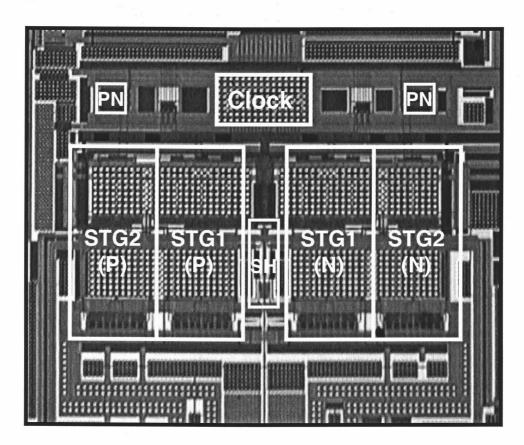

| 5.17        | Die photo of the prototype cyclic ADC        | 107  |

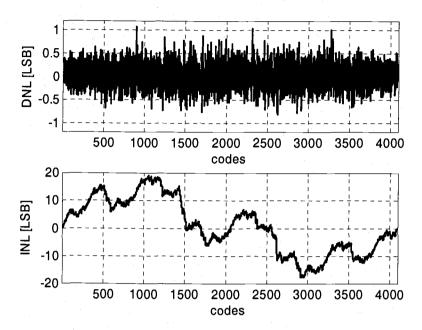

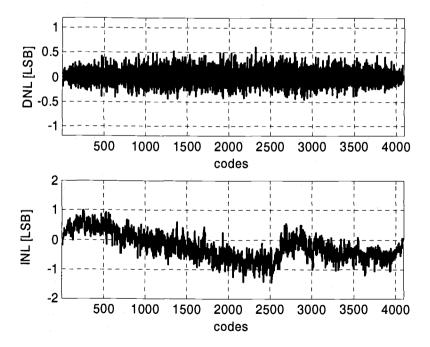

| 5.18        | DNL and INL before calibration               | 108  |

| 5.19        | DNL and INL after calibration                | 108  |

| 5.20        | Measured ADC output spectrum at 2MSPS        | 109  |

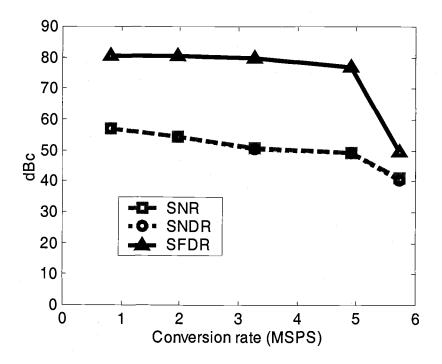

| 5.21        | Dynamic performance vs. conversion rate      | 110  |

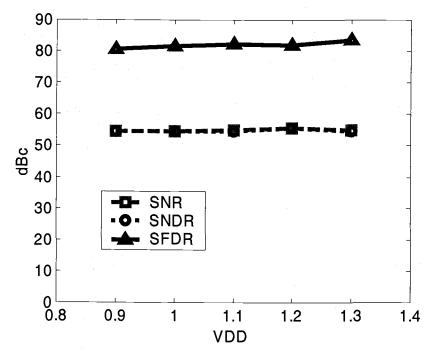

| 5.22        | Dynamic performance vs. power supply voltage | .111 |

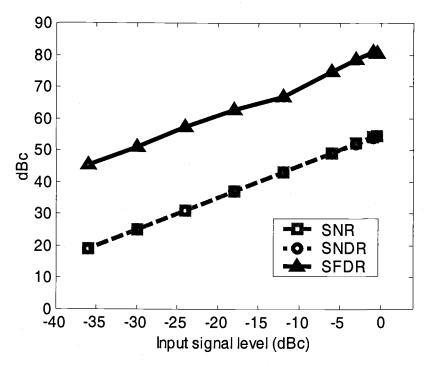

| 5.23        | Dynamic performance vs. input signal level   | .111 |

### LIST OF TABLES

| Tabl | <u>Pa</u>                                       | <u>ze</u> |

|------|-------------------------------------------------|-----------|

| 1.1  | Typical applications for pipelined ADCs         | 7         |

| 4.1  | Simulation results of CMOS inverter             | 5         |

| 4.2  | Performance summary of the prototype ADC        | 5         |

| 5.1  | Summary of opamp design                         | 3         |

| 5.2  | Performance summary of the prototype cyclic ADC | 2         |

# To

# my parents Shukun Li, Yongzhi Gao

and

my wife Lanyue Xu

#### ACCURACY ENHANCEMENT TECHNIQUES IN LOW-VOLTAGE HIGH-SPEED PIPELINED ADC DESIGN

#### 1 INTRODUCTION

#### 1.1 Background

Analog-to-digital converters (ADCs) are very important building blocks in modern signal processing and communication systems. Many good ADC architectures have been invented to satisfy different requirements in different applications. To name some: flash ADC, folding and interpolating ADC, two-step ADC, pipeline ADC, successive-approximation-register (SAR) ADC, delta-sigma ADC, integrating ADC etc. Among various ADC architectures, the pipelined ADC has the attractive feature of maintaining high accuracy at high conversion rate with low complexity and power consumption. Therefore it is used extensively in high-quality video systems, high-speed data acquisition systems and high performance digital communication systems where both precision and speed are critical. Some typical applications for pipelined ADCs are listed in Table 1.1.

#### 1.2 Motivation

The rapid growth of these applications is driving the pipelined ADC design towards higher speed, higher precision, lower power consumption, lower supply voltage, smaller size and higher levels of integration along with the advancement of the fabrication technology. While continual speed improvement can still be achieved by using the advanced sub-micron or deep sub-micron CMOS processes, data converter designers find it more and more difficult to improve or even keep the accuracy of pipeline ADCs which reply on high gain operational-amplifier (opamp) and well matched components to produce high-precision converters. First, large open loop opamp gain is difficult to realize without sacrificing bandwidth given the continuing trend of submicron CMOS scaling which is coupled with lower power supply voltages. Second, there are some physical limits on the component matching due to process variation, so it can not be improved continually with CMOS technology scaling. Thus, while the state-of-the-art pipelined ADCs has exceeded 100MSPS (mega-samples-per-second) in CMOS technology [1]-[6], the commonly achieved resolution is still bound within the range of 8-12 effective-number-of-bits (ENOBs) due to the limitations set by component mismatches and finite opamp gain. Use of multi-bit-per-stage architecture and design optimization can achieve 14-bit performance as demonstrated in [7], but most pipelined ADCs with more than 12-bit resolution will usually require some kind of linearity enhancement techniques.

#### 1.3 Existing Methods

Trimming is one such method but it cannot track variations over time caused by component aging and temperature changes despite the high cost of implementation. Some traditional analog techniques such as ratio-independent multiplication [8], reference-refreshing method [9], and capacitor error averaging [10][11] can also correct errors due to component mismatches. However, these techniques require at least one extra clock phase for correction, which equivalently reduces the conversion rate. To avoid this kind of speed penalty, self-calibration techniques, which measure errors by the converter itself and subtract the code error during the normal operation, can be used to improve the accuracy of high resolution ADCs. In many of the selfcalibration techniques, although the code errors are calculated in the digital domain, they are actually subtracted in the analog domain using a separate calibration digitalto-analog converter (DAC) [12][13]. More recently, digital self-calibration techniques, which subtract the code errors in the digital domain, have been introduced to relieve the accuracy requirements of analog calibration circuits [14]-[17]. While digital selfcalibration has the advantage of low complexity and high accuracy, most are calibrated in the foreground. That means the normal operation has to be interrupted to start the calibration cycle. Although the calibration can be done during the system power-up or standby, it is desirable to run the calibration at all times to track device and environmental variations.

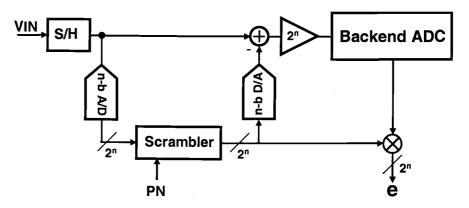

To avoid the foreground interruptions, several background calibration schemes that are transparent to the normal operation have been proposed. A resistor-string DAC instead of a capacitor DAC was used in a 13-bit ADC, so that it could be calibrated in the background by a slow-but-accurate delta-sigma ADC [18]. This scheme can only be applied to an ADC with a resistor-string DAC. Redundant pipeline stages can be added to substitute the stages under calibration as shown in [19], so that the normal operation need not be stopped during calibration. This results in a large overhead for die area and power dissipation. To create the needed time slots for calibration, a skip-and-fill algorithm was proposed [20][21]. In this algorithm, the conversion of input samples is occasionally skipped, and a sample of the calibration signal is converted instead. The missing input samples are later filled in digitally via nonlinear interpolation of data. To avoid the complexity of the digital post-processing required by this skip-and-fill algorithm, a queue-based architecture was used in an algorithmic ADC [22]. The skip-and-fill method is relatively simple and accurate for implementation, but the input signal bandwidth has to be limited to avoid performance degradation due to interpolated regeneration of skipped samples [20][21].

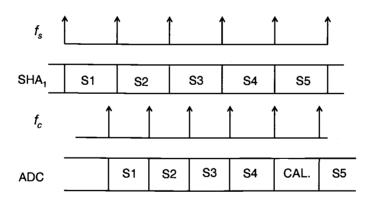

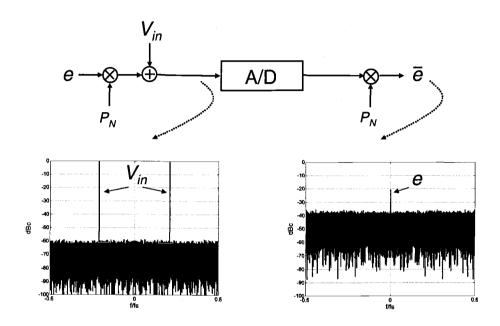

Several correlation-based methods have been proposed for background calibration in pipelined ADCs [23]-[27]. These methods modulate the calibration

signal or capacitor DAC errors with a pseudo-random noise sequence in the analog domain and then demodulate them in the digital domain to extract the errors from the processed input signal. The input signal bandwidth limitation and/or redundant analog hardware can be avoided using this method. Despite the added advantages, the previously reported correlation-based schemes are quite complex and slow to converge.

#### 1.4 Proposed Approaches

Although many accuracy enhancement techniques are already available and work well under certain context, all of them have some drawbacks. Usually, either speed or power consumption or both have to be compromised. And most of them are difficult to implement in low-voltage and high-speed designs. Therefore, simple and efficient accuracy enhancement techniques which can be used in low-voltage and high-speed pipelined ADCs would be worthy of focused research.

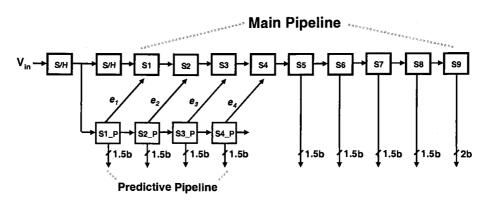

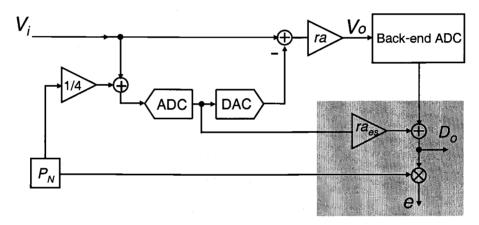

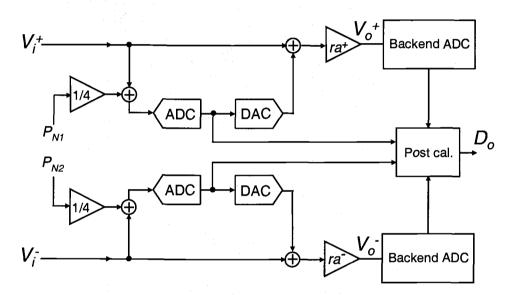

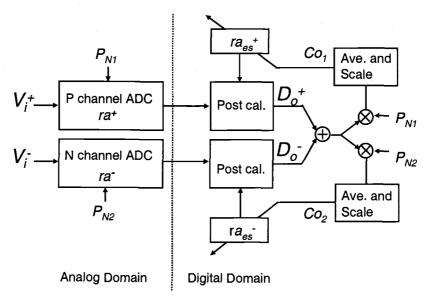

In this work, two novel accuracy enhancement techniques are proposed. The first one is the *time-shifted* correlated-double-sampling (CDS) technique [28][29] which can be used to compensate finite opamp gain in the context of a 1.5-bit-per-stage pipelined ADC. This technique can significantly reduce the errors due to finite opamp gain without compromising conversion speed. The second approach is a fast and accurate correlation-based background digital calibration scheme [30]. The input

signal magnitude needs not to be reduced to allow the injection of a pseudo-random calibration signal. The minimal addition of analog hardware for calibration keeps the original ADC design essentially unchanged. The correlation algorithm converges very quickly in the proposed two-channel ADC architecture because of the interference canceling scheme employed. The effectiveness of both methods is demonstrated in simulations as well as experiments.

#### 1.5 Thesis Organization

The thesis is organized as follows. The basic operation and design techniques of pipelined ADCs are described in Chapter 2. An overview of some accuracy enhancement techniques in high performance pipelined ADC designs is given in Chapter 3. Next, two novel accuracy enhancement techniques are presented. In Chapter 4, the *time-shifted* correlated-double-sampling (CDS) technique which can efficiently compensate the finite opamp gain in pipeline ADCs is explained. In Chapter 5, a novel background digital calibration technique which can correct errors due to finite opamp gain as well as capacitor mismatch is described. The conclusions and a summary of research are given in Chapter 6.

| <b>—</b> 1                  |                                                                                                                                                                                                                                                                                                   |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Resolution (number of bits) | Applications                                                                                                                                                                                                                                                                                      |

| 8                           | <ul> <li>Flat-panel displays</li> <li>Lab instrumentation</li> <li>HDTV</li> <li>Medical imaging (low-end portable)</li> <li>WLAN and WAN</li> <li>Radar</li> </ul>                                                                                                                               |

| 10                          | <ul> <li>Flat-panel displays</li> <li>HDTV</li> <li>Medical imaging such as ultrasound</li> <li>Cellular basestations (power amp linearization)</li> <li>High-data-rate radios (point-to-point microwave, LMDS, and MMDS)</li> <li>Cable headends (for digitizing cable modem uplinks)</li> </ul> |

| 12                          | <ul> <li>Cellular basestations</li> <li>Test equipment for ATE and communications</li> <li>Cable headends</li> <li>Professional HDTV cameras</li> <li>Medical imaging</li> </ul>                                                                                                                  |

| 14                          | <ul> <li>Cellular basestations, particularly 3G multicarrier systems</li> <li>ATE</li> <li>High-end instrumentation</li> <li>Military and aerospace</li> </ul>                                                                                                                                    |

Table 1.1 Typical applications for pipelined ADCs

#### 2 REVIEW OF FPIPLINED ADC

Deep insight into of the practical design of a high-performance pipelined ADC is the cornerstones of developing a successful accuracy enhancement technique. In this chapter, the basic knowledge of pipelined ADCs and more advanced design techniques in CMOS technology are reviewed. First, the structure and operation of a typical pipelined ADC are introduced. Then the details of the building blocks design are described. The design issues which are critical to the function as well as performance are also discussed. A simple introduction of some advanced design techniques is given in the last section of this chapter.

#### 2.1 Pipelined ADC Fundamentals

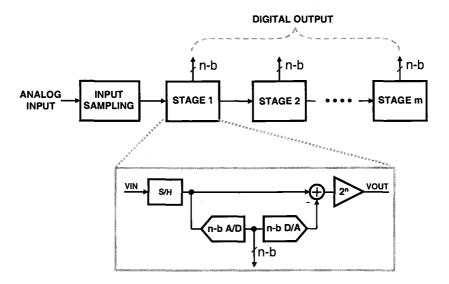

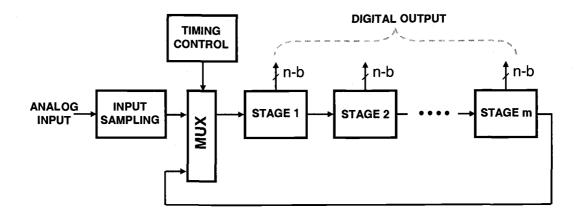

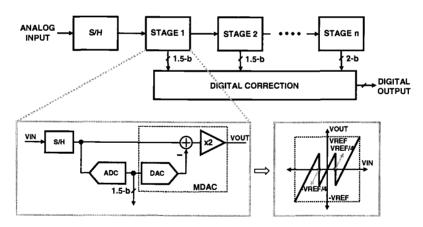

Fig.2.1 A typical pipelined ADC

Figure 2.1 shows the structure of a typical pipelined ADC. It includes several cascaded stages. In each stage, there is a sample and hold (S/H) block, a sub-ADC (usually low resolution flash type ADCs), a sub digital-to-analog converter (sub-DAC), a subtractor and an inter-stage gain amplifier. The operation of each stage is as follows. The sampled input signal is first quantized by the sub-ADC to produce the output digital code for this stage. Then the output digital code is converted back to an analog signal by the sub-DAC. This quantized analog signal is subtracted from the input signal, resulting in a residue that is amplified and then passed onto the next stage. A binary bit searching scheme is employed in the operation of pipelined ADCs. While the overall resolution of the pipelined ADC is the sum of the number of bits resolved in each stage, the throughput rate of the overall pipelined ADC is equal to each stage's throughput rate because of the pipelining. Of course, there is also a latency introduced by this pipelining. Fortunately, this is not an issue in most applications.

Two distinguished attributes of the pipelined ADC architecture can be observed from the simple introduction above. First, unlike the flash type ADC whose circuit complexity increases exponentially with resolution, the circuit complexity of a pipelined ADC increases only linearly with the converter's resolution because of the binary bit searching scheme involved. Second, the throughput rate does not increase with the number of stages because of the pipelining. Ideally, the pipeline ADC could be as fast as flash the ADCs and consume much less power. However, this is not completely true in practical designs particularly in low resolution and very high-speed

converters. The opamps used in pipelined ADCs usually consume more power than the comparators and limit the speed of the overall ADC. This will be explained in detail in later sections.

Two other advantages of pipelined ADCs which maybe not be obvious are the input S/H function and the inter-stage gain function. The front S/H block makes the pipelined ADC insensitive to the frequency of the input signal processed. Actually, it is not unusual for a carefully designed pipeline ADC to maintain good performance at the Nyquist input frequency or higher (sub-sampling). The inter-stage gain makes the pipelined ADC less insensitive to the noise and non-idealities of the later stages in the pipeline. Therefore, scaling can be used to optimize the design for low power consumption and small area.

Another very important concept to mention here is the digital correction which is used in almost every pipelined ADC design. Digital correction dramatically reduces the pipelined ADC's sensitivity to the nonlinearities in the sub-ADCs, therefore makes the design of comparators in sub-ADCs much easier. While the detailed analysis of digital correction can be found in [31], a simple introduction is given below.

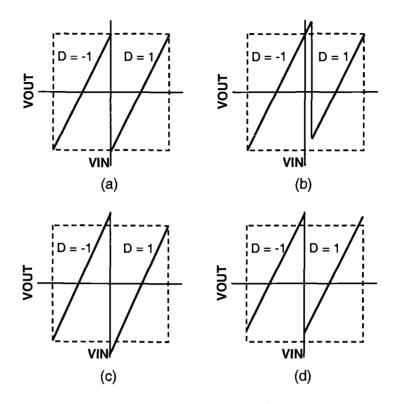

Fig. 2.2 Effects of non-idealities in 1b/stage pipelined ADC

To understand the digital correction, some basic knowledge of the non-idealities in the pipelined ADC and their effects is necessary. Comparator and opamp offsets, capacitor mismatches, finite opamp gains, charge injections are some major error sources in pipelined ADCs. Their effects on the transfer curve of the pipeline ADC can be illustrated in Fig. 2.2. Figure 2.2(a) is the ideal stage input-output transfer curve of a 1bit/stage pipelined ADC. The comparator offset will shift the transition point and cause the residue to exceed the signal range as indicated in Fig. 2.2(b). The capacitor mismatch and finite opamp gain can change the inter-stage gain. This gain error will change the slope of the curve as shown in Fig. 2.2(c). The vertical shift of

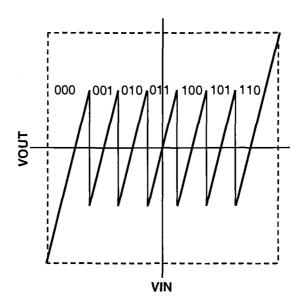

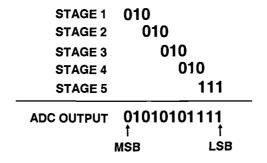

the transfer curve in Fig. 2.2(d) is caused by the charge injection offset. Thus the linearity of the comparator is corrupted. It can be seen that all the error sources can possibly cause the residue to go out of signal range. Once this happen, the missing levels will be produced and the linearity of the overall ADC will be corrupted. Although the example of a 1bit/stage ADC is given for simplicity, a similar issue exists in multi-bit/stage ADCs. To avoid the residue going out of signal range, a simple approach is to introduce some redundancy in the pipelined ADC design. In a practical design, this can be done by choosing smaller inter-stage gain factor. For instance, an inter-stage gain of 4 instead of 8 can be chosen in a 3bit/stage ADC design. So in the ideal case, the residue will be just half of the signal range. And it will not exceed the signal range even if there are some comparator offsets as far as they are less than  $\pm 1/2$ LSB of the stage resolution. However, this modification (adding redundancy) changes the encoding scheme of the overall pipelined ADC and a digital correction is needed to post-process the ADC's output code. The digital correction logic can be greatly simplified if some offsets are added to the sub-ADCs and the sub-DACs which results in a mid-tread transfer curve as shown in Fig. 2.3. Note only 6 comparators are needed to resolve 7 levels for a 3bit sub-ADC. Note one more comparator is needed for the last stage to give a true 3bit output representing 8 levels. Otherwise, there will be one missing code. Now the digital correction is just some simple bit-shift adding on the pipeline ADC's digital output (overlap the LSB of each stage and the MSB of its following stage) as demonstrated in Fig.2.4. Note the final

number of bits is reduced after this digital correction. For example, a five stages pipelined ADC (3bit/stage) only give 11 bit output instead of 15bit after digital correction. However, this drawback is well compensated given the fact that fairly large comparator offsets can be tolerated without affecting the linearity of the overall ADC. As a result, the comparator design is much easier (usually no need for offset canceling) and the digital calibration of the inter-stage gain errors is feasible.

Fig. 2.3 Mid-tread transfer curve with redundancy

Fig. 2.4 Digital correction algorithm

Fig. 2.5 General structure of cyclic ADCs

One variant of the pipelined ADC is the cyclic ADC or algorithm ADC which is shown in Fig. 2.5. It is almost the same as the pipeline ADC. But one multiplexer (MUX) is put in front of all the pipelined stages. Each input sample will be processed through all the stages in the same way of a pipelined ADC. However, the residue of the last stage will be feed back to the input of the pipeline to quantize again. This kind of "recycling" process can equivalently extend the length of the pipeline, and so increase the resolution. The price is the increased time to process an input sample. Actually, both the resolution and conversion time will increase proportionally with the number of "cycles" used in the conversion. So the cyclic ADC can be seen as one kind of pipeline ADC which trades speed with space and power consumption. And it can be used in those applications where the small die area and low power consumption are important but the conversion rate is relatively low.

#### 2.2 Building Block Design

Although the highest performance monolithic pipelined ADCs are still built in BiCMOS or bipolar processes, the mainstream of pipelined ADC design has already shifted to CMOS process for lower cost and power. Since fine-line CMOS technology can provide good sampling switches and well matched capacitors, the switched-capacitor (SC) techniques based on charge transferring are used extensively in the CMOS pipelined ADC designs. In the following, the building blocks design of a typical CMOS pipelined ADC using switched-capacitor techniques will be described.

#### 2.2.1 Input Sample and Hold Circuit

Most pipeline ADCs have an on-chip sample and hold circuit in front of the pipeline stages to buffer the input signal as indicated in Fig. 2.1. This front S/H circuit can give some isolation between the pipelined ADC and its driving circuit. So the driver suffers less kick-back noise from the comparators in the pipelined ADC. More importantly, since the S/H circuit keeps the sampled input signal constant during holding phase, it can eliminate the signal discrepancy between the input of sub-ADC and subtractor caused by the clock skew. Note this signal discrepancy adds equivalent comparator offsets to the pipelined ADC and it could be very large if the input signal frequency is very high (up to or higher than Nyquist frequency). Once the comparator offsets exceed the range of digital correction, huge amount of errors will happen to the conversion.

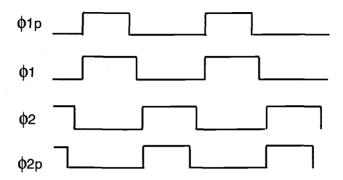

Fig. 2.6 Non-overlap and early falling clock scheme

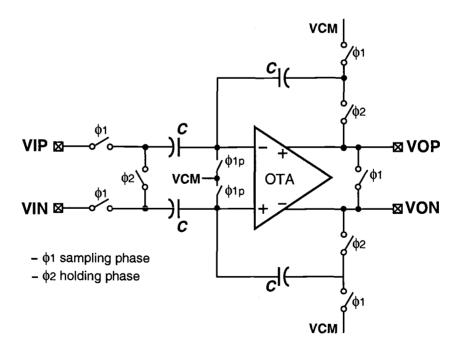

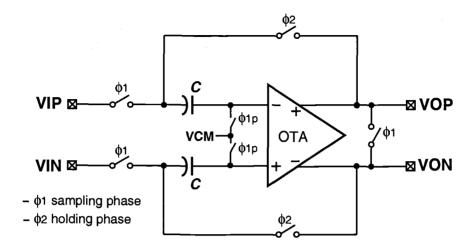

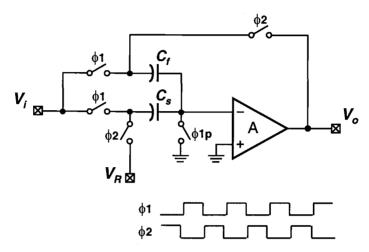

Two CMOS S/H architectures are used widely in the pipelined ADC design. Both of them are fully differential circuits. And the classic four clock scheme (two non-overlap clock signals and two additional clock phases with early falling edge) for switched-capacitor circuits is employed. The clock waveforms are shown in Fig. 2.6. The first one is referred as the charge redistribution S/H circuit as shown in Fig. 2.7. Four capacitors with the same size are used in this structure. During the sampling phase, the differential input signal is sampled into the two input sampling capacitors. Next, during the holding phase, the bottom plates of the two sampling capacitors are connected together. Thus only the differential charge is transferred to the feedback capacitors. As a result, this S/H can handle very large input common mode variation. The second one is the capacitor flip-over S/H as shown Fig. 2.8. No charge transferring happens in this scheme and only two capacitors are used. During the sampling phase, the differential input signal is sampled into the input capacitors in the same way as the first S/H. However, during the holding phase, the input capacitors are

"flipped over" by connecting their bottom plates to the output the amplifier. By doing this, both the common mode and differential mode charge is transferred. Although the amplifier's common mode feedback circuit will force the output common mode to the nominal value, the amplifier's input common mode level will change according to the difference between the input signal's common mode level and the amplifier output's common mode level. That means the amplifier must be capable of handling large input common mode variation. Even with this drawback, the flip-over S/H is more popular than the charge redistribution S/H in the state of the art high-speed pipelined ADC designs because of its smaller size, lower noise and lower power consumption. These advantages stem from the large feedback factor and lower number of capacitors. The detailed analysis can be found in [7].

Fig. 2.7 Charge redistribution S/H circuit

Fig. 2.8 Capacitor flip-over S/H circuit

The design of front S/H circuit is very critical to the overall performance of a pipelined ADC. The noise and linearity requirement should be the same or better than the overall noise and linearity requirement of the ADC. As a result, the S/H circuit usually takes large die area and consumes quite amount of power. To achieve low power consumption, a pipeline ADC without S/H circuit is proposed [32]. However, special efforts have to be put into the design to avoid the signal discrepancy issue mentioned above.

#### 2.2.2 Multiplying Digital to Analog Converter

In the practical implementation of a pipelined ADC sown in Fig. 2.1, the sub-ADC, subtractor and inter-stage gain block in each stage are usually combined together and referred as multiplying-digital-to-analog converter (MDAC). The ideal

input-output transfer function of an n-bit MDAC with digital redundancy can be expressed as:

$$V_{out} = V_{in} \cdot 2^{n-1} - D \cdot V_{REF}, \qquad (2.1)$$

where  $V_{in}$ ,  $V_{out}$  and  $V_{REF}$  are input voltage, output residue voltage and reference voltage respectively. And D is  $0,\pm 1,\pm 2\cdots \pm (2^{n-1}-1)$  digital code generated in sub-ADC depending on the input signal range.

MDAC is probably the most critical unit in a pipelined ADC design. It consumes most of the power dissipated by the ADC. And usually is the bottleneck for speed and accuracy improvement of a pipelined ADC. Therefore, almost all the low power, high speed and high precision techniques developed so far are focused on the MDAC design. And most of the design optimization work is also done in MDAC.

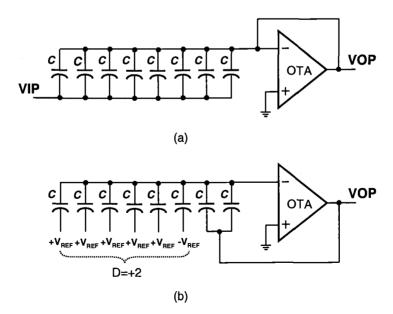

Fig. 2.9 A 3-b switched-capacitor MDAC

Despite its importance, the structure of a switched-capacitor MDAC is not very complex. Figure 2.9 illustrates the structure and operation of a typical 3-bit switched-capacitor MDAC whose input-output transfer curve is shown in Fig. 2.3. For simplicity, the single-ended version is shown although fully differential architecture is usually used in practical design. It takes two clock phases to fulfill the all the functions of a MDAC. During sampling phase, the input signal is sampled into eight unit size capacitors and the amplifier is reset as shown in Fig. 2.9(a). Note, in the mean time, the sub-ADC is sampling the input signal also and will give the output digital code and DAC control signal at the end of sampling phase. Next, during amplifying phase, two capacitors are flipped-over and have their bottom plates connected to the output of the amplifier while the bottom plates of the remaining capacitors are connected to +V<sub>REF</sub> or -V<sub>REF</sub> depending on the digital code (+2 for this case) from the sub-ADC output as shown in Fig.2.9(b).

The opamps used in MDACs and S/H circuits are actually operational transconductance amplifiers (OTAs) since they have high output impedance and only drive capacitor load. Opamp is the key part of the MDAC and worthy of most attention when designing a pipelined ADC. The main requirements on opamp design are high gain, large bandwidth, large slew rate, large signal swing, low noise, low power consumption and low power supply voltage. Besides these, high power supply noise rejection ratio (PSRR), high common mode noise rejection ratio (CMRR), small offset and small size are also desirable. Unfortunately, these factors can not be

improved together and many trade-offs exist among them. For example, an increase in bandwidth almost always necessitates an increase in power consumption. So a good opamp design is the optimization of these factors according to the design specification.

Fig. 2.10 Cascode opamp

Fig. 2.11 Two-stage opamp

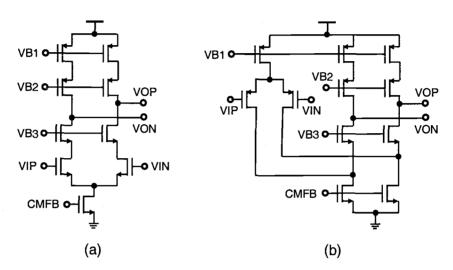

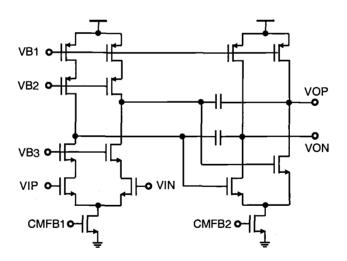

Many good opamps have been developed for different pipelined ADCs.

Among them, the telescopic opamp shown in Fig. 2.10(a) and the folded cascode

opamp shown in Fig. 2.10(b) are the most commonly used for their high gain and large bandwidth at given power consumption. While both opamp designs employ cascoded transistors to boost the opamp gain, they have many differences. The telescopic opamp has the advantages of higher speed and lower power consumption. But folded cacode opamp has large output signal swing and large input common mode range. Another good opamp design is the two-stage opamp design using miller compensation shown in Fig. 2.11. Although this two-stage opamp is usually slower than single stage designs, it can provide higher gain and large output signal swing, therefore is popular in low voltage pipelined ADC designs. Besides cascode and cascade (multi-stage opamp), another way to increase opamp gain is gain-boost technique which employs feedback scheme to enhance the output impedance of an opamp [33][34]. Because this technique does not compromise opamp bandwidth (like cascade) or signal swing (like cascode) and can be used with cascode and cascode together if more gain is needed, it is extensively used in current high-speed and high resolution pipelined ADC design. If highest bandwidth is of interest, the G<sub>m</sub> boost technique [35] which employs a wide band low gain preamplifier to boost the input equivalent G<sub>m</sub> and so bandwidth without increasing input parasitic capacitance can be used.

#### **2.2.3 Sub-ADC**

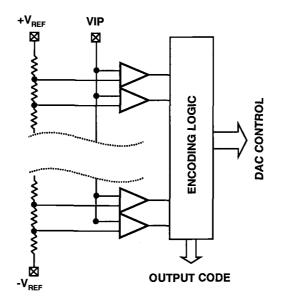

Another important building block in pipelined ADCs is the sub-ADC within each stage. Usually, the flash ADC architecture is employed and the resolution is less

than 5-bit. Figure 2.12 shows the diagram of a typical sub-ADC. The input signal is fed into 2<sup>N</sup> comparators in parallel directly (for an N-bit sub-ADC). The threshold voltages of these comparators are provided by a resistor string. And their outputs will go through bubble correction logic to minimize the effects of threshold error. Note the output word is thermometer code. So, after the bubble correction, an encoding circuit is needed to translate it to binary code to reduce the data bus width. Besides the function of a standard flash ADC, the sub-ADC has to provide the DAC control signal for MDAC. While the absolute delay of output binary code is relatively unimportant, the delay time of the DAC control signal is really critical and need to minimize in practical designs. Otherwise, it will take up the settling time of MDAC and limit the speed of overall ADC.

Fig. 2.12 Structure of a typical sub-ADC

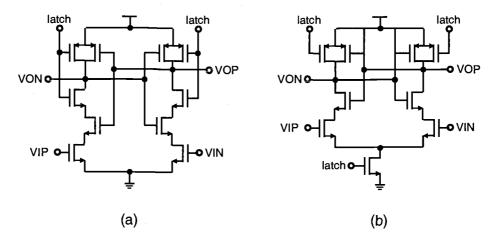

Fig. 2.13 Capacitive coupled comparator module

The capacitive coupled comparator shown in Fig. 2.13 is commonly used in sub-ADC designs because it can handle large input signal range and adopt offset cancellation easily. The non-overlap clock two phase clock is the same as shown before in Fig. 2.6. During the resetting phase (last sample), the input capacitors are reset to threshold voltage. Next, during the sampling phase (current sample), the input signal is sampled into the input capacitors. Thus the difference between input signal and threshold voltage will show up at the input of lathed comparator. Right before the end of the sampling phase, the latched comparator will be triggered, and the comparison result will be available to use by the encoding logic and DAC control logic in the beginning of the resettling phase. Notice that the comparator latching time is only about the non-overlap time of the two phase clock. This time gap is very small compared to the clock period (usually less than 10%). For instance, the comparator needs to latch within 1ns even though the pipelined ADC's clock frequency is only

about 100MHz. In very high speed pipelined ADC design, this stringent latching time requirement could pose a speed limitation. A simple solution to this problem is to reduce the sampling time of the comparator, so more latching time is assigned.

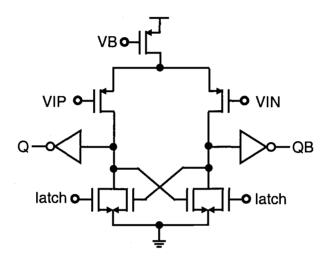

Fig. 2.14 Static latched comparator

The latched comparator used in the capacitive coupled comparator module could be just a single stage comparator without preamplifier since the accuracy requirement is very relaxed (usually less than 4bit). For example, in a 1.5bit/stage pipelined ADC, the static latched comparator shown in Fig. 2.14 can be used in for its simplicity, or the dynamic comparators shown in Fig. 2.15 can be used for their ultra low power consumption. When the sub-ADC has resolution more than 4bit, multistage comparator design with offset cancellation is usually required to reduce kickback noise and increase accuracy.

Fig. 2.15 Dynamic latched comparator

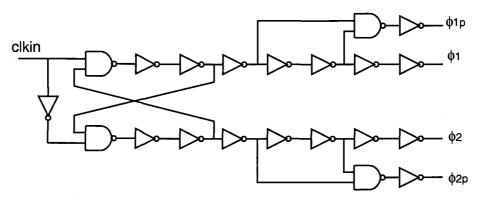

## 2.2.4 Clock Generator and Clock Buffer

Fig. 2.16 Clock generator

The clock generator shown in Fig. 2.16 can be used to generate the four clock signals shown in Fig. 2.6 from the input reference clock. The non-overlap time and the early falling time can be adjusted easily by changing the number or the unit delay time of the delay cells in this clock generator. The size of these delay cells can be minimized to reduce the power consumption and the noise injection to the substrate and power supply. However, the jitter added in the clock generator will increase

accordingly with smaller transistor size. Moreover, smaller transistor size makes the circuit more sensitive to the layout interconnection parasitic capacitance. In practical design, the transistor size should be optimized considering the trade-off mentioned above and the specific design requirement. Another thing needs to mention is that minimizing the input-output delay of the clock generator can help reduce the added jitter in clock generator.

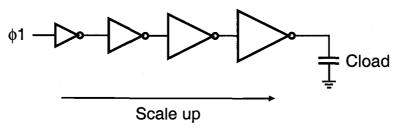

Fig. 2.17 Clock buffer

Except in those very low-speed switched capacitor circuit, usually clock buffers are needed between the outputs of the clock generator and their loads. These buffers can improve the driving capability of the clock generator so fast rising/falling edge clock waveforms can be maintained even with big capacitive loads. Moreover, the skew and clock rising/falling time can be also tuned by tweaking the clock buffer design. As shown in Fig. 2.17, a typical clock buffer is just a chain of inverters with their sizes scaled up. The scaling ratio is usually about 2.7 for minimum delay but can be varied in practical design depending specific requirement.

#### 2.2.5 Reference Buffer

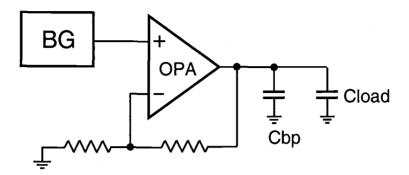

Fig. 2.18 Reference buffer

Although voltage reference circuit is not necessary a part of pipelined ADC, it is worthy of a simple introduction because it is very critical to the performance of the pipelined ADC. The voltage reference can be generated from a band-gap reference circuit amplified/buffered by a non-inverting amplifier shown in Fig. 2.18. While the gain of opamp and the matching of the resistor are usually not very important as far as one reference circuit is shared by all the stages of the pipelined ADC, the bandwidth requirement of a reference buffer is very critical and must be designed carefully. There are two opposite scheme for choosing the bandwidth. First, make the bandwidth very high to satisfy the settling requirement for given total capacitor load. Obviously, this scheme will consume quite amount of power (20%-30% of the overall power consumption a pipelined ADC). Sometime class-AB reference buffer are used to reduce the power consumption. The second scheme is to put a very big bypassing capacitor in parallel with the loading capacitor. Now the transient voltage change at the voltage reference node is approximately:

$$V_{tran} = V_{REF} \frac{C_{load}}{C_{byp} + C_{load}}, \tag{2.2}$$

where  $V_{\it REF}$  is the average reference voltage. It can be seen that the settling accuracy is decoupled from the bandwidth of the reference buffer and is only a function a bypassing capacitor size. Thus, dramatic power saving can be achieved since the bandwidth can be very low. However, the required bypassing capacitor is usually too big to put on-chip and an external bypassing capacitor has to be used. This can limit the speed of the pipelined ADC because of the bonding wire inductance. A simple solution to this issue is to carefully design the capacitor switching scheme so  $C_{load}$  takes the same amount of charge from  $C_{byp}$  at each clock period. Therefore large transient reference voltage change is not a problem since it is always the same. As a result smaller on-chip bypassing capacitor can be used.

### 2.2.6 Other Circuitry

The other circuitry in the pipelined ADC includes bias generator, digital correction logic, switches, capacitors and resistors. These circuits or components are either very simple or less important and will be discussed wherever needed in the later sections or chapters.

#### 2.3 Important Design Issues

#### 2.3.1 MOS Switches

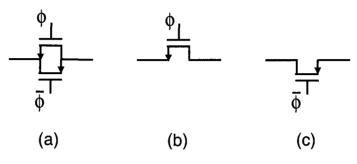

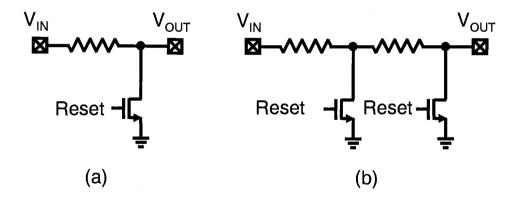

Fig. 2.19 MOS switches

The MOS switches used in SC circuits are shown in Fig. 2.19. Among them, NMOS/PMOS switches are usually used at the node where fixed voltage levels are applied (NMOS switches for lower voltage and PMOS switches for higher voltage), while CMOS switches are usually used in signal path where the voltage is changing between low level and high level. Two major concerns when designing a MOS switch are the on-resistance and charge injection. The on-resistance for a NMOS switch (assume  $V_{ds}=0$ ) can be written as:

$$R_{on} = r_{ds} \approx \frac{1}{\mu C_{ox}(\frac{W}{L})(V_{GS} - V_{tn})},$$

(2.3)

And the charge injection voltage error is:

$$V_{ch} = \frac{Q_{ch}}{C_{ea}} = \frac{WLC_{ox}(V_{GS} - V_{th})}{C_{ea}},$$

(2.4)

Where  $C_{eq}$  is the overall capacitance associated with source/drain of the MOS switch. In practical design, the sizes of MOS switches need to be optimized to minimize both on-resistance and charge injection. Furthermore, the nonlinearity of on-resistance must be considered also when the switches are used as the sampling switches in the very first S/H circuit of the pipelined ADC. Otherwise, extra nonlinearity will be introduced by the nonlinear switches. This is particularly important in low voltage and high-speed design.

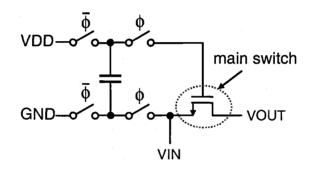

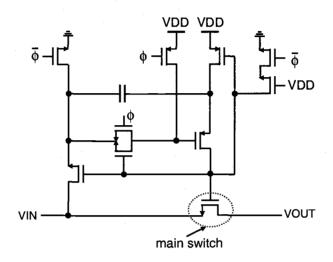

Fig. 2.20 Conceptual bootstrapped switch

To solve this issue, bootstrapped switches instead of simple CMOS switches are usually used as sampling switches to sample high frequency input signal [36][37][38]. Their operation can be illustrated in Fig. 2.20. A constant voltage (VDD in this case) is put across the gate and source of the main NMOS sampling switch to turn on this switch during sampling phase. Thus the on-resistance of the main sampling switch is kept constant even the input signal amplitude is changing quickly. As a result, the nonlinearity from sampling switches is eliminated. A practical implementation of bootstrapped switch proposed in [37] is shown in Fig. 2.21. It is

much more complex than the common CMOS switch, therefore usually only used as the sampling switch in the S/H stage.

Fig. 2.21 Implementation of bootstrapped switch

#### **2.3.2** Noise

Two type of noise can be added into the input signal during the A/D conversion. One is the external interfering noise such as digital switching noise and power supply noise. It can be coupled into the ADC through power supply, substrate and interconnection. The other is the internal circuit noise generated from the transistors and resistors used in the ADC design as well as the quantization noise due to the quantization. Since the quantization noise is fixed after the ADC's resolution is determined, here we only focus on how to reduce interference noise and circuit noise.

While the external interference can be suppressed effectively by good layout skills and fully differential architecture, the internal circuit noise must be taken care in

the beginning of the pipelined ADC design. The total input referred noise in a pipelined ADC is:

$$V_{n_{-}in}^{2} = V_{n_{-}SH}^{2} + V_{n_{-}1}^{2} + \frac{1}{2^{2m}} V_{n_{-}2}^{2} + \frac{1}{2^{4m}} V_{n_{-}3}^{2} + \dots + \frac{1}{2^{2km}} V_{n_{-}k}^{2} + \dots,$$

(2.5)

where  $V_{n\_SH}^2$  is the noise in S/H stage,  $V_{n\_k}^2$  is the noise in the kth stage and m is the inter-stage gain of each stage. Since the noise from the following stages is suppressed by the inter-stage gain, the noise in S/H stage and the first stage pipeline is the dominant noise source and need to be controlled carefully in the pipelined ADC design.

The input referred noise in S/H or MDAC due to switch resistance and opamp can be calculated as:

$$V_n^2 \approx \frac{kT}{C_s} \cdot \frac{C_{total}}{C_s} + V_{opamp}^2(\omega) \cdot \omega_{noise} \cdot \frac{G_n^2}{G_{sig}^2}$$

(2.5)

where  $C_s$  is the sampling capacitor;  $C_{total}$  is the total capacitor used in S/H or MDAC,  $V_{opamp}^2(\omega)$  is the opamp's input-referred noise power density,  $\omega_{noise}$  is the opamp noise bandwidth,  $G_n$  is the opamp noise gain,  $G_{sig}$  is the signal gain. If we only consider thermal noise since it is the dominant source in high-speed pipelined ADC and ignore the 1/f noise. Eq. (2.5) can be written as:

$$V_n^2 \approx \frac{kT}{C_s} \cdot \frac{C_{total}}{C_s} + \gamma \cdot \frac{\beta}{C_c} \cdot \frac{G_n^2}{G_{sig}^2}$$

(2.6)

where  $\beta$  is the feedback factor,  $C_c$  is the opamp compensation capacitor and  $\gamma$  is a constant determined by the actual opamp design. Several design guidelines for low noise operation can be observed from above equation. First, the circuit noise is determined by the sizes of sampling capacitor and compensation capacitor. Increasing the size of these capacitors can reduce the noise. However, it will increase the die area and power consumption. In practical design, the sizes of these capacitors should be optimized considering this power-noise tradeoff. Second, the capacitors which are not connected to the input as sampling capacitor during sampling phase will contribute extra noise. So it is not a good practice to have separate feedback capacitor or reference sampling capacitor during sampling phase in terms of low noise operation. Third, the opamp should be optimized to achieve small noise factor  $\gamma$ . For example, we can reduce the trans-conductance of the active load of the input differential pair in the opamp to reduce the noise contribution from these transistors.

One thing need to mention is that the noise from the resetting switches and the switches connecting the feedback capacitor to the opamp's output during holding/amplifying phase is assumed to be very small and ignored in Eq. (2.5). However, this is not always true in practical circuit design. In reality, the noise of these switches is probably comparable to the noise due to the sampling capacitor.

Some designers take it into account by adding another  ${}^{kT}\!\!/_{C_s}$  noise in Eq. (2.5). This is probably a pessimistic estimate since this noise will be filtered by the opamp which usually has lower bandwidth than the RC network formed by the switches and associated capacitors. In practical pipelined ADC design, the more accurate noise analysis can be obtained by indirect simulation using AC noise analysis or direct simulation by PSS and PNOISE analysis in SPECTRE.

# 2.3.3 Opamp Gain and Bandwidth

Finite opamp DC gain will create a non-zero voltage at the virtual ground, therefore makes the charge transfer-function of S/H or MDAC inaccurate. This effect can be modeled as adding a voltage error to the ideal opamp output:

$$V_{out} \approx V_{out ideal} + V_{err, opamp} \tag{2.7}$$

While this error voltage is proportional to the input voltage, its largest value is bounded by the opamp's output signal range:

$$V_{err\_opamp} \le \frac{V_{ref}}{a\beta} \tag{2.8}$$

where a is the opamp DC open loop gain,  $\beta$  is the feedback factor and  $V_{ref}$  is the reference voltage value which determine the signal range. Eq. (2.8) can be used to set the spec. for each stage's opamp DC gain. For example, in a 10b pipelined ADC with 1.5b/stage, the first stage's opamp gain should be at least 60dB if the feedback factor

is 0.5. In practical design, at least 70dB or even 80dB gain should be achieved for opamp design to guarantee robust operation. Similar to the noise calculation, the errors due to finite opamp gain in the following stages will be suppressed by the interstage gain of the pipeline ADC. Thus, the opamp gain requirement is scaled down with the pipeline.

The opamp's closed-loop bandwidth determines the output settling accuracy of S/H or MDAC. The settling error due to opamp's finite bandwidth (single pole system) can be written as:

$$V_{err set} \approx e^{-t_{set}/\tau} V_{set} = e^{-t_{set}\omega_{CL}} V_{set}$$

(2.9)

where  $t_{set}$  is the available settling time which is around half period of the clock cycle,  $\tau$  is the settling time constant determined by the opamp's closed-loop bandwidth  $\omega_{CL}$ ,  $V_{set}$  is the opamp's ideal output voltage step for settling which is usually in the range of 0 to  $V_{ref}$ . Eq. (2.9) can be used to set the bandwidth requirement for the opamp design. For example, again in a 10b pipelined ADC with 1.5b/stage, if the clock frequency is 100MHz, the clock period will be 10ns, so the maximum settling is about 5ns. The settling error of the first stage needs to be less than 0.1% to give 10b accuracy. Then the required opamp closed-loop bandwidth is:

$$f_{CL} = \frac{1}{2\pi} \cdot \frac{-\ln(\frac{1}{2^{10}})}{T/2} = \frac{1}{2\pi} \cdot \frac{7}{5 \times 10^{-9}} = 223 \text{MHz}$$

(2.10)

The relationship between opamp's unit-gain bandwidth and opamp's closed-loop bandwidth is:

$$f_{CL} = f_{UGR} \cdot \beta \tag{2.11}$$

So to maximize opamp gain-bandwidth and feedback factor can lead to maximum closed-loop bandwidth and then minimum settling time or settling error.

## 2.3.4 Capacitor Mismatch

Capacitor mismatch is another major error source in pipelined ADC and can affect the linearity directly. Therefore must be considered from the very beginning of the ADC design. The differential non-linearity (DNL) due to capacitor mismatch of the first stage, normalized to the least significant bit (LSB), can be written as [7]:

$$DNL = \frac{\lambda \cdot 2^{N - m/2}}{\sqrt{C_{total}}}$$

(2.12)

where N is the resolution (bits) of the overall ADC, m is the resolution (bits) of the first stage,  $C_{total}$  is the total sampling capacitor in the first stage and  $\lambda$  is the constant related to the random variation of capacitance. From Eq. (2.12), it can be seen that the DNL improves by a factor of  $\sqrt{2}$  with every extra bit in the first stage or doubling the total capacitance in the first stage. This also means the DNL can be improved by resolving more bits in the first stage for given total capacitance. That's probably the main reason that most people prefer multibit/stage architecture for high resolution

pipeline ADC design. However, the integral non-linearity (INL) is not affected by the stage resolution and only depends on the total capacitance:

$$INL = \frac{\lambda \cdot 2^N}{\sqrt{C_{total}}} \tag{2.13}$$

The interesting truth here is that INL follows the same rule as the  ${}^{kT}\!\!/_{C}$  noise: both of them can only improved by increasing the total capacitance. Like the finite gain effect, the requirement on capacitor matching is also scaled down with the pipeline.

## 2.3.5 Charge Injection and Clock Feed-through

Charge injection and clock feed-through can cause differential signal error and/or common mode level shift. The signal dependant charge injection due to the switches connected to the bottom plate of the sampling capacitor can be eliminated by turning off the switches connecting the top plate to ground node earlier. Fully differential architecture can cancel the errors due to clock feed-through. And it is always helpful to insert dummy switches at sensitive nose such as virtual ground to absorb the charge injection. Finally, it is a good practice to try to use as less switches as possible and make them as small as possible (but enough to satisfy on-resistance requirement).

#### 2.4 Advanced Design Techniques

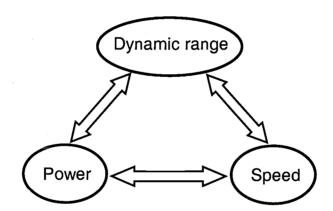

As with most analog circuits, pipelined ADC designs suffer from trade-offs among various parameters. The main trade-off exists among power, speed and dynamic range as illustrated in Fig. 2.22. In addition, the die area, design complexity and cost are also need to be considered. Facing these trade-offs, a good designer should adopt appropriate techniques to optimize the design for the best figure-of-merit. Besides the standard pipelined ADC design techniques described earlier, there are many more advanced techniques developed for optimizing the overall design and enhancing the performance of pipelined ADCs.

Fig. 2.22 Dynamic range, power and speed trade-off

The most commonly used design optimization technique in pipeline ADC design is capacitor scaling. As described earlier, the capacitor size is determined by kT/C noise and matching requirements which are decreased down the pipeline. So it is very natural to scale down the sizes of the capacitors and their associated opamps from the first stage to the last stage in the pipeline. As a result, 20%-30% power and area

saving can be achieved easily even in 10b ADC. And more power and area saving can be expected for a higher resolution design.

While 1.5bit/stage architecture is very popular for its simplicity and high speed, many designers choose multibit/stage architecture for better DNL and lower power consumption, particularly in high resolution ADCs (more than 12b). Then the choosing of stage resolution becomes a critical issue. Higher bits/stage means less number of stages. However, each opamp's feedback factor will be small and consumes more power to keep the same speed. Moreover, the number of comparators in each stage will increase exponentially with stage resolution. So it is not easy to determine the optimum stage resolution. This issue gets more complicated when entangled with the capacitor scaling. While the detailed analysis can be found in [39][40], some architecture level simulation incorporating accurate process information can be done to get the optimum point.

Another very effective power saving technique is opamp sharing [41][42][43] which is proposed based on the observation that, in standard pipeline ADC design, the opamps are only resetting during one clock phase. So they can be shared between two cascaded stages by serving each stage alternately during two clock phases. This technique can reduce the opamp number. As a result drastic power and area save can be achieved. The main drawback of this method is the memory issue to opamps since they are never reset. A new opamp sharing configuration is just developed recently

which can reduce the memory voltage to 1/3 of conventional configuration [6]. Another minor issue in opamp sharing technique is, since opamp are being switched back and forth between two stages, more switches are needed and charge injection is increased.

While the power saving can be achieved by applying the approaches introduced above, the speed of pipelined ADCs can be improved dramatically by using multi-channel architecture with time interleaved operation [44][45]. Although the area and power also increase in this case, it is still worth if the conversion rate is the primary concern and is limited by the process. The main design issue in multi-channel ADC design is the channel mismatches including offset, gain and timing mismatch. Offset mismatch can produce tone at  $f_s/M$ , where  $f_s$  is the sampling frequency and M is the numbe of channels. Gain and timing mismatch can generate the tone at the image frequency of the input signals. Usually certain calibration is needed to eliminate these mismatches even at 10-b level design [46].

Besides the power optimization techniques and speed boosting technique, there are many accuracy enhancement techniques to improve the accuracy of pipelined ADCs which is limited mainly by component mismatches and finite opamp gains, for example, digital self-calibration techniques, background calibration techniques and other analog techniques. The details of them will be described in the next chapter.

### 3 ACCURACY ENHANCEMENT TECHNIQUES

The accuracy of pipelined ADCs is limited mainly by finite opamp gains and capacitor mismatches. During the not very long history of monolithic pipelined ADCs, many correction techniques have been developed to exceed these technology limits. And these accuracy enhancement techniques can be categorized into three types: analog correction, digital self-calibration and background calibration. The key concepts of them will be explained in this chapter.

## 3.1 Analog Correction

In analog correction techniques, the errors due to component mismatches and finite opamp gains are corrected in analog domain with extra analog circuitry. The advantage of analog correction techniques is low complexity. But like any other analog circuit, they are usually sensitive to process and environment variation. And the conversion rate may be compromised. Ratio-independent multiplication, reference-refreshing, capacitor error averaging, analog trimming and correlated double sampling (CDS) technique are such kind of classical analog correction techniques.

Ratio independent multiplication [8] can be illustrated in Fig. 3.1. The input signal is sampled twice by the same capacitor. The charge collected during the first sampling is transferred and stored temporarily in another capacitor. After the second sampling, this stored charge is transferred back to the sampling capacitor again to

realize voltage amplification. Note the accuracy of this amplification is independent of capacitor ratio because there is no net charge transferring between two capacitors. However, four steps are required to implement this method. As a result, the conversion rate is almost reduced by half given the same opamp settling time.

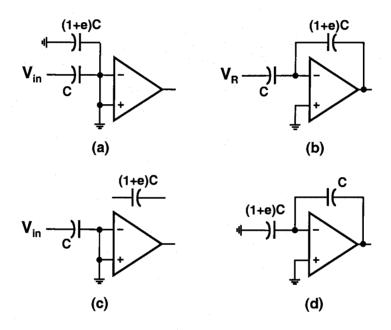

Fig.3.1 Ratio independent multiplication

While the ratio independent multiplication approach tries to avoid the errors due to capacitor mismatches, the error averaging technique [10] cancels them in three steps with two switched capacitor amplifiers as illustrated in Fig.3.2. During the sampling phase, the input signal is sampled by the first amplifier. Next, during the amplification phase, the sampled input signal is amplified by the first amplifier like regular MDAC. In the mean time, the output of the first amplifier is sampled by the second amplifier. Note this output contains the error due to capacitor mismatch.

Finally, during error averaging phase, the two capacitors in the first amplifier exchange their positions. As a result, the error component in the first amplifier's output changes the polarity. This inverting error passes through the second amplifier and cancels out the sampled error component during amplification phase. So the final output of the second amplifier will be free of error due to the capacitor mismatch in the first amplifier. However, the price is the conversion rate is reduced by 1/3, the power consumption is doubled and the noise also increases significantly.

Fig.3.2 Capacitor error averaging

Another analog correction technique is the capacitor trimming [13][47]. It is a very straight forward solution to the capacitor mismatch problem as shown in Fig.3.3. The capacitance of one capacitor in regular MDAC can be tuned to match the other

capacitor by connecting a small trimming capacitor to it. In practical circuit implementation, this "trimming capacitor" is usually an array of capacitors controlled by digital logic. The accuracy of this capacitor trimming technique is limited by the accuracy of the small trimming capacitors, therefore sensitive to process variation. Another thing need to mention is the capacitor trimming technique is a foreground correction method which means the normal A/D conversion has to be interrupted to do the trimming.

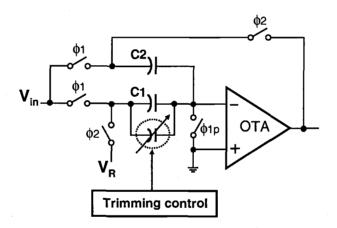

Fig.3.3 Capacitor trimming

An indirect but equivalent solution to capacitor mismatch and finite opamp gain problem is the reference refreshing technique [9]. Instead of making the MDAC as accurate as possible, this technique varies the reference voltage injected at each MDAC to compensate the errors due to capacitor mismatches and finite opamp gain. This can be explained by a simple equivalent transformation:

$$G_{i}(V_{in}^{[i]} - D_{i}V_{ref}^{[i]}) - D_{i+1}V_{ref}^{[i+1]}$$

$$= G_{i}(V_{in}^{[i]} - D_{i}V_{ref}^{[i]} - D_{i+1}\frac{V_{ref}^{[i+1]}}{G_{i}})$$

$$= G_{i}(V_{in}^{[i]} - D_{i}V_{ref}^{[i]} - D_{i+1}\frac{V_{ref}^{[i]}}{2})$$

(3.1)

where

$$G_i = 2(1 + e_i)$$

$$V_{ref}^{[i+1]} = V_{ref}^{[i]}(1 + e_i).$$

(3.2)

It can be seen that the reference voltage of next stage can be adjusted to compensate the inter-stage gain error caused by capacitor mismatches and finite opamp gain. The accurate adjustment of reference voltage can be done by letting the voltage reference go through the same path as the input signal. However, the implementation is usually complex and requires more clock phases.

While most analog correction methods described above mainly deal with capacitor mismatches, the correlated double sampling (CDS) technique is a very effective approach to reduce the errors due to finite opamp gain and make it inversely proportional to the square of opamp gain [48]-[53]. Equivalently, this doubles the opamp gain in dB. Moreover, the opamp offset is cancelled and 1/f noise is suppressed. The linearity of the amplifier can be also improved dramatically [53]. There are several different CDS schemes. But their principles are similar: stores the non-zero opamp input voltage due to finite opamp gain in a capacitor, then this pre-stored error

is used to cancel out the error in the next clock phase. Note there is very small added power consumption in CDS technique since only passive components such as switches and capacitors are needed. This technique will be discussed with more details in the next chapter.

## 3.2 Digital Self-calibration

In the early period of the development on accuracy enhancement techniques, analog correction is the focus of the study. However, with the rapid improvement of fine line CMOS technology and digital signal processing techniques, people realized that it maybe a better solution to measure the errors by ADC itself and correct them in digital domain for the robustness. As a result, several digital self-calibration techniques [14][15][16] were developed to incorporate these two features. And they have been the most extensively used calibration techniques in high resolution pipelined ADC designs so far because of their superior performance.

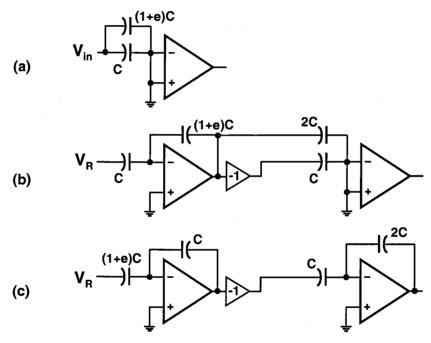

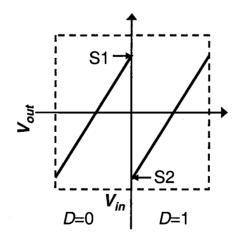

Fig. 3.4 Transfer curve of 1b MDAC

The operation of digital self-calibration can be illustrated in the context of a 1b/stage pipelined ADC for simplicity although it can be applied to multibit/stage ADC as well. Fig.3.4 shows the transfer curve of a 1bit MDAC. S1 and S2 correspond to the quantized residue voltage when  $V_{in} = 0$  with D = 0 and D = 1 respectively, where D is the bit decision of this stage. After S1 and S2 are measured by the following pipeline ADC stages, the calibration of this stage can be done in the digital domain by correcting the raw code:

$$Y = X$$

, if  $D = 0$

$Y = X + S1 - S2$ , if  $D = 1$  (3.3)

where X is the raw code (the digital output of this stage and its following stages) and Y is the final code. This correction algorithm eliminates the gap in the ADC's transfer curve at  $V_{in} = 0$ . As a result, a highly linear A/D conversion is achieved even with imperfect MDAC. Note there is still probably a gain error to the overall ADC, but that is usually not a problem in most applications. In the calibration algorithm just described, it is assumed that the following stages are linear. This can be guaranteed by doing the calibration from the last stage to the first stage.

Unlike the analog correction, the digital self-calibration requires no extra analog circuit. This makes the original MDAC design (the most critical part in pipelined ADC) essentially unchanged. So there is no compromise of conversion rate or power consumption due to calibration. Some extra digital circuitry is added, but

with the sub-micron CMOS technology, the resulting power consumption and die area overhead will be negligible. More importantly, the calibration is very robust and insensitive to process and environment variation. However, there is one limit: the normal ADC's operation has to be interrupted for the error measurement. Usually, the calibration is done during the system power-up or standby mode to avoid this interruption. However, it is desirable to run the calibration at all time to track the device and environment variation. That necessitates the concept of background calibration which will be introduced in the next section.

#### 3.3 Background Calibration

Background calibration is a much more difficult job than foreground calibration. Usually, much more hardware is needed and the performance of ADC is compromised. Here, the main issue is how to isolate the calibration process from the normal operation of ADC. Many clever schemes are developed so far on this isolation. Unfortunately, they all have their limitations. Therefore, background calibration is still a good topic worthy of continuing study.

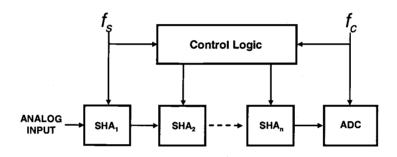

A very straightforward background calibration scheme is to replace the pipeline stage under calibration with an identical redundant stage. So the normal A/D conversion will not be interrupted [19]. And any suitable foreground calibration approach can be employed to correct the stage being substituted. The main drawbacks of this method is the large overhead of power consumption and die area overhead