### AN ABSTRACT OF THE DISSERTATION OF

<u>Mahmoud Sadollahi</u> for the degree of <u>Doctor of Philosophy</u> in <u>Electrical and</u> <u>Computer Engineering</u>, presented on <u>February 5, 2018</u>.

Title: <u>Power Efficient Architectures for Medium-high Resolution Analog-to-Digital</u> <u>Converters.</u>

Abstract approved: \_\_\_\_\_

Gabor C. Temes

Analog-to-digital converters are essential components to the portable devices that we are using today. Wireless sensors, body implanted devices, communication devices and so forth require low power ADCs. Therefore achieving higher resolution and bandwidth with lower power consumption is targeted in ADCs design. In this work power efficient ADCs for medium-high resolution is presented.

In this dissertation first an ultra-low power successive approximation register SAR ADC is presented. The ADC is an 11-bit single-ended, low power, area efficient one with small loading effect, targeted for biomedical applications. The design features an energy-efficient switching technique to cover an input range twice the reference voltage. The ADC's loading effect to previous stage is reduced by using single-ended structure and eliminating the largest capacitor (MSB capacitor) in the switching network. All building blocks were designed in subthreshold for power efficiency, with asynchronous self-controlled SAR logic. The ADC was fabricated in 0.18  $\mu$ m CMOS 2P4M process. The measured peak SNDR was 60.5 dB, the SFDR was 72 dB, the DNL +0.6/-0.37 LSB and the INL +0.94/-0.89 LSB. The total power consumption was 250 nW from a 0.75V supply voltage. This gives a Walden FoM of 28.8 fJ/Conv-step.

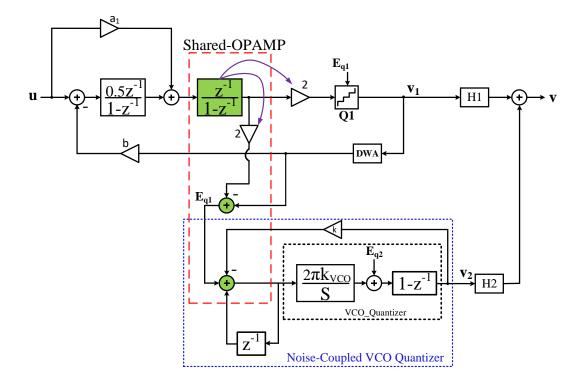

In addition, a noise-coupled VCO-based quantizer is presented. By applying the noise-coupling technique a second order noise-shaped quantizer is achieved, which gets one order from VCO-quantizer and another order from noise-coupling technique.

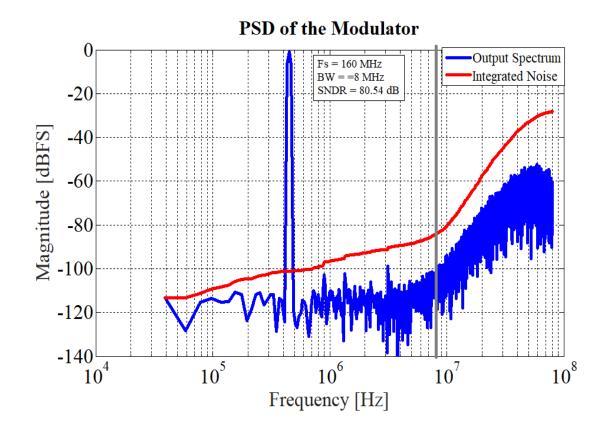

This quantizer is employed as the second stage in a 2-2 MASH delta-sigma modulator with  $4^{rd}$  order noise-shaping. Thus the input signal range of the VCO is the quantization error of the first stage and it is in the linear range of the VCO. OPAMP sharing technique is used between the first and second stage to save power. Proposed architecture was designed and implemented in 0.18 µm CMOS 2P6M process at sampling frequency of 160 MHz with 8 MHz bandwidth. The achieved peak SNDR is 80.54 dB and SFDR is 94 dB.

Finally a 3<sup>rd</sup> order passive delta-sigma modulator employing a VCO-based quantizer is presented. A conventional passive delta-sigma modulator and proposed passive delta-sigma modulator has been designed and simulated for comparison. The results show power efficiency for the proposed structure.

©Copyright by Mahmoud Sadollahi February 5, 2018 All Rights Reserved

# Power Efficient Architectures for Medium-high Resolution Analog-to-Digital Converters

by Mahmoud Sadollahi

## A DISSERTATION

submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Presented February 5, 2018 Commencement June 2018 Doctor of Philosophy dissertation of Mahmoud Sadollahi presented on February 5, 2018

APPROVED:

Major Professor, representing Electrical and Computer Engineering

Director of the School of Electrical Engineering and Computer Science

Dean of the Graduate School

I understand that my dissertation will become part of the permanent collection of Oregon State University libraries. My signature below authorizes release of my dissertation to any reader upon request.

Mahmoud Sadollahi, Author

#### ACKNOWLEDGEMENTS

I would like to express my deepest and sincere appreciation to my advisor, Professor Gabor C. Temes, who gave me the chance to do research and my PhD under his advisory. It is my honor and privilege to benefit from his extensive knowledge in Analog/Mixed signal circuit design area. His personality is as admirable and outstanding as his expertise in circuit design. I thank him for providing a comfortable and free environment to follow my research and providing all the financial support. It was great honor and pleasure for me to work under his supervision.

I also would like to thank my Ph.D. program committee members, Professor Karti Mayaram, Professor Matthew Johnston, Professor Thinh Nguyen and Professor Huaping Liu for serving in my committee and giving a valuable feedbacks on my dissertation. Special thanks to Professor William Warnes for serving as graduate council representative on my committee.

Thanks to AKM for providing the chip fabrication and their support. Kazuki Sobue and Koichi Hamashita helped a lot with chip fabrication and they provided a great technical support.

I had privilege to take different courses during my study in Oregon State University, and I learned a lot from those classes. I would like to thank Professor Un-Ku Moon, Professor Pavan Kumar Hannumolu, Professor Arun Natarajan, and Professor Patrick Chiang.

I would like to thank Nicole Thompson and all other EECS office members for their supports.

I have to thank all my research-group members, officemates, colleagues, and my friends present and past for their help and supports.

Finally and specially, I want to express my deepest appreciation and thanks to my parents and siblings for their unconditional love and supports.

# TABLE OF CONTENTS

|                         |                                           | Page                  |

|-------------------------|-------------------------------------------|-----------------------|

| CHAPTER 1. INTR         | ODUCTION                                  | 1                     |

| 1.1 Motivation          |                                           | 1                     |

| 1.2 Contributions       |                                           | 2                     |

| 1.3 Organization of Di  | ssertation                                | 3                     |

| CHAPTER 2. NYQU         | JIST-RATE AND OVERSAMPLING ADCS           | 5                     |

| 2.1 Nyquist-Rate ADC    | Cs                                        | 6                     |

| 2.2 Oversampling AD     | Cs                                        | 8                     |

| CHAPTER 3. AN 11        | -BIT 250-nW 10-kS/s SAR ADC WITH DOUB     | LED INPUT             |

| RANGE for BIOMEDIC      | CAL APPLICATIONS                          | 12                    |

| 3.1 Introduction        |                                           | 12                    |

| 3.2 Proposed SAR AD     | C Architecture                            | 15                    |

| 3.3 Circuit Realization | of the Proposed SAR ADC                   | 23                    |

| 3.3.1 Capacitive        | DAC                                       | 23                    |

| 3.3.1.a Capacito        | or mismatch and static linearity, DNL/INL | 24                    |

| 3.3.1.b DAC and         | offset error canceling network            | 29                    |

| 3.3.2 Comparato         | r circuit design                          |                       |

| 3.3.3 Asynchrono        | ous SAR control logic circuit             | 35                    |

| 3.4 Measurements Res    | ults                                      |                       |

| 3.5 Summary             |                                           | 45                    |

| CHAPTER 4. A NO         | ISE-COUPLED VCO-BASED QUANTIZER AN        | ND $\Delta\Sigma$ ADC |

| BASED ON NOISE-CO       | UPLED VCO-BASED QUANTIZER                 | 46                    |

### Page

# TABLE OF CONTENTS (Continued)

| 4.1 Introduction                                                              | 7   |

|-------------------------------------------------------------------------------|-----|

| 4.2 Noise-Coupled VCO-Based Quantizer                                         | )   |

| 4.3 Architecture of 2-2 MASH Modulator with Noise-Coupled VCO-Bas             | sed |

| Quantizer and OPAMP Sharing                                                   | 5   |

| 4.4 Circuit Implementation                                                    | 3   |

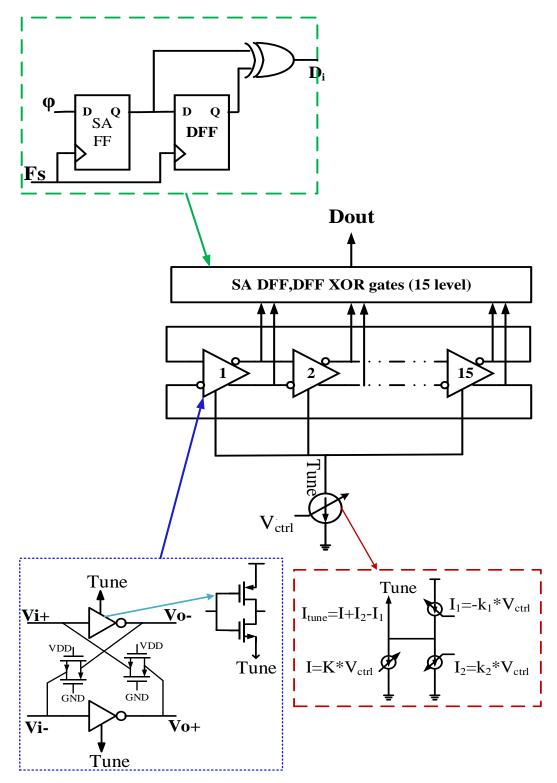

| 4.4.1 VCO-Based Quantizer                                                     | 3   |

| 4.4.2 OPAMP Circuit                                                           | }   |

| 4.4.3 First Quantizer                                                         | }   |

| 4.4.4 Clock Generator Circuit                                                 | )   |

| 4.4.5 DWA Circuit71                                                           |     |

| 4.5 Results                                                                   | }   |

| 4.6 Summary77                                                                 | 7   |

| CHAPTER 5. A PASSIVE 3 <sup>RD</sup> ORDER DELTA-SIGMA ADC WITH VCO-          |     |

| BASED QUANTIZER78                                                             | 3   |

| 5.1 Introduction                                                              | 3   |

| 5.2 Passive Switched Capacitor Integrator and Passive Sigma-Delta Modulator80 | )   |

| 5.3 The Proposed Passive $\Delta\Sigma$ ADC with VCO-based Quantizer          | 3   |

| 5.4 Simulation Results                                                        | 5   |

| 5.5 Summary                                                                   | )   |

| CHAPTER 6. CONCLUSION90                                                       | )   |

| Bibliography                                                                  | 2   |

# LIST OF FIGURES

| Figure     Page                                                                                                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. 1.1 Interface between real world signal and digital signal processing2                                                                                  |

| Fig. 2.1 Bandwidth vs resolution for different ADC architectures                                                                                             |

| Fig. 2.2 Nyquist-rate ADC's block diagram and power Spectrum density7                                                                                        |

| Fig. 2.3 Different biomedical signals specifications7                                                                                                        |

| Fig. 2.4 SAR ADC block diagram                                                                                                                               |

| Fig. 2.5 Oversampling ADC block diagram and power spectrum density9                                                                                          |

| Fig. 2.6 State-of-the-art $\Delta\Sigma$ ADC's energy plot vs. DR [2]9                                                                                       |

| Fig. 2.7 a) Block diagram and b) behavioral model of the VCO-based quantizer10                                                                               |

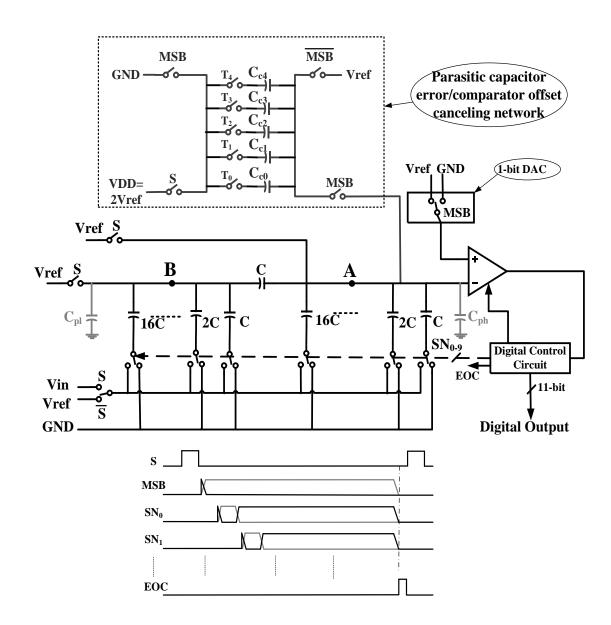

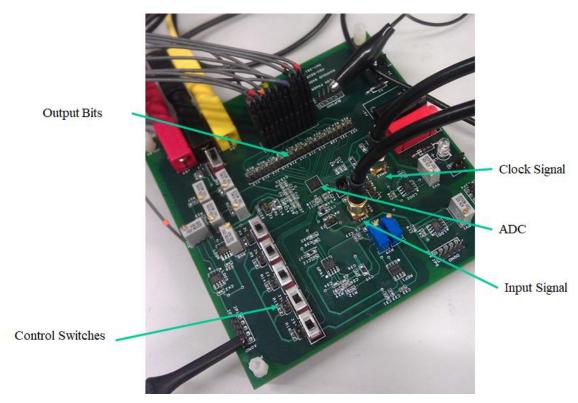

| Fig. 3.1 The proposed SAR ADC architecture and timing signals16                                                                                              |

| Fig. 3.2                                                                                                                                                     |

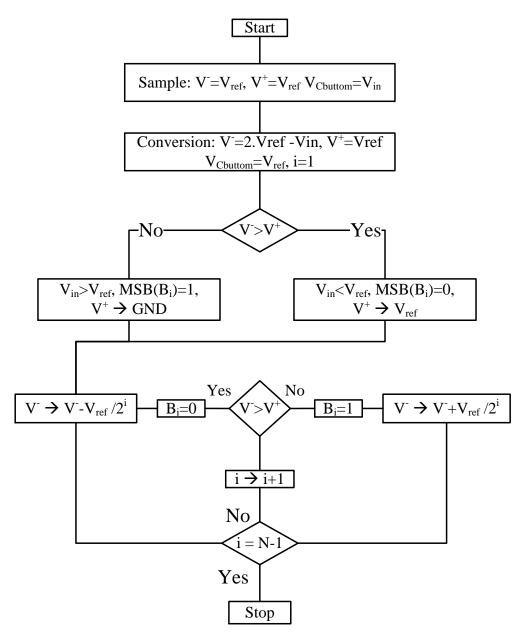

| Fig. 3.3 a) Switching procedure and switching energy for 3-bit example of the proposed structure, b) Voltage waveforms at non-inverting node of comparator20 |

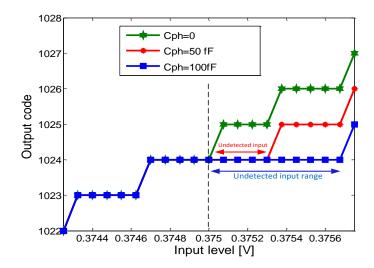

| Fig. 3.4 Output code for different C <sub>ph</sub> around midpoint transition21                                                                              |

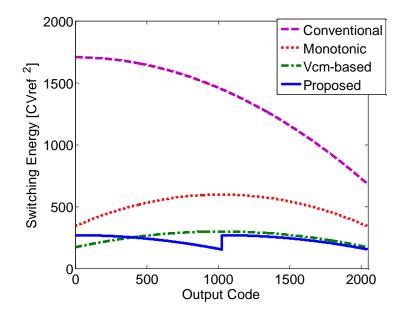

| Fig. 3.5 Switching energy versus output code comparison                                                                                                      |

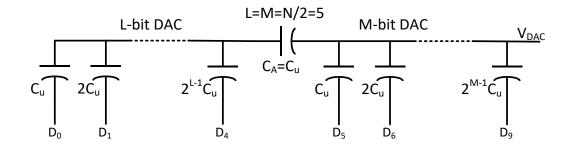

| Fig. 3.6 Capacitive DAC with unit bridge capacitor                                                                                                           |

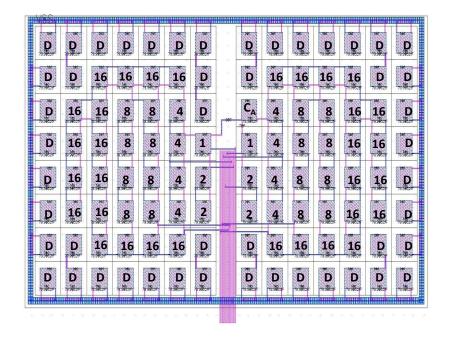

| Fig. 3.7 Capacitor DAC array with bridge capacitor                                                                                                           |

| Fig. 3.8 Capacitive DAC array floorplan and layout                                                                                                           |

| Fig. 3.9 Bootstrap switch schematic                                                                                                                          |

| Fig. 3.10 DAC error and comparator offset/error canceling capacitor network29                                                                                |

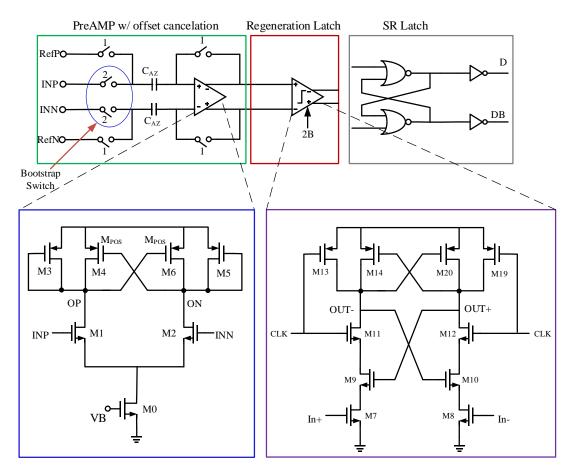

| Fig. 3.11 Circuit schematic of the comparator with preamplifier and dynamic latch.33                                                                         |

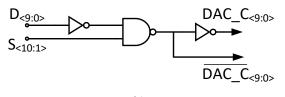

| Fig. 3.12 a) Block diagram of the asynchronous SAR control logic and timing diagram b) DAC switches control signal c) Control signals waveform               |

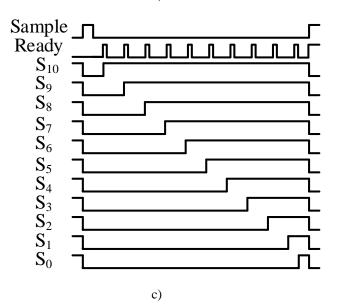

| Fig. 3.13 Die micrograph and the zoomed-in core                                                                                                              |

# LIST OF FIGURES (Continued)

| Figure                                                                                                                                                        | Page |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

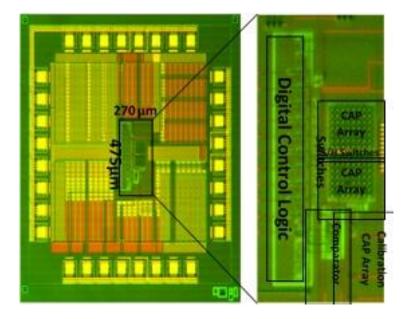

| Fig. 3.14 Test Set-up of the ADC.                                                                                                                             | 38   |

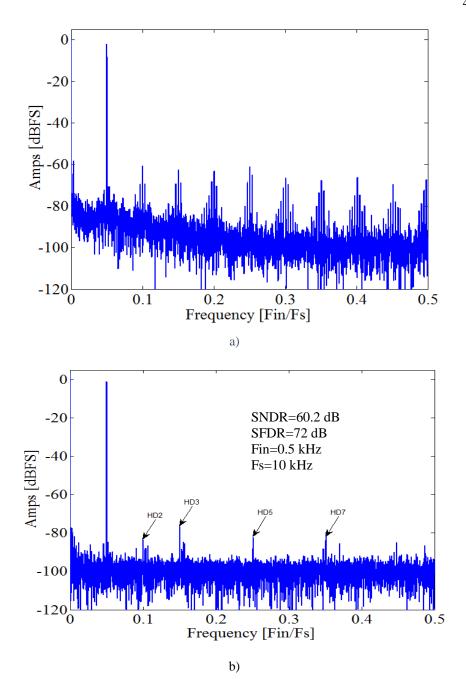

| Fig. 3.15 Measured ADC output for 0.5 kHz sinewave input a) without (EOC) error/offset canceling b) with error/offset canceling.                              | 39   |

| Fig. 3.16 Measured ADC output spectrum for 0.5 kHz sinewave input a) With error/offset canceling network off b) With error/offset canceling network on        | 40   |

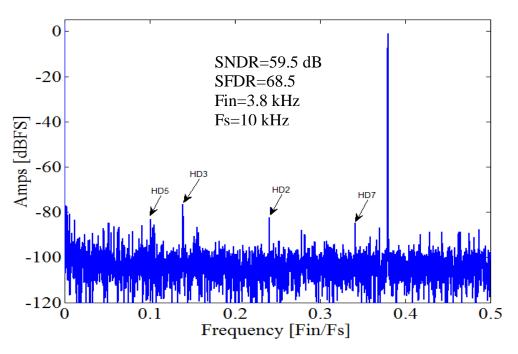

| Fig. 3.17 Measured ADC output spectrum for 3.8 kHz sinewave input with error/<br>canceling network on.                                                        |      |

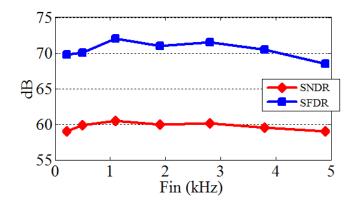

| Fig. 3.18 Measured ADC dynamic performance (SNDR/SFDR) versus input frequency                                                                                 | 42   |

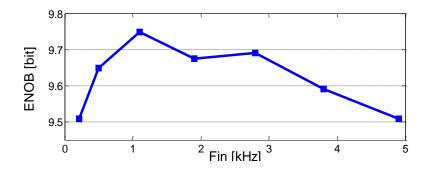

| Fig. 3.19 Measured ENOB of the ADC versus input frequency.                                                                                                    | 42   |

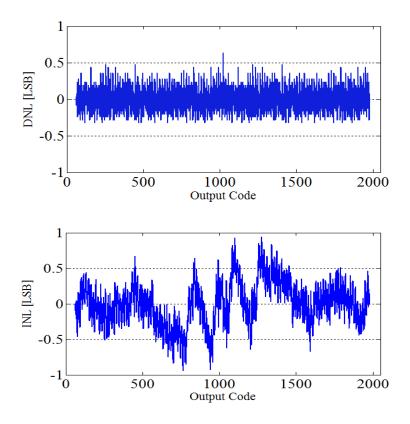

| Fig. 3.20 Measured DNL and INL.                                                                                                                               | 43   |

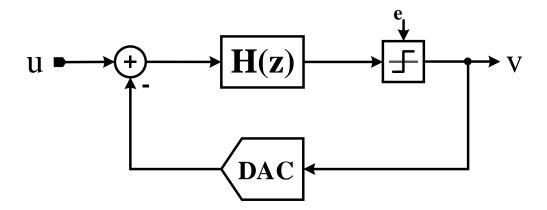

| Fig. 4.1 Block diagram of delta-sigma ADC.                                                                                                                    | 48   |

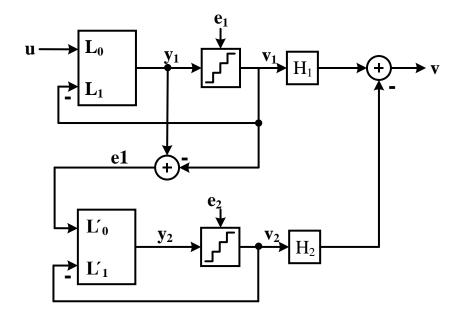

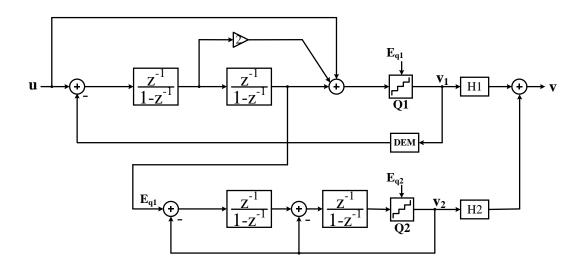

| Fig. 4.2 Block diagram of two-stage MASH delta-sigma ADC                                                                                                      | 49   |

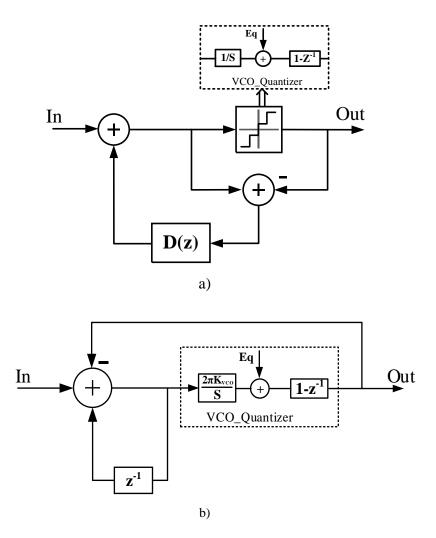

| Fig. 4.3 Proposed noise-coupled VCO-based quantizer b) Simplified structure for $D=z^{-1}$ .                                                                  |      |

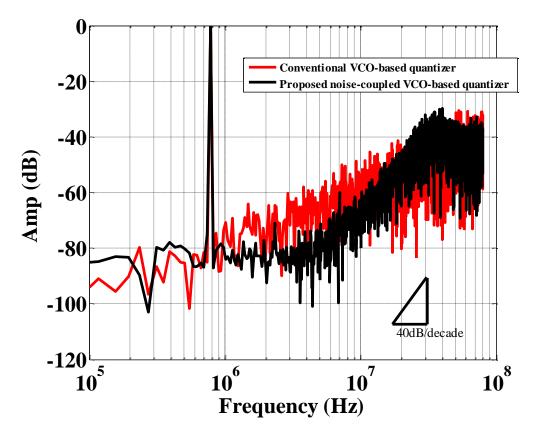

| Fig. 4.4 Conventional VCO-based quantizer and the proposed noise-coupled VC based quantizer output spectrum comparison.                                       |      |

| Fig. 4.5 Block diagram of 2-2 MASH $\Delta\Sigma$ ADC                                                                                                         | 54   |

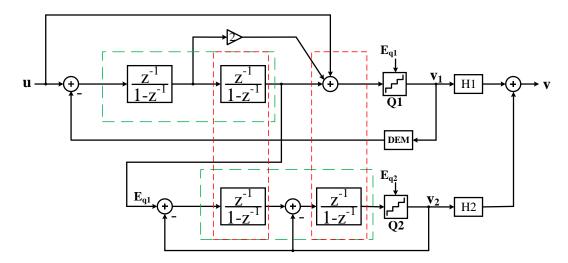

| Fig. 4.6 Block diagram of 2-2 MASH $\Delta\Sigma$ ADC with possible OPAMP sharing methods.                                                                    | 55   |

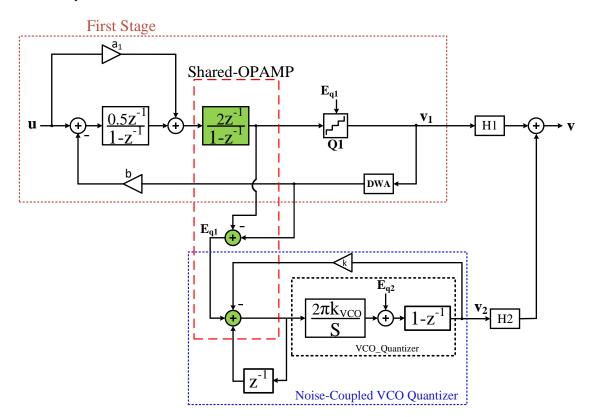

| Fig. 4.7 Block diagram of 2-2 MASH $\Delta\Sigma$ ADC with noise-coupled VCO-based quantizer and OPAMP sharing after scaling                                  | 57   |

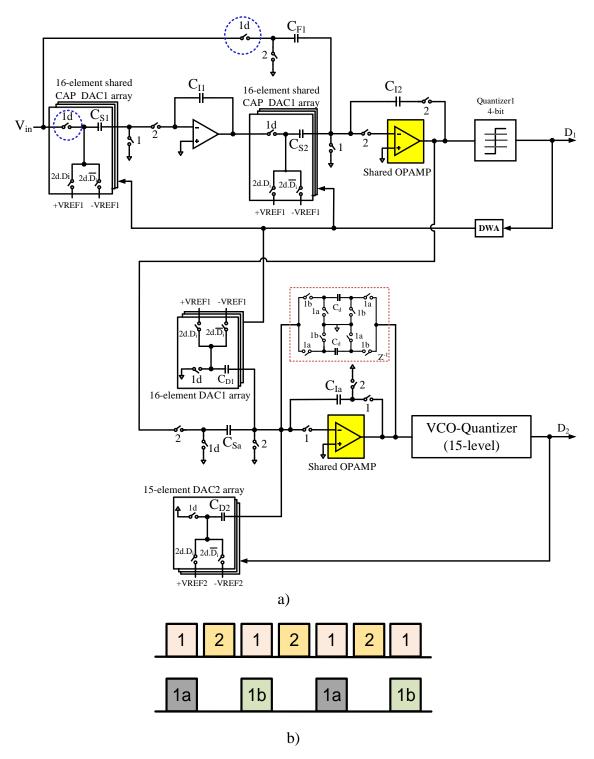

| Fig. 4.8 a) Circuit-level implementation block diagram of 2-2 MASH $\Delta\Sigma$ ADC w noise-coupled VCO-based quantizer and OPAMP sharing b) timing diagram |      |

| Fig. 4.9 Schematic of the VCO quantizer with 15-stage ring oscillator                                                                                         | 61   |

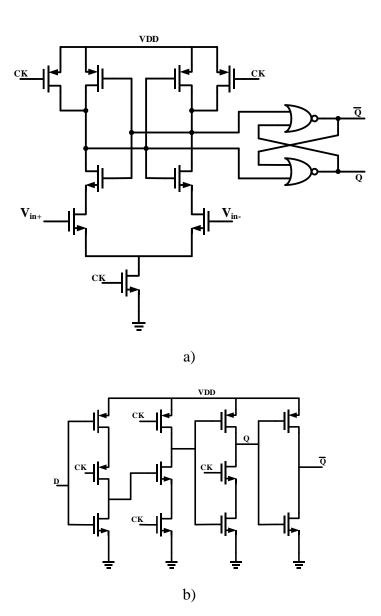

| Fig. 4.10 a) Schematic of the sense-amplifier DFF b) True single phase clock DF                                                                               | F.62 |

# LIST OF FIGURES (Continued)

| <u>Figure</u> <u>Page</u>                                                                                                       |

|---------------------------------------------------------------------------------------------------------------------------------|

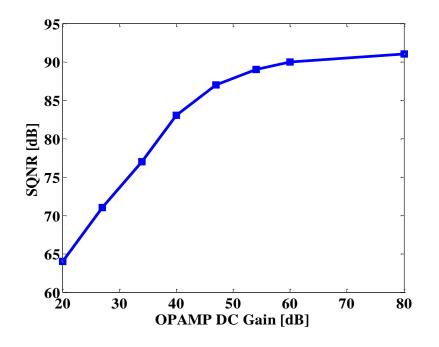

| Fig. 4.11 SQNR vs OPAMP DC gain63                                                                                               |

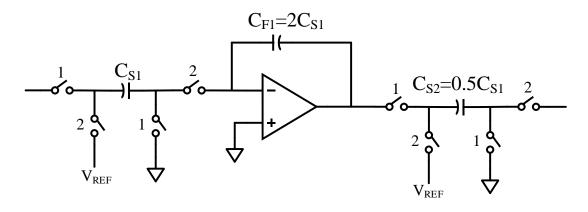

| Fig. 4.12 a) First integrator and OPAMP configuration b) Second integrator and OPAMP configuration                              |

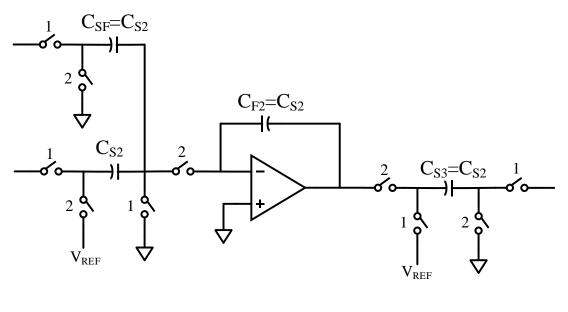

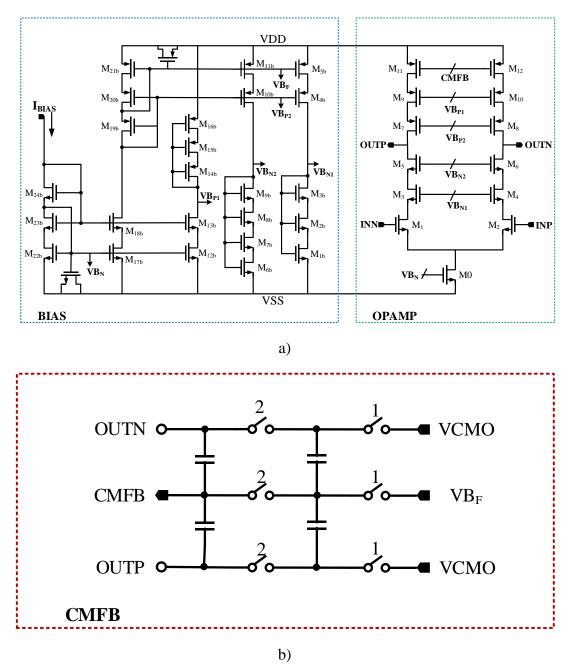

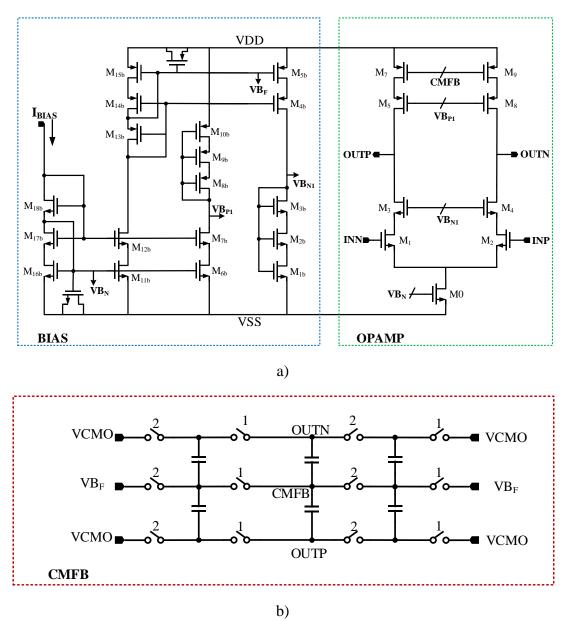

| Fig. 4.13 a) OPAMP schematic with bias circuit and b) Switched capacitor common mode feedback                                   |

| Fig. 4.14 a) OPAMP schematic with bias circuit and b) Switched capacitor common mode feedback                                   |

| Fig. 4.15 Circuit block diagram of the comparator in first stage flash quantizer69                                              |

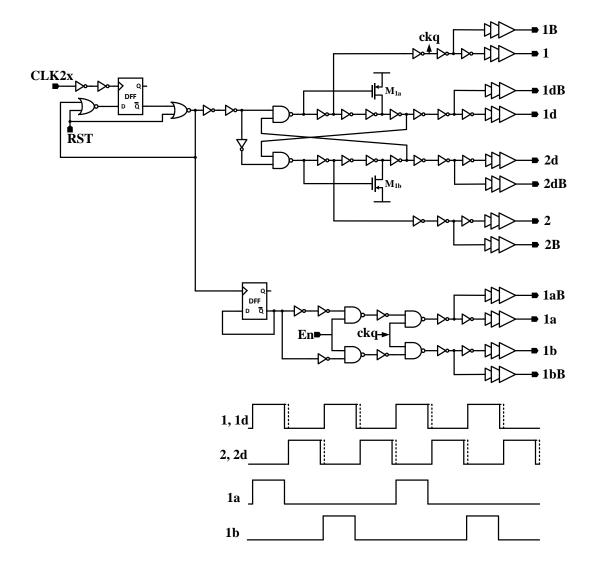

| Fig. 4.16 Clock-phases generator diagram70                                                                                      |

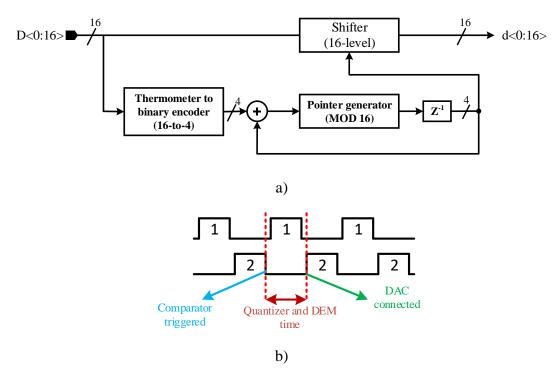

| Fig. 4.17 a) DWA block diagram, b) timing diagram of DWA72                                                                      |

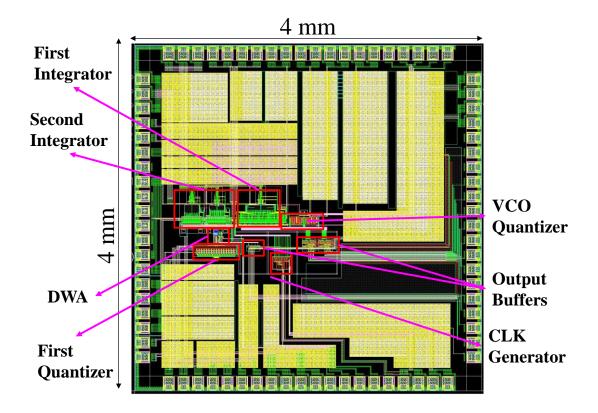

| Fig. 4.18 Chip Layout73                                                                                                         |

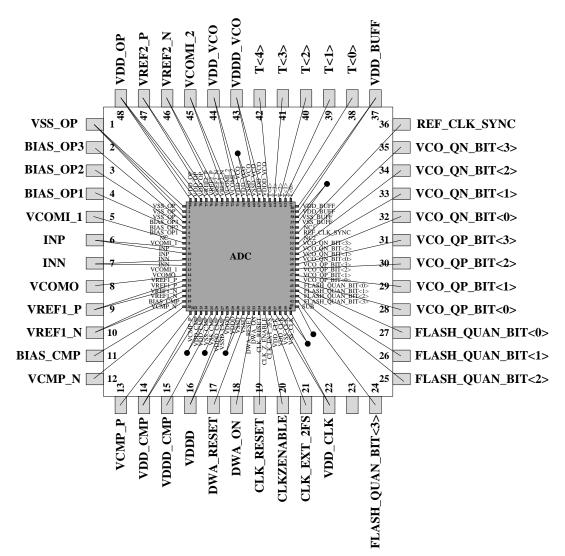

| Fig. 4.19 Chip package and PIN connections74                                                                                    |

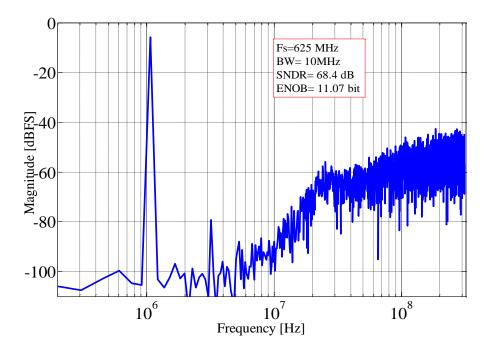

| Fig. 4.20 Output power spectrum density75                                                                                       |

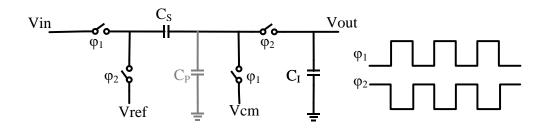

| Fig. 5.1 Passive switched capacitor integrator80                                                                                |

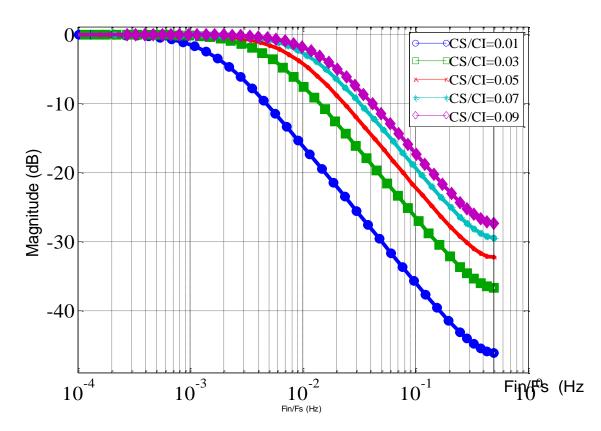

| Fig. 5.2 Passive switched capacitor integrator frequency response for different Cs/C <sub>1</sub> value                         |

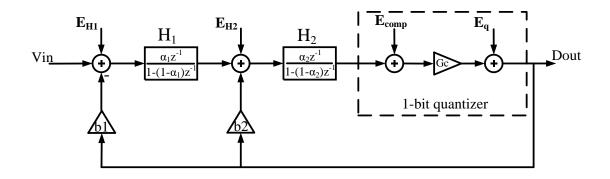

| Fig. 5.3 Passive 2 <sup>nd</sup> order delta-sigma ADC with single-bit quantizer82                                              |

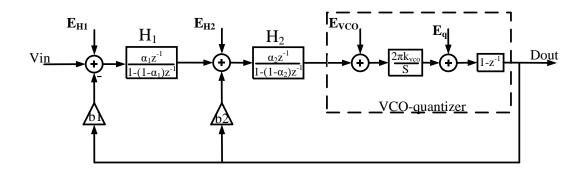

| Fig. 5.4 Proposed passive $3^{rd}$ order $\Delta\Sigma$ ADC with VCO-based quantizer                                            |

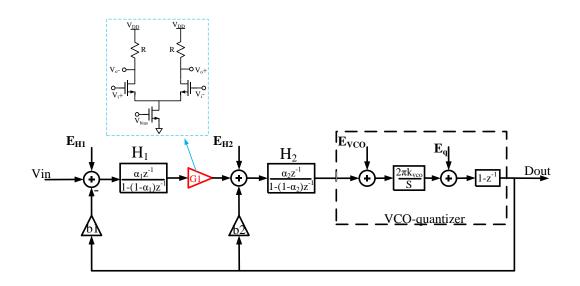

| Fig. 5.5 Proposed passive $3^{rd}$ order $\Delta\Sigma$ ADC with VCO-based quantizer and gain stage between passive integrators |

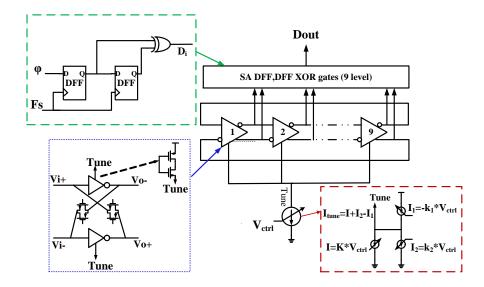

| Fig. 5.6 The VCO quantizer circuit schematic with 9-level ring oscillator and the control circuit                               |

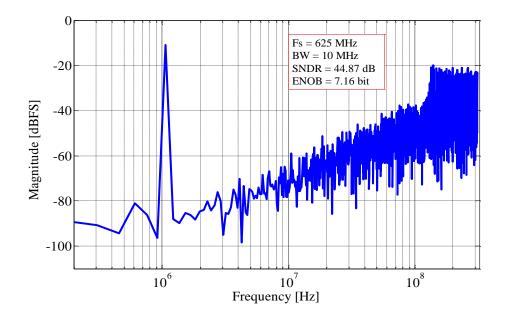

| Fig. 5.7 Simulated power spectral density of the second order passive delta-sigma ADC with single-bit quantizer                 |

# LIST OF FIGURES (Continued)

| Figure                                                                                                                                          | <u>Page</u> |

|-------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

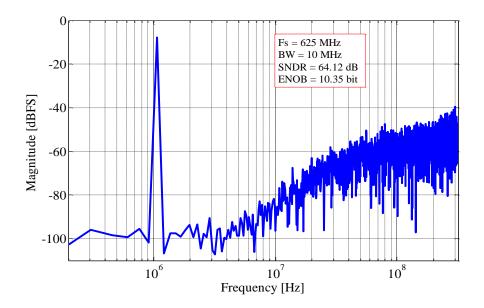

| Fig. 5.8 Simulated power spectral density of the proposed passive delta-sigma A with VCO quantizer.                                             |             |

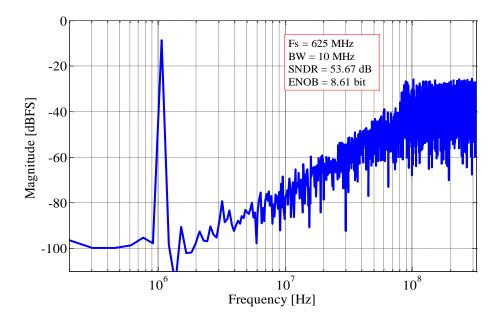

| Fig. 5.9 Simulated power spectral density of the second order passive delta-sigm ADC with added gain stage of $G_1=4$ .                         |             |

| Fig. 5.10 Simulated power spectral density of the proposed passive delta-sigma $A$ with VCO quantizer and added gain stage of G <sub>1</sub> =4 |             |

### **1.1 Motivation**

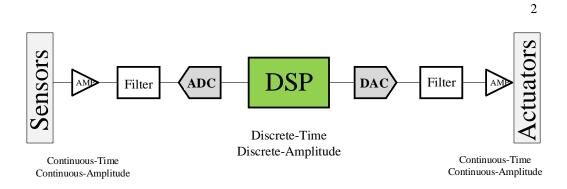

Data converters are bridges between the real world signals and the digital signal processing DSP units. All real word signals are continuous-time continuous-amplitude signals, and they have to be converted to digital domain to be processed by DSP block. Analog-to-digital converter ADC is a block which is used for this purpose. At the end, the digital signal will be converted to analog through digital-to-analog converter DAC to provide the output signal for actuators. Figure 1.1 shows system-level block diagram of general digital-signal processing and its interface between real world signals.

Analog-to-digital converter (ADCs) are essential function to take advantages of digital processing. There are different type of ADCs and they can be categorized as Nyquist-rate and oversampled ADCs [1]. Each of these categories can be implemented in different architectures depending on the application and required specification. They can be very low–bandwidth to very high-bandwidth, low resolution to high resolution for biomedical applications, audio-signal processing, video-signal processing, communication and so on. The power efficiency is a key parameter in recent ADCs, because of increasing demand of portable application to electronic devices.

Biomedical application requires a low-bandwidth, medium resolution but ultralow power ADC while wireless communications require medium-to-high resolution and very high-speed ADCs. The power efficiency is important for these applications because they are mostly portable devices and for long-time battery life they have to be power efficient.

Fig. 1.1 Interface between real world signal and digital signal processing.

In this dissertation, ADCs in both Nyquist and oversampled analog-to-digital converters are designed and analyzed. An improvement in power efficiency is presented in both.

### **1.2 Contributions**

- A switching technique is proposed for successive-approximation register (SAR) analog-to-digital converter. This scheme reduces the switching energy of the ADC.

- A power efficient SAR ADC is proposed and implemented based on the switching scheme. It can cover two-times input range of the reference voltage.

- A noise-coupled VCO-based quantizer is proposed to improve the order of noise-shaping in VCO-based quantizer.

- A 2-2 Multi-stAge noise-SHaping MASH, delta-sigma ADC is designed and implemented based on the noise-coupled VCO-based quantizer.

- To reduce the power dissipation an OPAMP sharing technique is used between the stages of 2-2 MASH.

A passive delta-sigma ADC is designed and proposed with VCO-based quantizer.

#### **1.3 Organization of Dissertation**

Chapter 2 reveiws the Nyquist rate and oversampling ADCs architecture and the required specification for different applications. It focuses on the SAR architecture in Nyquist-rate and discrete-time delta-sigma in oversampling ADC, the two structures of the proposed ADCs are covered in the next Capters.

Chapter 3 describes and presents the proposed SAR ADC. It covers the analysis and circuit design procedure and requirement for the proposed SAR ADC. It presents the simulation and measurement results. It is an asynchronous SAR ADC with 11-bit resolution, 5KHz bandwidth and 250 nW power dissipation. Most of the material in this chapter is published in:

M. Sadollahi, K. Hamashita, K. Sobue and G. C. Temes, "An 11-Bit 250-nW 10kS/s SAR ADC With Doubled Input Range for Biomedical Applications," in *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 65, no. 1, pp. 61-73, Jan. 2018.

In Chater 4, a noise-coupled VCO-based quantizer is presented and a 2-2 MASH delta-sigma ADC is proposed based on that. OPAMP sharing techniques is used between the MASH satges for even more power efficency. The architecture is analyzed and the required building blocks are designed and implemented. It covers the result and disscusion of the ADC. Some part of this is presented at:

M. Sadollahi and G. Temes, "Two-stage  $\Delta\Sigma$  ADC with noise-coupled VCO-based quantizer," 2015 IEEE International Symposium on Circuits and Systems (ISCAS), Lisbon, 2015, pp. 305-308.

Chapter 5 disscusses the passive delta-sigma ADC and presents a passive deltasigma ADC with VCO-based quantizer. it compares the proposed structure with conventional passive delta-sigma ADC. It provides the simulation results. Some part of this chater presented at:

M. Sadollahi and G. C. Temes, "Passive 3<sup>rd</sup> order delta-sigma ADC with VCObased quantizer," 2017 IEEE 60th International Midwest Symposium on Circuits and Systems (MWSCAS), Boston, MA, 2017, pp. 743-746.

Finally, Chapter 6 summerizes the contribution of this research and concludes the dissertation.

# CHAPTER 2. NYQUIST-RATE AND OVERSAMPLING ADCS

Analog to digital converters ADCs are key building blocks to electronic systems. They are the part of the front-end in radio-frequency RF receivers, sensor circuits and sensor networks, audio and video systems, medical devices and instruments and etc.

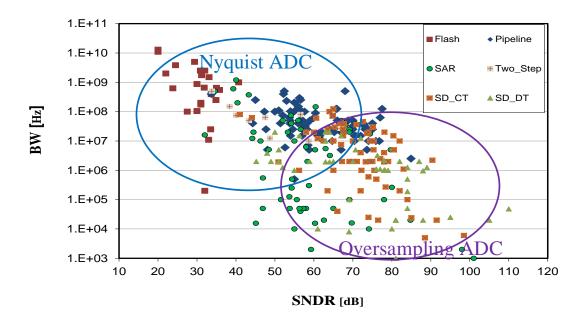

There are different architectures to implement an ADC depending on the required resolution and bandwidth. Fiquire 2.1 illustrates the state-of-the-art ADCs with different architectures based on achieved resolution and bandwidth [12]. The ADCs which process and quantize signals at, or slightly above the Nyquist rate are referred as Nyquist rate ADCs. This includes architectures such as flash, folding, two-step, pipeline, or succesive-approximation-register (SAR). This category is mostly low-to-medium resolution and medeium-to-high bandwidth.

The other category is oversampled ADCs, which are delta-sigma modulators. They can achieve very high resolution with employing a low resolution quantizer. The sampling rate at this type of ADC is much higher than the bandwdith, and it can shape the in-band noise and achieve high accuracy by oversampling. Delta-sigma modulator can be implemented in discrete-time or continuous-time structure, where each of them has pros and cons. Recently many techniques have been presented to improve the performance of delata-sigma ADC, including VCO-based quantizer, time domain and etc.

This chapter disscuses and reviewes Nyquist-rate ADC, specifically the SAR architecture, and oversampling ADC, delta-sigma modulator, to provide enough background for next chapters.

Fig. 2.1 Bandwidth vs resolution for different ADC architectures.

#### 2.1 Nyquist-Rate ADCs

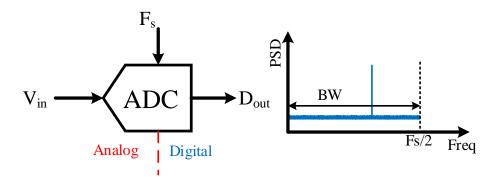

Figure 2.2 shows the general block diagram and power spectrum of Nyquist-rate ADC. Those are suitable for high-speed but low-medium resolution application. There are different Nyquist-rate ADC architectures. The simplest architecture is flash quantizer, which consists of comparators and thermometer-to-binary decoder. The other architecture is a pipeline, which consists of several stages working together. Another architecture which got attention again is successive-approximation register SAR. SAR ADC is the most suitable architecture for low power applications. Biomedical devices is one of the areas where power consumption is very restricted. Specifically for body implanted devices, the long-time battery life, and the power dissipation should be very low.

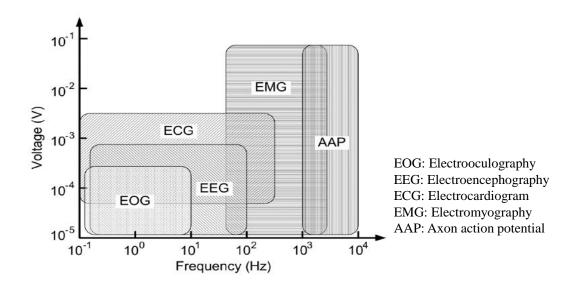

Figure 2.3 shows different biomedical signals specifications [11]. Those signals frequency range is from DC to few kHz and their magnitude range is from  $\mu V$  to mV. The required ADC's specifications in these applications are 8-12 bit resolution, few kHz bandwidth and  $\mu$ W-nW power dissipation.

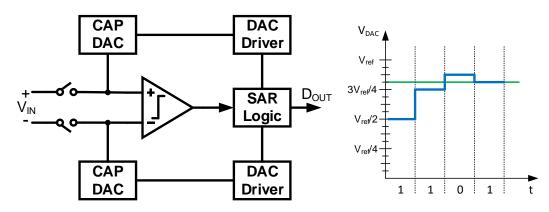

Fig. 2.2 Nyquist-rate ADC's block diagram and power Spectrum density.

SAR ADC consists of a comparator, DAC and digital timing block as shown in Fig. 2.4. Switching energy in capacitive DAC, comparator power and digital power are the three power dissipation parts. To achieve ultra-low power, all of these three blocks should be designed for ultra-low power.

Monotonic switching scheme [15],  $V_{cm}$ -based switching scheme [19] and merged-capacitive switching scheme [20] for capacitive DAC are the methods to reduce the switching energy in DAC comparing to conventional switching scheme in SAR ADC.

Fig. 2.3 Different biomedical signals specifications.

Fig. 2.4 SAR ADC block diagram.

Single-ended implementation is another way to save power in biomedical application, since it reduces total capacitance size. However the mentioned switching schemes are differential and cannot be implemented in single-ended structure. Also if some can use smaller reference voltage to cover same input signal range in SAR ADC, it can save even more power, based on Eq (2.1)

$$E_{sw} = \frac{1}{2} C_{tot} V_{ref}^2$$

(2.1)

In chapter 3, we present an ultra-low power SAR ADC for biomedical applications.

## 2.2 Oversampling ADCs

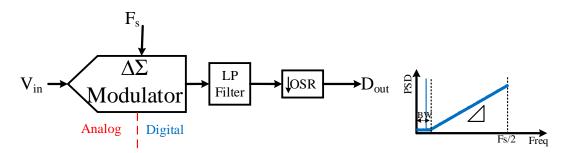

Figure 2.5 shows the general block diagram and power spectrum of oversampling ADC. Since the quantization noise are shaped, oversampled and then filtered-out, this architecture is suitable for high-resolution applications.

Fig. 2.5 Oversampling ADC block diagram and power spectrum density.

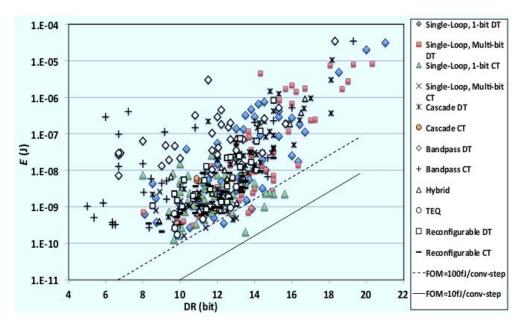

The design of the  $\Delta\Sigma$  ADC involves different design challenges and trade-offs to optimize their performances in terms of resolution, bandwidth and power consumption. These issues can be categorized as system level issues (including stability, linearity range, and clock jitter) and circuit level issues (including loop filter, quantizer, and feedback DAC and clock generation). Significant efforts have been made to increase the bandwidth and reduce the power consumption of the  $\Delta\Sigma$ ADCs. Figure 2.6 shows a survey on the  $\Delta\Sigma$  ADC in terms of energy, number of bits and architecture [2].

Fig. 2.6 State-of-the-art  $\Delta\Sigma$  ADC's energy plot vs. DR [2].

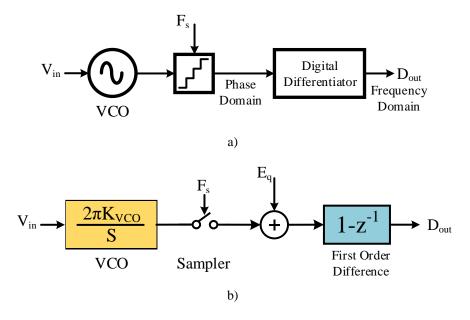

Fig. 2.7 a) Block diagram and b) behavioral model of the VCO-based quantizer.

One way to improve the SNDR in  $\Delta\Sigma$  modulator is to increase the loop-filter order. Higher loop-filter order in single-loop can cause stability issue. A solution for this issue is cascading of low-order modulators to achieve high-order loop filter which is known as MASH architecture. Every increase in loop-filter order requires additional OPAMP, which means more power dissipation. Also each stage would require its own quantizer which adds even more power consumption.

Recently the voltage controlled oscillator (VCO)-based ADCs have emerged as an attractive solution due to their highly digital circuit architecture, inherent noise shaping characteristic, as well as anti-aliasing property. Fig. 2.7 shows the block diagram and behavioral model of the VCO-based quantizer [51]. This quantizer can provide first order of noise-shaping besides the quantizing the input signal. The signal transfer function and noise-transfer function is:

$$STF = \frac{D_{out}}{V_{in}} = \frac{2NK_{VCO}z^{-1}}{F_s}$$

$$NTF = 1 - z^{-1}$$

(2.2)

Where N is the number of levels,  $K_{VCO}$  is the oscillator gain and  $F_s$  is the sampling frequency [52]. However, the nonlinear behavior of the VCO, voltage-to-frequency characteristic has severe limitation on the performance of the VCO-based ADC.

In chapter 4, we will present a noise-coupled VCO-based quantizer that acheives second order of noise-shaping. To enhance the dynamic range, the proposed noise-coupled VCO-quantizer is employed at second stage of 2-2 MASH architecture. To improve the power efficiency, first and second stage shares the OPAMP. The details of the design and result will be covered as well.

# CHAPTER 3. AN 11-BIT 250-nW 10-kS/s SAR ADC WITH DOUBLED INPUT RANGE for BIOMEDICAL APPLICATIONS

#### Abstract

This chapter presents a low power, area efficient 11-bit single-ended successiveapproximation-register (SAR) analog-to-digital converter (ADC) targeted for biomedical applications. The design features an energy-efficient switching technique with an error cancelling capacitor network. The input range is twice the reference voltage. The ADC's loading of the previous stage is reduced by using a single-ended structure, and by eliminating the largest capacitor in the array. The common mode voltage of the input signal can be used as reference voltage. All building blocks were designed in subthreshold for power efficiency, with an asynchronous self-controlled SAR logic. The ADC was fabricated in 0.18  $\mu$ m CMOS 2P4M process. The measured peak SNDR was 60.5 dB, the SFDR was 72 dB, the DNL +0.6/-0.37 LSB and the INL +0.94/-0.89 LSB. The total power consumption was 250 nW from 0.75V supply voltage [42, 43].

### **3.1 Introduction**

Biomedical wearable sensors or implanted devices, such as defibrillators, retinal prosthesis and pacemakers, require ultra-low power consumption since their longtime operation is restricted by battery life [3-9]. The interface of such biomedical devices consists of several blocks. The analog-to-digital converter ADC is a key block in the interface, and ultra-low power consumption is mandatory for longer operation. Also, it is necessary to minimize the area of the ADC for such

applications. In addition, the loading of the preceding stage, which usually is a sensing amplifier, is another key parameter to consider in the design of the ADC [3, 7, and 8, 44]. Thus, in ADC design low power, small area and small loading effect are the key parameters [10, 11].

Successive approximation register SAR ADCs have recently gained renewed attention because of their low power, simple structure and minimal analog circuitry [12, 65]. In advanced process it is possible to achieve very good performance with SAR ADC [13]. Biomedical signals are usually slow (DC to a few kHz) [14], and for low speed applications SAR ADCs are the best candidates to achieve low power consumption. The power dissipation in SAR ADC consists of the switching power of the capacitive DAC network, comparator power (analog) and SAR control logic power (digital). To achieve ultra-low power operation, it is necessary to reduce the power consumption of all of these three main blocks.

The switching power of the capacitive DAC (digital-to-analog converter) in a SAR ADC is related to the switching activity, capacitor size and reference voltage  $V_{ref.}$  There are many research papers on how to reduce this switching power [15-22]. Monotonic or set-and-down switching [15] has been presented recently to reduce the amount of switching activity. It allows up to 81% energy saving comparing to conventional switching scheme. V<sub>cm</sub>-based switching [22] has been proposed to reduce the effective voltage range of charging and discharging the capacitive DAC, and thus save switching power. This scheme saves up to 87% switching power compared to the conventional switching scheme. Also in [23] a bidirectional switching technique is presented. These schemes use differential structures, and they require two reference voltages (+/-VFS/2) or (0, VFS), where VFS is the full-scale input range. Extra reference voltage generation needs added power. Also, the loading effect of these structures to previous stage is twice that of the single-ended capacitor DAC. Thus, a single-ended structure is preferable for biomedical applications to reduce the area, power consumption, loading effect, and also to avoid the need for a common-mode feedback circuit [24]. However, the trade-off is in the design complexity for comparator and common-mode variation effects. An estimation based noise reduction presented in [26] to relax the comparator.

Advanced CMOS processes benefit from smaller feature size, lower threshold voltage and higher bandwidth, but they have higher device leakage current [9]. Therefore besides accommodating a small supply voltage, we have to minimize the leakage power to achieve best power efficiency. Since the signals in biomedical applications are slow, larger feature size processes with lower leakage current can be used, if one can optimize the design for smaller power supply and minimum area.

In this paper, a single-ended SAR ADC with a doubled (0 -  $2V_{ref}$ ) input range and an error-and-offset canceling capacitor network is described. In this scheme, first the most significant bit (MSB) is detected directly after sampling without any switching activity. This saves 50% of total capacitance size, and thus of the switching energy. Next, a one-bit DAC is used to choose the comparator's reference voltage V<sub>ref</sub> as 0 or V<sub>FS</sub>/2 depending on the MSB's value. The capacitors are charged from a voltage source V<sub>ref</sub> = V<sub>FS</sub>/2 which is half of the reference voltage of the conventional singleended SAR ADC, and therefore the switching power is reduced by a factor over 4.

The proposed switching scheme gives an 87.5% reduction in switching power loss compared to the conventional single-ended counterpart SAR ADC. Also, this scheme requires  $V_{FS}/2$  as the reference voltage. This is the common-mode level of the previous stage's output. Therefore the circuit does not require a dedicated reference voltage generator; the common-mode voltage which is generated in the preceding blocks can be used as reference voltage for this ADC. A single-ended split capacitor DAC with a bridging capacitor is used to allow a small total capacitance. This leads to smaller area and loading effect.

This paper also proposes a novel comparator. It is designed to operate in the subthreshold region to have very low power consumption. An adjustable calibration capacitor array is used to cancel charge error caused by parasitic capacitors, and also the comparator's offset variation when switching comparator's reference voltage

between 0 and  $V_{ref}$ . The power supply of the ADC is 0.75V and the process is 0.18  $\mu$ m CMOS, which allows a significant reduction in the leakage current and power needed in the logic circuits. Also, high threshold-voltage devices are used in the logic circuitry to reduce the leakage current further.

### **3.2 Proposed SAR ADC Architecture**

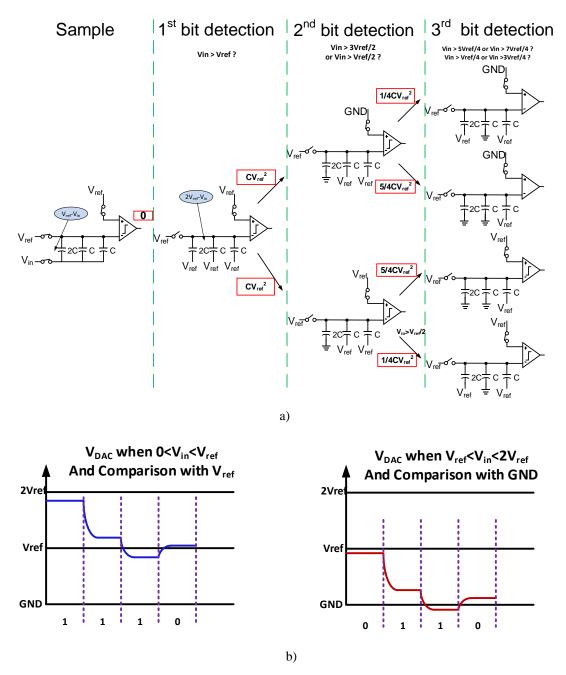

Figure 3.1 shows the architecture of the proposed 11-bit SAR ADC with  $2V_{ref}$  input range. It consists of a single-ended switched capacitor network DAC, a low-power comparator, the asynchronous SAR control logic, comparator reference control, and parasitic capacitor error/comparator offset cancellation network. The DAC uses a 10-bit split scheme with a bridge capacitor. Since the MSB determination does not require DAC switching, a 10-bit DAC can be used for an 11-bit ADC. The DAC is divided into two 5-bit networks (MSB DAC and LSB DAC) to optimize the area and power. The comparator reference control connects the non-inverting input of the comparator to  $V_{ref}$  or GND, depending on the MSB value. The comparator uses a preamplifier and latch to meet the noise and accuracy requirements. The SAR control logic controls the DAC switches, based on the comparator decisions and control signals [42, 43].

The operation of the ADC is as follow: As shown in Fig. 3.1 there are three operation phases; sampling phase (samples the input signal), conversion phase (converts the sampled input signal to digital form) and reset phase (resets the ADC to prepare for the next sample). During the sampling phase, the bottom plates of all capacitors are connected to the input signal, and all top plates are connected to the reference voltage (V<sub>ref</sub>). Therefore, the signal on all capacitors will be  $V_{cap} = V_{ref} - V_{in}$ . At the same time, the noninverting input of the comparator is connected to V<sub>ref</sub>, and the parasitic error/comparator offset cancelling capacitor C<sub>c</sub> is connected between  $2V_{ref}=V_{DD}$  and V<sub>ref</sub>.

Fig. 3.1 The proposed SAR ADC architecture and timing signals.

When the sampling clock transitions from '1' to '0', the bottom plates of all capacitors will be disconnected from the input signal, and connected to  $V_{ref}$ , while the top plates of the capacitors will be disconnected from  $V_{ref}$ . Therefore the voltage across the capacitors will move up by  $V_{ref}$ , and the voltage at nodes *A* and *B* will be  $V_{A, B} = 2V_{ref} - V_{in}$ . This step does not take charge from reference voltage source to

charge the capacitors, and hence no energy is consumed at this step, except for the very small amount of energy that is taken to charge the parasitic capacitors at node A (C<sub>ph</sub>) and B (C<sub>pl</sub>).

At this time, the most-significant-bit (MSB) is detected by comparing the voltage at node A (inverting input of the comparator) with V<sub>ref</sub> (noninverting input of the comparator). The MSB detection is performed without any switching activity and energy consumption unlike in a traditional SAR ADC. The detected MSB bit will be stored at SAR logic circuit, and sets the reference voltage of the 1-bit DAC to be V<sub>ref</sub> or GND.

Next, depending on the MSB value, there will be two paths to detect the rest of bits.

If MSB = 0, so that the input signal is smaller than  $V_{ref}$  and  $0 < V_{in} < V_{ref}$ , the positive input of the comparator will stay connected to  $V_{ref}$ , and the rest of the comparisons will continue using  $V_{ref}$  as reference voltage. To detect the MSB-1 bit, the MSB-1 capacitor switches from  $V_{ref}$  to GND. Now the voltage at node *A* will be  $V_A = 2V_{ref} - V_{in} - 1/2V_{ref}$ . This voltage will be compared to  $V_{ref}$ , and based on the result MSB-1 will be detected and stored in the SAR logic circuit. This procedure will continue until the Least-Significant-Bit (LSB) is detected.

If MSB = 1, so the input signal is greater than  $V_{ref}$  and  $V_{ref} < V_{in} < 2V_{ref}$ , the noninverting input of the comparator will be switched from  $V_{ref}$  to GND, and rest of the comparisons will continue using GND as reference voltage. To detect the MSB-1 bit, the MSB-1 capacitor switches from  $V_{ref}$  to GND, and the voltage at node *A* will be  $V_A = 2V_{ref} - V_{in} - 1/2V_{ref}$ . This voltage will be compared to GND, and based on that, MSB-1 will be detected and stored in the SAR logic circuit. This procedure will again continue until the least-significant-bit is detected. The flow chart of the proposed SAR ADC is shown in Fig. 3.2. The voltage of node A can vary below GND. Therefore, a PMOS switch was used to connect the C<sub>c</sub> to node A (MSB switch) to avoid any possibility of the latch-up.

Fig. 3.2 Flow chart of the proposed SAR ADC.

Figure 3.3 shows an example of the operation for a 3-bit ADC, and the possible two cases that can occur for the voltage waveform at the DAC's output signal (inverting input of the comparator).

As shown in Fig. 3.3, when MSB = 0, the voltage at node *A* (inverting input of the comparator) goes to V<sub>ref</sub> eventually, and since the initial voltage at this node was V<sub>ref</sub> as well, therefore the charge injected by the parasitic capacitor (C<sub>ph</sub>) will not introduce error at the final digitized output code. But when MSB = 1, the voltage at node *A* goes to GND eventually, and the parasitic capacitor will introduce error, since its initial voltage was V<sub>ref</sub> and the final voltage is GND. The charge injected by this parasitic capacitor is C<sub>ph</sub>V<sub>ref</sub>/C<sub>tot</sub>, and resulting error will be:

$$\Delta V_{A-err} = \frac{C_{ph}V_{ref} - C_{ph}V^+}{C_{tot}}$$

(3.1)

Here  $\Delta V_{A-err}$  is the voltage error at node *A*, C<sub>ph</sub> is the parasitic capacitance at node *A*, V<sup>+</sup> is the voltage at the noninverting input of the comparator, and C<sub>tot</sub> is total capacitance of the main DAC. Figure 3.4 shows the effect of this error for 50fF and 100 fF parasitic capacitance where the LSB capacitor size is C=100 fF. It causes dead band or undetected range of input signal around the midpoint transition. To cancel this voltage error, caused by switching the reference between V<sub>ref</sub> and GND, a parasitic error canceling network is introduced. The parasitic capacitor array C<sub>e</sub> containing series and parallel capacitors with unit size of 2.75 fF is used to provide a matching charge to cancel the voltage error caused by the parasitic capacitor. Capacitor C<sub>c</sub> is charged initially to V<sub>ref</sub> in the sampling phase, and if MSB = 1 it will be connected to node *A* and discharged to this node. This capacitor network C<sub>c</sub> also is used to cancel the error due to the comparator's offset difference introduced by reference voltage switching to GND or V<sub>ref</sub> at the noninverting input of the comparator. This will be explained in the next Sections.

Fig. 3.3 a) Switching procedure and switching energy for 3-bit example of the proposed structure, b) Voltage waveforms at non-inverting node of comparator.

Fig. 3.4 Output code for different C<sub>ph</sub> around midpoint transition.

Comparison of the proposed SAR ADC with a single-ended conventional SAR ADC shows that the total capacitance is reduced to half, since finding the MSB does not require a capacitor, and the reference voltage is reduced to half for the same input range and therefore the switching energy is reduced. The total switching energy for the proposed SAR ADC is 12.5% of that of the conventional single-ended SAR ADC. Comparing it to the monotonic switching [15] and Vcm-based switching [16], the proposed SAR ADC uses similar technique to detect the MSB without capacitor switching and thus to eliminate the MSB capacitor, but monotonic and Vcm-based switching require differential implementation, while the proposed architecture is implementable by a single-ended structure which saves power and chip area. Therefore, the total capacitor size is half of the monotonic and V<sub>cm</sub>-based switching, and also the reference voltage is half of the reference voltage for same input range. The switching energy for the different structures was calculated and simulated for the same resolution, same binary weighted capacitor DAC and same input range. The average energy formulas for different switching schemes are given below

$$E_{avg,Conv} = \sum_{i=1}^{n} 2^{n+1-2i} \left( 2^{i} - 1 \right) C V_{ref}^{2}$$

(3.2)

$$E_{avg,Monotonic} = \sum_{i=1}^{n-1} 2^{n-2-i} C V_{ref}^2$$

(3.3)

Figure 3.5 plots the switching energy versus the output code for the proposed structure and for the previously reported structures.

Another important aspect is the common-mode voltage of the comparator. In the monotonic and V<sub>cm</sub>-based structures, the final voltage of the comparator's input (DAC's output) is code dependent, and varies with input signal, from GND-to-V<sub>ref</sub>. This introduces a signal dependent dynamic offset for the comparator. But in the proposed structure the final voltage of the comparator's input (DAC's output) will have one of two values: GND if  $V_{ref} < V_{in} < 2V_{ref}$  or  $V_{ref}$  if GND<  $V_{in} < V_{ref}$ . This will introduce only an MSB dependent offset difference, which will be cancelled by the error/offset canceling capacitor network C<sub>c</sub>.

Fig. 3.5 Switching energy versus output code comparison.

22

### **3.3 Circuit Realization of the Proposed SAR ADC**

This Section describes the circuit design and layout considerations of the capacitive DAC, comparator, and asynchronous SAR control logic.

### 3.3.1 Capacitive DAC

The capacitive DAC was implemented with a split architecture (MSB DAC and LSB DAC) with a bridge capacitor [27, 28], to reduce the total capacitor size and therefore the power consumption and area (Fig. 3.6). The ratio between MSB DAC (M-bit) and LSB DAC (L-bit) is determined by considering the number of unit capacitors and total area. Since there is  $1/2^{M}$  gain from LSB DAC to MSB DAC, by choosing an equal or higher value for MSB DAC, the MSB DAC dominates the total mismatch error, so we can ignore the mismatch error from the sub DAC.

Table 3.1 shows the total number of unit capacitors for different combinations of the M and L for a 10-bit DAC. In this design L=M=5 has been chosen for power and area efficiency.

Fig. 3.6 Capacitive DAC with unit bridge capacitor.

| Μ                     | 1   | 2   | 3   | 4  | 5  | 6  | 7   | 8   | 9   |

|-----------------------|-----|-----|-----|----|----|----|-----|-----|-----|

| L                     | 9   | 8   | 7   | 6  | 5  | 4  | 3   | 2   | 1   |

| No. of C <sub>u</sub> | 513 | 260 | 136 | 80 | 64 | 80 | 136 | 260 | 513 |

TABLE 3.1. TOTAL NO. OF CU FOR DIFFERENT M AND L COMBINATION

The power consumption of a capacitive DAC is directly propositional to the unit capacitor size  $C_u$  in the DAC array [31]. The smallest value of the  $C_u$  is determined by the minimum value of capacitor which satisfy the following criteria [27, 28]: 1) thermal noise power kT/C; 2) the required capacitor matching accuracy (DNL, INL); 3) design rules and parasitic capacitance of the technology. Usually the matching property is the dominant condition in finding the unit capacitance  $C_u$  for medium/ high resolution SAR ADCs [32]. The worst-case standard deviation of differential nonlinearity (DNL) and integral nonlinearity (INL) for the used capacitive DAC is calculated as follow.

#### 3.3.1.a Capacitor mismatch and static linearity, DNL/INL

To calculate the static linearity of the binary-weighted capacitor array with bridge capacitor, each of the capacitors can be considered by its nominal value and some error

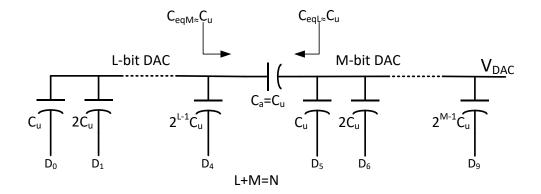

Fig. 3.7 Capacitor DAC array with bridge capacitor.

$$C_n = 2^n \left( C_u + \Delta C_u \right) \tag{3.4}$$

For capacitor mismatch with a  $\sigma_0$  standard deviation, the mean-square error will be

$$E[\Delta C_n^2] = 2^n \sigma_0^2 \tag{3.5}$$

and the ADC output with  $b_i$  digital bits will be

$$V_{out}(n) = \frac{\sum_{i=1}^{n} (C_i + \Delta C_i) b_i}{C_{tot}} V_{ref} = D_{out} V_{ref}$$

(3.6)

The DAC error and its variance can be calculated from (17)-(19) as

$$V_{err}(n) = \frac{\sum_{i=1}^{n} \Delta C_i b_i}{2^N C_u} V_{ref}$$

(3.7)

$$E[V_{err}^{2}(n)] = \frac{\sum_{i=1}^{n} 2^{n-1} \sigma_{0}^{2} b_{i}}{2^{2N} C_{u}^{2}} V_{ref}^{2}, \quad LSB = \frac{V_{ref}}{2^{N}}$$

(3.8)

For ADC we can calculate the DNL and INL by finding the maximum error of

$$DNL(n) = V_{out}(n) - V_{out}(n-1) - (LSB)$$

$$INL(n) = V_{out}(n) - V_{ideal}(n)$$

(3.9)

The worst case for nonlinearity is the transition for the MSB, (0111...1) to (1000...0). By calculating the DAC voltage from Fig. 3.7 we can get the error of this transition. The DAC voltage V<sub>DACi</sub> in Fig. 3.7 is

$$V_{DACi} = \frac{\sum_{i=1}^{M} \frac{D_{Mi}}{2^{i}} C_{Mi}}{C_{totM} + C_{eqL}} + \frac{\sum_{i=1}^{L} \frac{D_{Li}}{2^{i}} C_{Li}}{C_{totL} + C_{eqM}} \frac{C_{a}}{C_{totM} + C_{a}}$$

(3.10)

Here,  $C_{Li}$  is for the LSB DAC capacitor and  $C_{Mi}$  is for the MSB DAC capacitor. Then by calculating the DNL from (22) for the worst case and finding the variance of this error from (21) we get

$$E[DNL_{MAX}^{2}] = E\left[\left(\frac{\delta_{M}}{(2^{M}-1)C_{u}+C_{egL}}\right) - \left(\frac{\sum_{i=1}^{M-1}\delta_{M}}{(2^{M}-1)C_{u}+C_{egL}}\right) - \left(\frac{\sum_{i=1}^{L}\delta_{i}}{(2^{L}-1)C_{u}+C_{egM}}\frac{C_{a}}{(2^{M}-1)C_{u}+C_{eqL}}\right)\right)^{2}\right]$$

$$= E\left[\left(\frac{\delta_{M}}{(2^{M}C_{u})} - \left(\frac{\sum_{i=1}^{M-1}\delta_{M}}{(2^{M}C_{u})}\right) - \left(\frac{\sum_{i=1}^{L}\delta_{i}}{(2^{L}C_{u})}\frac{1}{2^{M}}\right)\right)V_{ref}^{2}\right]$$

(3.11)

By considering the standard deviation for the capacitors from (18) we can get

$$E[DNL_{MAX}^{2}] = E\left[\left(\left(\frac{2^{M-1}\sigma_{0}^{2}}{2^{2M}C_{u}^{2}}\right) + \left(\frac{(2^{M-1}-1)\sigma_{0}^{2}}{2^{2M}C_{u}^{2}}\right) + \left(\frac{(2^{L}-1)\sigma_{0}^{2}}{2^{L}C_{u}^{2}}\frac{1}{2^{2M}}\right)\right)V_{ref}^{2}\right]$$

$$= E\left[\left(\left(\frac{(2^{M}-1)\sigma_{0}^{2} \times 2^{2L}}{2^{2M}C_{u}^{2}}\right) + \left(\frac{(2^{L}-1)\sigma_{0}^{2}}{2^{2L}C_{u}^{2}}\frac{1}{2^{2M}}\right)\right)V_{ref}^{2}\right]$$

(3.12)

Therefore the standard deviation of the DNL based on capacitor mismatch will be

$$\sigma^{2}[DNL_{MAX}] = \left[ \left( 2^{M} - 1 \right) 2^{2L} + \left( 2^{L} - 1 \right) \right] \left( \frac{\sigma_{0}}{C_{u}} \right)^{2} LSB^{2}$$

$$\sigma[DNL_{MAX}] = 2^{N - \frac{M}{2}} \frac{\sigma_{0}}{C_{u}} LSB \qquad (3.13)$$

By following a similar procedure for INL we can get

$$\sigma[INL_{MAX}] = 2^{N - \frac{M}{2} - 1} \frac{\sigma_0}{C_u} LSB$$

(3.14)

And based on this DNL and INL equations the minimum capacitor value can be calculated to satisfy the required linearity.

In terms of the LSB, the results are

$$\sigma_{DNL,MAX} \approx 2^{N - \frac{M}{2}} \frac{\sigma_u}{C_u} LSB$$

(3.15)

$$\sigma_{INL,MAX} \approx 2^{N - \frac{M}{2} - 1} \frac{\sigma_u}{C_u} LSB$$

(3.16)

Here, N is the overall resolution in bits, M is the number of bits of the MSB DAC,  $C_u$  is the nominal unit capacitor and  $\sigma_u$  is the standard deviation of  $C_u$  from nominal value [33].

Metal-insulator-metal (MIM) capacitors which have small parasitic capacitors have been used to implement the capacitive DAC. In the used technology, a MIM capacitor has 1.73 fF/ $\mu$ m<sup>2</sup> density and a matching of 0.3 %. $\mu$ m. Based on the calculation and simulation results, a unit capacitor size of 90 fF has been chosen, which satisfies all matching requirements. Besides larger size, a careful layout and routing has been done to avoid nonlinearity degradation. Figure 3.8 shows the floor plan and layout of the capacitor DAC. It is divided into the main and low side capacitive DACs. Each side has 32 unit capacitors, and is surrounded by dummy unit capacitors. The bridge capacitor is located in the middle, and connects the two sides together.

Fig. 3.8 Capacitive DAC array floorplan and layout.

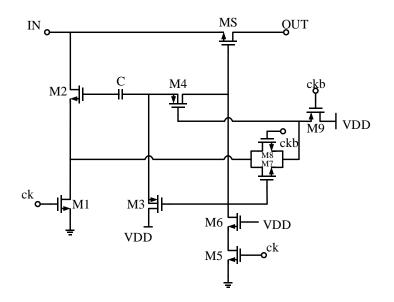

Figure 3.9 shows the schematic of the bootstrap switch, which has been used to sample input signal. It provides a linear on resistance over the full range of the input signal.

Fig. 3.9 Bootstrap switch schematic.

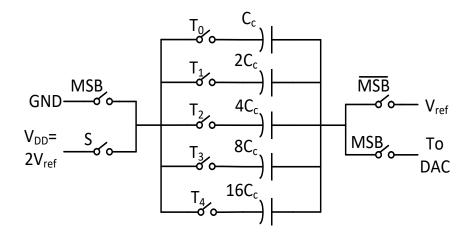

#### 3.3.1.b DAC and offset error canceling network

Figure 3.10 shows a capacitive array which has been implemented to cancel out the DAC charge error and the comparator's offset difference when switching the reference voltage between GND and  $V_{ref}$ . This array is adjustable with 5-bit (T<sub>0</sub> – T<sub>4</sub>) external control bits. The resolution of this capacitive array should be small enough to cancel the DAC error due to the parasitic capacitor at the top plate of the main-DAC and also the comparator's offset difference. A minimum capacitor size of 2.86 fF (C<sub>c</sub>) which is  $1/2^{L}$  times of C<sub>u</sub> has been used in this array, based on the calculation and simulation results. Poly-insulator-poly (PIP) capacitor which has a smaller minimum size has been used to implement this capacitor array. PIP capacitor has larger parasitic capacitance than a MIM one, but the parasitic capacitance and matching are unimportant in the error canceling network.

Fig. 3.10 DAC error and comparator offset/error canceling capacitor network.

During the sampling phase these capacitors are connected between  $V_{DD}=2V_{ref}$  and  $V_{ref}$ , since all output bits are reset during sampling phase and MSB = 0. Then during the conversion phase, if MSB = 1 the capacitor array will be connected to the DAC

output node (the comparator's non-inverting input). The best setting for T<sub>0</sub>-T<sub>4</sub> is obtained by applying different DC inputs around the switching point (Vref) and finding the output code. Therefore it is calibrated to cancel out the DAC error and comparator offset error between the two cases of  $0 < V_{in} < V_{ref}$  and  $V_{ref} < V_{in} < 2V_{ref}$ . The power needed by this array is very small, since the capacitor size is very small and it only discharges half of the time when the input is larger than  $V_{ref}$ .

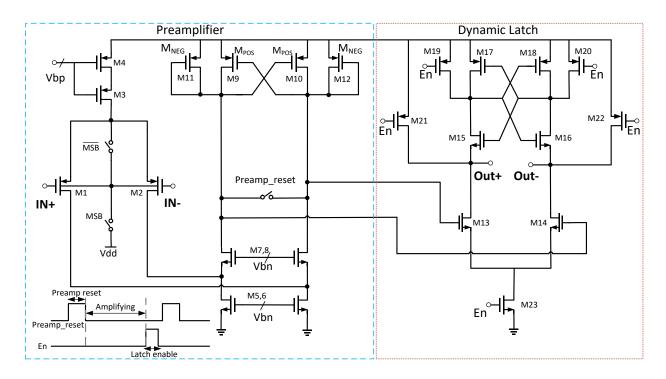

#### 3.3.2 Comparator circuit design

Figure 3.11 shows the circuit schematic of the proposed comparator, which is designed in the subthreshold region. It uses a preamplifier (preamp) and a dynamic regeneration latch [34, 35]. The operation of the comparator is divided into a preamp reset phase, amplification and latch enable phase as shown in Fig. 3.11. The control clock phases were generated by a SAR control logic, and they have a controlled duty cycle depending on the comparator's input. Thus, the total time for the 11-bit conversion (100 µsec) is automatically distributed for each bit: for large difference at comparator's input, shorter amplification time is allocated, and for smaller difference, a larger amplification time is allocated. During the preamp reset, the output nodes of the preamp are shorted together to avoid memory effect of the pervious comparison. Then the preamp starts to amplify the voltage difference between the inputs, while the regeneration latch is disabled, and its output is set to V<sub>dd</sub> by M<sub>21</sub> and M<sub>22</sub>. After amplification, the regeneration latch will be enabled to make its decision, and it provides a full-scale output digital signal, which will be stored in the SR-latch. The preamp uses folded-cascode circuitry, with  $g_m$  load to avoid the common-mode feedback circuit requirement. To get enough gain, positive feedback has been used in the load branch. The bias current of the input differential pair is 10 times of that of the load branch, which causes the input transconductance  $g_m$  to be 10 times larger than the  $g_m$  of the load branch, since  $g_m = I_d / n.V_T$  in the subthreshold region.

The DC voltage gain of the preamp is

$$Av = -\frac{g_{m_{IN}}}{g_{m_{NEG}} - g_{m_{POS}}}$$

(3.17)

Here,  $g_{mIN}$  is the transconductance of the input differential pair (M<sub>1</sub>, M<sub>2</sub>),  $g_{mNEG}$  is of M<sub>NEG</sub>'s (M<sub>11</sub>, M<sub>12</sub>), and  $g_{mPOS}$  is of M<sub>POS</sub> (M<sub>9</sub>, M<sub>10</sub>). We have (W/L)<sub>POS</sub>=(7/8)(W/L)<sub>NEG</sub> and  $g_{mPOS} = (7/8)g_{mNEG} = (1/10)g_{mIN}$ . The total DC gain is around 45 dB. In order to achieve high output impedance, the tail current and load branch devices use cascades of low-threshold (LVT) and standard-threshold (SVT) devices. This insures that both devices are in saturation. Based on the current equation (9) in subthreshold [36] we need 100 mV across the devices to be sure that they are in saturation

$$I_{D} = \mu C_{ox} \frac{W}{L} V_{T}^{2} e^{\frac{V_{gs} - Vth}{nV_{T}}} \left( 1 - e^{-\frac{Vds}{V_{T}}} \right)$$

(3.18)

Here,  $V_T$  is the thermal voltage and *n* is the subthreshold slope factor (~1.5). Since the reference voltage of the comparator switches between GND and  $V_{ref}$ , in order to make sure all transistors are operating in saturation in all process corners, the bulk of input pair is switched between  $V_{dd}$  and the source of input pair, based on MSB values. When MSB = 0 and comparison is with  $V_{ref}$ , the bulks of the input pair (M<sub>1</sub>, M<sub>2</sub>) connect to their source and when MSB = 1 and comparison is with GND, the input pair's bulk connect to  $V_{dd}$ .

This switching minimizes the voltage variation at the source of the input pair by controlling the bulk voltage and therefore the threshold voltage of the input devices. Larger threshold voltage occurs when reference voltage is GND, and smaller when the reference voltage is  $V_{ref}$ . This switching may introduce some offset, which can be cancelled by the charge error and offset cancelling capacitor network. The total input referred offset of the comparator is

$$Vos_{in-tot} = Vos_{preAmp} + \frac{1}{Gain_{preAmp}} Vos_{latch}$$

(3.20)

Since the preamp has a large gain, we can ignore the offset caused by the latch, also the input referred offset of the load branch of the preamplifier (M<sub>7-12</sub>) would be negligible, since the input pair's bias current and therefore its  $g_m$  is 10 times larger than load branch's  $g_m (g_m = \frac{I_D}{nN_T})$ . However the bias current of the M<sub>5, 6</sub> is in the similar range of the input pair's bias current. Therefore, we can consider only the preamp's input pair M<sub>1, 2</sub> and M<sub>5, 6</sub> as the main source of the offset voltage. Based on the I<sub>D</sub> equation in subthreshold region (9), and following the procedure described in [37], the input offset voltage for M<sub>1, 2</sub> can be estimated from (similar approach can be applied for M<sub>5, 6</sub>)

$$\begin{cases} Vos_{in} = V_{GS1} - V_{GS2} \\ V_{GS} = V_{ih} + nV_T \ln \left[ \frac{I_D}{\mu C_{ox} \frac{W}{L} V_T^2} \right] \end{cases}$$

(3.21)

By considering the mismatches in the threshold voltage  $V_{th}$ , physical size W/L and load R<sub>load</sub>, this represent the dynamic effect of the load branch M<sub>5-12</sub>, after some algebra we can get

$$Vos_{in} = \Delta V_{ih1,2} + nV_T \left[ \frac{\Delta \left(\frac{W}{L}\right)_{1,2}}{\left(\frac{W}{L}\right)_{1,2}} + \frac{\Delta R_{load}}{R_{load}} \right]$$

(3.22)

The first term is static offset. It will be different in the two reference voltage modes, when the comparator's input is switched to GND or  $V_{ref}$  based on the MSB value. This offset difference would be canceled by the charge error and offset canceling network (background calibration). The second term is slightly input

32

dependent because of the changes it can cause in the load impedance (R<sub>load</sub> is the total impedance at the output node of the preamp,  $R_{load} = \frac{1}{g_{m11,12} - g_{m9,10}} \|g_{m7,8} r_{ds7,8} r_{ds5,6}$  and  $\Delta R_{load}$  represents its variation). But this effect is small compared to conventional comparators which operate in strong inversion [15, 38] with the input offset of

$$Vos_{in} = \Delta V_{ih1,2} + \frac{\left(V_{GS} - V_{ih}\right)_{1,2}}{2} \left[ \frac{\Delta \left(\frac{W}{L}\right)_{1,2}}{\left(\frac{W}{L}\right)_{1,2}} + \frac{\Delta R_{load}}{R_{load}} \right]$$

(3.23)

Here, instead of  $nV_T$  as in (12) we have  $\frac{1}{2}(V_{GS}-V_{th})$  and  $\frac{1}{2}(V_{GS}-V_{th}) >> nV_T$ . Also, the effect of  $\Delta R_{load}/R_{load}$  in (12) is smaller, since the total  $R_{load}$  is smaller (only  $1/g_m$ ) and distributed to four devices. Therefore the comparator offset is mostly static and it would not affect the performance of the ADC.

Fig. 3.11 Circuit schematic of the comparator with preamplifier and dynamic latch.

The input referred noise of comparator is mostly coming from the preamp [34]. The input differential pair ( $M_1$ ,  $M_2$ ) and current devices in the load branches ( $M_5$ ,  $M_6$  and  $M_{9...12}$ ) are the dominant noise sources. For operation in the subthreshold region the power spectral density PSD of devices noise is [36]

$$PSD_{\frac{1}{i_{nd}^2}} = 2kTng_m + \frac{K_f g_m^2}{fWLc_{ox}}$$

(3.24)

Here, the second term represents flicker noise. The input pair was designed large enough  $\left(\left(\frac{W}{L}\right)_{1,2} = \frac{8\mu}{0.4\mu} \times 4\right)$  to reduce the flicker noise and make it negligible [35]. The power spectral density of the input referred noise is given by

$$PSD_{\overline{Vn_{in}^{2}}} = 2kTn \frac{1}{g_{m_{IN}}} \left[ 1 + \frac{g_{m_{N}}}{g_{m_{IN}}} + \frac{g_{m_{P}}}{g_{m_{IN}}} \right]$$

(3.25)

Here  $g_{mN}$  and  $g_{mP}$  are for the top PMOS (M<sub>9</sub>...M<sub>12</sub>) and bottom NMOS (M<sub>5</sub>, M<sub>6</sub>) devices in the load branches of preamp, respectively. The input pair's transconductance  $g_{mIN}$  is 10 times larger than the load branch  $g_m$ , to reduce the input-referred noise. Also, the transfer function of preamp is second order, and its second pole is designed to be close enough to the first pole to make the transfer function sharper, which helps to reduce the total integrated in-band noise. Total in-band input-referred noise is obtained by integrating this PSD over the preamp's bandwidth. Simulated total in-band input-referred noise is around 63  $\mu$ V which is small enough compared to the LSB = 366  $\mu$ V.

The input common-voltage (CM) to the comparator can vary with different input signals [34]. The CM variation range for MSB generation is  $V_{ref}/2$ -to- $3V_{ref}/2$ . To generate rest of the bits and eventually the LSB, depending on the input signal range, the CM voltage will converge to  $V_{ref}$  or GND. This variation can cause the dynamic offset in the single-ended structure. To overcome this issue a high output impedance current source (M<sub>3</sub>, 4) was used in the preamplifier circuit, which determines the

current flowing through the  $M_{1, 2}$  and therefore reduces the overdrive voltage variation and indeed the dynamic offset.

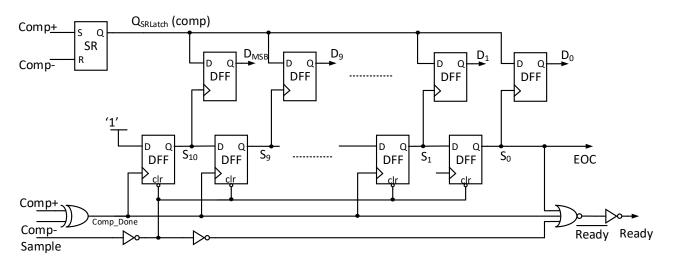

#### 3.3.3 Asynchronous SAR control logic circuit

Asynchronous control logic is used in this ADC. The circuit schematic and timing diagram of the asynchronous controller are illustrated in Fig. 3.12. Low power supply voltage and the use of high threshold devices in the logic circuit reduced the power consumption and the leakage currents. The input signals to this circuit are Sample (external signal with 10% duty cycle), V<sub>comp</sub> (comparator decision at SRlatch) and Comp Done (XOR of comparator's positive and negative output). The output signals are DAC control bits, preamp\_reset, En and EOC (end of conversion). During the sampling phase, the DFFs are reset and their outputs ( $S_0$  to  $S_{10}$ ) will be '0', therefore all of controlling signals for DAC (DAC C) will be '0' and the bottom plates of all capacitors in DAC will be connected to the input. When the sample signal changes from '1' to '0', all capacitors will be switched to V<sub>ref</sub> from the input signal, and conversion starts. When the first comparison is done, MSB is ready and stored at SR latch, and Comp Done goes to '1'. This will trigger DFF and S10 goes to '1', and it generates trigger clock for the bit FFs. At the rising edge of this clock, the bit DFFs will sample the comparator's output witch was stored in the SR latch. Meanwhile,  $\overline{Ready}$  goes to '0' and resets the En signal in comparator. This will set the comparator's output to '1' and Comp Done goes to '0' again.

If DAC\_C = 1, the bottom plate of the affected capacitor will be connected to GND, and if DAC\_C = 0 the bottom plate of the relevant capacitor will be stay connected to  $V_{ref}$ . This procedure will continue until the detection of the last bit. Then the EOC signal will go from '0' to '1', and it will reset the capacitors to prepare for the next sampling and conversion. The preamp\_reset and En signals will be generated as shown in Fig. 3.12. The Preamp\_reset duty cycle is tunable by Itd1, and the amplifying time is adjustable by Itd2.

a)

Fig. 3.12 a) Block diagram of the asynchronous SAR control logic and timing diagram b) DAC switches control signal c) Control signals waveform.

When  $\overline{\text{Ready}}$  goes low, preamp\_reset goes high and after a t<sub>d1</sub> delay it goes low, and amplification starts. The t<sub>d2</sub> time is amplifying time, and at the end of this time En signal goes high and enables the latch. When the comparator's output becomes ready, it will be detected by xor of positive and negative output of comparator, and comp\_Done goes high.

#### **3.4 Measurements Results**

The prototype ADC was fabricated in 0.18  $\mu$ m CMOS 2P4M process and tested. Figure 3.13 shows a full micrograph and zoomed-in view of the core ADC. The total chip size is  $1.9 \times 1.9$  mm<sup>2</sup>, while the core size is  $270 \times 475$   $\mu$ m<sup>2</sup>. The sampling frequency is 10 kS/s, and the power supply voltage is 0.75 V. The sampling trigger is a pulse waveform with a 10% duty cycle. It was generated by an arbitrary waveform generator. This trigger pulse controls the sampling switch, and rest of the control clocks are generated internally by the asynchronous control logic inside the chip. The test set-up is shown at Fig. 3.14.

Fig. 3.13 Die micrograph and the zoomed-in core.

Fig. 3.14 Test Set-up of the ADC.

Figure 3.15 shows the output of the ADC for a sine-wave input signal with and without error/offset cancelling capacitor network. When the input signal is getting larger than  $V_{ref}$ , the reference voltage for the comparator switches from GND to  $V_{ref}$ . As explained earlier, because of the parasitic capacitor at the comparator's input node, this reference switching creates error in the final code. The reference switching creates a comparator offset change as well. This error and offset change cause nonlinearity at the output when the input signal varies around  $V_{ref}$ . This nonlinearity is visible in Fig. 3.15.a, where the error/offset canceling network is turned off. Figure 3.15.b shows the output of the ADC for same input signal with the error/offset canceling network turned on and calibrated to cancel the voltage error. The curve around the  $V_{ref}$  (middle of amplitude) point is zoomed in to show the effectiveness of the error/offset canceling network.

Fig. 3.15 Measured ADC output for 0.5 kHz sinewave input a) without (EOC) error/offset canceling b) with error/offset canceling.

Figure 3.16 shows the ADC output spectrum without and with the error/offset canceling network for a 0.5 kHz input signal. As expected, without error cancellation there are large harmonics (Fig. 16. a,) due to the nonlinearity around the mid-range signal level. Figure 3.17 shows the ADC output spectrum with the input frequency at 3.8 kHz. The possible source of the higher third order harmonic distortion is from the input signal source and the filter that have been used for the measurement. Another possibility is not enough resolution in the parasitic voltage error canceling network.

Fig. 3.16 Measured ADC output spectrum for 0.5 kHz sinewave input a) With error/offset canceling network off b) With error/offset canceling network on.

Fig. 3.17 Measured ADC output spectrum for 3.8 kHz sinewave input with error/offset canceling network on.

Figure 3.18 shows the dynamic performance (SNDR/SFDR) of the ADC with the input frequency swept from DC to Nyquist at a 10 kS/s sampling rate. The effective number of bits (ENOB) versus the input frequency is shown in Fig. 3.19. There is no significant drop in the ENOB at higher input frequencies, because of the lower operation frequency and (more importantly) the asynchronous control signal which controls the comparator's pre-amplification and latching time based on the input signal. The ADC can achieve 9.76 ENOB at 0.9 kHz and 9.6 ENOB at 4.8 kHz.

Fig. 3.18 Measured ADC dynamic performance (SNDR/SFDR) versus input frequency.

Fig. 3.19 Measured ENOB of the ADC versus input frequency.

The DNL and INL are illustrated in Fig. 3.20. The peak DNL and INL are +0.6/-0.37 and +0.94/-0.89, respectively at a 10 kS/s sampling rate. The power consumption is 250 nW from a 0.75 V supply voltage. The analog power is the main part of the power consumption. It includes the comparator, the capacitive DAC array and the sampling switches. The digital power, including control logic and output buffers, is a small portion of the total power consumption. It is because of the high threshold devices that had been used in digital blocks to reduce the leakage current, and also the lower leakage current of the process compared to more modern technologies.

Fig. 3.20 Measured DNL and INL.

The measurement performance of the prototype ADC is summarized in Table 3.2. The prototype ADC is compared with the most relevant state-of-the-art works in Table 3.3.

The figure-of-merit (FOM) used to compare the ADC performance was

$$FOM = \frac{Power}{\min\{fs, 2 \times ERBW\} \times 2^{ENOB}}$$

(3.26)

Lower power consumption is important factor for biomedical application as well as FoM. Reference [7] is benefiting from the advanced process, and in [23, 24], which used similar process, they achieved slightly better FoM but their power consumption is much higher. In [25] the performance is reported up to 10 kHz input, which is way lower than Nyquist.

| TABLE 5.2 Summary of Terrormanee |                   |  |  |  |  |  |  |

|----------------------------------|-------------------|--|--|--|--|--|--|

| Technology                       | 0.18 µm CMOS 2P4M |  |  |  |  |  |  |

| Area [mm <sup>2</sup> ]          | 0.12              |  |  |  |  |  |  |

| Resolution [bit]                 | 11                |  |  |  |  |  |  |

| Sampling Rate [kS/s]             | 10                |  |  |  |  |  |  |

| Supply Voltage [V]               | 0.75              |  |  |  |  |  |  |

| Input Range (Single Ended) [V]   | 2×Vref (2×0.375)  |  |  |  |  |  |  |

| SNDR [dB]                        | 60.5              |  |  |  |  |  |  |

| SFDR [dB]                        | 72                |  |  |  |  |  |  |

| ENOB [bit]                       | 9.76              |  |  |  |  |  |  |

| DNL [LSB]                        | +0.6/-0.37        |  |  |  |  |  |  |

| INL [LSB]                        | +0.94/-0.89       |  |  |  |  |  |  |

| Total Power Dissipation [nW]     | 250               |  |  |  |  |  |  |

| FoM [fJ/Conv.]                   | 28.8              |  |  |  |  |  |  |

|                                  |                   |  |  |  |  |  |  |

TABLE 3.2 Summary of Performance

TABLE 3.3 COMPARISON TO STATE-OF-ART WORKS

|                      | This Work<br>[42] | JSSC'13<br>[7] | TBCS'14<br>[8] | JSSC'12<br>[9] | TCASI'15<br>[10] | ISSCC'10<br>[11] | ESSCIRC'14<br>[23] | ASSCC'15<br>[24] | TCASI'16<br>[25]     | TCASII'16<br>[41]   |

|----------------------|-------------------|----------------|----------------|----------------|------------------|------------------|--------------------|------------------|----------------------|---------------------|

| Architecture         | Single-ended      | Diff           | Single-ended   | Diff           | Single-ended     | Single-ended     | Diff               | Single-ended     | Diff                 | Diff                |

| Technology [nm]      | 180               | 65             | 180            | 130            | 130              | 350              | 180                | 180              | 180                  | 65                  |

| Supply Voltage [V]   | 0.75              | 0.6            | 0.9            | 1/0.4          | 1.0              | 1.0              | 1.0                | 0.6              | 0.8                  | 1.0                 |

| Resolution [bit]     | 11                | 10             | 9              | 10             | 10               | 10               | 11                 | 10               | 10                   | 14                  |

| Sampling Rate [kS/s] | 10                | 20             | 100            | 1.0            | 1000             | 10               | 1000               | 100              | 200                  | 10                  |

| SNDR [dB]            | 60.5              | 55             | 50.1           | 56.7           | 54               | -                | 63.4               | 58.83            | 57.86                | 77                  |

| SFDR [dB]            | 72                | 69             | 65.1           | 67.6           | -                | -                | 76.6               | 63.6             | 72.27                | 88.8                |

| ENOB [bit]           | 9.76              | 8.84           | 8.02           | 9.1            | 8.8              | 9.06             | 10.3               | 9.48             | 9.3                  | 12.5                |

| DNL [LSB]            | +0.6/-0.37        | 0.58           | 0.85           | +0.54/-0.61    | -0.33/+0.56      | 0.89             | +0.53/-0.85        | +0.85/-0.47      | +0.29/-0.26          | -0.9/+2.2           |

| INL [LSB]            | +0.94/-0.89       | 0.57           | 1.52           | +0.45/-0.46    | -0.61/+0.55      | 0.73             | +0.68/-0.91        | +1.52/-1.26      | +0.36/-0.8           | -2.2/+2.2           |

| Power [nW]           | 250               | 206            | 1330           | 53 / 72        | 9000             | 22000            | 24000              | 1720             | 2010                 | 1980                |

| FOM [fJ/Conv-Step]   | 28.8              | 22.4           | 51.3           | 94.5           | 27               | 45               | 19.9               | 24.1             | 15.5(10kHz)          | 34.2                |

| Core Area [µm×µm]    | 270×475           | 470×750        | 478×316        | 357×536        | 235×240          | -                | -                  | 360×380          | 0.154mm <sup>2</sup> | 0.28mm <sup>2</sup> |

# **3.5 Summary**

A single-ended 250 nW SAR ADC with a 0 -  $2V_{ref}$  input range using a charge error/offset canceling network is presented. It has a small total capacitance and a reduced loading effect on the previous stage. It is suitable for biomedical applications. A comparator operating in the subthreshold region with low dynamic offset was used, along with a self-controlled SAR logic at a 0.75 V supply voltage. The measurement results verify the power, area and loading efficiency of the ADC.

# CHAPTER 4. A NOISE-COUPLED VCO-BASED QUANTIZER AND ΔΣ ADC BASED ON NOISE-COUPLED VCO-BASED QUANTIZER

#### Abstract