#### AN ABSTRACT OF THE THESIS OF

| Jai Eun Jang           | for the degree of <u>Doctor of Philosophy</u> in       |

|------------------------|--------------------------------------------------------|

| Computer Science       | presented on April 4, 1990                             |

| Title: Design and Anal | ysis of Robust Algorithms for Fault Tolerant Computing |

|                        | Redacted for Privacy                                   |

| Abstract approved:     | Bella Bose                                             |

We propose a new strategy to recognize the maximum subcube of size k in an n-cube multiprocessor. This strategy will enhance the performance drastically so that our algorithm will outperform the buddy system by a factor  ${}_{n}C_{k}$ , the gray strategy by  ${}_{n}C_{k}/2$  and Al-Dhelaan strategy by  ${}_{n}C_{k}/(k(n-k)+1)$  in cube recognition. We present a very efficient processor allocation strategy which makes larger contiguous spaces for the new coming job than the buddy, gray and the Al-Dhelaan strategies do. Furthermore, this new strategy is suitable for static as well as dynamic processors allocation and it results in a less fragmentation and higher fault tolerance. We also describe an efficient procedure for task migration under the new strategy: 1) goal configuration under the new strategy; 2) node-mapping between source and destination nodes; and 3) the shortest deadlock-free routing algorithm.

We describe an optimal fault-tolerant broadcasting algorithm in the hypercube in the presence of n-1 faulty processors. This algorithm takes  $log_2(N) + 1$  steps to broadcast the message to all other processors. Our broadcasting algorithm is a procedure by which a

processor can pass a message to all other processsors in the network non-redundantly: This procedure is important for diagnosis of the network, distribution agreement or clock synchronization.

A simple yet efficient algorithm to broadcast in a Cube-Connected Cycles Network containing faulty node/links is proposed. The algorithm is particularly useful in critical real-time systems that can't tolerate the time overhead of identifying the faulty processors online. The algorithm delivers multiple copies of the broadcast message through disjoint paths to all the nodes in the system. The salient feature of the proposed algorithm is that the delivery of the multiple copies is transparent to the processes receiving the message and does not require that the precesses know the identity of the faulty processors. The precesses on non-faulty nodes that receive the message identify the original message from the multiple copies using some scheme appropriate for the fault model used.

We describe the definition and theory of adjacent asymmetric error masking codes. When these codes are used for short-circuit faults, they are capable of masking a single adjacent asymmetric error in bus in LSIs. This can be used in minimizing the number of transistors in the decoder of the bus line circuits, i.e., the code have the minimum weight. The bus lines can also be minimized. We systematically derive more codewords than those of previously known codes and present a formula to find the total number of codewords for each weight 2, 3 and 4 in the constant weight codes. When the weight is 2 in constant weight code, we prove that the number of codewords obtained is maximum.

# Design and Analysis of Robust Algorithms for Fault Tolerant Computing

by

Jai Eun Jang

A THESIS submitted to Oregon State University

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Completed April 4, 1990 Commencement June 1990

| APPROVED:                                               |

|---------------------------------------------------------|

| Redacted for Privacy                                    |

| Assoc. Professor of Computer Science in charge of major |

| Redacted for Privacy                                    |

| Chairman of Department of Computer Science              |

| Redacted for Privacy                                    |

| Dean of Graduate School                                 |

|                                                         |

|                                                         |

|                                                         |

| Date thesis is presented April 4, 1990                  |

|                                                         |

| Typed by Jai Eun Jang for <u>Jai Eun Jang</u>           |

#### **ACKNOWLEDGEMENT**

I would like to express my sincere gratitude to my advisor Professor Bella Bose for the guidance, support, helpful discussion and encouragement throughout this research.

Also, I would like to extend my thanks and respect to other members in my Ph.D committee: Professor Ted Lewis, Professor Toshi Minoura, Professor Pat Lenders and Professor Christopher Mundt for their support, encouragement and unfailing cooperation during my graduate study at OSU and during the development of this research.

I would like to acknowledge Oregon State University for giving me the opportunity to pursue my Ph.D work and Army Headquarters of Republic of Korea for its financial support.

I am very thankful for visiting professor, Won-Kyung Cho, for his helpful comments and encouragement.

I am very thankful to Huan Keh, Seung-Jin Park, Sungwoon Choi, Hae-Sung Kim, Inkyu Kim and Major Kwon for having good discussions and fun here.

Also, I am very thankful for my family for putting up with the pressure of my work that comes with such research and for providing the warm and loving environment that is so important for such an endeavor.

# TABLE OF CONTENTS

| 1. | Intro | oduction                                            | 1         |

|----|-------|-----------------------------------------------------|-----------|

|    |       | References                                          | 7         |

| 2. | A No  | ew Approach to Processor Allocation and Fault-Tole  | rance     |

|    | in aı | n N-cube Multiprocessor                             | 9         |

|    | 2.1   | Introduction                                        | 9         |

|    | 2.2   | Preliminaries and Background                        | 11        |

|    | 2.3   | Maximality of Subcube Recognition                   | 16        |

|    | 2.4   | A New Method to Allocate Processors                 | 18        |

|    | 2.5   | Analysis of Algorithm                               | 23        |

|    | 2.6   | A New Approach to Task Migration                    | 25        |

|    | 2.7   | Half-Task Migration Under Processor Failure         | 31        |

|    |       | References                                          | 36        |

| 3. | An (  | Optimal Fault-Tolerant Broadcasting Algorithm for a | Hypercube |

|    | Mul   | tiprocessor                                         | 38        |

|    | 3.1   | Introduction                                        | 38        |

|    | 3.2   | Preliminaries and Problem Statement                 | 40        |

|    | 3.3   | Previous Fault-Tolerant Broadcasting                | 41        |

|    | 3.4   | Optimal Fault-Tolerant Broadcasting Algorithm       | 43        |

|    | 3.5   | Analysis of Broadcasting Algorithm                  | 57        |

|    |       | References                                          | 60        |

| 4.   | Relia      | Reliable Broadcasting Algorithm for a Cube-Connected Cycles |     |  |  |  |

|------|------------|-------------------------------------------------------------|-----|--|--|--|

|      | Network    |                                                             |     |  |  |  |

|      | 4.1        | Introduction                                                | 62  |  |  |  |

|      | 4.2        | Preliminaries and Problem Statement                         | 64  |  |  |  |

|      | 4.3        | Proposed Broadcasting Algorithm                             | 68  |  |  |  |

|      | 4.4        | Performance of Algorithm Broadcasting                       | 76  |  |  |  |

|      | 4.5        | An Optimal Fault-Tolerant Broadcasting Algorithm            | 78  |  |  |  |

|      | 4.6        | Analysis of Broadcasting Algorithm                          | 91  |  |  |  |

|      |            | References                                                  | 96  |  |  |  |

| 5.   | Mas        | king Adjacent Asymmetric Line Faults                        | 98  |  |  |  |

|      | 5.1        | Introduction                                                | 98  |  |  |  |

|      | 5.2        | Masking Asymmetric Line Faults                              | 99  |  |  |  |

|      | 5.3        | Preliminaries and Definition                                | 103 |  |  |  |

|      | 5.4        | Code Construction                                           | 105 |  |  |  |

|      | 5.5        | Comparison and Application                                  | 118 |  |  |  |

|      |            | References                                                  | 121 |  |  |  |

| 6.   | Conclusion |                                                             |     |  |  |  |

|      | 6.1        | Summary                                                     | 122 |  |  |  |

|      | 6.2        | Future Research                                             | 123 |  |  |  |

| Bibl | iograp     | hy                                                          | 125 |  |  |  |

| App  | endix A    | A : AAEMC  when  n=12 & w=3                                 | 129 |  |  |  |

| Ann  | endix B    | S: AAEMC when n=12 & w=3                                    | 130 |  |  |  |

# LIST OF FIGURES

| Figure |                                                                        | Page |

|--------|------------------------------------------------------------------------|------|

| 2.1    | A 3-dimensional hypercube, Q <sub>3</sub>                              | 11   |

| 2.2    | A 4-dimensional hypercube, Q <sub>4</sub>                              | 12   |

| 2.3    | An example of hypercube fragmentation                                  | 26   |

| 3.1    | Broadcasting in the presence of a single faulty processor              | 43   |

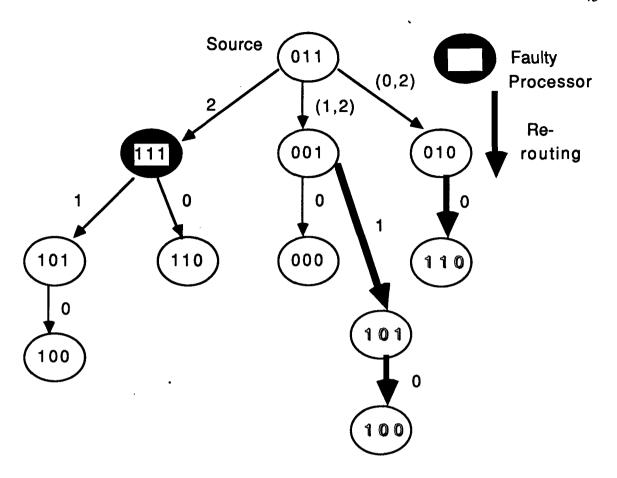

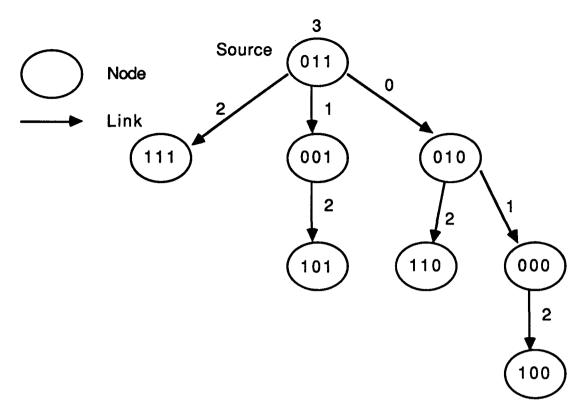

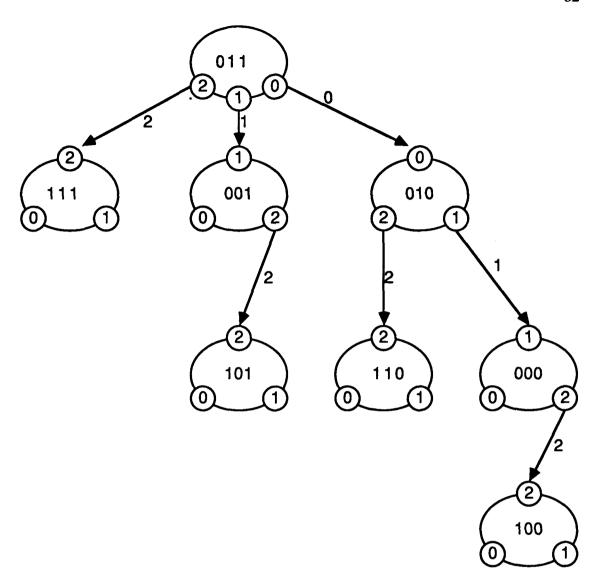

| 3.2    | Broadcasting in a Q <sub>3</sub> from the node 011                     | 45   |

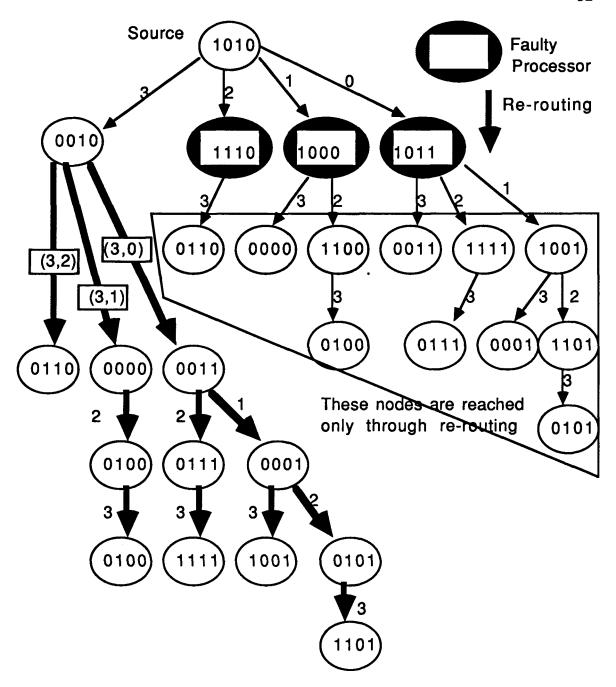

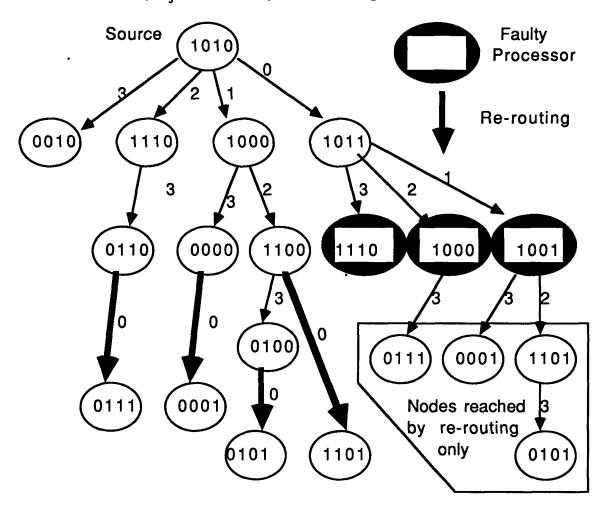

| 3.3    | Broadcasting where 3 faulty processors under the source node in Q4     | 52   |

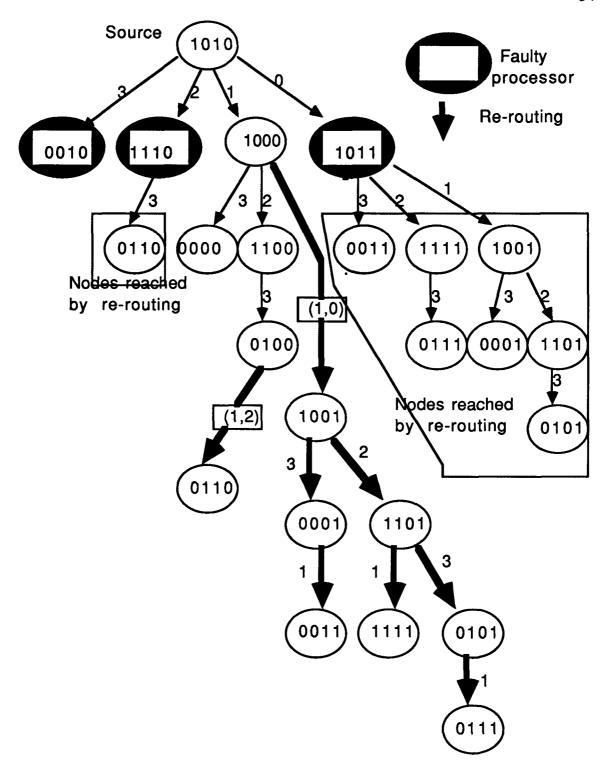

| 3.4    | Broadcasting when middle node is non-faulty in Q4                      | 54   |

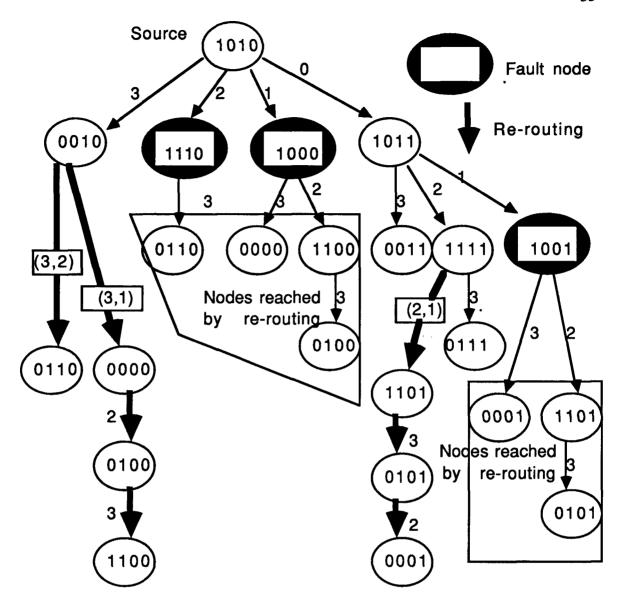

| 3.5    | Broadcasting in the presence of 3 faulty processors in different level |      |

|        | in Q <sub>4</sub>                                                      | 55   |

| 3.6    | Broadcasting when all-sons processors are faulty in Q4                 | 56   |

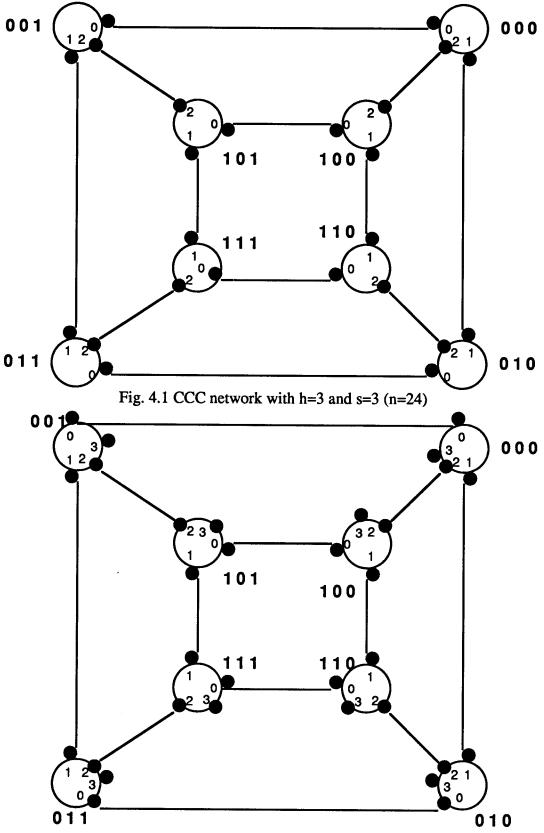

| 4.1    | CCC network with h=3 and s=3 (n=24)                                    | 66   |

| 4.2    | CCC network with h=4 and s=3 (n=32)                                    | 66   |

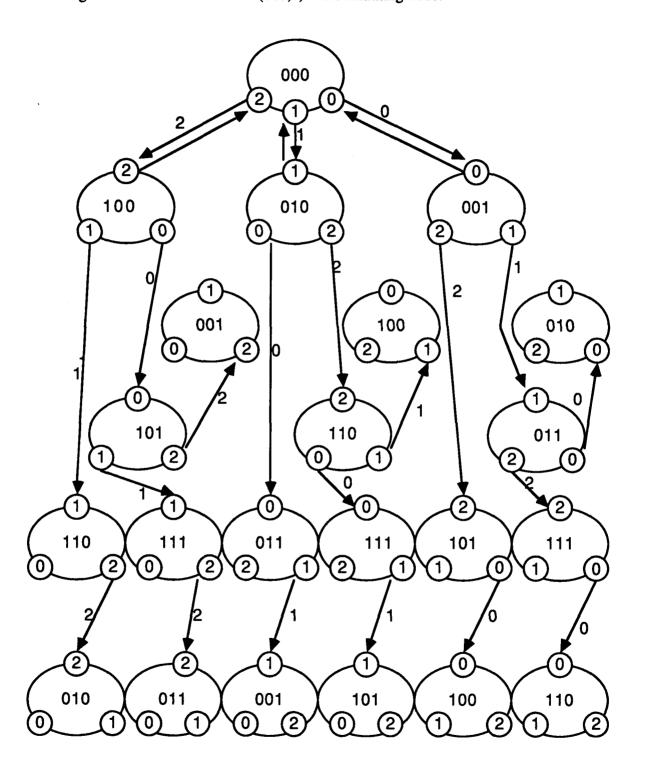

| 4.3    | Broadcasting multiple copies in a CCC                                  | 70   |

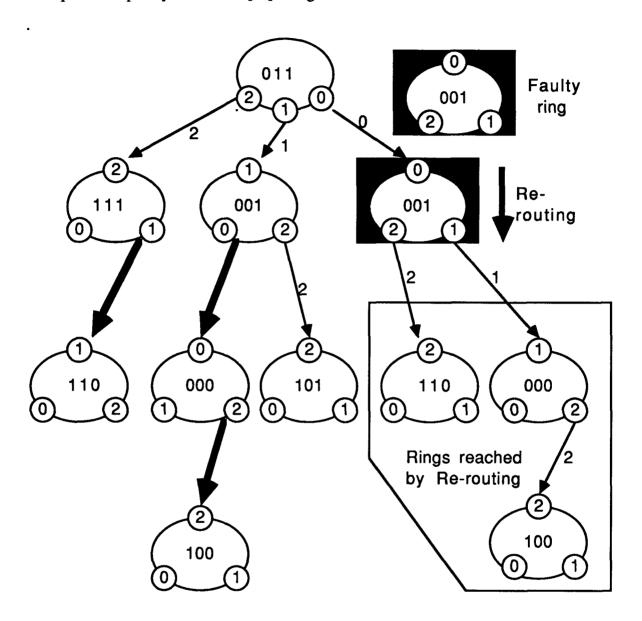

| 4.4    | Broadcasting in a faulty CCC with h=3 and s=3                          | 79   |

| 4.5    | Broadcasting in a CCC with s=3 and h=3 from the node (011,01)          | 82   |

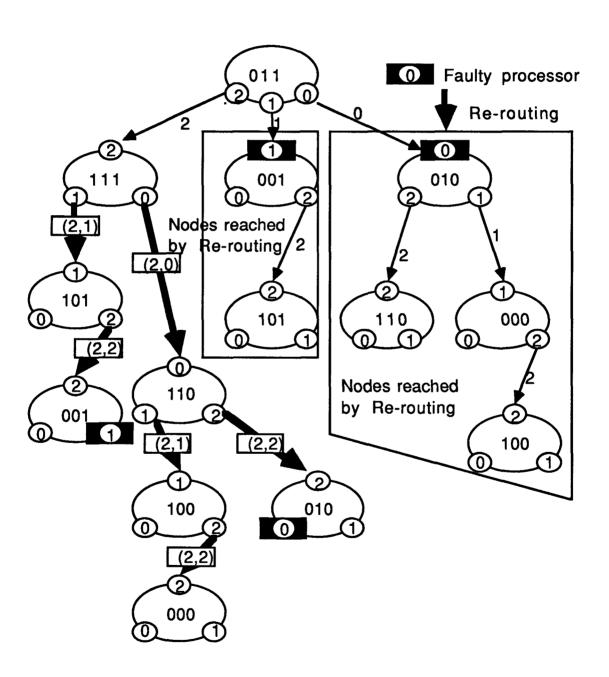

| 4.6    | Broadcasting in a CCC with faulty nodes (011,1) and (010,0)            | 89   |

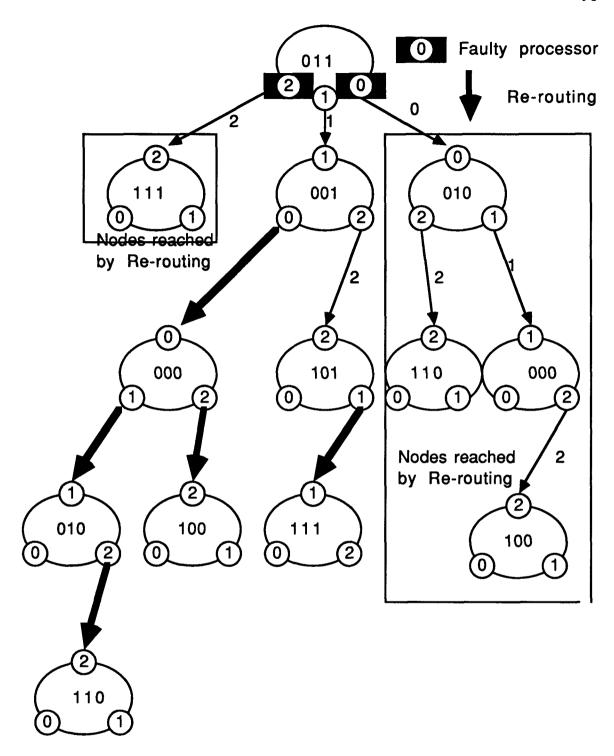

| 4.7    | Broadcasting in a CCC with faulty nodes (011,0) and (011,2)            | 90   |

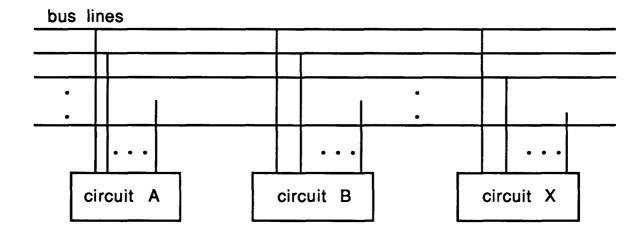

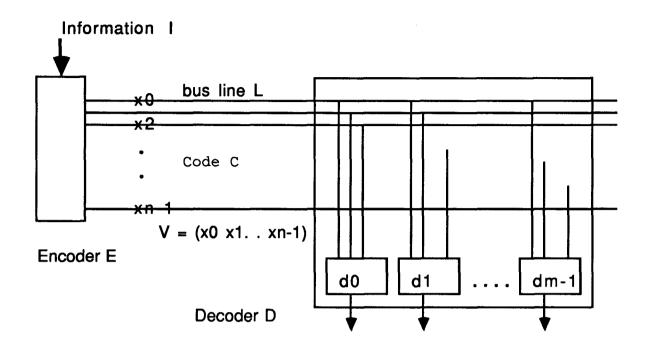

| 5.1    | A typical model of bus line circuit                                    | 100  |

| 5.2    | A bus line circuit with defect masking coding                          | 101  |

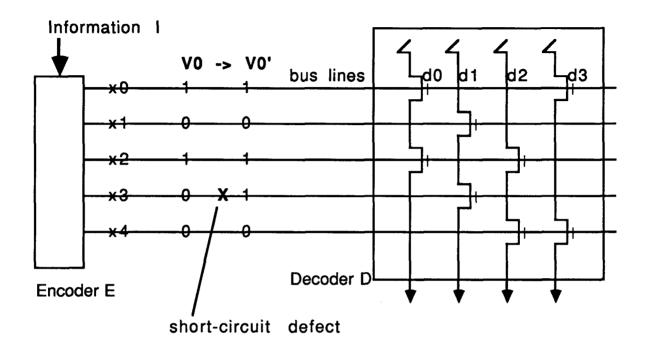

| 5.3    | An example of a masking single asymmetric fault                        | 102  |

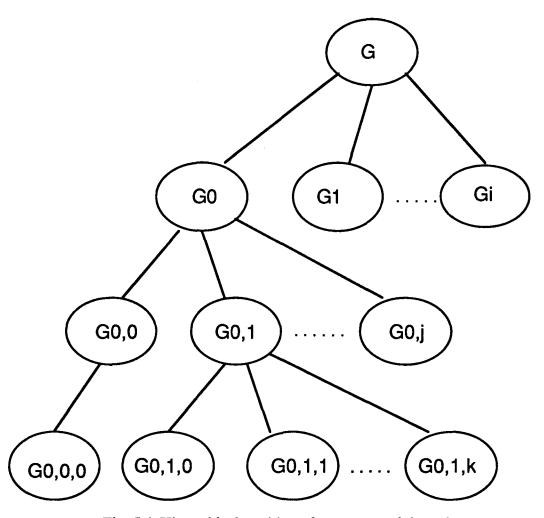

| 5.4    | Hierarchical partition of constant weight codes                        | 107  |

# LIST OF TABLES

| <u>Table</u> |                                                                           | Page |

|--------------|---------------------------------------------------------------------------|------|

| 2.1          | Link connections to each processors without duplication in Q <sub>4</sub> | 13   |

| 2.2          | The number of subcube recognizable by the Buddy, Gray,                    |      |

|              | Al-Dhelaan and New strategy                                               | 18   |

| 2.3          | Comparison among 4 different allocation strategies                        | 22   |

| 2.4          | Mask migration under the GC strategy and New strategy                     | 28   |

| 4.1          | Paths through which the nodes receive the broadcasting in a CCC           | 72   |

| 5.1          | Number of codewords in each class when weight is 3                        | 114  |

| 5.2          | Number of codewords in each class when weight is 4                        | 118  |

| 5.3          | Comparison between Graham and Ref[15] and new result                      | 119  |

| 5.4          | Comparison of the number of bus lines                                     | 120  |

# Design and Analysis of Robust Algorithms for Fault Tolerant Computing

#### Chapter 1

#### Introduction

Fault tolerance is one of the principle mechanisms for achieving high reliability and high availability in digital systems. The field of fault-tolerance ranges from failure mechanisms in integrated circuits to the design of robust software[1,2].

High reliability in computer design was first achieved through so-called fault-avoidance techniques:these involved computer design which used high quality, thoroughly tested components. Sometimes simple redundancy techniques were employed to achieve limited fault-tolerance.

The issue of organization and architecture of computers are key ones to the design of fault-tolerant computers. In recent years the field of computer architecture has been increasingly concerned with multiprocessors and distributed processing. It is expected that the next generation of computers will consist of innovative interconnections of multiple computing elements. Fault-tolerance issues in interconnecting multiple computing elements therefore will inevitably receive increasing attention.

In this thesis we have contributed some results in these areas and in the rest part of the chapter we briefly describe them.

When designing a large multiprocessor, one of the most important factors is the topology of the communication structure among the processors.

One of the most popular topologies is the n-cube multiprocessors[3-13]. The hypercube is a network of loosely coupled processors connected in such a way that two processors, u and w, are linked if and only if the Hamming distance(u,w) = 1. Hypercube multiprocessors have been drawing considerable attention due to their structual regularity for easy construction and high potential for the parallel execution of various algorithms.

A task arriving at a hypercube multiprocessor must be assigned "optimally" to a subcube in the multiprocessor for execution. Upon completion of execution, the subcube used for the task must be released for later use. Efficient allocation and/or deallocation is a key to its performance and utilization. The processor allocation in a hypercube multiprocessor consists of two steps:

- 1) determination of the size of the incoming task in terms of the number of processors needed in order to accommodate it.

- 2) recognition and location of subcube of accommodating the incoming task within the hypercube multiprocessor. We want to maximize the utilization of available resources and also minimize the inherent system fragmentation.

Three allocation strategies for n-cube multiprocessor are addressed: the buddy strategy which is based on the buddy system, the GC strategy which uses single or multiple Gray codes and the Al-Dhelaan strategy[6]. The Buddy system strategy is implemented in [8], and the GC strategy is implemented on an NCUBE/six by the University of Michigan Advanced Architecture Lab[4]. Due to special structure of the n-cube multiprocessor, the availability of some subcubes can't be detected by any of the above systems, and processor utilization is thus degraded.

In chapter 2, we propose a new strategy to recognize the maximum subcube in a n-cube multiprocessor. This strategy will enhance the performance drastically so that our algorithm will outperform the buddy system by a factor  ${}_{n}C_{k}$ , the gray strategy by  ${}_{n}C_{k}/2$  and Al-Dhelaan[6] by  ${}_{n}C_{k}/(k(n-k)+1)$  in cube recognition.

We present a very efficient processor allocation strategy which makes larger contiguous spaces for the new coming job than buddy, gray strategy and Al-Dhelaan[6] do.

Furthermore, this new strategy is suitable for static as well as dynamic processors allocation and it results in a less fragmentation and higher fault tolerance.

Also we describe an efficient procedure for the *task migration* under this new strategy. 1) goal configuration, 2) node mapping between source and destination node, 3) shortest deadlock-free routing algorithm.

And we describe the half-task migration in the presence of faulty processors. The half-task migration is defined as follows: When  $2^k$  processors are allocated for the job in an n-cube, we can have half-task migration from  $2^{k-1}$  processors to another  $2^{k-1}$  processors in order to continue the job in the case of processors failure. This approach has the following advantages: 1) We don't have to have the extra processors to reconfigure[11]. 2) It is easy and efficient to reconfigure the processors if the alternatives are chosen.

Broadcasting is an important means of communication among processors by which a processor can pass data or control to all other processors in the network. This operation is extremely important for diagnosis of the network, distributed agreement[13] or clock synchronization[14]. Distributed agreement and clock synchronization can be achieved only if there is no faulty node to deliver the message in the system[13-14]. This, however, is not easy to achieve in the presence of faulty node/link because the faulty nodes can either omit, corrupt, reroute, or alter information passing through them.

There are two possible approaches to overcome this problem. In the first approach, each node keeps limited information about the faulty nodes in the system. Fault-tolerant routing/broadcasting is achieved by going around the faulty nodes[7,16,21]. This approach can be used only if it is possible to identify the faulty processors "on-line". Since the overhead of identifying the faulty processors and passing the fault information to the other nodes could be quite severe, this approach is not suitable for many real-time applications. In the second approach, fault tolerance is achieved by sending multiple copies of the message through disjoint paths[13,17,20]. The nodes that receive the message identify the

original message from the multiple copies by using some scheme that is appropriate for the fault model, e.g., majority voting. The second approach has the advantage of not having to identify the faulty processors.

Sullivan and Bashkov[12] developed an algorithm for broadcasting in the hypercube. This algorithm was developed on the assumption of having no faulty processors. Al-Dhelaan[7] developed an algorithm for broadcasting in the hypercube in the presence of some faulty processors. The algorithm works if only one child processor is faulty under any node in the broadcasting tree. Their algorithm does not make explicit use of the properties of the hypercube topology. Ramanathan and Shin[13] developed another algorithm for the hypercube in the presence of faults which uses the second approach mentioned above.

In chapter 3, we describe an optimal fault tolerant broadcasting algorithm when n-1 processors are faulty. The proposed algorithm takes  $log_2(N)+1$  steps to broadcast a message from one processor to all other processors. Our broadcasting algorithm is a procedure by which a processor can pass a message to all other processors in the network non-redundantly: this message can either be information or control.

Cube-connected-cycles is a parallel network architecture proposed by Preparata and Vuillemin[18]. The CCC can efficiently solve a large class of problems that include Fourier transform, sorting, permutations, etc., The operation of the cube-connected-cycles network is based on the combination of piplining and parallelism, which leads to the following results[19]:

- 1. The number of connections per processor is reduced to three.

- 2. Processing time is not significantly increased with respect to that achievable on the cube-connected network.

3. The overall structure complies with the basic requirements of the VLSI technology: modularity, ease of layout, simplicity of communication among processors, simplicity in timing and control of the entire system.

In chapter 4, we present two approaches mentioned earlier in the presence of faulty node/link in the CCC. The first broadcasting algorithm[17] delivers multiple copies of the message to all nodes in the CCC through disjoint paths. The basic idea of our algorithm is as follows. The node that wants to broadcast a message sends the message to all its neighbors in the same ring. The neighbors in the same ring and the node initiating the message in turn broadcast the message using a simple yet efficient algorithm. The algorithm executed by the neighbors is coordinated such that the copies of the message received by a node have traveled through disjoint paths. The good feature of the proposed algorithm is that the delivery of the multiple copies is transparent to the processes receiving the message and does not require the processes to know the identity of the faulty processors. Depending on the fault modes used, the algorithm can tolerate either s-1 or  $\lfloor s/2 \rfloor$  or  $\lfloor s/3 \rfloor$  node/link faults. The algorithm completes in  $\lfloor s/2 \rfloor + (2s-1) + \lfloor s/2 \rfloor$  steps and 4s steps if each node can use all and at most one of its outgoing links at a time respectively.

The second broadcasting algorithm[21] delivers a copy of message to all nodes nonredundantly. The basic idea of our algorithm is as follows. The node that wants to broadcast a message checks if its neighbor node is faulty or not. If the neighbor node is faulty, the initiating node gives this information to its non-faulty neighbor node. This non-faulty node broadcasts the message to the nodes to be broadcasted by faulty-node. We prove that this algorithm is optimal. This algorithm tolerates 2 processors if two adjacent nodes are faulty and s-1 rings or s-1 processors faults, otherwise. This optimal fault-tolerant broadcasting algorithm takes (5s+4)/2 steps.

In Chapter 5, we design efficient adjacent asymmetric error masking codes (AAEMC) which are useful for masking adjacent bus lines in ROMs. We systematically derive the number of codewords in AAEMC of constant weight, with weight 2, 3 and 4.

When these codes are used in VLSIs, they are capable of masking a single adjacent asymmetric error in bus lines. Furthermore, using these codes we can minimize the number of transistors in the decoder of the bus line circuits and the number of bus lines. However a separate encoder circuit is needed which is not very complex.

#### REFERENCES

- 1. R. Negrini and M. G. Sami, Fault Tolerance Through Reconfiguration in VLSI and WSI Arrays, MIT Press, 1989

- 2. Fault-Tolerant Computing: Theory and Techniques, Prentice-Hall, 1986

- 3. M. Chen and K.G. Shin, "Processor Allocation in an N-cube Multiprocessor Using Gray Codes", IEEE Trans. Computer, Dec. 1987 pp. 1396-1407.

- 4. M. Chen and K.G. Shin, "Task Migration in Hypercube Multiprocessor", Proc. 16th Annual Int'l Symp. on Computer Architecture. Jun 1989, pp. 105-111

- 5. B. Becker and H.U. Simon, "How robust is the n-cube?", in Proc. 27th Ann. Symp. Foundations of Comp. Sci. Oct. 1986 pp. 283-291.

- 6. A. Al-Dhelaan and B. Bose, "A New strategy for Processor Allocation in an N-cube Multiprocessor", Phoenix Conference on Computer and Communication, Mar 1989. pp. 114-118.

- 7. A. Al-Dhelaan and B. Bose, "Efficient Fault Tolerant Broadcasting Algorithm for the Hypercube", Proc. The fourth Conf. on Hypercube Concurrent Comp. and Applications, Monterey, Mar 1989, pp. 123-128.

- 8. NCUBE Corp, NCUBE/10: An Overview, Beverton, OR, Nov 1985

- 9. J. E. Jang, S. W. Choi and W. K. Cho, "A New Approach to Processor Allocation and Task Migration in an N-cube Multiprocessor, Proceedings, International Conference on Supercomputing, Nov, 1989. pp. 314-325.

- 10. J. E. Jang and W. K. Cho, "Maximality of Subcube Recognition and Fault Tolerance in an N-cube Multiprocessor", Proceedings, 4th SIAM conference on Parallel Processing for Scientific Applications, Dec, 1989.

- 11. M. Sultan and Rami Melhem, "Fault Tolerance and Reliable Routing in Augmented Hyercube Architecture", 8th IEEE Int'l Phoenix Conference on Computer and Communication, Mar, 1989. pp. 19-23.

- 12. H. Sullivan and T. R. Baskow, "A large scale homogeneous, fully distributed parallel machine,I," Proc. Fourth Symp. Comp. Architecture, Mar. 1977, pp. 105-117.

- 13. P. Ramanathan and K.G. Shin, "Reliable Broadcasting in Hypercube Multicomputers", IEEE Trans. on Comp. Dec 1988, pp 1654-1657.

- 14. L. Lamport, R. Shostak, and M. Pease, "The Byzantine generals problem," ACM Trans. Programming language System, pp. 382-401, Jul. 1982.

- 15. T. K. Srikanth and S. Toueg, "Optimal clock synchronization," J. ACM pp.626-645, Jul.1987.

- 16. J. E. Jang, "Optimal Fault Tolerant Broadcasting Algorithm for Hypercube Multiprocessor", Proceedings, 1990 ACM Computer Science Conference, Feb, 1990. pp. 96-102.

- 17. J. E. Jang, "Reliable Broadcasting Algorithm in an Cube-Connected Cycles Network", Proceedings. 9th International Phoenix Conference on Computers and Communications, Mar, 1990

- 18. F. P. Preparata and J. Vuillemin, "The Cube-Connected Cycles, A Versatile Network for Parallel Computation," Communication of ACM, pp. 30-39, May 1981.

- 19. A. Al-Dhelaan and B. Bose, "Efficient Fault Tolerant Broadcasting Algorithm for the Cube-Connected Cycles Network", Proc. IEEE Pacific Rim Conference, May 1989, pp. 161-164.

- 20. T. K. Srikanth and S. Toueg, "Simulating authenticated broadcasts to derive simple fault-tolerating algorithms," Tech. Rep. 84-623, Dep. Comp. Cornell Univ., Jul. 1984.

- 21. J. E. Jang, "Optimal Fault Tolerant Broadcasting Algorithm in an Cube-Connected Cycles Network", Proceedings. in the PARBASE-1990, Mar, 1990. pp. 206-215.

- 22. Kazumitsu. Matsuzawa and Eiji. Fujiwara, "Masking Asymmetric Line Faults using Semi-distance Codes", 18th FTCS, pp. 354-359

#### Chapter 2

# A New Approach to Processor Allocation and Fault-Tolerance in an N-cube Multiprocessor

#### 2.1 Introduction

Hypercube multiprocessors have been drawing considerable attention due to their structual regularity for easy construction and high potential for the parallel execution of various algorithms. Numerous research efforts related to hypercube architectures, operating systems, etc., have been undertaken[1-15]. The problem of processor recognition, allocation, task migration and fault-tolerance in an n-cube is the subject of this chapter. A task arriving at a hypercube multiprocessor must be assigned "optimally" to a subcube in the multiprocessor for execution. Upon completion of execution, the subcube used for the task must be released for later use. Efficient allocation and/or deallocation is a key to its performance and utilization. The processor allocation in a hypercube multiprocessor consists of two steps: 1) determination of the size of the incoming task in terms of the number of processors needed in order to accommodate it, and 2) recognition and location of subcube of accommodating the incoming task within the hypercube multiprocessor. We want to maximize the utilization of available resources and also minimize the inherent system fragmentation.

Three allocation strategies for n-cube multiprocessor are addressed: the buddy strategy which is based on the buddy system, the GC strategy which uses a single or multiple Gray codes and Al-Dhelaan strategy[8]. Due to special structure of the n-cube multiprocessor, the availability of some subcubes can't be detected by any of the above systems, and processor utilization is thus degraded.

In this chapter we propose a new strategy to recognize the maximum subcube in a n-cube multiprocessor. This subcube recognition algorithm can be done in both serial and parallel and this method is analyzed. This strategy will enhance the performance drastically so that our algorithm will outperform the buddy system by a factor  ${}_{n}C_{k}$ , the gray strategy by  ${}_{n}C_{k}/2$  and Al-Dhelaan[8] by  ${}_{n}C_{k}/(k(n-k)+1)$  in cube recognition.

Also we present a very efficient processor allocation strategy which makes larger contiguous spaces for the new coming job than buddy, gray strategy and Al-Dhelaan[8] do. Furthermore, this new strategy is suitable for static as well as dynamic processors allocation and it results in a less fragmentation and higher fault tolerance.

Even though enough number of hypercube nodes are available for the incoming job, allocation and deallocation of subcube usually result in a fragmented hypercube. The fragmentation problem in a hypercube can be solved by task migration, i.e., relocating tasks within the hypercube to remove the fragmentation. We describe a shortest deadlock-free routing algorithm for task migration under the new strategy. 1) goal configuration, 2) node mapping between source and destination nodes, 3) shortest deadlock-free routing algorithm.

We describe the half-task migration in the presence of faulty processors. The half-task migration is defined as follows: When  $2^k$  processors are allocated for the job in an n-cube, we can have half-task migration from  $2^{k-1}$  processors to another  $2^{k-1}$  processors in order to continue the job in the case of processors failure. This approach has the following advantages: 1) We don't have to have the extra processors to reconfigure[15]. 2) It is easy and efficient to reconfigure the processors if the alternatives are chosen.

This chapter is organized as follows. Section 2.2 introduces the necessary notation and background. Section 2.3 will describe the new approach to recognize the maximum subcubes in Q<sub>n</sub>. Section 2.4 will explain the new allocation strategy which is suitable for static as well as dynamic processor allocation and results in a less system fragmentation, more subcube recognition and higher fault tolerance. In section 2.5 we will describe the

parallel algorithm for processor allocation problem and this algorithm has a time complexity of  $O({}_{n}C_{k})$ . The time complexity of serial algorithm is  $O(2^{k}{}_{n}C_{k}2^{n-k})$ . Section 2.6 will describe an efficient procedure for the task migration under this new strategy. 1) goal configuration, 2) node mapping between source and destination node, 3) shortest deadlock-free routing algorithm. Section 2.7 will describe an efficient procedure for the half-task migration under this new strategy.

## 2.2 Preliminaries and Background

A n-cube can be defined as follows:

Definition: An n-cube Qn is defined recursively as

- a) Q<sub>0</sub> is a trivial graph with one node, and

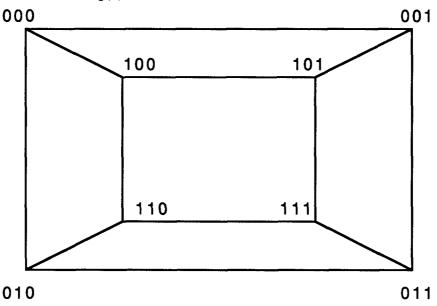

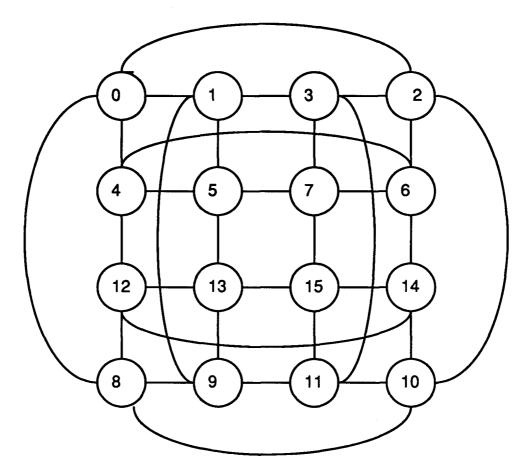

- b)  $Q_n = K_2 * Q_{n-1}$ , where  $K_2$  is the complete graph with two nodes. Fig. 2.1 and Fig 2.2 shows a  $Q_3$ , and a  $Q_4$ , hypercubes respectively.

A coding scheme with n bits is defined as a one-to-one mapping from an integer number between 0 and  $2^{n}-1$  to a binary representation with n bits. For example, the three bit binary representation of 5 is  $B_3(5) = 101$ .

Fig 2.1 A 3-dimensional hypercube, Q3

Fig 2.2 A 4-dimensional Hypercube, Q4

Gray codes,  $G_n$ , can be generated as follows. One starts with the sequence of the two 1-bit numbers 0 and 1. This is a 1-bit Gray code. To build a 2-bit Gray code, take the same sequence and insert a zero in front of each number, then take the sequence in reverse order and insert a one in front of each number. In other words, we get the sequence

$$G_2 = \{00,01,11,10\},$$

$G_3 = \{000,001,011,010,110,111,101,100\}$

The gray code can be obtained from the corresponding binary number as follows[16].

$$g_i = b_i \oplus b_{i+1}$$

where  $0 \le i \le n-1$

$g_n = b_n$

<u>Definition</u>: The Hamming distance between two hypercube nodes with addresses  $u = u_n$  $u_{n-1} \dots u_1$  and  $w = w_n w_{n-1} \dots w_1$  in a  $Q_n$  is defined as

$$H(u,w) = \sum_{i=1}^{n} h(u_i,w_i), \text{ where } h(u_i,w_i) = 1, \text{ if } u_i \neq w_i$$

$$= 0$$

, if  $u_i = w_i$

For example, if u = (10010) and v = (01011), then H(u,w) = 3.

The hypercube is a network of a loosely coupled processors connected in such a way that two processors, u and w, are linked if and only if H(u,w) = 1, i.e., the indices of neighboring processors differ by a power of 2. We can represent an n-cube using link list structure. For example, a processor with address 0000(0) in Fig. 2.2 is linked with 0001(1), 0010(2), 0100(4), 1000(8) in Q4. In the same way we can represent all the connections of Q4 in the Table 2.1, where each connection has no duplicated link.

| # | address | link(H1) | #  | address | link(H1) |

|---|---------|----------|----|---------|----------|

| 0 | 0000    | 1,2,4,8  | 8  | 1000    | 9,10,12  |

| 1 | 0001    | 3,5,9    | 9  | 1001    | 11,13    |

| 2 | 0010    | 3,6,10   | 10 | 1010    | 11,14    |

| 3 | 0011    | 7,11     | 11 | 1011    | 15       |

| 4 | 0100    | 5,6,12   | 12 | 1100    | 13,14    |

| 5 | 0101    | 7,13     | 13 | 1101    | 15       |

| 6 | 0110    | 7,14     | 14 | 1110    | 15       |

| 7 | 0111    | 15       | 15 | 1111    |          |

Table 2.1 Link connections to each processor without duplication in Q4

Therefore we can represent all the connection of  $Q_n$  with each address using link list structure like Table 2.1. From the Table 2.1 we can find some interesting properties.

First of all, the number of link at each address is the same as the the number of 0's with same address. The value of link in each address is sorted in ascending order and greater than that of each address.

Let  $\Sigma$  be the ternary symbol set  $\{0,1,x\}$ , where x is Don't Care symbol. Then every subcube of an n cube can be uniquely represented by a string of symbols in S. By assigning all combinations of "0" and "1" to x, we can find all the *partners* for the job. For example, when incoming job requires  $2^3$  processors with node "0", arbitrary 3 link are chosen. If we choose processors  $\{1,2,4\}$  connected to address "0" node, then we have  $\{0000, 0001, 0010, 0100\}$ , that is  $\{0xxx\}$  type. Thus, we can find all the *partners*,  $\{0110,0101,0011,0111\}$ , thus assigning  $\{0000, 0001, 0010, 0100, 0101, 0011, 0011, 0011\}$  for the incoming job to require  $2^3$  processors.

Let us define some notation to find all the *partners* directly from above table. Let the first column which ranges  $0 \sim 2^{n}-1$  in the link connection table be table\_index. Definition: There are r links per table\_index in ascending order. Let p be the position in r. Then partner(table\_index, p) will give the corresponding value. For example, partner(4, 2) = 6.

We have the following Lemmas from the characteristics of the link list table.

**Lemma 2.1:** For every combination pa and pb in the table\_index where pb > pa, position(pa) will be the p and pb will be new table\_index. Then partner(pb,position(pa)) will be the partner, where position(pa) is the position in r.

proof: All the codewords in the link column are constant weight codes which are Hamming distance 1 from table\_index. Therefore, they are Hamming distance 2 from each other and H(table\_index,pa) and H(table\_index,pb) =1. Thus, H(partner(pb,position(pa)),pb) = 1 And H(partner(pb,position(pa)),table\_index) = 2. So, H(partner(pb,position(pa)),pa) = 1. Partner(pb,position(pa)) gives the partner.

For example, when incoming job needs  $Q_2$  subcubes in  $Q_4$  with address 0, there are  ${}_4C_2$  combinations, that is, (1,2) (1,4) (1,8) (2,4) (2,8) (4,8). Therefore we can find the partners 3, 5, 9, 6, 10, 12, respectively.

Lemma 2.2: While finding the partners, if there are two more links in the new table\_index, keep doing Lemma 2.1. Then we will find all the partners.

**Proof:** If there are one more links in the new table\_index, there are one more partners. This means we must find another partner to satisfy Hamming distance 1 for those links. The other part is the same as Lemma 2.1.

For example, when incoming job needs  $Q_3$  subcubes in  $Q_4$  with address 0, there are  ${}_4C_3$  combinations, that is, (1,2,4) (1,2,8) (1,4,8) (2,4,8). Let's get the partner when we choose processors (1,2,4). We have the following partner processors: processor 3 for processors (1,2), 5 for (1,4), 6 for (2,4), 7 for (5,6). Thus, we can recognize processors (0,1,2,3,4,5,6,7) for  $Q_3$ .

Lemma 2.3: When we have r links at each node with table\_index we can recognize  ${}_{r}C_{j}$  subcubes for the incoming  $2^{j}$  jobs where  $r \ge j$ .

*proof:* Let r and j be the number of link at each table-index and size j for the incoming job  $2^j$ , respectively. When we have j combination in r, we can find the partners using Lemma 2.1. And there are  ${}_rC_j$  ways to combine. Therefore we can recognize  ${}_rC_j$  subcubes for the incoming  $2^j$  jobs.

For example in Table 2.1, node 0 has 4 links. When incoming job needs  $2^2$  subcubes, there are  $4C_2$  ways to recognize the subcubes. We can find the partners for each connection. Therefore we have the following subcubes, which are  $\{(0,1,2,3), (0,1,4,5), (0,1,8,9), (0,2,4,6), (0,2,8,10), (0,4,8,12)\}$ .

This three Lemmas leads to the following important result.

Theorem 2.1: We can find all the partners to recognize the incoming subcubes  $Q_k$  from the link list table of  $Q_n$ .

#### 2.3 Maximality of Subcube Recognition

In this section we propose a new strategy that outperforms the buddy system by a factor of  ${}_{n}C_{k}$ , the gray strategy by a factor of  ${}_{n}C_{k}/2$  and Al-Dhelaan [8] by  ${}_{n}C_{k}/(k(n-k)+1)$  in recognizing subcubes of size k in  $Q_{n}$ . Now we are considering how many ways to recognize the subcubes for the incoming jobs.

**Lemma 2.4:** Total number of subcubes of  $Q_n$  to recognize subcubes of size k for incoming  $2^k$  jobs are  $\sum\limits_{j=0}^{n-k} {}_nC_{n-j} {}_{n-j}C_k$ .

proof: According to Lemma 2.2, there are  ${}_{n}C_{k}$  ways to recognize subcubes of size k. The number of link, r, at each address is the same as the number of 0's in the table index. The number, j, of 0's distribution in  $Q_{n}$  is  ${}_{n}C_{j}$  where  $0 \le j \le n$ . In order to recognize the size k, j must be equal or greater than k. So, the total number of subcubes of  $Q_{n}$  to recognize subcubes of size k is  $\sum_{i=0}^{n-k} {}_{n}C_{n-j} {}_{n-j}C_{k}$ .

For example, we have the following 0's distribution in Q4.

$$4C_0 = 1$$

$4C_1 = 4$   $4C_2 = 6$   $4C_3 = 4$   $4C_4 = 1$

So there are 1 four 0, 4 three 0, 6 two 0, 4 one 0, 1 zero 0. When we examine the Table 2.1, we have 1 4-links, 4 3-links, 6 2-links, 4 1-link 1 0-link. According to Lemma 2.4, the total number of subcubes to recognize the incoming  $2^2$  processors in  $Q_4$  is  $4C_4$   $4C_2$  +  $4C_3$   $3C_2$  +  $4C_2$   $2C_2$  = 24

Lemma 2.5: All the subcubes generated by the new approach are disjoint among themselves.

*proof:* We choose every combination in each table index and then find the partner according to the combination. partner(table\_index,p) will search different value every time, since every combination gives different table\_index and p. Thus, all the subcubes are disjoint.

These Lemmas 2.4 and 2.5 lead to the following important result.

Theorem 2.2: Total number of subcubes generated by Lemma 2.4 are maximum.

**Proof:** The number of distinct subcubes are  ${}_{n}C_{k}2^{n-k}[3]$ .

Therefore we can prove  ${}_{n}C_{k}2^{n-k} = \sum_{i=0}^{n-k} {}_{n}C_{n-j} {}_{n-j}C_{k}$ .

$$\begin{split} \sum_{j=1}^{n-k} & C_{n-j} \, {}_{n-j} C_k = \sum_{j=0}^{n-k} \, \frac{n!}{i!(n-i)!} \, \frac{(n-i)!}{k!(n-i-k)!} \\ & = \sum_{j=0}^{n-k} \, \frac{n\,!}{k!} \, \frac{1}{j!(n-j-k)!} \\ & = \frac{n!}{k!(n-k)!} \, \sum_{j=0}^{n-k} \, \frac{(n-k)!}{j!(n-j-k)!} \\ & = {}_{n} C_k \, \sum_{j=0}^{n-k} \, \frac{(n-k)!}{j!(n-j-k)!} \end{split}$$

We have the binomial theorem as follows.

$$(a+b)^{n} = \sum_{j=0}^{n} {}_{n}C_{j} a^{n-j}b^{j}$$

$$2^{n-k} = \sum_{j=0}^{n-k} {}_{n-k}C_{j} = \sum_{j=0}^{n-k} \frac{(n-k)!}{j!(n-j-k)!}$$

Therefore,  ${}_{n}C_{k}2^{n-k} = \sum_{j=0}^{n-k} {}_{n}C_{n-j} {}_{n-j}C_{k}$

Here is the example of Q<sub>2</sub> in Q<sub>4</sub>, which shows 24 subcubes.

$$(5,7,13,15)$$

$(6,7,14,15)$   $(8,9,10,11)$   $(8,9,12,13)$

$$(8,10,12,14)$$

$(9,11,13,15)$   $(10,11,14,15)$   $(12,13,14,15)$

The number of subcubes recognizable by each of the four strategies is presented in Table 2.2, especially for 2<sup>2</sup> incoming jobs in Q<sub>4</sub>.

|                            | $Q_0$          | $Q_{\mathbf{k}}$                | Qn |

|----------------------------|----------------|---------------------------------|----|

| Number of distinct subcube | 2 <sup>n</sup> | ${}_{n}C_{k}2^{n-k}=24$         | 1  |

| The Buddy strategy         | 2n             | $2^{\mathbf{n}-\mathbf{k}} = 4$ | 1  |

| The Gray Code strategy     | 2 <sup>n</sup> | $2^{n-k+1} = 8$                 | 1  |

| Ref[8]                     | 2 <sup>n</sup> | $(k(n-k)+1)2^{n-k} = 20$        | 11 |

| The New strategy           | 2 <sup>n</sup> | $_{n}C_{k}2^{n-k}=24$           | 1  |

Table 2.2 The number of subcube recognizable by the Buddy, Gray, Al-Dhelaan[8] and New strategy.

#### 2.4. A New Method To Allocate Processors

Node processors in an n-cube multiprocessor must be allocated to incoming tasks in order to maximize processor utilization and minimize system fragmentation. First we will briefly describe the known methods, the buddy strategy and the Gray strategy[3,8] and the one described in ref[8]. Then we can describe the new processor allocation strategy which outperforms the above three strategies. An example of the buddy, Gray, Al-Dhelaan[8] and the new strategies is given in Table 2.3.

#### A. The Buddy Strategy

Since there are  $2^n$  processor node in a  $Q_n$ ,  $2^n$  allocation bits are used to keep track of the availability of all the nodes. An allocation bit with value 0 (1) is available (not available). The buddy strategy consists of two parts, processor allocation and processor relinquishment. The algorithm is given below.

#### Processor allocation:

Step 1 : Set k to the dimension of a subcube required to accommodate the request.

Step 2 : Determine the least integer  $\alpha$ ,  $0 \le \alpha \le 2^{n-k+1}-1$  such that all the  $\beta$ th allocation bits are 0's where  $\alpha 2^k \le \beta \le (\alpha+1)2^k-1$ .

Set all these bits to 1's.

Step 3 : Allocate processors with address  $B_n(\beta)$  to the request, where  $\alpha 2^k \le \beta \le (\alpha+1)2^{k-1}$ .

#### Processor Relinquishment:

Reset every pth allocation bits to 0, where B<sub>n</sub>(p) is used in the subcube released.

This strategy can be explained by the completely binary tree. The level where the root node resides is numbered 0, and the nodes in level i are associated with subcubes of dimension n-i. When a  $Q_k$  is needed, the buddy strategy searches for a region of allocation bits with 0's whose addresses start with an integral multiple of  $2^k$ .

## B. The Grav Strategy

Similar to the buddy strategy, the GC strategy can also be described by the following two parts[3,8].

#### Processor allocation:

Step 1: Set k to the dimension of a subcube required to accommodate the request.

Step 2: Determine the least integer a,  $0 \le a \le 2^{n-k+1}-1$  such that all the (b mod  $2^n$ )th allocation bits are 0's, where  $a2^{k-1} \le b \le (a+2)2^{k-1}-1$ .

Set all these bits to 1's.

Step 3 : Allocate processors with address  $G_n(b \mod 2^n)$  to the request, where  $a2^{k-1} \le b \le (a+2)2^{k-1} - 1$ .

#### Processor Relinquishment:

Reset every pth allocation bits to 0, where  $G_n(p)$  is used in the subcube released.

This strategy also can be explained by the complete binary tree. This strategy recognizes  $2^{n-k+1}Q_k$  within the n-cube multiprocessor and this is an improvement by a factor of two over the buddy strategy.

#### C. Al-Dhelaan[8]

The path from the root of the tree to any node is that node's address. This address corresponds to the subcube which consists of all the descendents processors (leaf node). Note that in Q<sub>4</sub> subcube 01, 01X or 01XX denotes the same subcube. Before describing the algorithms some definitions are stated first.

<u>Definition</u>: The  $\alpha$ th partner of  $a_{k-1}, a_{k-2}, \ldots a_{\alpha+1}, a_{\alpha}, a_{\alpha-1}, \ldots a_0$  for any  $0 \le \alpha \le k-1$  is defined as

$$a_{k-1}, a_{k-2}, \dots a_{\alpha+1}, a_{\alpha}, a_{\alpha-1}, \dots a_{0},$$

if  $a_{\alpha} = 0$  undefined if  $a_{\alpha} = 1$ .

The pth partner of  $B_k(i)$  is defined as  $B_k(i)$ .

<u>Definition</u>: For any integer a, 0≤a≤2<sup>n-k+1</sup>-1, the node B<sub>n-k+1</sub>(a) is free if and only if all of its descents are free. For example, for n=4 and k=2, the node 000 is free if and only if the processors 0000, 0001 are free.

#### Processor allocation:

Step 1 : Set k to the dimension of a subcube required to accommodate the request.

Step 2: Determine the least integer  $\alpha$ ,  $0 \le \alpha \le 2^{n-k+1}-1$  such that  $B_{n-k+1}(\alpha)$  is free and it has a pth partner  $B^p_{n-k+1}(\alpha)$  which is also free where  $0 \le p \le n-k$ . Take p as small as possible.

Step 3: Allocate these processors to the request and set their allocation bits to 1.

#### Processor Relinquishment:

Reset the allocation bits of all the processors that correspond to the descendents of the nodes  $B_{n-k+1}(a)$  and  $B_{n-k+1}(a)$  to 0.

This strategy can recognize (n-k+1)2<sup>n-k</sup> Q<sub>k</sub> cubes.

#### D. A New Strategy:

In this section we present a very efficient processor allocation strategy which makes larger contiguous spaces for the new coming job than buddy, Gray strategy and Al-Dhelaan[8] do. This is a significant improvement because in practical system it is normal to have many small incoming jobs and large number of processors. Furthermore, this new strategy is suitable for static as well as dynamic processors allocation and it results in a less fragmentation and higher fault tolerance.

The new strategy can be described by the following two parts.

#### **Processor Allocation:**

Step 1 : Set k := |Ij|, where |Ij| is the dimension of a subcube required to accommodate the request Ij.

Step 2: Get one possible link combination(in order) in the link table and Find the partner processors

Check if those processors are available or not

If operation succeed then go to step 3

else go to step 2

Step 3. Allocate nodes.

#### Processor Relinquishment:

Reset every allocation nodes.

This allocation strategy is different from 3 strategies mentioned earlier. Though all three strategies can be explained by the binary tree, tree structure may not express all the link connections in the n-cube. So, instead of using tree structure, we allocate the processors for the incoming job using index scheme from the link table.

Because of its enhanced subcube recognition ability, the new strategy can allocate subcubes more densely at one end, thus making larger subcubes available at the other end for future use. An allocation strategy is said to be statically optimal if a  $Q_n$  using the strat-

egy can accommodate any input request sequence  $\{I_i\}$  iff  $\sum_{j=1}^k 2^{|I_i|} \le 2^n$ , where  $|I_i|$  is the subcube dimension required by request  $I_i$ . The buddy and Gray strategies are statically optimal[4]. Also the new strategy is statically optimal.

#### **Theorem 2.3:** The new strategy is statically optimal.

An example of the buddy, Gray, Al-Dhelaan[8] and the new strategies is given in Table 2.3 where the input sequence is as follows.

$$I_1=Q_0$$

$I_3=Q_0$   $I_5=Q_1$   $I_7=Q_0$   $I_2=Q_2$   $I_4=Q_0$   $I_6=Q_2$   $I_8=Q_1$

| # Buddy sy | ystem C           | ray system        | Ref[8]              | New system          |

|------------|-------------------|-------------------|---------------------|---------------------|

| 0. 0000    | $\cdot I_1$ 0     | 000I <sub>1</sub> | 0000 I <sub>1</sub> | 0000I <sub>1</sub>  |

| 1. 0001    | ·I <sub>3</sub> 0 | 001I <sub>3</sub> | 0001 I <sub>3</sub> | 0001I <sub>2</sub>  |

| 2. 0010    |                   | 011I <sub>2</sub> | 0010 I <sub>2</sub> | 0010I <sub>3</sub>  |

| 3. 0011    |                   | 010I <sub>2</sub> | 0011 I <sub>2</sub> | 0011I <sub>2</sub>  |

| 4. 0100    |                   | 110I <sub>2</sub> | 0100 I <sub>4</sub> | 0100I <sub>4</sub>  |

| 5. 0101    | $-I_2$ 0          | 111I <sub>2</sub> | 0101 I <sub>5</sub> | 0101I <sub>2</sub>  |

| 6. 0110    |                   | 101I <sub>4</sub> | 0110 I <sub>2</sub> | 0110I <sub>5</sub>  |

| 7. 0111    | $-I_2$ 0          | 100I <sub>5</sub> | 0111 I <sub>2</sub> | 0111 I <sub>2</sub> |

| 8. 1000    | ~                 | 100I <sub>5</sub> | 1000 I <sub>6</sub> | 1000I <sub>6</sub>  |

| 9. 1001    |                   | 101I <sub>7</sub> | 1001 I <sub>6</sub> | 1001I <sub>6</sub>  |

| 10 1010    |                   | 111I <sub>6</sub> | 1010 I <sub>6</sub> | 1010I <sub>6</sub>  |

| 11 1011    | -I <sub>8</sub> 1 | 110I <sub>6</sub> | 1011 I <sub>6</sub> | 1011I <sub>6</sub>  |

| 12 1100    | -I <sub>6</sub> 1 | 010I <sub>6</sub> | 1100 I <sub>7</sub> | 1100I <sub>7</sub>  |

| 13 1101    | -I <sub>6</sub> 1 | 011I <sub>6</sub> | 1101 I <sub>5</sub> | 1101I <sub>8</sub>  |

| 14 1110    | ·I <sub>6</sub> 1 | 001I <sub>8</sub> | 1110 I <sub>8</sub> | 1110I <sub>5</sub>  |

| 15 1111    | -I <sub>6</sub> 1 | 000I <sub>8</sub> | 1111 I <sub>8</sub> | 1111I <sub>8</sub>  |

Table 2.3 Comparison among 4 different allocation strategies

It can be observed that the new strategy outperforms the buddy strategy, the GC strategy and Al-Dhelaan[8] in the first-fit search and will pack incoming request more densely, thus making larger contiguous regions available than the buddy strategy, the GC strategy and Al-Dhelaan[8] can.

The subcube recognition problems becomes more important when considering some faulty processors. In these situations the new strategy does better than the above strategies as illustrated in the following example.

Example: (Fault tolerance)

In a 4-cube multiprocessor if two nodes, one from (0000, 0001) and the other from (1000, 1001) are faulty. Then neither the buddy system allocation strategy nor Gray code strategy will be able to satisfy the requests  $\{I_1=Q_3, I_2=Q_2\}$  but new strategy will satisfy this. When (0000, 1000) are faulty, (1,3,5,7,9,11,13,15) for  $Q_3$  and (4,6,12,14) for  $Q_2$  are assigned.

When processor relinquishment is taken into account, the buddy strategy and the GC strategy is shown to be poor in recognizing the availability of subcubes in the n-cube multiprocessor, and the processor utilization is thus degrade. But the new strategy does better than those strategies as illustrated in the following example.

Example: (Dynamic allocation)

Consider the request  $\{I_1=Q_1, I_2=Q_2, I_3=Q_1, I_4=Q_3\}$ . Let processors  $\{0,1\}$  and Processors  $\{4,5\}$  be allocated for  $I_1$  and  $I_3$ , respectively. If  $I_1$  and  $I_3$  released their processors and others do not then using the buddy system strategy or the Gray code strategy a request like  $\{I_5=Q_2\}$  will not be satisfied. But new strategy will combine the two released  $Q_1$ s into a  $Q_2$  and allocate it to  $I_5$ . When  $I_1$  and  $I_3$  released their processors, we can allocate  $\{0,1,4,5\}$  for  $\{I_5=Q_2\}$ .

#### 2.5 Analysis of Algorithm

In this section we describe the algorithm explained in previous sections. In sequential version of our algorithm, we get  $O(2^k * {}_{n}C_k \ 2^{n-k})$  time complexity. A formal description of our algorithm as follows.

```

Algorithm allocation;

(tindex=0; tindex<2subcubes; tindex++)

get_combination(Qn, Qk, tindex);

get_combination(Qn, Qk, tindex)

find all kinds of combination in tindex-th row in the link table;

(i=0; i<rlink; i++) /* rlink is the number of links in the table index */

index=0:

find_one_cube(0, tindex, n);

find_one_cube(pos,tindex, size) /* find the partners */

if (pos <size) {

if (pos == 0) {

path[index] = table[tindex][temp[pos]].no;

if (table[path[index]][0] == ON)

return(FAILURE);

index++;

if (index== exp(subcubes))

/* print result when one cube is found */

print path;

return(find_one_cubes(pos+1,tindex,size);

}

else {

path[index] = table[tindex][temp[pos]].no;

if (table[path[index]][0].duty == ON)

return(FAILURE);

index++;

if(find_one_cube(0,table[tindex][temp[pos]].no, pos) == SUCCESS)

return(find_one_cube(pos+1,tindex,size));

else

return(FAILURE);

}

}

```

It can be parallelized resulting in  $O({}_{n}C_{k})$  time complexity as shown below. A further advantage of our parallel allocation algorithm is that they are dynamic and require

little storage. The algorithm is shown in c style with added constructs, "par" and "seq" like those of the parallel language Occam. Here is the parallel version of our algorithm.

```

par (tindex=0;tindex<2^n; tindex++)

get_combination(Qn, Qk, tindex);

get_combination(Qn, Qk, tindex)

sea

find all kinds of combination in tindex-th row in the link table:

par (i=0; i< rlink; i++) /* rlink is the number of links in the table index */

index=0;

find_one_cube(0, tindex, combination);

/* find the partners */

find_one_cube(pos,tindex, size)

par

seq

path[index] = table[tindex][temp[pos]].no;

index++;

if (index== Q_k2)

print path;

/* print result when one cube is found */

par(pos=1;pos<size;pos++1)</pre>

path[index] = table[tindex][temp[pos]].no;

index++:

find_one_cube(table[tindex][combination[pos].no],pos);

```

#### 2.6 A New Approach to Task Migration

Even though enough number of hypercube nodes are available for the incoming job, allocation and deallocation of subcube usually result in a fragmented hypercube. That is, they don't form the recognizable subcube to accommodate an incoming job. The fragmentation problem in a hypercube can be solved by task migration, i.e., relocating tasks within the hypercube to remove the fragmentation.

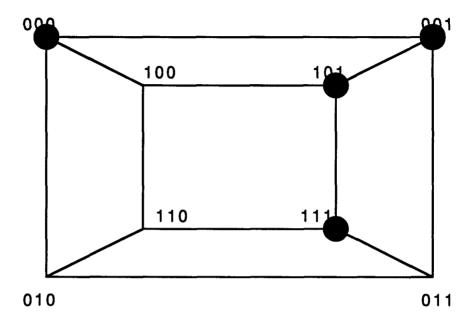

Fig. 2.3 shows an example of a fragmented hypercube where four available nodes {010,011,110,100} can't form a Q<sub>2</sub> to be used: thus, when a task requiring a Q<sub>2</sub> arrives, it has to be either queued or rejected.

Fig. 2. 3 An example of hypercube fragmentation

Such fragmentation leads to poor utilization of hypercube nodes, thus limiting the improvement achieved by the new strategy. Fragmentation problem in conventional memory allocation can be handled by memory compaction. Also the fragmentation problem in a hypercube can be solved by *task migration*[4], i.e., relocating active tasks and compacting those within the hypercube at one end in order to make enough subcubes available for the incoming request. There is a close relationship between allocation strategy used and task migration, because active tasks must be relocated to where allocation strategy can recognize.

A collection of occupied subcubes is called a configuration. We first find the goal configuration so that a given fragmented hypercube must change its position by relocating

active tasks. When a task is allocated to a subcube, the portion of the task located at each hypercube node of this subcube is called a *task module*[4].

A moving step is called H(source node, neighboring node) = 1. The cost of each task migration is then measured in terms of Hamming distance required while task migrations between different pairs of source nodes and destination nodes are performed in parallel. In order to move tasks in parallel, it is very important to avoid deadlock during task migration.

We formulate the node-mapping between each pair of source and destination node in such a way that the Hamming distance(source,destination) is minimized and develop a routing algorithm for shortest deadlock-free paths for task migration.

We assume that the hardware of the hypercube system under consideration is designed in such a way that each hypercube node has separate input and output ports. So, each node can receive a task module while sending another task module to its next hop. One time unit is defined as each moving step which will take the same amount of time.

In the following section we shall determine the goal configuration, the node-mapping between the source and destination subcubes, and shortest deadlock-free paths for task migration.

#### A. Determination of Goal Configuration

Since task migrations between different pairs of source nodes and destination nodes are performed in parallel, it is very important to avoid any deadlock during the migration. A deadlock might occur if there is a circular wait among nodes. To prevent this, a linear ordering of hypercube nodes is established in such a way that a node with address  $G(B_n(p))$  sends its task module to another node with address  $G(B_n(q))$  if and only if p>q. Thus, we can avoid the any circular wait. The goal configuration without fragmentation can be determined by the allocation algorithm developed in section IV.

Given a configuration of occupied subcubes, we do the following steps.

step 1: Label each task in the availability list with a distinct number

step 2: Relocate all tasks according to an increasing order of their labels.

We can compare the goal configuration without fragmentation between Ref[4] and the new strategy developed in Section 2.4 in Table 2.4.

| Gray strategy |        |        | New strategy |        |        |

|---------------|--------|--------|--------------|--------|--------|

| #             | Before | After  | #            | Before | After  |

| 0. 0000       |        | task 1 | 0. 0000      |        | task 1 |

| 1. 0001       |        | task 4 | 1. 0001      |        | task 2 |

| 2. 0011       | task 1 | task 2 | 3. 0010      | task 1 | task 3 |

| 3. 0010       |        | task 2 | 2. 0011      |        | task 2 |

| 4. 0110       |        | task 2 | 7. 0100      |        | task 4 |

| 5. 0111       |        | task 2 | 6. 0101      |        | task 2 |

| 6. 0101       | task 2 | task 3 | 4. 0110      |        | task 3 |

| 7. 0100       | task 2 | task 3 | 5. 0111      |        | task 2 |

| 8. 1100       | task 2 |        | 15. 1000     | task 2 |        |

| 9. 1101       | task 2 |        | 14. 1001     | task 2 |        |

| 10. 1111      |        |        | 12. 1010     | task 2 |        |

| 11. 1110      | task3  |        | 13. 1011     | task 2 |        |

| 12. 1010      | task3  |        | 8. 1100      | task 3 |        |

| 13. 1011      |        |        | 9. 1101      | task 3 |        |

| 14. 1001      | task4  |        | 11. 1110     |        |        |

| 15. 1000      |        |        | 10. 1111     | task 4 |        |

Table 2.4 Task migration under the GC strategy and New strategy

## B. Node mapping Between Source and Destination Node

After the goal configuration is determined, each active task will be moved from its source subcube to the destination subcube. The minimal number of moving steps required to move a task from one node to another node can be determined by Hamming distance between the two node locations.

We can define that the shortest distance between the source, p and destination, q subcube is the Hamming distance(p,q). The order of source in the new strategy is not necessarily the same as their corresponding destination nodes after the node-mapping. For example, if we have the same order between the source and destination node for task 2, we have the following node-mapping.

task 2: 1000 -> 0001,

$$H(p,q) = 2$$

; 1001 -> 0011,  $H(p,q) = 2$ ; 1010 -> 0101,  $H(p,q) = 4$ ; 1011 -> 0111,  $H(p,q) = 2$ ;

Therefore it will take 4 steps even though all moving can be done in parallel.

If we adjust the order in the goal configuration, we will reduce the steps. For example, we have a different following node-mapping.

task 2: 1000 -> 0001,

$$H(p,q) = 2$$

; 1001 -> 0101,  $H(p,q) = 2$ ; 1010 -> 0011,  $H(p,q) = 2$ ; 1011 -> 0111,  $H(p,q) = 2$ ;

In this case all nodes have Hamming distance 2, resulting in 2 steps. Here, we want to use the Theorem developed in [4]. The node-mapping between two subcubes recognizable by the new strategy can be determined as follows: Suppose  $\alpha = a_n a_{n-1} \dots a_1$  is the source subcube and  $\beta = b_n b_{n-1} \dots b_1$  is the destination subcube. Let p and q be the dimension in which  $a_p \in \{0,1\}$  and  $b_p = *$  and  $a_q = *$  and  $b_q \in \{0,1\}$ .

Theorem 2.4[4]: Each source node  $u=u_nu_{n-1}...u_1 \in \alpha$  can be one-to-one mapped to a destination node  $w=w_nw_{n-1}...w_1 \in \beta$  in such a way that

when

$$i \neq p$$

,  $w_i = b_i$  if  $b_i \in \{0,1\}$ ,

$$u_i \text{ if } a_i = b_i = *,$$

when  $i = p$ ,  $w_p = u_p(\text{negate})$  if  $w_q = u_q$ ,

$$u_p, \qquad \text{if } w_q \neq u_q.$$

When modules of a task are migrated in parallel, the moving distance between two nodes is equal to the number of Hamming distance between the source and destination node of a task.

#### B. Determination of Shortest Deadlock-Free(SDF) Routing

Now we want to develop a routing method to move each task module from its source node to its destination node. In order to avoid deadlock, a linear ordering among hypercube nodes is needed such that each node can only move its task module to a node with a lower address. So, we give all the nodes the value of Gray code to corresponding to the original binary node.

If  $G_n(B_n(i))$  and  $G_n(B_n(j))$  are two nodes in a SDF path, then  $G_n(B_n(i))$  is ahead of  $G_n(B_n(j))$  in the path iff i>j.

For example,  $\{1111(10)->1101(9)->1100(8)->0100(7)\}$  is a SDF path in G4, whereas  $\{1111(10)->0111(5)->0101(6)->0100(7)\}$  is not.

Once the node-mapping between each pair of source and destination subcubes is determined, each source node appends to its task module the address of its destination node. Each node can then determine the next hop on which to route a task module by the algorithm below[4].

Step 1: Each node compares the destination address  $d=d_nd_{n-1}\dots d_1$  with its own address  $s=s_ns_{n-1}\dots s_1$  from left to right. Let the j-th and k-th dimensions be respectively the first and second dimensions in which they differ.

step 2: If  $\sum_{i=k}^{j-1} s_i$  is even then send the task module to a neighboring node along the

#### k-th dimension

else send the task module to a neighboring node along the j-th dimension.

For example, suppose the source node is  $B_4(15)=1111$  and the destination node is  $B_4(4)=0100$ , then j=4 and k=2. The next determined by above algorithm is  $B_4(13)=1101$  since  $\sum_{i=2}^3 s_i$  is odd. Then the next hop by the intermediate node  $B_4(13)=1101$  is  $B_4(1100)$

then final destination (0100). is reached. It can be verified that  $[1111(10) \rightarrow 1101(9) \rightarrow 1100(8) \rightarrow 0100(7)]$  is a SDF path.

## Theorem 2.5[4]: The path determined by above algorithm is SDF.

To illustrate the entire process of task migration, consider the fragmented configuration in Table 4. From above theorem, we obtain the goal configuration. By the node-mapping scheme developed above, we have 0001->0000 for task 1,1000->0001, 1001-> 0101, 1010->0011, 1011->0111 for task 2, 1100->0010,1101->0110 for task 3, 1111-> 0100 for task 4. The SDF routing can then determined by above algorithm as follows.

task 1: 0001-> 0000

task 2: 1000 ->1001->0001, 1001->1101-> 0101,

1010 ->0010->0011, 1011->1111-> 0111

task 3: 1100 ->0100-> 0110->0010, 1101-> 0101-> 0111->0110

task 4: 1111 ->1101->1100->0100

### 2.7 Half-Task Migration Under Processor Failure

One approach to achieve fault tolerance is to decompose the hypercube structure hierachially and add redundancy at several levels. This approach requires a global reconfiguration algorithm in which a global controller reconfigures a set of cross-bar switches. It also does not take full advantage of the available hardware because a given module at a specific level may be replaced by a spare module even when most of its components are functioning properly. Another approach to achieve fault tolerance where degraded performance is not allowed is to initially designate only some of the processors as active and designate the rest as spares that may cover for faulty processors. Such approach is only useful for applications that require a number of processors less than the number of processors in the available hypercube.

In this section we describe the half-task migration in the presence of faulty processors. The half-task migration is defined as follows: When  $2^k$  processors are allocated for the job in an n-cube, we can relocate active tasks from  $2^{k-1}$  processors to another  $2^{k-1}$  processors in order to continue the job in case of processors failure. Note that there is a strong dependence of half-task migration on the subcube allocation strategy used, since active tasks must be relocated in such a way that the availability of subcubes can be detected by the new allocation strategy.

The procedure can be done as follows: 1) determination of a goal configuration, 2) the node-mapping between the source and destination subcubes, and 3) determination of the shortest routing for moving half-task modules. This approach has the following advantages: 1) We don't have to have the extra processors to reconfigure[15]. 2) It is easy and efficient to reconfigure the processors if the alternatives are chosen.

We assume that the hardware of the hypercube system under consideration is designed in such a way that each hypercube node has separate input and output ports. So each node can receive a task module while sending another task module to its next hop. Each moving step will take the same amount of time and will be used to define one time unit.

### A. Goal configuration

When  $2^k$  processors are allocated for the job in an n-cube, we can relocate active tasks from  $2^{k-1}$  processors to another  $2^{k-1}$  processors so as to continue the job in case of processors failure. Given the configuration of  $2^{k-1}$  faulty subcubes, the goal configuration can be determined by the algorithm below. There are n-k alternatives for  $Q_k$  in  $Q_n$ .

# Algorithm A2: Determination of the goal configuration

A2: (tindex=0; tindex<2<sup>n</sup>; tindex++)

choose smallest tindex in Q<sub>k</sub>

get\_combination(Q<sub>n</sub>, Q<sub>k</sub>, tindex);

```

get_combination(Q<sub>n</sub>, Q<sub>k</sub>, tindex)

find every combination in tindex-th row in the link table;

(i=0; i< rlink; i++) /* rlink is the number of links in the table index */

index=0;

find_one_cube(tindex, Q<sub>k</sub>, combination);

find_one_cube(tindex,size, combination)

path[index] = table[tindex][combination[0]].no;

index++;

if ((index ==Q<sub>k</sub><sup>2</sup>) and (path is not faulty))

print path; /* print result when one cube is found and non-faulty */

(pos=1; pos<size; pos++)

path[index] = table[tindex][combination[pos]].no;

index++;

find_one_cube(table[tindex][combination[pos]].no,pos);

```

For example, processors  $\{0,1,4,5\}$  are allocated for task which requires  $Q_2$  in  $Q_4$ . Let processors  $\{4,5\}$  be faulty during execution. We can replace processors  $\{4,5\}$  with processors  $\{2,3\}$  or  $\{8,9\}$ . Thus we can have processors  $\{0,1,2,3\}$  or  $\{0,1,8,9\}$  in order to continue the job. We check processors  $\{2,3\}$  and  $\{8,9\}$  in sequence if they are available.

## B. Node-Mapping

After the goal configuration is determined,  $2^{k-1}$  processors will be moved from their source subcube to the destination subcube. The minimal number of moving steps required to move  $2^{k-1}$  processors location to another location is determined by the Hamming distance between the two subcube locations.

We have the following theorem for the minimal number of moving steps required to move a task from one subcube location to another.

<u>Theorem 2.6:</u> The order of source subcubes must be the same as their corresponding destination subcubes after node mapping.

**Proof:** Let  $a_1 \ a_2 \ a_3 \ \dots a_n$  be the  $2^{k-1}$  faulty source subcubes and  $b_1 \ b_2 \ b_3 \dots b_n$  be the alternative  $2^{k-1}$  destination subcubes and  $c_1 \ c_2 \ c_3 \ \dots c_n$  be the  $2^{k-1}$  remaining source subcubes. There are  $2^{k-1}$ ! ways to map from source subcube to the destination subcube. Here we can find  $H(a_1, c_1) = 2$ ,  $H(a_2, c_2) = 2$ ,  $H(a_n, c_n) = 2$ . Thus, in order to minimize the moving steps, we must have  $H(b_1, c_1) = 2$ ,  $H(b_2, c_2) = 2$ ,  $H(b_n, c_n) = 2$ . Therefore, we have to move the half-task in the same order as their corresponding destination subcubes. That is,  $a_1 \rightarrow b_1$ ,  $a_2 \rightarrow b_2 \ \dots \ a_n \rightarrow b_n$ .

Corollary 2.1: The maximum Hamming distance between source processor and destination processor in half-task migration is 2.

According to above theorem, we can choose only one way which minimizes the Hamming distance. For example, processors  $\{2,3,6,7,10,11,14,15\}$  are allocated for Q<sub>3</sub>. Assume that processors  $\{6,7\}$  are faulty during the execution. Then according to the goal configuration, we can find processors  $\{8,9,12,13\}$  available. Here we have  $2^{3-1}$ ! ways to map from processors  $\{2,3,6,7\}$  to  $\{8,9,12,13\}$ . If we choose 2->13, 3->9, 6->12, 7->8 respectively, then we have H(0010,1101)=4, H(0011,1001)=2, H(0110,1100)=2, H(0111,1000)=4. Therefore it will take 4 steps even though all moving can be done in parallel. But according to the above theorem, we have H(0010,1000)=2, H(0011,1001)=2, H(0110,1100)=2, H(0111,1101)=2. Thus, it will take only 2 steps.

#### C. Shortest Routing Procedure

Now we want to develop a routing method to move each half-task module from the source node to its destination node. Once the node-mapping between each pair of source and destination subcubes is determined, each source node appends to its task module the address of its destination node. Each node can then determine the next hop on which to route a half-task module by the algorithm below.

Step 1: Each node compares the destination address  $d=d_nd_{n-1}\dots d_1$  with its own address  $s=s_ns_{n-1}\dots s_1$  from left to right. Let the j-th and k-th dimension be respectively the first and second dimensions in which they differ.

Step 2: if the j-th dimension in the source processor is 0 then send the task module to a neighboring node along the j-th dimension else send it to a neighboring node along along the k-th dimension.

Theorem 2.7: The path determined by the above algorithm is the shortest safe-path. proof: Let  $a_1 \ a_2 \ a_j \ ... \ a_k \ ... \ a_n$  be the source subcubes and  $b_1 \ b_2 \ b_j \ ... \ b_k \ ... \ b_n$  be the destination subcubes. In corollary 2.1, we described that the maximum Hamming distance between source processor and destination processor is 2. Thus, when  $a_j$  is 0, we have to send the task along j-dimension.

For example, when processors  $\{0,1,4,5\}$  are assigned for  $Q_2$ , processors  $\{4,5\}$  are faulty during the execution. If we have half-task migration from processors  $\{4\}$  to  $\{2\}$  and  $\{5\}$  to  $\{3\}$  in the goal configuration, then we have 0100 -> 0110 -> 0010 and 0101 -> 0011. If we don't follow the above procedure, we may have 0100 -> 0000 -> 0010 and 0101 -> 0001 -> 001. Then we give unnecessary interrupt to processors  $\{0,1\}$ .

#### REFERENCES

- 1. K. Hwang and F.A. Briggs, Computer Architecture and Parallel Processing, New York: McGraw Hill, 1984

- 2. R. M. Chamberlain, "Gray codes, Fast Fourier Transformations and Hypercubes", Parallel Computing, 6, 1988, pp. 225-233.

- 3. M. Chen and K.G. Shin, "Processor Allocation in an N-cube Multiprocessor Using Gray Codes", IEEE Trans. Computer, Dec. 1987 pp. 1396-1407.

- 4. M. Chen and K.G. Shin, "Task Migration in Hypercube Multiprocessor", Proc. 16th Annual Int'l Symp. on Computer Architecture. Jun 1989, pp. 105-111

- 5. M. Chen and K.G. Shin, "Embedment of interesting task modules into a hypercube multiprocessor", in Proc. Second Hypercube Conf., Oct 1986, pp. 121-129

- 6. B. Becker and H.U. Simon, "How robust is the n-cube?", in Proc. 27th Ann. Symp. Foundations of Comp. Sci. Oct. 1986 pp. 283-291.

- 7. H. P. Kattesff, "Incomplete hypercubes", IEEE Trans. Computer, May 1988, pp. 604-608.

- 8. A. Al-Dhelaan and B. Bose, "A New strategy for Processor Allocation in an N-cube Multiprocessor", Phoenix Conference on Computer and Communication, Mar 1989. pp. 114-118.

- 9. A. Al-Dhelaan and B. Bose, "Efficient Fault Tolerant Broadcasting Algorithm for the Hypercube", Proc. The fourth Conf. on Hypercube Concurrent Comp. and Applications, Monterey, Mar 1989, pp. 123-128.

- 10. P. Ramanathan and K.G. Shin, "Reliable Broadcasting in Hypercube Multicomputers", IEEE Trans. on Comp. Dec 1988, pp 1654-1657.

- 11. Y. Saad and M.H. Schultz, "Topological Properties of Hypercubes", IEEE Trans. on Computer, Jul 1988, pp 867-872

- 12. J. E. Jang, S. W. Choi and W. K. Cho, "A New Approach to Processor Allocation and Task Migration in an N-cube Multiprocessor", Proceedings, International Conference on Supercomputing, Nov, 1989. pp. 314-325

- 13. J. E. Jang and W. K. Cho, "Maximality of Subcube Recognition and Fault Tolerance in an N-cube Multiprocessor", Proceedings, 4th SIAM conference on Parallel Processing for Scienctific Applications, Dec. 1989.

- 14. M. Sultan and Rami Melhem, "Fault Tolerance and Reliable Routing in Augmented Hyercube Architecture", Proc, 8th IEEE Phoenix Int'l Conference on Computer and Communication, Mar, 1989. pp. 19-23.

- 15. H. P. Kattesff, "Incomplete hypercubes", IEEE Trans. Computer, May 1988, pp 604-608.

- 16. Z. Kohavi, Switching and Finite Automata Theory, New York: McGraw-Hill, 1978

## Chapter 3

# An Optimal Fault-Tolerant Broadcasting Algorithm for a Hypercube Multiprocessor

#### 3.1 Introduction

Rapid advancing technology has made it possible for a large number of processing elements (PEs) to be interconnected together on a single chip as a viable means of implementing high performance integrated systems. A number of parallel architectures have been proposed, such as hypercubes, meshes, trees and cube-connected-cycles (CCC)[1-4]. Among them, hypercube multiprocessors have been drawing considerable attention due to their structual regularity for easy construction and high potential for the parallel execution of various algorithms. And its architecture allows high level of concurrency and efficiency. Numerous research efforts related to hypercube architectures, operating systems, etc., have been undertaken[5-15, 20-21].

Most of the research effort on hypercube architecture has focused on the fault-free situation. However, the increasing use of hypercube multicomputers for critical applications has made their fault tolerance an important issue. Efficient routing of message is a key to the performance of a multicomputer system. Especially, the increasing use of multicomputer systems for reliability-critical applications has made it essential to design fault-tolerant routing strategies for such systems. By fault-tolerant routing, we mean the successful routing of messages between any pair of non-faulty nodes in the presence of faulty components.

Broadcasting is an important means of communication among processors by which a processor can pass data or control to all other processors in the network. This operation is extremely important for diagnosis of the network, distributed agreement [16] or clock syn-

chronization[17]. Distributed agreement and clock synchronization can be achieved only if there is no faulty node to deliver the message in the system[16-17]. This, however, is not easy to achieve in the presence of faulty node/link because the faulty nodes can either omit, corrupt, reroute, or alter information passing through them.