### AN ABSTRACT OF THE THESIS OF

Darren W. Stevens for the degree of <u>Master of Science</u> in <u>Physics</u> presented on February 25, 1992.

Title : <u>The Design and Architecture of An Improved Microcomputer-Controlled</u> <u>Perturbed Angular Correlation Spectrometer</u> Redacted for Privacy

Abstract approved : \_\_\_\_\_

John A. Gardner

An improved, integrated perturbed angular correlation (PAC) spectrometer was designed, built and exhaustively tested. PAC spectroscopy is an experimental method used for probing the structure of materials. At the core of the technique is the experimental apparatus which is used in data collection. This work was undertaken in order to improve upon the existing data collection scheme by building an integrated, computer-controlled spectrometer that would be both easy to use and reliable, so that the focus of the user could be dedicated to the physics learned from the data and not committed to the problems associated with the collection of the data. Instead of redesigning the older, existing systems, a revolutionary new design was developed and implemented. An experimental run using room-temperature  $HfO_2$  as the sample and <sup>181</sup>Ta as the probe was performed to verify the operation of the system. Analysis of two different data sets from this run showed PAC frequencies that agreed with work done on the same material by other groups. The frequencies for the first data set were:

$$\omega_1 = 829 \pm 2 Mrad/s$$

$\omega_2 = 1447 \pm 5 Mrad/s$

and for the second data set were:

$$\omega_1 = 827 \pm 3 Mrad/s$$

$\omega_2 = 1448 \pm 5 Mrad/s$

The agreement between these two data sets and the favorable comparison of both of them to other published results indicates that the spectrometer is fully functional, although some problems associated with purchased components used in the system were discovered. The overall system performed well enough throughout extensive testing to be considered a successful venture and consequently the new system will be the basis for significant future development.

<sup>c</sup> Copyright by Darren W. Stevens February 25, 1992

All Rights Reserved

# The Design and Architecture of An Improved Microcomputer-Controlled Perturbed Angular Correlation Spectrometer

by

Darren W. Stevens

# A Thesis submitted to Oregon State University

in partial fulfillment of the requirements for the degree of

Master of Science

Completed February 25, 1992 Commencement June 1992 APPROVED:

**Redacted for Privacy**

Professor of Physics in charge of major

# Redacted for Privacy

Chairman of the Department of Physics

Redacted for Privacy

$\langle |$

Dean of the Graduate School

Date thesis is presented \_\_\_\_\_ February 25, 1992

Typed by Darren W. Stevens for \_\_\_\_\_ Darren W. Stevens

### ACKNOWLEDGEMENT

I would like to take this opportunity to thank the many people that have helped me on the long road to the completion of this project. First of all, I would like to thank my major professor, Dr. John A. Gardner, for introducing me to this interesting and challenging project and then helping me achieve the completion of such a complicated and detailed endeavor. I would also like to thank Walt Dillon for his many hours of electronics discussion and Tim Taylor for his help in pc-board etching.

I would also like to thank several people in my research group for the help at various points along the way, thanks to: Randy Lundquist for his help in writing the control program for the spectrometer and his writing of the astounding data analysis programs; Matthew Zacate for his extensive hardware help, his friendship, and his many conversations over Thai food; John Griffith for making the hafnium oxide sample that was used to verify the operation of the spectrometer; Eric Antonnissen for lending me the photomultiplier tube from his spectrometer when mine went kaput; Lisa Dundon for providing me with the numbers from old data that I needed for verification.

A couple of my close friends are also deserving of thanks for their friendship and support. Thanks to Neil Roberts for his encouragement at several trying times and to Scott Fuller for his friendship and the many trips to various places when I really needed a break. I would also like to thank the others in the physics department for making it an interesting place to be. I would also like to thank the good folks at Suds and Suds for the refreshing blasts of reality that I was able to squeeze in from time to time.

To my family, without whose support this project would have been an impossible task, I thank you for everything. Special thanks to mom and dad for financial and emotional support and much, much more. To my brother Dean, his wife Robin and their children Jennifer, Heather and Derrick, to my sister Linda and her husband Bob, to my sister Carol, her husband Barry and their children Emily and Brenton, I would like to say thanks for making my occasional trips home so wonderful. You are all very special to me! Darren W. Stevens, February 25, 1992

# TABLE OF CONTENTS

| 1. Introduction                                              | 1  |

|--------------------------------------------------------------|----|

| 1.1. Theory of perturbed angular correlations                | 1  |

| 1.2. Experimental perturbed angular correlation spectroscopy | 6  |

| 2. The design of the old spectrometer                        | 12 |

| 2.1. Overview                                                | 12 |

| 2.2. Data collection and analysis                            | 19 |

| 3. The architecture of the new spectrometer                  | 22 |

| 3.1. Overview                                                | 23 |

| 3.2. The STINTSET board                                      | 30 |

| 3.3. The Energy boards                                       | 34 |

| 3.4. The Brain board                                         | 37 |

| 3.5. The computer interface                                  | 39 |

| 4. Operation of the new spectrometer                         | 42 |

| 4.1. Procedure                                               | 42 |

| 4.2. Data analysis                                           | 46 |

| 5. The experimental verification                             | 50 |

| 6. Summary and conclusions                                   | 66 |

| 6.1. Comparison of design features                           | 68 |

| 6.2. Future considerations                                   | 69 |

|                                                              |    |

# APPENDICES

| A. | Some of the known PAC probes                                             | 74  |

|----|--------------------------------------------------------------------------|-----|

| B. | List of EPROM-based functions used to control<br>the VME-based boards    | 75  |

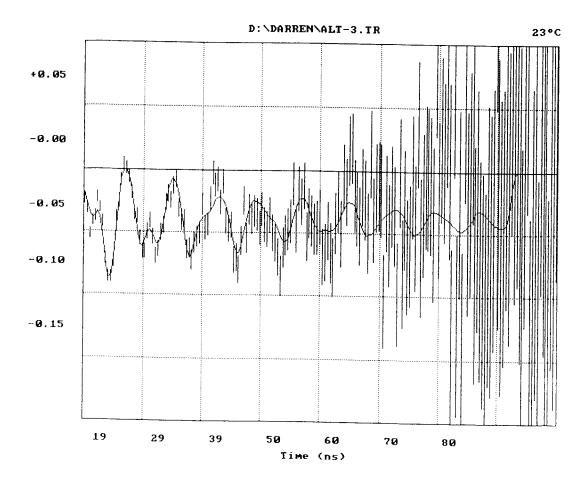

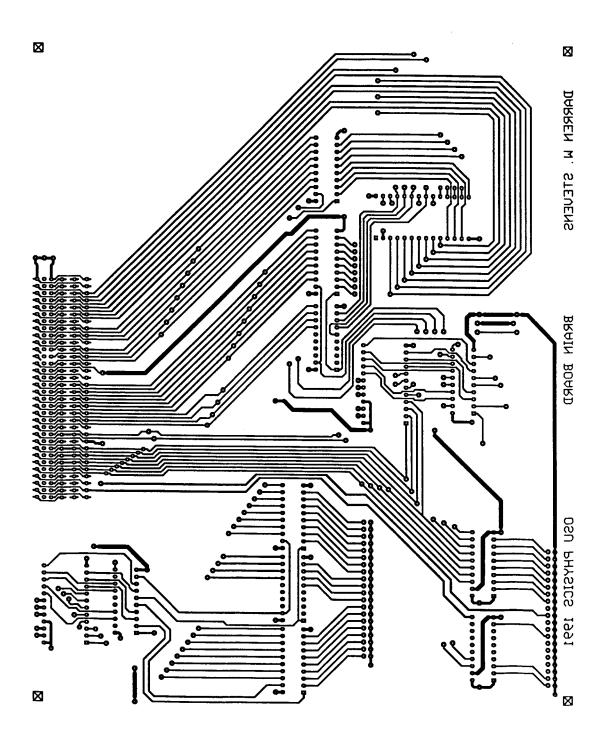

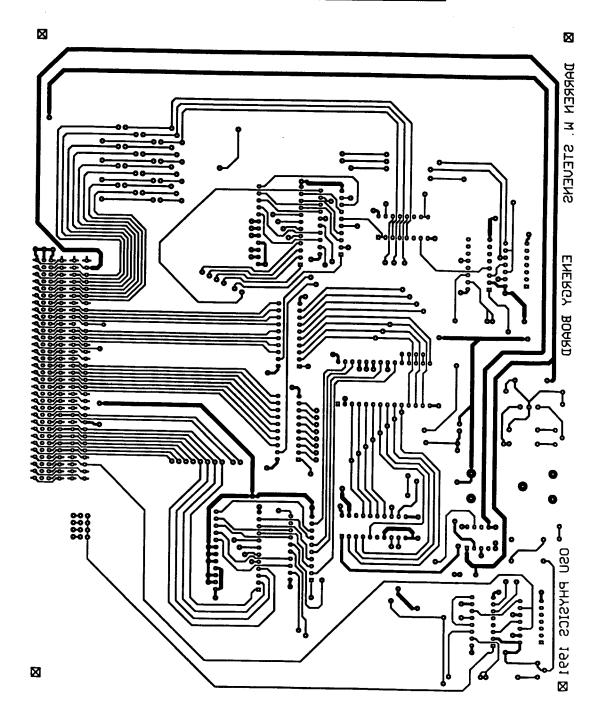

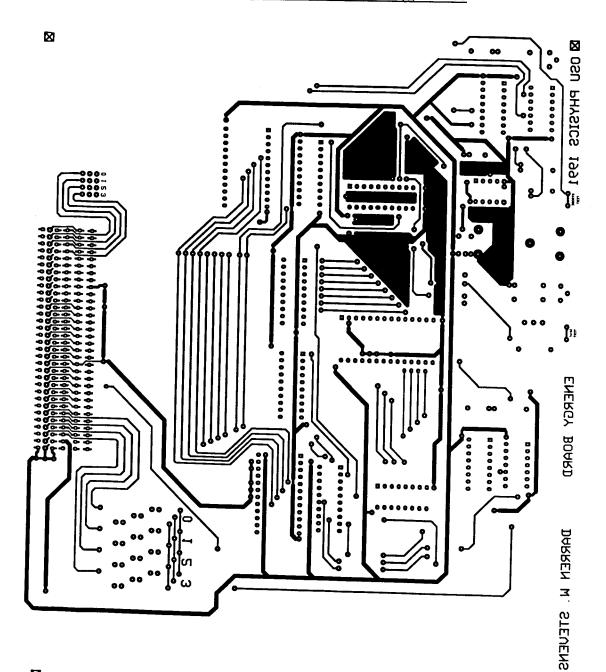

| C. | The PCB artwork used in the etching process (reduced from full-size)     | 86  |

| D. | Assembly language listing of the program VMEASS.ASM                      | 91  |

| E. | Listing of the QuickBASIC module SETWIND.BAS<br>(module of VMEMCA.BAS)   | 114 |

| F. | Listing of the QuickBASIC program READRAM.BAS<br>(a stand-alone program) | 125 |

# LIST OF FIGURES

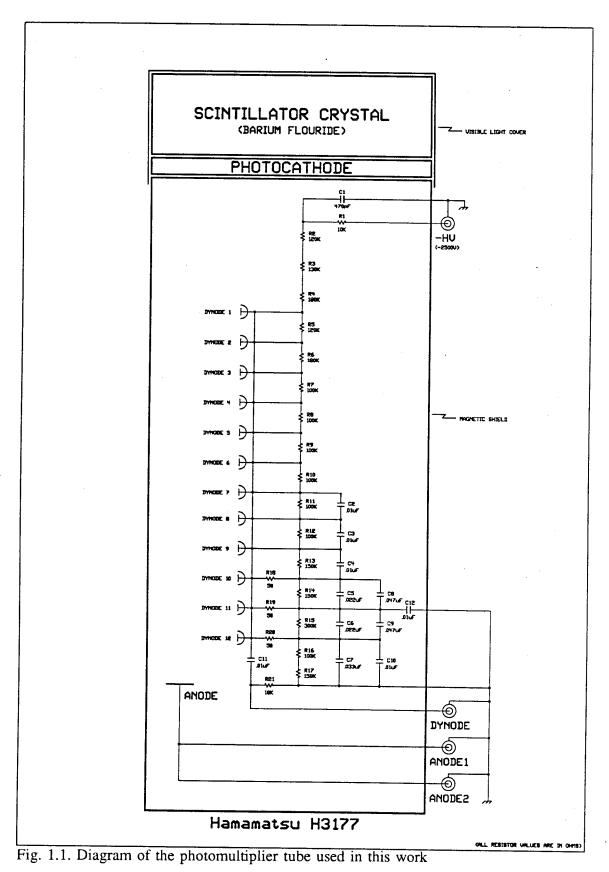

| 1.1. | Diagram of the photomultiplier tube used in this work                     | 8  |

|------|---------------------------------------------------------------------------|----|

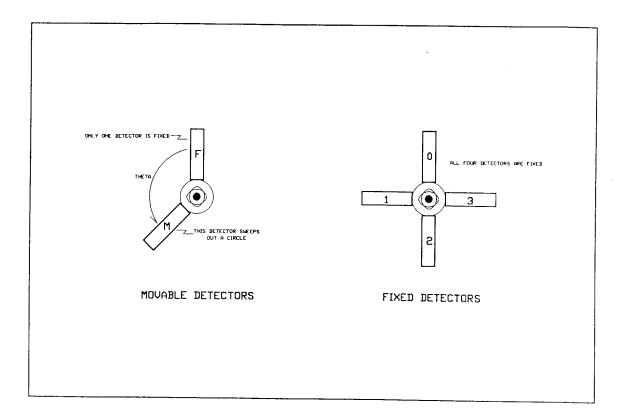

| 1.2. | Diagram of the different detector configurations used in PAC              | 11 |

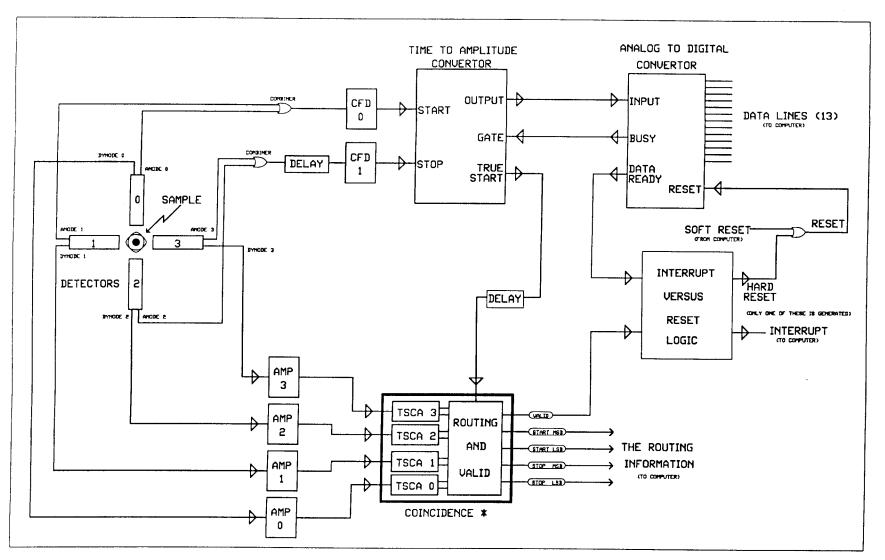

| 2.1. | Block diagram of the old spectrometer                                     | 13 |

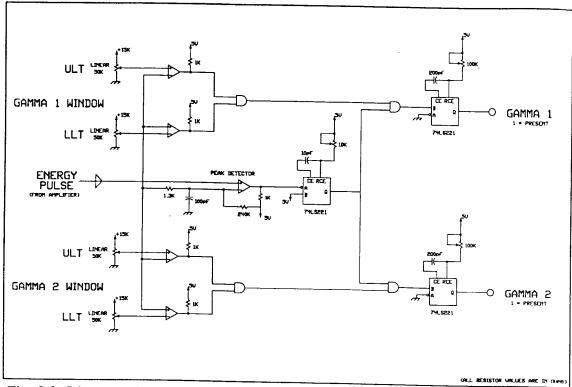

| 2.2. | Diagram of a single TSCA. There is a total of 4 of these,                 | 16 |

|      | one for each detector.                                                    |    |

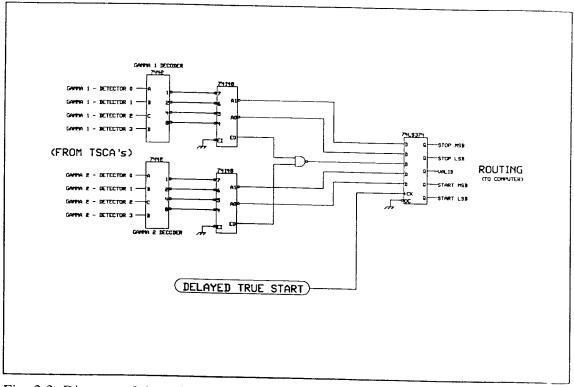

| 2.3. | Diagram of the coincidence section of the old spectrometer                | 16 |

| 3.1. | Block diagram of the timing section of the new spectrometer               | 24 |

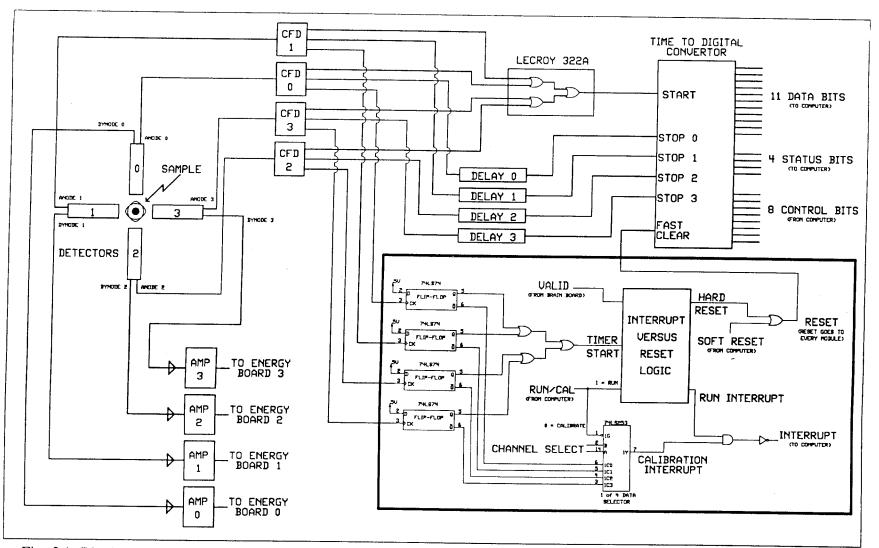

| 3.2. | Block diagram of the energy analysis section of the new spectrometer      | 27 |

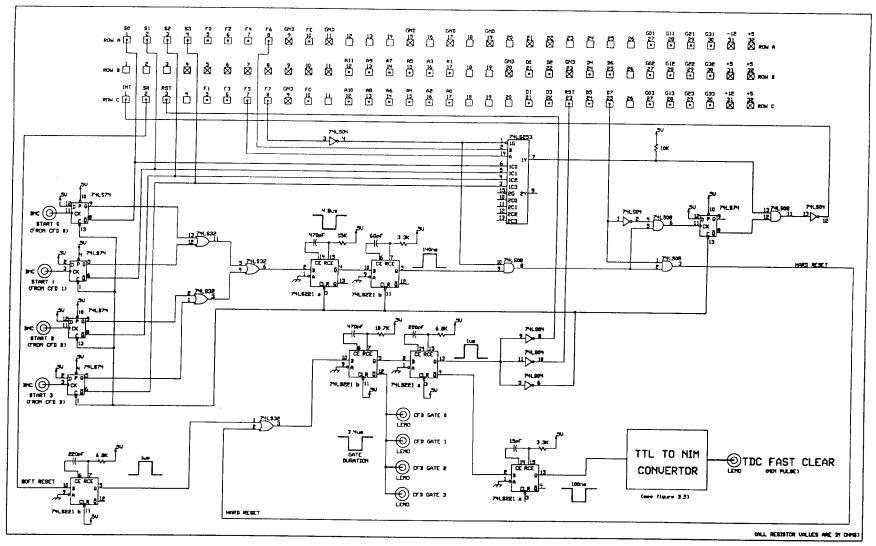

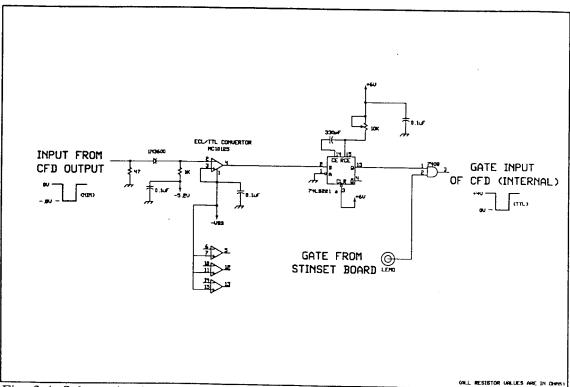

| 3.3. | Schematic diagram of the STINTSET board                                   | 31 |

| 3.4. | Schematic diagram of the modification made to the CFD's                   | 33 |

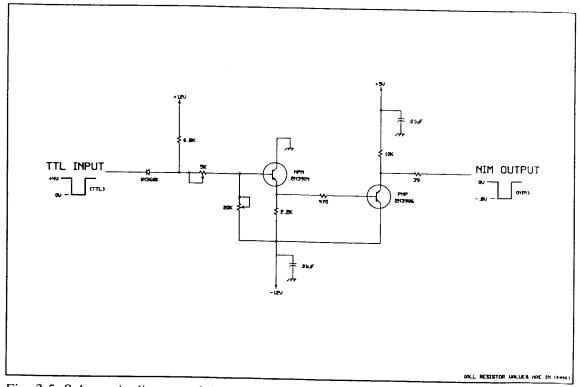

| 3.5. | Schematic diagram of the TTL-to-NIM conversion circuit                    | 33 |

|      | for the TDC fast clear                                                    |    |

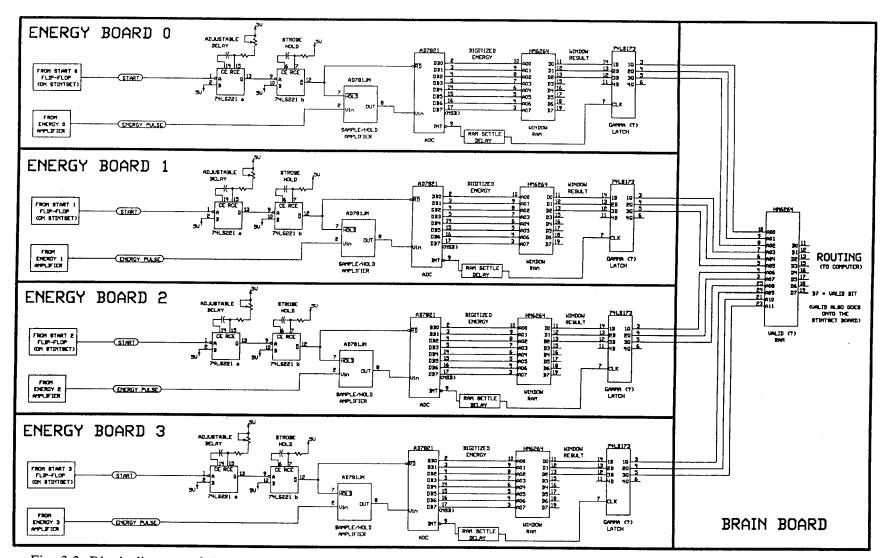

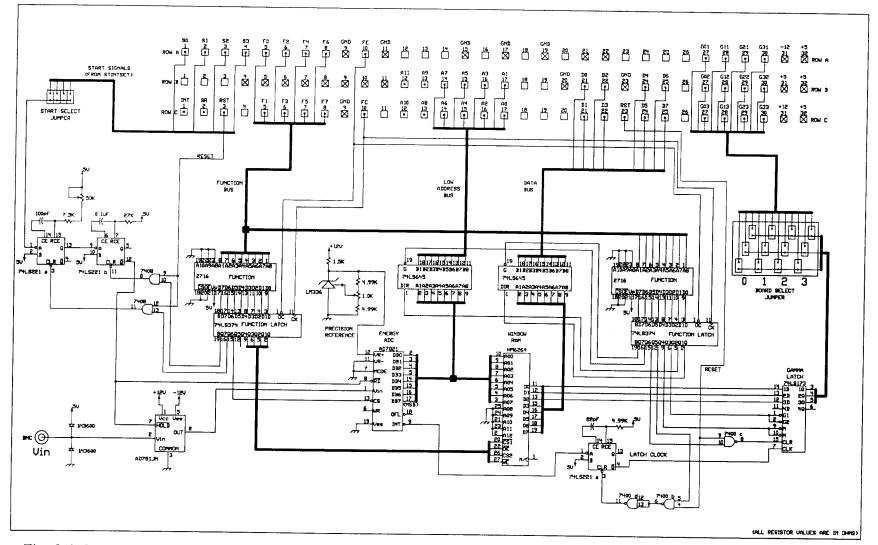

| 3.6. | Schematic diagram of the Energy boards                                    | 36 |

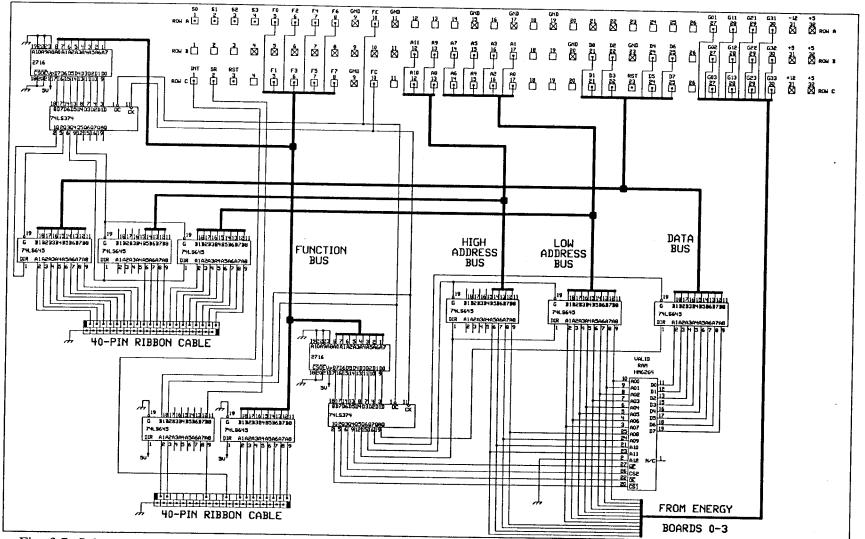

| 3.7. | Schematic diagram of the Brain board                                      | 38 |

| 3.8. | Block diagram of the computer interface board                             | 40 |

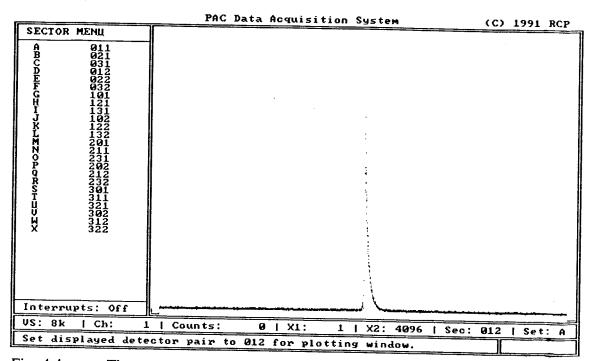

| 4.1. | The computer display as seen when starting the VMEMCA program             | 44 |

| 4.2. | A typical computer display as seen while using the VMEMCA                 | 44 |

|      | program to set windows                                                    |    |

| 4.3. | The computer display as seen when starting the VMEPAC program             | 45 |

| 4.4. | A typical computer display as seen while using the VMEPAC                 | 45 |

|      | program to collect data                                                   |    |

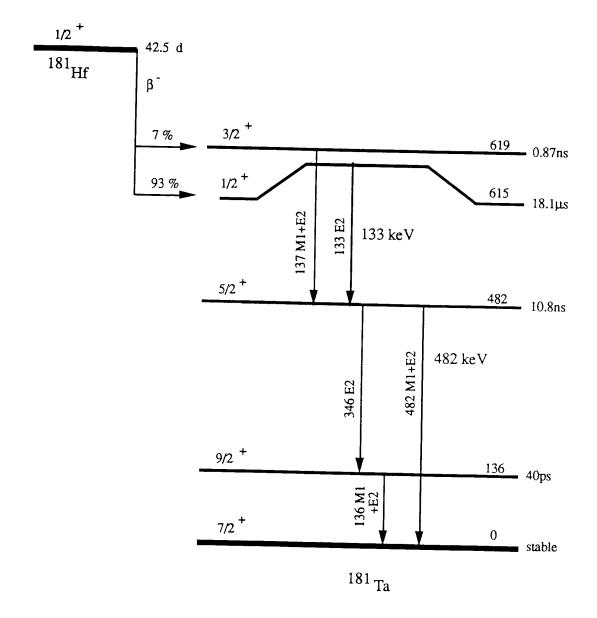

| 5.1. | The decay scheme for $^{181}$ Hf $\rightarrow ^{181}$ Ta                  | 51 |

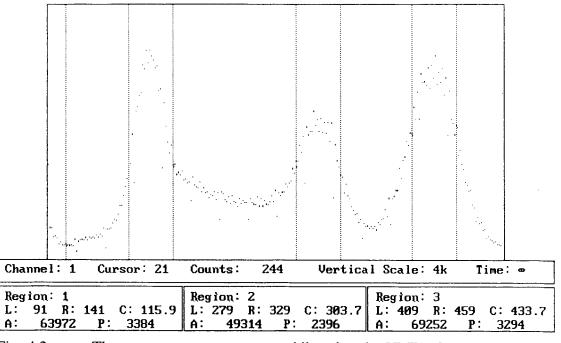

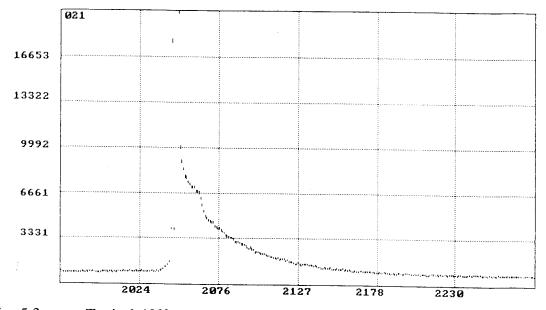

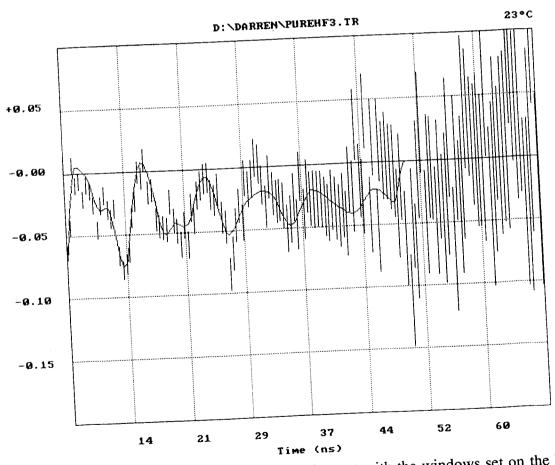

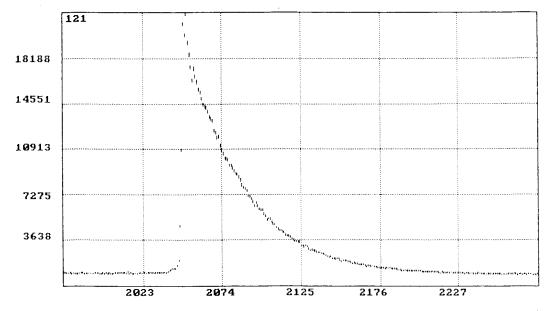

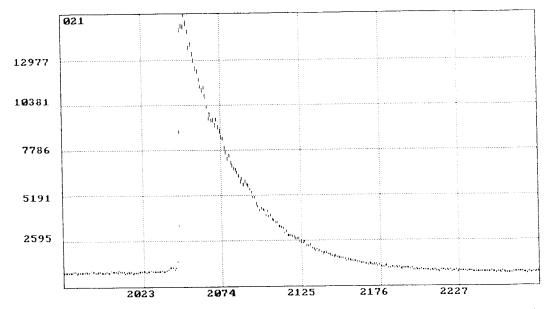

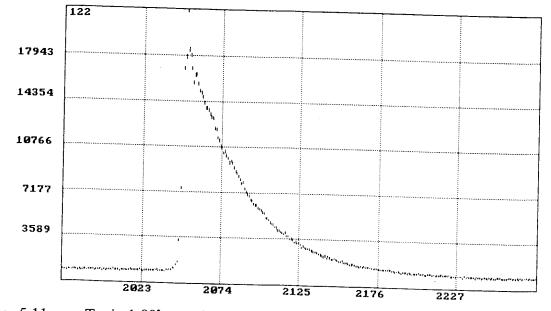

| 5.2. | Typical 90° raw data for a sector with the stop window set on the         | 53 |

|      | low energy stop gamma ray peak                                            |    |

| 5.3. | Typical 180° raw data for a sector with the stop window set on the        | 53 |

|      | low energy stop gamma ray peak                                            |    |

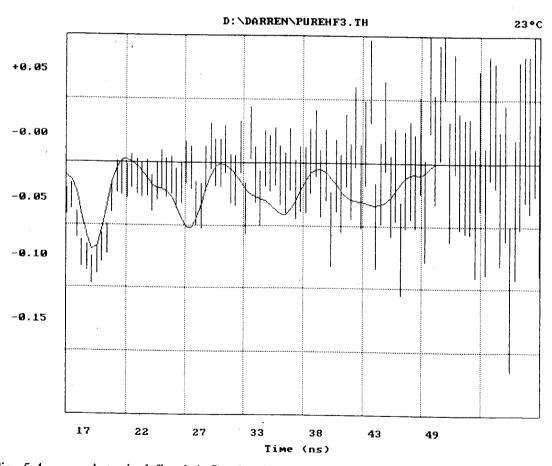

| 5.4. | A typical fitted $A_2G_2$ plot for a data set with the windows set on the | 54 |

|      | low energy stop gamma ray peak                                            |    |

|      |                                                                           |    |

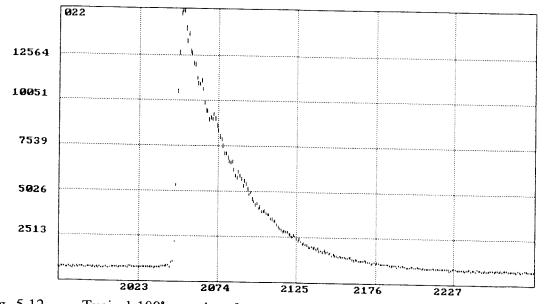

| 5.5.  | Typical 90° raw data for a sector with the stop window set on the         | 55 |

|-------|---------------------------------------------------------------------------|----|

|       | high energy stop gamma ray peak                                           |    |

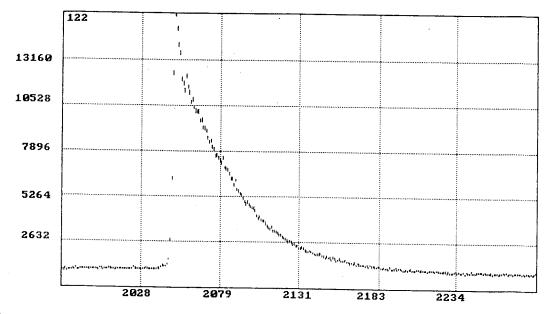

| 5.6.  | Typical 180° raw data for a sector with the stop window set on the        | 55 |

|       | high energy stop gamma ray peak                                           |    |

| 5.7.  | A typical fitted $A_2G_2$ plot for a data set with the windows set on the | 56 |

|       | high energy stop gamma ray peak                                           |    |

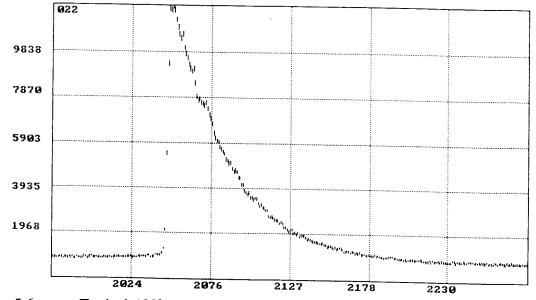

| 5.8.  | Typical 90° raw data for a sector with the stop window set on the         | 58 |

|       | lower half of the high energy stop gamma ray peak                         |    |

| 5.9.  | Typical 180° raw data for a sector with the stop window set on the        | 58 |

|       | lower half of the high energy stop gamma ray peak                         |    |

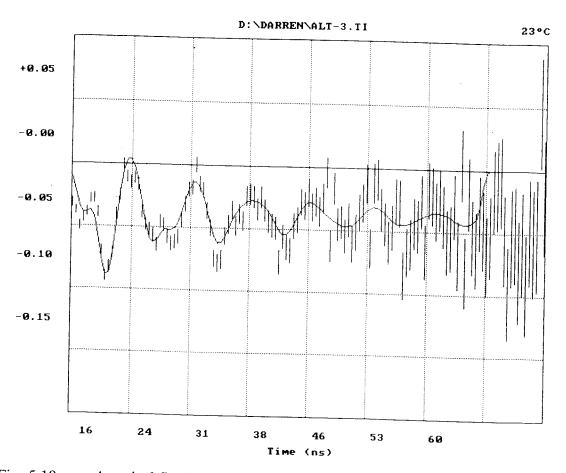

| 5.10. | A typical fitted $A_2G_2$ plot for a data set with the stop windows set   | 59 |

|       | on the lower half of the high energy stop gamma ray peak                  |    |

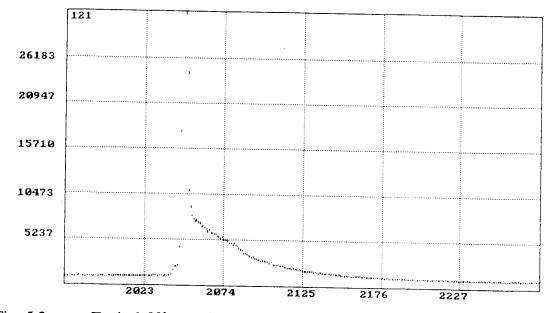

| 5.11. | Typical 90° raw data for a sector with the stop window set on the         | 60 |

|       | upper half of the high energy gamma ray peak                              |    |

| 5.12. | Typical 180° raw data for a sector with the stop window set on the        | 60 |

|       | upper half of the high energy gamma ray peak                              |    |

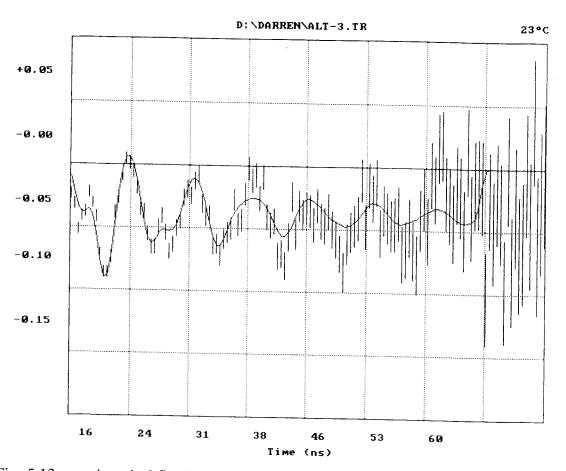

| 5.13. | A typical fitted $A_2G_2$ plot for a data set with the stop windows set   | 61 |

|       | upper half of the high energy stop gamma ray peak                         |    |

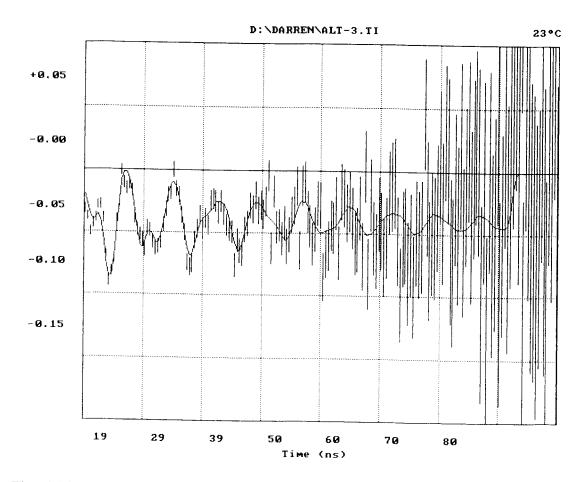

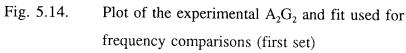

| 5.14. | Plot of the experimental $A_2G_2$ and fit used for                        | 64 |

|       | frequency comparisons (first set)                                         |    |

| 5.15. | Plot of the experimental $A_2G_2$ and fit used for                        | 65 |

|       | frequency comparisons (second set)                                        |    |

|       |                                                                           |    |

# LIST OF TABLES

| 2.1. | The raw data sectors for the old system                                | 21 |

|------|------------------------------------------------------------------------|----|

| 2.2. | The different $A_2G_2$ sets for the old system and how they are formed | 21 |

| 4.1. | The raw data sectors for the new system                                | 47 |

| 4.2. | The different $A_2G_2$ sets for stop window 1 and how they are formed  | 48 |

| 4.3. | The different $A_2G_2$ sets for stop window 2 and how they are formed  | 49 |

| 5.1. | Summary of the properties of <sup>181</sup> Ta                         | 52 |

# The Design and Architecture of An Improved Microcomputer-Controlled Perturbed Angular Correlation Spectrometer

### 1. Introduction

Perturbed angular correlation (PAC) spectroscopy is a useful tool for research in nuclear and solid state physics. Data obtained from PAC studies gives information about the energy levels of the nuclear states of radioactive probe nuclei which can be used to deduce information about its local environment. This information can then be compared to theoretical predictions about the structure of a material, behavior of defects in the material, or various other related entities. It has advantages over other types of study in that it interrogates the local environment of the probe nuclei and thus can be used to study particular properties of materials as chosen by the exact method of study. It has been used by Professor John A. Gardner's research group to study liquid and amorphous selenium-tellurium alloys<sup>1</sup>, zirconia ceramics<sup>2,3</sup>, oxide ceramics<sup>4</sup>, high T<sub>c</sub> superconductors <sup>5,6</sup>, defects in ceria<sup>7</sup>, and various other materials. There have been compilations done of results obtained from PAC studies done on compounds by Lerf and Butz<sup>8</sup>, on metals by Vianden<sup>9</sup>, and a general list of applications by Rinneberg<sup>10</sup>.

### 1.1. Theory of perturbed angular correlations

Radiations from an atomic or nuclear system are not random in their direction, but have a pattern dependent on the observed system<sup>11</sup>. This means that when two successive gamma rays are emitted from a single excited nucleus in the process of decaying to the ground state, there is a preferred direction for the emission of the second with respect to the emission of the first (a pattern exists). This result is what allows the whole technique

of PAC to be useful; By observing these patterns, the environment of the nuclei responsible for the emissions can be deduced, and then this information can be used to understand the physical structure and other properties of the studied materials. If the decay process is repeated by many nuclei that share the same (or very nearly the same) environment and these patterns are recorded, then these observations can be used to determine the properties of the system. An example of a system that meets the similar environment criteria would be nuclei occupying the same lattice positions in a well-ordered crystalline material. Analysis of the data would reveal properties of the solid could then be characterized.

The underlying theory behind the use of PAC is quite complex. In order to fully understand how the interactions within the system produce the results that are observed, one must understand electricity and magnetism, quantum mechanics, solid-state, and nuclear physics. A complete theoretical treatment of the formalism for the static electric field gradient (EFG) is given by Frauenfelder and Steffen<sup>12</sup>. A summary of that treatment and a complete development of the PAC theory has been done by Gaskill<sup>13</sup>, Jaeger<sup>14</sup>, Su<sup>15</sup>, Weidlich<sup>16</sup>, Fuchs<sup>17</sup>, Schwenker<sup>18</sup>, and Wang<sup>19</sup>. Only a brief theoretical development will be presented here, since this work was not undertaken as an exercise in using PAC spectroscopy, it was done to improve the experimental system. The form and notation of Jaeger<sup>20</sup> and Su<sup>21</sup> will be adopted in this discussion and their work will be summarized.

Consider the intermediate state of the nuclei that undergo the decay cascade mentioned previously. During its finite lifetime  $\tau$ , the nuclei will interact with any external or internal electromagnetic fields that act upon them. The interaction with these fields will cause the nuclei to precess and the angular distribution of the second gamma ray with respect to the first will be changed from the case where there are no fields acting. By measuring the angular correlation for the system in which the fields are acting and comparing it to the expected angular correlation with no fields acting, information about the interaction can be obtained. By learning about the interaction, the environment of the nuclei can be determined and the properties of the sample can be characterized. The only interactions that must be taken into account for the most popular

PAC probes is the interaction of the electric quadrupole moment of the nucleus with the electric field gradient. The reason for this is that (i) the most common PAC probes have closed electronic shells (spherical symmetry) and therefore no electric or magnetic dipole moments, (ii) the materials that are studied are usually non-magnetic, and (iii) higher order electronic terms are negligible. It will be assumed that this is the case in the rest of this discussion.

In PAC spectroscopy, the observation of the first gamma ray emission from the nuclear decay (through cascade  $I_i \rightarrow I \rightarrow I_f$ ), selects a subset of all of the decaying nuclei in the sample. This must be the case, because only certain spin orientations can produce gamma ray emissions in the direction of a detector. As a result of this, the second gamma ray from these nuclei must be emitted in an angular distribution that is correlated with the direction of the first. The probability that a nucleus decays by the emission of two gamma rays,  $\gamma_1$  and  $\gamma_2$ , in the directions  $\mathbf{k}_1$  and  $\mathbf{k}_2$  into solid angles  $d\Omega_1$  and  $d\Omega_2$  is defined as:

$$W(\mathbf{k_1}, \mathbf{k_2}, t) d\Omega_1 d\Omega_2$$

By using quantum mechanics to describe the transition from  $I_i \to I \to I_f\,$  it can be shown that:

$$W(\boldsymbol{k_1}, \boldsymbol{k_2}) = \sum_{k=0, \text{even}}^{k_{\text{max}}} A_{kk} P_k(\cos\theta)$$

is the angular correlation function for free nuclei. In this equation,  $A_{kk}$  are numbers that depend only on the spins of the nuclear states and  $P_k(\cos\theta)$  are the Legendre polynomials where  $\theta$  is the angle between the gamma ray emissions.

If a static extranuclear perturbation field is taken into account, after similar analysis it can be shown that:

$$W(\boldsymbol{k_1}, \boldsymbol{k_2}) = \sum_{k=0, \text{ even}}^{k_{\text{max}}} A_{kk} G_{kk} P_k(\cos\theta)$$

is the resulting perturbed angular correlation function. The assumption made in the derivation of this equation is that the sample is made up of many crystals that are randomly oriented. The resulting perturbation function  $G_{kk}$  can then be understood as the average of the perturbation function for a single crystal. This perturbation function can be expressed as:

$$G_{kk}(t) = \sum_{n} S_{nn}^{kk} + \sum_{n \neq n'} S^{kk} \cos\left[\frac{(E_n - E_{n'})t}{\hbar}\right]$$

where the coefficients  $S^{kk}$  depend on the nuclear states in the transition. The energies  $E_n$  and  $E_{n'}$  are the energy eigenvalues for the interaction Hamiltonian. It is important to note the time independent term  $\sum_{n} S_{nn}^{kk}$ . Due to the existence of this term, the angular correlation of a polycrystalline sample is never completely destroyed by the static perturbing fields. For this reason, the term has historically been called the "hard-core".

In order to fully understand the perturbation function, the energy eigenvalues for the interaction Hamiltonian must be found. Solving for the energy eigenvalues of the interaction Hamiltonian is quite complicated and only the results will be shown here. As was stated earlier, the only interaction that must be taken into account is the interaction of the electric quadrupole moment of the nucleus with the electric field gradient (EFG). To simplify things, the principle axis system is chosen for the EFG in such a way that  $|V_{xx}| \le |V_{yy}| \le |V_{zz}|$  ( $V \equiv EFG$ ). For external charges the Poisson equation reduces to the Laplace equation  $V_{xx} + V_{yy} + V_{zz} = 0$  so that  $\eta$ , which is defined by:

$$\eta = \frac{V_{xx} - V_{yy}}{V_{zz}}$$

is restricted to  $0 \le \eta \le 1$ . In the above definition,  $\eta$  is called the asymmetry parameter. For static, axially-symmetric EFG's the quadrupole Hamiltonian is diagonal and results in energy eigenvalues:

$$E_m = \hbar \omega_{\mathcal{Q}} [3m^2 - I(I+1)]$$

where the quadrupole frequency  $\omega_{\!Q}$  is defined as:

$$\omega_{\varrho} = \frac{e Q V_{zz}}{4 I (2I - 1) \hbar}$$

where Q is the the quadrupole moment of the nucleus. For the case where the electric field gradient is not axially symmetric, the Hamiltonian is not diagonal. In this situation, the Hamiltonian must be diagonalized in order to solve for the eigenvalues, a process which can be quite difficult. If the system is restricted to I = 5/2, which is the case for the PAC probe used in this work, then the diagonalization results in :

$$E_{\pm\frac{5}{2}} = 2\alpha \hbar \omega_{\rho} \cos\left[\frac{1}{3}\cos^{-1}\beta\right]$$

$$E_{\pm\frac{3}{2}} = -2\alpha\hbar\omega_{\rho}\cos\left[\frac{1}{3}\left(\pi + \cos^{-1}\beta\right)\right]$$

$$E_{\pm\frac{1}{2}} = -2\alpha\hbar\omega_{\rho}\cos\left[\frac{1}{3}(\pi - \cos^{-1}\beta)\right]$$

where

$$\alpha = \sqrt{\frac{28}{3}(\eta^2 + 3)}$$

and  $\beta = \frac{80(1 - \eta^2)}{\alpha^3}$

Recall that:  $(I = \frac{5}{2} \rightarrow m = \pm \frac{5}{2}, \pm \frac{3}{2}, \pm \frac{1}{2})$

By substituting these into the equation for  $G_{kk}$ , the expression can be now be directly linked to the energy states of the nucleus and the EFG at the probe nuclei. This is the fundamental basis for PAC; by extracting the  $G_{kk}$  function for the experimental data, information about the environment of the probe is also obtained.

Before closing this discussion, there are a few conclusions that should be drawn. One observation is that the  $\pm m$  energy levels for both cases (symmetric and asymmetric EFGs) are doubly degenerate. This results in (2I+1)/2 distinct energy levels for halfinteger I, and to I+1 distinct energy levels for integer I. For the case I=5/2, there are three distinct frequencies (depending on m - shown on the previous page) observed when the data is analyzed, corresponding to the differences between these energy levels. These three frequencies are referred to as the PAC frequencies. For the asymmetric EFG case, the energy levels (and therefore the PAC frequencies) depend on the degree of the asymmetry ( $\eta$ ). The last conclusion that should be mentioned is that the three PAC frequencies must obey the sum rule,  $\omega_1 = \omega_2 + \omega_3$ .

It should also be noted that the possibility exists that the electromagnetic fields in the local environment of the probe may change as a function of time. If the fields change during the lifetime of the intermediate state, then the electric quadrupole interaction becomes time-dependent and therefore very complicated. By studying this, there is quite a bit to be learned about such things as the jump rate of defects, correlation times, and the trapping energy. The system can (and usually does) include both static and timedependent perturbing fields. The derivations for time-dependent perturbations are beyond the scope of this discussion and will not be presented here.

### 1.2. Experimental perturbed angular correlation spectroscopy

PAC spectroscopy is an experimental method that allows for detailed study of the structural properties of various materials. As its name implies, it involves establishing the angular correlation between the emissions of two (or more) gamma rays from an

excited nucleus as it decays to the ground state. Obviously, the first requirement in studying a material involves the presence of radioactive probe nuclei in the material. If a probe species is not naturally present or cannot be manufactured by a process such as irradiation, than it can be artificially introduced by one of many different methods. Once the probe nuclei have been introduced into the sample, the sequence for a decay of interest would be for the parent nucleus to decay by some mechanism, usually electron capture or beta decay, into a daughter nucleus which is left in an excited state. This nucleus then decays to the ground state by the emission of a single gamma ray or a cascade of gamma rays. It is the latter emission scheme that is useful for this experimental method.

It is necessary to carefully pick the probe nuclei so that certain criteria are fulfilled for this type of work. The first, and most important, is that the gamma rays are emitted in a cascade in such a way that the intermediate state of the nucleus exhibits a half-life that is suitable for the resolution of the time measuring device. The gamma rays must also have energies that are within the range of common detectors. There are several radioactive probe nuclei that satisfy these criteria (see appendix A). The next restrictions on the choice of probe depend directly on the physical characteristics of the material to be studied and the specific properties of the material that are of interest. For example, if the material to be studied is a crystalline structure, the charge on the probe atom and the physical size of the atom must also be compatible with the lattice site in which the probe is to be introduced. This is very important if the results are to be correctly interpreted, since analysis of the angular correlation gives information about the local environment in which the probe nuclei are placed. By knowing the site (or sites) where the probe nuclei are located, predictions and simulations of the results can be made, thereby confirming or disproving theoretical models about the material.

The data collection for this experimental procedure can be performed in many different ways. The first essential pieces of equipment are the detectors, which are normally photomultiplier (pm) tubes (see figure 1.1). The basic operation of a pm tube is very simple. A gamma ray is incident upon the scintillation crystal and excites the crystal lattice. The lattice then produces visible light in the process of relaxation. These

photons strike the photocathode which causes it to emit electrons. These electrons are accelerated towards a chain of dynodes, each of which is held at a different electric potential. The first electrons (from the photocathode) hit the first dynode, which causes it to emit secondary electrons. This process is repeated throughout the length of the dynode chain, with each link multiplying the number of electrons that are emitted. At the end of the chain there is anode which "collects" the electrons. This burst of electrons produces a voltage pulse across a resistor, the amplitude of which is proportional to the number of electrons and therefore to the energy of the incident photon. There is also a secondary, slower output of the pm tube which comes directly from one of the last dynodes in the chain. It is different in that it is shaped by an R-C network to have a form that is better representative of the energy of the incident photon and is easier to use in conventional amplifiers. The primary, fast pulse (called the anode pulse) is usually used for timing purposes and the slower, secondary pulse (called the dynode pulse) is usually used for energy analysis.

The essential sections of the system after the detectors are a section which analyzes the energy of the emitted gamma rays and a high resolution timer that records the time between the reception of these emissions. The capture of an "event" of interest can be simply stated as a sequence that includes the detection of the first gamma ray of the cascade which starts a timer and the detection of the second gamma ray of the cascade which stops the timer. It is for this reason that the first gamma ray of the cascade is called the start gamma ray and the second gamma ray of the cascade is called the stop gamma ray. By recording thousands of these events, it is possible to establish the angular correlation of the emission of these gamma rays. With these parts of the system in place, the last necessary part of the hardware of the system is the section which collects the data and stores it in a usable form. There is also the need for a data analysis system to process the data after it has been gathered. For flexibility and efficiency reasons, a personal computer was chosen to perform those tasks in the new system instead of the conventional multi-channel analyzer.

This work was undertaken to improve upon existing data collection systems. The goal was to design and build an integrated system that was easy to use, efficient, and

could gather a more complete set of data than was currently being accomplished. Care was taken at every step to insure that the design was flexible enough to make future hardware modifications unnecessary by allowing the software to dictate what data is gathered from the system. By making the information available to the computer through software, there is an inherent flexibility in the types of experiments that can be performed with this new system.

For the record, it should be noted that there are actually two different strategies that can be employed in order to gather the data necessary for analysis (see figure 1.2). The first strategy is to use a pair (or pairs) of detectors, keeping one fixed and moving the second detector on the circumference of a circle with the source at the center of the circle (labelled MOVABLE DETECTORS in figure 1.2). By moving the second detector to a sufficient number of different locations and collecting data for a known period of time at each position, the angular correlation between gamma ray emissions can be established. The second method (called time differential perturbed angular correlation or TDPAC) involves placing two pairs of detectors at fixed positions (usually 90° and 180° apart) on the circumference of a circle with the source at the center (labelled FIXED DETECTORS in figure 1.2). It is this experimental set-up that was used for this work and all discussions from this point on will refer to this scheme (references to this method from this point on will be shortened to PAC).

Fig. 1.2. Diagram of the different detector configurations used in PAC

## 2. The design of the old spectrometer

In preparation for a detailed treatment of the new spectrometer design, it is helpful to first examine the architecture of the system from which it has evolved. The "old" spectrometer which is referred to here is, itself, an evolution from an earlier system<sup>22</sup>. This earlier system has been modified and improved upon to the point that inclusion of a discussion on it would not prove beneficial and therefore will be excluded. The evolution that has taken place in the past has been to improve upon the existing design, with the central "core" of the system left relatively unchanged. The new system has been significantly changed and should be considered a new generation. Throughout this discussion, figure 2.1. should be consulted. The discussion will be limited to what is relevant to understanding the overall hardware functions and will not include supporting hardware such as the furnace or furnace controller. Detailed discussion of the calibration and other necessary procedures is mentioned, but the purpose here is not to explain the full operation of the old system.

#### 2.1. Overview

The old spectrometer can best be discussed by tracing the different sequences of events that would occur when the system is running. Consider the fixed detector system in figure 1.2. The four detectors (labelled 0, 1, 2, and 3) are placed on the circumference of a circle with a radius of approximately 5 cm, and the sample is placed in the center of the circle. The radioactive nuclei that are present in the sample are constantly decaying and emitting their gamma rays in all directions. On occasion, a gamma ray will be incident on one of the four detectors and the detector will react to this occurrence (in the manner described in section 1.2).

Fig. 2.1. Block diagram of the old spectrometer

This occurrence starts the ball rolling. The detector that received the gamma ray will output an anode pulse which travels down a length of coax cable to a constant fraction discriminator (CFD). The function of the CFD is to discriminate electrical noise from the photon signal in the pm-tube and to produce a timing pulse which alerts the rest of the system that a gamma ray has been detected. The noise level threshold is adjustable by means of a potentiometer accessible on the front panel of the CFD. The CFD internally splits the signal from the anode and delays one branch. The delayed portion of the signal is subtracted from a fraction of the undelayed signal. The result is a bipolar signal which has a baseline crossover that is independent of the amplitude of the input signal. The bottom line is that the CFD outputs a signal at a time that is independent of signal amplitude and is therefore independent of the energy of the incident photon. Therefore, the CFD is exactly what is needed for the timing section of the spectrometer.

An important feature of the old spectrometer is that it was designed with only two CFD's. The output of detectors 0 and 1 are first fed into a radio frequency combiner which performs an "or" function on their signals. The output of the combiner is then routed into the start of a Time-to-Amplitude Convertor (TAC). In a similar manner, the output of detectors 2 and 3 are sent into another combiner. The output of this combiner is sent through a delay module that delays the signal for an amount of time equal to about half of the full-scale of the TAC. The TAC functions in a manner similar in principle to a stopwatch, in that it measures the time between the reception of a start signal and the reception of a stop signal. The difference is that it outputs a voltage level that is proportional to the difference in time, not a conventional representation of the time.

The output of the TAC is sent into an Analog-to-Digital Convertor (ADC), which converts the analog representation of the time into a corresponding digital (binary) value. The delay placed before the CFD that generates the stop of the TAC serves a very important role; It makes the TAC output a value corresponding to half of its maximum for a simultaneous (or as close to simultaneous as electronically possible) event. Thus an event that has a "stop" pulse arriving at the stop combiner **before** the "start" pulse will be recorded as a positive time, provided the time between them is less than half of full scale on the TAC. The end result is that the TAC now records two different time scales, one that is forward in time and one that is backward in time. In other words, since midrange on the TAC corresponds to a zero time difference between CFD signals, a value between mid-range and the TAC maximum corresponds to positive time and a value between mid-range and the TAC minimum corresponds to negative time. This feature is crucial to the function of the overall system because of the way that the energy branch of the system is designed.

The energy branch starts from the dynode signal of the pm-tubes. Each detector's dynode output signal is connected to a linear amplifier which simultaneously shapes and amplifies the signal. The positive, unipolar output of each amplifier is connected to a laboratory-built Twin Single Channel Analyzer (TSCA). The schematic diagram for these is shown in figure 2.2. The basic function of them is to check to see if the amplitude of the signal from the amplifier is within two different "windows". These two windows are set by manually adjusting potentiometers which adjust a lower level threshold (LLT in the figure) and an upper level threshold (ULT in the figure). Since the amplitude of the voltage pulse from the amplifier depends on the energy of the incident photon, these windows can be set so that one of them gives a "true" output for pulses that correspond to an energy that signifies the detection of a start gamma ray and the other one gives a positive output for pulses that correspond to an energy that signifies the detection of a stop gamma ray. The windows have a finite width that is determined experimentally, since the behavior of all of the associated electronics tends to spread out the range of voltages that correspond to a photon of a specific incident energy. Since there are two "channels" that are possible, the name TSCA is used for this section. One channel is tuned to the start gamma ray and the other to a stop gamma ray.

It should be noted that this design has some inherent problems. One is that the thresholds tend to drift with changes in temperature and with fluctuations in the power supply. Another is that the timing that governs the window-checking employs a peak-sensing operational-amplifier (op-amp) circuit, which is pulse-height sensitive by nature of its design. This means that the timing will be different for a start or stop photon if they are of significantly different energy. The fact that it works at all can be explained by the notion that the energy resolution is not a critical factor in the overall system. If

Fig. 2.2. Diagram of a single TSCA. There is a total of 4 of these, one for each detector

Fig. 2.3. Diagram of the coincidence section of the old spectrometer

the windows are set too wide, then there is an decrease in the signal-to-noise ratio in the data because of the increase in stray (or background) counts. If the windows are set too narrow, then there is a increase in the dead time of the system due to the tight restrictions placed on the acceptable range of energies. If the windows are set somewhere in the middle of this range, than neither of these problems contributes significantly to the overall performance of the system. However, setting windows still remains as one of the biggest problems with the old design and is one area that was addressed in the new design.

In continuing with the design discussion, it is assumed that the windows are set in such a manner that there is a reasonable probability that if a start or stop gamma ray is incident upon a detector than the corresponding TSCA will provide the correct output. The next part of the system is the coincidence section (see figure 2.3). The output of the four TSCA outputs are the inputs to this portion of the system. This section is responsible for providing two crucial pieces of information about the photons that were detected. The first provided information is about which detectors received photons of energies corresponding to a start or stop (the routing information) and the second is whether or not it corresponds to a valid event. A valid "normal" event is one in which detector 0 or 1 absorbed a start gamma ray and detector 2 or 3 detected a stop gamma ray. A valid reverse event is one in which detector 2 or 3 detected a start gamma ray and detector 0 or 1 received a stop gamma ray. The case where more than one detector received either a start or a stop is ambiguous, and is therefore considered invalid. The result of the energy analysis is clocked into a latch by the delayed TRUE START signal from the TAC. This signal only occurs if the TAC received a start and stop signal within its full-scale range. If the TAC receives a start with no stop, than it resets itself and a new sequence is processed. It will now be assumed that the TAC received a start and stop and the current sequence is continued.

At this point in the cycle there are two different cases to be considered. In either case, the timing of the system is such that spectrometer will now be in a state where the event has been flagged as valid or invalid and the system waits for the ADC to assert the DATA READY signal, which lets the rest of the system know that it is done digitizing the signal from the TAC. The VALID line, the DATA READY line, and a line

that distinguishes between run or calibrate mode (an output from the computer called RUN/CAL) are now inputs to the interrupt versus reset logic. At the time the DATA READY line is asserted, the decision is made whether or not to interrupt the computer. If the VALID line is not asserted, then the computer will be interrupted only if the RUN/CAL input has the system in the calibrate mode. If the system is in run mode, than a hardware reset (HARD RESET) is asserted and the system is reset. If the system is in the calibrate mode than the computer is interrupted every time the DATA READY line is asserted and calibration data can be obtained from the system by the computer. In the case where the VALID line is asserted, the computer is interrupted at the time the DATA READY line.

Upon interrupt, the computer stops whatever it is doing (after completing the instruction it is executing), saves the state of the machine and executes an interrupt service routine. The interrupt service routine reads the routing information, reads the output of the ADC, and figures out where in memory it will increment a value that corresponds to the count of the occurrences of the event. The computer memory is divided into segments that corresponds to the different possible events (see table 2.1). The offset within the segment corresponds to the digitized value of the time between the detection of events. This scheme allows a table look-up method to be implemented in the interrupt service routine and time spent in the service routine to be minimized. This is an important consideration, since this time contributes directly to the dead-time of the system. After the proper memory location has been incremented, the computer issues a software reset (SOFT RESET) signal and the system is reset.

The data is collected in this manner for a long period of time, usually a few days to ensure good statistics. The computer has on-line data analysis capabilities, so that data can be checked from time to time and problems can be detected if they occur. An important point to note is that the interrupt service routine runs in the background and that the computer can be used to do various other tasks while it is collecting data. After a run is completed, the data is transferred by floppy disk to more powerful computers for analysis.

#### 2.2. Data collection and analysis

The data sets that are collected in the old system are limited by the design of the spectrometer. Since the start of the TAC results from an "or" of the signals from CFD 2 and CFD 1 and the stop of the TAC results from an "or" of the signals from CFD 2 and CFD 3, there are four coincidences that are impossible to obtain any information about (see table 2.1). The events that result from a coincidence between the pairs of detectors in the "or" of the start or stop do occasionally occur, but because of the design of the system, they only start (or stop) the TAC twice. This means that these events will do nothing but contribute to the dead time of the system. However, the overall effect is not that significant, because the system processing time is already dominated by events in which a start is received, but there is no corresponding stop (called singles). The fact remains that there is a portion of data that exists but cannot be collected by the spectrometer.

At the end of an experimental run, the data that is collected can be analyzed in a straightforward manner. For each valid detector pair, the data consists of an array in which the index is the time between the reception of a start and stop and the contents in each location is the number of occurrences of that event. If we define  $D_{ij}$  to be the raw data for the detector pair i and j, then this raw data can be expressed as:

$$D_{ij} = \frac{1}{\tau_N} e^{-\frac{t}{\tau_N}} e_i e_j N_0 W(\boldsymbol{\theta}, t) + B_{ij}$$

and then the background corrected count rate can be expressed as:

$$C_{ij} = D_{ij} - B_{ij} = \frac{1}{\tau_N} e^{-\frac{t}{\tau_N}} e_i e_j N_0 W(\theta, t)$$

in this notation<sup>23</sup>  $\theta$  is the separation angle between the ith and jth detector and  $e_i$ ,  $e_j$  are the detectors efficiencies. N<sub>0</sub> is the decay rate of the parent isotope and  $\tau_N$  is the average

half-life of the intermediate state of the daughter isotope.  $W(\theta,t)$  is the angular correlation function which contains all of the information about the probe-environment interaction.  $B_{ij}$  is the background rate for the ijth data sector.

Recalling the angular correlation function for polycrystalline samples with static interactions from the first chapter, we can write  $W(\theta,t)$  as:

$$W(\boldsymbol{\theta}, t) = \sum_{k=0, \, \boldsymbol{\theta} \vee \boldsymbol{\theta} n}^{k_{\text{max}}} A_{kk} G_{kk}(t) P_{k}(\boldsymbol{\theta})$$

For most of the isotopes used in this research group, I=5/2, which restricts the value of k in such a way that  $k_{max} = 4$  (due to selection rules). Using this, the approximation that  $A_{44} \approx 0$ , and adopting the notation  $A_{22} \equiv A_2$ , then the angular correlation can be written:

$$W(\mathbf{\theta}, t) \approx 1 + A_2 G_2(t) P_2(\cos \theta)$$

If the spectra-ratio for the normal spectrum is written<sup>24</sup> as:

$$R_{n}(t) = 2 \frac{(C_{02}C_{13})^{\frac{1}{2}} - (C_{03}C_{12})^{\frac{1}{2}}}{(C_{02}C_{13})^{\frac{1}{2}} + 2(C_{03}C_{12})^{\frac{1}{2}}}$$

and for the reverse is written as:

$$R_{n}(t) = 2 \frac{(C_{20}C_{31})^{\frac{1}{2}} - (C_{30}C_{21})^{\frac{1}{2}}}{(C_{20}C_{31})^{\frac{1}{2}} + 2(C_{30}C_{21})^{\frac{1}{2}}}$$

then the spectra-ratio is approximately equal to  $A_2G_2$ . Therefore, by very simple calculations, the interesting physics can be extracted from the raw data.

| SECTOR<br>NUMBER | SECTOR<br>LABEL | START<br>GAMMA | STOP<br>GAMMA | COMMENTS      |

|------------------|-----------------|----------------|---------------|---------------|

| 0                | 01              | 0              | 1             | INVALID       |

| 1                | 02              | 0              | 2             | VALID,FORWARD |

| 2                | 03              | 0              | 3             | VALID,FORWARD |

| 3                | 10              | 1              | 0             | INVALID       |

| 4                | 12              | 1              | 2             | VALID,FORWARD |

| 5                | 13              | 1              | 3             | VALID,FORWARD |

| 6                | 20              | 2              | 0             | VALID,REVERSE |

| 7                | 21              | 2              | 1             | VALID,REVERSE |

| 8                | 23              | 2              | 3             | INVALID       |

| 9                | 30              | 3              | 0             | VALID,REVERSE |

| 10               | 31              | 3              | 1             | VALID,REVERSE |

| 11               | 32              | 3              | 2             | INVALID       |

Table 2.1. The raw data sectors for the old system

Table 2.2. The different  $A_2G_2$  sets for the old system and how they are formed

| A <sub>2</sub> G <sub>2</sub><br>SET | 90°<br>SECTORS | 180°<br>SECTORS | FORMULA<br>(* SECTOR FORM)                                                             |

|--------------------------------------|----------------|-----------------|----------------------------------------------------------------------------------------|

| FORWARD                              | 03,12          | 02,13           | $\frac{(02^{*}13)^{1/2} - (03^{*}12)^{1/2}}{(02^{*}13)^{1/2} + 2^{*}(03^{*}12)^{1/2}}$ |

| REVERSE                              | 30,21          | 20,31           | $\frac{(21*30)^{1/2} - (20*31)^{1/2}}{(21*30)^{1/2} + 2*(20*31)^{1/2}}$                |

\* In sector form the sector label represents the number of background-corrected counts in the sector. There is also an implicit function of time in this equation. In other words:

$$ij = C_{ij}(t) = D_{ij}(t) - B_{ij}(t)$$

in the above table.

## 3. The architecture of the new spectrometer

Before discussing the internal architecture of the new spectrometer, it would be beneficial to consider an overview of the components. The natural starting place for a discussion on the new spectrometer is at the detectors. The fixed detector method (shown in figure 1.2) is employed in the new system, with the positions of the four detectors being perpendicular to each other. There are two standard "NIM bins" that hold and power devices such as the CFD's and amplifiers. These NIM bins are mounted in a standard 19" rack, which also houses a "VME" card cage and a power supply for the VME card cage. There is also a personal computer (IBM-XT) connected to the rackmounted components which controls the system.

The VME card cage is usually used for the building of a custom-made computer system, but it is not used for that purpose in the new spectrometer. It was chosen because a standard backplane (or motherboard) was available that provided 14 different mounting positions for "cards", each of which had 96 connections to a common bus. This design allowed custom electronics to be built and plugged into the backplane with the interconnections used for intercommunication. The backplane was also designed in such a way that allowed for easy connection of an external power supply to the power buses which were provided at each card slot. The only restriction placed on the custom electronics was that the boards that the circuits were assembled on had to use the type of connector that the VME standard required. As it turned out, this requirement was a problem in the manufacturing process used for the custom printed boards, because the connectors were of triple row design and the boards could only be manufactured with two layers. This problem was resolved by carefully choosing the placement for the traces on the printed circuit boards. Now that the outline of the system has been described, the internal workings can be described.

#### 3.1. Overview

Although the new spectrometer functions as one integrated unit, it can best be discussed by separating the system into two different sections (see figures 3.1 and 3.2). The natural division between the energy and timing channels will be used in this discussion, since there is only minor overlap between these two segments. The reality that they are both tied together should not be forgotten, however. Without simultaneous processing of events in both of these channels, experimental data could never be recorded. It is also worthwhile to remember that the starting point for the processing of an event in both channels is ultimately at the detectors. From there, the timing signals governing the processing of a given event are tied together until they take separate routes from the CFD's. For this reason, each detector and CFD set can be thought of as a single entity for the discussion of the timing system.

Instead of the two CFD's used in the old system, there is one CFD for each of the four detectors in the new setup. This method allows a more accurate tuning of the CFD threshold to the individual detectors and also provides for the distinction between all timing events. The timing of event processing for a given detector splits up at the three CFD outputs, each of which conforms to the NIM standard. Two of the three CFD outputs are dedicated to recording the time between the reception of gamma rays and the other one is used for the starting the energy analysis channel. It should be noticed that all of the timing signals (both the timing and the energy sections of the system) are generated from the output of the CFDs.

It seems natural to dedicate the first part of this overview to the timing channel, since the control of the overall event processing is governed by this channel. It is assumed that the reader will be consulting the block diagram of the timing section shown in figure 3.1 in conjunction with this discussion. Consider the system from the state in which every component has been reset and is ready to process an event. The first part of the sequence is established following the detection of a gamma ray is when the pm-tube (Hamamatsu H3177) sends out an anode (timing) pulse, followed shortly thereafter

Fig. 3.1. Block diagram of the timing section of the new spectrometer

by a dynode (energy) pulse. The anode pulse travels along a coaxial cable to the CFD (ORTEC model 934-S), where it is level-discriminated. Assuming that the anode pulse resulted from the detection of a photon of interest (above CFD threshold), then the CFD asserts the three output lines. One of these is connected to a Lecroy (model 322A) logic unit that is configured in the "or" mode. This signal propagates through the logic unit and starts the Time-to-Digital Convertor (TDC - Lecroy model 2228A) by asserting the common start input of the TDC. The second output of the CFD traverses a long length of cable that serves as a delay (approximately 80ns). This time delay has been experimentally tuned to stop the channel of the TDC corresponding to the detector channel that started it at a TDC count of about 20. This event is called a self-stop and provides a zero-time reference.

In order to understand this more clearly, a discussion of the TDC is necessary. The TDC is a device that performs the same function as the TAC and ADC from the old system. It is different in that there are eight different channels that keep track of time relative to a common start. Of these eight channels, the four that had the closest calibrations were chosen to be used for this spectrometer. The TDC uses a common start signal to trigger the charging of capacitors in all eight channels (in unison). The charging of the capacitor in each one of these channels can be individually stopped and the resulting total charge on that particular capacitor will then be proportional to the time that elapsed from the reception of the start until it was stopped. If no stop signal for a channel comes within the maximum time allowed, then the unstopped channel will have the maximum possible charge. At the end of this preset maximum time (referred to as fullscale) the TDC starts a 20MHz oscillator and begins discharging the capacitors. Internal counters (each channel) count the number of clock cycles that pass while the capacitors are discharging. In this way, the time that elapsed between reception of start and stop pulses for each individual channel is recorded by the counters. This method, called the Wilkinson run-down method<sup>25</sup>, can be made very accurate by choosing high quality circuit components, and therefore a very precise measure of time can be achieved. It should be noted that the time scale resolution of the TDC can be adjusted by an external switch, making it possible to use the device for radioactive probe isotopes with different halflives. For this work, the TDC had a resolution of approximately 0.45ns per channel.

In parallel with the two signals that are associated with the TDC, there is a signal which travels to a circuit board called the STINTSET board which is housed in the VME cage (this board will be discussed in detail in the next section). On that board, a timer is started which keeps a limit on how much time is spent processing each "event". For continuity, assume another gamma ray arrives at one of the other detectors in a time that would allow it to be recorded as a valid event. The second detector sends out an anode pulse which travels to its corresponding CFD. Just like the first CFD sends out three signals, this one does the same. Since the TDC has already been started, the second start signal from the "or" gate is ignored. The delayed stop signal is not ignored, however, and the channel that received this second gamma ray is stopped at a count of about 20, plus the count of whatever amount of time elapsed since the start was received. Using this scheme, the count difference between the second channel that was stopped and the selfstopped channel will be an accurate measure of the time between the detection of the two photons in the detectors (all channels are tuned to self-stop at a count of about 20). At this point, the TDC has recorded an accurate measure of the time between the detection of the two gamma rays and it is time to check the result from the energy analysis to see if a cascade of interest has been timed.

The energy analysis has been taking place in parallel to the timing sequence that was just discussed. The energy analysis section (see figure 3.2) of the new spectrometer is probably the most innovative section of this spectrometer (see the following sections for a more complete discussion of the individual boards). The overall idea is based on the recent technological innovations in the area of flash-type, integrated-circuit Analog-to-Digital Convertors (flash ADCs). The new generation of these components allows analog information to be quickly transformed into its digital representation, which can be processed using fast and accurate digital electronic circuits. The old spectrometer used analog circuitry (the TSCA's) to decide if the voltage pulse from the amplifier was in the correct range to correspond to a gamma ray of interest. The new system uses a fast ADC (Analog Devices AD7821KN - 650ns conversion) to obtain an accurate digital representation of the same information which can than be processed digitally. The binary

Fig. 3.2. Block diagram of the energy analysis section of the new spectrometer

output of the ADC is used to address a Random Access Memory (RAM) chip (Hitachi HM6264), which has been previously loaded with a "table" of values. In this way, the RAM (referred to as a "WINDOW" RAM) can be used as a hardware look-up table to see if the digital representation of the energy corresponds to a gamma ray of interest. One of these systems (an Energy Board) is attached to the output of each amplifier, which is attached to the dynode signal of each detector.

Further analysis is performed by a printed circuit board in the VME cage called the Brain board. The output of all four of the individual WINDOW RAM outputs are latched and the output of these latches (74LS173) are used as the input to another RAM (HM6264). This RAM is also used as a look-up table (referred to as the "VALID" ram). This RAM has the job of deciphering whether or not the combination of gamma rays that have been detected corresponds to the detection of a gamma ray cascade of interest (a VALID event). This RAM also encodes the combination of individual detector events into the same type of information that was encoded by the coincidence section of the old spectrometer. This information is referred to the "ROUTING" INFORMATION and it identifies which of the detectors received the start and stop gamma rays. For example, if detector 0 detected a start gamma ray and detector 1 detected a stop gamma ray, then this would correspond to a valid 90° event. The valid bit would be asserted and the routing would describe the sources that produced it. In this way, the VALID RAM gives direct information as to whether or not an event is of interest and if it is, what the details of the event were.

The timer on the STINTSET board is preset for an amount of time equal to the full-scale of the TDC (currently  $\approx 1\mu s$ ), plus the time of propagation through the energy analysis section ( $\approx 3\mu s$ ). The reason for this should be fairly obvious. If the second gamma ray comes in at a time just less than full-scale, then it is valid as far as the timing is concerned, and the final selection criteria must come from the VALID RAM. At the end of the preset time the system looks at the VALID line and decides on one of two choices. If the VALID bit is not asserted, then the event is not interesting, and a hardware reset (HARD RESET) is generated. The total amount of time that the system takes to process an invalid event is approximately 9 $\mu$ s. If the VALID bit is asserted, then

the computer is interrupted and executes an interrupt service routine. This service routine is responsible for gathering the timing data after interrogation of the routing information. Just as in the old system, a memory location corresponding to the count of the number of occurrences of the particular type of event is incremented. It then issues a software reset (SOFT RESET) and the system is reset for the processing of another event. The total amount of processing for a valid event is approximately 250µs, due mainly to the processing time of the interrupt service routine.

One section of the new system that was not described above is the CALIBRATION INTERRUPT section of the STINTSET board. The implementation will be left to the next section which describes the STINTSET board in detail. The use of it is very specialized and it is only active while the system is being prepared for a data collection run. The basic need that it fulfills is to provide the computer (and therefore the operator) with the calibration information needed to load the value into the WINDOW RAM. Basically, a known energy gamma ray will give a defined range of ADC outputs, but how is the computer and operator to know what that range is? The answer comes from the use of the CALIBRATION INTERRUPT circuitry. The user sets the system into special mode that interrogates each ADC output individually and thus provides the information necessary for the loading of the WINDOW RAM.

An important detail of the system that should be addressed at this point is the method of overall control within the VME cage. There are six different cards connected to the VME backplane that all have to be **simultaneously** controlled if there is to be any hope of passing information back and forth between them. Imagine a group of people that are all talking at once; No person can hope to hear what another person across the room might be trying to tell them! The scheme that was devised and implemented to solve this problem is one of the most ingenious parts of the new system. On each one of the Energy boards and on the Brain board, there are two Erasable-Programmable Read-Only Memory (EPROM) chips. These integrated circuits are used to store the possible "modes" that each one of the boards needs to be in for a given state of the overall system. After correlating the contents correctly (see Appendix B), the computer can be used to address these EPROMs and all parts of the VME cage can be configured to the correct

mode. It should be noted that the STINTSET board does not have any EPROMs on it because it does not have any connections that might conflict with the other boards. It does, however, have connections to the VME FUNCTION bus (the EPROM addresses) and thus can be configured to the CALIBRATION mode (mentioned above).

## **3.2. The STINTSET board**

The name STINTSET board (see figure 3.3) was derived from STart-INTerruptreSET which describes the functions that the circuitry on the board performs. Its inputs are the four START signals from the CFDs, the VALID signal from the Brain board, the SOFT RESET line (from the computer), and the three most significant FUNCTION bits (EPROM address bits) which act as the mode control for the board. The outputs include four gate signals for the CFDs, two reset lines that are sent to the Brain and Energy boards via the VME backplane, and the INTERRUPT line (to the computer). Also recall that it has the timer associated with the length of time each event is processed.

The STINTSET board is best viewed as the overall timing control for the whole system. It receives the start signals from the CFDs, which are immediately sent into flip-flops on this board. It should be mentioned that the CFD outputs had to be modified to provide the necessary TTL (transistor-transistor logic) signals (see figure 3.4) for these flip-flops. The positive outputs from each of these flip-flops are "ORed" together resulting in a single signal that is asserted if any one of the detectors receives a photon. This signal is then used to start a timer "one-shot" (the timer was mentioned previously; a one shot can be considered as a preset timer throughout this discussion) that is preset for full-scale of the TDC plus the propagation time through the energy analysis section. At that preset point in time, the valid bit is "looked at" to see if the sequence that started the timer resulted in a valid event. If the event was valid, then a pulse from a second one-shot is steered (by the valid bit) to trigger a flip-flop and the computer is interrupted.

Fig. 3.3. Schematic diagram of the STINTSET board

If the event is not valid, then the pulse is steered (HARD RESET) to a one-shot that controls the resetting of the system. It should be noted that this HARD RESET signal is ORed together with the output of a one-shot that is connected to the computer (SOFT RESET). In the event that the computer was interrupted, after executing an interrupt service routine, the computer will trigger this other one-shot and a reset will be generated.

The one-shot connected to the computer SOFT RESET line was implemented due o the slowness of the computer. It was found that the interrupt service routine holds the SOFT RESET line in the high state for a seven microsecond time period. This caused a problem if an invalid event followed the interrupt, since the computer would hold the input to the OR gate in the high state. The positive edge from the HARD RESET was not able to propagate through the OR gate and the result was that the edge did not reset the system, resulting in a locking-up of the system. By placing the one-shot with a one microsecond pulse width in the path of the computer signal, the problem was avoided.

The reset sequence is something that should also be discussed, since it is not very straightforward. The output of the reset OR gate is a positive edge that triggers the first one-shot. This one-shot pulse width is set to a time of 3.4us, which is connected to the CFD gate inputs and gates them off during this time period. It also triggers a second one-shot which has a time-constant of about 1us, which is the reset signal that is sent onto the VME bus. This second one-shot is always contained within the pulse width of the gate one-shot, thereby insuring that the TTL components in the VME cage will be reset while the CFD is gated off. At the end of the second one-shot pulse (1us), there is a third one-shot triggered which is connected to a TTL-to-NIM convertor (see figure 3.5). The TTL-to-NIM convertor is necessary because the TDC will only accept NIM level signals as its FAST-CLEAR input.

There is one reason that the reset sequence is so complicated in this system; the separation of the timing and energy analysis sections at such an early point in the overall sequence (at the CFD). Recall that in the old system, the delayed TRUE-START of the TAC was use to strobe the result of the energy analysis. In the new design, this signal is absent, which means that the energy and timing sections are no longer tied together in the processing of an event. Therefore, it is necessary to **guarantee** that the entire system

Fig. 3.4. Schematic diagram of the modification made to the CFD's

Fig. 3.5. Schematic diagram of the TTL-to-NIM conversion circuit for the TDC fast clear

is reset and ready to go at **exactly** the same time. If the timing section becomes ready before the energy section or vice-versa, then the possibility exists that the two sections will process signals from different photons. In order to prevent this from occurring, theCFDs had to be gated off while everything was reset, and then the CFD gate could be turned off. This was further complicated when it was learned that there was a 700ns delay from the time the CFD gate was asserted until the CFD output was actually gated off. The knowledge that the TDC required a 2us time delay from the assertion of the FAST CLEAR until it was ready to process an event also complicated matters.

The other section of this board that is pertinent to this discussion is the CALIBRATION INTERRUPT section. The computer FUNCTION output to the VME bus is used to control this section. In the calibration mode, the regular interrupt section is disabled and the 1-of-4 decoder is enabled by the most significant bit of the FUNCTION. The computer sets the address to whatever channel the user wants to calibrate via the next two most significant bits of the FUNCTION, and the output of the ADC for the selected channel is available to the computer. In this way, the user can determine what ADC outputs correspond to which gamma rays and can set the WINDOW RAM accordingly. The disabling of the interrupt-delay timer used in regular data gathering mode means that every single incident photon causes the computer to be interrupted, so the count rate is astronomical in this mode. The reader should refer to section 4 for a further discussion of the use of this mode for window setting.

## **3.3.** The Energy boards

The Energy board(s) also obtained their name by the function that they perform in the spectrometer; they are responsible for the energy analysis for each of the detectors. Care was taken in the design of these boards to make sure that all four of the boards could be built as identical units and jumper selected to be a given channel. This feature allowed the boards to be tested and debugged by using the same procedures. During the construction of the first prototype, some flaws in the design were noted and were taken into account before the construction of the final four boards. Several testing methods established while verifying the operation of the first board were carefully chronicled so that the final four boards could be tested in the shortest period of time. Most importantly, computer code written for the basic testing of the single Energy board prototype could be used for the testing the rest of them. Refer to figure 3.6 for a diagram of these boards.

There are only two inputs to the energy boards that should be considered as external, the energy signal from the amplifier and the start signal from the CFDs. The start signal actually comes through the VME bus from the flip-flop on the STINTSET board, a feature which limits the start signal to occurring only once during a processing cycle (the flip-flops on the STINTSET board are set up that way). This prevents the board from losing the information that it is processing due to the occurrence of another start signal. The basic function of the energy boards is the WINDOWing. It is on these boards that the digitization and analysis of the energy pulses is performed. It will be assumed that the WINDOW RAM contains the correct contents in the following discussion.

The first part of the Energy board sequence is the reception of the start pulse (jumper selected) from the STINTSET board. This pulse triggers a one-shot that is adjustable to the rise time of the amplifier pulse. The amplifier output is connected to a sample-and-hold amplifier (SHA), which samples the amplifier pulse at its peak (it is strobed by the variable one-shot). It should be noted that the SHA was necessary because the rise-time of the amplifier pulse is too fast for the ADC to accurately track the pulse. The output of the SHA is the input to the ADC. Notice that the SHA and the ADC are strobed simultaneously (by the same signal). This is possible because the SHA has a propagation delay of only 250ns, whereas the ADC has a 350ns set-up time. The output of the ADC is used to address the WINDOW RAM as was previously mentioned. There is also a signal (INT) from the ADC which is asserted when the ADC is done digitizing the analog signal. That signal is used to trigger another one-shot (labelled LATCH CLOCK in the diagram). The LATCH CLOCK one-shot has a preset pulse width of

Fig. 3.6. Schematic diagram of the Energy boards

140ns that is just long enough to allow the ADC-addressed result of the RAM to settle. The positive edge of the one-shot is used to trigger the latch which holds the result from the RAM. The three output lines of the latch are then sent (jumper selected) onto the VME bus and is used on the brain board.

It should be noted that there is also the communication link between the VME bus and the WINDOW RAM on this board. The EPROMs that were mentioned previously are employed to make sure there is no bus contention between the RAMs on the other boards and the one that is being loaded (or read). This provision allows the computer to individually to establish the contents of the WINDOW RAM on each Energy board during calibration mode. For further discussion of this functional aspect of the board, refer to chapter 4.

### 3.4. The Brain board

The Brain board (see figure 3.7) has two different functions in the overall system. Both of these are cerebral in nature, so the name of this board also resulted from its overall function (just like the other boards in the system). The inputs to this board are the outputs from the four Energy board latches. This board is also at the other end of two forty-conductor ribbon cables from the computer some of which can be bi-directional. The FUNCTION bus (and its associated control signals) from the computer is routed via this board, but the overall destination of that bus should be considered as the whole VME cage. The SOFT RESET line from the computer is routed through this board in a similar fashion, but its destination is the STINTSET board (solely). In the opposite direction, the INTERRUPT line from the STINTSET board travels through this board. The outputs from this board (during RUN mode) are the VALID line and the rest of the ROUTING information.

One of the assignments of the Brain board has already been alluded to in earlier

Fig. 3.7. Schematic diagram of the Brain board

discussions. The Brain board is where the VALID RAM is located, and thus it has the job of making the decision of whether or not an event is VALID. This is accomplished by a table-look-up similar to the Energy analysis on the energy boards. It is different inthat the contents of the VALID ram are "predetermined". Unlike the Energy boards, where the ADC output range determines the contents of the WINDOW RAM, the inputs to the VALID RAM are already established by the connections to the Energy boards. For example, if detector 0 receives a start gamma ray and detector 1 receives a stop, then the event is VALID. The memory location that is addressed by this set of outputs from the Energy boards is established as VALID, and it will always be that way. The result of this is that the computer routine that loads the contents of the VALID RAM is unchanging, unless some special circumstances warrant an unusual look-up table.

The other responsibility of the Brain board is the job of communication between the VME bus and the computer. There are two different 40 pin ribbon connectors on this board that go directly to the computer (every other conductor is grounded on these cables). There are also EPROMs on this board that control all of the necessary control bits on the board for the bi-directional bus transceivers at the end of this ribbon cable. The basic idea here is that there must be some way to control the communication between the computer and the card cage while the different modes are being executed. For example, the direction of communication between the computer and VME cage is different when the WINDOW RAM is being loaded then when the ROUTING information is being read.

# **3.5.** The computer interface

The computer interface is centered around a parallel interface board (Quatech PXB-721) that plugs into a single slot in the PC bus. This board is based on three 8255 parallel interface chips. A block diagram is shown in figure 3.8. Access to these 8255's

| 8255 # 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                         |                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|