#### AN ABSTRACT OF THE DISSERTATION OF

Ruoxin Jiang for the degree of <u>Doctor of Philosophy</u> in <u>Electrical & Computer</u> Engineering presented on July 30, 2001.

Title: Design of a 1.8-V 14-bit  $\Delta - \Sigma$  A/D Converter with 8X Oversampling and 4 MHz Nyquist Output Rate.

|                      | Redacted for Privacy |    |       |

|----------------------|----------------------|----|-------|

| Abstract approved: _ | <br>                 |    | <br>_ |

| • •                  | $\supset$            |    |       |

|                      | Terri S. Fi          | ez |       |

In this dissertation, a new  $\Delta\Sigma$  A/D converter is presented that is ideally suited for communication applications. It is based on a single-loop single-stage structure, which can realize a high maximum out-of-band quantization noise gain while maintaining stable operation and thus achieve 14-bit resolution at 8 times oversampling. A fifth-order  $\Delta\Sigma$  analog-to-digital converter (A/D) has been designed and tested in a 0.18  $\mu m$  CMOS process. This is the first single-stage  $\Delta\Sigma$  A/D converter reported in the literature that achieves 14-bit resolution at 4 MHz equivalent Nyquist rate with a 1.8-V power supply.

©Copyright by Ruoxin Jiang

July 30, 2001

All rights reserved

# Design of a 1.8-V 14-bit $\Delta - \Sigma$ A/D Converter with 8X Oversampling and 4 MHz Nyquist Output Rate

by

Ruoxin Jiang

#### A DISSERTATION

submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Completed July 30, 2001 Commencement June 2002

| Doctor of Philosophy dissertation of Ruoxin Jiang presented on July 30, 2001        |

|-------------------------------------------------------------------------------------|

| APPROVED:                                                                           |

| Redacted for Privacy                                                                |

| Major Professor, representing Electrical & Computer Engineering                     |

| Redacted for Privacy                                                                |

| Head of the Department of Electrical & Computer Engineering                         |

| Redacted for Privacy                                                                |

| Dean of the Graduate School                                                         |

|                                                                                     |

|                                                                                     |

| I understand that my dissertation will become part of the permanent collection of   |

| Oregon State University libraries. My signature below authorizes release of my dis- |

| sertation to any reader upon request.                                               |

| Redacted for Privacy                                                                |

| Ruoxin Jiang, Author                                                                |

#### ACKNOWLEDGMENT

I would like to express my special appreciation to my advisor, Professor Terri S. Fiez, for her consistent guidance and support during my study at Oregon State University and Washington State University as a Ph.D. student. Her guidance in the design of the  $\Delta\Sigma$  A/D converter and in the writing of this dissertation is a great support to this work. I also thank Professor Terri S. Fiez for the opportunities she gave me to attend all the meetings of the Center for Design of Analog-Digital Integrated Circuits (CDADIC).

This project is funded by Semiconductor Research Corporation (SRC) under contract No. 711.001. The author also wants to express thanks to SRC.

I also wants to express my appreciation to Dr. Solomon Yim, Dr. Thomas K. Plant, Dr. Karti Mayaram, Dr. Un-Ku Moon, Dr. Gabor C. Temes, and Dr. John T. Stonick for spending their valuable time as my committee members. I especially thank Dr. Karti Mayaram for the expertise I gained from his classes. His systematic teaching and thinking have helped me in circuit simulation, analog circuit design and RF circuit design. I also thank Dr. Gabor Temes and Dr. Un-Ku Moon for their valuable advice and information on this work.

I would like to thank Bijoy G. Chatterjee, Howard T. Gnauden, Andy Franklin, Sarah Luna, Wai Lao, Paula Zhang, Virginia Abellera and Peter Misich of National Semiconductor for their help in reviewing and fabricating this chip.

Special thanks to Ferne Simendinger, Sarah O'Leary and April Melton for their help during my stay at Oregon State University.

I am grateful to Robert Batten, Tina Batten, Aria Eshraghi, Steve Dunlap, Yongmin Ge, Suet Fong Tin, Paul Stulik, Travis John, Mete Eray, Shanthi Bhagavatheeswaran, Haiming Tang, John Mcnitt for their help during my study at Oregon State University and Washington State University. I want to express special thanks to Robert Batten for valuable discussions on circuit design, PCB design and test equipment setup. I also thank Aline Sadate, Vinay Chandrasekhar, Madhusudhan Chennam, Yemelong Constand, Taras Dudar, Yutao Hu, Kalyan Ghatak, Zhimin Li, Nathan Barton, Yuxian Ou, Dicle Ozis, Volodymyr Kratyuk, Oleg Mikulchenko and Nilakantan Seshan for the joy and friendship they brought to me. Jose Silva always offers timely help on Cadence problems. Tetsuya Kajita offers valuable advice on Switcap2 simulations. I also want to express special thanks to them.

Thanks to my parents for their encouragement from elementary school through the Ph.D. degree. Finally, I would like to express special thanks to my wife, Hui Zhou, who has been helping and encouraging me all these years.

### TABLE OF CONTENTS

|   |     | <u> </u>                                                                                           | 'age |

|---|-----|----------------------------------------------------------------------------------------------------|------|

| 1 | INT | RODUCTION                                                                                          | 1    |

|   | 1.1 | Motivation                                                                                         | 1    |

|   | 1.2 | Dissertation Organization                                                                          | 2    |

| 2 |     | INFLUENCE OF MAXIMUM OUT-OF-BAND QUANTIZATION SE GAIN ON $\Delta\Sigma$ A/D PERFORMANCE            |      |

|   | 2.1 | Introduction to Quantization Noise of $\Delta\Sigma$ Modulators                                    | 5    |

|   | 2.2 | The Relationship Between $\ \mathbf{H}\ _{\infty}$ and $\Delta\Sigma$ Modulator System Performance |      |

|   | 2.3 | Conclusion                                                                                         | 35   |

| 3 | STA | BILITY ANALYSIS OF EXISTING $\Delta\Sigma$ A/D ARCHITECTURES                                       | 36   |

|   | 3.1 | Analysis of a Fifth-Order Leapfrog $\Delta\Sigma$ Modulator                                        | 36   |

|   | 3.2 | Review of Other Commonly Used Structures                                                           | 41   |

|   | 3.3 | Conclusion                                                                                         | 45   |

| 4 |     | RID $\Delta\Sigma$ A/D CONVERTER FOR LOW OVERSAMPLING APPLIONS                                     | 46   |

|   | 4.1 | The Derivation of Hybrid $\Delta\Sigma$ Modulator Structure                                        | 46   |

|   | 4.2 | Stability of the Fifth-Order Hybrid $\Delta\Sigma$ Modulator                                       | 51   |

|   | 4.3 | Dynamic Element Matching Algorithms                                                                | 59   |

|   | 4.4 | Coefficient Quantization                                                                           | 70   |

|   | 4.5 | Simulation Results                                                                                 | 78   |

|   | 4.6 | Conclusion                                                                                         | 81   |

### TABLE OF CONTENTS (Continued)

|   |            | $\underline{	ext{Page}}$                                                                               |

|---|------------|--------------------------------------------------------------------------------------------------------|

| 5 | DES<br>SAM | IGN OF A 1.8-V 14-BIT $\Delta\Sigma$ A/D CONVERTER WITH 8X OVERIPLING AND 2 MHZ INPUT SIGNAL BANDWIDTH |

|   | 5.1        | Block Diagram of the A/D Converter 82                                                                  |

|   | 5.2        | Front-End Integrator Design                                                                            |

|   | 5.3        | Design of the Second-Order Transposed Direct Form II Blocks 95                                         |

|   | 5.4        | Design of the Summing-Amplifying Block                                                                 |

|   | 5.5        | Design of the 17-Level 4-Bit Flash A/D                                                                 |

|   | 5.6        | Design of the Clock Generator                                                                          |

|   | 5.7        | Logic Design of the Data Weighted Averaging Algorithm                                                  |

|   | 5.8        | Layout Design                                                                                          |

|   | 5.9        | Simulation Results                                                                                     |

| 6 | MEA        | ASUREMENT AND CONCLUSION                                                                               |

|   | 6.1        | Test Circuit Setup                                                                                     |

|   | 6.2        | Measured Results                                                                                       |

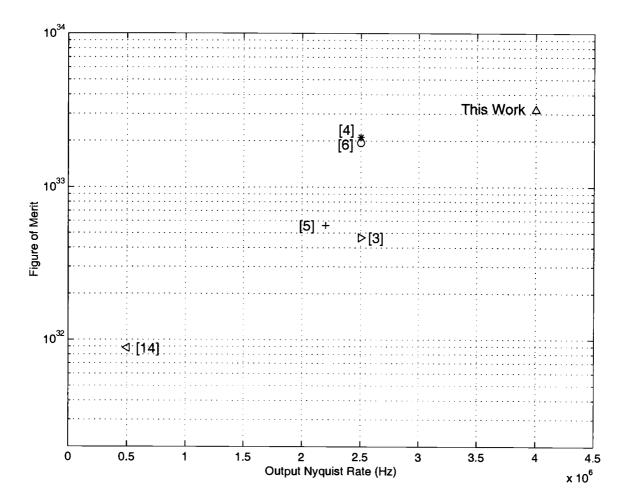

|   | 6.3        | Comparison of This Work with Existing Designs                                                          |

|   | 6.4        | Conclusion and Future Work                                                                             |

| 7 |            | IGN OF A MULTI-INPUT DOUBLE BALANCED CMOS MULTI-                                                       |

|   | 7.1        | Introduction                                                                                           |

|   | 7.2        | Principles of Multi-Input Multipliers                                                                  |

|   | 7.3        | Design of a CMOS Multi-Input Multiplier                                                                |

### TABLE OF CONTENTS (Continued)

|        |                                                     | Page |

|--------|-----------------------------------------------------|------|

| 7.4    | Harmonic Distortion Analysis and Simulation Results | 136  |

| 7.5    | Measurement                                         | 142  |

| 7.6    | Conclusion                                          | 149  |

| BIBLIO | GRAPHY                                              | 150  |

| APPEN  | DICES                                               | 155  |

### LIST OF FIGURES

| Page |                                                                                                                                                                                                                                                                                                                                       | Figure |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

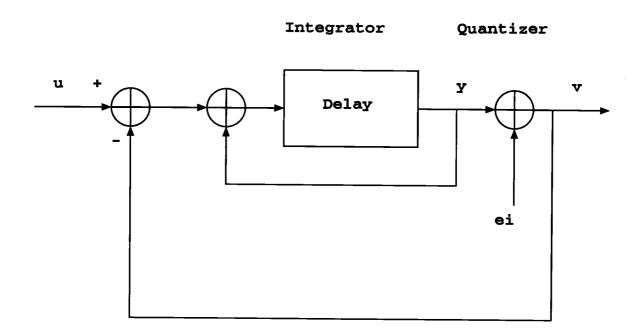

| 6    | Block diagram of a first-order $\Delta\Sigma$ modulator                                                                                                                                                                                                                                                                               | 2.1    |

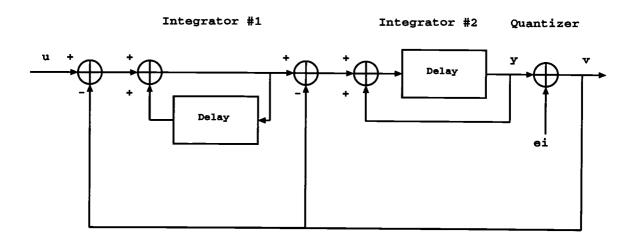

| 8    | Block diagram of a second-order $\Delta\Sigma$ modulator                                                                                                                                                                                                                                                                              | 2.2    |

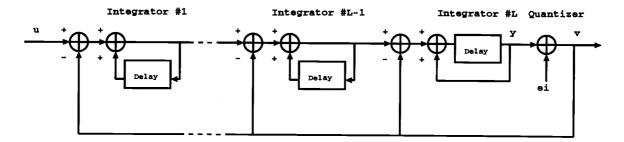

| 9    | Block diagram of an L-th order $\Delta\Sigma$ modulator                                                                                                                                                                                                                                                                               | 2.3    |

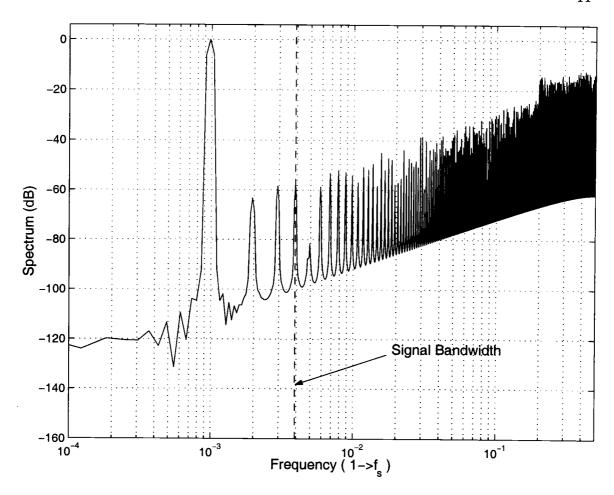

| 11   | Spectrum of a first-order $\Delta\Sigma$ modulator with an oversampling ratio of 128                                                                                                                                                                                                                                                  | 2.4    |

| 12   | Spectrum of a second-order $\Delta\Sigma$ modulator with an oversampling ratio of 128                                                                                                                                                                                                                                                 | 2.5    |

| 13   | Pattern noise spectrum of a first-order $\Delta\Sigma$ modulator with a -24dB DC input                                                                                                                                                                                                                                                | 2.6    |

| 15   | A second-order $\Delta\Sigma$ modulator proposed by B. E. Boser                                                                                                                                                                                                                                                                       | 2.7    |

| 16   | Comparison of integrator output histograms for the traditional and the Boser architecture with sinusoidal input 3dB below overload                                                                                                                                                                                                    | 2.8    |

| 17   | Block diagram of a $\Delta\Sigma$ modulator                                                                                                                                                                                                                                                                                           | 2.9    |

| 18   | ) Block diagram of a $\Delta\Sigma$ modulator with a variable gain                                                                                                                                                                                                                                                                    | 2.10   |

| 20   | NTF root locus of a third-order $\Delta\Sigma$ modulator                                                                                                                                                                                                                                                                              | 2.11   |

| 21   | NTF root loci of two second-order modulators, (a) Candy modulator with $  H  _{\infty} = 4$ and (b) Boser modulator with $  H  _{\infty} = 2.3.$                                                                                                                                                                                      | 2.12   |

| 22   | Comparison of two noise transfer functions, The solid line is for a 4th order $\Delta\Sigma$ modulator with a 4-bit quantizer and the dotted line is for a 5th order modulator with a 4-bit quantizer.                                                                                                                                | 2.13   |

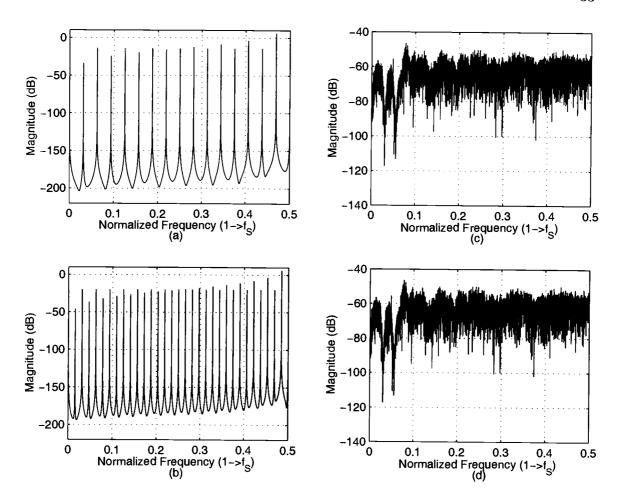

| 24   | Comparison of two fifth-order noise transfer functions: (a) pole-zero plot of the noise transfer function with $  H  _{\infty}=1.5$ , and (b) the corresponding noise transfer function of (a). (c) Pole-zero plot of the noise transfer function with $  H  _{\infty}=6$ , and (d) the corresponding noise transfer function of (c). | 2.14   |

| 25   | SNDR as a function of $  H  _{\infty}$ for third, fifth, and seventh-order $\Delta\Sigma$ modulators with a 4-bit quantizer and 8X OSR                                                                                                                                                                                                | 2.15   |

| $\underline{\text{Figure}}$ |                                                                                                                                                                                                                                                                                                                                                                 | Page |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 2.16                        | (a) The pole-zero plot of a fifth-order 4-bit $\Delta\Sigma$ modulator with $\ H\ _{\infty}$ =1.5 and 8X OSR, and (b) simulated spectrum of the modulator shown in (a). (c) The pole-zero plot of a fifth-order 4-bit $\Delta\Sigma$ modulator with $\ H\ _{\infty}$ =6 and 8X OSR, and (d) simulated spectrum of the modulator shown in (c)                    | 27   |

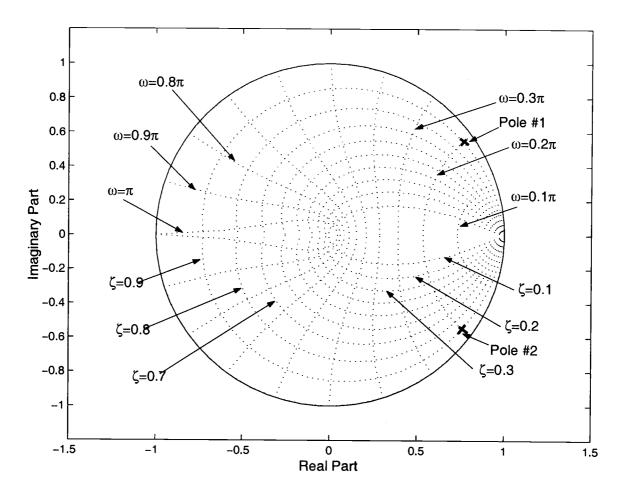

| 2.17                        | Constant natural frequency $\omega$ contours and constant damping rate $\zeta$ contours in a Z-plane, two poles are shown at $\omega=0.2\pi$ and $\zeta=\pm0.9$                                                                                                                                                                                                 | . 28 |

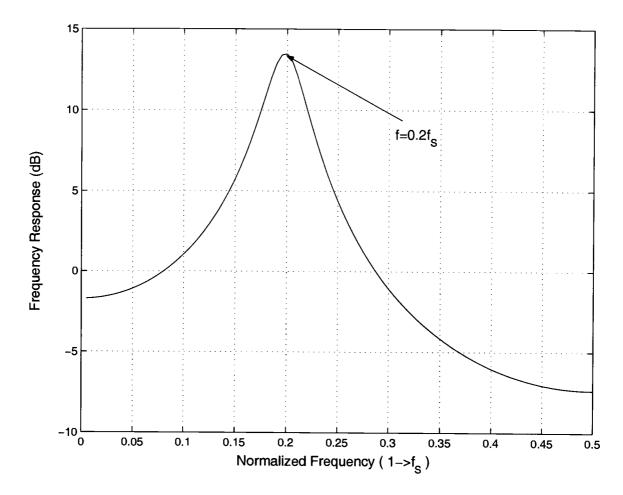

| 2.18                        | The frequency response of a two pole system, two poles are at $\omega \approx 0.2\pi$ and $\zeta = 0.9$ in the Z-plane                                                                                                                                                                                                                                          | 29   |

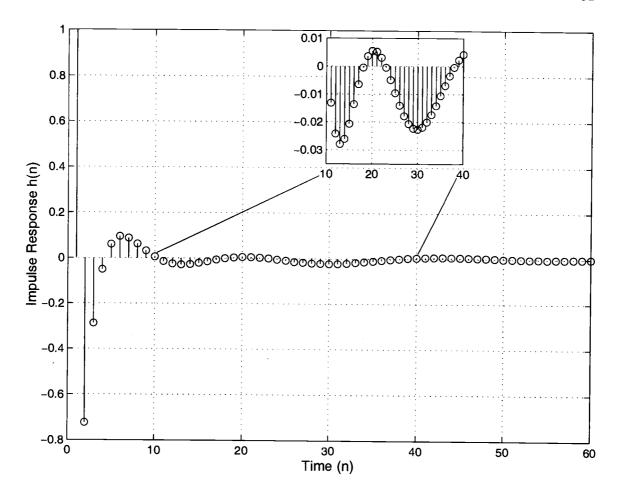

| 2.19                        | Impulse response of the noise transfer function shown in Fig. 2.14(a).                                                                                                                                                                                                                                                                                          | 31   |

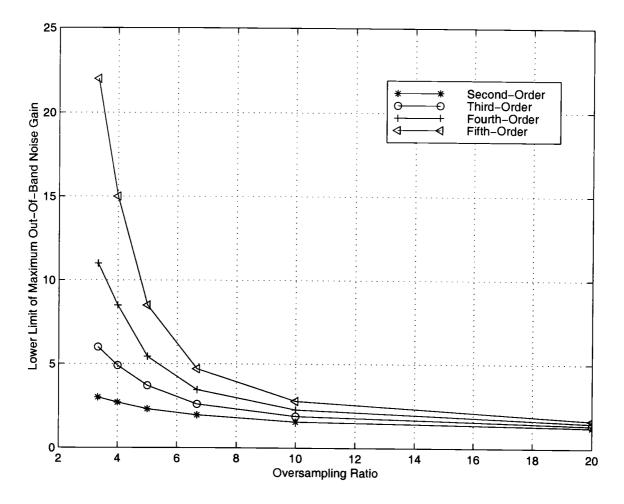

| 2.20                        | Minimum $\ H\ _{\infty}$ to avoid tones in the baseband as a function of oversampling ratio and $\Delta\Sigma$ modulator order                                                                                                                                                                                                                                  | 32   |

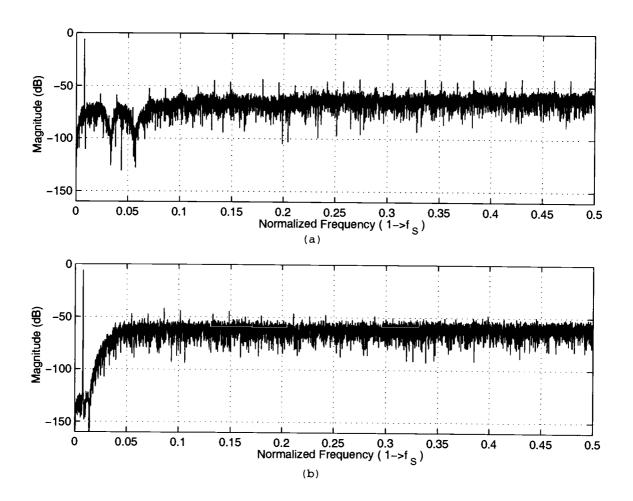

| 2.21                        | Spectra of two $\Delta\Sigma$ modulators with different DC input levels. First-order $\Delta\Sigma$ modulator with 1-bit quantizer (a) DC input is -24 dB relative to full scale and (b) DC input is -30 dB. Fifth-order hybrid $\Delta\Sigma$ modulator with 4-bit quantizer where OSR=8, $\ H\ _{\infty}$ =1.5 (c) DC input is -24 dB, (d) DC input is -30 dB | 33   |

| 2.22                        | Spectra of two fifth-order $\Delta\Sigma$ modulators with 4-bit quantizers with (a) $\ H\ _{\infty} = 1.5$ and OSR=8, (b) $\ H\ _{\infty} = 1.5$ and OSR=32                                                                                                                                                                                                     | 34   |

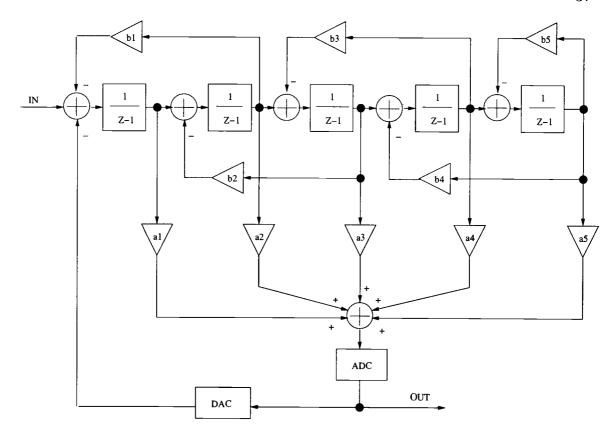

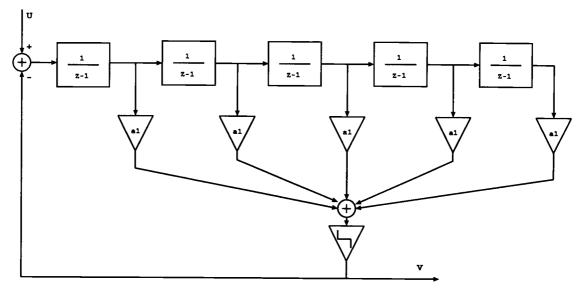

| 3.1                         | Structure of a fifth-order leapfrog $\Delta\Sigma$ modulator before coefficient scaling                                                                                                                                                                                                                                                                         | 37   |

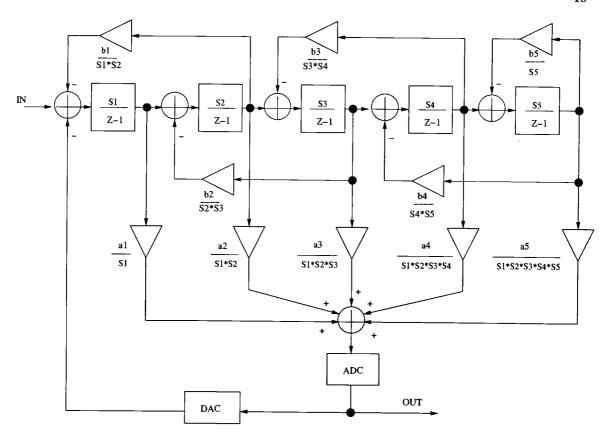

| 3.2                         | Structure of a fifth-order leapfrog $\Delta\Sigma$ modulator after coefficient scaling                                                                                                                                                                                                                                                                          | 40   |

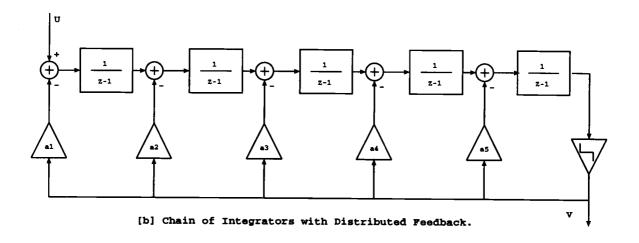

| 3.3                         | Block diagrams of two typical $\Delta\Sigma$ modulators                                                                                                                                                                                                                                                                                                         | 44   |

| 4.1                         | Block diagram of a $\Delta\Sigma$ modulator with a simple feed-back                                                                                                                                                                                                                                                                                             | 49   |

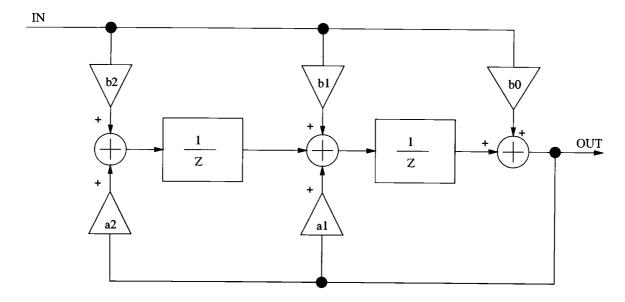

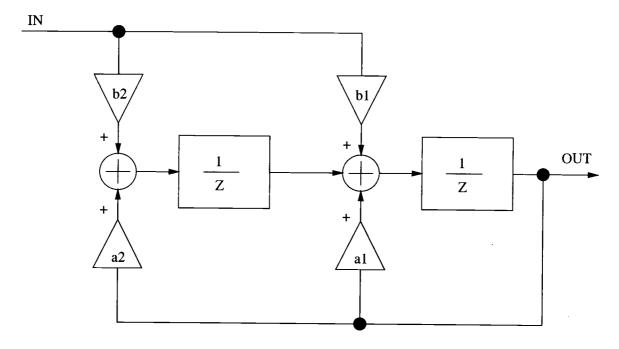

| 4.2                         | Block diagram of a second-order transposed direct form II structure.                                                                                                                                                                                                                                                                                            | 50   |

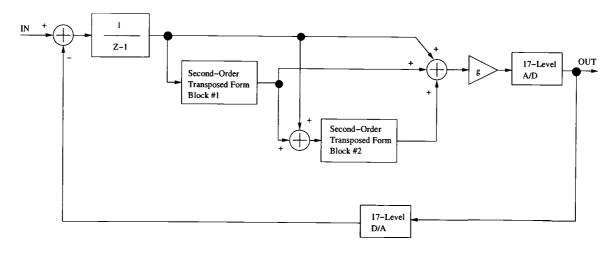

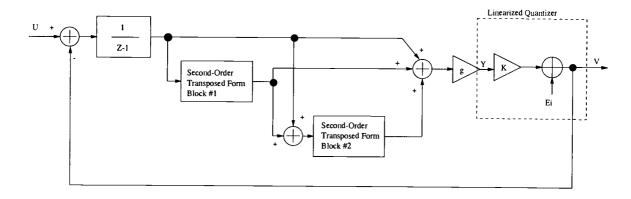

| 4.3                         | Block diagram of a fifth-order $\Delta\Sigma$ modulator                                                                                                                                                                                                                                                                                                         | 51   |

| 4.4                         | Block diagram of the second-order transposed direct form II structure shown in Fig. 4.3                                                                                                                                                                                                                                                                         | 52   |

| F'ig | ure  |                                                                                                                                                                                                                                                                                     | Page |

|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

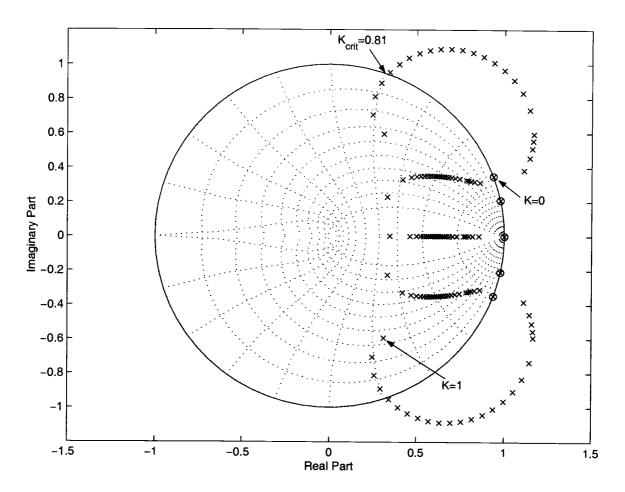

|      | 4.5  | Root locus of a fifth-order Hybrid $\Delta\Sigma$ modulator with $\ H\ _{\infty}=6$                                                                                                                                                                                                 | . 54 |

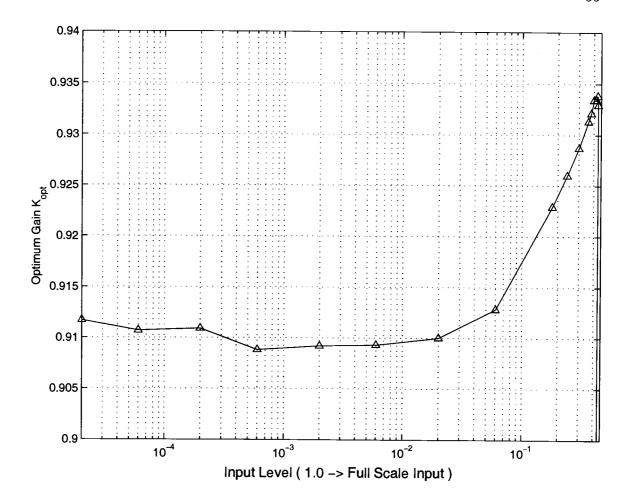

|      | 4.6  | Optimum quantizer gain of a fifth-order hybrid $\Delta\Sigma$ modulator with $\ H\ _{\infty}=6$                                                                                                                                                                                     |      |

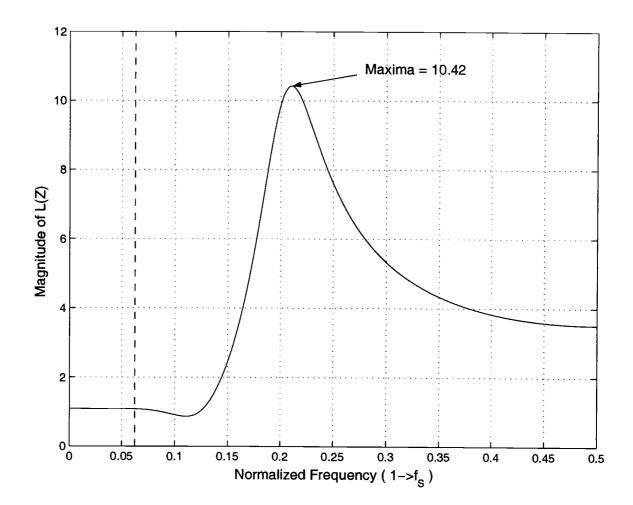

|      | 4.7  | A simplified linear model of the fifth-order $\Delta\Sigma$ modulator                                                                                                                                                                                                               | . 56 |

|      | 4.8  | Frequency response of $L(Z)$ . The quantizer gain is 0.915 and the dashed line is the upper bound of the baseband frequency                                                                                                                                                         |      |

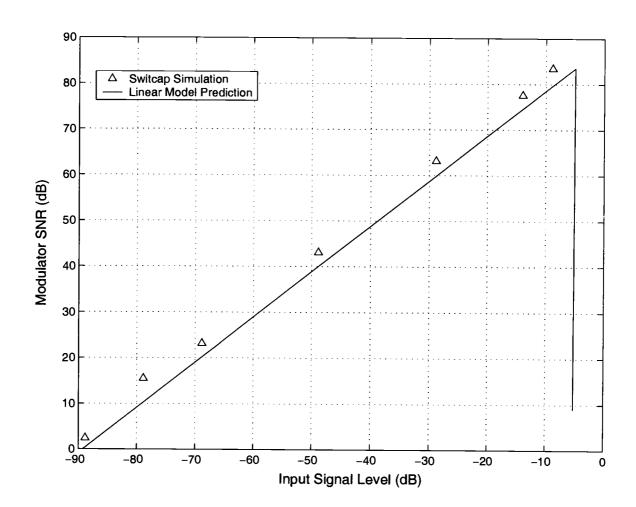

|      | 4.9  | Comparison of the SNR as a function of input signal level obtained from Switcap2 and the linear model, respectively                                                                                                                                                                 |      |

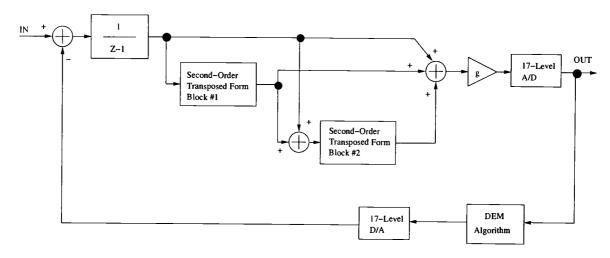

|      | 4.10 | The fifth-order hybrid $\Delta\Sigma$ modulator with dynamic element matching block                                                                                                                                                                                                 | . 61 |

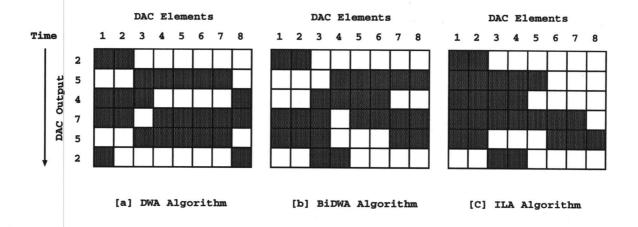

|      | 4.11 | Examples of three first-order DEM algorithms: (a) data weighted averaging algorithm, (b) bi-directional data weighted averaging algorithm, (c) individual level averaging algorithm                                                                                                 | . 64 |

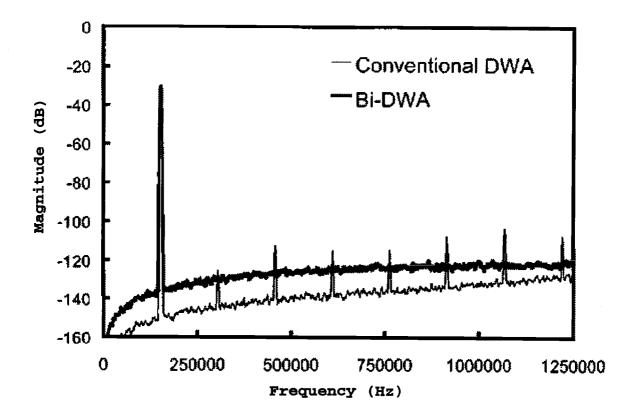

|      | 4.12 | Spectra of BiDWA and DWA algorithms                                                                                                                                                                                                                                                 | . 67 |

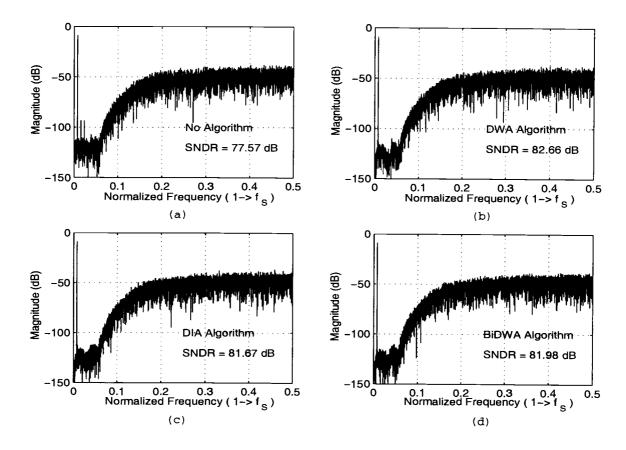

|      | 4.13 | Comparison of different DEM algorithms with DAC capacitor mismatch $\sigma=0.1\%$ , opamp DC gain $\approx 43 \mathrm{dB}$ , and the maximum clock jitter of 10 ps. (a) No DEM algorithm is used, (b) DWA algorithm is used, (c) DIA algorithm is used, (d) BiDWA algorithm is used | . 69 |

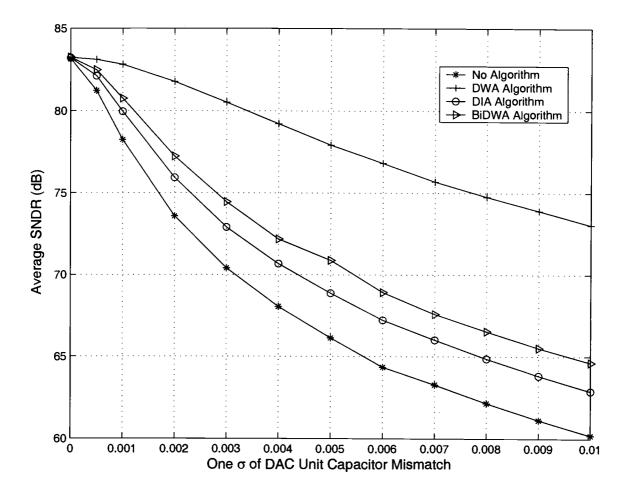

|      | 4.14 | SNDR as a function of DAC unit capacitor mismatch for different algorithms. Each point is the average of 100 simulations                                                                                                                                                            | . 70 |

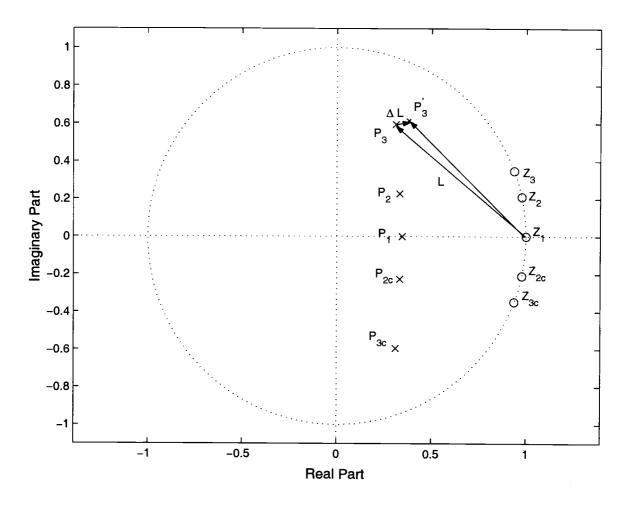

|      | 4.15 | The illustration of pole/zero sensitivity to coefficient variation                                                                                                                                                                                                                  | . 72 |

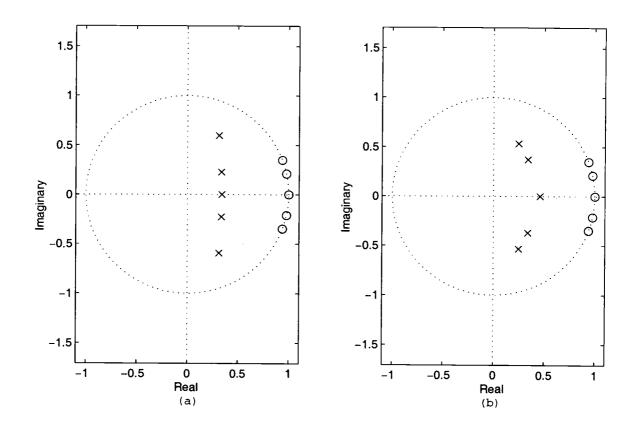

|      | 4.16 | Pole/zero positions of the fifth-order hybrid $\Delta\Sigma$ modulator, (a) pole/zero positions before coefficient quantization, (b) pole/zero positions after coefficient quantization                                                                                             | . 76 |

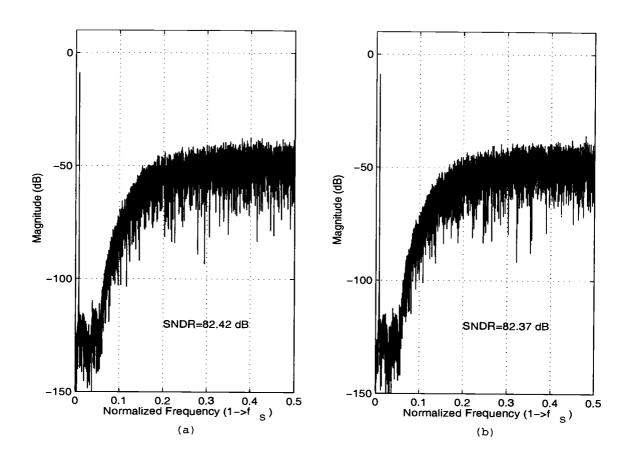

|      | 4.17 | Spectra of the fifth-order hybrid $\Delta\Sigma$ modulator, (a) before coefficient quantization, (b) after coefficient quantization                                                                                                                                                 | . 77 |

| Fig | gure |                                                                                                                                                                                                                                                  | Page |

|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

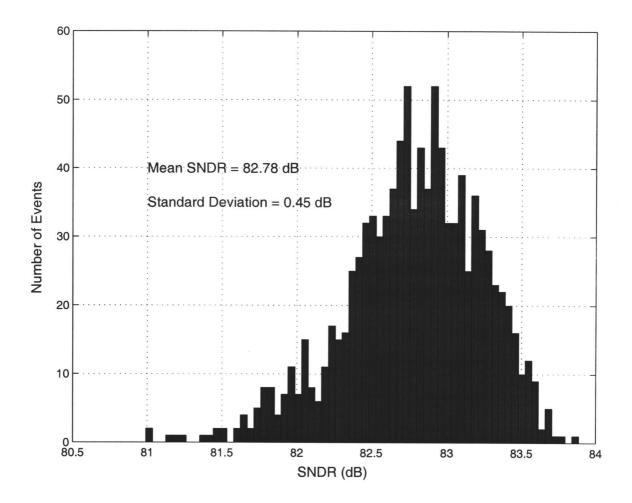

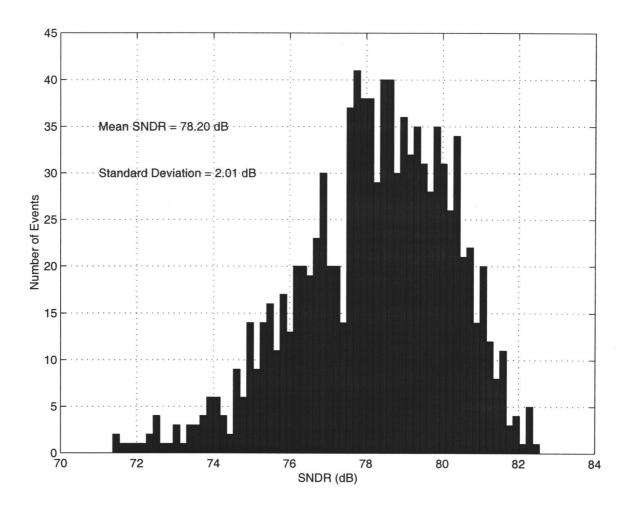

|     | 4.18 | Monte Carlo simulation of the $\Delta\Sigma$ modulator with the DWA algorithm after coefficient quantization. The DAC capacitor mismatch is $\sigma=0.1\%$ , the opamp DC gain $\approx 43 \mathrm{dB}$ , and the maximum clock jitter is 10 ps  | . 79 |

|     | 4.19 | Monte Carlo simulation of the $\Delta\Sigma$ modulator after coefficient quantization without a DEM algorithm. The DAC capacitor mismatch is $\sigma=0.1\%$ , the opamp DC gain $\approx 43 \mathrm{dB}$ , and the maximum clock jitter is 10 ps | 80   |

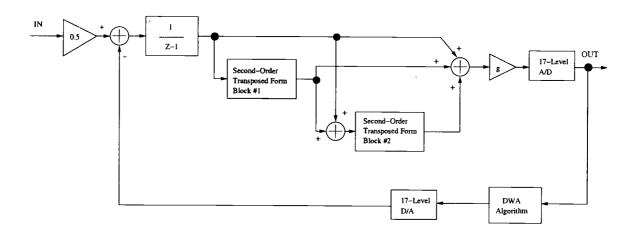

|     | 5.1  | Block diagram of the fifth-order $\Delta\Sigma$ A/D converter                                                                                                                                                                                    | 82   |

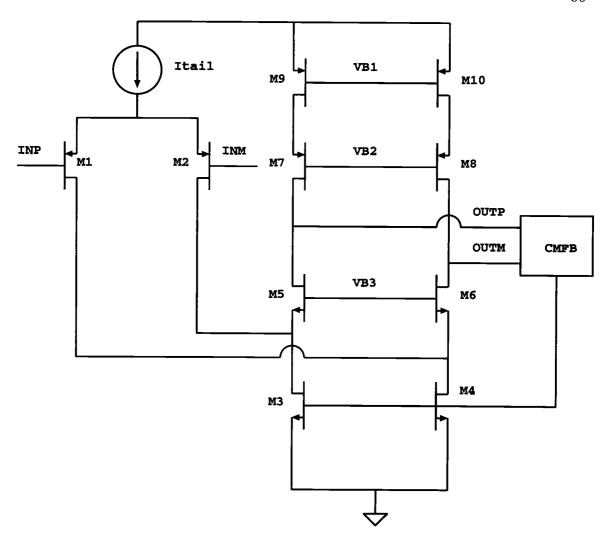

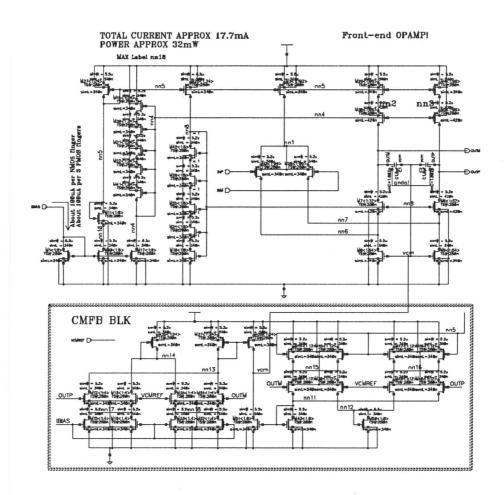

|     | 5.2  | The front-end folded-cascode amplifier                                                                                                                                                                                                           | 86   |

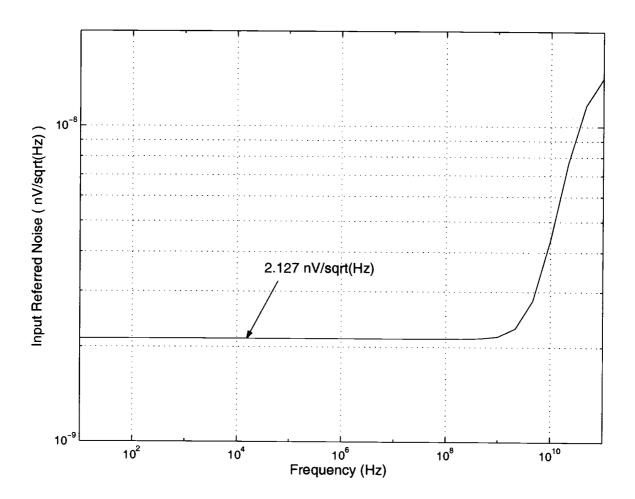

|     | 5.3  | Input-referred noise of the main Opamp                                                                                                                                                                                                           | 87   |

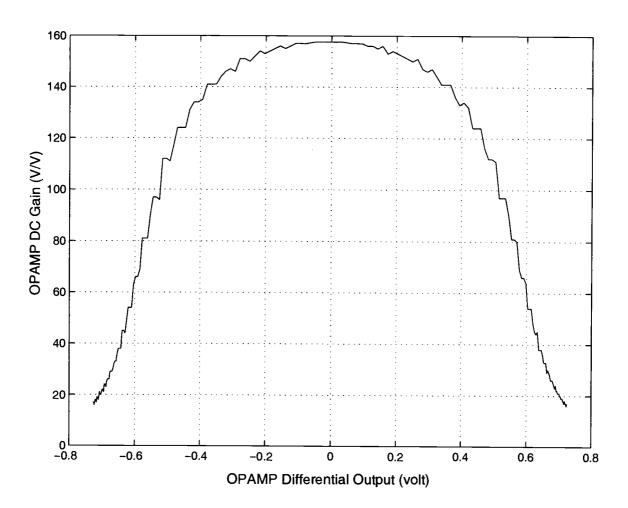

|     | 5.4  | The front-end opamp DC gain as a function of the differential output                                                                                                                                                                             | . 88 |

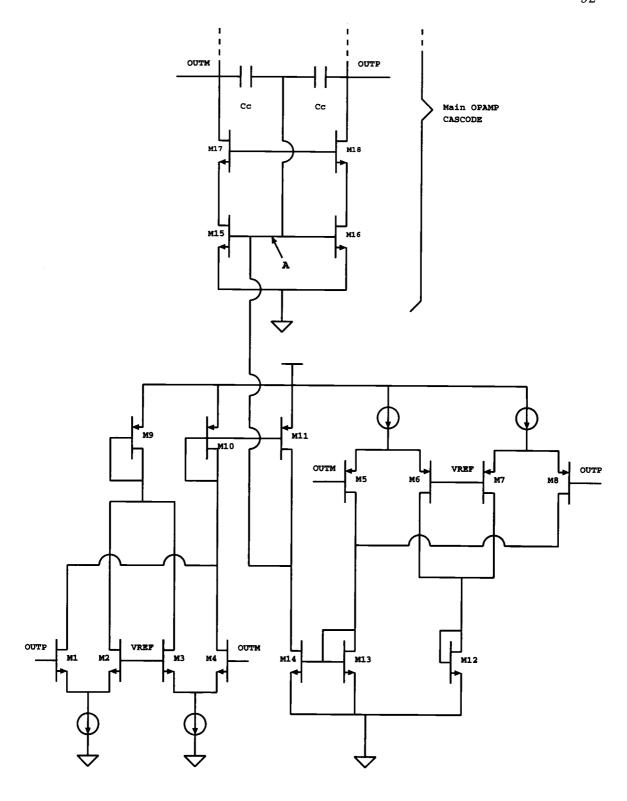

|     | 5.5  | Common-mode feedback circuit used in the front-end Opamp                                                                                                                                                                                         | 92   |

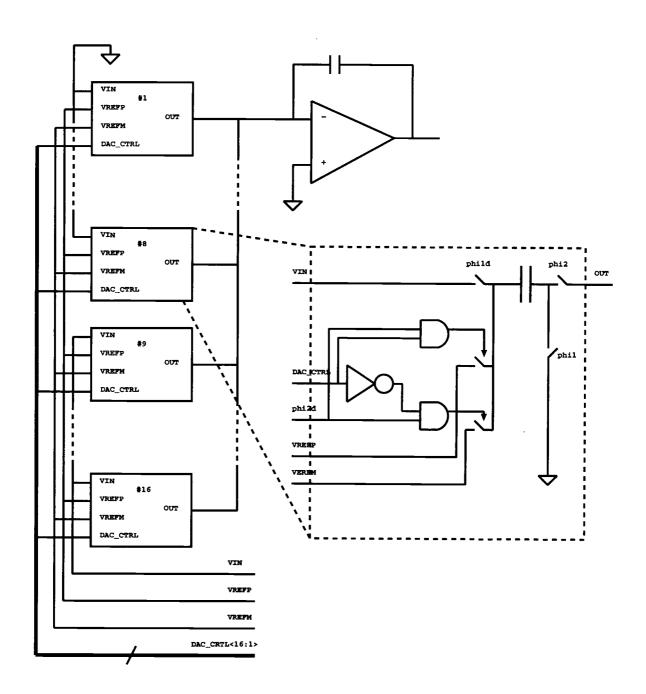

|     | 5.6  | Block diagram of the front-end integrator                                                                                                                                                                                                        | 93   |

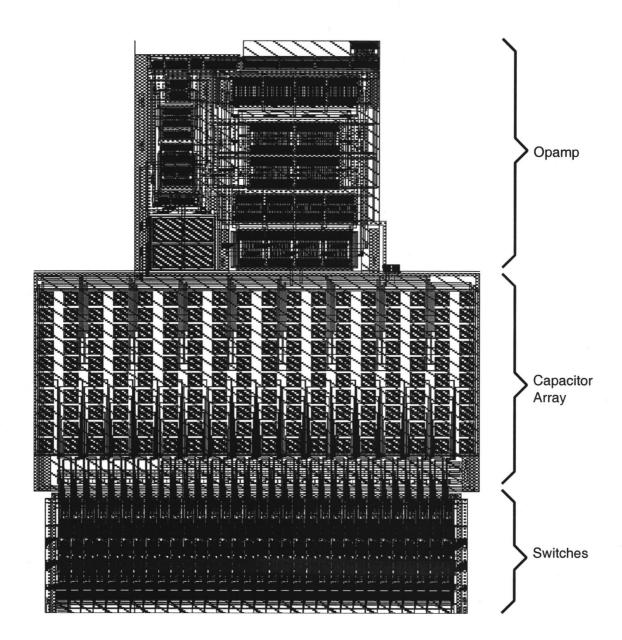

|     | 5.7  | Layout of the front-end integrator                                                                                                                                                                                                               | 94   |

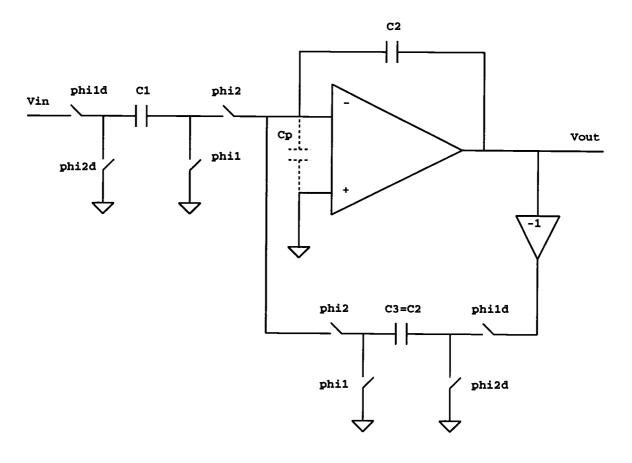

|     | 5.8  | Analog implementation of one clock period delay                                                                                                                                                                                                  | 96   |

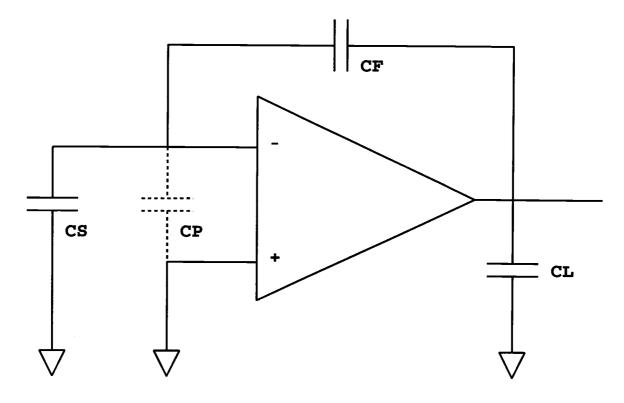

|     | 5.9  | A simplified schematic of the switched-capacitor integrator during $\phi 2$                                                                                                                                                                      | . 98 |

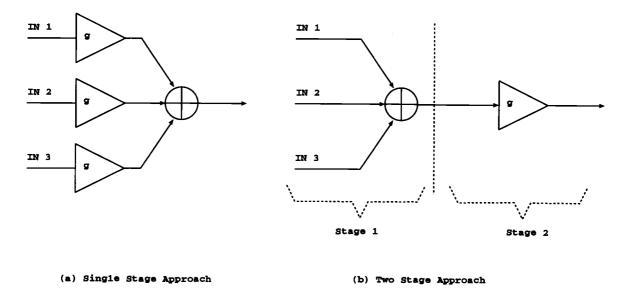

|     | 5.10 | Two approaches to the summing-amplifying block                                                                                                                                                                                                   | 99   |

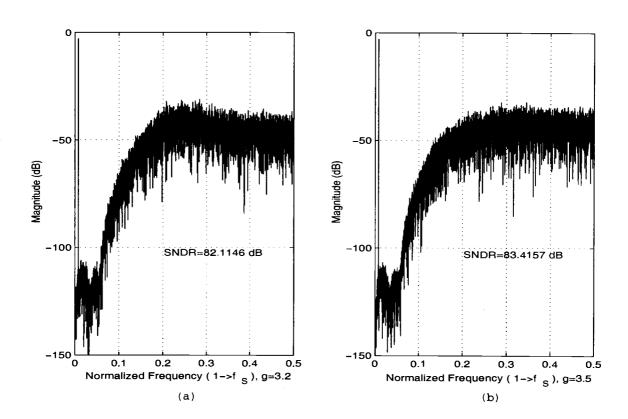

|     | 5.11 | Comparison of coefficient compensation effect on the hybrid $\Delta\Sigma$ modulator, (a) no coefficient compensation (g=3.2), (b) with coefficient compensation (g=3.5)                                                                         | 100  |

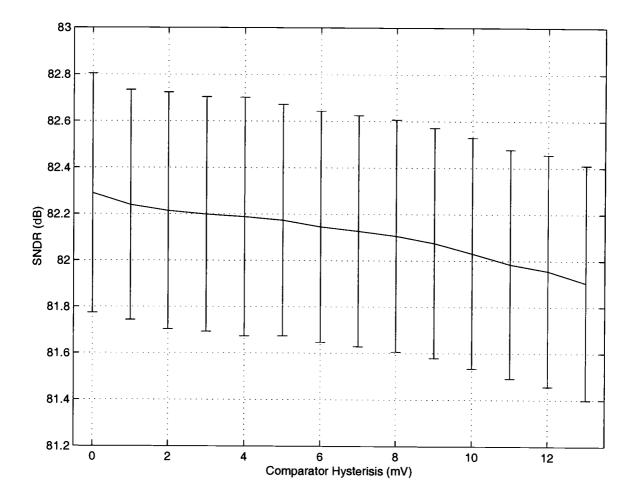

|     | 5.12 | Error bar of the SNDR of the $\Delta\Sigma$ modulator as a function of comparator hysteresis                                                                                                                                                     | 102  |

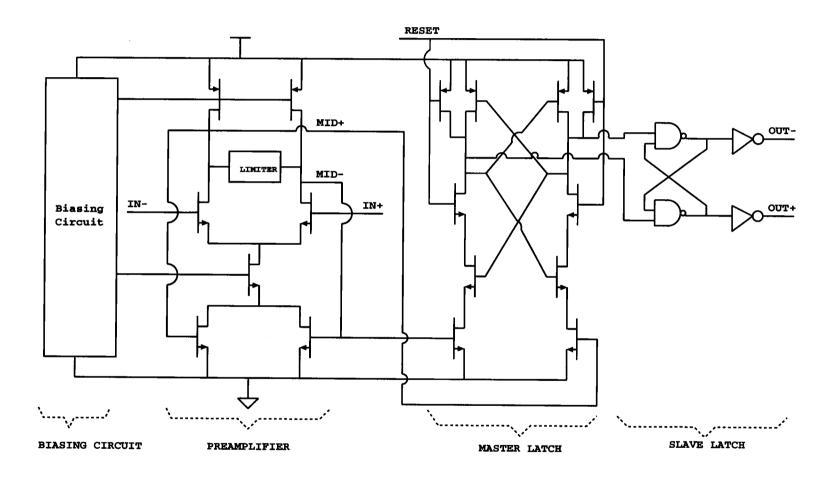

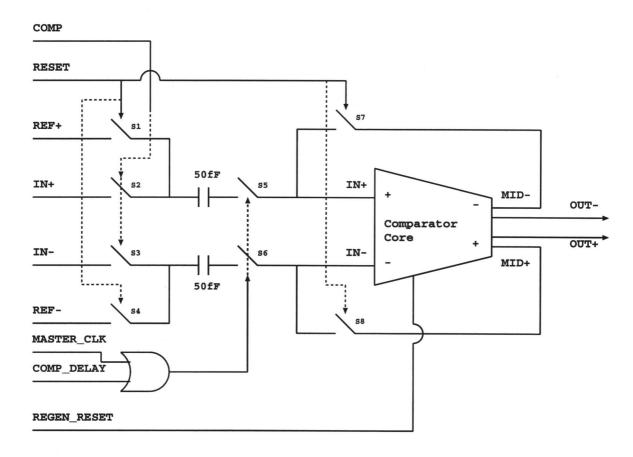

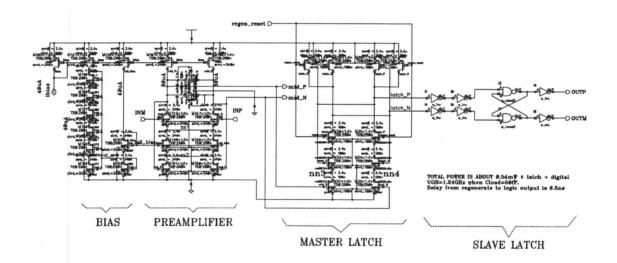

|     | 5.13 | Comparator core of the 4-bit A/D used in the $\Delta\Sigma$ modulator                                                                                                                                                                            | 104  |

|     | 5.14 | Schematic of the comparator cell                                                                                                                                                                                                                 | 105  |

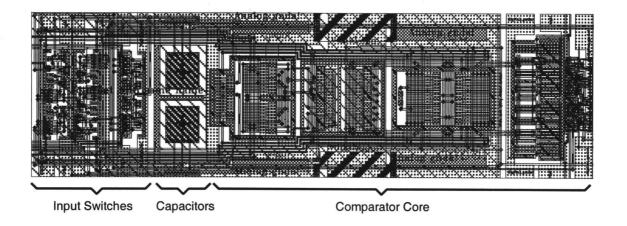

|     | 5.15 | Layout of the comparator cell                                                                                                                                                                                                                    | 105  |

| F'igure |                                                                                                                                                                                                                     | Page  |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

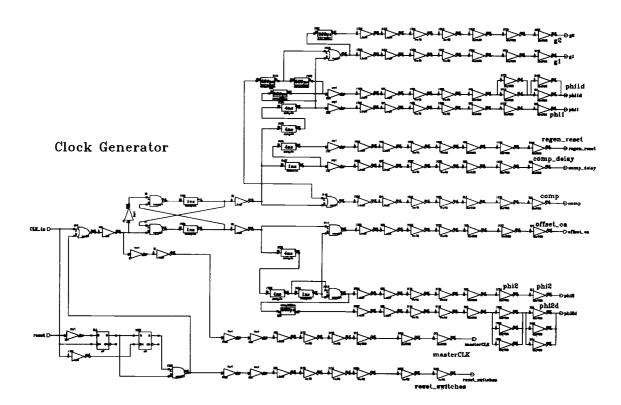

| 5.1     | 6 Schematic of the clock generator                                                                                                                                                                                  | . 106 |

| 5.1     | 7 Timing diagram of the clock generator.                                                                                                                                                                            | . 107 |

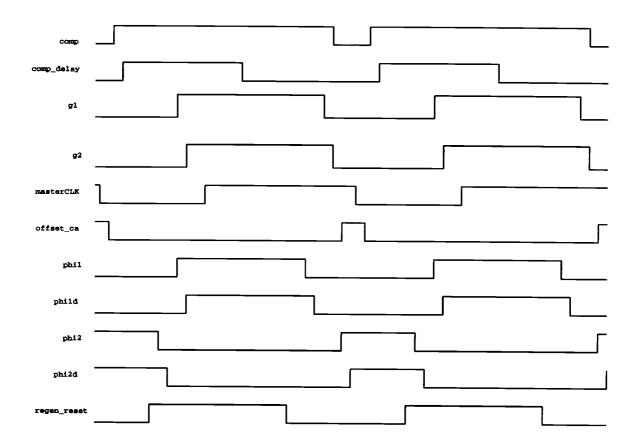

| 5.1     | 8 Block diagram of the data weighted averaging logic                                                                                                                                                                | 109   |

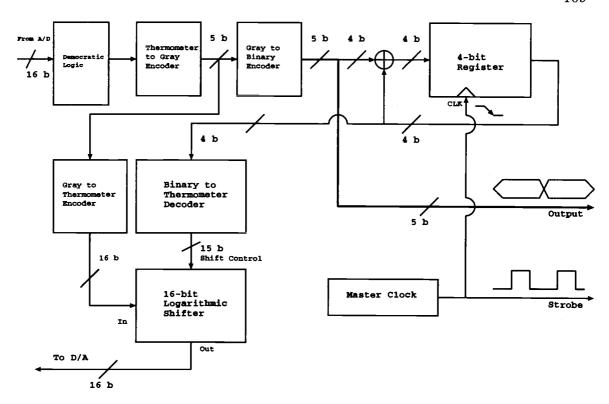

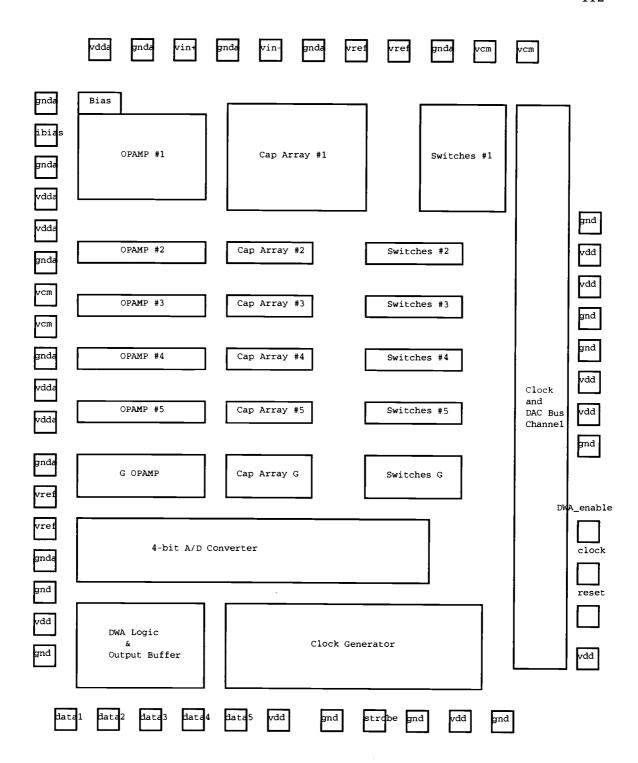

| 5.1     | 9 Floorplan of the fifth-order $\Delta\Sigma$ modulator                                                                                                                                                             | 112   |

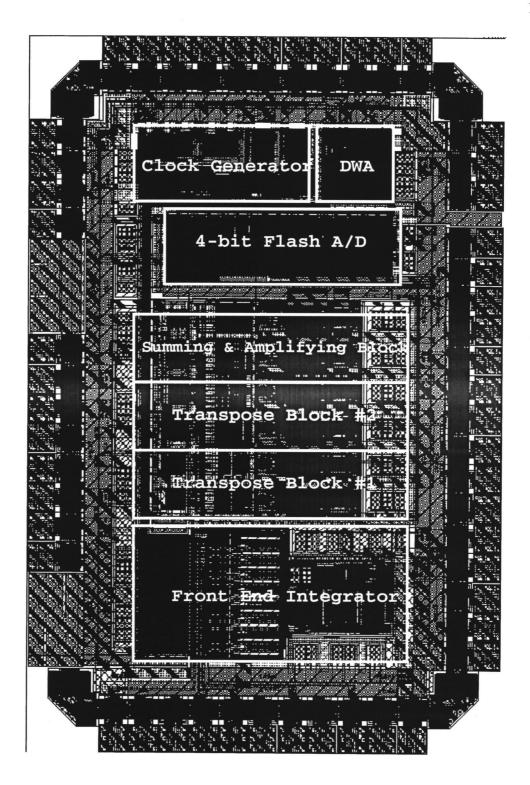

| 5.2     | 0 Layout of the fifth-order hybrid $\Delta\Sigma$ A/D converter                                                                                                                                                     | 113   |

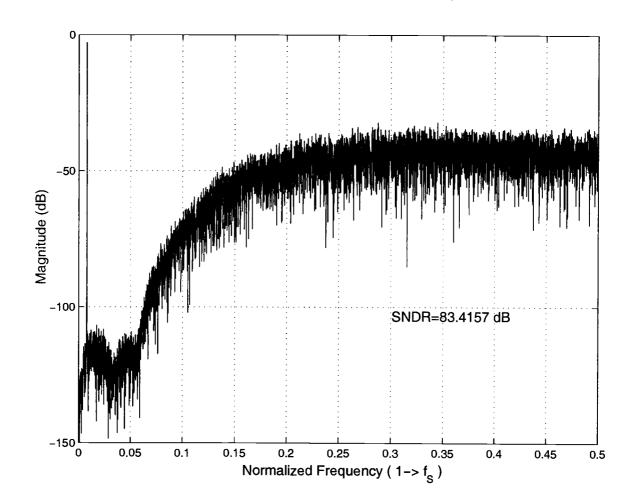

| 5.2     | 1 Simulated spectrum of the fifth-order $\Delta\Sigma$ modulator obtained from Switcap2                                                                                                                             | 114   |

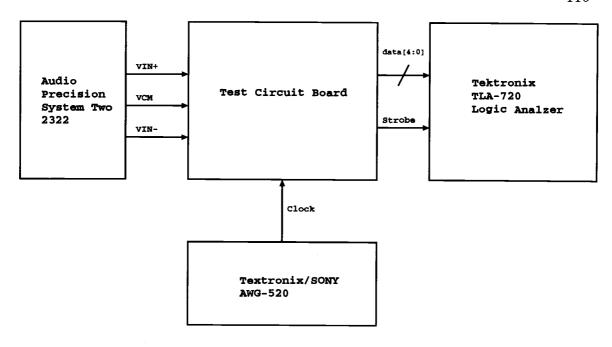

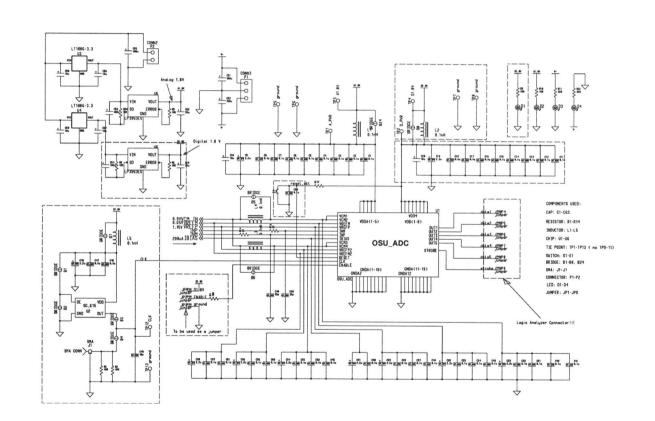

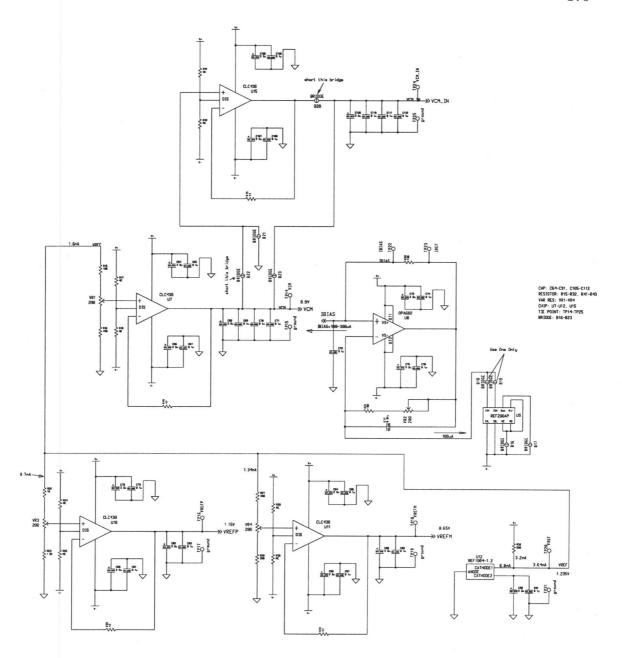

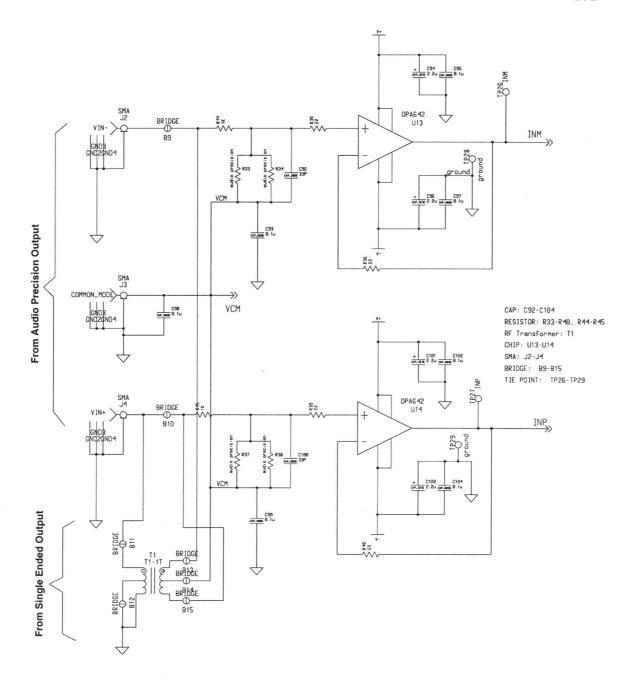

| 6.1     | Block diagrm of the $\Delta\Sigma$ A/D test circuit setup                                                                                                                                                           | 116   |

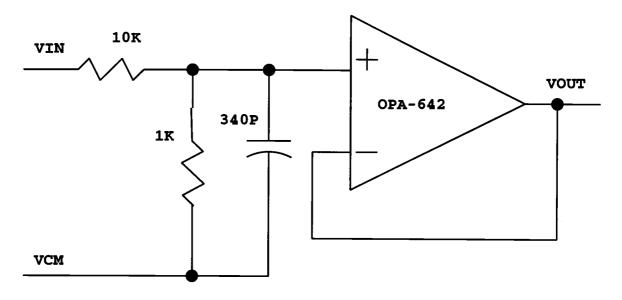

| 6.2     | The attenuator at the input of the A/D converter                                                                                                                                                                    | 117   |

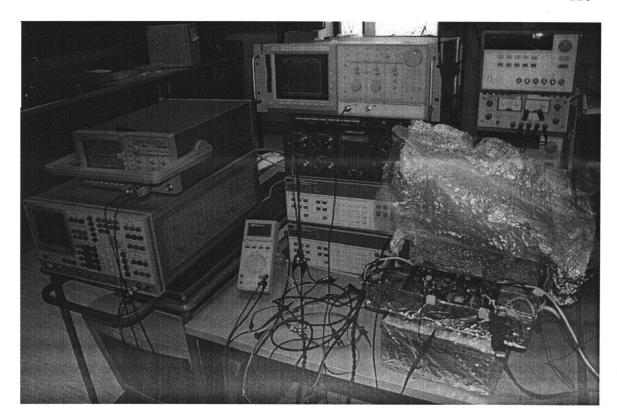

| 6.3     | Photo of the test equipment of the $\Delta\Sigma$ A/D converter                                                                                                                                                     | 118   |

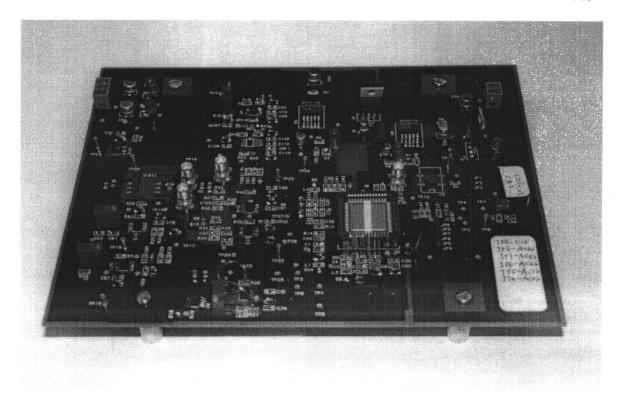

| 6.4     | Photo of the test circuit board with the $\Delta\Sigma$ A/D converter                                                                                                                                               | 119   |

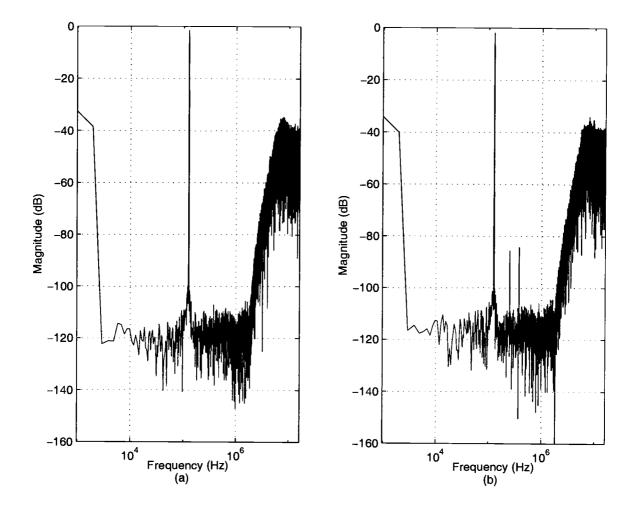

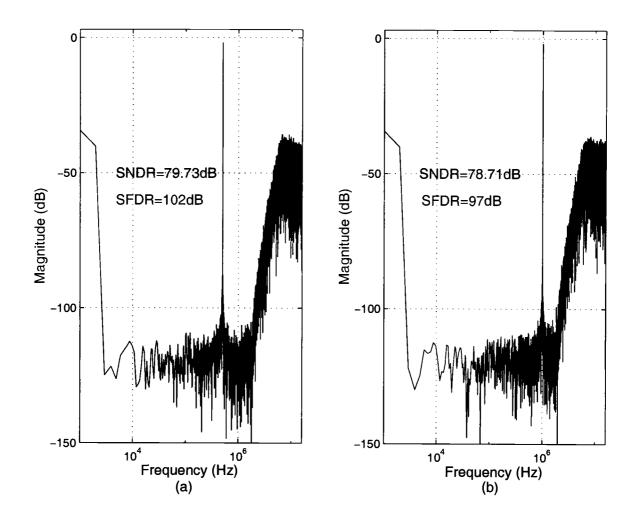

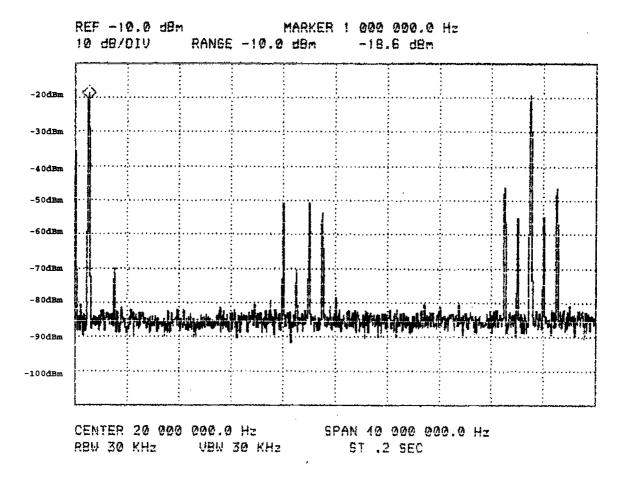

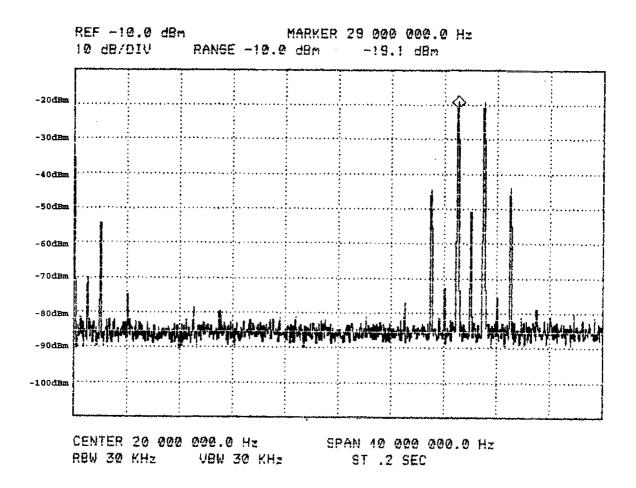

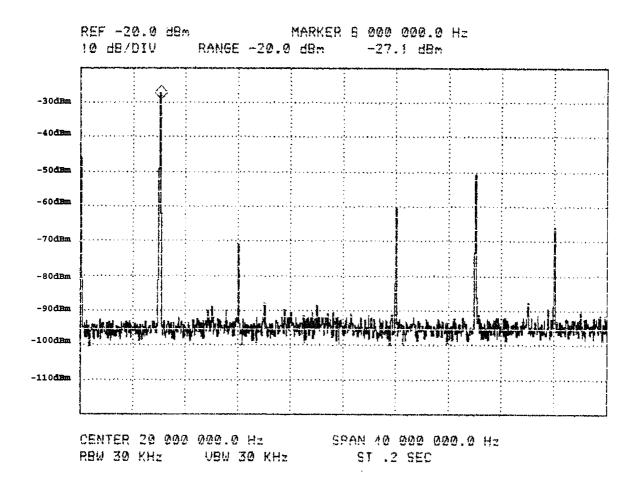

| 6.5     | Measured spectra of the $\Delta\Sigma$ modulator with a clock frequency of 32 MHz and an input signal frequency of 125KHz. (a) SNDR=81.63dB with the DWA algorithm, and (b) SNDR=76.80 dB without the DWA algorithm | 120   |

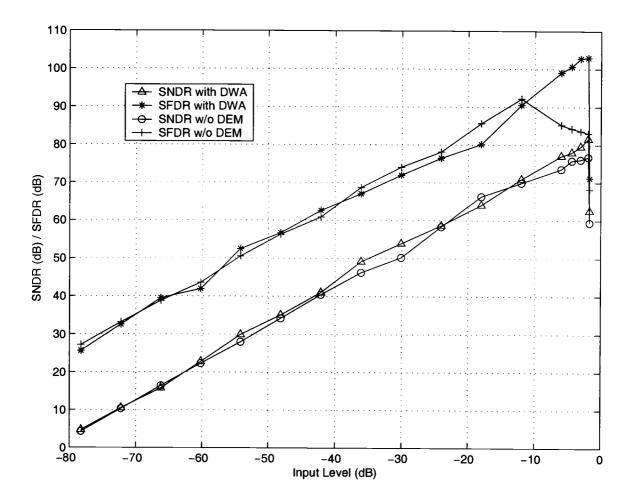

| 6.6     | Measured SNDR and SFDR as a function of the input signal level with a clock frequency of 32 MHz and an input frequency of 125KHz                                                                                    | . 121 |

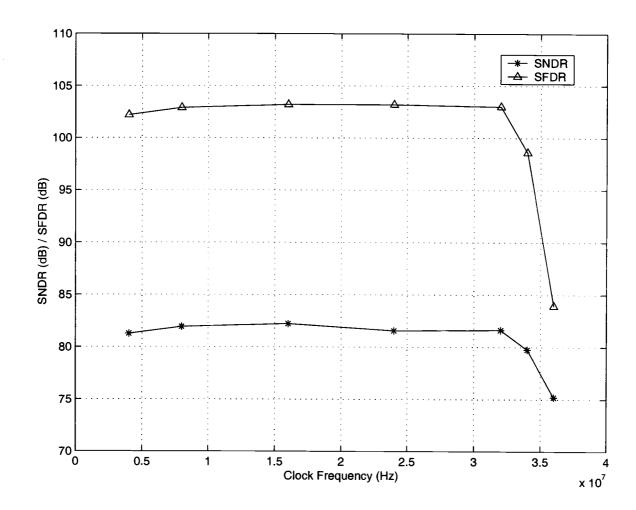

| 6.7     | Measured maximum SNDR and maximum SFDR as a function of clock frequency, the input signal is 125KHz.                                                                                                                | 122   |

| 6.8     | Measured spectra of the $\Delta\Sigma$ A/D converter with different input signal frequencies and a 32MHz clock, (a) $f_{in}$ =500KHz, (b) $f_{in}$ =1MHz                                                            | 123   |

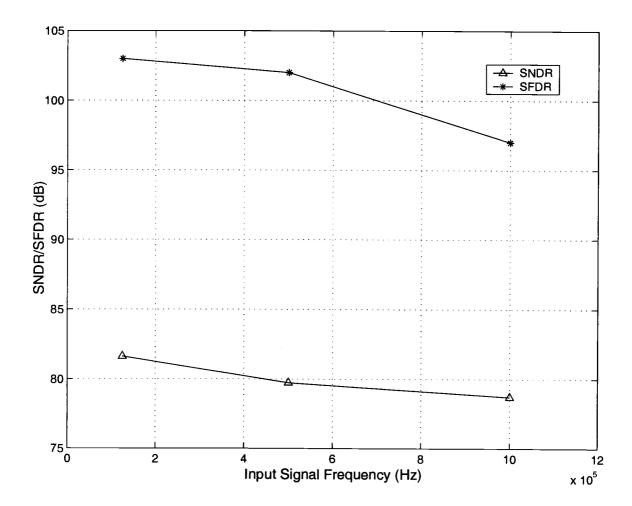

| 6.9     | Measured SNDR and SFDR as a function of input signal frequency with a 32MHz clock                                                                                                                                   | 124   |

| 6.1     | ) Figure of merits of some low oversampling $\Delta\Sigma$ A/D converters                                                                                                                                           | 128   |

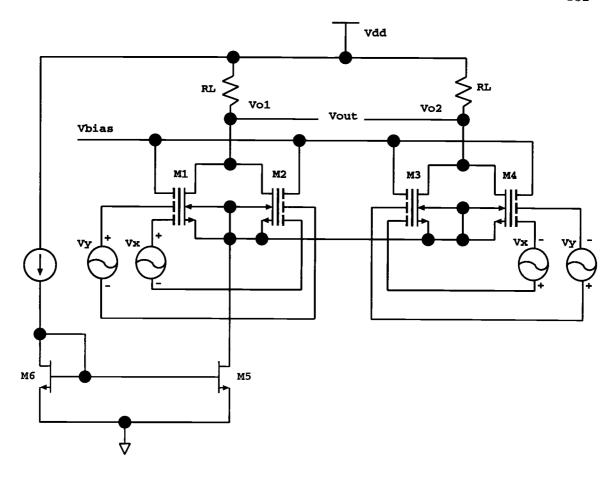

| 7.1     | Schematic of the multi-input floating-gate multiplier                                                                                                                                                               | 132   |

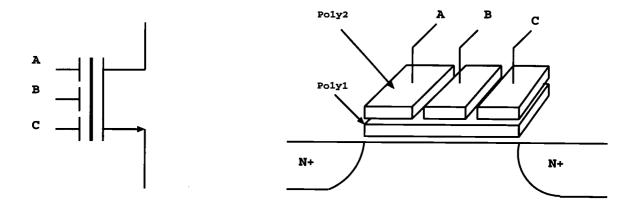

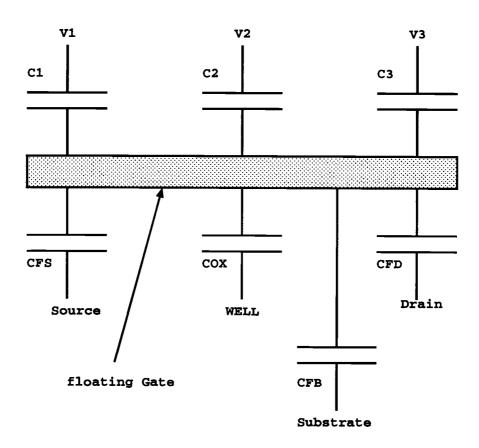

| 7.2     | Illustration of a multi-input floating-gate MOSFET                                                                                                                                                                  | 133   |

| Figure |                                                                                                                                                                                               | Page |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 7.3    | Illustration of all capactiors connected to the floating gate                                                                                                                                 | 134  |

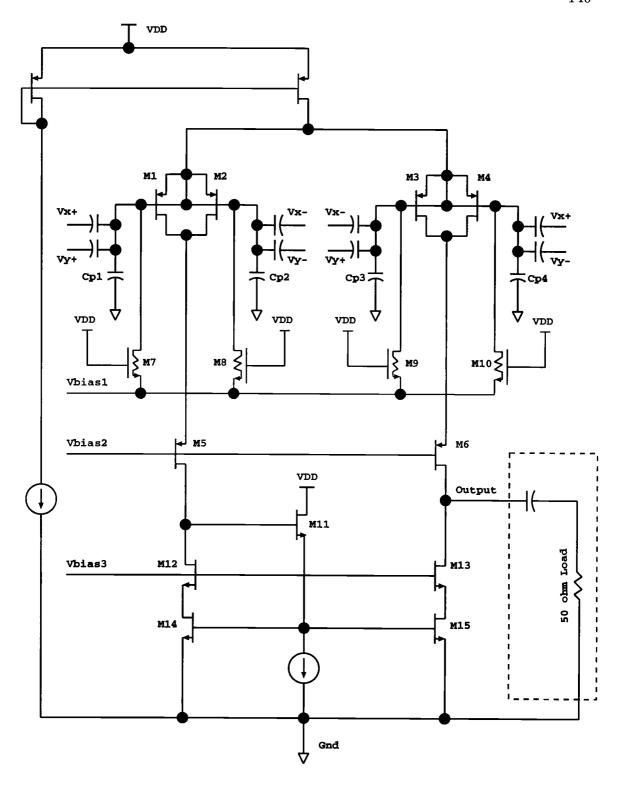

| 7.4    | Schematic of the new multiplier                                                                                                                                                               | 140  |

| 7.5    | Simulated down conversion output spectrum of the multiplier where one input is $64 \text{MHz} \ 0.8 V_{P-P}$ and one input is $70 \text{MHz} \ 0.8 \text{Vp-p}$ . The output THD is $0.290\%$ | 141  |

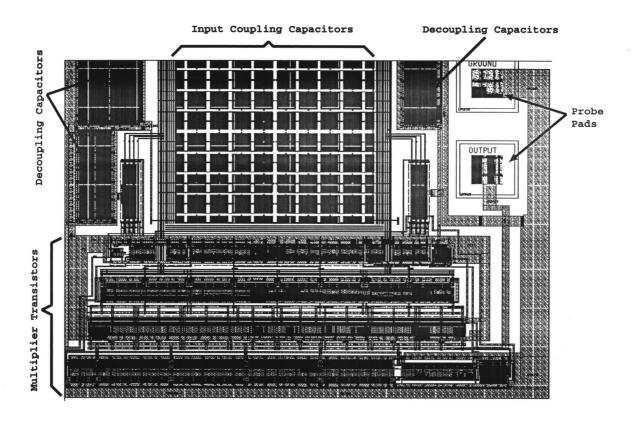

| 7.6    | Layout of the multiplier                                                                                                                                                                      | 142  |

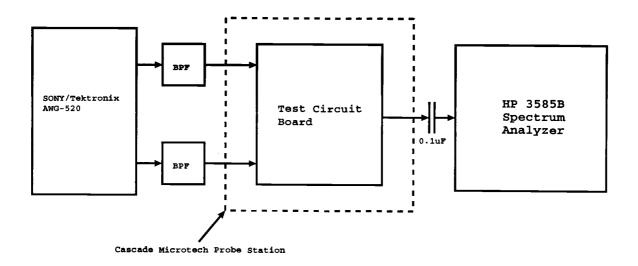

| 7.7    | Test equipment setup of the multiplier                                                                                                                                                        | 143  |

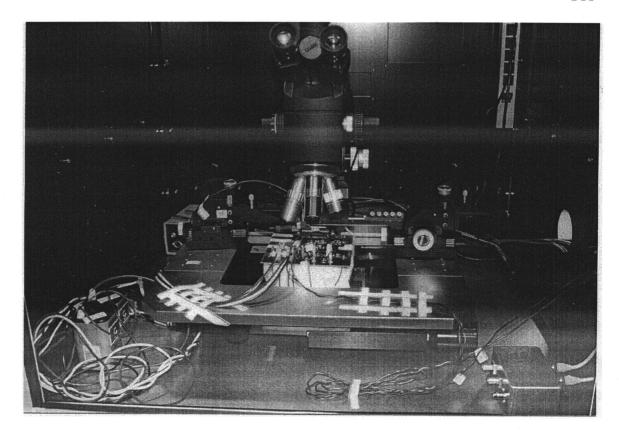

| 7.8    | Photo of the probe station and the test circuit board                                                                                                                                         | 144  |

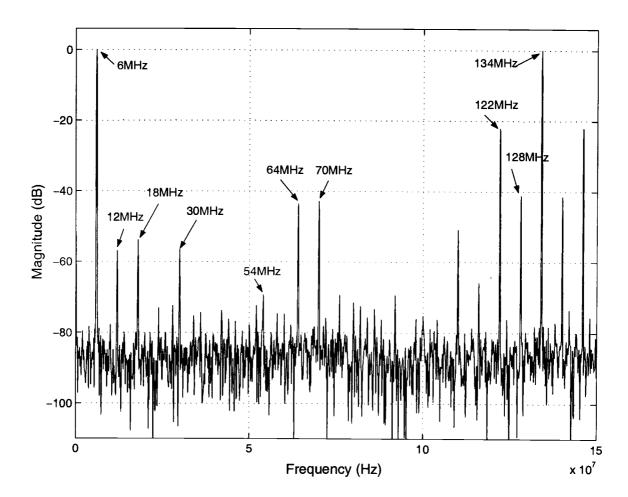

| 7.9    | Measured spectrum of the down conversion with two input signals at 17 MHz and 18 MHZ, respectively                                                                                            | 145  |

| 7.10   | Measured spectrum of the up conversion with two input signals at 1 MHz and 30 MHZ, repsectively                                                                                               | 146  |

| 7.11   | Measured spectrum of the down conversion with two input signals at 30 MHz and 36 MHZ, repsectively                                                                                            | 147  |

### LIST OF TABLES

| $\overline{\Gamma able}$ |                                                                                                                                                                                                   | Page  |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 3.1                      | The coefficients of the fifth-order leapfrog $\Delta\Sigma$ A/D converter of Fig. 3.1 with $  H  _{\infty}=1.5$ and $  H  _{\infty}=6$                                                            | 38    |

| 4.1                      | The coefficients of a fifth-order Hybrid $\Delta\Sigma$ A/D converter (shown in Fig. 4.3) for $\ H\ _{\infty} = 1.5$ and $\ H\ _{\infty} = 6$ before coefficient scaling                          | 53    |

| 4.2                      | The pole/zero sensitivity of the fifth-order hybrid $\Delta\Sigma$ A/D converter shown in Fig. 4.3 to circuit coefficient variations with $\ H\ _{\infty} = 6$                                    | 73    |

| 4.3                      | The pole/zero sensitivity of the fifth-order leapfrog $\Delta\Sigma$ A/D converter (shown in Fig. 3.1) to circuit coefficient variations with $  H  _{\infty} = 6$                                | 74    |

| 4.4                      | The coefficient values of the fifth-order hybrid $\Delta\Sigma$ modulator before and after coefficient quantization with $\ H\ _{\infty} = 6$                                                     | 75    |

| 5.1                      | Specifications of the front-end opamp with a capacitive load of 8 pF.                                                                                                                             | 90    |

| 6.1                      | Specifications of the Fifth-Order Hybrid $\Delta\Sigma$ A/D Converter with a Clock Frequency of 32 MHz and an Input Signal Frequency of 125 KHz                                                   | z.125 |

| 6.2                      | Comparison of this design and some previous designs                                                                                                                                               | 127   |

| 7.1                      | The W/L of the Transistors Shown in Fig. 7.4                                                                                                                                                      | 136   |

| 7.2                      | Specifications of the multiplier. For the up conversion, the two input signals are 1MHz and 30MHz, respectively. For the down conversion, the two input signals are 17MHz and 18MHz, respectively | 148   |

### LIST OF APPENDICES

| Appendix |   |                                                                                                                               | Page |

|----------|---|-------------------------------------------------------------------------------------------------------------------------------|------|

|          | A | Mathematica Solutions of the Coefficients of the Fifth-Order Leapfrog $\Delta\Sigma$ Modulator for Different $\ H\ _{\infty}$ | 156  |

|          | В | Switcap2 Simulation Source Code of the Fifth-Order Hybrid $\Delta\Sigma$ Modulator                                            | 158  |

|          | C | Schematic of the Front-End Opamp and the Comparator Core                                                                      | 167  |

|          | D | Schematic of the Printed Circuit Board for the Hybrid $\Delta\Sigma$ Modulator A/D Testing                                    | 169  |

### LIST OF APPENDIX FIGURES

| Figure |                                           | Page  |

|--------|-------------------------------------------|-------|

| C.1    | Schematic of the front-end opamp          | . 167 |

| C.2    | Schematic of the comparator core          | . 168 |

| D.1    | Main schematic of the PCB                 | . 169 |

| D.2    | Biasing and reference circuits of the PCB | . 170 |

| D.3    | Input amplifiers of the PCB               | . 171 |

# DESIGN OF A 1.8-V 14-BIT $\Delta$ – $\Sigma$ A/D CONVERTER WITH 8X OVERSAMPLING AND 4 MHZ NYQUIST OUTPUT RATE

#### 1. INTRODUCTION

#### 1.1. Motivation

The idea of delta-sigma ( $\Delta\Sigma$ ) modulation emerged long before it was practical for integrated circuit implementation [1]. In the late 1980's, the rapid advances in VLSI technologies made  $\Delta\Sigma$  modulators the most attractive way of implementing high resoultion low to medium speed A/D converters. Unlike conventional Nyquistrate A/D converters,  $\Delta\Sigma$  A/D converters can achieve 16-bit or higher resolution without imposing stringent requirements on device matching [2] .

In recent years, high speed data communications have become one of the most promising applications for the IC industry. High speed data communications, such as xDSL, require high resolution and wideband A/D converters with high dynamic range and high linearity.  $\Delta\Sigma$  A/D converters can achieve high dynamic range and high linearity more readily than Nyquist-rate A/D converters such as pipelined and two-step A/D converters. In these applications, the typical oversampling ratio (OSR) of  $\Delta\Sigma$  A/D converters varies from 32 to 256. To achieve wide bandwidth, the oversampling ratio must be reduced. Reducing the oversampling ratio will lead to a significant reduction in the signal-to-noise ratio (SNR). Thus, with the existing

design approaches for  $\Delta\Sigma$  A/D converters, both high bandwidth and high resolution are not feasible.

Many low oversampling  $\Delta\Sigma$  A/D converters have been reported [3], [4], [5], [6]. These A/D converters have up to 1.25MHz input signal bandwidth. In [3], a 2-0 MASH structure is used. The first stage is a second-order  $\Delta\Sigma$  modulator with a 5-bit quantizer. The second stage is a 10-bit pipelined A/D converter with correction logic. The chip consumes 550mW with 5V power supply. And the total die size is 5.7 X 6.2  $mm^2$ . To achieve wide bandwidth, the chip is very complex and requires excessive die area. The complexity and large area make  $\Delta\Sigma$  A/D converters less attractive than Nyquist converters, because Nyquist A/D converters can achieve similar specifications with similar area and power consumption [38]. Thus, it is very important to find a simple and robust  $\Delta\Sigma$  modulator structure, which is capable of implementing high resolution and wide bandwidth with low power dissipation and small die area.

#### 1.2. Dissertation Organization

In this dissertation, the role of Maximum out-of-band Quantization Noise Gain ( $\|H\|_{\infty}$ ) is explored in the design of high bandwidth  $\Delta\Sigma$  A/D converters. It is found that high signal-to-noise ratio (SNR) with low oversampling in  $\Delta\Sigma$  A/D converters can be achieved by maximizing the  $\|H\|_{\infty}$ . To realize this performance, a new  $\Delta\Sigma$  modulator structure is developed that directly maps the pole and zero locations to the integrator coefficients. The final implementation is easy to design, insensitive to coefficient variation and achieves the best performance reported to date. This dissertation is organized as follows:

Chapter 2 shows that  $\|H\|_{\infty}$  is a very important parameter for  $\Delta\Sigma$  modulators, especially when the oversampling ratio is low. By increasing  $\|H\|_{\infty}$  from a typical value of between 1.5 and 2 to between 5 and 6, the signal-to-noise ratio of  $\Delta\Sigma$  modulators can be increased greatly compared with other  $\Delta\Sigma$  modulators with a low  $\|H\|_{\infty}$ . The relationships between  $\|H\|_{\infty}$ , oversampling ratio, signal band tones and SNR are provided. The minimum  $\|H\|_{\infty}$  for a particular oversampling ratio is given, which shows that Lee's rule [8] is an approximation that is effective for only high oversampling ratios. It is shown that  $\|H\|_{\infty}$  should be greater than 2 to avoid corrupting the *spurious free dynamic range* (SFDR) of  $\Delta\Sigma$  modulators, when low oversampling is used.

Chapter 3 is a review of existing low oversampling  $\Delta\Sigma$  A/D converters which describes the relationship between the A/D converter topologies and the circuit parameters. By dissecting a typical high-order  $\Delta\Sigma$  modulator, it is shown that existing  $\Delta\Sigma$  modulators tend to be unstable when  $\|\mathbf{H}\|_{\infty}$  goes up even with multibit quantizers.

In Chapter 4, a novel  $\Delta\Sigma$  structure called a hybrid structure is presented. This structure provides a direct mapping from the  $\Delta\Sigma$  modulator coefficients to the pole/zero locations of the noise transfer function (NTF). This structure can implement a high  $\|H\|_{\infty}$  with very low sensitivity to coefficient variations and can tolerate low DC gain of the opamps. The design methodology of the hybrid  $\Delta\Sigma$  modulator is also described in this chapter.

Chapter 5 describes the design of a 1.8-V 14-bit hybrid  $\Delta\Sigma$  A/D with 8X oversampling and 2 MHz input signal bandwidth. Design considerations for the front-end integrator, delay blocks, comparators, charge injection, clock timing and digital-to-analog (DAC) performance are discussed in detail. The results of Monte Carlo simulations and the comparison of commonly used dynamic element match-

ing techniques (DEM) in DACs are also provided. Layout design, including the floorplan, cell design and final chip layout, is also included in this chapter.

Chapter 6 shows the measurement results and conclusions of this  $\Delta\Sigma$  A/D converter. The chip is tested with a single 1.8 volt power supply and measurement results are provided. This chip achieves 81.63dB SNDR and 103dB SFDR with 8X oversampling in an active die area of 2.86  $mm^2$ . The power dissipation is 102mW for the analog circuitry and 47mW for the digital circuitry. This is the first  $\Delta\Sigma$  A/D ever reported that can achieve 14-bit resolution and 2 MHz input signal bandwidth with a single 1.8-V power supply. The results show that the hybrid  $\Delta\Sigma$  A/D converter is suitable for high resolution, wide bandwidth applications.

Chapter 7 describes the design of an important block used in analog signal processing: the multiplier. A new double balanced multiplier based on the multiinput floating-gate multiplier is presented [45]. The multiplier is devised to make

it suitable for down converting high frequency signals. The harmonic distortion

due to systematic errors and random errors is discussed. This chip is fabricated

in a  $0.35\mu m$  double poly triple metal CMOS process. Measurements show that

this multiplier achieves 0.25% total harmonic distortion. This linearity is difficult

to achieve with conventional multipliers based on the Gilbert six transistor cell.

Measurement results show that this multiplier is suitable for use in dual IF receivers.

# 2. THE INFLUENCE OF MAXIMUM OUT-OF-BAND QUANTIZATION NOISE GAIN ON $\Delta\Sigma$ A/D PERFORMANCE

#### 2.1. Introduction to Quantization Noise of $\Delta\Sigma$ Modulators

A simple first-order  $\Delta\Sigma$  modulator is shown in Fig. 2.1. The quantizer is represented by an adder which sums its input signal y and a quantization noise  $e_i$ . The variables u, y, v denote the input signal, the quantizer input and the quantizer output, respectively. At time t = n, the output v[n] is:

$$v[n] = u[n-1] + (e_i[n] - e_i[n-1])$$

(2.1)

The corresponding Z-domain function is:

$$V = UZ^{-1} + E_i(1 - Z^{-1}) (2.2)$$

The output V is a function of input, U, and quantization noise,  $E_i$ . The above equation can be expressed as:

$$V = USTF(Z) + E_iNTF(Z) (2.3)$$

where STF(Z) denotes the signal transfer function and NTF(Z) denotes the quantization noise transfer function. In this example, STF(Z) is simply a delay. Thus, the input signal is passed to the output after one clock cycle delay. NTF(Z) is a first-order difference function and in the frequency domain, the amplitude response of  $NTF(\omega)$  is:

$$|NTF(\omega)| = 2\sin(\omega T/2) \tag{2.4}$$

where T is the period of the sampling clock,  $f_s$ . When the input signal frequency is much higher than the sampling frequency  $f_s$ , the amplitude in (2.4) will be very small at low frequencies. As a result, the baseband quantization noise will be greatly attenuated when high oversampling is used. This filtering of the noise is referred to as noise shaping.

FIGURE 2.1. Block diagram of a first-order  $\Delta\Sigma$  modulator.

If we assume the quantization noise is a white gaussian noise, the average quantization noise power is  $\frac{\Delta^2}{12}$ , where  $\Delta$  is the least significant bit (LSB) of the quantizer. The output mean square baseband noise power can be obtained by integrating the noise-shaped quantization noise over the baseband:

$$P_N = \int_{-\omega_B}^{+\omega_B} |NTF(\omega)|^2 \frac{\Delta^2}{12\omega_S} d\omega \approx (\frac{\pi^2}{3})(\frac{1}{M^3})\frac{\Delta^2}{12}, M >> 1$$

(2.5)

where  $P_N$  is the mean square noise power,  $\omega_B$  is the signal bandwidth,  $NTF(\omega)$  is the noise transfer function described in (2.4), and  $M=\frac{2\omega_B}{\omega_S}$  is defined as the oversampling ratio. For a  $\Delta\Sigma$  modulator with an N-bit quantizer, the maximum sinusoidal input has an amplitude of  $\frac{(2^N-1)\Delta}{2}$ . The power of the maximum sinusoidal input is then:

$$P_S = \frac{(2^N - 1)^2 \Delta^2}{8} \tag{2.6}$$

and the dynamic range (DR) of the first-order  $\Delta\Sigma$  modulator with a multi-bit quantizer can be obtained from (2.5) and (2.6) as:

$$DR = \frac{P_S}{P_N} = \frac{3}{2} (\frac{3}{\pi^2})(2^N - 1)^2 M^3, M >> 1$$

(2.7)

From (2.7), it can be seen that every doubling of the oversampling ratio, M, will result in 9 dB (i.e. 1.5 bit) dynamic range increase compared with 6 dB dynamic range increase that can be observed in Nyquist rate A/D converters. Thus increasing the oversampling ratio M is an effective way of increasing the dynamic range.

A second-order  $\Delta\Sigma$  modulator is shown in Fig. 2.2. Similar to the first-order  $\Delta\Sigma$  modulator, the output V is:

$$V = UZ^{-1} + E_i(1 - Z^{-1})^2 (2.8)$$

The noise transfer function is a second-order difference. The corresponding amplitude response of the noise transfer function is:

$$|NTF(\omega)| = (2\sin(\omega T/2))^2 \tag{2.9}$$

The dynamic range of the second-order  $\Delta\Sigma$  modulator is:

$$DR = \frac{3}{2}(\frac{5}{\pi^4})(2^N - 1)^2 M^5, M >> 1$$

(2.10)

Comparing (2.10) with (2.7), we see that, for a second-order  $\Delta\Sigma$  modulator, each doubling of M results in 15 dB increase (i.e., 2.5 bit) in dynamic range. Thus, increasing the order of a  $\Delta\Sigma$  modulator is another effective way to increase the dynamic range.

FIGURE 2.2. Block diagram of a second-order  $\Delta\Sigma$  modulator.

The topology of an L-th order  $\Delta\Sigma$  modulator is shown in Fig. 2.3. The output V is:

$$V = UZ^{-1} + E_i(1 - Z^{-1})^L (2.11)$$

The above equation shows that the noise transfer function NTF(Z) is an L-th order difference. In the frequency domain, the amplitude of the L-th order noise transfer function is:

$$|NTF(\omega)| = (2\sin(\omega T/2))^L \tag{2.12}$$

For an L-th order  $\Delta\Sigma$  modulator, each doubling of oversampling ratio M results in approximately (6L+3) dB dynamic range increase, which is close to

FIGURE 2.3. Block diagram of an L-th order  $\Delta\Sigma$  modulator.

(L+0.5) bit/octave. If L is a large number, the modulator can achieve very high dynamic range with a high oversampling ratio M as shown below.

$$DR = \frac{3}{2} \left(\frac{2L+1}{\pi^{2L}}\right) (2^N - 1)^2 M^{2L+1}, \ M >> 1$$

(2.13)

In Section 2.1, all equations are obtained based on the assumption that the quantization noise is white noise, where the quantization noise is flat over the spectrum. Actually, the characteristics of the quantization noise spectra depends on many factors such as the order of the modulator, input signal amplitude and maximum out-of-band quantization noise gain to name a few. The relationships between them are very complicated, since  $\Delta\Sigma$  modulators are virtually non-linear systems. The purpose of this section is to provide an intuitive explanation of these relationships.

For a  $\Delta\Sigma$  modulator, an input signal passes through each integrator before it reaches the quantizer input node. After passing through each integrator, the signal is scrambled by signals such as the DAC feedback signals, local feedback signals and feedforward signals. As a result, the output signal will be less correlated with the original input signal. If a high-order  $\Delta\Sigma$  modulator is used, the signal will be

scrambled many times. It will become uncorrelated with the original quantizer input signal, and very few if any tones will be detected at the output.

If a low order  $\Delta\Sigma$  modulator is employed, the input signal is not scrambled enough before it reaches the quantizer input. Thus the quantizer output code is somewhat correlated with the original input. The quantization noise will have a periodic component whose period is the same as the original input signal. As a result, the output will contain tones in the signal bandwidth due to the correlated quantization noise.

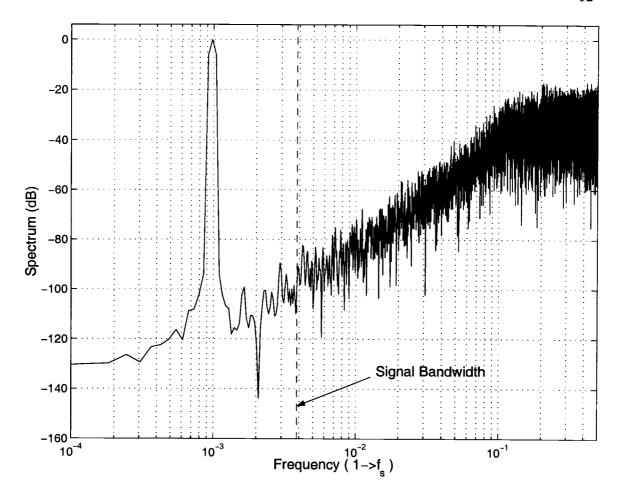

Figure 2.4 is the spectrum of the first-order  $\Delta\Sigma$  modulator with a 1-bit quantizer as shown in Fig. 2.1. Due to the simple structure of the first-order  $\Delta\Sigma$  modulator, there are very large tones in the baseband frequency (for an oversampling ratio of 128). The spurious free dynamic range (SFDR) is only 55dB. Thus, first-order stages are almost never used for practical applications (excluding the first-order  $\Delta\Sigma$  modulators used in MASH  $\Delta\Sigma$  A/D converters).

Figure 2.5 is the spectrum of the second-order single bit  $\Delta\Sigma$  modulator with an OSR of 128 as shown in Fig. 2.2. It can be seen that the tones are significantly reduced compared with the tones of the first-order  $\Delta\Sigma$  modulator. Thus, increasing the order of a  $\Delta\Sigma$  modulator can reduce the tones in the signal band.

When the input signal is a DC signal, it will generate some tones, whose amplitude and frequency depend on the amplitude of the DC input. Let's consider the first-order  $\Delta\Sigma$  modulator shown in Fig. 2.1. To simplify the problem, we assume the  $\Delta\Sigma$  modulator has a 1-bit quantizer and the 1-bit DAC has an output of  $\pm 1$  volt. If the DC input signal amplitude is a rational number of the reference voltage, the output may form a periodic pattern that results in tones in the output spectrum.

FIGURE 2.4. Spectrum of a first-order  $\Delta\Sigma$  modulator with an oversampling ratio of 128.

For example, if the DC input signal is  $\frac{1}{16}$  volt, on average there will be 17 (1)'s and 15 (-1)'s for each 32 clock cycles. As a result, tones will appear with a uniform spacing of  $\frac{1}{32}f_s$  as shown in Fig. 2.6. The tones are very high in amplitude and the first-order noise shaping is corrupted. This kind of noise is called *pattern noise*. Pattern noise is a particularly serious issue for low order  $\Delta\Sigma$  modulators.

FIGURE 2.5. Spectrum of a second-order  $\Delta\Sigma$  modulator with an oversampling ratio of 128.

Maximum out-of-band quantization noise gain ( $\|H\|_{\infty}$ ) is also an important parameter of  $\Delta\Sigma$  modulators. A high  $\|H\|_{\infty}$  will amplify out-of-band quantization noise and attenuate signal band quantization noise. But when  $\|H\|_{\infty}$  is increased, the maximum stable input range will be reduced. For a given  $\Delta\Sigma$  modulator, there is an optimum  $\|H\|_{\infty}$  value for which the modulator can reach the maximum SNR. If  $\|H\|_{\infty}$  is above this value, the maximum stable input range decreases rapidly and the SNR decreases. On the other hand, if  $\|H\|_{\infty}$  is less than this value, the

FIGURE 2.6. Pattern noise spectrum of a first-order  $\Delta\Sigma$  modulator with a -24dB DC input.

signal band quantization noise shaping becomes worse and the SNR again decreases. When choosing  $||H||_{\infty}$ , a trade-off must be made between the stability and the aggressiveness of the noise shaping. It has also been observed that a higher  $||H||_{\infty}$  can help to reduce the tones in the signal band.  $||H||_{\infty}$  has a profound effect on  $\Delta\Sigma$  modulators and its influence will be discussed in detail in the next section of this chapter.

## 2.2. The Relationship Between $\|\mathbf{H}\|_{\infty}$ and $\Delta\Sigma$ Modulator System Performance

In (2.12), it was shown that the L-th order  $\Delta\Sigma$  modulator shown in Fig. 2.3 has a maximum out-of-band quantization noise gain of  $2^L$ . If a 1-bit quantizer is used for a high-order  $\Delta\Sigma$  modulator, quantization noise can be greatly amplified so that the quantizer is overloaded and the  $\Delta\Sigma$  modulator becomes unstable. Thus,  $\Delta\Sigma$  modulators with an order of 3 or greater usually use MASH structures to suppress quantization noise power.

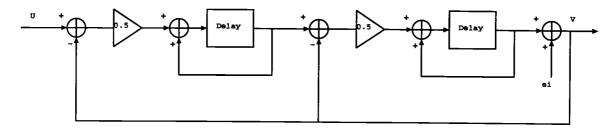

The second-order  $\Delta\Sigma$  modulator shown in Fig. 2.2 has a  $\|H\|_{\infty}$  of 4. Figure 2.7 is a second-order  $\Delta\Sigma$  modulator proposed by B. E. Boser [7]. Compared with the circuit shown in Fig. 2.2, each integrator in this modulator has one clock cycle delay and a -6dB attenuator at the input. The noise transfer function is:

$$NTF(Z) = \frac{(1-Z^{-1})^2}{1-1.5Z^{-1}+0.75Z^{-2}}$$

(2.14)

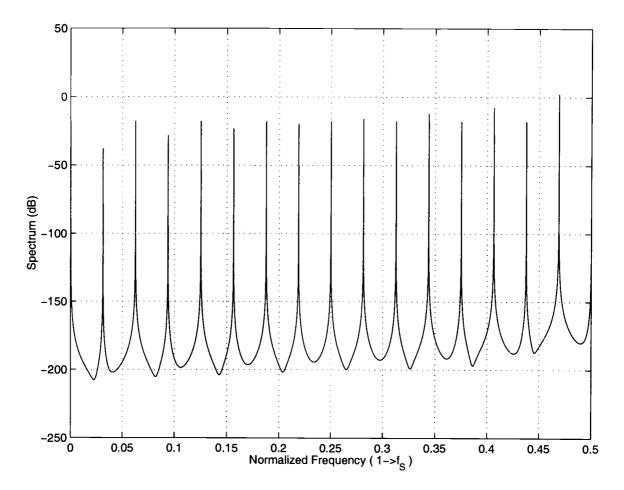

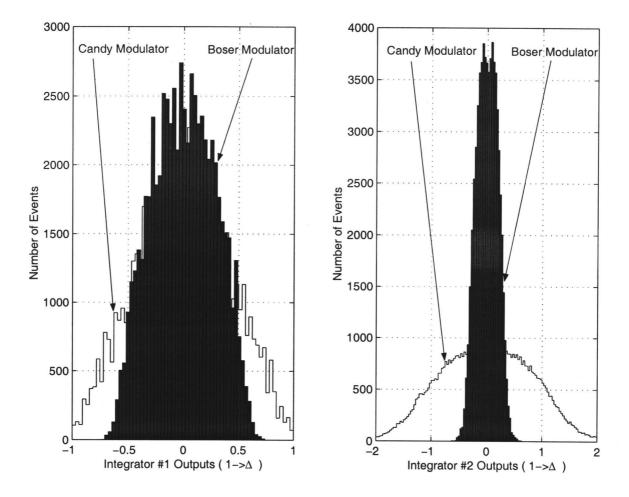

The  $\|H\|_{\infty}$  for (2.14) is 2.3093. By reducing  $\|H\|_{\infty}$  from 4 to 2.3093, the integrator output probability density width is much smaller than that of the modulator shown in Fig. 2.2. The histograms of the two modulators are shown in Fig. 2.8. The modulator proposed by B. E. Boser has a narrower integrator output distribution than the traditional one. This is very important for practical circuit design, since a narrower integrator output distribution implies a wider input signal dynamic range.

The two second-order  $\Delta\Sigma$  modulators shown in Figs. 2.2 and 2.7 have a maximum out-of-band quantization noise gain of 4 and 2.3093, respectively, and they are both stable. For higher order  $\Delta\Sigma$  modulators, stability is a complicated issue. Lee's rule [8] states that high-order  $\Delta\Sigma$  modulators with a 1-bit quantizer

FIGURE 2.7. A second-order  $\Delta\Sigma$  modulator proposed by B. E. Boser.

must have a  $\|H\|_{\infty}$  less than 2 to remain stable. This rule of thumb is derived from simulations and is verified by practical designs [10] [12]. In high-order single stage  $\Delta\Sigma$  modulator designs, typically  $\|H\|_{\infty}$  varies from 1.5 to 2.0.

The quantizers of  $\Delta\Sigma$  modulators are highly non-linear due to their discrete output levels and are overloaded if the input signal is too large. This provides a reasonable guide for high oversampling  $\Delta\Sigma$  A/D converters.

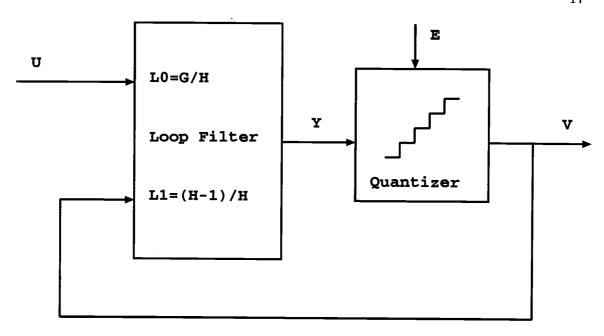

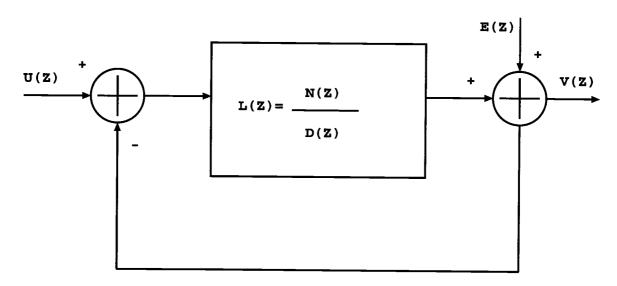

To estimate the stability of  $\Delta\Sigma$  modulators, a linear model with a variable gain can be used [13]. If we assume the quantizer gain is unity, a  $\Delta\Sigma$  modulator can be represented by the block diagram shown in Fig. 2.9. In this figure, the loop filter has two inputs and the output, Y, is a function of input signal, U, and quantizer output, V.

$$Y(Z) = L_0(Z)U(Z) + L_1(Z)V(Z)$$

(2.15)

The quantizer output, V(Z), can also be expressed as a function of the input, U(Z), and the quantization noise, E(Z).

$$V(Z) = G(Z)U(Z) + H(Z)E(Z)$$

(2.16)

FIGURE 2.8. Comparison of integrator output histograms for the traditional and the Boser architecture with sinusoidal input 3dB below overload.

where G(Z) and H(Z) are the signal transfer function (STF) and noise transfer function (NTF), respectively. The relationship between G(Z), H(Z),  $L_0$  and  $L_1$  is:

$$L_0(Z) = \frac{G(Z)}{H(Z)} (2.17)$$

$$L_1(Z) = \frac{H(Z) - 1}{H(Z)} \tag{2.18}$$

FIGURE 2.9. Block diagram of a  $\Delta\Sigma$  modulator.

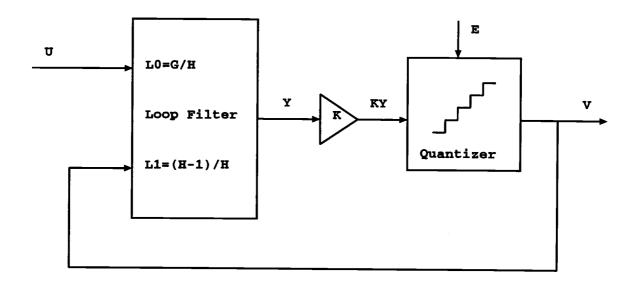

The above linear model has a major drawback in that it assumes the quantization noise, E(Z), is not correlated with the input signal, U(Z). As discussed in Section 2.1, quantization may be correlated to the input signal. To take this into account, a variable gain block is used to represent the quantizer gain as shown in Fig. 2.10. For this model, the output, V(Z), can be expressed as:

$$V(Z) = G'(Z)U(Z) + H'(Z)E'(Z)$$

(2.19)

where

$$E'(Z) = V(Z) - KY(Z) \tag{2.20}$$

$$G'(Z) = \frac{KG(Z)}{K + (1 - K)H(Z)}$$

(2.21)

$$H'(Z) = \frac{H(Z)}{K + (1 - K)H(Z)}$$

(2.22)

Equation (2.22) is the noise transfer function (NTF) of this model. In order to make the new model more accurate than the previous model, we must choose the variable gain K such that the quantization noise, E(Z), and the signal component, V(Z), are uncorrelated. This effect makes the quantization noise and the input signal uncorrelated. The optimum K that satisfies this condition is:

$$K_{opt} = \frac{covariance(y,v)}{variance(y,y)}$$

(2.23)

FIGURE 2.10. Block diagram of a  $\Delta\Sigma$  modulator with a variable gain.

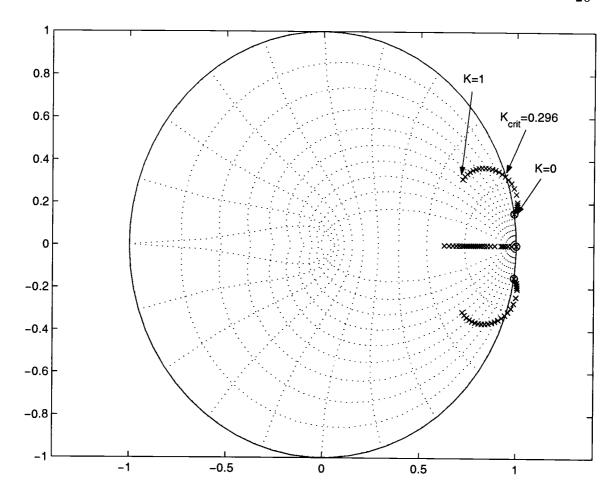

The quantizer gain depends on the modulator structure and the input signal amplitude. As the gain varies, the loop gain also varies, which causes the NTF poles to move. If the NTF poles move out of the unit circle, the quantizer will not be able to bring the modulator output back into the unit circle and the modulator becomes unstable. From (2.23), when the quantizer input y has a very large amplitude, the gain K will drop. A large signal y implies a large input signal y. Thus,  $\Delta\Sigma$  modulators can be unstable if the input signal amplitude is too large. Figure 2.11

shows the NTF root locus of a third-order  $\Delta\Sigma$  modulator. When K is less than the critical value 0.296, the poles are outside of the unit circle and the modulator becomes unstable.

Since the signal y is also a function of the quantization noise, stability also depends on quantization noise. If a  $\Delta\Sigma$  modulator has a high  $\|H\|_{\infty}$ , the quantization noise will be amplified and fed back to the loop filter. This will result in a large signal y. If y is large enough to reduce the quantizer gain K below a certain value, the modulator can be unstable. If the  $\Delta\Sigma$  modulator has a high  $\|H\|_{\infty}$ , it can be unstable even when the input signal amplitude is very small. Thus  $\|H\|_{\infty}$  is very critical in terms of modulator stability. For this reason, the  $\|H\|_{\infty}$  of high order  $\Delta\Sigma$  modulators is typically chosen in the range of 1.5 to 2.

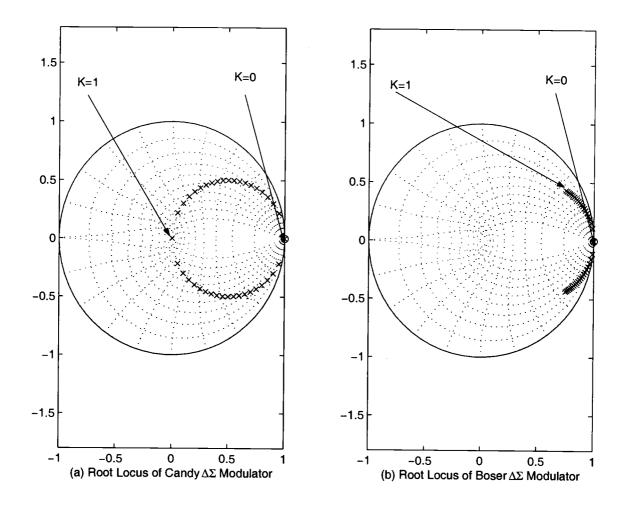

The two  $\Delta\Sigma$  modulators shown in Fig. 2.2 and Fig. 2.7 have  $\|\mathbf{H}\|_{\infty}$  of 4.0 and 2.3093, respectively, and they are both stable. The corresponding root loci are shown in Fig. 2.12. When quantizer gain, K, approaches zero, the poles are still inside the unit circle and consequently, the modulators are always stable even when  $\|\mathbf{H}\|_{\infty}$  is as high as 4.

As previously shown,  $||H||_{\infty}$  is an important factor in determining the  $\Delta\Sigma$  modulator stability. To maintain stability, high order  $\Delta\Sigma$  modulators with a 1-bit quantizer must have a maximum out-of-band quantization noise gain less than 2. Equation (2.13) demonstrates that  $||H||_{\infty}$  has little or no bearing on the dynamic range of the  $\Delta\Sigma$  modulator.

Lee's rule is appropriate for high order  $\Delta\Sigma$  modulators with a 1-bit quantizer. If a multi-bit quantizer is used, quantization noise power will decrease. As a result,  $\|H\|_{\infty}$  can be increased without compromising the stability of the  $\Delta\Sigma$  modulator.

FIGURE 2.11. NTF root locus of a third-order  $\Delta\Sigma$  modulator.

The influence of  $\|H\|_{\infty}$  on  $\Delta\Sigma$  modulators has been explored using state space simulation [11]. When the modulator has a multi-bit quantizer, it is likely that the state space simulation is stable with a high  $\|H\|_{\infty}$ . However, when the implementation of a high-order single-stage multi-bit  $\Delta\Sigma$  modulator with a  $\|H\|_{\infty}$  much higher than 2 is considered, it is found that nearly all existing high-order  $\Delta\Sigma$  modulators become unstable. Thus, many implementations of high-order single-stage  $\Delta\Sigma$  modulators with a multi-bit quantizer have a  $\|H\|_{\infty}$  of approximately 2.

FIGURE 2.12. NTF root loci of two second-order modulators, (a) Candy modulator with  $||H||_{\infty} = 4$  and (b) Boser modulator with  $||H||_{\infty} = 2.3$ .

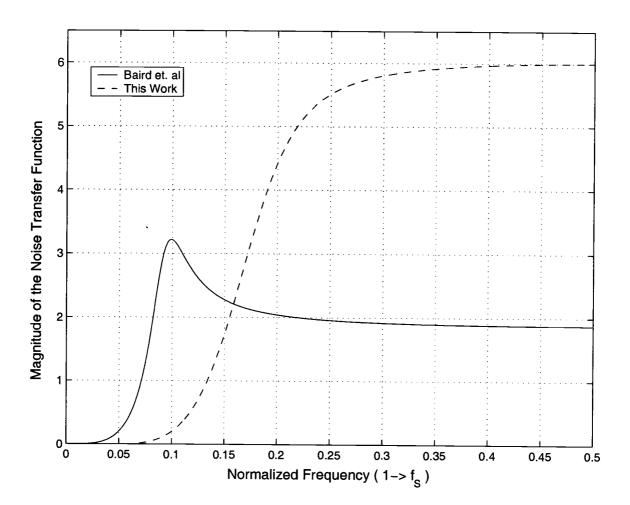

To illustrate this, consider the noise transfer function shown in Fig. 2.13 of the fourth-order  $\Delta\Sigma$  A/D with a 4-bit quantizer in [14]. Although the NTF peaks at 3.1886, a large portion of the NTF is less than 2 and the average out-of-band NTF is close to 2. This  $\Delta\Sigma$  modulator has a 16X oversampling ratio and achieves 14-bit resolution with a 250 kHz input signal bandwidth. The dynamic range estimated by (2.13) is 103.4 dB while the measured dynamic range is 84 dB.

The dashed curve in Fig. 2.13 shows the NTF of a fifth-order  $\Delta\Sigma$  modulator with a 4-bit quantizer. It has an 8X oversampling ratio and  $||H||_{\infty} = 6$ . Since the NTF curve is smooth and there is no peaking, the average out-of-band quantization noise gain is very close to the maximum  $||H||_{\infty}$ . The dynamic range estimated by (2.13) is 85.3 dB and the measured dynamic range is 83dB.

FIGURE 2.13. Comparison of two noise transfer functions, The solid line is for a 4th order  $\Delta\Sigma$  modulator with a 4-bit quantizer and the dotted line is for a 5th order modulator with a 4-bit quantizer.

When  $\|H\|_{\infty}$  is high, it can boost the signal-to-noise ratio of a  $\Delta\Sigma$  modulator. The noise transfer function can be written as:

$$NTF(Z) = A \frac{\prod_{i}(Z - a_i)}{\prod_{i}(Z - b_i)}$$

(2.24)

where A is the coefficient,  $a_i$  and  $b_j$  are the NTF zeros and poles. A higher out-of-band quantization noise gain can be achieved by moving the poles toward the Z = -1 point in a Z-plane (i.e., the  $\frac{\omega_s}{2}$  point in the frequency domain). This means the poles are away from the Z = 1 point (i.e., the DC point in the frequency domain) and the baseband quantization noise can be suppressed.

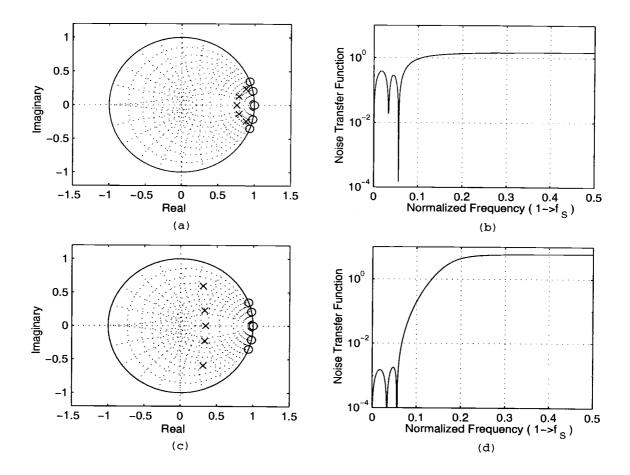

Figure 2.14 shows two fifth-order noise transfer functions with  $||H||_{\infty}$  of 1.5 and 6, respectively. For the noise transfer function with a low  $||H||_{\infty}$ , the poles are close to the Z=1 point and the baseband noise shaping is below 0.3891. If  $||H||_{\infty}$  is increased to 6, the NTF poles are far away from the Z=1 point, which results in aggressive noise shaping. The maximum out-of-band quantization noise gain is 6 and the baseband magnitude is below 0.0033. Thus by increasing  $||H||_{\infty}$  from 1.5 to 6, the baseband noise can be reduced by about two orders of magnitude. This implies that  $||H||_{\infty}$  is a very important parameter for  $\Delta\Sigma$  modulators with multi-bit quantizers.

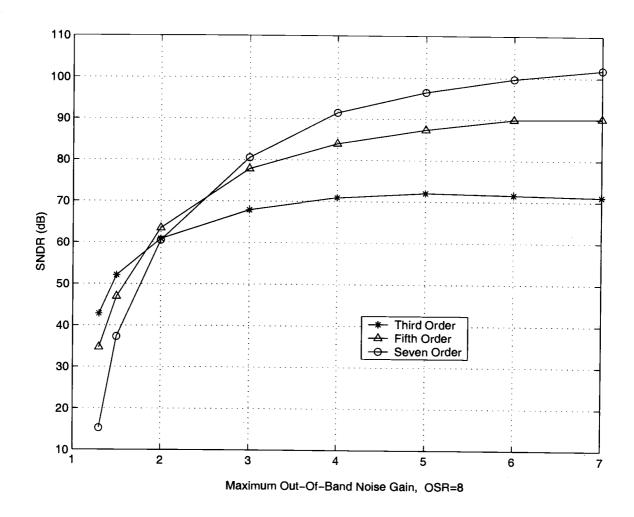

Figure 2.15 shows the signal-to-noise plus distortion ratios (SNDR) of third-, fifth-order  $\Delta\Sigma$  modulators with 4-bit quantizers and 8X oversampling ratios as a function of  $\|H\|_{\infty}$ . The Matlab delta-sigma toolbox is used to generate each of these and the NTF poles and zeros are optimally placed in each case [15]. The fifth-order  $\Delta\Sigma$  modulator can only achieve about 48 dB SNDR with  $\|H\|_{\infty} = 1.5$ . However, when  $\|H\|_{\infty} = 6$ , 90 dB SNDR is achieved. By increasing  $\|H\|_{\infty}$  from 1.5 to 6, the resolution of the fifth-order  $\Delta\Sigma$  modulator increases by 6 to 7 bits. Recall that the

FIGURE 2.14. Comparison of two fifth-order noise transfer functions: (a) pole-zero plot of the noise transfer function with  $||H||_{\infty}=1.5$ , and (b) the corresponding noise transfer function of (a). (c) Pole-zero plot of the noise transfer function with  $||H||_{\infty}=6$ , and (d) the corresponding noise transfer function of (c).

resolution of an n-th order  $\Delta\Sigma$  modulator drops about n+0.5 bit for each halving of oversampling ratio. For low oversampling  $\Delta\Sigma$  modulators, a high  $||\mathbf{H}||_{\infty}$  can greatly amend the loss of resolution due to the reduced oversampling ratios.

The Matlab  $\Delta\Sigma$  modulator toolbox uses state space matrices to represent  $\Delta\Sigma$  modulators. When the implementation of the  $\Delta\Sigma$  modulator is considered, the structure is usually different from the state space representation and the maximum

stable input is different from that obtained from the state space representation. Thus the maximum achievable SNDR is typically different from the curves shown in Fig. 2.15 (and usually less than that predicted in Fig. 2.15).

FIGURE 2.15. SNDR as a function of  $\|H\|_{\infty}$  for third, fifth, and seventh-order  $\Delta\Sigma$  modulators with a 4-bit quantizer and 8X OSR.

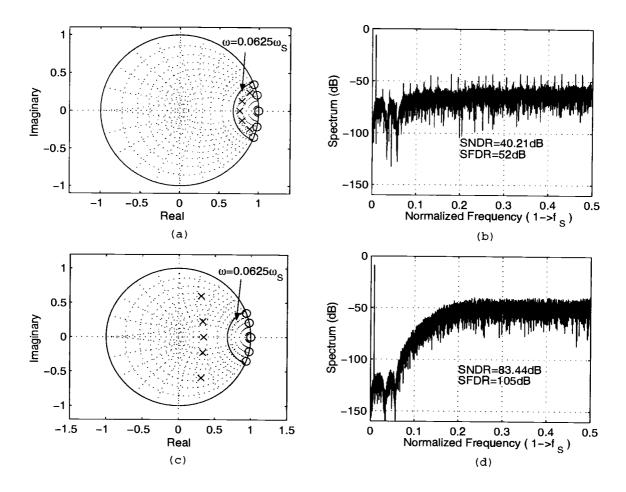

Another  $\|H\|_{\infty}$  related phenomenon has also been observed when the two  $\Delta\Sigma$  modulators with 8X oversampling are examined. Figure 2.16(a) is the NTF pole-zero plot of a fifth-order  $\Delta\Sigma$  modulator with a 4-bit quantizer and  $\|H\|_{\infty}=1.5$ .

Fig. 2.16(b) is the simulated output spectrum. Apart from poor noise shaping, large tones inside the baseband are also observed. The SNDR is only 40.21 dB and SFDR is only 52 dB, because the linearity is corrupted by the in-band tones. If  $||H||_{\infty}$  is increased to 6 as is shown in Fig. 2.16(c), the SNDR can be increased to 83.44 dB and the baseband is tone free. This results in a SFDR of 105 dB (Fig. 2.16(d)). The solid curves in Fig. 2.16(a) and Fig. 2.16(c) denote the baseband bandwidth  $(\omega = 0.0625\omega_s)$  for 8X oversampling).

For the simulations shown in Fig. 2.16, idealities are included in the  $\Delta\Sigma$  modulator such as no mismatch, noise, opamp finite DC gain or other non-ideal effects. Since the  $\Delta\Sigma$  modulator is fifth-order, the correlation between the input signal and the quantization noise is also very weak. Thus, we would expect the baseband tones in the high-order modulator to be minimal. However, simulations show that there are large tones when  $\|H\|_{\infty}$  is reduced to a small value. To explain this phenomenon, the Z-plane of Fig. 2.17 is considered more carefully. The natural frequency,  $\omega$ , varies from 0 to  $\pi$  (i.e., from DC to  $\frac{\omega_s}{2}$ ) and it is represented by the radial dotted lines in Fig. 2.17. The damping factor,  $\zeta$ , varies from 0 to 1 and it is constant along circles inside the unit circle. If a complex conjugate pole pair is located at  $(\omega, \zeta)$  in the Z-plane, the corresponding impulse response is:

$$h(n) = \zeta^n cos(\frac{2\pi\omega n}{\omega_s}), \ n = 0, 1, 2, 3...$$

(2.25)

where  $\omega_s$  is the sampling frequency. The impulse response is a damped oscillation with a frequency,  $\omega$ , and a damping rate of  $\zeta^n$ . For two poles located at  $\omega = 0.2\omega_s$  and  $\zeta = 0.9$  in the Z-plane (as shown in Fig. 2.17), the corresponding frequency domain responses are shown in Fig. 2.18. Note that the signal peaks at  $f \approx 0.2f_s$ . For  $\Delta\Sigma$  modulators with low  $\|H\|_{\infty}$ , the NTF poles are close to DC. If

FIGURE 2.16. (a) The pole-zero plot of a fifth-order 4-bit  $\Delta\Sigma$  modulator with  $\|H\|_{\infty}=1.5$  and 8X OSR, and (b) simulated spectrum of the modulator shown in (a). (c) The pole-zero plot of a fifth-order 4-bit  $\Delta\Sigma$  modulator with  $\|H\|_{\infty}=6$  and 8X OSR, and (d) simulated spectrum of the modulator shown in (c).

the  $\Delta\Sigma$  modulator also has a low oversampling ratio, the frequency domain peaking can be within the baseband frequency and this will generate tones in the output within the baseband bandwidth.

FIGURE 2.17. Constant natural frequency  $\omega$  contours and constant damping rate  $\zeta$  contours in a Z-plane, two poles are shown at  $\omega = 0.2\pi$  and  $\zeta = \pm 0.9$ .

This is a simple explanation for a two-pole system. For a high-order  $\Delta\Sigma$  modulator, this explanation is also valid. Figure 2.14 shows the pole-zero plots and noise transfer functions of a fifth-order  $\Delta\Sigma$  modulator with  $||\mathbf{H}||_{\infty} = 1.5$  and  $||\mathbf{H}||_{\infty} = 6$ , respectively. If a random input signal x passes through a linear time invariant system H(f), the output signal y is also a random signal. The power spectral density of y is:

FIGURE 2.18. The frequency response of a two pole system, two poles are at  $\omega \approx 0.2\pi$  and  $\zeta = 0.9$  in the Z-plane.

$$S_Y(f) = |H(f)|^2 S_X(f)$$

(2.26)

where  $S_X(f)$  is the power spectral density of x and  $S_Y(f)$  is the power spectral density of y. If the quantization noise is a gaussian white noise source, the spectrum of the output signal resembles the two noise function curves shown in Fig. 2.14(b) and (d). The output does not have any tones in the baseband. But when  $||H||_{\infty} = 1.5$ , the output spectrum has large tones as shown in Fig. 2.16.