#### AN ABSTRACT OF THE THESIS OF

<u>Chee Lee</u> for the degree of <u>Master of Science</u> in <u>Electrical and Computer Engineering</u> presented on <u>May 30, 2003.</u>

Title: A Resource Constrained Scheduling Scheme that Considers Resources

Operating at Multiple Voltages and Register Assignment

Abstract approved:

# Redacted for Privacy

Wen-Tsong Shiue

Power and timing requirements are becoming more and more stringent as applications move from less mobile devices to more mobile ones. As such, it is important to optimize these applications as much as possible in order to provide the best solution that is low power and low latency. Although there are many different techniques to achieve a low power, low latency solution, this thesis focuses specifically on low power scheduling at the behavioral level where resourceconstrained scheduling is the technique of choice since it directly considers the resource limitations of mobile devices. Conventional resource-constrained scheduling schemes are concerned with minimizing the latency or improving the speed of an algorithm—represented by a data flow graph (DFG)—given a limitation on resources. However, these conventional resource-constrained scheduling schemes are no longer applicable since power has grown to be a major issue, especially in mobile devices. Hence, the conventional resource-constrained scheduling schemes gave way to current resource-constrained scheduling schemes that utilize multiple voltages, which work to find a balance between speed and

power. These current multiple voltage schemes use various techniques to balance and meet the speed and power requirements. But while they do a good job of meeting these requirements, they fail to address a new issue that is beginning to surface—the number of memory registers needed. Therefore, to address this new arising issue, this paper presents a novel resource-constrained scheduling scheme that balances the speed, power, and register requirements. This algorithm is compared to both a conventional resource-constrained scheduling scheme and a current resource-constrained scheduling scheme with multiple voltages to show that it performs better in finding a scheduling solution. Benchmark results show that, on average, our algorithm has a better power savings while keeping the maximum number of registers needed and the latency low compared to conventional resource-constrained scheduling schemes utilizing just multiple voltages.

© Copyright by Chee Lee May 30, 2003 All Rights Reserved

# A Resource-Constrained Scheduling Scheme that Considers Resources Operating at Multiple Voltages and Register Assignment

by Chee Lee

A THESIS

submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Master of Science

Presented May 30, 2003 Commencement June 2004

| APPROPRED APPROPRIES A |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Major Professor, representing Electrical and Computer Engineering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Redacted for Privacy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Director of the School of Electrical Engineering and Computer Science                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Redacted for Privacy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Dean of the Graduate School                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| I understand that my thesis will become part of the permanent collection of Oregon                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| State University libraries. My signature below authorizes release of my thesis to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| any reader upon request.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Redacted for Privacy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Chee Lee, Author                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

#### ACKNOWLEDGEMENTS

I would like to take this time to express my gratitude to my major advisor, Professor Wen-Tsong Shiue, for his role in my M.S. program. I have learned a lot from working with him. I would also like to thank the members of my committee, Professors Alexandre Tenca, Alexandre F.T. Yokochi, and Cetin Kaya Koc for taking the time to review my research.

Next, I am also grateful to all my peers who have helped me stay focused on my research. I am especially grateful to Weetit Wanalertlak for helping with the technical questions I had as well as helping with my teaching assistant duties when I was overloaded with deadlines.

I would also like to thank my very good friend Ange Ly for all he has done for me this year. I have learned many important lessons and have grown significantly as a person thanks to him. Not to mention, I am also a lot healthier since we have started playing soccer together. I am glad he is staying in Oregon for a few more years.

Thanks also go to my extend family—aunts, uncles, cousins, etc.—who have welcomed me with open arms when I needed to escape from the stress of my academic life. During my stress filled times, I could always count on them for a temporary escape while I relaxed and recharged. They allowed me to refocus and efficiently deal with my stressful situations.

And last, but not least, I am sincerely thankful for my parents, Giachue Lee and Mai Yang Lee, and my brother, Jai Lee, for all their support, encouragement, and patience. Without them, I could not have accomplished all that I have. They stood with me no matter what the situation was and have sacrificed a lot for me. For all that they have done, I am eternally grateful.

### TABLE OF CONTENTS

|    |        |                                                        | <u>Page</u> |

|----|--------|--------------------------------------------------------|-------------|

| 1. | Intro  | duction                                                | 1           |

| 2  | Prelin | minaries                                               | 4           |

|    | 2.1    | Resource-Constrained Scheduling Definitions            | 4           |

|    | 2.2    | Delay and Power Models                                 | 5           |

|    | 2.3    | Simulation Environment                                 | 18          |

| 3. | Relat  | ed Work                                                | 20          |

|    | 3.1    | Conventional Resource-Constrained Scheduling           | 20          |

|    | 3.2    | Resource-Constrained Scheduling with Multiple Voltages | 23          |

| 4. | Regis  | ster Significance                                      | 29          |

| 5. |        | urce-Constrained Scheduling with ster Assignment       | 31          |

|    | 5.1    | Our Scheduling Scheme and Example                      | 31          |

|    | 5.2    | C++ Implementation                                     | 37          |

| 6. | Bencl  | hmarks                                                 | 40          |

|    | 6.1    | Simple Example                                         | 40          |

|    | 6.2    | Lattice Filter                                         | 45          |

|    | 6.3    | Elliptic Wave Filter                                   | 49          |

|    | 6.4    | Fast Fourier Transform (FFT)                           | 51          |

|    | 6.5    | Discrete Cosine Transform (DCT)                        | 54          |

# TABLE OF CONTENTS (Continued)

|       |            |                                    | <u>Page</u> |

|-------|------------|------------------------------------|-------------|

|       | 6.6 Optin  | nal Scheduling Scheme              | 58          |

| 7.    | Conclusion |                                    | 61          |

| Bibli | ography    |                                    | 63          |

| Appe  | endices    |                                    | 65          |

|       |            | My PublicationsBiographical Sketch | 66<br>67    |

### LIST OF FIGURES

| Figure | <u>2</u>                                                         | Page |

|--------|------------------------------------------------------------------|------|

| 1.     | 1-bit Full Adder                                                 | 6    |

| 2.     | 32-bit Carry-Ripple Adder Schematic                              | 7    |

| 3.     | 32-bit Carry-Ripple Multiplier Schematic                         | 7    |

| 4.     | 32-bit Register Schematic                                        | 8    |

| 5.     | Power Meter Circuit for Simulation of Dynamic Power Dissipation  | 9    |

| 6.     | Delay Measurements for the 32-bit Carry-Ripple Adder             | 10   |

| 7.     | Power Measurements for the 32-bit Carry-Ripple Adder             | 11   |

| 8.     | Functional Unit Latency Comparisons                              | 13   |

| 9.     | 32-bit Adder Delay vs. Power for AMI 0.5 um                      | 14   |

| 10.    | 32-bit Adder Delay for AMI 1.2 um, AMI 0.5 um, and TSMC 0.35 um. | 15   |

| 11.    | 32-bit Adder Power for AMI 1.2 um, AMI 0.5 um, and TSMC 0.35 um  | 16   |

| 12.    | Conventional Resource-Constrained Scheduling Example             | 22   |

| 13.    | Resource-Constrained Scheduling with Multiple Voltages Example   | 26   |

| 14.    | Multiple Voltages Level Shifter Overhead                         | 27   |

| 15.    | Register Contributions to Power and Delay                        | 30   |

| 16.    | Register Savings from a CFG                                      | 32   |

# LIST OF FIGURES (Continued)

| Figure |                                                                  | <u>Page</u> |

|--------|------------------------------------------------------------------|-------------|

| 17.    | Resource-Constrained Scheduling with Register Assignment Example | 35          |

| 18.    | C++ Program Flow                                                 | 38          |

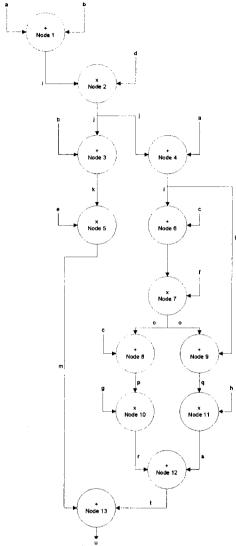

| 19.    | 2 <sup>nd</sup> Order Lattice Filter DFG                         | 46          |

| 20.    | 5 <sup>th</sup> Order Elliptic Wave Filter DFG                   | 49          |

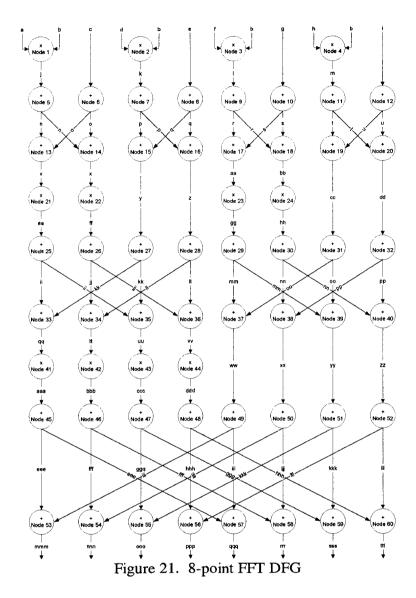

| 21.    | 8-point FFT DFG                                                  | 52          |

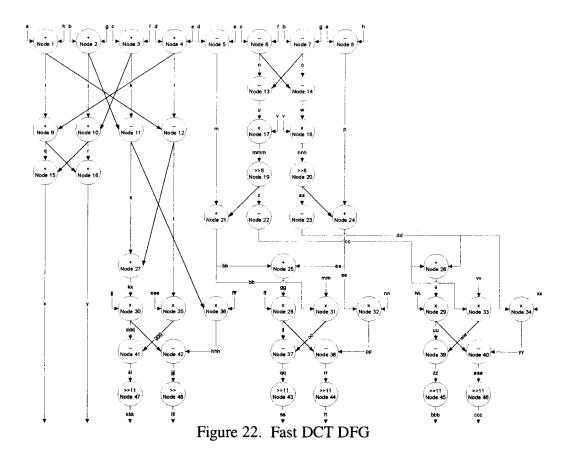

| 22.    | Fast DCT DFG                                                     | 55          |

## LIST OF TABLES

| <u>Table</u> |                                                                                                                 | Page     |

|--------------|-----------------------------------------------------------------------------------------------------------------|----------|

| 1.           | National Technology Roadmap of Semiconductor                                                                    | 9        |

| 2.           | Delay and Power Characteristics for a 32-bit Carry-Ripple Adder                                                 | 11       |

| 3.           | Delay and Power Characteristics for a 32-bit Carry-Ripple Multiplier                                            | 12       |

| 4.           | Delay and Power Characteristics for a 32-bit Register                                                           | 12       |

| 5.<br>6.     | Power (uW) Characteristics for 32-bit Level Shifters                                                            | 18<br>41 |

| 7.           | Simple Example Results for Resource-Constrained Scheduling with Multiple Voltages                               | 42       |

| 8.           | Simple Example Results for Resource-Constrained Scheduling with Multiple Voltages and Register Assignment       | 43       |

| 9.           | Lattice Filter Results for Resource-Constrained Scheduling with Multiple Voltages                               | 47       |

| 10.          | Lattice Filter Results for Resource-Constrained Scheduling with Multiple Voltages and Register Assignment       | 47       |

| 11.          | Elliptic Wave Filter Results for Resource-Constrained Scheduling with Multiple Voltages                         | 50       |

| 12.          | Elliptic Wave Filter Results for Resource-Constrained Scheduling with Multiple Voltages and Register Assignment | 50       |

| 13.          | FFT Results for Resource-Constrained Scheduling with Multiple Voltages                                          | 53       |

| 14.          | FFT Results for Resource-Constrained Scheduling with Multiple Voltages and Register Assignment                  | 53       |

# LIST OF TABLES (Continued)

| <u>Table</u> |                                                                                                       | Page |

|--------------|-------------------------------------------------------------------------------------------------------|------|

| 15.          | Fast DCT Results for Resource-Constrained Scheduling with Multiple Voltages                           | 56   |

| 16.          | Fast DCT Results for Resource-Constrained Scheduling with Multiple Voltages and Register Assignment   | 57   |

| 17.          | Average Performance of Resource-Constrained Scheduling with Multiple Voltages                         | 58   |

| 18.          | Average Performance of Resource-Constrained Scheduling with Multiple Voltages and Register Assignment | 59   |

# A Resource-Constrained Scheduling Scheme that Considers Resources Operating at Multiple Voltages and Register Assignment

#### 1. Introduction

The mobile devices market is expected to grow at approximately 20% each year for the next few years with sales exceeding 60 million units in 2008 [1]. As the market grows, more and more consumers are expected to use small, mobile devices such as PDAs and cell phones to perform multimedia tasks like browsing the Internet, taking and sharing pictures, and watching movies. However, the extent of which these tasks can be performed is extremely limited due to strict timing, area, and power requirements. Unlike larger devices such as desktop computer systems, mobile devices cannot support the requirements of complex applications. They are designed to be low power and have limited resources. Therefore, complex applications need to be optimized before they can be effectively used on mobile systems.

In particular, these complex applications need to be able to use less power while still maintaining an acceptable performance. Low power usage is desirable for the following reasons: 1) to increase battery lifetime; 2) to increase system reliability; and 3) to reduce packaging and cooling costs [2,3]. The battery lifetime is determined by the current consumption. If the power consumption is high, then the current consumption is also high, which may reduce the battery lifetime. High power consumption also translates to higher operating temperatures, which may lead to system/circuit failures. Also, with higher temperatures, cooling costs

increase, as more resources are needed to cool the system/circuit. This also leads to larger packaging and a larger overall size. In mobile devices, it is important to have long battery lifetimes, good reliability, and a small size. Hence, it is important to keep the power consumption low.

Power reduction can be achieved at many different levels, such as architecture, algorithm, behavioral, and transistor levels [4]. This thesis focuses on low power scheduling at the algorithm level. Although there are many different low power scheduling schemes, this thesis discusses a practical resource-constrained scheduling since it directly considers resource limitations making it more suitable to mobile devices.

This thesis presents a novel resource-constrained scheduling scheme utilizing multiple voltages and register assignment that performs better than current resource-constrained scheduling schemes for multi-dimensional signal processing. Unlike conventional resource-constrained scheduling schemes, which focus primarily on reducing latency, and current resource-constrained scheduling schemes with multiple voltages, which focus primarily on reducing power usage, our resource-constrained scheduling scheme works to find a balance between the latency and power usage by considering the register usage as well as multiple supply voltages. Latency is kept low by reducing the emphasis on using resources that operate at multiple voltages. These resources are still used, but they are used sparingly. Power usage is kept low by considering the data dependence and the

maximum number of registers needed. By exploiting data dependencies, the maximum number of registers needed can be reduced, which, in turn, helps to reduce the overall power usage. By balancing the latency and power, our resource-constrained scheduling scheme ends up performing, on average, better than either the conventional resource-constrained scheduling or current resource-constrained scheduling schemes utilizing just multiple voltages.

The rest of the thesis is organized as follows. The following section defines terms, equations, and constants used in our resource-constrained scheduling scheme as well as in the conventional resource-constrained scheduling and current resource-constrained scheduling with multiple voltages schemes. Section 3 discusses the background and related work in resource-constrained scheduling. Section 4 illustrates the significance or role that registers have in achieving low power. Section 5 discusses our resource constrained scheduling scheme. Section 6 presents the benchmark results. And section 7 concludes the thesis.

#### 2. Preliminaries

This section defines terms, equations, etc. that are used in the typical resource-constrained scheduling scheme, our resource-constrained scheduling scheme, and our simulations.

#### 2.1 Resource-Constrained Scheduling Definitions

The input to a resource-constrained scheduling scheme is a data flow graph (DFG) and a resource constraint. A resource constraint is a restriction or a limit imposed on the number of each type of resource such as an adder, multiplier, or shifter. A DFG is a directed acyclic graph whose nodes represent operations and edges represent dependencies between the operations. Each node also has information linked to it in order to help determine its priority.

The mobility of a node is defined as the difference between its as-late-aspossible (ALAP) schedule time and its as-soon-as-possible (ASAP) schedule time.

Mobility determines which nodes are given priority when assigning to a certain

resource. Nodes with high mobility are given priority when assigning to lowvoltage resources. Nodes with low mobility are given priority when assigning to

high-voltage resources. It is not used in the conventional resource-constrained

scheduling scheme and applies primarily to resource-constrained scheduling with

resources operating at multiple voltages.

The depth of a node is defined as the length of the path from the node to the sink in the DFG. Depth is directly linked to latency. In order to reduce the number of control cycles, nodes with higher depth are scheduled first. The conventional resource-constrained scheduling scheme as well as the scheme with multiple voltages makes use of the depth.

Resource-constrained scheduling schemes are primarily list-based. Therefore, there is a ready set associated with every control cycle. The ready set is defined as the set of nodes that could all be assigned at that particular control cycle if there were no resource constraints.

In addition to the items mentioned above, our resource-constrained scheduling scheme also takes a conflict flow graph (CFG) as an input. A CFG is similar to a DFG except that the edges represent conflicts between nodes. The CFG helps our algorithm address register concerns.

# 2.2 Delay and Power Models

The delay and power of the different functional units (adders, multipliers, and registers) operating at various voltages have been obtained from simulations using Mentor Graphic's *Design Architect* and *Accusim* in a Sun/Solaris unix environment. *Design Architect* is a schematic tool that allows the user to create circuits by placing components (resistors, capacitors, transistors, etc.) and wiring

them together. Accusim is a circuit simulation tool similar to spice except that it operates through a graphical user interface (GUI).

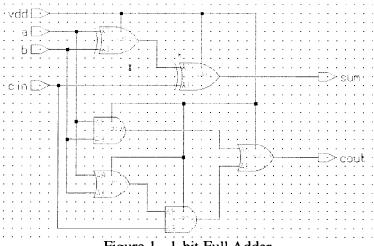

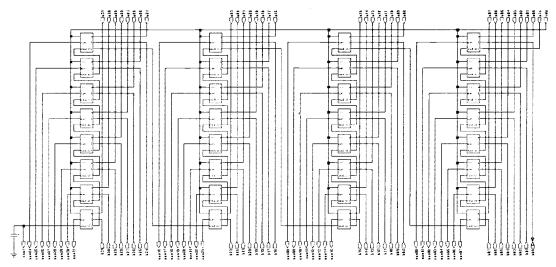

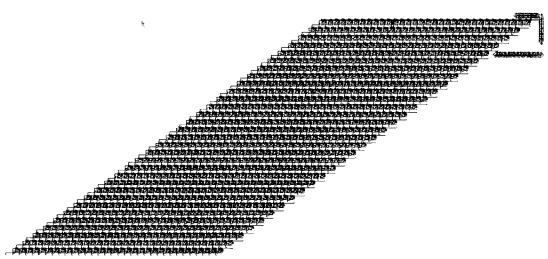

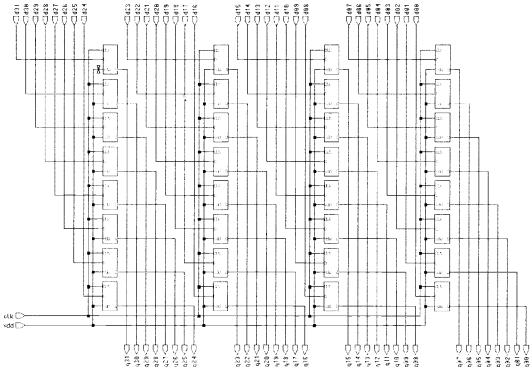

We constructed and simulated a 32-bit carry-ripple adder, a 32-bit carryripple multiplier, and a 32-bit register for three technologies (AMI 1.2, AMI 0.5, and TSMC 0.35) operating at 5V, 3.3V, 2.4V, 2.2V, 1.8V, 1.5V, 1.2V, and 1.0V. Figure 1 illustrates the typical 1-bit full adder that is used to construct our 32-bit carry-ripple adder in Figure 2 and our 32-bit carry-ripple multiplier in Figure 3. Figure 4 illustrates our 32-bit register.

Figure 1. 1-bit Full Adder

Figure 2. 32-bit Carry-Ripple Adder Schematic

Figure 3. 32-bit Carry-Ripple Multiplier Schematic

Figure 4. 32-bit Register Schematic

There are different adder and multiplier architectures. However, we chose the ones we did for simplicity and as a starting point. As our library grows, we will include different adder and multiplier architectures as well as other functional units. Only three technologies were used since we were only able to gain access to these technologies. Simulations were done at the specified voltages in order to address the national technology roadmap of semiconductor summarized in Table 1 from [5].

| Table 1. National | Technology | Roadman of | Semiconductor |

|-------------------|------------|------------|---------------|

|-------------------|------------|------------|---------------|

| Year    | 1997 | 1999 | 2001 | 2003 | 2006 | 2009 | 2012 |

|---------|------|------|------|------|------|------|------|

| L (nm)  | 250  | 180  | 150  | 130  | 100  | 70   | 50   |

| Vdd (V) | 2.2  | 1.8  | 1.5  | 1.2  | 1    | 0.8  | 0.6  |

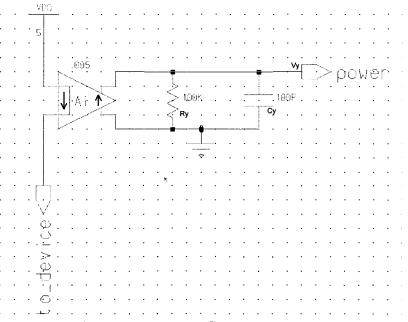

The delay is a measure of the time it takes for the output to see a change in the input. It is calculated based on the following equation from [6]:  $(T_{PLH} + T_{PHL}) / 2$ .  $T_{PLH}$  and  $T_{PHL}$  correspond to a low to high transition at the input and a high to low transition at the input, respectively. The power is determined using a power meter circuit similar to the one in [7] (see Figure 5).

Figure 5. Power Meter Circuit for Simulation of Dynamic Power Dissipation

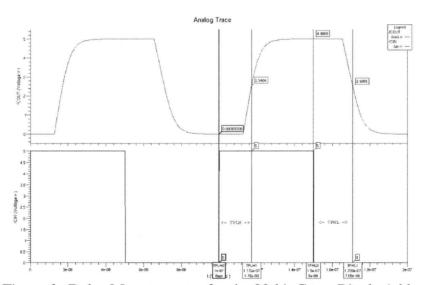

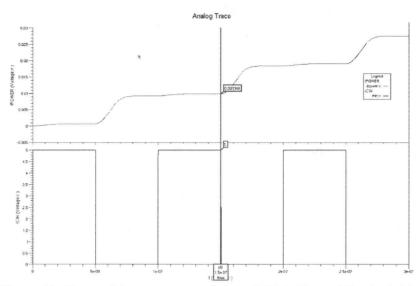

The meter measures the current drawn by the device and amplifies that current by a value  $\beta = V_{DD} * C_y / T$ , where  $V_{DD}$  is the supply voltage,  $C_y$  is a capacitance, and T is the period of the input signal. This current runs through  $R_y$  (a resistor) and  $C_y$  (a capacitor) and allows us to determine the power by taking measurements at  $V_y$ . Figure 6 and Figure 7 show the measurements used to determine the delay and power for the 32-bit carry-ripple adder operating at 5V.

Figure 6. Delay Measurements for the 32-bit Carry-Ripple Adder

Figure 7. Power Measurements for the 32-bit Carry-Ripple Adder

Measurements for the 32-bit carry-ripple multiplier and 32-bit register are done exactly as with the 32-bit carry-ripple adder. Tables 2, 3, and 4 show the delay and power characteristics for the adder, multiplier, and register for each of the three different technologies and the different operating voltages.

Table 2. Delay and Power Characteristics for a 32-bit Carry-Ripple Adder

| adder32      | <b>AMI 1.2 um</b> |            | AMI 0.5 um |            | TSMC 0.35 um |            |

|--------------|-------------------|------------|------------|------------|--------------|------------|

| Voltages (V) | Delay (ns)        | Power (uW) | Delay (ns) | Power (uW) | Delay (ns)   | Power (uW) |

| 5            | 35.09             | 10,692.00  | 19.03      | 9,946.00   | 13.51        | 9,335.60   |

| 3.3          | 51.73             | 4,457.55   | 31.16      | 4,246.00   | 16.50        | 3,984.48   |

| 2.4          | 78.45             | 2,272.50   | 38.38      | 2,213.40   | 21.49        | 2,068.21   |

| 2.2          | 90.31             | 1,878.33   | 43.94      | 1,846.70   | 23.66        | 1,835.20   |

| 1.8          | 132.75            | 1,151.84   | 64.67      | 1,081.86   | 31.20        | 986.25     |

| 1.5          | 210.60            | 439.92     | 104.82     | 419.17     | 43.71        | 402.57     |

| 1.2          | 494.98            | 137.91     | 263.88     | 129.28     | 78.81        | 121.41     |

| 1            | 1,983.55          | 17.49      | 1,117.20   | 16.37      | 170.64       | 15.54      |

Table 3. Delay and Power Characteristics for a 32-bit Carry-Ripple Multiplier

| mult32       | AMI 1.2 um |            | AMI 0.5 um |            | TSMC 0.35 um |            |

|--------------|------------|------------|------------|------------|--------------|------------|

| Voltages (V) | Delay (ns) | Power (uW) | Delay (ns) | Power (uW) | Delay (ns)   | Power (uW) |

| 5            | 101.46     | 32,562.00  | 52.57      | 30,290.00  | 33.22        | 28,431.00  |

| 3.3          | 149.56     | 13,575.27  | 86.10      | 12,930.96  | 40.57        | 12,134.50  |

| 2.4          | 226.81     | 6,920.78   | 106.04     | 6,740.79   | 52.85        | 6,298.60   |

| 2.2          | 261.09     | 5,720.37   | 121.42     | 5,624.02   | 58.19        | 5,588.98   |

| 1.8          | 383.80     | 3,507.87   | 178.70     | 3,294.73   | 76.72        | 3,003.56   |

| 1.5          | 608.88     | 1,339.75   | 289.65     | 1,276.56   | 107.47       | 1,226.01   |

| 1.2          | 1,431.06   | 419.99     | 729.18     | 393.72     | 193.79       | 369.75     |

| 1            | 5,734.75   | 53.28      | 3,087.15   | 49.86      | 419.59       | 47.32      |

Table 4. Delay and Power Characteristics for a 32-bit Register

| reg32        | AMI 1.2 um |            | AMI 0.5 um |            | <b>TSMC 0.35 um</b> |            |

|--------------|------------|------------|------------|------------|---------------------|------------|

| Voltages (V) | Delay (ns) | Power (uW) | Delay (ns) | Power (uW) | Delay (ns)          | Power (uW) |

| 5            | 7.12       | 8,559.50   | 5.20       | 8,473.50   | 3.67                | 8,390.60   |

| 3.3          | 10.49      | 3,741.63   | 7.21       | 3,618.20   | 4.50                | 3,558.90   |

| 2.4          | 15.95      | 2,045.27   | 10.38      | 1,909.70   | 5.63                | 1,897.33   |

| 2.2          | 18.44      | 887.88     | 11.85      | 794.04     | 6.44                | 778.81     |

| 1.8          | 27.01      | 662.23     | 16.86      | 545.39     | 8.12                | 526.89     |

| 1.5          | 42.80      | 389.39     | 27.20      | 368.18     | 11.27               | 358.80     |

| 1.2          | 102.85     | 78.09      | 66.71      | 75.53      | 20.01               | 73.19      |

| 1            | 428.55     | 14.61      | 80.05      | 12.76      | 43.95               | 11.41      |

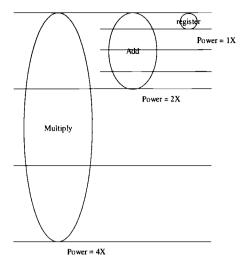

Notice that, in general, the 32-bit register is approximately four times faster than the 32-bit adder and that the 32-bit adder is approximately three times faster than the 32-bit multiplier (see Figure 8).

Figure 8. Functional Unit Latency Comparisons

This is an important factor in determining the latency of a DFG. A DFG with many multiply nodes will usually have a longer latency compared to a DFG with fewer multiply nodes. However, since a multiplier is approximately three times slower than an adder, we can complete three add operations during one multiplier operation, which will also impact the latency. As for the power, the register consumes the least, followed by the adder, and then the multiplier (see Figure 8). Thus, a DFG with many multiply nodes will also usually consume more power than a DFG with fewer multiply nodes. Two other relationships to note are: 1) as the voltage decreases, the delay increases but the power decreases; 2) as the technology becomes smaller, both the power and delay decrease. These relationships can be seen in more detail in Figure 9, 10, and 11.

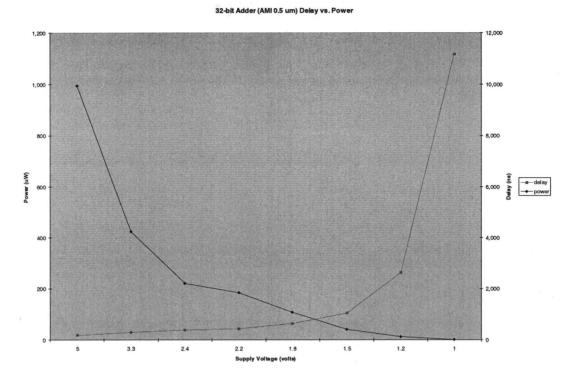

Figure 9. 32-bit Adder Delay vs. Power for AMI 0.5 um.

At higher voltages, the power usage is high while the delay is low. Therefore, if delay is the primary concern, then a higher voltage should be used. However, if power is the primary concern, then a lower voltage should be used. A complete balance can also be obtained. From Figure 9, if we choose the voltage where the power and delay lines cross, then we will have the best possible balance between the power usage and delay.

#### 32-bit Adder Delay

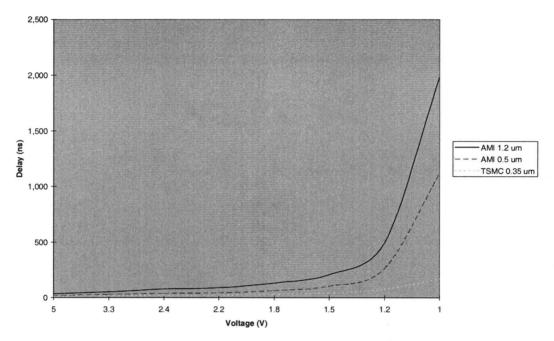

Figure 10. 32-bit Adder Delay for AMI 1.2 um, AMI 0.5 um, and TSMC 0.35 um.

The technology also plays an important role in the delay. AMI 1.2 um has the highest delay followed by AMI 0.5 um and then TSMC 0.35 um. However, it is not always necessary to choose the smallest technology. From Figure 10, all three technologies perform almost identically at the higher voltages. Therefore, if a high voltage is being used, then it may be more beneficial to use a bigger technology, which will cost less, over a smaller technology, which will cost more. However, if a low voltage is being used, then the technology is very important. At lower voltages, TSMC 0.35 um has the lowest delay followed by AMI 0.5 um and then AMI 1.2 um. Hence, if low delay and high voltage were the requirements,

then AMI 1.2 um would meet those requirements best considering performance and cost. However, if low delay and low voltage were the requirements, then TSMC 0.35 um would meet those requirements best considering performance and cost. AMI 0.5 um would give the middle of the line solution.

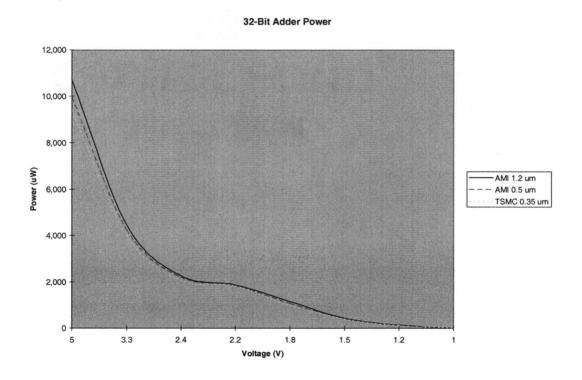

Figure 11. 32-bit Adder Power for AMI 1.2 um, AMI 0.5 um, and TSMC 0.35 um.

Like with delay, the technology also plays an important role in the power usage. AMI 1.2 um has the highest power usage followed by AMI 0.5 um and then TSMC 0.35 um. However, it is not always necessary to choose the smallest technology. From Figure 11, all three technologies perform almost identically at

the lower voltages. Therefore, if a low voltage is being used, then it may be more beneficial to use a bigger technology, which will cost less, over a smaller technology, which will cost more. However, if a high voltage is being used, then the technology is very important. At higher voltages, TSMC 0.35 um has the lowest power usage followed by AMI 0.5 um and then AMI 1.2 um. Hence, if low power and high voltage were the requirements, then TSMC 0.35 um would meet those requirements best considering the performance and cost. However, if low power and low voltage were the requirements, then AMI 1.2 um would meet those requirements best considering the performance and cost. AMI 0.5 um would give the middle of the line solution.

Overall, our library provides information for designers so that they may make a more informed choice about which technology to use. Then within each technology, we provide information that allows the designer to decide on which voltage. All this information allows the designer to make the best choice to meet their latency and power requirements.

The power characteristics for level shifters, which are needed to transfer data between resources operating at different voltages is derived from [8]. Table 5 summarizes the power characteristics. Delay characteristics are ignored because they are significantly smaller than the other functional unit delays.

| Table 5. | Power ( | (uW | ) Characteristics: | for | 32-bit I | evel Shifter | 'S |

|----------|---------|-----|--------------------|-----|----------|--------------|----|

|          |         |     |                    |     |          |              |    |

| Vx to Vy | 1.8 | 2.2 | 3.3 | 5   |

|----------|-----|-----|-----|-----|

| 1.8      | 0   | 96  | 146 | 220 |

| 2.2      | 70  | 0   | 160 | 320 |

| 3.3      | 124 | 90  | 0   | 356 |

| 5        | 184 | 220 | 260 | 0   |

Although only the 32-bit adder was analyzed in detail in Figure 9, 10, and 11, the 32-bit multiplier and 32-bit register have the same relationships. The actual numbers for delay and power are different. However, the general trend and the relationships are similar to the 32-bit adder.

#### 2.3 Simulation Environment

All our resource-constrained scheduling simulations are run on a Pentium 4, 1.7 GHz laptop with 512 MB of RAM running Microsoft Windows XP. Each of the resource-constrained scheduling schemes discussed in this thesis have been coded in Microsoft Visual C++ 6.0. All inputs are entered in a table or list format similar to the one shown in Figure 12b in section 3.1. For our resource-constrained scheduling simulations, we chose the delay and power characteristics for AMI 0.5 and the operating voltages of 5V, 3.3V, 2.2V, and 1.8V. This was an arbitrary choice. We could have easily used different characteristics. Implementing the resource-constrained scheduling schemes in C++ allows us to easily change the delay and power characteristics should the need arise. Also, we have assumed that a 32-bit shifter has the same characteristics as the 32-bit adder we built. Our

benchmarks are digital signal processing (DSP) kernels. We chose these benchmarks since they would be the most likely applications run on mobile devices where resource-constrained scheduling is most valuable. DSP refers to various techniques or algorithms for improving the accuracy and reliability of digital communications and work by clarifying, or standardizing, the levels of or states of a digital signal [9].

#### 3. Related Work

Resource-constrained scheduling has been around for many years and simply refers to a scheduling scheme that tries to schedule an algorithm represented with a DFG given a limitation on the number of resources available. An operation in the DFG can only be scheduled if a resource exists and is unused, otherwise the operation must wait. Each operation may be given priority based on a number of different priority functions. The goal is to schedule the DFG, given resource constraints, such that the number of control cycles is minimum. Resource-constrained scheduling is a valuable technique for applications used on mobile devices since resource-constrained scheduling directly deals with the resource limitations of small, portable devices. Resource-constrained scheduling has the advantage of finding the best solution in terms of speed and power given the resource limitation. However, the best solution may have the disadvantage of not meeting the speed requirement (i.e. the latency is too long for practical purposes even though the power may be small and the resource requirements are met).

## 3.1 Conventional Resource-Constrained Scheduling

The conventional resource-constrained scheduling scheme, presented in [10] and [11], used a list scheduling approach that scheduled operations one control step at a time. For the current control step, a list of ready operations is constructed and then sorted according to a priority function. The operation with the highest

priority, usually the one on the longest path or with the highest depth, was scheduled first. The conventional resource-constrained scheduling scheme is as follows:

- 1) From the DFG, construct a table listing the nodes, the time they are ready, and their depth.

- 2) For each cycle:

- a. Construct the ready set (collect all the nodes that are ready to be scheduled at this cycle into one set).

- b. Prioritize the ready set according to highest depth first.

- c. While resources are available, schedule nodes from the prioritized ready set.

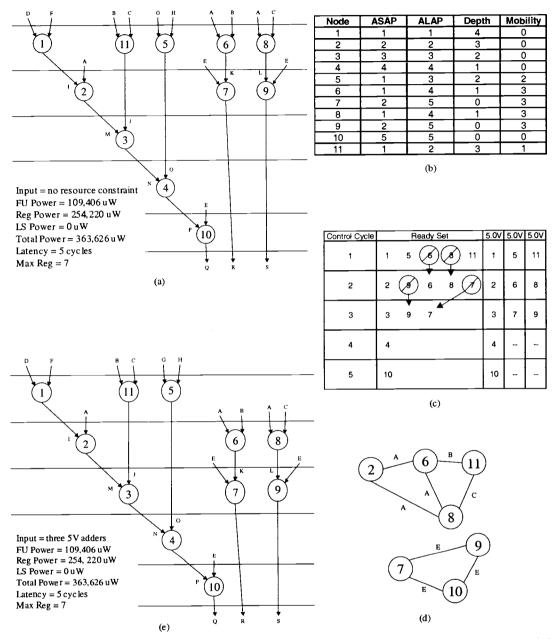

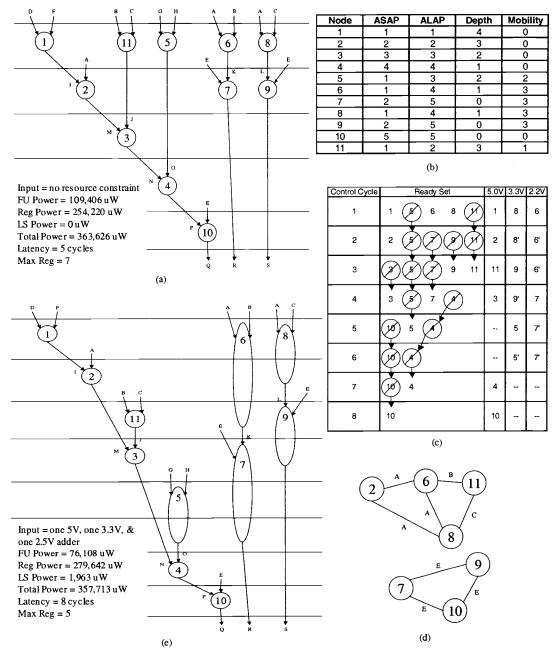

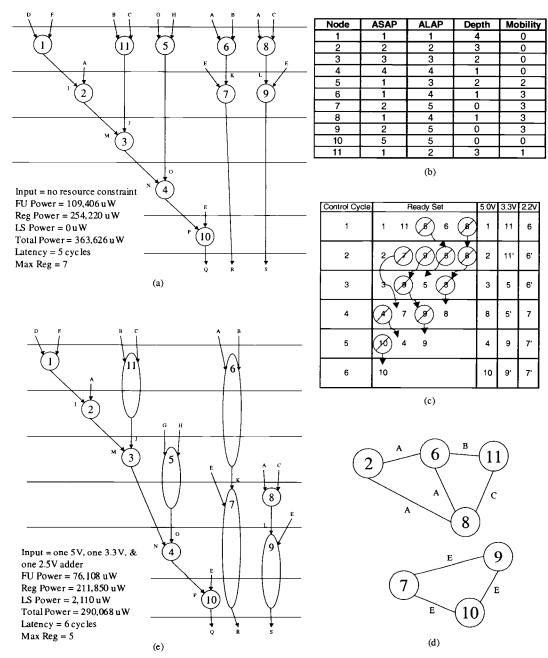

Figure 12 illustrates the conventional resource-constrained scheduling scheme for a simple example with a resource constraint of three adders all at 5V.

Figure 12. Conventional Resource-Constrained Scheduling Example. (a) Initial DFG. (b) ASAP, ALAP, depth, and mobility of each node. (c) Final Scheduling showing ready sets and scheduling at each cycle. (d) CFG. (e) Final DFG.

Figure 12 shows that the conventional resource-constrained scheduling scheme was able to maintain the lowest possible latency of five clock cycles given a

reduced number of resources to use. Instead of having five resources to use as in the no resource constraints case (see Figure 12a), there were only three resources available. Yet, the conventional scheme was able to schedule the nodes efficiently to keep the latency and power low.

Overall, the conventional resource-constrained scheduling scheme worked well in scheduling DFGs under resource limitations while keeping latency low. However, it did not address the power concerns in mobile devices very well. In Figure 12e, the total power was not reduced at all from what it was in the no resource constraint case, Figure 12a. Conventional resource-constrained scheduling schemes cannot deal with the technique of having resources operating at multiple voltages, which was developed to help with power issues. Hence, the conventional resource-constrained scheduling schemes gave way to current resource-constrained scheduling schemes that are capable of dealing with multiple voltages.

## 3.2 Resource-Constrained Scheduling with Multiple Voltages

The need for resource-constrained scheduling schemes to address resources operating at multiple voltages led to the development of current resource-constrained scheduling schemes such as those in [11], [12] and [13], which use multiple voltages (5.0V, 3.3V, and 2.2V) and consider items such as switching and level shifters to achieve a low power, low latency scheduling of a DFG. In these newer schemes, the priority function is more complex allowing the resource-

constrained scheduling scheme to address both the power and latency issues simultaneously. However, there is a trade-off to consider. A resource operating at a lower voltage uses less power but takes longer to complete its operation (the latency increases), while a resource operating at a higher voltage completes sooner (the latency decrease) but uses more power. The scheduling schemes in [11], [12], and [13] realize this relationship and do their best to balance the conflicting requirements of reducing the latency and utilizing resources operating at reduced voltages. The general resource-constrained scheduling scheme with multiple voltages is as follows:

- 1) From the DFG, determine the ASAP, ALAP, & mobility of each node.

- 2) For each cycle:

- a. For nodes in the ready set with mobility  $\geq 2$

- i. Compute priority.

- ii. Assign high priority nodes to available 2.2V resources.

- b. For nodes in the ready set with mobility >= 1

- i. Compute priority.

- ii. Assign high priority nodes to available 3.3V resources.

- c. For nodes in the ready set with mobility >= 0

- i. Compute priority.

- ii. Assign high priority nodes to available 5V resources.

- d. If resources remain, then for the nodes that have not been assigned:

- i. Compute priority.

- ii. Assign high priority nodes to available 2.2V resources, then 3.3V resources, and the 5V resources.

The priority of a node for the scheduling schemes in [11], [12], and [13] is a function of its depth, mobility, switched capacitance, and level shifter. The depth and mobility are discussed in section 2. The switched capacitance refers to the total capacitance when the inputs of a functional unit are switching. Having a smaller capacitance will result in less power usage. Therefore, nodes with lower switched capacitance are given higher priority. The level shifters also consume power. Therefore, it is beneficial to reduce the total number of up and down level shifters. This is accomplished by assigning a voltage to the child that is the same voltage that has been assigned to its parents whenever possible.

Figure 13 illustrates the resource-constrained scheduling scheme with multiple voltages for a simple example with a resource constraint of three adders—one at 5V, one at 3.3V, and one at 2.2V.

Figure 13. Resource-Constrained Scheduling with Multiple Voltages Example. (a) Initial DFG. (b) ASAP, ALAP, depth, and mobility of each node. (c) Final Scheduling showing ready sets and scheduling at each cycle. (d) CFG. (e) Final DFG.

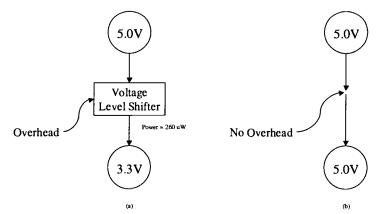

Figure 13 shows that the current resource-constrained scheduling scheme with multiple voltages was able to reduce the total power given a reduced number of resources to use. Instead of having five resources to use as in the no resource constraints case (see Figure 13a), there were only three resources available, each at a different voltage. These resources at different voltages allowed the total power to be reduced by 1.63%. The maximum number of registers needed also reduced going from seven to five. However, these power and register reductions came at the cost of latency. Instead of a latency of five like in the no resource-constraints case, the latency is now three greater at eight. This increase in latency may not be acceptable in some applications. Also, there is now an overhead associated with this solution. Voltage level shifters need to be used when using multiple voltages. In some cases, the added area and complexity that level shifters bring may out weigh the gains from using a resource-constrained scheduling scheme with multiple voltages. Figure 14 illustrates the overhead from voltage level shifters.

Figure 14. Multiple Voltages Level Shifter Overhead. (a) No Overhead. (b) Overhead

With more and more resources operating at different voltages, more and more voltage level shifters will be needed. If the area requirements are already tight, there may not be room for the level shifters. The power from the level shifters is not too much of a concern since they usually make up less than 1% of the total power.

Overall, resource-constrained scheduling schemes with multiple voltages perform well in finding an optimal solution that addresses the power issues at the slight cost of latency. Although they perform well in general, these schemes do not take into consideration a new surfacing issue—the number of registers needed. As the next section will illustrate, registers play an important role in power consumption and, thus, must be dealt with as well.

## 4. Register Significance

Memory systems are a vital part of any computer system and are needed by applications so that they can be run faster and perform better. Therefore, it is important to be aware of the contributions they make. In applications targeted for mobile devices, it is even more important due to the stricter power and timing requirements. Overall, there are many levels of memory. However, in this thesis, we focus only on registers.

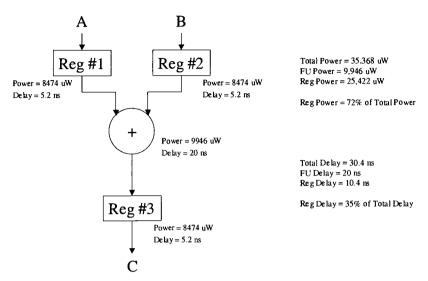

A single 32-bit register operating at 5V consumes approximately 8,474 uW of power and has a delay of 5.2 ns. So as more and more memory is needed, the power and delay will increase. Although the power and delay of a single 32-bit register is small, they make up a large part of a circuit making the number of registers an important part in reducing latency and power. Figure 15 illustrates the contribution of registers in a circuit. We consider registers operating only at a single voltage since it is not very feasible to have registers operating at multiple voltages in a single device. The level shifter overhead would be larger than the benefit obtained from operating registers at multiple voltages.

Figure 15. Register Contributions to Power and Delay

Even for a simple circuit with only one adder operating at 5V, the registers contribute approximately 72% of the total power and approximately 35% of the total delay. This can change drastically if the registers have a longer lifetime than one cycle (the registers have to hold the data for more than one cycle). Referring to Figure 15, if each of the registers has to hold its data for an extra cycle before it can be used, the power contribution jumps to approximately 84% while the delay remains unchanged. Hence, it is important to minimize the number of registers needed in order to efficiently reduce the power consumption. The delay plays less of a vital role. However, reducing the number of registers will also help reduce the latency. The register significance is also emphasized in [14]. Although [14] deals exclusively with latency and latency-constrained scheduling, the register principles are also directly applicable to resource-constrained scheduling.

## 5. Resource-Constrained Scheduling with Register Assignment

In addition to latency and power, the number of registers needed at each control cycle also need to be considered as illustrated in the previous section. While conventional and current resource-constrained scheduling schemes with multiple voltages do a good job of addressing the latency and power, they fail to address the registers needed at each cycle. Our resource-constrained scheduling scheme was developed to address the number of registers while still maintaining an acceptable balance between latency and power.

### 5.1 Our Scheduling Scheme and Example

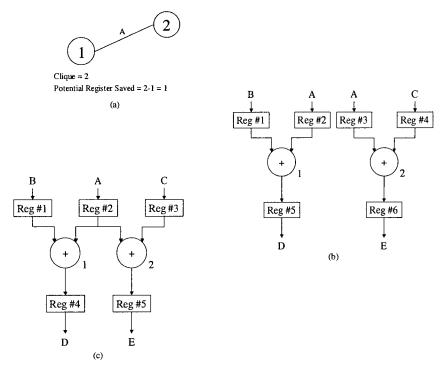

We employ a simple technique to address the register problem. Recognizing the data dependency in the DFG, we use a CFG to help determine where to schedule nodes in order to reduce the number of registers needed. We note that if we schedule all the nodes in the CFG that share a conflict in the same cycle, then we can reduce the number of registers needed by the total number of conflicts or clique minus one.

Figure 16. Register Savings from a CFG. (a) CFG. (b) DFG before utilizing CFG. (c) DFG after utilizing CFG.

For example, in Figure 16a, we see that node 1 and node 2 share an edge or have a conflict. If node 1 has an input of A and B and node 2 has an input of A and C, the CFG tells us that if we are able to schedule node 1 and node 2 in the same clock cycle, then we would be able to reduce the number of registers by one. The reason this is possible is because node 1 and node 2 can now use one register to store the value A instead of two registers (see Figure 16b and 16c).

To maintain a balance between latency and power, our scheme also uses multiple voltages (5V, 3.3V, 2.2V, and 1.8V) and a priority function that includes the depth and mobility of a node. Our heuristic, list-based resource-constrained scheduling scheme tries to balance the conflicting requirements of reducing the

latency and utilizing resources operating at multiple voltages with the need to reduce the number of registers needed at each cycle and operates as follows:

- 1) Determine the depth, mobility, ASAP, and ALAP of each node in the DFG.

- 2) Construct the ready set.

- *3)* For the current cycle:

- a. For all nodes with a mobility of zero or less,

- i. Place all nodes with the same mobility into a single group and prioritize the nodes in each group according to highest depth first.

- ii. Prioritize the groups according to the lowest mobility first.

- iii. Schedule the prioritized nodes starting with the fastest available resource first and moving to the slowest resource.

- iv. Continue scheduling until all nodes with mobility less than zero have been scheduled or all resources have been used. If there are resources remaining, go to Step 3b. Otherwise go to Step 4.

- b. For all remaining nodes with a mobility greater than zero.

- i. Calculate the number of conflicts with each other.

- ii. Place all nodes with the same number of conflicts into a single group and prioritize the nodes in each group according to highest depth first.

- iii. Prioritize the groups according to the highest number of conflicts first.

- iv. Schedule the prioritized nodes starting with the fastest available resource first and moving to the slowest resource.

- v. Continue scheduling until all nodes with a conflict greater than zero have been scheduled or all resources have been used. If there are resources remaining, go to Step 3c. Otherwise go to Step 4.

- c. For all remaining nodes with no conflicts,

- i. Place all nodes with the same mobility into a single group and prioritize the nodes in each group according to highest depth first.

- ii. Prioritize the groups according to the lowest mobility first.

- iii. Schedule the prioritized nodes starting with the fastest available resource first and moving to the slowest resource.

- iv. Continue scheduling until all nodes have been scheduled or all resources have been used. Then go to Step 4.

- 4) Recalculate the mobility of each node, go to the next cycle, and repeat starting with Step 2.

Our resource-constrained scheduling scheme schedules a DFG according to the following order of importance: latency, power determined by the number of registers, power determined from the operating voltages. Conventional schemes simply consider latency since power is determined by the resource constraint. Current multiple voltage schemes consider power determined from the operating voltages then latency. Figure 17 illustrates our resource-constrained scheduling scheme with a resource constraint of three adders—one at 5V, one at 3.3V, and one at 2.2V.

Figure 17. Resource-Constrained Scheduling with Register Assignment Example. (a) Initial DFG. (b) ASAP, ALAP, depth, and mobility of each node. (c) Final Scheduling showing ready sets and scheduling at each cycle. (d) CFG. (e) Final DFG.

Figure 17 shows that our resource-constrained scheduling scheme with multiple voltages and register assignment was able to reduce the total power given a reduced number of resources to use. Instead of having five resources to use as in the no resource constraints case (see Figure 17a), there were only three resources available, each at a different voltage. These resources at different voltages allowed the total power to be reduced by approximately 20%. The maximum number of registers needed also reduced going from seven to five. This is similar to the example in Figure 13. However, the important item to note is that although the maximum number of registers needed is the same in the resource-constrained scheduling scheme with multiple voltages and our scheme, our scheme has a smaller total register power allowing it to achieve a 18% power reduction over the resource-constrained scheduling scheme with multiple voltages. This is possible since our scheme takes advantage of the CFG while the other two schemes do not.

Again though, these power and register reductions came at the cost of latency. Instead of a latency of five like in the no resource-constraints case, the latency is now one greater at six. This is still less than the resource-constrained scheduling scheme with multiple voltages case and is the lowest latency possible for this case. However, this increase in latency may still not be acceptable in some applications. And again, there is also a voltage level shifter overhead associated with this solution.

Overall, our resource-constrained scheduling scheme with multiple voltages and register assignment perform well in finding an optimal solution that addresses and balances the latency and power issues. Power is greatly reduced with only a slight increase in latency. If this slight increase is acceptable, then our scheduling scheme provides the best solution over the conventional resource-constrained scheduling scheme and the current resource constrained scheduling scheme with multiple voltages.

## 5.2. C++ Implementation

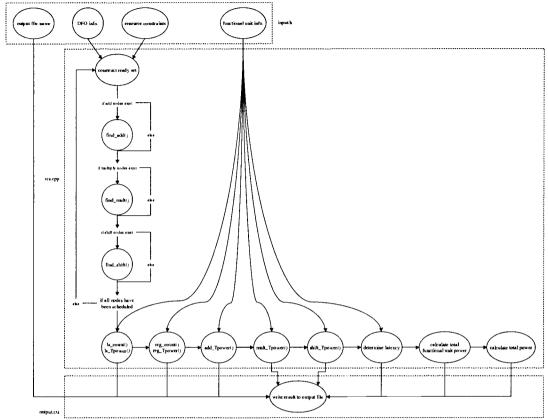

Our C++ implementation has three main parts: 1) the input file; 2) the scheduling scheme; and 3) the output file. The flow of our C++ implementation is shown in Figure 18.

Figure 18. C++ Program Flow

The input file (input.h) is a C++ header file that includes information about the DFG, resource constraints, output file name, and delay and power of the functional units. The DFG is entered as a list of nodes where the format of each node is as follows: {Node Number, ASAP, ALAP, Depth, Mobility, Parent A, Parent B, Child, Node A, Node B, Operation}. The node number is the number of the current node. The ASAP, ALAP, depth, and mobility are defined in section 2. Parent A and B and child refer to the name of the input data values and output data value for the current node, respectively. Node A and B are the node numbers

providing the input data values to the current node. And operation is the type of operation of the current node. The output file name is simply the name the user specifies for the output file. The resource constraint is the maximum number of each type of resource that is available. The functional unit information is obtained from the delay and power characteristics in section 2.