#### AN ABSTRACT OF THE THESIS OF

SUNG CHIAO HU for the M.S. in ELECTRICAL AND (Degree) ELECTRONICS ENGINEERING (Major)

Date thesis is presented May 12, 1967

Title TERNARY DIGITAL SYSTEMS

Redacted for Privacy

Abstract approved Professor Lewis N. Stone

In view of recent developments in large-scale, complex digital systems, it is of interest to broaden the study of two-leveled logical systems to the study of three-leveled systems. This paper introduces the ternary logic system and develops a design approach for ternary digital systems that is based on familiar binary techniques.

Ternary number systems are introduced and two baseconversion algorithms are given: one for integral numbers and the other for fractional numbers. Ternary

arithmetic is similar to binary arithmetic or to decimal

arithmetic. Four algebraic operations, Cycling, Negation, And, and Or, are then defined and the algebra is

systematically developed through postulates and theorems.

The algebraic method of minimization is difficult for a

large number of variables or terms, and the map method

is impracticable for more than three variables. Hence

a programmable minimization method is developed by

analogy with the Quine-McCluskey method for binary minimization.

Diode-transistor schemes of circuit realization are presented. In these, the idea is to use p-n-p and n-p-n transistor pairs to provide the three different voltage levels desired. Tristable devices using three Cycling-gates are also described. A core storage element employs two differently oriented cores and provides one ternary digit of storage. Additional algebraic operations that are used in the current literature are given in the Appendix.

#### TERNARY DIGITAL SYSTEMS

by

SUNG CHIAO HU

A THESIS

submitted to

OREGON STATE UNIVERSITY

in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE

June 1967

APPROVED:

# Redacted for Privacy

Professor of Electrical and Electronics Engineering

in charge of major

# Redacted for Privacy

Head of Department of Electrical and Electronics Engineering

# Redacted for Privacy

Dean of Graduate School

| Date  | thes | sis i | s presented |       | Jay | 12,1 | 967 | <del></del> |  |

|-------|------|-------|-------------|-------|-----|------|-----|-------------|--|

| Турес | l by | Erma  | McClanathar | n for |     | Sun  | , C | Hu          |  |

## ACKNOWLEDGMENTS

The writer is indebted to Professor Louis N. Stone for his valuable help and comments in the writing of this thesis. The writer also wishes to thank Professor Robert A. Short who read the manuscript and offered many constructive suggestions.

## TABLE OF CONTENTS

| I.   | INTRO  | DUCTION                              | 1   |

|------|--------|--------------------------------------|-----|

| II.  | TERNA  | RY NUMBER SYSTEMS AND ARITHMETIC     | 4   |

|      | Α.     | Ternary Number Systems               | 4   |

|      | В.     | Base Conversions                     | 5   |

|      | C.     | Ternary Arithmetic                   | 9   |

| III. | TERNA  | RY ALGEBRA                           | 12  |

|      | Α.     | General Description                  | 12  |

|      | в.     | Basic Operations                     | 14  |

|      | c.     | Postulates                           | 17  |

|      | D.     | Theorems                             | 17  |

| IV.  | MINIM  | IZATION OF TERNARY FUNCTIONS         | 21  |

|      | Α.     | Definitions                          | 21  |

|      | В.     | Algebraic Method                     | 26  |

|      | C.     | Map Method                           | 29  |

|      | D.     | Tabular Method                       | 36  |

| V.   |        | RY SWITCHING CIRCUITS AND STORAGE ES | 42  |

|      | Α.     | Basic Gates                          | 43  |

|      | В.     | Memory Elements                      | 47  |

|      | C.     | Ternary Memory                       | 50  |

| VI.  | CONCL  | USION                                | 54  |

|      | BIBLI  | OGRAPHY                              | 56  |

|      | A DDFN | NTY                                  | 5.8 |

# LIST OF FIGURES

| Figure |                                                           |    |

|--------|-----------------------------------------------------------|----|

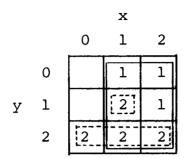

| 1.     | A Two-variable Map                                        | 30 |

| 2.     | Ternary Map for the Function Given in Table XI            | 31 |

| 3.     | A Three-variable Map                                      | 32 |

| 4.     | Three-dimensional Representation of a Three-variable Map  | 33 |

| 5.     | Map for the Function Given in Table XIII                  | 35 |

| 6.     | The Simplification of (a) h-subfunction (b) g-subfunction | 35 |

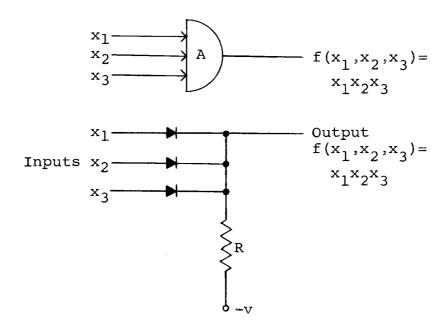

| 7.     | Or-gate                                                   | 44 |

| 8.     | And-gate                                                  | 44 |

| 9.     | Cycling-gate                                              | 45 |

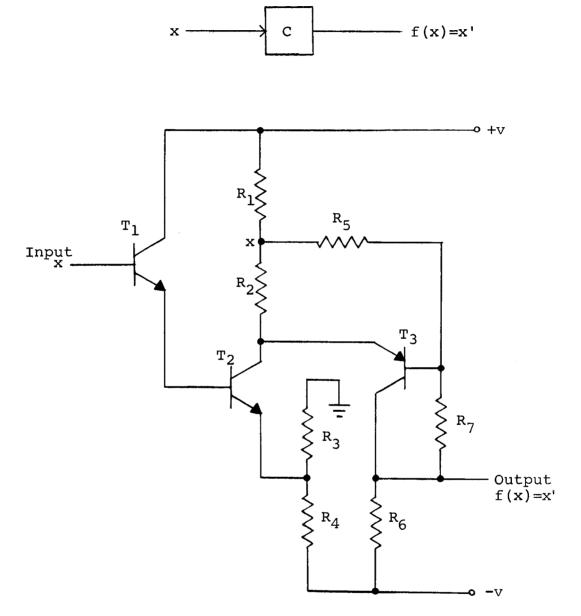

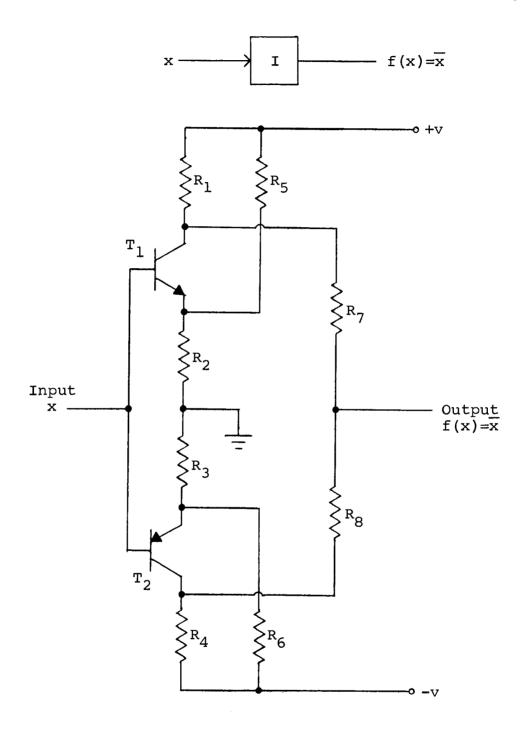

| 10.    | Inverter                                                  | 46 |

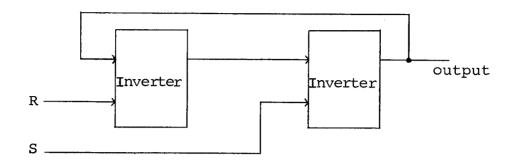

| 11.    | R-S TFF Composed of Two Inverters                         | 48 |

| 12.    | R-S FF in Binary System                                   | 48 |

| 13.    | R-S-T TFF                                                 | 49 |

| 14.    | Astable TFF                                               | 50 |

| 15.    | Ternary Core Switch                                       | 51 |

16. Coincident Current Core Storage Unit..... 52

17.

Ternary Core Memory...... 53

## LIST OF TABLES

| п | n | _ | L | ٦  | _          |

|---|---|---|---|----|------------|

| • | ľ | а | n | -1 | $\epsilon$ |

| I.     | Base Conversions Between (a) Base 2 Digits and Base 3 Digits, (b) Base 3 Digits and Base 10 Digits | 6  |

|--------|----------------------------------------------------------------------------------------------------|----|

| II.    | Ternary Addition                                                                                   | 10 |

| III.   | Ternary Subtraction                                                                                | 10 |

| IV.    | Ternary Multiplication                                                                             | 13 |

| ٧.     | Ternary Functions of One Ternary Variable                                                          | 13 |

| VI.    | Cycling-operation                                                                                  | 14 |

| VII.   | And-operation                                                                                      | 15 |

| VIII.  | Or-operation                                                                                       | 16 |

| IX.    | Negation-operation                                                                                 | 16 |

| х.     | Proof of Theorem 3.6                                                                               | 20 |

| XI.    | An Arbitrary Function to be Expanded in Canonical Form                                             | 24 |

| XII.   | Truth Table for a 10-counter                                                                       | 25 |

| XIII.  | A Three-variable Function                                                                          | 34 |

| XIV.   | Minimization of the Three-variable Function of Table XIII                                          | 39 |

| XV.    | h-type Prime Implicant Table                                                                       | 40 |

| XVI.   | g-type Prime Implicant Table                                                                       | 41 |

| XVII.  | Operation of R-S TFF                                                                               | 48 |

| XVIII. | J <sub>i</sub> -, K <sub>i</sub> -operation                                                        | 59 |

| XIX.   | Another Binary Operator for the Ternary System. (Analogous to the Binary "Stroke" Function)        | 63 |

#### TERNARY DIGITAL SYSTEMS

#### I. INTRODUCTION

The ternary digital system is one possible form of digital system. Although binary switching theory has been used in almost every digital system developed so far, this is mainly due to the fact that basic switching elements in common use are two-state devices and that design techniques for the binary system are well-developed. However, it is useful to broaden the study of two-leveled logical systems to that of three-leveled systems. The motivation for such an extension is based upon the following reasons:

- 1. Some of the operating systems in use actually involve three discrete states in logical relations. For example, industrial control systems can be most directly handled with mathematical models of three-valued logical systems.

- 2. Three-valued systems offer an alternative approach to ameliorate some of the complicated problems which arise in two-valued systems.

- 3. The advance of electronic technology should make reliable three-state devices available in the not-too-remote future. It is shown in (8) that if the amount of the equipment required is proportional to the

number base, then the most efficient base to use is base three.

- 4. Ternary systems can provide several advantages over binary systems such as speed, cost, space, weight, etc. Also, they have been proposed to enhance reliability by using the third value to indicate error situations.

- 5. In the fields of communication and data transmission, the greater base implies more accurate transmission per transmitted digit. In this regard, the

study of the ternary system can be thought of as a start

for systems utilizing even higher bases.

With a three-valued system, three-valued switching functions must be used. To this end, a number of authors have been concerned recently with the design of ternary switching circuits. A ternary number system was introduced by Morris (9). A comparison of base three vs. base two systems is given by Santos (14). Lee and Chen (5), Muehldorf (10), and Vacca (16) consider the algebraic aspects of the ternary system. Lowenschuss (6) and Muehldorf (9) have suggested the application of the Rutz transistor to the design of ternary circuits. Other ternary devices also have been suggested in the literature (1), (4), (13). Diode-transistor schemes were introduced by Hallworth and Heath (2) and Santos

(15). Other papers on switching theory and logical design include (6), (7), (10), and (17). An extension of the application of binary devices and Boolean algebra to the realization of three-valued logic circuits was recently introduced by Pugh (12).

This paper develops a design theory for a ternary digital system that is based on familiar binary algebra, including the simplification and circuit design techniques of binary systems. The main text is divided into four parts. The first part introduces the ternary number systems and arithmetic; the second part discusses the algebraic properties of the ternary system; the third part gives three minimization methods for ternary functions; the last part presents some techniques appropriate for hardware realizations.

#### II. TERNARY NUMBER SYSTEMS AND ARITHMETIC

The most commonly used number system in computers and other switching circuits is the well-known binary number system. This is due to the fact that most physical devices in common use exhibit two easily distinguished states. Ternary (base 3) number systems, however, have been shown to be the most efficient number system if the assumption that the required equipment is proportional to the number base is met. In this chapter, the ternary number system will be introduced. Algorithms for base conversions will be developed and illustrated by means of examples. Finally, ternary arithmetic will be defined.

## A. Ternary Number Systems

Definition 2.1. A number N is said to be in ternary form if and only if

$$N = \sum_{i=-n}^{m-1} t_i 3^{i}$$

$$= t_{m-1} 3^{m-1} + t_{m-2} 3^{m-2} + \dots + t_1 3^{1} + t_0 3^{0} + t_{-1} 3^{-1} + \dots + t_{-n} 3^{-n}$$

where m is the number of integral digits,  $n \ \ \text{is the number of fractional digits,}$  and  $t_{\dot{1}} \in \big\{\, 0\,, 1\,, 2\,\big\}\,.$

In general, we simply write

$$N = t_{m-1}t_{m-2}\cdots t_1t_0 \cdot t_{-1}\cdots t_{-n}$$

where the "." is called the "ternary point," and  $\textbf{t}_{\hat{\textbf{i}}}$  is a "ternary digit."

Definition 2.2. The complement of a ternary digit, t, denoted by  $\overline{t}$ , is the difference between that digit and the number 2, thus

$$\overline{t} = 2 - t$$

.

There are three ways to represent a negative ternary number, and these are analogous to the usual binary conventions.

Negative of N = -N sign magnitude

= 3<sup>m</sup>-N 3's complement

= 3<sup>m</sup>-N-L 2's complement.

L represents one in the least significant place of N.

#### B. Base Conversions

Since most present digital devices utilize the binary number system, the conversion between a base 2 number and a base 3 number is very important. The conversion between ternary and decimal systems is, of course, also of great interest. Table I defines such conversions on a digit basis.

Table I. Base Conversions Between (a) Base 2

Digits and Base 3 Digits, (b) Base 3

Digits and Base 10 Digits.

| (a) | Base 2 | Base 3 |

|-----|--------|--------|

|     | 0 0    | 0      |

|     | 0 1    | 1      |

|     | 1 0    | 2      |

| (b) | Base 3 | Base 10 |

|-----|--------|---------|

|     | 0 0 0  | 0       |

|     | 0 0 1  | 1       |

|     | 0 0 2  | 2       |

|     | 0 1 0  | 3       |

|     | 0 1 1  | 4       |

|     | 0 1 2  | 5       |

|     | 0 2 0  | 6       |

|     | 0 2 1  | 7       |

|     | 0 2 2  | 8       |

|     | 100    | 9       |

Two algorithms are now presented for conversions between any two number systems. One is for integral numbers, and the other is for fractional numbers.

Algorithm A: (for base conversion of integral numbers)

- 1. Express the "new base,"  $b_2$ , in terms of the "old base,"  $b_1$ .

- 2. Divide the "old number" and its successive quotients by the number found in step one until

the quotient is zero. Name the successive remainders as  $r_1$ ,  $r_2$ ,  $r_3$ ,  $\cdots$ . Note that the remainders are still in the "old base."

- 3. If  $b_2 < b_1$ , then the remainders obtained in step two are in correct form. If  $b_2 > b_1$ , then the remainders must be converted into the "new base."

- 4. The remainders in correct form are then taken in reverse order to produce the "new number."

Example: Convert the number 101001 in base 2 to its representation in base 3.

1. 3 is represented by 11 in base 2

3. Since 3>2, the remainders are converted from base 2 to base 3

$$r_{1}: \quad 10 \longrightarrow 2$$

$$r_{2}: \quad 1 \longrightarrow 1$$

$$r_{3}: \quad 1 \longrightarrow 1$$

$$r_{4}: \quad 1 \longrightarrow 1$$

4. The number in base 3 form is

$$N_3 = r_4 r_3 r_2 r_1 = 1112.$$

Algorithm B: (for base conversion of fractional numbers)

- l. Express the "new base," b<sub>2</sub>, in terms of the

"old base," b<sub>1</sub>.

- 2. Multiply the given fractional number by the number found in step one. The resulting integral part is designated as  $\mathbf{I}_1$  and the fractional part as  $\mathbf{F}_1$ .

- 3. Again multiply the fractional part,  $F_1$ , by the number found in step one. The resulting integral part is designated as  $I_2$  and the fractional part as  $F_2$ .

- 4. Continue the process in this fashion until  $\mathbf{F}_{i}$  becomes zero or i reaches the desired degree of significance.

- 5. If b<sub>2</sub> < b<sub>1</sub>, then no conversions are made to the successively obtained integral parts. If b<sub>2</sub> > b<sub>1</sub>, each integral part is converted into the "new base."

- 6. The "new number" is formed by taking integral parts in right order, i.e.,  $I_1I_2I_3\cdots$ .

Example: Convert the binary number 0.101001 into a ternary number. Express the ternary number to five places if the conversion is not exact within this range.

- 1. 3 is represented by 11 in binary

- 2.  $0.101001 \times 11 = 1.111011$   $I_1 = 1, F_1 = 0.111011$

3.

$$0.111011x11 = 10.110001 I_2=10, F_2=0.110001$$

4.

$$0.110001x11 = 10.010011$$

$I_3=10$ ,  $F_3=0.010011$   $0.010011x11 = 0.111001$   $I_4=0$ ,  $F_4=0.111001$   $0.111001x11 = 10.101011$   $I_5=10$ ,  $F_5=0.101011$

5. Since  $b_2 > b_1$ , conversions to base 3 equivalents are made on the I's.

$$I_{1}: 1 \longrightarrow 1$$

$$I_{2}: 10 \longrightarrow 2$$

$$I_{3}: 10 \longrightarrow 2$$

$$I_{4}: 0 \longrightarrow 0$$

$$I_{5}: 10 \longrightarrow 2$$

6. The "new number" in ternary form is

$$N_3 = 0.1_1 I_2 I_3 I_4 I_5 = 0.12202$$

The conversion is not exact in this case.

## C. Ternary Arithmetic

Ternary arithmetic is similar to binary arithmetic or to decimal arithmetic. The following tables define the addition, subtraction, and multiplication of ternary digits.

# Definition 2.3. Ternary addition:

Table II. Ternary Addition

(Entries define the results of A + B)

| АВ | 0  | 1 | 2 | B  | 0    | 1 | 2  |

|----|----|---|---|----|------|---|----|

| 0  | 0  | 1 | 2 | 0  | 0    | 0 | 0  |

| 1  | 1  | 2 | 0 | 1. | 0    | 0 | 1  |

| 2  | 2  | 0 | 1 | 2  | 0    | 1 | 1. |

|    | su | m |   | C  | arry |   |    |

Definition 2.4. Ternary subtraction:

Table III. Ternary Subtraction (Entries define the results of A - B)

| 0    | 1     | 2                 | В           | 0                         | 1.                                                                                        | 2                                                                                           |

|------|-------|-------------------|-------------|---------------------------|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| 0    | 1     | 2                 | 0           | 0                         | 0                                                                                         | 0                                                                                           |

| 2    | 0     | 1                 | 1           | 1                         | 0                                                                                         | O                                                                                           |

| 1    | 2     | 0                 | 2           | 1                         | 1                                                                                         | 0                                                                                           |

| ffer | enc   | е                 | bo bo       | orro                      | W                                                                                         |                                                                                             |

|      | 0 2 1 | 0 1<br>2 0<br>1 2 | 0 1 2 2 0 1 | B 0 1 2 0 2 0 1 1 1 2 0 2 | 0     1     2     0     0       2     0     1     1     1       1     2     0     2     1 | 0     1       2     0       1     1       1     2       2     0       1     2       1     1 |

# Definition 2.5. Ternary multiplication:

Table IV. Ternary Multiplication (Entries define the results of  $A \cdot B$ )

| ВА | 0    | 1  | 2 | B | 0   | 1 | 2 |

|----|------|----|---|---|-----|---|---|

| 0  | 0    | 0  | 0 | 0 | 0   | 0 | 0 |

| 1  | 0    | 1  |   | 1 | 0   | 0 | 0 |

| 2  | 0    | 2  | 1 | 2 | 0   | 0 | 1 |

| pı | rodu | ct |   | C | arr | У |   |

The arithmetic operations can easily be performed by following the above definitions.

#### III. TERNARY ALGEBRA

## A. General Description

The mathematical model for a ternary switching circuit is the three-valued propositional calculus or composition algebra. The form used here was first introduced by E. L. Post in his "Introduction to General Theory of Elementary Propositions" (11). Various people have made contributions in this area (6), (10), (17), and the resulting algebra is often referred to as "Post Algebra."

The truth table used in two-valued switching theory can be readily extended to the three-valued case. All possible combinations of input variables are listed at the left and the corresponding value of the function is written at the right. In a ternary system, the truth table for n-input variables has 3<sup>n</sup> different combinations of the values of the input variables (i.e., 3<sup>n</sup> rows). The function can have any one of the three different values for each input combination. Hence there are 3<sup>3n</sup> functions of n-variables in a ternary system. The 27 (3<sup>31</sup>) functions of one input variable are shown in Table V.

Table V. Ternary Functions of One Ternary Variable.

| х | fo | f <sub>l</sub> | f <sub>2</sub> | f <sub>3</sub> | f <sub>4</sub> | f <sub>5</sub> | f <sub>6</sub> | f <sub>7</sub> | f <sub>8</sub> | f <sub>9</sub> | f <sub>10</sub> | f <sub>11</sub>         |

|---|----|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|-----------------|-------------------------|

| 0 | 0  | 0              | 0              | 0              | 0              | 0              | 0              | 0              | 0              | 1              | 1               | f <sub>11</sub> 1  0  2 |

| 1 | 0  | 0              | 0              | 1              | 1              | 1              | 2              | 2              | 2              | 0              | 0               | 0                       |

| 2 | 0  | 1              | 2              | 0              | 1              | 2              | 0              | 1              | 2              | 0              | 1               | 2                       |

| f <sub>12</sub> | f <sub>13</sub> | f <sub>14</sub> | f <sub>15</sub> | <sup>f</sup> 16 | f <sub>17</sub> | f <sub>18</sub> | f <sub>19</sub> | f <sub>20</sub> |

|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| 1               | 1               | 1               | 1               | 1               | 1               | 2               | 2               | 2               |

| 1               | 1               | 1               | 2               | 2               | 2               | 0               | 0               | 0               |

| 0               | 1               | 2               | 0               | 1               | 2               | 0               | 1               | 2               |

| f <sub>21</sub> | f <sub>22</sub> | f <sub>23</sub> | f <sub>24</sub> | f <sub>25</sub> | f <sub>26</sub> |

|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| 2               |                 |                 | 2               |                 |                 |

| 1               | 1               | 1               | 2               | 2               | 2               |

| 0               | 1               | 2               | 0               | 1               | 2               |

|                 |                 |                 |                 |                 |                 |

Ternary algebra is developed in three steps. The first step is to define symbols and operations. The second step is to select a set of postulates which are the basis for the algebra. The third step is to formulate some fundamental theorems. These theorems together with the postulates are the working rules for the algebra.

### B. Basic Operations

Definition 3.1. Cycling-operation ('): The Cycling of x, denoted as x', is defined as

$x' = (x+1) \mod 3$  where x and  $x' \in \{0,1,2\}$ . This definition is also given in Table VI.

Table VI. Cycling-operation

| x | x' |

|---|----|

| 0 | 1  |

| 1 | 2  |

| 2 | 0  |

|   |    |

Definition 3.2. And-operation ( $\cdot$ ): X and y, denoted as x $\cdot$ y (or simply xy), is defined as the smaller of the two, i.e.,

$$x \cdot y = \min \{x, y\}$$

.

This definition is also given in Table VII.

Table VII. And-operation

| x           | У | х.у |

|-------------|---|-----|

| 0           | _ | 0   |

| 0           | 0 | 0   |

| 0           | 1 | 0   |

| 0           | 2 | 0   |

| 1           | 0 | 0   |

| 1           | 1 | 1   |

| 1           | 2 | 1   |

| 2           | 0 | 0   |

| 2<br>2<br>2 | 1 | 1   |

| 2           | 2 | 2   |

|             | 1 |     |

It was shown by Post (11) that these two operations constitute a functionally complete set; that is, all ternary functions can be synthesized by some composition of these two operations. Although the two operations as defined constitute a logically complete set, the resulting algebraic expressions can be very long and complicated, hence circuit realizations corresponding to such expressions can be costly. Fortunately other logical gates can be devised that correspond to additional algebraic operations to be introduced. The set of operations will still be logically complete as long as the Cycling and And operations are included.

Definition 3.3. Or-operation (+): x Or y, denoted as x+y, is defined as the larger of the two, i.e.,

$$x+y = max \{x,y\}$$

.

Table VIII gives this definition in truth table form.

Table VIII. Or-operation

| x | У | x+y         |

|---|---|-------------|

| 0 | 0 | 0           |

| 0 | 1 | 1           |

| 0 | 2 | 2           |

| 1 | 0 | 1           |

| 1 | 1 | 1           |

| 1 | 2 | 2           |

| 2 | 0 | 2           |

| 2 | 1 | 2<br>2<br>2 |

| 2 | 2 | 2           |

|   |   |             |

The set  $\{0,1,2\}$  and the two binary operations And and Or form a distributive lattice with zero element 0 and universal element 2.

Definition 3.4. Negation- (complementation-) operation (): the negation of x, denoted as  $\overline{x}$ , is defined as  $\overline{x} = 2 - x$ .

The truth table of this definition is given in Table IX.

Table IX. Negation-operation

| 0 2 |

|-----|

|     |

| 1 1 |

| 2 0 |

Additional operations have been used in the literatures. Some of the more important ones are given in the Appendix, together with theorems associated with them.

#### C. Postulates

Definition 3.5. An algebraic structure  $f = \langle T,0,1,2,\cdot,+,', = \rangle$ , where T is a set,  $0,1,2 \in T$ ,  $\cdot$  and + are binary operations on T, ' is a unary operation on T, and = is the equality relation on T, is called a ternary algebra if and only if it satisfies the following postulates. For all  $a,b,c \in T$

- Pl. Idempotent a+a=a a·a=a

- P2. Commutative a+b=b+a a·b=b·a

- P3. Associative (a+b)+c=a+(b+c)  $(a\cdot b)\cdot c=a\cdot (b\cdot c)$

- P4. Distributive a+bc=(a+b)(a+c) a(b+c)=ab+ac

- P5. Identity a+0=a  $a\cdot 2=a$

Note that usually 1 is used as the symbol for the identity operation of And. The symbol 2 is used as the identity element in this paper so that it agrees with Table VII which defines the And operation.

#### D. Theorems

From the above basic definitions and postulates, the following theorems of ternary algebra can be formulated and proved.

Theorem 3.1. a''' = a

Proof: We use finite induction

Let

$$a=0$$

, then  $a' = 0' = 1$  Def. 3.1

$$a'' = (a')' = 1' = 2$$

$$a''' = (a'')' = 2' = 0$$

Let

$$a=1$$

, then  $a' = 1'=2$

$$a'' = (a')' = 2' = 0$$

$$a''' = (a'')'=0'=1$$

Let

$$a=2$$

, then  $a' = 2'=0$

$$a'' = (a')'=0'=1$$

$$a''' = (a'')'=1'=2$$

Theorem 3.2.  $a \cdot a' \cdot a'' = 0$ , a + a' + a'' = 2

$$0 \cdot 1 \cdot 2 = 0$$

Def. 3.2 and P3

$$0+1+2=2$$

Def. 3.3 and P3

Theorem 3.3.  $a \cdot 0 = 0$ , a + 2 = 2

Proof:

$$a \cdot 0 = a \cdot (a \cdot a' \cdot a'')$$

Th. 3.2

$$= 0$$

Th. 3.2

$$a+2 = a+(a+a'+a'')$$

Th. 3.2

$= (a+a)+a'+a''$  P 3

$= a+a'+a''$  P 1

$= 2$  Th. 3.2

Theorem 3.4.  $a \cdot (a+b)=a$ ,  $a+ab=a$

Theorem 3.4.

$$a \cdot (a+b)=a$$

,  $a+ab=a$

Theorem 3.5.

$$ab+ab'+ab'' = a$$

$(a+b) \cdot (a+b') \cdot (a+b'') = a$

Proof:

$$ab+ab'+ab'' = a(b+b'+b'')$$

P 4

$$= a \cdot 2$$

Th. 3.2

$$= a$$

P 5

$$(a+b) \cdot (a+b') \cdot (a+b'') = a+bb'b''$$

P 4

= a+0 Th. 3.2

= a P 5

Theorem 3.6.  $\overline{ab}=\overline{a+b}$   $\overline{a+b}=\overline{a}$

Proof: By perfect induction

Table X. Proof of Theorem 3.6.

| a | b | a+b | a+b | <u>a</u> | b | <u>a</u> <u>b</u> | a•b | a ⋅ b | a+b |

|---|---|-----|-----|----------|---|-------------------|-----|-------|-----|

| 0 | 0 | 0   | 2   | 2        | 2 | 2                 | 0   | 2     | 2   |

| 0 | 1 | 1   | 1   | 2        | 1 | 1                 | 0   | 2     | 2   |

| 0 | 2 | 2   | 0   | 2        | 0 | 0                 | 0   | 2     | 2   |

| 1 | 0 | 1   | 1   | 1        | 2 | 1                 | 0   | 2     | 2   |

| 1 | 1 | 1   | 1   | 1        | 1 | 1                 | 1   | 1     | 1   |

| 1 | 2 | 2   | 0   | 1        | 0 | 0                 | 1   | 1     | 1   |

| 2 | 0 | 2   | 0   | 0        | 2 | 0                 | 0   | 2     | 2   |

| 2 | 1 | 2   | 0   | 0        | 1 | 0                 | 1   | 1     | 1   |

| 2 | 2 | 2   | 0   | 0        | 0 | 0                 | 2   | 0     | 0   |

|   |   |     |     |          |   |                   |     |       |     |

Note that the principle of duality also holds in the ternary algebra. The application of these theorems will be illustrated in the next chapter.

#### IV. MINIMIZATION OF TERNARY FUNCTIONS

#### A. Definitions

One of the basic problems of logical design is the simplification of a given function. The problem of determining the minimal representation of a function is very complicated and has not been completely solved even for the binary case. Minimization in the ternary case, as in the binary case, will depend greatly on the switching devices available. The usual procedure is to establish one parameter, and then the circuitry is minimized with respect to that parameter. There are many ways to select the parameter of interest and the one used here is represented by the cost function, C.

Definition 4.1. The cost function, C, is defined as the number of variable occurrences plus the number of operations in a given function. All three states of a variable are assumed to be available, i.e., the Cycling operation on individual variables is not included in the cost function.

There are basically three ways to minimize a logic function. These are:

- 1. The algebraic method,

- 2. the map method, and

- 3. the tabular method.

Before these methods are discussed, the following terms will be defined. The definitions used here are analogous to those used for the binary system.

Definition 4.2. Literal -- a variable or its cycling, e.g., a, a', a'', etc.

Definition 4.3. Monomial -- a product of literals, e.g., ab, a'bc'', etc.

Definition 4.4. Elementary monomial -- a monomial which contains all the variables on which the function is defined.

Definition 4.5. Implicant -- there are two types of implicants of a function f of n variables.

- 1) An h-type implicant,  $I_h$ , is a monomial satisfying the condition  $l \cdot I_h(a) \le f(a)$  for every  $a \in T^n.$

- 2) A g-type implicant,  $I_g$ , is a monomial satisfying the condition  $I_g(a) \le f(a)$  for every  $a \in T^n$ .

Definition 4.6. Essential -- a literal is essential in an implicant if the deletion of that literal will make it a non-implicant.

Definition 4.7. Prime implicant — there are two types of prime implicant of a function f of n variables.

- 1) An h-type prime implicant,  $P_h$ , is an h-type implicant in which every literal is essential.

- 2) A g-type prime implicant,  $P_g$ , is a g-type implicant in which every literal is essential.

Definition 4.8. Cover -- a function  $\overline{\Phi}$  covers a function f if and only if

$$f = 0 \Longrightarrow \overline{\Phi} = 0$$

$$f = 1 \Longrightarrow \overline{\Phi} = 1$$

$$f = 2 \implies \overline{\Phi} = 2$$

Definition 4.9. Prime implicant table -- a prime implicant table is a table in which columns are represented by prime implicants and rows represented by elementary monomials of a given function. The entries are filled with check marks where the column covers the row.

Definition 4.10. Minimal function — a function  $\overline{\Phi}$  is said to be minimal if  $\overline{\Phi}$  covers f and the cost function is minimal.

Theorem 4.1. Any ternary function can be written in the form

$$f = l \cdot h(x_1, \dots, x_n) + g(x_1, \dots, x_n)$$

where  $h(x_1, \dots, x_n)$  represents the subfunction whose output is 1 and  $g(x_1, \dots, x_n)$  represents the subfunction whose output is 2.

A function in the form of Theorem 4.1 is called in canonical form. Note that the h-subfunction and the q-subfunction cannot contain the same terms.

Example: Give an algebraic expression for the function defined by Table XI.

Table XI. An Arbitrary Function to be Expanded in Canonical Form.

| _x | у | f |  |

|----|---|---|--|

|    |   |   |  |

| 0  | 0 | 0 |  |

| 0  | 1 | 0 |  |

| 0  | 2 | 2 |  |

| 1  | 0 | 1 |  |

| 1  | 1 | 2 |  |

| 1  | 2 | 2 |  |

| 2  | 0 | 1 |  |

| 2  | 1 | 1 |  |

| 2  | 2 | 2 |  |

|    |   |   |  |

Notation: If w is a variable, let

w represent w = 0

w' represent w = 1

w'' represent w = 2

then, for this example

$$h(x,y) = x'y+x''y+x''y'$$

$$g(x,y) = xy'' + x'y' + x'y'' + x''y''$$

$f = l \cdot h + g = l \cdot [x'y + x''y + x''y'] + xy'' + x'y' + x'y'' + x''y'' +$

Example: Write the logic equations for a sequential 10-counter.

The truth table of a possible 10-counter is given below.

Table XII. Truth Table for a 10-Counter.

| P <sub>3</sub> | P <sub>2</sub> | P <sub>1</sub> | Р3 | P <sub>2</sub> | P <sub>1</sub> |

|----------------|----------------|----------------|----|----------------|----------------|

| 0              | 0              | 0              | 0  | 0              | 1              |

| 0              | 0              | 1              | 0  | 0              | 2              |

| 0              | 0              | 2              | 0  | 1              | 0              |

| 0              | 1              | 0              | 0  | 1              | 1              |

| 0              | 1              | 1              | 0  | 1              | 2              |

| 0              | 1              | 2              | 0  | 2              | 0              |

| 0              | 2              | 0              | 0  | 2              | 1              |

| 0              | 2              | 1              | 0  | 2              | 2              |

| 0              | 2              | 2              | 1  | 0              | 0              |

| 1              | 0              | 0              | 0  | 0              | 0              |

The logic equations can be written as

$$P_{1} = 1 \cdot (p_{3}p_{2}p_{1} + p_{3}p_{2}'p_{1} + p_{3}p_{2}'p_{1}) + p_{3}p_{2}p_{1}' + p_{3}p_{2}'p_{1}' + p_{3}p_{2}'p_{1$$

#### B. Algebraic Method

The algebraic method of simplification is performed by utilizing the properties of the ternary algebra stated in Chapter III. Since the g-subfunction represents the input combinations that produce the output value 2 and the h-subfunction represents the input combinations that produce the output value 1, the complete function is represented by f = 1·h+g. By the nature of "·" and "+" operations, the terms in the g-subfunction can be used as "don't care" terms for the simplification of h-subfunction but not vice versa.

In the binary logic, a very useful relationship for minimization is

$$AB+A\overline{B} = A$$

.

The counter part of this relationship in the ternary logic is

$$AB+AB'+AB'' = A$$

.

Several examples are given below to illustrate the algebraic method of simplification.

Example: Simplify the function obtained in Section A, page 24.

$$f = 1 \cdot (x'y + x''y + x''y') + xy'' + x'y' + x'y'' + x''y''$$

Each subfunction will be minimized individually.

Example: Simplify the logic equations of the 10-counter in Section A.

$$P_{1} = 1 \cdot (p_{3}p_{2}p_{1} + p_{3}p_{2}p_{1} + p_{3}p_{2}p_{1}) + p_{3}p_{2}p_{1} + p_{3}p_{2}p_{1} + p_{3}p_{2}p_{1}' + p_{3}p_{2}'p_{1}' + p$$

Example: Simplify the following functions as much as possible.

= xy

$$1 \cdot h = 1 \cdot (x \cdot (x+y) + x' \cdot (x' + z) + x'' \cdot (x'' + w))$$

$$= 1 \cdot (x+x' + x'')$$

$$= 1 \cdot 2$$

$$= 1$$

$$f = 1 \cdot h + q = 1 + xy$$

As in the binary system, the algebraic manipulation may be difficult for a large number of variables or terms, and one is not certain that the function so obtained is minimal.

# C. Map Method

Although the map method is easy and convenient, its applicability to the ternary system is very limited due to the large number of combinations. In the binary system, the map method is efficient up to about five or six variables. In the ternary system, the limit is three.

A two-variable map is given in Figure 1. The minimization procedures are similar to those used in binary minimization. These procedures consist of joining corresponding cells into blocks as large as possible.

|   |   |   | х |   |

|---|---|---|---|---|

|   |   | 0 | 1 | 2 |

|   | 0 | 1 | 4 | 7 |

| У | 1 | 2 | 5 | 8 |

|   | 2 | 3 | 6 | 9 |

Figure 1. A two-variable map.

The rules for map method of simplification are:

- Joining of adjacent cells with equal outputs.

The required conditions are 3xl, 3x2, 3x3

arrays.

- 2. Multiple use of cells for different blocks is permitted.

- 3. Cells with output value 2 can be considered as "don't care" cells for the formation of blocks with output value 1.

- 4. Always block the largest possible blocks first. Example: Use map method to simplify the function given by Table XI, Section A.

The table is converted into map form as shown in Figure 2.

Figure 2. Ternary map for the function given in Table XI.

- 1. The cells in third row have the same output value, that is, 2. They are combined as one block since they satisfy the condition lx3. This block is represented by y".

- 2. The center cell (cell 5) cannot be combined with its adjacent cells, hence no simplification can be made here. It is represented by x'y'.

- 3. For the cells 4 through 9, the three cells with output value of 2 can be used as "don't care" cells for the other three cells according to rule 3. Hence a block containing 3x2 cells can be formed. The term that represents this block is 1 · (x'+x").

The function that results from this simplification technique is therefore

$$f = 1 \cdot (x' + x'') + y'' + x'y',$$

which agrees with what was obtained by algebraic manipulation in Section B, page 27.

For a three-variable function, a three-dimensional map can be used. But with pencil and paper, it is more convenient to use a two-dimensional map as shown in Figure 3. In this map, cell 14 is considered to be adjacent to cells 11, 13, 15, 17 and also cells 5 and 23.

|   |   |   |   |   |    | . <b>X</b> |    |    |    |    |

|---|---|---|---|---|----|------------|----|----|----|----|

|   |   | 0 | 0 | 0 | 1  | 1          | 1  | 2  | 2  | 2  |

|   | 0 | 1 | 4 | 7 | 10 | 13         | 16 | 19 | 22 | 25 |

| z | 1 | 2 | 5 | 8 | 11 | 14         | 17 | 20 | 23 | 26 |

|   | 2 | 3 | 6 | 9 | 12 | 15         | 18 | 21 | 24 | 27 |

|   |   | 0 | 1 | 2 | 0  | 1          | 2  | 0  | 1  | 2  |

|   |   |   |   |   |    | У          |    |    |    |    |

Figure 3. A three-variable map.

Cell 11 is adjacent to cells 10, 12, 14 and cells 2 and 20, but not to cell 8. It is probably easier to visualize the adjacencies if the x-variable is displayed in a third dimension as shown in Figure 4. The front-back adjacencies are then clear.

The rules for combination of cells are the same as given for the case of two variables except that now the front-back adjacencies should also be considered. This will complicate the determination of the minimal set of implicants to a great extent.

|   |   |   |    | 2  |    |    |

|---|---|---|----|----|----|----|

|   | x |   | 1  | 19 | 22 | 25 |

|   |   | 0 | 10 | 13 | 16 | 26 |

| z | 0 | 1 | 4  | 7  | 17 | 27 |

|   | 1 | 2 | 5  | 8  | 18 | 2  |

|   | 2 | 3 | 6  | 9  | 2  | •  |

|   | • | 0 | 1  | 2  | •  |    |

|   |   |   |    | У  |    |    |

Figure 4. Three-dimensional representation of a three-variable map.

Example: Simplify the function given in Table XIII (d stands for "don't care").

Table XIII. A Three-variable Function

|                                       | x                                       | У                          | z                       | f                                               |

|---------------------------------------|-----------------------------------------|----------------------------|-------------------------|-------------------------------------------------|

|                                       | 0 0                                     | 0 0                        | 0<br>1<br>2             | 1<br>0<br>1                                     |

|                                       | 000000000000000000000000000000000000000 | 0000 111 222 0000 111 2222 | 012 012 012 012 012 012 | 1 0 1 2 0 d 1 2 1 1 2 d 2 0 0 2 2 2 1 0 1 2 1 d |

|                                       | 0                                       | 2                          | 0                       | 1                                               |

|                                       | 0                                       | 2                          | 1                       | 2                                               |

|                                       | 0                                       | 2                          | 2                       | 1                                               |

|                                       | 1                                       | 0                          | 0                       | 1                                               |

|                                       | 1                                       | 0                          | 1                       | 2                                               |

|                                       | 1                                       | 0                          | 2                       | d                                               |

|                                       | 1                                       | 1                          | 0                       | 2                                               |

|                                       | 1                                       | 1                          | 1                       | 0                                               |

|                                       | 1                                       | 1                          | 2                       | 0                                               |

|                                       | 1                                       | 2                          | 0                       | 2                                               |

|                                       | 1                                       | 2                          | 1                       | 2                                               |

|                                       | 1                                       | 2                          | 2                       | 2                                               |

| · · · · · · · · · · · · · · · · · · · | 2                                       | 0                          | 0                       | 1                                               |

|                                       | 2                                       | 0                          | 1                       | 0                                               |

|                                       | 2                                       | 0                          | 2                       | 1                                               |

|                                       | 2                                       | 1                          | 0                       | 2                                               |

|                                       | 2                                       | 1                          | 1                       | 1                                               |

|                                       | 2                                       | 1                          | 2                       | 0                                               |

|                                       | 2<br>2<br>2                             | 2 2 2                      | 0<br>1<br>2             | 1<br>1<br>d                                     |

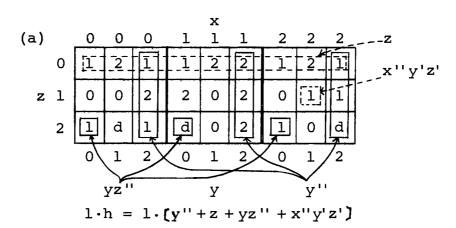

The map that corresponds to this given function is shown in Figure 5. For clarity, the simplifications of the h-subfunction and that of the g-subfunction are

shown in Figure 6 (a) and (b) respectively.

|   |   |   |   |   |   | x  |   |   |   |   |

|---|---|---|---|---|---|----|---|---|---|---|

|   |   | 0 | 0 | 0 | 1 | 1_ | 1 | 2 | 2 | 2 |

|   | 0 | 1 | 2 | 1 | 1 | 2  | 2 | 1 | 2 | 1 |

| z | 1 | 0 | 0 | 2 | 2 | 0  | 2 | 0 | 1 | 1 |

|   | 2 | 1 | d | 1 | đ | 0  | 2 | 1 | 0 | d |

|   | , | 0 | 1 | 2 | 0 | 1  | 2 | 0 | 1 | 2 |

|   |   |   |   |   |   | У  |   |   |   |   |

Figure 5. Map for the function given in Table XIII.

g = x'y'' + y'z + xy''z' + x'yz'

Figure 6. The simplification of

- (a) h-subfunction

- (b) g-subfunction

From these maps, it is determined that  $f = 1 \cdot h + g = 1 \cdot \left[z + y'' + yz'' + x''y'z'\right] + x'y'' + y'z + xy''z' + x'yz'.$

It is obvious that the map method is also very limited, and is not as straightforward as that of the binary system.

# D. Tabular Method

For a greater number of variables than about three, neither algebraic nor map methods are practical. However, the tabular method described in this section may be used in these cases. This method can also be programmed for automatic machine simplification.

The procedures for tabular simplification are described by the following algorithm. The algorithm provides a systematic method of applying a limited set of reduction rules in a converging process in order to obtain a minimal function.

# Algorithm C:

- List all elementary monomials corresponding to f=1 as group 1, to f=2 as group 2, and to the don't care as group 3.

- 2. Minimize each group using the relationship AB+AB'+AB''=A.

Note that groups 2 and 3 can both be used as don't care terms to minimize group 1, and

- group 3 alone as don't care terms for the minimization of group 2.

- 3. Check those monomials which have been used to form new monomials. Also, monomials can be repeatedly used if so applicable. Note that if a monomial in group 2 is used as a don't care term for group 1, no check mark is made for the monomial in group 2, as it must be accounted for in group 2.

- 4. The process continues until no further simplification can be made. All unchecked monomials in groups 1 and 2 are prime implicants.

- 5. Make prime implicant tables for groups 1 and 2. Choose appropriate prime implicants to form a minimal function.

Example: Simplify the function given in Table XIII using the tabular method.

- 1. The three groups are listed below in column 1.

For ease in tracing the steps of the process,

each monomial is assigned an identifying number.

- 2. The "new monomials" are shown in column 2 together with the identifying number of the "parent monomials."

- 3. Each monomial used in forming a reduced monomial is checked. No check mark is placed for

the monomial in group 2 if it is used as a don't care for reducing the monomials of group 1.

4. The successively generated "new monomials" are given in successive columns. Note that the "parent monomials" for each "new monomial" are contained in the column immediately preceding the new column.

Table XIV. Minimization of the Three-variable Function of Table XIII.

|       | _ , |              |     | - 7        |               |     |            |             |

|-------|-----|--------------|-----|------------|---------------|-----|------------|-------------|

| Group |     |              |     | Column 2   |               |     | Column 3   | <del></del> |

|       | l.  |              | ì   | (1,3,11)   |               |     |            |             |

|       | 2.  | 002 ✓        | 2.  | (1,5,6)    | X00 🗸         | 2 。 | (6,7,12) ~ | X2X         |

|       | 3.  | 020 V        | 3.  | (2,4,19)   | 0 <b>X</b> 2  |     |            |             |

|       | 4.  | 022 <b>∨</b> | 4.  | (2,7,20)   | <b>X</b> 02   |     |            |             |

| 1     | 5.  | 100✓         | 5.  | (3,4,12)   | 02 <b>X</b> 🗸 |     |            |             |

|       | 6.  | 200 ✓        | 6.  | (3,9,15)   | X20 ✓         |     |            |             |

|       | 7.  | 202 ✓        | 7.  | (4,17,21)  | x22✓          |     |            |             |

|       | 8.  | 211          | 8.  | (5,13,20)  | 10x           |     |            |             |

|       | 9.  | 220✓         | 9.  | (5,14,15)  | 1x0 🗸         |     |            |             |

|       | 10. | 221 <b>V</b> | 10. | (6,9,18)   | 2X0 🗸         |     |            |             |

|       |     |              | 11. | (9,10,21)  | 22 <b>x</b> ✓ |     |            |             |

|       |     |              | 12. | (10,12,16) | X21 🗸         |     |            |             |

|       | 11. | 010 🗸        | 13. | (11,14,18) | X10           |     |            |             |

|       | 12. | 021          | 14. | (15,16,17) | 12X           |     |            |             |

|       | 13. | 101          |     |            |               |     |            |             |

|       | 14. | 110 🗸        |     |            |               |     |            |             |

| 2     | 15. | 120 <b>✓</b> |     |            |               |     |            |             |

|       | 16. | 121 🗸        |     |            | İ             |     |            |             |

|       | 17. | 122 🗸        |     |            |               |     |            |             |

|       | 18. | 210 🗸        |     |            | ļ             |     |            |             |

|       | 19. | 012          |     |            |               |     |            |             |

| 3     | 20. | 102          |     |            |               |     |            |             |

|       | 21. | 222          |     |            |               |     |            |             |

<sup>\*</sup> also from (2,6,13) \*\* also from (5,11,14)

5. The unchecked monomials that remain after the process terminates are the desired prime implicants. They are, in this case:

6. Prime implicant tables for selection of appropriate prime implicants.

12X

Table XV. h-Type Prime Implicant Table.

| 10210 | - 11 0 0 | 11 1110 | - 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | , ±1111D ± | LCuirc   | Tubic.   |

|-------|----------|---------|-----------------------------------------|------------|----------|----------|

|       | 211      | 0X2     | X02                                     | 10X        | xx0      | x2x      |

| 000   |          |         |                                         |            | <b>/</b> |          |

| 002   |          | /       | /                                       |            |          |          |

| 020   |          |         |                                         |            | <b>/</b> | /        |

| 022   |          | /       |                                         |            |          | /        |

| 100   |          |         |                                         | <b>/</b>   | <b>/</b> |          |

| 200   |          |         |                                         |            | <b>/</b> |          |

| 202   |          |         | <b>/</b>                                |            |          |          |

| 211   | >        |         |                                         |            |          |          |

| 220   |          |         |                                         |            | <b>✓</b> | /        |

| 221   |          |         |                                         |            |          | <b>V</b> |

| Table | S VAT.   | darabe bi | тше тшрт. | cant Table |

|-------|----------|-----------|-----------|------------|

|       | 021      | 101       | X10       | 12X        |

| 010   |          |           | <b>✓</b>  |            |

| 021   | <b>/</b> |           |           |            |

| 101   |          | <b>/</b>  |           |            |

| 110   |          |           | <b>/</b>  |            |

| 120   |          |           | -         | <b>/</b>   |

| 121   |          |           |           | <b>✓</b>   |

| 122   |          |           |           | <b>/</b>   |

| 210   |          |           | <b>~</b>  |            |

Table XVI. g-type Prime Implicant Table.

The most economical function from Table XV is the combination of X2X, XXO, XO2, 211, and that from Table XVI is the combination of 12X, X1O, 101, 021 (all prime implicants in this case). The function can be written as

$f = 1 \cdot (y'' + z + yz'' + x'' y'z') + x'y'' + y'z + x'yz' + xy''z'$  which agrees with that obtained in Section C, page 36.

### V. TERNARY SWITCHING CIRCUITS AND STORAGE DEVICES

If the advantages of the ternary logic are to be realized, it is necessary to use a simple, inexpensive ternary element. Most of the electromagnetic and electronic switching elements are, however, two-valued devices. There is, at present, no device in common use that inherently has three stable states.

The nearest approximation to this requirement is the non-linear Hall-effect ternary logic element (4) and the thin magnetic film for storage in (17). A magnetic ternary device was developed by Anderson and Dietmeyer (1). But none of these devices are well-developed, and each is either expensive, or not practical for other reasons.

Ternary switching circuits could also be built up with devices of a basically binary type. Hallworth and Heath (2) have devised several circuits using p-n-p and n-p-n transistor pairs to fulfill the purpose. A set of tunnel-diode circuits for ternary logic have been devel-oped by the faculties of Engineering in Osaka University, Japan (3). The tunnel-diodes are fast but expensive, and always present the problem of synchronization. The circuits presented in this chapter may not be the best but they will do the job. More development effort is needed to make them more suitable.

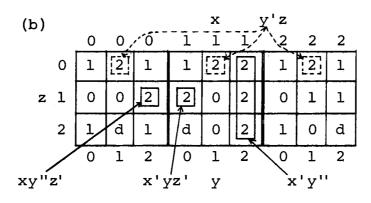

## A. Basic Gates

The basic gates of ternary logic together with the symbols that represent each gate are shown in Figures 7, 8, 9 and 10. The diode-transistor scheme will be employed as other ternary devices are not practically usable yet. The representations of logic levels by voltages are given below.

logic 0

$$V \ge + 2v$$

(typical value 2v)

logic 1  $-lv \le V \le + lv$  (" " 0v)

logic 2  $V \le - 2v$  ( " " -2v)

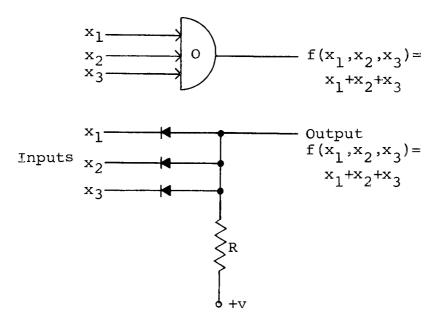

Note that the ternary Or-gate and And-gate (Figures 7 and 8) are the same as binary Or-gate and And-gate realizations, hence no explanation will be given here.

In Figure 9, if the input represents "0" (+2v), the base of  $T_2$  is near +2v.  $R_1$ ,  $R_2$ , and  $R_3$  are designed so that  $T_2$  is saturated, and  $T_3$  keeps the output proportionately as far below the emitter of  $T_3$  as point X is above it. This gives an output of approximately 0v, or the "1" state. If the input is "1" (0v), the base of  $T_2$  is near ground potential, and  $R_1$ ,  $R_2$  and  $R_3$  still keep  $T_2$  saturated. Thus the output is kept proportionately below the emitter of  $T_3$  by  $T_3$ . This gives an output of -2v, which represents the truth value "2". If the input is "2" (-2v),  $T_2$  is cut off.  $R_1$ ,  $R_2$  and  $R_6$

Figure 7. Or-gate

Figure 8. And-gate

Figure 9. Cycling-gate.

Figure 10. Inverter

together with the circuit of  $T_3$  now give an output of +2v, which is adequate for the truth value "0".

In Figure 10, if the input is positive (+2v),  $T_1$  acts as an amplifier and is saturated while  $T_2$  is cut off. The output is then determined by  $R_4$ ,  $R_7$  and  $R_8$  and the output is negative. If the input is at zero voltage, both transistors are cut off, and the output is approximately zero volts, because of the symmetry of the circuit. If the input is negative (-2v),  $T_2$  is saturated while  $T_1$  is cut off. The output is determined by  $R_1$ ,  $R_7$  and  $R_8$  and is positive.

## B. Memory Elements

The work-horse of the binary digital system is the bistable circuit or flip-flop. The ternary versions of such a circuit will be referred to as tristable circuit or ternary-flip-flop or simply TFF. Several circuits are proposed below. They are designed by making analogy with binary circuits.

A RaS TFF is shown in Figure 11.

Figure 11. R-S TFF composed of two inverters.

Table XVII defines the operation of R-S TFF.

Table XVII. Operation of R-S TFF

| R |     | S | Output |

|---|-----|---|--------|

| 0 | or  | 2 | 0      |

| 1 | and | 1 | 1      |

| 2 | or  | 0 | 2      |

|   |     |   |        |

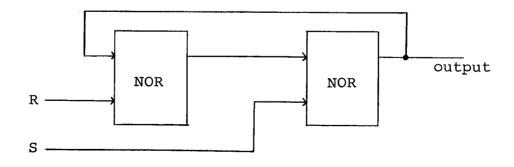

Note the similarity between this circuit and the binary R-S FF in Figure 12 which is composed of two NOR-gates.

Figure 12. R-S FF in binary system.

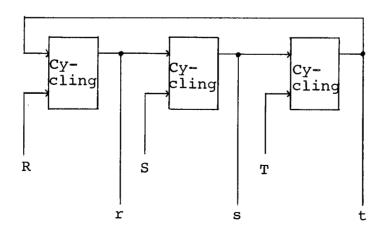

While the R-S TFF is not very useful in its present form, the R-S-T TFF shown in Figure 13 should be of great use. The circuit is composed of three Cycling-gates. A triggering voltage of positive polarity applied to R will produce the following logical outputs:

r : 1

s : 2

t: 0

If the triggering is applied to S, the outputs are

r : 0

s : 1

t: 2

If the triggering is applied to T, the outputs are

r : 2

s : 0

t:1

Figure 13. R-S-T TFF.

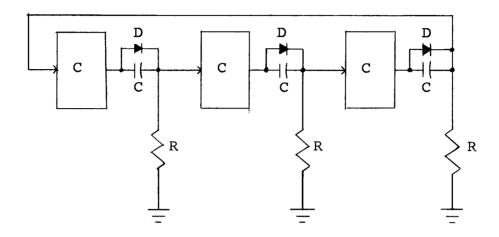

An astable TFF is shown in Figure 14.

Figure 14. Astable TFF.

A monostable TFF can be constructed by simply short-circuiting one of the coupling circuits in Figure 14.

## C. Ternary Memory

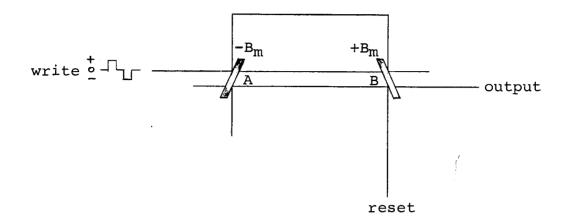

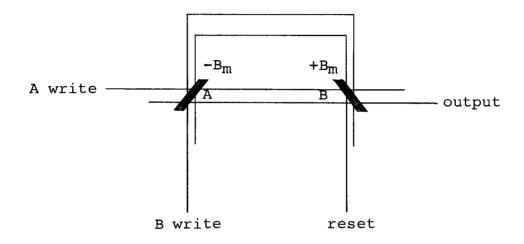

The greatest drawback of the ternary digital system is the unavailability of economical storage devices. Several authors have tried to develop a ternary storage element but all failed under the criteria of practical—ity, simplicity and economy. Figure 15 shows one method of accomplishing this task. It is composed of two two-state magnetic cores to provide one ternary digit of storage.

Figure 15. Ternary core switch.

The cores are wired in series as shown. Initially, one core is in  $+B_{\rm m}$  state while the second core is in the  $-B_m$  state. The input pulses to write the value "2" are of negative polarity, and thus can only switch core B. The input pulses to write the value "0" are of positive polarity and can only switch core A. The zero is represented by no pulse, and the core states are not changed in this case. The reset pulse which occurs subsequent to the write pulse is driven through both cores in such a way that it will return either of the cores back to its original state. An output pulse of positive or negative polarity or no pulse is obtained on the output winding (when the cores are reset) to indicate if a "0", "2", or "1" was previously written. The magnitude of the write and reset currents in both cores will have to be of sufficient amplitude to switch the cores.

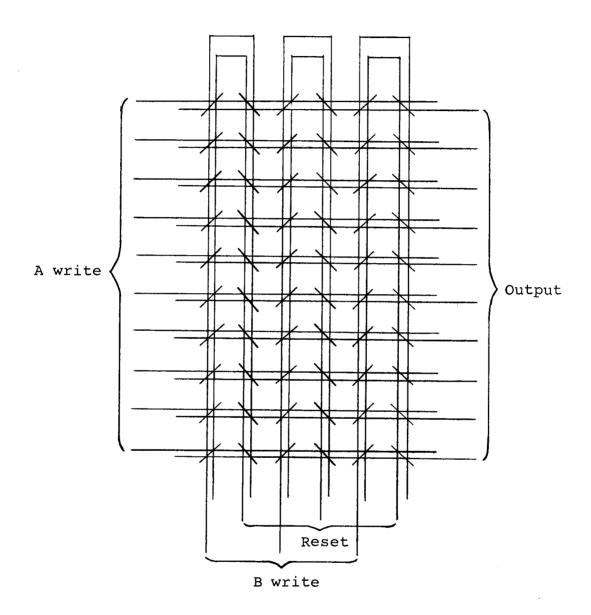

A storage unit of the "coincident current" type is shown in Figure 16. This circuit can be used in the matrix form shown in Figure 17. The A write pulse will be of positive or negative polarity according to the digit which is to be stored. The B write pulses are

Figure 16. Coincident current core storage unit.

always of positive polarity. All write current pulses have an amplitude of  $I_{\rm m}/2$ , thus only one chosen core will get the full switching current. The selection of any core in the matrix is effected by selecting a row and a column as in the case of binary coincident current memory.

Figure 17. Ternary core memory.

### VI. CONCLUSION

In this paper, a systematic method of designing a ternary digital system was described. The system of logic described is characterized by a rather close analogy to the systems of Boolean algebra which are normally employed in the cases where two values only are permitted. The method described here is not the only possible method, but it is one of the simplest and can be easily understood and applied by designers familiar with binary techniques.

Apart from the arithmetic computer applications, the technique provides a very practical method for the realization of special logical functions concerned with three-valued digital system. It is foreseeable that a completely ternary-based computer will find a useful place in a digital control system. The advancing microelectronic techniques may well lead to more economical ternary-based circuits where thin-magnetic film assemblies are integrated with thin-film semiconductor assemblies.

At present, however, binary systems are still preferred. Much work still needs to be done, in both theory and hardware, before ternary systems can be practically realized. Whether ternary systems ultimately will be widely used or not depends mainly on

the development of economical ternary switching elements and storage devices. The problems are both challenging and interesting. It is hoped that digital technology will see further advances in this area.

#### **BIBLIOGRAPHY**

- 1. Anderson, D. J. and D. L. Dietmeyer. A magnetic ternary device. IEEE Transactions on Electronic Computers EC-12:911-914. 1963.

- 2. Hallworth, R. P. and F. G. Heath. Semiconductor circuits for ternary logic. IEE Proceedings 109(C):219-225. 1962.

- 3. Hasegawa, T. et al. Tunnel-diode circuits for ternary logic. Electronics and Communications in Japan 47:88-95. 1964.

- 4. Hooi, C. F. and J. L. Weaver. Non-linear Hall-effect ternary logic element. Solid-State Electronics 7:311-321. 1964.

- 5. Lee, C. Y. and W. H. Chen. Several-valued combinational switching circuits. AIEE Transactions 75:278-283. 1956.

- 6. Lowenshuss, Oscar. Non-binary switching theory. IRE National Convention Record 6(4):305-317. 1958.

- 7. Merrill, Roy D. A tabular minimization procedure for ternary switching functions. IEEE Transactions on Electronic Computers EC-15:578-585. 1966.

- 8. Miller, Raymond E. Switching theory. Vol. 1. New York, John Wiley, 1966. 351p.

- 9. Morris, D. J. and W. Alexander. An introduction to the ternary code number system. Electronic Engineering 32:554-557. 1960.

- 10. Muehldorf, E. I. Multivalued switching algebras and their applications in digital systems.

National Electronics Conference, Proceedings 15:467-480. 1959.

- 11. Post, Emil L. Introduction to a general theory of elementary propositions. American Journal of Mathematics 43:163-185. 1921.

- 12. Pugh, A. Application of binary devices and Boolean algebra to the realization of 3-valued logic circuits. IEE Proceedings 114:335-338. 1967.

- 13. Salter, Forrest. A ternary memory element using a tunnel diode. IEEE Transactions on Electronic Computers EC-13:155-156. 1964.

- 14. Santos, J. and H. Arango. Base 3 vs base 2 synchronous arithmetic units. IEEE Transactions on Electronic Computers EC-13:608-609. 1964.

- 15. Santos, J. and H. Arango. On the analysis and synthesis of 3-valued digital systems. AFIPS Spring Joint Computer Conference, Proceedings 25:463-475. 1964.

- 16. Vacca, R. A three-valued system of logic and its applications to base three digital circuits. In: International Conference on Information Processing, Proceedings. Paris, UNESCO, 1959. p.407-414.

- 17. Yoeli, M. and G. Rosenfeld. Logical design of ternary switching circuits. IEEE Transactions on Electronic Computers EC-15:19-29. 1965.

### APPENDIX

Two more operations have been widely discussed in ternary switching theory. These additional operations will, in many instances, reduce the hardware cost, although at the same time they will complicate the algebraic manipulation. The definitions of these two operations are given below.

Definition A.1. J<sub>i</sub>-operation is defined as

$$J_{i}(x) = \begin{cases} 0 & \text{if } i = x \\ \\ 2 & \text{if } i \neq x \end{cases}$$

$$i,x \in \{0,1,2\}.$$

Definition A.2. Ki-operation is defined as

$$K_{i}(x) = \begin{cases} 0 & \text{if } i \neq x \\ \\ 2 & \text{if } i = x \end{cases}$$

$$i,x \in \{0,1,2\}.$$

Definitions A.1 and A.2 are summarized in Table XVIII.

|   |                    |                    | 1                  | 1 1                | <b>-</b>           |                    |

|---|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|

| х | J <sub>o</sub> (x) | J <sub>1</sub> (x) | J <sub>2</sub> (x) | К <sub>о</sub> (х) | κ <sub>1</sub> (x) | к <sub>2</sub> (х) |

| 0 | 0                  | 2                  | 2                  | 2                  | 0                  | 0                  |

| 1 | 2                  | 0                  | 2                  | 0                  | 2                  | 0                  |

| 2 | 2                  | 2                  | 0                  | 0                  | 0                  | 2                  |

Table XVIII.  $J_i$ -,  $K_i$ -operation

Note that

$$K_{i}(x) = \overline{J_{i}(x)}$$

and  $J_{i}(x) = \overline{K_{i}(x)}$

The  $J_i$ -operation and  $K_i$ -operation can be expressed in terms of two fundamental operations, And and Cycling.

$$J_{O}(x) = (x' \cdot x'')''$$

$$J_{1}(x) = (x \cdot x')''$$

$$J_{2}(x) = (x'' \cdot x)''$$

$$K_{O}(x) = (x \cdot x')'' \cdot (x \cdot x'')''$$

$$K_{1}(x) = (x' \cdot x'')'' \cdot (x \cdot x'')''$$

$$K_{2}(x) = (x' \cdot x'')'' \cdot (x \cdot x')'' \cdot .$$

The relationships between  $J_i$ -operation and  $K_i$ -operation are:

$$J_{O}(x) = K_{1}(x) + K_{2}(x)$$

$$J_{1}(x) = K_{O}(x) + K_{2}(x)$$

$$J_{2}(x) = K_{O}(x) + K_{1}(x)$$

$$K_{O}(x) = J_{1}(x) \cdot J_{2}(x)$$

$$K_{1}(x) = J_{O}(x) \cdot J_{2}(x)$$

$$K_{2}(x) = J_{O}(x) \cdot J_{1}(x)$$

Also the following relations are useful in reducing algebraic expressions.

$$K_{O}(x) + K_{1}(x) + K_{2}(x) = 2$$

$$J_{O}(x) \cdot J_{1}(x) \cdot J_{2}(x) = 0$$

$$K_{i}(x) \cdot K_{j}(x) = \begin{cases} K_{i}(x) & \text{if } i = j \\ 0 & \text{if } i \neq j \end{cases}$$

$$J_{i}(x) + J_{j}(x) = \begin{cases} J_{i}(x) & \text{if } i = j \\ 2 & \text{if } i \neq j \end{cases}$$

It is well-known that binary functions can be expanded in disjunctive normal form and conjunctive normal form by applying the expansion theorems (due to Shannon):

$$f(x_1, x_2, \dots, x_n) = x_1 f(1, x_2, \dots, x_n) + \overline{x}_1 f(0, x_2, \dots, x_n)$$

or,

$$f(x_1, x_2, \dots, x_n) = [x_1 + f(0, x_2, \dots, x_n)]$$

$$[\overline{x}_1 + f(1, x_2, \dots, x_n)]$$

Not surprisingly, there exists a similar pair of expansion theorems in the ternary system:

$$f(x_{1},x_{2},...,x_{n}) = J_{o}(x_{1})f(0,x_{2},...,x_{n}) + J_{1}(x_{1})f(1,x_{2},...,x_{n}) + J_{2}(x_{1})f(2,x_{2},...,x_{n})$$

or,

$$\begin{split} f(x_{1}, x_{2}, \cdots, x_{n}) &= \left( K_{0}(x_{1}) + f(0, x_{2}, \cdots, x_{n}) \right) \\ & \left( K_{1}(x_{1}) + f(1, x_{2}, \cdots, x_{n}) \right) \\ & \left( K_{2}(x_{1}) + f(2, x_{2}, \cdots, x_{n}) \right) \end{split}$$

If the cost of a  $J_i$ -gate or a  $K_i$ -gate is the same as that of an And-gate or an Or-gate, then the use of  $J_i$ -operation and  $K_i$ -operation will tend to reduce the cost of a given function.

Example: Reduce the following equation (a) without  $J_i$ -,  $K_i$ -operation.

$$f = 1 \cdot (x+yz+yz''+x'') + y'z'+yz'+y''z+y''z'' + y''z'$$

$$(a) \quad g = y'z'+yz'+y''z+y''z''+y''z'$$

$$= z'(y+y')+y''(z+z'+z'')$$

$$= z'(y+y')+y''$$

$$1 \cdot h = 1 \cdot (x+yz+yz''+x'') \quad don't \ care \ (from \ g)$$

$$= 1 \cdot ((x+yz+yz''+x'')+y'z')$$

$$= 1 \cdot (x+x''+y(z+z'+z''))$$

$$= 1 \cdot (x+x''+y)$$

$$f = 1 \cdot h+g = 1 \cdot (x+x''+y)+z'(y+y')+y''$$

$$cost = 14$$

(b)

$$g = z'(y+y')+y''$$

from part (a)

$= z'J_2(y)+y''$

$1 \cdot h = 1 \cdot (x+x''+y)$  from part (a)

$= 1 \cdot (J_1(x)+y)$

$f = 1 \cdot h+g = 1 \cdot (J_1(x)+y) + z'J_2(y)+y''$

$= cost = 11$ . A saving of 3.

Example: Simplify the following expression as much as possible.

$$f = xx' + xx'' + x'x'' + x''$$

(a) Without

$$J_i$$

-,  $K_i$ -operation

$$f = xx'+xx''+x'x''+x''$$

$$= xx'+x'' \qquad cost = 5$$

(b) With

$$J_i$$

-,  $K_i$ -operation

$f = xx' + xx'' + x'x'' + x''$

$= x(x' + x'') + x''(x' + x'')$

$= (x' + x'')(x + x'')$

$= J_o(x) \cdot J_1(x)$

$= K_2(x)$  cost = 2

There are many operations in ternary algebra which are analogous to the sheffer stroke operation in binary algebra. One of these is the following:

Table XIX. Another Binary Operator for the Ternary System.

(Analogous to the binary "stroke" function)

| х | У  | х |

|---|----|---|

| 0 | 0  | 1 |

| 0 | ĺц | 1 |

| 0 | 2  | 1 |

| 1 | 0  | 1 |

| 1 | 1  | 2 |

| 1 | 2  | 2 |

| 2 | 0  | 1 |

| 2 | 1  | 2 |

| 2 | 2  | 0 |

|   |    |   |

It can be seen that  $x' = x \mid x$

$$x \cdot y = (x|y)$$

".

The operation "|" is therefore logically complete. The simplification achieved, however, would only be one of notation, whereas the actual physical circuits would be more complicated, both because of the lesser flexibility of the operation and because of the fact that a physical circuit realizing the operation would be rather complicated in itself.