#### AN ABSTRACT OF THE THESIS OF

Yunteng Huang for the degree of <u>Doctor of Philosophy</u> in <u>Electrical & Computer</u> Engineering presented on <u>March 6, 1997.</u>

Title: <u>Design Techniques of High-Performance Switched-Capacitor Circuits in the Presence of Component Imperfections.</u>

## Redacted for Privacy

| Abstract approved: | _ |                | <br> |  |

|--------------------|---|----------------|------|--|

| 11                 |   | Gabor C. Temes |      |  |

This thesis describes design techniques for high-performance switched-capacitor (SC) circuits, primarily for high-linearity low-noise SC circuits in the presence of component imperfections, such as nonlinear op-amp voltage transfer characteristics, capacitor nonlinearities as well as the finite op-amp dc gain and op-amp offset and noise. Various correlated-double-sampling (CDS) schemes are discussed, and some novel predictive CDS schemes are proposed. Analysis, simulation and experimental results show that these schemes are very effective for reducing the effects of op-amp imperfections, resulting in lower signal distortion and reduced low-frequency noise and dc offset. The effect of capacitor nonlinearity in an SC circuits is analyzed in detail, and techniques for linearization are discussed. Applying these techniques, MOSFET capacitors can be used in high-performance digital-process-compatible SC circuit designs.

To verify the effectiveness of the proposed techniques, three prototype chips containing a 3-V all-MOSFET delta-sigma modulator, predictive gain- and offset-compensated track-and-hold stages, and SC amplifiers with various CDS techniques, were designed and fabricated in 1.2  $\mu$ m CMOS technology. The measured results show that these circuit techniques are highly effective in high-performance SC circuit designs.

©Copyright by Yunteng Huang March 6, 1997 All Rights Reserved

# Design Techniques of High-Performance Switched-Capacitor Circuits in the Presence of Component Imperfections

by

Yunteng Huang

A THESIS

submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Completed March 6, 1997 Commencement June 1997 Doctor of Philosophy thesis of Yunteng Huang presented on March 6, 1997

APPROVED: Redacted for Privacy

Major Professor, representing Electrical & Computer Engineering

Redacted for Privacy

Chair of Department of Electrical & Computer Engineering

## Redacted for Privacy

Dean of Graduate School

I understand that my thesis will become part of the permanent collection of Oregon State University libraries. My signature below authorizes release of my thesis to any reader upon request.

## Redacted for Privacy

#### **ACKNOWLEDGEMENTS**

I wish to express my sincere appreciation to my research advisor Prof. Gabor C. Temes. I have been very honored and privileged to have worked under his supervision. I am deeply indebted to him for his guidance and support and for providing an excellent environment for research. I have benefited greatly from his deep intuition for circuits and systems, from his emphasis on clarity in presentation, and from being exposed to his supremely high technical and professional standards.

I would like to thank Prof. Richard Schreier for many inspiring discussions, for providing laboratory facilities, and for teaching a great class on oversampling data converters from which I learned first about delta-sigma modulator design. Thanks also to Prof. Dave J. Allstot for making critical suggestions and comments during my prototype chip design reviews and for useful discussions during the research. I would especially like to thank Prof. Shih-Lien Lu for essential help with the chip implementation and fabrication. Thanks to Prof. Jack Kenney, Rita Wells and other ECE department faculty and staff members for their support throughout my time here.

I also want to thank Prof. Timothy Budd of the Computer Science Department for taking time out of his busy schedule to serve on my graduate committee.

I am very privileged to have worked with Paul F. Ferguson, Jr. I appreciate his advice and encouragement and many enlightening technical exchanges over the years. Thanks also to my colleague Hirokazu Yoshizawa, who performed earlier work on MOSFET capacitors, for sharing research results and new ideas, and for essential technical discussions.

I would also like to thank Jorge Grilo, Danny Shamlou and Guangming Yin at Rockwell Semiconductor Systems Corp. for two fruitful summer internships.

Special thanks to my chinese friends Yaohua Yang, Yuming Cao, Ting Fang, Stephanie Liu, Bo Zhang and Haiqin Lin, with whom I shared many great times in Corvallis, for their constant support and encouragement in all aspects of life and study. I am grateful to my cousin Wenhao Liu and his wife Limei Yan for their unselfish help during my first year of study in this country.

I would like to thank the people in our research group: Bo Wang, Tao Sun, Xiangping Qiu, Andreas Wiesbauer and Jesper Steensgaard for their friendship and useful technical discussions during the weekly meetings.

I would also like to thank Luis Hernandez for making important suggestions on lab testing, and for spending time taking the waveform pictures.

Thanks to the National Science Foundation (NSF) Center for the Design of Analog/Digital ICs (CDADIC) for their support, and to Orbit Semiconductor, Inc. for their generous support in chip fabrication.

Finally, I am grateful to the people who made it all possible, my wife Xiaofang, my parents and the rest of my family, for their love, patience and belief in me throughout my life.

### TABLE OF CONTENTS

| Page Page                                                                               | : |

|-----------------------------------------------------------------------------------------|---|

| Chapter 1. Introduction                                                                 |   |

| 1.1 Motivation                                                                          | 1 |

| 1.2 Thesis Structure                                                                    | 5 |

| Chapter 2. Correlated Double Sampling: Background                                       |   |

| 2.1 Introduction                                                                        | 7 |

| 2.2 The Basic Principle of CDS                                                          | 8 |

| 2.3 Offset-Compensated SC Circuits                                                      | 0 |

| 2.4 Gain- and Offset-Compensated SC Circuits1                                           | 2 |

| 2.5 Reducing Harmonic Distortion Using CDS Schemes                                      | 5 |

| 2.6 Conclusions1                                                                        | 9 |

| Chapter 3. Predictive Correlated Double Sampling                                        |   |

| 3.1 Gain- and Offset-Compensated Track-and-Hold Stages                                  | 0 |

| 3.2 Predictive Gain- and Offset-Compensated SC Amplifiers3                              | 8 |

| 3.3 Predictive Gain- and Offset-Compensated Integrators                                 | 3 |

| 3.4 Reduced Nonlinear Harmonic Distortion in Predictive CDS Circuits4                   | 4 |

| 3.5 Conclusions5                                                                        | 1 |

| Chapter 4. Design of High-Linearity SC Circuits without Using High-Linearity Capacitors |   |

| 4.1 The Effect of Capacitor Nonlinearity in SC Circuits                                 | 2 |

## **TABLE OF CONTENTS (Continued.)**

<u>Page</u>

| 4.2 Reducing the Capacitor Nonlinearity Using the Series Capacitor Branch55  |

|------------------------------------------------------------------------------|

| 4.3 Reducing Capacitor Nonlinearity Using Parallel Compensation58            |

| 4.4 Reduced Capacitor Nonlinearity Effect in Fully-Differential Structures59 |

| 4.5 MOSFET Capacitors60                                                      |

| 4.6 SC Circuits Using MOSFET Capacitors63                                    |

| 4.7 Conclusions72                                                            |

| Chapter 5. Thermal Noise Calculation in Switched-Capacitor Circuits          |

| 5.1 kT/C Noise in CDS Circuits74                                             |

| 5.2 Op-amp Noise in SC Circuits82                                            |

| 5.3 Other Noise Sources82                                                    |

| Chapter 6. A 3-V All-MOSFET Delta-Sigma Modulator                            |

| 6.1 Design Motivation and Design Goals84                                     |

| 6.2 Delta-Sigma Modulation: Background85                                     |

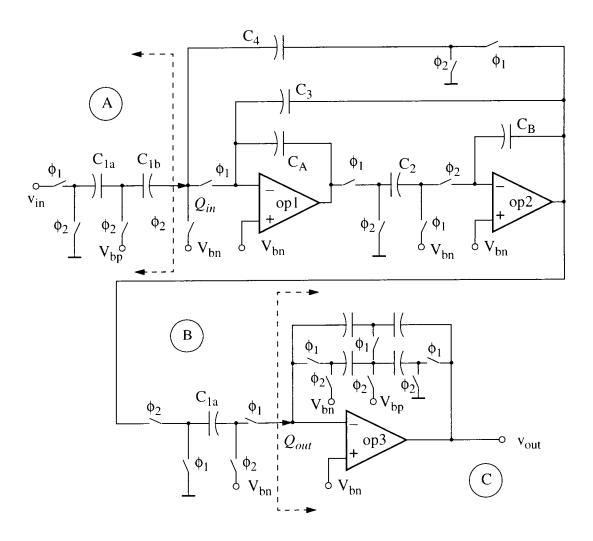

| 6.3 Modulator Architecture91                                                 |

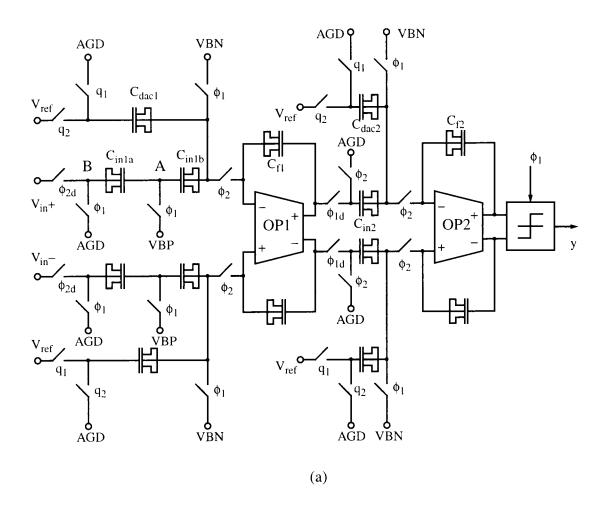

| 6.4 Circuit Implementation92                                                 |

| 6.5 Experimental Results                                                     |

| 6.6 Conclusions112                                                           |

|                                                                              |

Chapter 7. Experimental Results on the Predictive Gain- and Offset-Compensated Track-and-Hold Stage Prototype Chip

## **TABLE OF CONTENTS (Continued.)**

|                                                                                                            | <u>Page</u> |

|------------------------------------------------------------------------------------------------------------|-------------|

| 7.1 Motivation and Design Goal                                                                             | 115         |

| 7.2 Prototype Chip Structure                                                                               | 116         |

| 7.3 Circuit Implementation                                                                                 | 116         |

| 7.4 Experimental Results                                                                                   | 121         |

| 7.5 Conclusions                                                                                            | 130         |

| Chapter 8. Experimental Results On Reduced Harmonic Distortion in Circuits with Correlated Double Sampling |             |

| 8.1 Prototype Chip Description                                                                             | 131         |

| 8.2 Experimental Results                                                                                   | 136         |

| 8.3 Conclusions                                                                                            | 139         |

| Chapter 9. Summary and Future Work                                                                         |             |

| 9.1 Summary                                                                                                | 147         |

| 9.2 Future Work                                                                                            | 148         |

| Bibliography                                                                                               | 149         |

| APPENDIX: Digital Data Acquisition                                                                         | 154         |

## LIST OF FIGURES

| <u>Figure</u> |                                                                                                                                  | <u>Page</u> |

|---------------|----------------------------------------------------------------------------------------------------------------------------------|-------------|

| 2.1:          | A simple offset-compensated comparator                                                                                           | 8           |

| 2.2:          | The magnitude response of $H_n$                                                                                                  | 9           |

| 2.3:          | Uncompensated SC voltage amplifier                                                                                               | 10          |

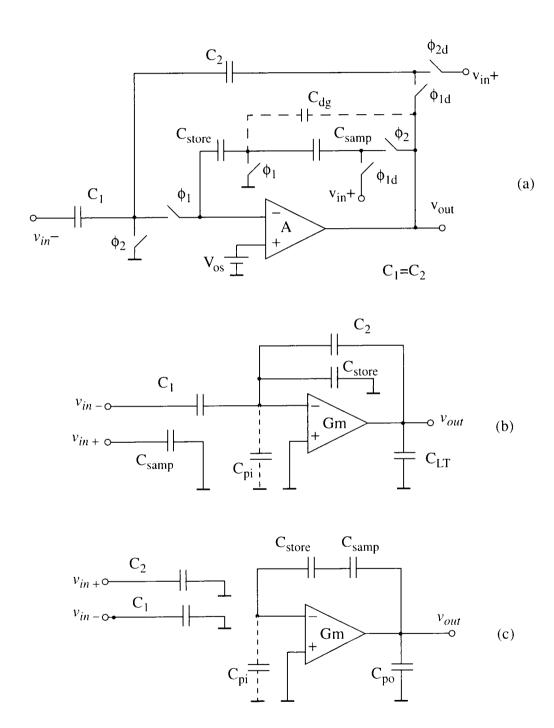

| 2.4:          | <ul><li>a. Offset-compensated SC amplifier; b. offset-compensated S/H;</li><li>c: output waveform the two circuits</li></ul>     | 11          |

| 2.5:          | <ul><li>a. An offset- and finite-gain-compensated SC amplifier;</li><li>b. clock and signal waveforms</li></ul>                  | 13          |

| 2.6:          | Gain- and offset-compensated SC integrator                                                                                       | 14          |

| 2.7:          | A closed-loop op-amp                                                                                                             | 15          |

| 2.8:          | Charge transfer in SC circuit                                                                                                    | 16          |

| 2.9:          | a: op-amp nonlinear transfer characteristics; b: op-amp gain vs. op-amp output                                                   | 17          |

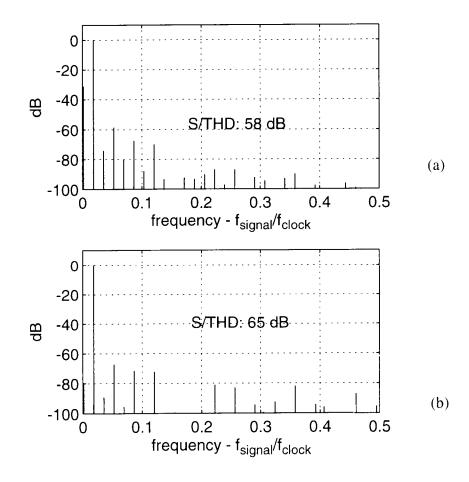

| 2.10          | : FFT spectrum of a: the uncompensated SC amplifier of Figure 2.3;<br>b: gain- and offset-compensated SC amplifier of Figure 2.5 | 18          |

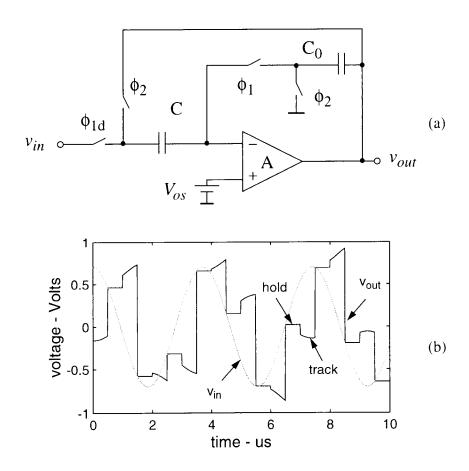

| 3.1:          | Gain- and offset-compensated track-and-hold stage. a: circuit diagram; b: input and output waveforms. $(C_0 / C = 4)$            | 21          |

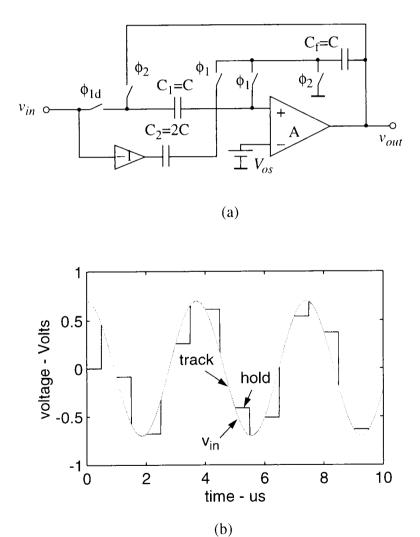

| 3.2:          | Predictive gain- and offset-compensated T/H. a: the circuit configuration; b: the input and output signal waveforms              | 23          |

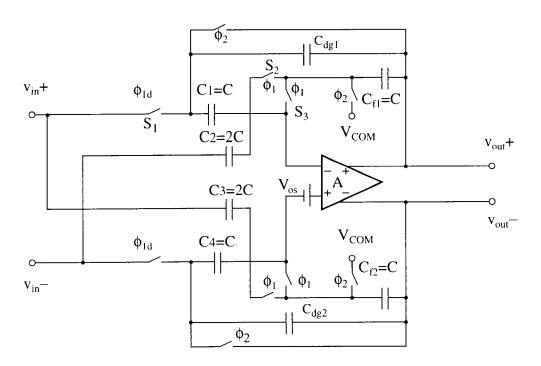

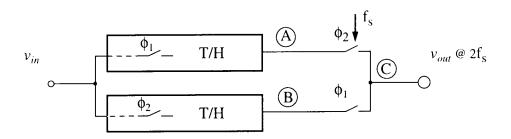

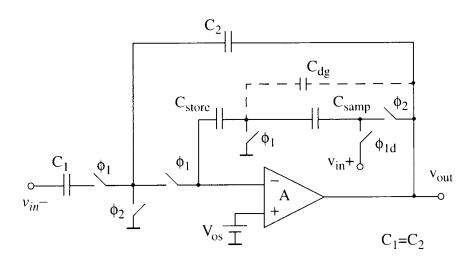

| 3.3:          | Fully-differential track-and-hold circuit                                                                                        | 25          |

| 3.4:          | S/H stage using two T/H blocks                                                                                                   | 26          |

| 3 5.          | Fully-differential track-and-hold circuit with improved switching scheme                                                         | 26          |

| <u>Figure</u> | <u>Page</u>                                                                                                                                                                                                                                            |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.6:          | Op-amp capacitive load for the circuit in Figure 3.5. a: during tracking; b: during holding                                                                                                                                                            |

| 3.7:          | A predictive gain- and offset-compensated T/H using an error storage capacitor. a: the basic circuit; b: circuit configuration during tracking; c: circuit configuration during holding                                                                |

| 3.8:          | An alternative predictive GOC T/H31                                                                                                                                                                                                                    |

| 3.9:          | High-speed T/H with a self-settling phase. a: the circuit; b: the clock signals; c: circuit configuration during self-settling interval (f <sub>3</sub> is low)                                                                                        |

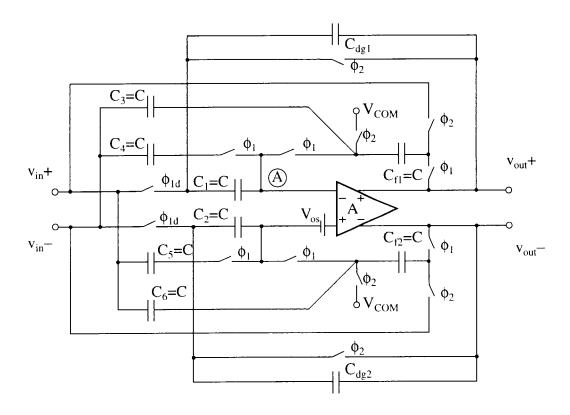

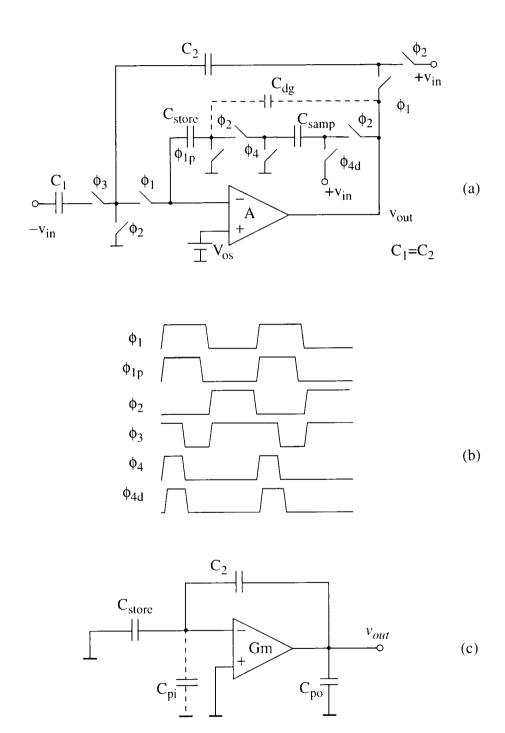

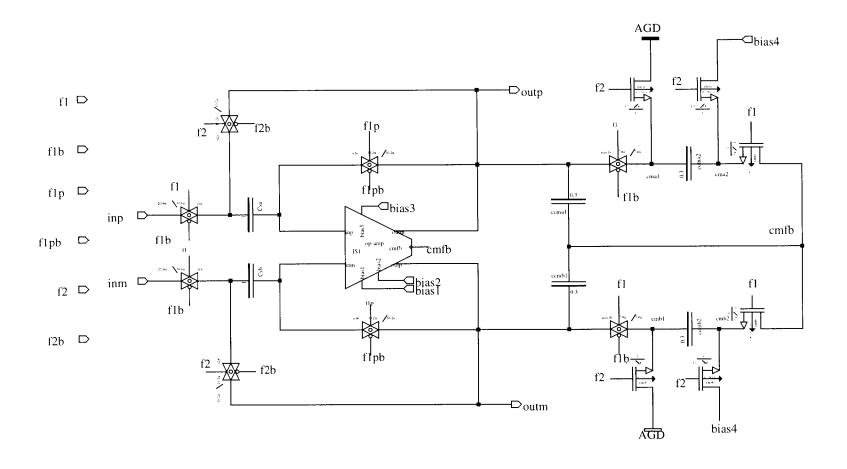

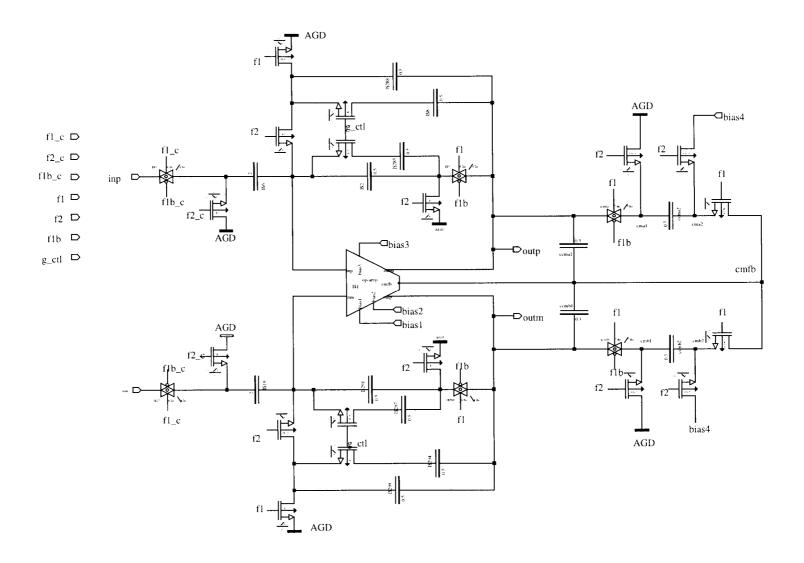

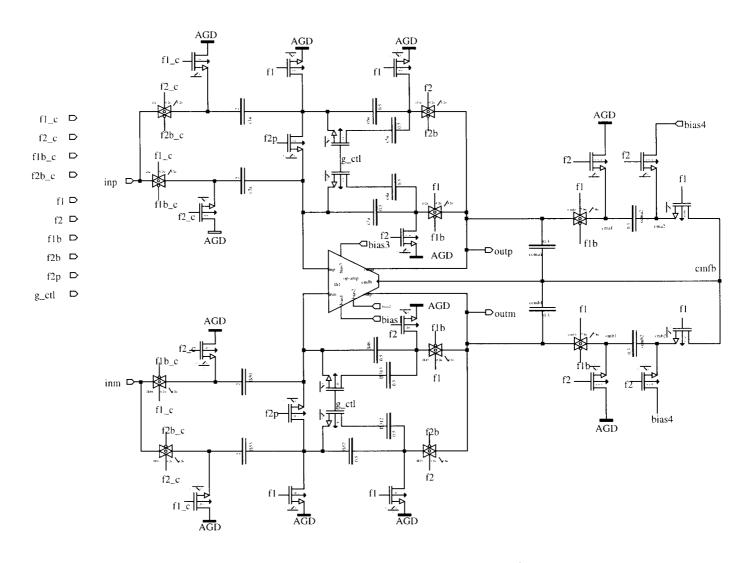

| 3.10:         | Fully differential realization of the improved gain- and offset-<br>compensated THA                                                                                                                                                                    |

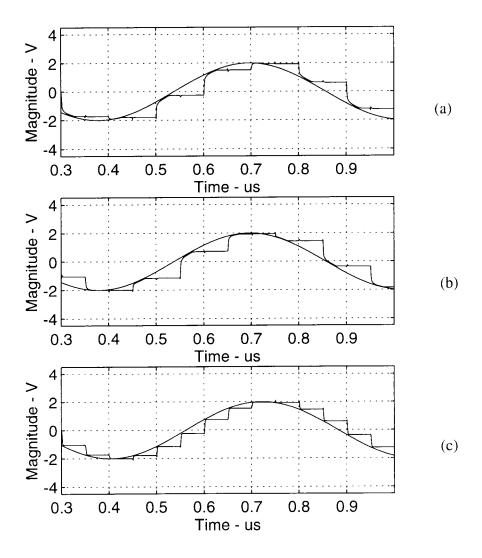

| 3.11:         | HSPICE simulation of the "ping-pong" structure. (a) T/H A output and the input signal; (b) T/H B output and the input signal; (c) the "ping-pong" output and the input signal                                                                          |

| 3.12:         | Signal spectra: (a) T/H A output; (b) T/H B output; (c) "ping-pong" output 35                                                                                                                                                                          |

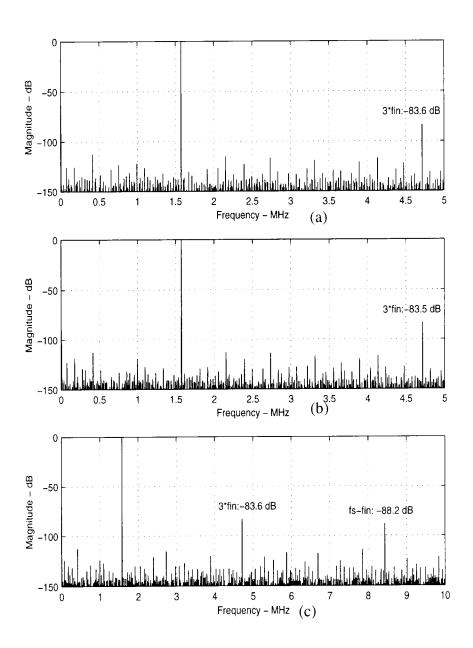

| 3.13:         | The Larson-Temes wideband GOC SC amplifier. a: the circuit; b: the input and output signal waveforms                                                                                                                                                   |

| 3.14:         | Nagaraj wideband OGC SC amplifier39                                                                                                                                                                                                                    |

| 3.15:         | a: Improved predictive SC amplifiers. b: simplified circuit without the disconnecting switch                                                                                                                                                           |

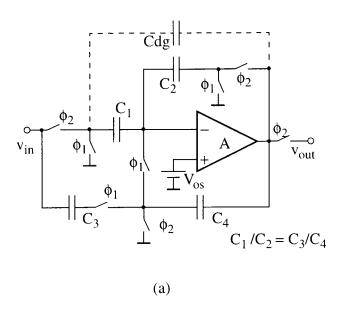

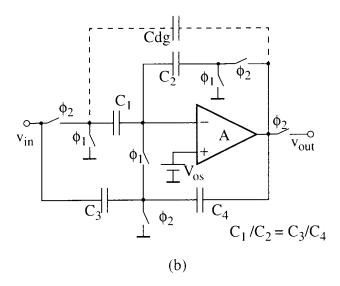

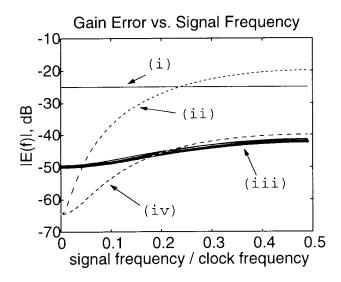

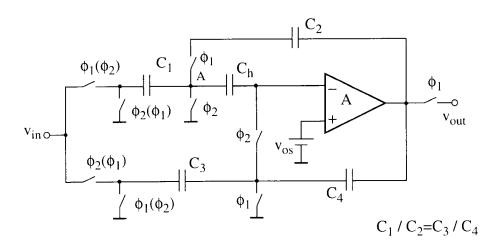

| 3.16:         | Gain error of SC amplifiers with $A_{closed-loop} = 5$ , $A_{opamp} = 40$ dB;<br>(i): uncompensated; (ii) narrowband compensated Figure 2.5;<br>(iii) wideband compensated (Figure 3.13, Figure 3.14 and Figure 3.15b;<br>(iv) circuit of Figure 3.15a |

| 3 17.         | Predictive gain- and offset-compensated integrator                                                                                                                                                                                                     |

| <u>Figure</u> | <u>Pa</u>                                                                                                                                                                                                             | <u>ige</u> |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

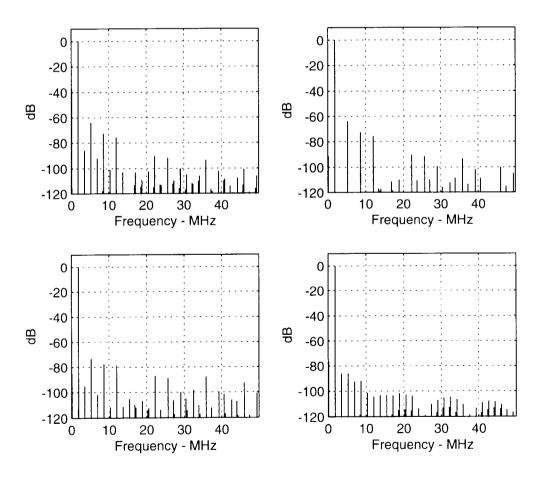

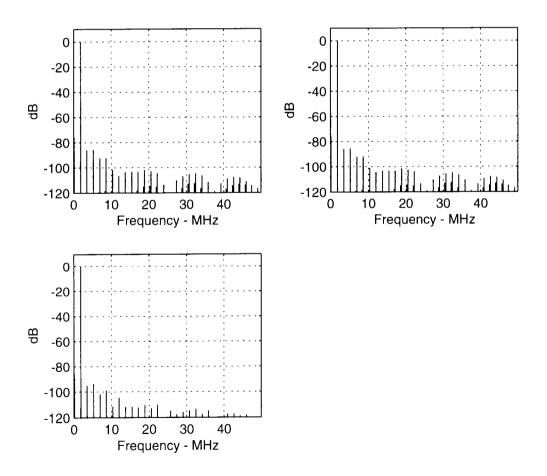

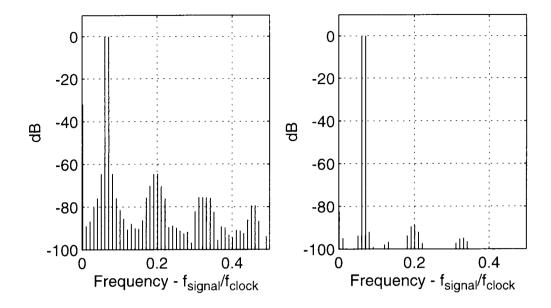

| 3.18:         | Simulated SC amplifier output spectra. a: uncompensated (Figure 2.3); b: offset-compensated (Figure 2.4); c: narrow-band compensated (Figure 2.5); d: wideband compensated (Figure 3.13)                              | 48         |

| 3.19:         | Simulated SC amplifier output spectrum. a: wideband compensated circuit using an offset storage capacitor (Figure 3.14); b: proposed novel SC amplifier (Figure 3.15b); c: proposed novel SC amplifier (Figure 3.15a) | 49         |

| 3.20:         | Output spectra with a two-tone input. a: the uncompensated SC amplifier; b: wideband GOC SC amplifier in Figure 3.15a                                                                                                 | 50         |

| 4.1:          | An SC biquad                                                                                                                                                                                                          | 53         |

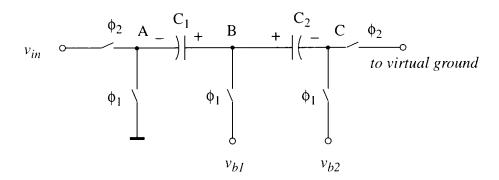

| 4.2:          | Switched-capacitor inter-stage signal coupling                                                                                                                                                                        | 54         |

| 4.3:          | A series SC branch                                                                                                                                                                                                    | 56         |

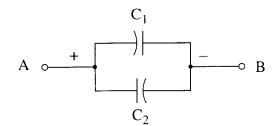

| 4.4:          | A parallel capacitor branch                                                                                                                                                                                           | 58         |

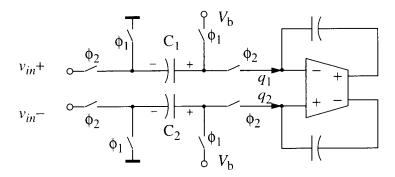

| 4.5:          | A fully-differential SC integrator                                                                                                                                                                                    | 59         |

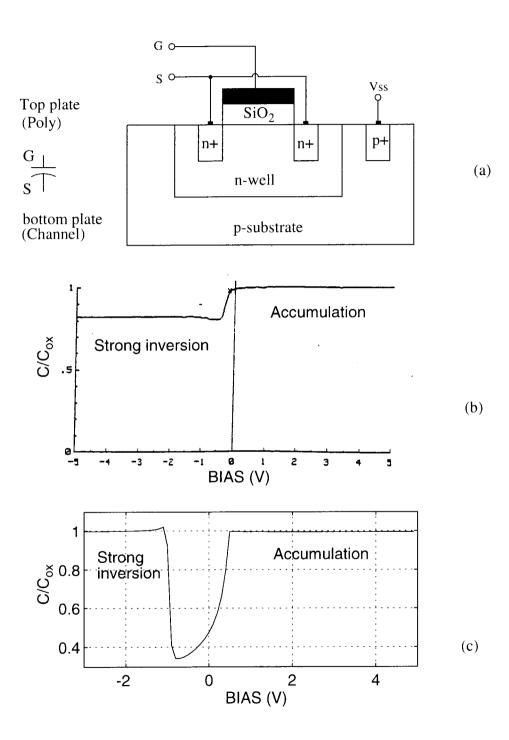

| 4.6:          | A MOSFET capacitor in n-well process. a: cross-section of the physical structure; b: measured high-frequency <i>c-v</i> curve. c: simulated low-frequency <i>c-v</i> curve                                            | . 62       |

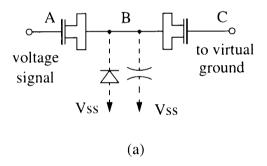

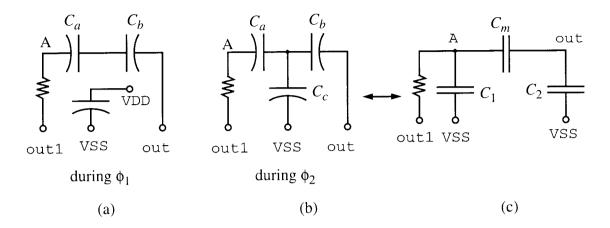

| 4.7:          | Series MOSFET capacitor branch. a. bottom-to-bottom connection; b. top-to-top connection                                                                                                                              | . 64       |

| 4.8:          | A gain- and offset-compensated T/H using MOSFET capacitors                                                                                                                                                            | . 65       |

| 4.9:          | Predictive gain- and offset-compensated T/H stage using MOSFET capacitors                                                                                                                                             | . 66       |

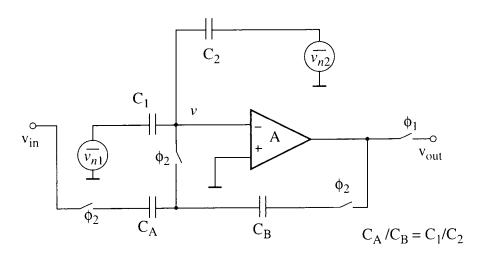

| 4.10:         | Predictive gain- and offset-compensated SC amplifier using MOSFET                                                                                                                                                     | . 67       |

| <u>Figure</u>                                                                                        | <u>Page</u> |

|------------------------------------------------------------------------------------------------------|-------------|

| 4.11: The basic MOSFET parallel compensation branch                                                  | 68          |

| 4.12: A third-order low-pass filter using MOSFET capacitors                                          | 70          |

| 4.13: An extra gain- and offset-compensated gain stage for linearizing the integrator output voltage | 71          |

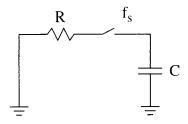

| 5.1: Periodically sampled capacitor                                                                  | 75          |

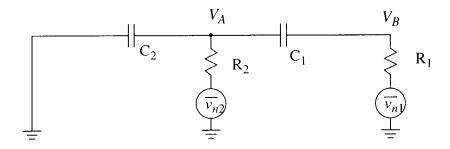

| 5.2: Thermal noise calculation model for a series capacitor branch with a switch at the center node  | 76          |

| 5.3: kT/C noise calculation model for the wide-band compensated SC amplifier of Figure 3.13          | 79          |

| 5.4: kT/C noise calculation for circuits with a storage capacitor                                    | 80          |

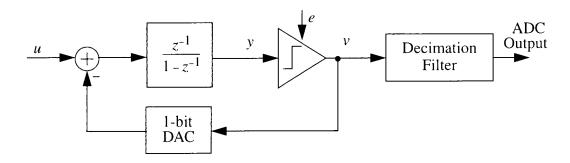

| 6.1: MOD1: A first-order delta-sigma ADC                                                             | 86          |

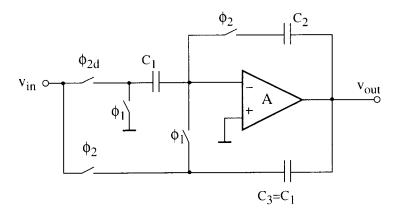

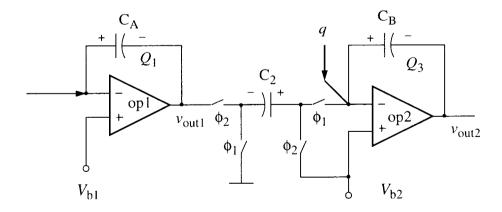

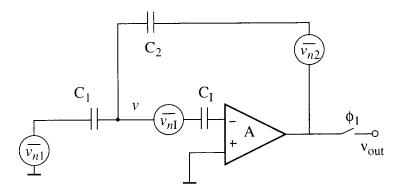

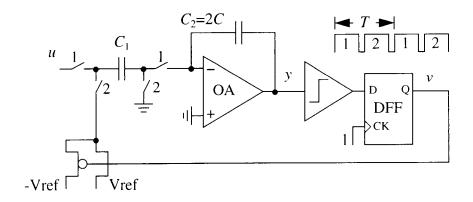

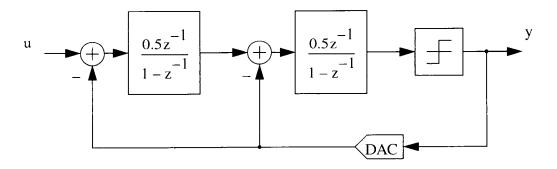

| 6.2: A switched-capacitor implementation of MOD1                                                     | 88          |

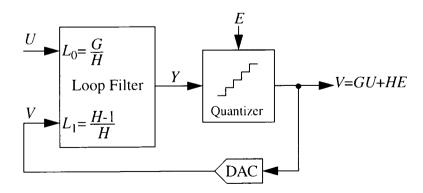

| 6.3: A general model of a discrete-time single-quantizer delta-sigma modulato                        | or89        |

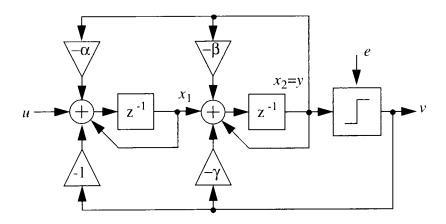

| 6.4: A general second-order delta-sigma modulator                                                    | 90          |

| 6.5: The architecture of the 2nd-order modulator                                                     | 91          |

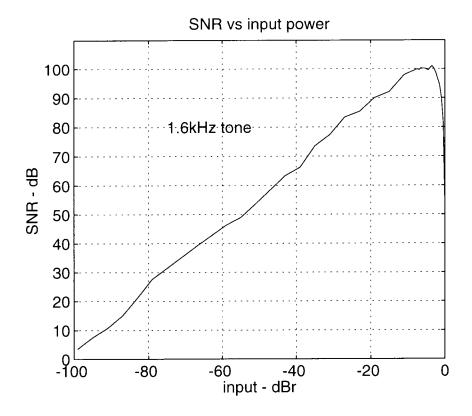

| 6.6: Simulated SNR vs. input signal amplitude                                                        | 92          |

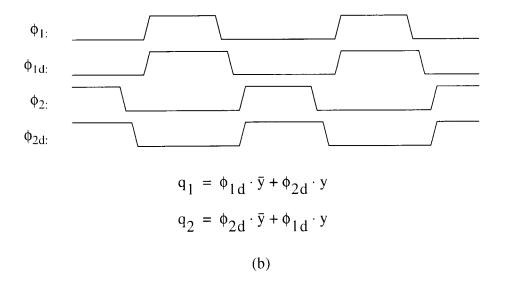

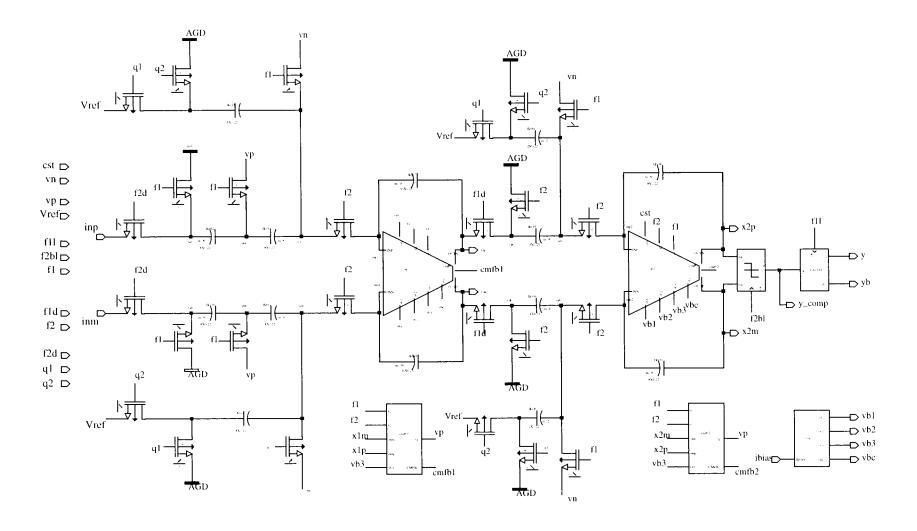

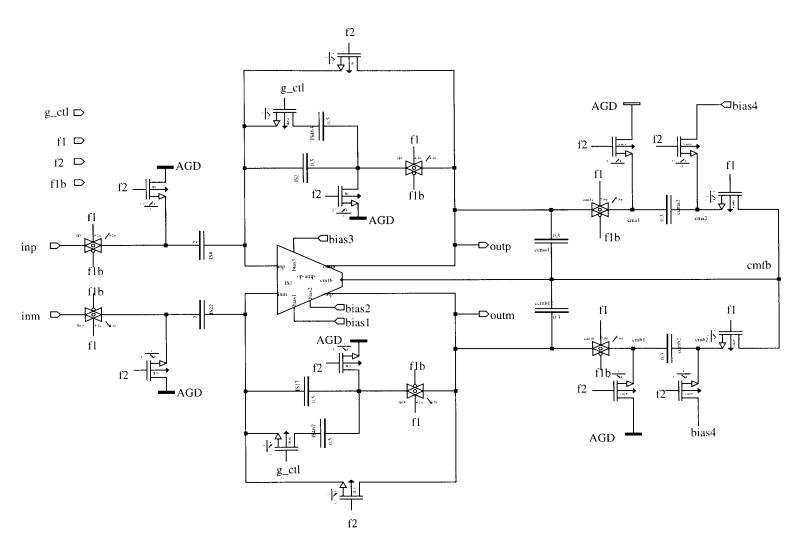

| 6.7: The second-order delta-sigma modulator: (a) circuit diagram; (b) clock signals                  | 94          |

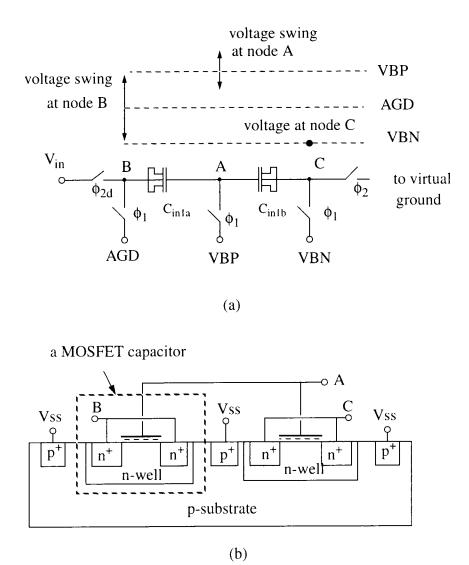

| 6.8: The linearized branch: (a) voltage swing at each node; (b) physical realization                 | 95          |

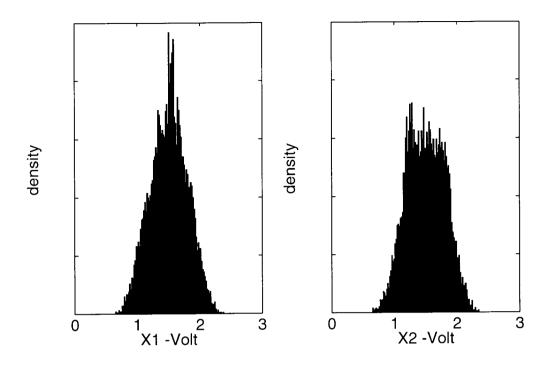

| 6.9: Histogram of integrator output. (a) first integrator; (b) second integrator                     | 98          |

| <u>Figure</u>                                                                                                                                        | <u>Page</u> |

|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

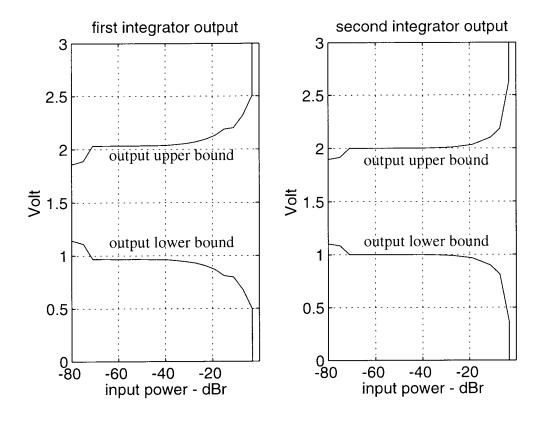

| 6.10: Maximum integrator output swing range vs. input power                                                                                          | 99          |

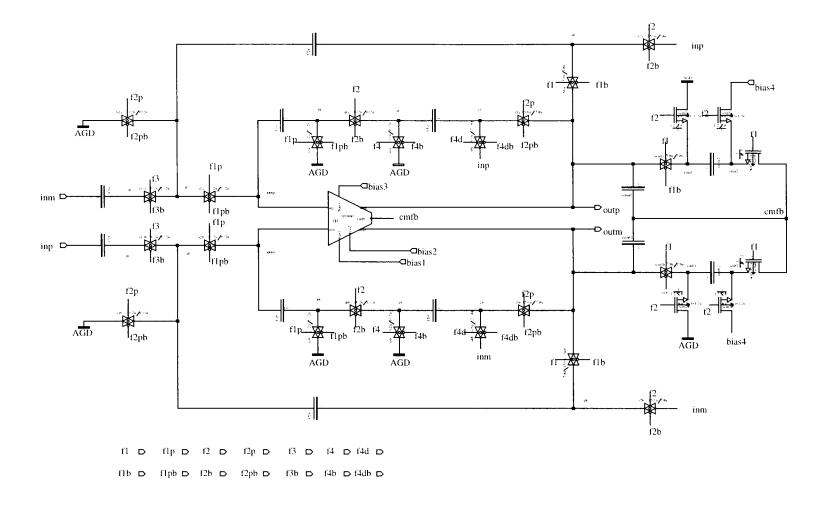

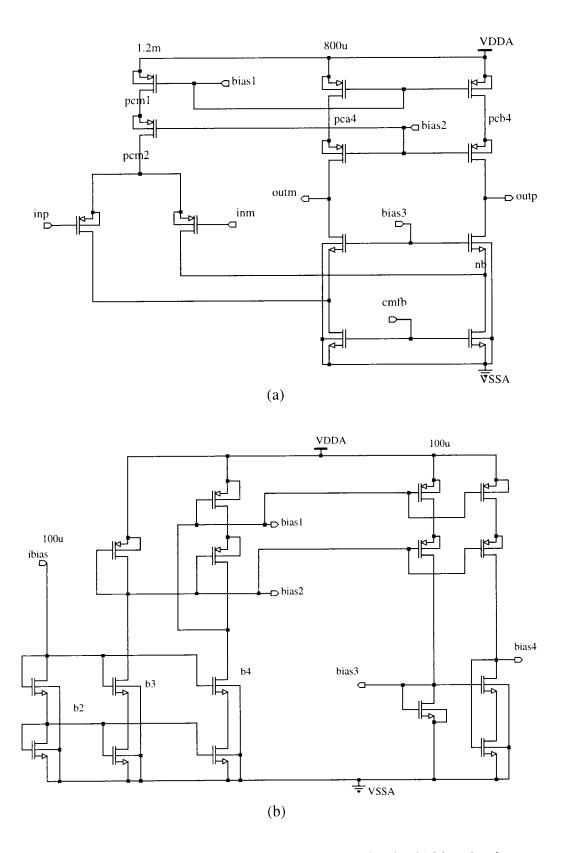

| 6.11: Two stage op-amp using a source follower for frequency compensation                                                                            | 100         |

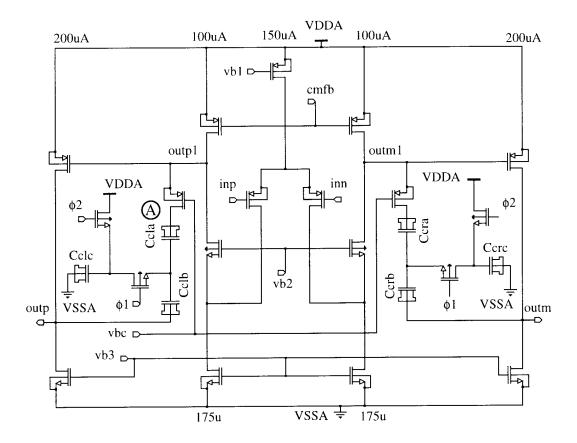

| 6.12: Two-stage op-amp using MOSFETs as Miller compensation capacitors                                                                               | 101         |

| 6.13: Frequency compensation branch. (a) during $\phi_1$ ; (b) during $\phi_2$ ; (c) equivalent circuit during $\phi_2$                              | 102         |

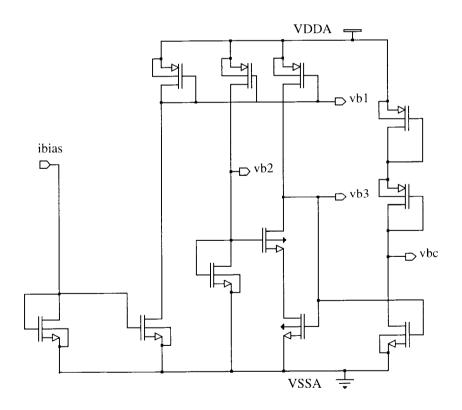

| 6.14: Bias circuit for the op-amp                                                                                                                    | 102         |

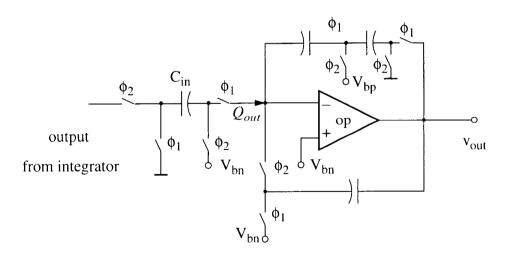

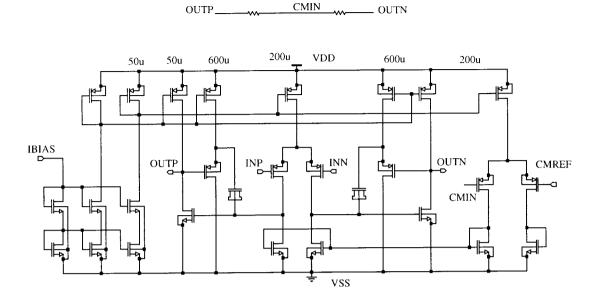

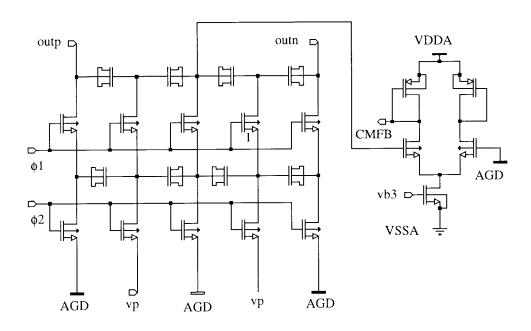

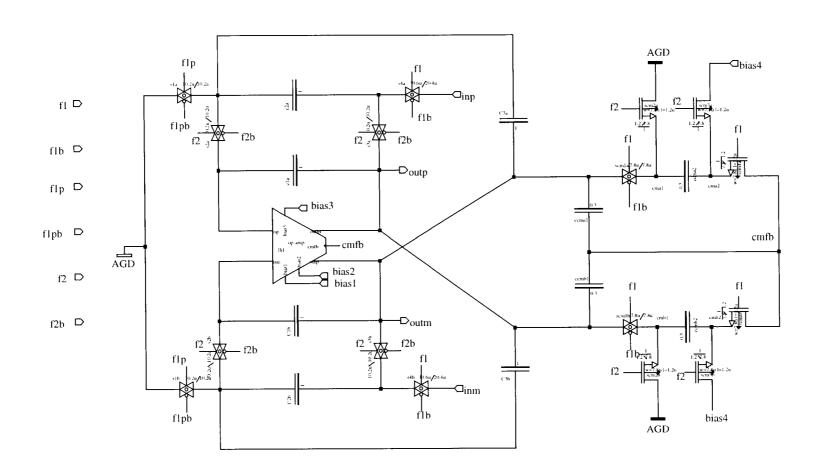

| 6.15: Common-mode feedback circuit                                                                                                                   | 103         |

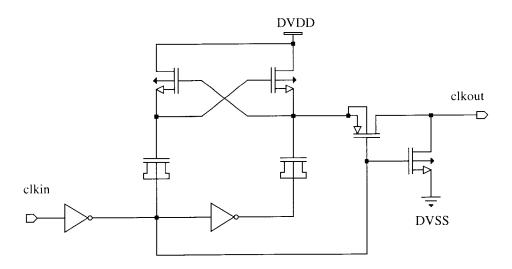

| 6.16: Clock bootstrapping circuit                                                                                                                    | 104         |

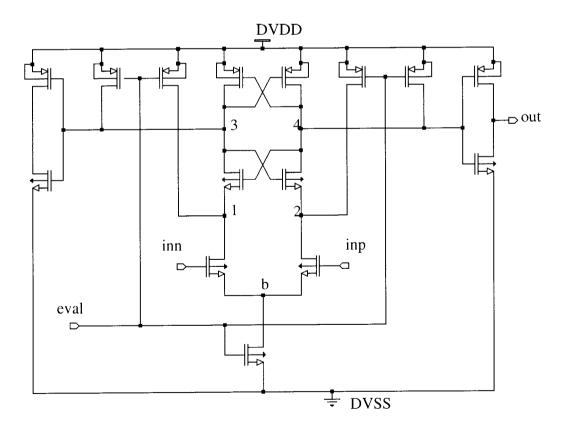

| 6.17: The comparator                                                                                                                                 | 105         |

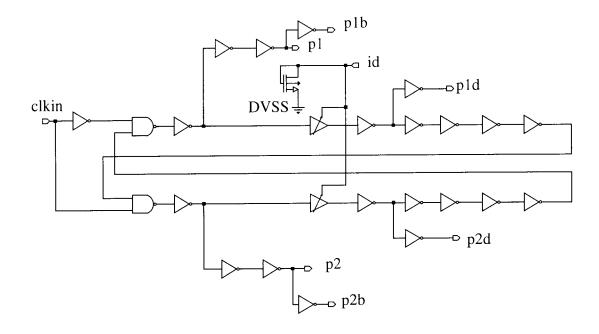

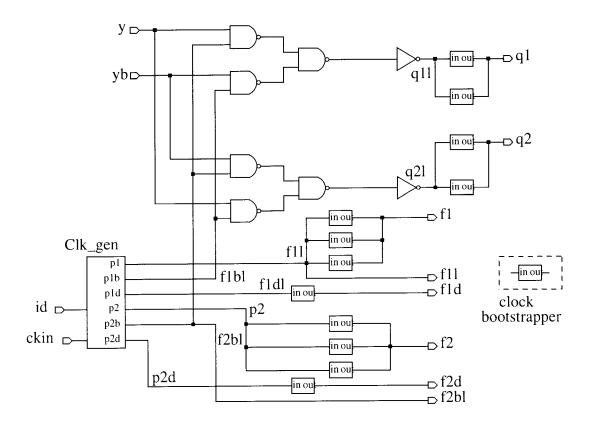

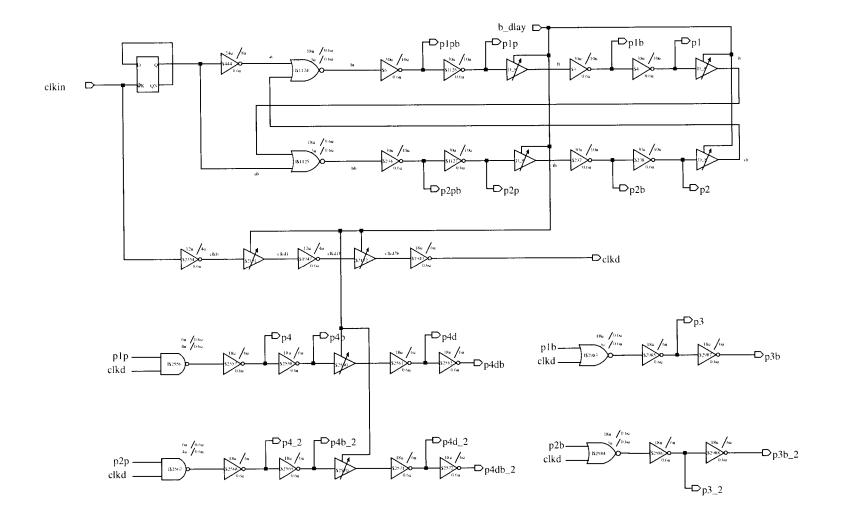

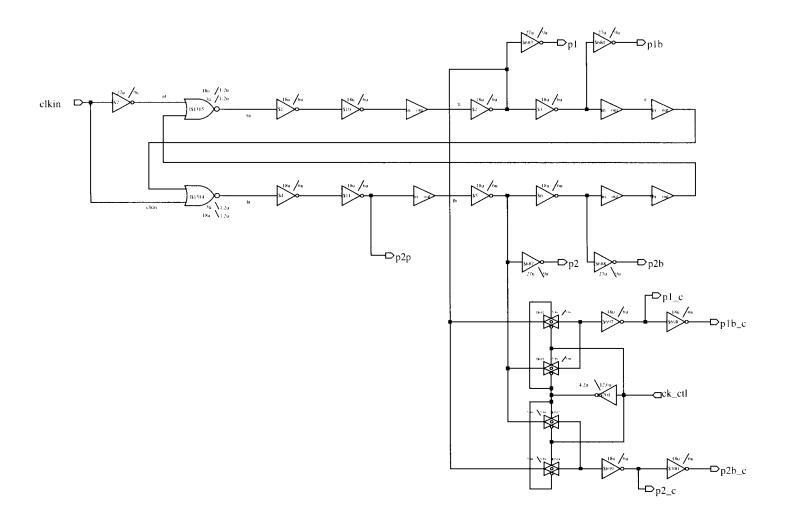

| 6.18: Clock generator                                                                                                                                | 106         |

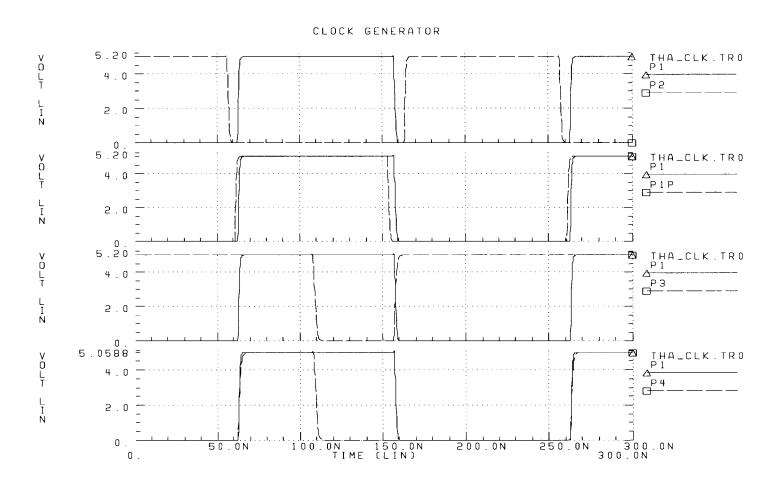

| 6.19: Clock generator with control logic and bootstrapping stages                                                                                    | 106         |

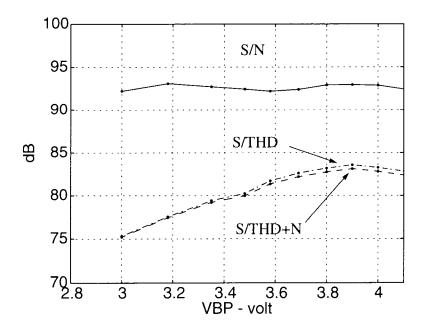

| 6.20: Complete modulator with comparator and latch                                                                                                   | 107         |

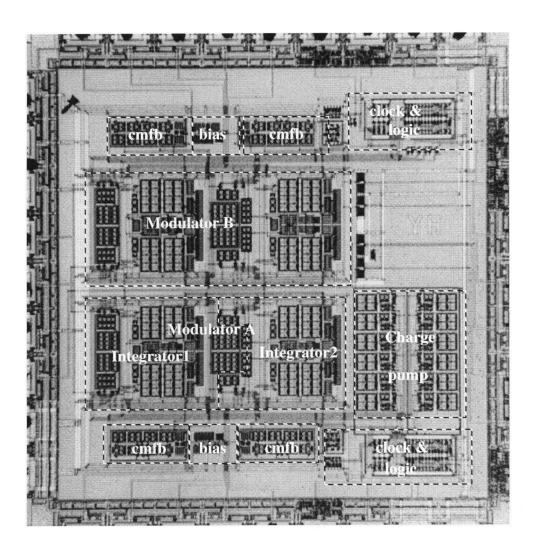

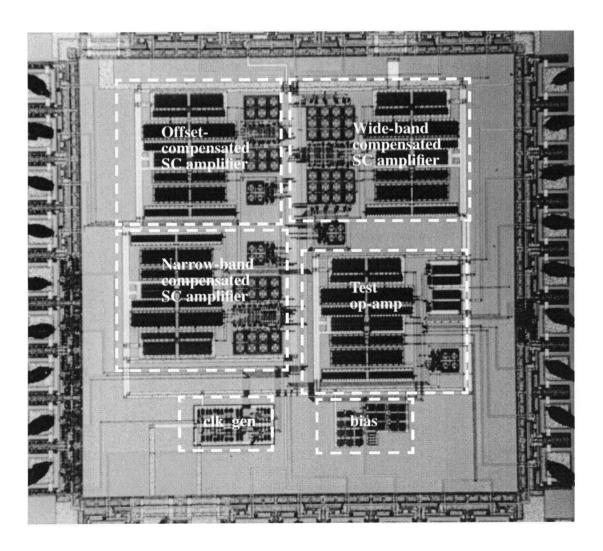

| 6.21: Chip photo                                                                                                                                     | 108         |

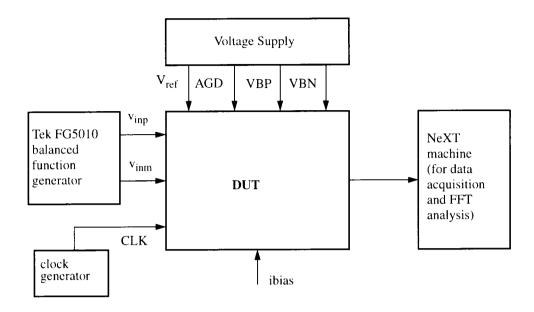

| 6.22: Test setup for the modulator                                                                                                                   | 109         |

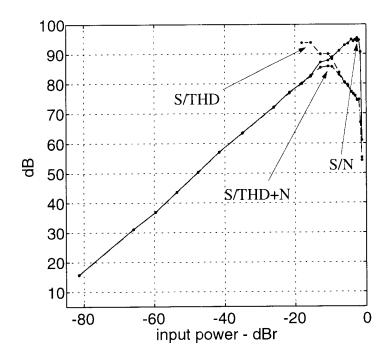

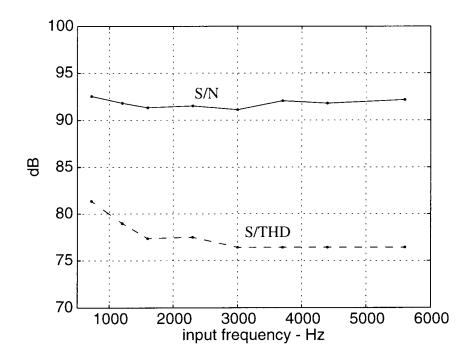

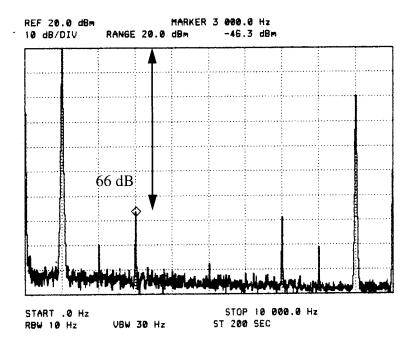

| 6.23: S/THD, S/THD+N and S/N vs. input power for a 1.28 kHz sine-wave input. Clock frequency was 3.072 MHz, signal band was 40 Hz - 6 kHz. (OSR=256) | 110         |

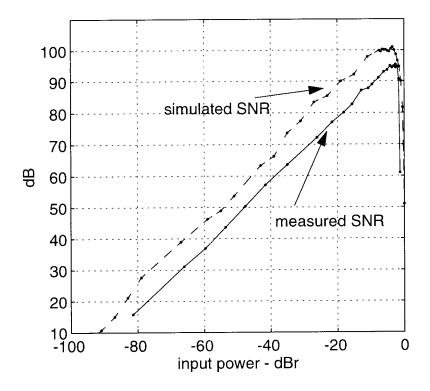

| 6.24: Comparison between simulated SNR and measured SNR                                                                                              |             |

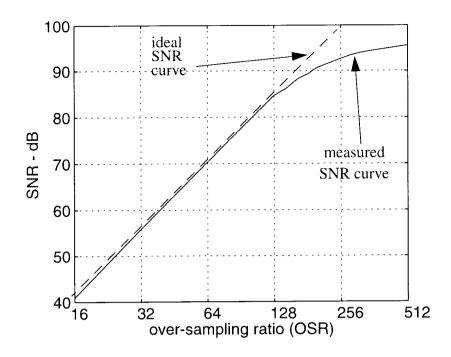

| 6.25: SNR vs. OSR for a -6 dBr input signal                                                                                                          | 112         |

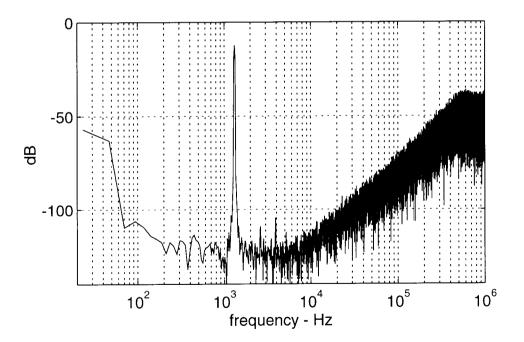

| 6.26: 128 k-point FFT spectrum of the modulator output for a -10 dBr, 1.28 kHz sine-wave input                                                       | 113         |

| <u>Figure</u> Pag                                                                                                                    | <u>ze</u> |

|--------------------------------------------------------------------------------------------------------------------------------------|-----------|

| 6.27: SNR and S/THD vs. input signal frequency for a -5 dBr sine-wave input.  THD includes harmonics from the 2nd to the fifth order | 14        |

| 6.28: SNR, S/THD and S/THD+N vs. VBP bias voltage for a -5 dBr, 1.28 kHz sine-wave input                                             | 14        |

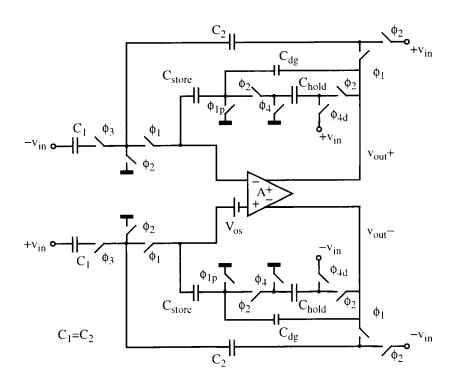

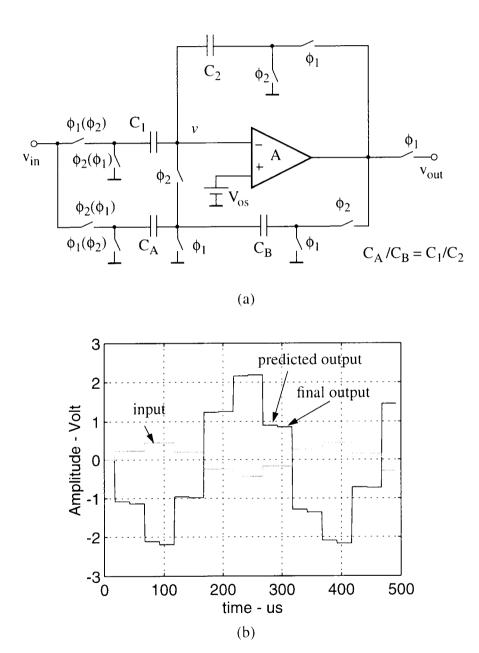

| 7.1: Schematic of the predictive T/H stage                                                                                           | 17        |

| 7.2: folded-cascode op-amp: (a) the op-amp circuit; (b) bias circuit11                                                               | 8         |

| 7.3: Clock generation circuit for the two T/H stages in a "ping-pong" structure11                                                    | 19        |

| 7.4: Clock signal waveforms                                                                                                          | 20        |

| 7.5: Nicollini's S/H stage                                                                                                           | 22        |

| 7.6: Offset-compensated S/H stage                                                                                                    | 23        |

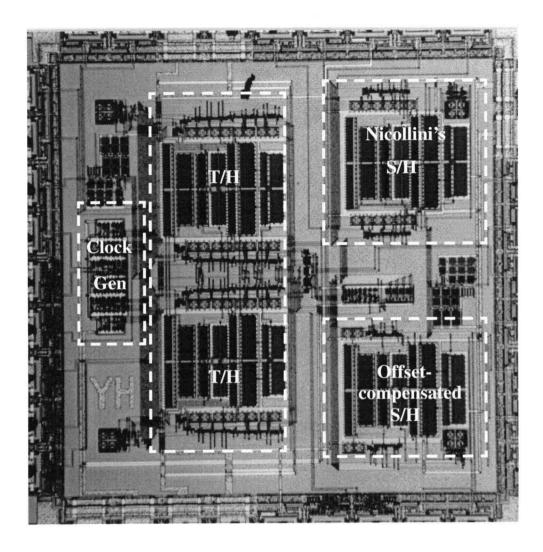

| 7.7: Die microphotograph of the S/H chip12                                                                                           | 24        |

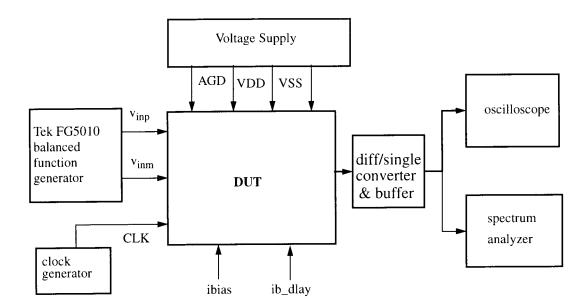

| 7.8: Test setup for the S/H chip12                                                                                                   | 25        |

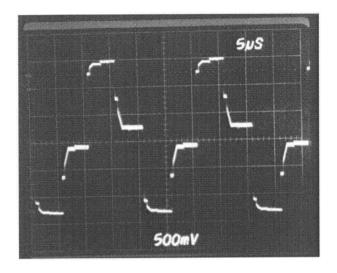

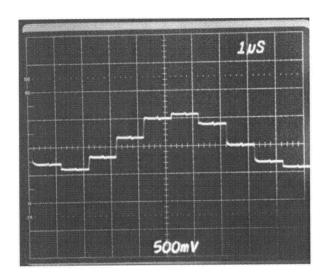

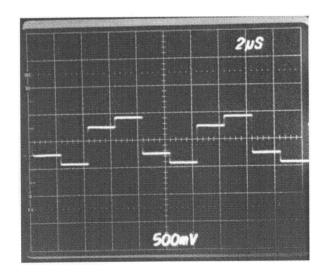

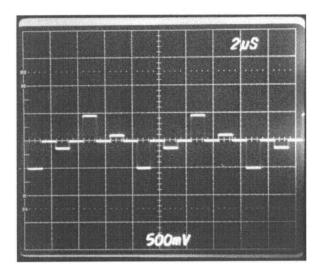

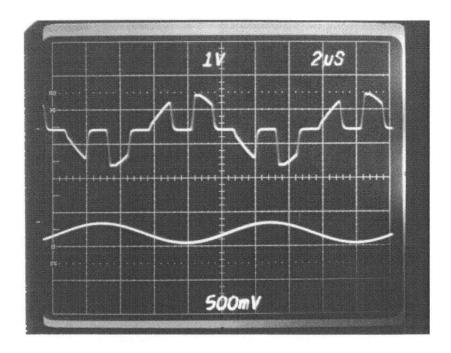

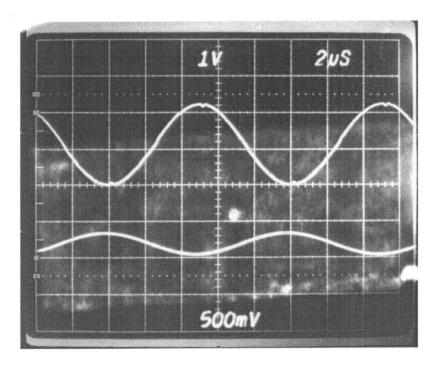

| 7.9: Track-and-hold stage output with a 50-kHz sine-wave input and a 200-kHz sampling rate                                           | 26        |

| 7.10: Output waveform of the "ping-pong" S/H output with a 50 kHz input and an effective sampling rate of 400 kHz                    | 26        |

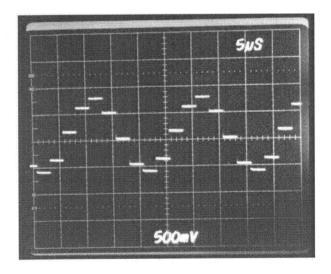

| 7.11: Output waveform of the "ping-pong" S/H output with a 125 kHz input and an effective sampling rate of 1 MHz                     | 27        |

| 7.12: Output wave-form of Nicollini's S/H stage with a 125 kHz input and a 500 kHz sampling rate                                     | 27        |

| 7.13: Output wave-form of the offset-compensated S/H stage with a 125 kHz input signal and a 500 kHz sampling rate                   | 28        |

| <u>Figure</u> |                                                                                                                                                              | <u>Page</u> |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 7.14:         | The output of the two predictive T/H stages operating in a "ping-pong" structure. The input signal frequency was 1 kHz and the sampling frequency was 10 kHz | 128         |

| 7.15:         | Output spectrum of Nicollini's S/H stage with a 1 kHz sine-wave input and a 10 kHz sampling rate                                                             | 129         |

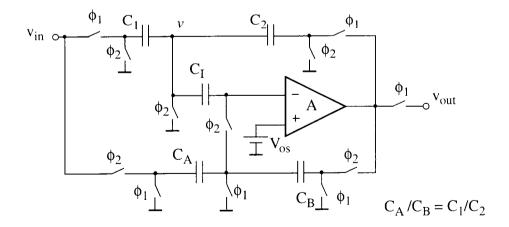

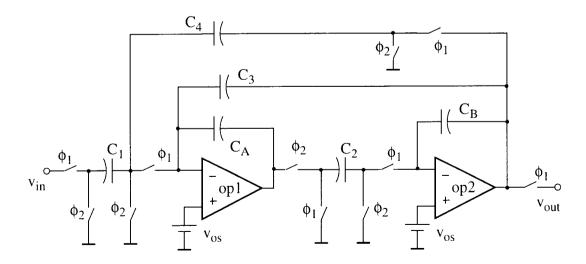

| 8.1:          | Offset-compensated SC amplifier                                                                                                                              | 132         |

| 8.2:          | Narrow-band gain- and offset-compensated SC amplifier                                                                                                        | 133         |

| 8.3:          | Wide-band gain- and offset-compensated SC amplifier                                                                                                          | 134         |

| 8.4:          | Clock generator                                                                                                                                              | 135         |

| 8.5:          | Microphotograph of the SC amplifier chip                                                                                                                     | 136         |

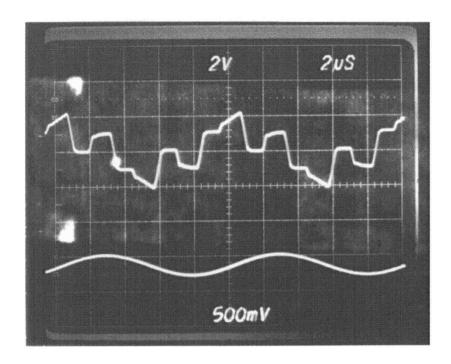

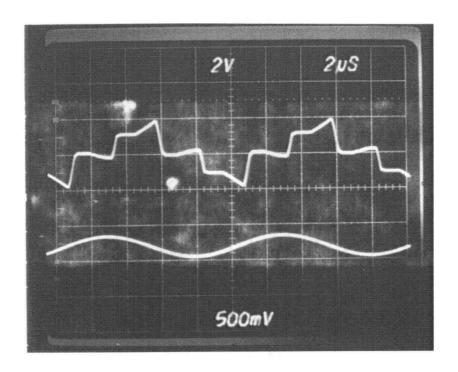

| 8.6:          | Signal waveforms of the offset-compensated SC amplifier. The upper curve is the output signal and the lower curve is the input signal                        | 140         |

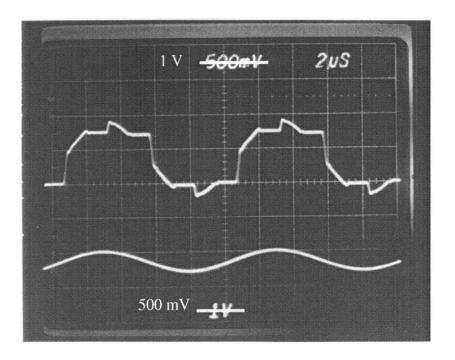

| 8.7:          | Output and input waveforms of the narrow-band compensated SC amplifier, when non-delaying operation was selected                                             | 140         |

| 8.8:          | Output and input signal waveforms of the narrow-band compensated SC amplifier when delaying operation was selected                                           | 141         |

| 8.9:          | Output and input signal waveforms of the wide-band compensated SC amplifier when non-delaying operation was selected                                         | 141         |

| 8.10          | : Output waveform for the wide-band compensated SC amplifier when delaying operation was selected                                                            | 142         |

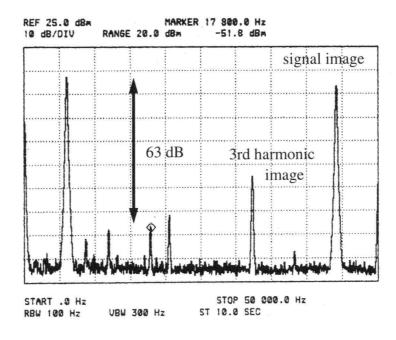

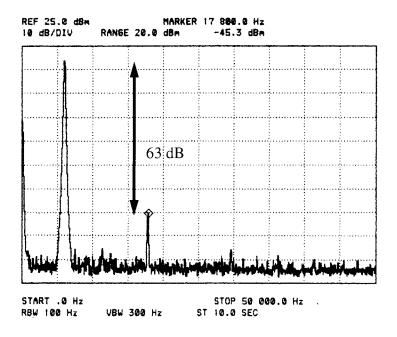

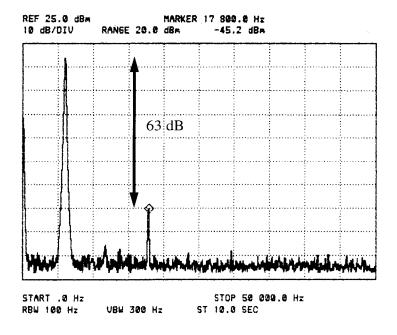

| 8.11          | : Output spectrum of the offset-compensated SC amplifier with a clock frequency of 50 kHz (non-delaying)                                                     | 142         |

| <u>Figure</u> Page                                                                                                                                                                                                           |   |       |      |     |   |    |    |    |    |     |    |   |     |     |     |     |       |     |      |      |               |      |       |     |      |       |      |    | <u>P</u> | age | 2 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-------|------|-----|---|----|----|----|----|-----|----|---|-----|-----|-----|-----|-------|-----|------|------|---------------|------|-------|-----|------|-------|------|----|----------|-----|---|

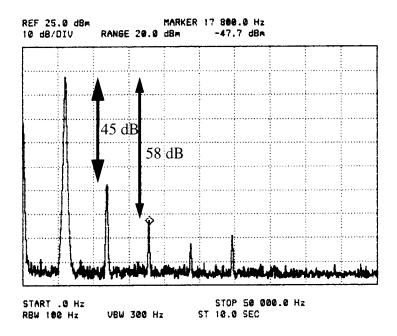

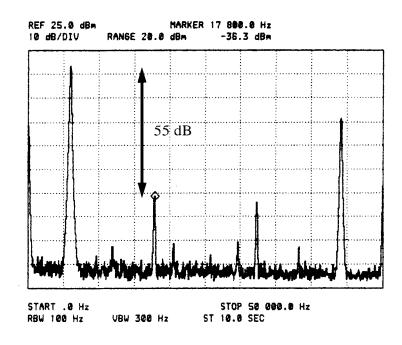

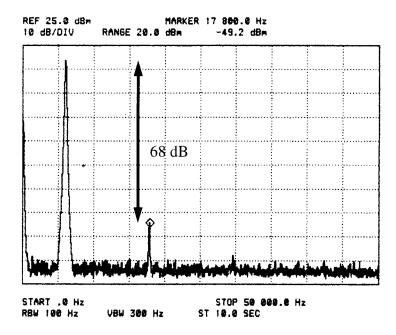

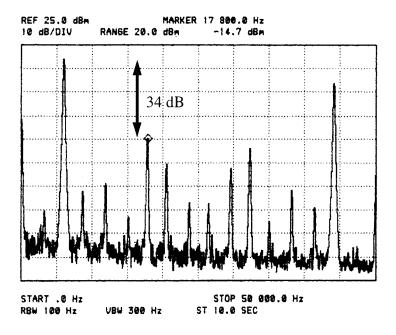

| 8.12: Output spectrum of the offset-compensated SC amplifier with a clock frequency of 500 kHz (non-delaying)                                                                                                                | - | •     |      |     | - |    |    |    |    |     |    |   |     |     |     |     |       | _   |      |      |               |      |       |     |      |       |      |    | ••••     | 143 | 3 |

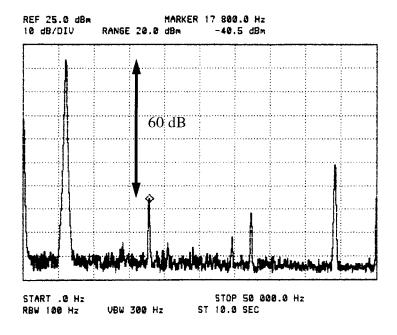

| 8.13: Output spectrum of the narrow-band compensated SC amplifier in non-delaying operation with a clock frequency of 50 kHz                                                                                                 | _ | _     |      |     | _ |    |    |    |    |     |    |   |     |     |     |     |       |     |      |      |               |      |       |     |      |       |      |    |          | 143 | 3 |

| 8.14: Output spectrum of the narrow-band compensated SC amplifier in non-delaying operation with a clock frequency of 500 kHz                                                                                                |   |       |      |     | • |    |    |    |    |     |    |   |     |     |     |     |       |     |      | •    |               |      |       | _   |      |       |      |    |          | 144 | 4 |

| 8.15: utput spectrum of the narrow-band compensated SC amplifier in delaying operation with a clock frequency of 50 kHz                                                                                                      |   |       | •    | •   |   |    |    |    |    |     |    |   |     |     |     |     |       |     | _    |      |               |      |       |     |      |       |      |    |          | 144 | 4 |

| 8.16: Output spectrum of the narrow-band compensated SC amplifier in delaying operation with a clock frequency of 500 kHz                                                                                                    | _ | _     |      |     | _ |    |    |    |    |     |    |   |     |     |     |     |       |     |      | _    |               |      |       |     |      |       |      |    |          | 145 | 5 |

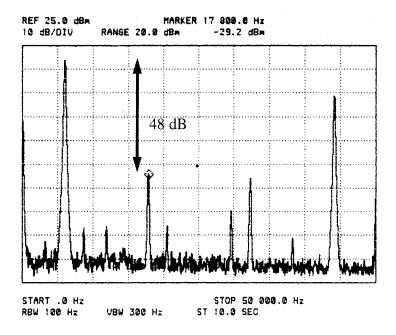

| 8.17: Output spectrum of the wide-band compensated SC amplifier in non-delaying operation with a clock frequency of 50 kHz                                                                                                   | - | -     |      |     | - |    |    |    |    |     |    |   |     |     |     |     |       |     |      |      |               |      |       |     |      |       | •••• |    |          | 145 | 5 |

| 8.18: Output spectrum of the wide-band compensated SC amplifier in delaying operation with a clock frequency of 50 kHz                                                                                                       | • | •     |      |     | • |    |    |    |    |     |    |   |     |     |     |     |       |     | _    |      |               |      |       |     |      |       |      |    |          | 146 | 5 |

| 8.19: Output spectrum of the wide-band compensated SC amplifier in non-<br>delaying operation with a clock frequency of 500 kHz. The resulting<br>spectrum for delaying operation is almost the same in this measurement 146 | O | ing c | ying | ing | g | op | pe | er | ra | tic | on | w | ith | ı a | clo | ock | c fre | equ | ienc | y of | f <b>5</b> 00 | ) kI | Iz. T | Γhe | resi | ultir | ng   | nt |          | 140 | 5 |

## LIST OF TABLES

| <u>Table</u> | <u>Page</u>                                              |

|--------------|----------------------------------------------------------|

| 3.1:         | Harmonic distortion comparison for various SC amplifiers |

| 6.1:         | Modulator design specifications                          |

| 6.2:         | MOSFET capacitor sizes                                   |

| 8.1:         | Measured S/THD for the SC amplifiers                     |

### Design Techniques of High-Performance Switched-Capacitor Circuits in the Presence of Component Imperfections

#### **Chapter 1. Introduction**

This thesis describes design techniques for high-performance switched-capacitor (SC) circuits, primarily for high-linearity low-noise SC circuits in the presence of component imperfections, such as nonlinear op-amp voltage transfer characteristics, capacitor nonlinearities as well as the finite op-amp dc gain and input-referred op-amp offset and noise. Various correlated-double-sampling (CDS) schemes are discussed, and some novel predictive CDS schemes are proposed. Analysis, simulation and experimental results show that these schemes are very effective in reducing the effects of op-amp imperfections, resulting in lower signal distortion and reduced low-frequency noise and dc offset. The effect of capacitor nonlinearity in SC circuits is analyzed in detail, and techniques for linearization are discussed. Applying these techniques, MOSFET capacitors can be used in high-performance digital-process-compatible SC circuit designs. As an example, a 3-V all-MOSFET delta-sigma modulator prototype was developed using the series capacitor nonlinearity compensation technique. The measured results show that these circuit techniques are highly effective in high-performance SC circuit designs.

#### 1.1 Motivation

There are a number of component imperfections that degrade the performance of an SC circuit. The most important ones can be divided into three categories. One is associated with noise effects, which corrupt the signal. These include the thermal noise, op-amp 1/f noise, op-amp offset and charge injection noise. The second category is associated with linear variations of the transfer function of the circuits, which cause gain error and misplaced pole/zero locations. These effects include the finite op-amp gain, parasitic capacitances and capacitor mismatch. The third one is associated with components'

nonlinear behavior, which causes signal distortion. These effects include the op-amps' nonlinear voltage transfer characteristics and the capacitors' voltage dependence. This research work concentrates on techniques for reducing the circuit's nonlinear distortion effect, with the other two categories only briefly discussed.

#### 1.1.1 Sources of Harmonic Distortion in SC Circuits

Switched-capacitor circuits are widely used in the area of analog signal processing, such as analog-to-digital and digital-to-analog data converters, filters, precision gain stages, track-and-hold/sample-and-hold stages, etc. High performance is usually desired for these important building blocks. They feature a large dynamic range (DR), a high signal-to-noise ratio (SNR), high signal to total harmonic distortion (S/THD), and sometimes low power consumption as well. While the limiting factors for the DR and SNR are mainly electronic noise and quantization noise, the mechanism causing circuit nonlinearity is far more complex. It is well known that the sources of circuit nonlinear distortion are mainly analog component imperfections, namely, nonlinear MOS switch on-resistances, charge injection from MOS switches, nonlinear op-amp voltage transfer characteristics and capacitor nonlinearity. Techniques are available to cope with the first two sources [1],[2], but effective techniques to suppress the nonlinear distortion resulting from the latter two are not well developed.

#### 1.1.2 Enhancing Op-amp Linearity Using CDS Techniques

With today's ICs moving towards the direction of low power and low cost, low supply voltages are commonly used in a mixed-signal device, and the use of basic CMOS technology for fabrication has become more and more desirable. Although low supply voltage does not necessarily lead to a low-power solution for analog circuitry, due to the large percentage of digital circuitry in today's mixed-signal ICs, it usually drastically reduces the overall chip power dissipation. Low-voltage operation, however, creates a

number of challenges for analog circuit designers who want to achieve high performance in SC circuits. One of these challenges is the trade-off between dynamic range and power consumption. In a low-voltage environment, the electronic noise becomes more significant relative to the reduced signal power. To achieve large dynamic range, large devices are normally used and more current is drawn. In addition, when the supply voltage is scaled down, the device threshold voltages do not get scaled down as much. This makes the signal voltage swing range even more important. Having larger signal voltage swing relative to the rails will decrease the power dissipation; but, on the other hand, due to the nonlinear op-amp voltage transfer characteristics, an increase of the op-amp output voltage swing increases the harmonic distortion as well. This scenario can be much improved by incorporating a CDS scheme in the circuit, especially by using the predictive CDS techniques proposed in this research work. It will be shown later that some types of CDS schemes can suppress nonlinear harmonic distortion in a narrow frequency range, while some can provide suppression over a wide frequency range.

#### 1.1.3 Design of High-linearity SC Circuits Without High Linearity Capacitors

The use of basic digital CMOS technology for mixed-signal ICs results in lower manufacturing costs and shorter fabrication cycle, but at the same time it causes poorer linearity as well. This is because of the lack of high-linearity capacitors. In an analog CMOS process, high-linearity capacitors can be realized in a poly-to-poly or metal-to-poly structure with a few more mask layers than that for a standard CMOS process, while in a basic CMOS process, such capacitors are not available. It was proposed by earlier researchers [3][4] that the gate-to-channel capacitances of a MOSFET can be used as capacitors. When operating in their strong-inversion region or accumulation region, such capacitors can have higher unit-area capacitance and better matching accuracy than the other types of capacitors such as poly-poly, poly-metal or metal-metal capacitors. And, most importantly, they are available in any basic CMOS technology. However, their

capacitance shows a strong voltage dependence that is usually 10 to 100 times higher than that of the poly-to-poly or poly-to-metal implementations [7][8][9]. This degree of nonlinearity imposes a significant limitation on the practical use of the MOSFET capacitors in high-performance applications. To the author's best knowledge, none of the reported SC circuits implemented using MOSFET capacitors had signal to total harmonic distortion ratio (S/THD) better than 80 dB [3][4] when signal swing is close to 1 V.

We next discuss how capacitor nonlinearity causes distortion. In a SC circuit, an analog signal is processed by charge scaling and by transferring charge between capacitors. Complete charge transfer from one capacitor to another is made possible by the virtual ground of the op-amp. As will be shown in detail in Chapter 4, under certain conditions, the capacitor nonlinearity need not cause any signal processing imperfections if all the signal processing is done in the charge domain. Nonetheless, the input and output signals of a SC circuit are usually voltages, and the charge delivery from one stage to the next stage is achieved by sampling the output voltage of the previous stage and converting the voltage into charge via the input capacitors. If we can have linear charge delivery between stages and linear conversion between voltage and charge at the input and output of a SC circuit, we can perform linear signal processing with the overall circuit.

Based on the above observation, a high-linearity SC circuit can be designed using a high-linearity voltage-to-charge (V-Q) converter at the input, then processing the signal in the charge domain before it is sent to a high-linearity charge-to-voltage (Q-V) converter at the output. The high-linearity V-Q and Q-V converters can be realized by using linearized SC branches [4][5][6]. Having capacitors connected in series, the signal voltage swing across each capacitors is smaller, thus the linearity is much improved. In addition, having two capacitors with similar nonlinearity connected in opposite direction (back-to-back) also cancels the nonlinearity to a first-order approximation. A delta-sigma modulator

prototype utilizing this technique is described in this thesis and experimental results are shown.

#### 1.2 Thesis Structure

Chapter 2 serves as an overview of correlated double sampling techniques. Some basic CDS schemes are discussed for comparators, T/H stages, voltage amplifiers and integrators. Then the principle of using CDS to suppress the op-amp harmonic distortion is introduced.

In Chapter 3, the concept of predictive CDS is introduced, and some novel predictive track-and-hold (T/H) stages are proposed. Some predictive CDS SC amplifiers and integrators are also discussed.

Chapter 4 deals with the capacitor nonlinearity problem. Analysis is performed on how capacitor nonlinearity affects the SC circuit linearity, then design techniques are described for high-linearity SC circuits using nonlinear capacitors.

In Chapter 5, kT/C noise analysis is performed for SC circuits, and a comparison is made between circuits employing correlated-double-sampling schemes.

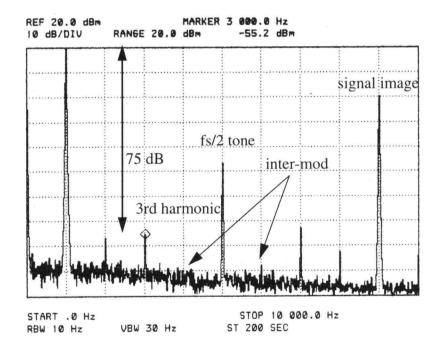

Chapter 6 presents the design of a 3-V 96-dB dynamic range all-MOSFET deltasigma modulator, and measurement results obtained from the prototype chip are also shown.

In Chapter 7, after a brief description of the predictive gain- and offset-compensated track-and-hold prototype chip, experimental results are shown and comparison is made with the other S/H stages implemented on the same chip.

Chapter 8 presents the experimental results on reduced harmonic distortion in circuits with gain-compensating CDS schemes. The measured results are obtained from a chip with various SC amplifiers.

Finally, Chapter 9 contains a summary of the work and plans for future work.

#### **Chapter 2. Correlated Double Sampling: Background**

Correlated double sampling techniques are often used to compensate for nonideal effects in op-amps, such as narrow-band (1/f) input-referred noise, input-referred offset and finite dc gain.

In this chapter, the basic principles of CDS operation are reviewed. Then the mechanism of signal distortion resulting from op-amp gain nonlinearity is investigated, and a solution based on CDS is proposed.

#### 2.1 Introduction

The accurate operation of switched-capacitor circuits relies on accurate charge transfer between capacitors, so that the signal can be processed in the charge domain. This is achieved by the active elements used in the circuit. Operational amplifiers (op-amps) are often used as such elements, whose main function is to create a virtual ground. A virtual ground is a node that is forced to a constant potential and the current required to force it is steered in an error free manner to another part of a circuit. Using op-amps with MOS input transistors, the op-amp input current, which is the same as the virtual ground error current, at low frequencies can be made very small; however, the input voltage of a practical opamp is usually significantly affected by several nonideal effects. These include input referred noise (most importantly, 1/f and thermal noise), input-referred dc offset voltage, as well as the signal voltage needed to generate the desired output voltage of the op-amp. In a low-supply-voltage design, such nonidealities will be more significant, because of the relatively larger noise compared to the limited signal swing, and high-gain op-amps might not be available. Typically, the thermal noise has a wide frequency band, while the 1/f noise and offset are narrow-band signals. The input signal can be either narrow-band or wideband, depending on the application. The narrow-band noise (dc offset and 1/f noise), because of the strong correlation between adjacent signal samples, can be greatly reduced using correlated double sampling techniques. These techniques are applicable to such important building blocks as comparators, voltage amplifiers, sample-and-hold (S/H) stages, ADC and DAC stages, integrators, etc.

### 2.2 The Basic Principle of CDS

The basic idea behind CDS is to sample the unwanted quantity (noise, offset as well as the induced signal at the op-amp input node), and then to subtract it from the instantaneous value of the contaminated signal either at the op-amp input node or the output node [10].

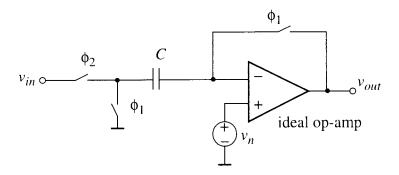

Figure 2.1 shows a simple offset-compensated comparator. The op-amp input referred noise is denoted as  $v_n$ , and is modeled as a voltage source at the op-amp input node. When  $\phi_1$  goes high, capacitor C is charged to the input-referred noise voltage  $v_n$  of the op-amp, and this value is subtracted from the input voltage  $v_{in}$  when  $\phi_2 = 1$ . A simple analysis shows that the transfer relation from  $v_n$  to  $v_{out}$  is

Figure 2.1: A simple offset-compensated comparator

$$V_{out}(z) = H_n(z) \cdot V_n(z) = (1 - z^{-1}) \cdot V_n(z).$$

(2.1)

The transfer function in the frequency domain is given by

$$|H_n| = 2 \cdot \left| \sin \left( \frac{\omega T}{2} \right) \right|, \tag{2.2}$$

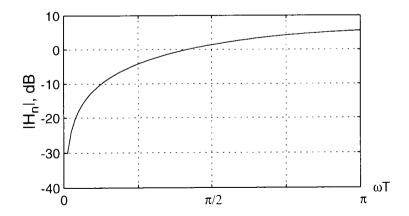

where  $V_{out}(z)$  and  $V_n(z)$  are the z-domain output signal and the op-amp input referred noise, respectively. Figure 2.2 shows the magnitude response of the noise transfer function  $H_n$ . Since  $H_n$  is a highpass function, the low-frequency components of  $v_n$  are suppressed by this operation. Thus, the dc offset voltage and much of the input-referred 1/f noise will be suppressed. Note, however, that the voltage acquired by C during the  $\phi_1 = 1$  interval does not contain the input signal  $v_{in}$ , and hence the effect of finite op-amp gain is not reduced by this circuit.

Unlike the dc offset voltage and 1/f noise, the thermal noise (generated by the switches and the op-amp) is a wide-band random process, and its adjacent samples are uncorrelated. Thus, the noise powers present at these samples do not cancel, but increase in the baseband due to aliasing.

Figure 2.2: The magnitude response of  $H_n$ .

The basic operation described above is called auto-zeroing or offset cancellation. Also, since it cancels low-frequency noise by sampling it twice and generating the difference of these correlated samples, it is often called correlated double sampling, or CDS. (The term CDS is usually reserved for sampled-data circuits, while the others are applied for continuous-time circuits as well.)

### 2.3 Offset-Compensated SC Circuits

Shown in Figure 2.3 is a conventional SC voltage amplifier [11]. The ideal output is  $v_{out} = -(C_1/C_2) v_{in}$ , but the finite op-amp gain A and the input-referred dc offset  $V_{os}$  change it to

$$v_{out} = G_{id} \cdot (1 + E) \cdot v_{in} + (1 + G_{id}) \cdot V_{os},$$

(2.3)

where

$$E = \frac{-(1 + C_1/C_2)/A}{1 + (1 + C_1/C_2)/A}$$

(2.4)

is the relative gain error and  $G_{id}$  is the ideal voltage gain  $-C_1/C_2$ . Thus, for typical values

Figure 2.3: Uncompensated SC voltage amplifier

of A,  $G_{id}$  and  $V_{os}$ , namely (A = 60 dB,  $G_{id} = 10$ , and  $V_{os} = 10 \text{ mV}$ ), a gain error of 1% and an output dc offset of 100 mV may occur. In some high-precision applications, e.g. if the amplifier is part of a DAC or ADC, this may be unacceptable. Also, the large output dc offset may become a significant limitation on the permissible signal swing, especially in low-supply-voltage designs.

Figure 2.4: a. Offset-compensated SC amplifier; b. offset-compensated S/H; c: output waveform the two circuits.

Figure 2.4a shows a simple offset-compensated amplifier [13]. The output of this stage at the end of  $\phi_2$  is

$$v_{out} = \frac{-C_1/C_2}{1 + (1 + C_1/C_2)/A} \cdot v_{in} + \frac{V_{os}}{A}.$$

(2.5)

The effect of the op-amp dc offset as well as the input referred 1/f noise is now reduced by the op-amp open-loop gain A, and becomes negligible in most applications. The same auto-zeroing operation can be applied to a S/H stage and an offset-compensated S/H circuit (Figure 2.4b) is resulted. However, these circuits have some drawbacks. As Figure 2.4c illustrates, during the  $\phi_1 = 1$  intervals the output is pulled to  $V_{os}$ , thus the opamp must have a high slew rate to enable  $v_{out}$  to slew back and forth at each clock transition. Also, the stage gain is still affected by the finite dc gain of the op-amp in a same way as in the circuit of Figure 2.3.

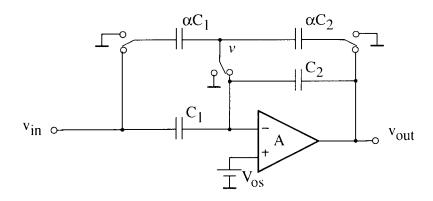

#### 2.4 Gain- and Offset-Compensated SC Circuits

An improved SC amplifier which does not require resetting of the output in each clock period, and hence allows more relaxed op-amp specifications for low- frequency inputs, is shown in Figure 2.5a [14]. In this circuit, the feedback reset switch is replaced by the elementary S/H branch consisting of  $C_3$  and its two associated switches. Assume that the circuit is used as a noninverting amplifier, and hence the clock phases shown outside of the parentheses in Figure 2.5a are valid. Then, when  $\phi_2 \to 1$ ,  $C_1$  discharges into  $C_2$ , and the valid output voltage is generated. This voltage is stored in  $C_3$ . When next  $\phi_1 \to 1$ ,  $C_3$  becomes the feedback capacitor,  $C_1$  samples the input, and  $C_2$  discharges. If the signal bandwidth is much smaller than  $f_s/2$ , i.e. the signal is significantly oversampled, then  $v_{out}$  does not vary much from one clock phase to the next clock phase. Thus, for a finite dc opamp gain A, the signal voltage  $-v_{out}/A$  at the virtual ground is a slowly varying signal which is therefore nearly cancelled by the CDS switching of  $C_1$  and  $C_2$ . This reduces the effect of the op-amp finite gain A on the voltage gain of the stage.

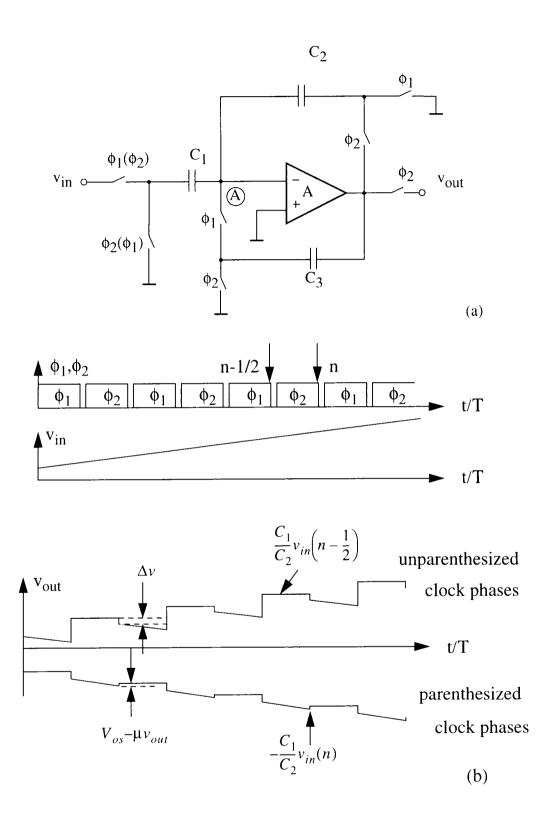

Figure 2.5: a. An offset- and finite-gain-compensated SC amplifier; b. clock and signal waveforms.

Figure 2.5b illustrates the clock phases and waveforms of the amplifier. When  $\phi_1 \to 1$  and the reset phase begins, there is a small step  $\Delta v = V_{os} - \mu v_{out} - (C_1/C_3) \Delta v_{in}$  in the output voltage, where  $\Delta v_{in}$  is the change in  $v_{in}$  during the  $\phi_2 = 1$  interval. (The  $\Delta v_{in}$  term enters only for noninverting operation.) This occurs because, as  $\phi_1 \to 1$ ,  $C_3$  is disconnected from ground and reconnected to the virtual ground. Here  $\mu \equiv 1/A$ . As  $\Delta v$  is of the order of a few mVs, this step change does not require a fast settling time or a high slew rate from the op-amp. The dc output offset voltage is  $\mu (1+C_1/C_2) V_{os}$ .

Detailed analysis [14] shows that the gain is now weakly frequency dependent due to the highpass CDS effect on the virtual ground voltage, with the dc gain given by

$$H(z)_{z=1} = \frac{-C_1/C_2}{1 + (1 + C_1/C_2)\mu^2}$$

(2.6)

As Eq. (2.6) demonstrates, the error term in the denominator of the transfer function is now proportional to  $\mu^2$ , rather than  $\mu$ , Thus, the effective value of the op-amp gain as far

Figure 2.6: Gain- and offset-compensated SC integrator.

as the dc gain is concerned is the square of the true value. Circuits with this property are called gain-enhanced or gain-squaring stages.

With some modifications, the compensation schemes described above can also be applied to SC integrators. Figure 2.6 shows a gain- and offset-compensated SC integrator. Unlike in a SC amplifier where the feedback capacitor  $C_2$  is completely discharged during every clock phase  $\phi_1$ , and its charge cancels the charge from  $C_1$ , here, in order to balance the charge flow from  $C_1$  when  $\phi_1$  goes high,  $C_3$  needs to be precharged between input and output during  $\phi_2$ . To reduce the signal-dependent charge injection, the switch that disconnects  $C_2$  from the feedback path should be moved from the side of the op-amp output to the op-amp input. Simple analysis shows the input referred offset is reduced to  $\mu (1+C_1/C_2) V_{os}$ , and the pole error is now  $(C_1/C_2)\mu^2$  [18].

#### 2.5 Reducing Harmonic Distortion Using CDS Schemes

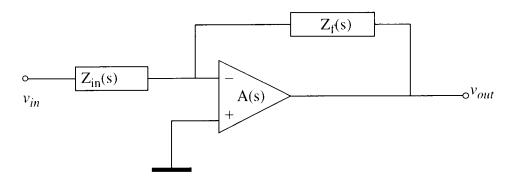

Aside from the input-referred noise and finite gain, one other major limitation of the monolithic op-amp in an SC circuit is its nonlinearity. In a continuous-time application (or during instantaneous operation within one clock phase in an SC circuit) as shown in

Figure 2.7: A closed-loop op-amp.

Figure 2.7, it is known that the open-loop harmonic distortion is suppressed by the loop gain under close-loop operation.

$$HD_{closed-loop} \approx \frac{HD_{open-loop}}{Z_{in}(s)}$$

(2.7)

Eq. (2.7) shows that the higher the loop gain is, the lower the harmonic distortion will be. In a sampled-data system, the harmonic distortion can be further suppressed by using a gain-compensation scheme. Depending on the actual scheme, CDS can provide harmonic suppression over a narrow band or a wide band in the discrete frequency domain.

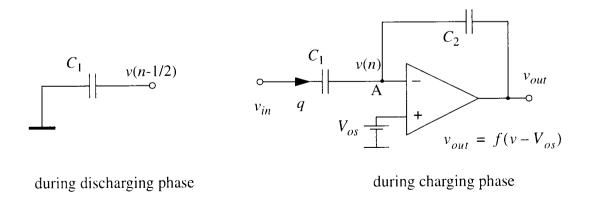

Consider the simple charge-transfer operation shown in Figure 2.8, where the opamp open-loop voltage transfer function is denoted as  $v_{out} = f(v_i - V_{os})$ . Here,  $v_i$  and  $v_{out}$  are the voltages of the op-amp input node and output node, respectively, and  $V_{os}$  is the input-referred offset. At the *n*th clock transition, the charge entering into node A can be found as

$$q = C_1[v_{in} - v(n) + v(n - 1/2)] = C_1[v_{in} - v_e],$$

(2.8)

where the error term is

Figure 2.8: Charge transfer in SC circuit.

$$v_e = v(n) - v(n - 1/2) = f^{-1}[v_{out}(n)] - f^{-1}[v_{out}(n - 1/2)].$$

(2.9)

Clearly, the closer  $v_{out}(n)$  is to  $v_{out}(n-1/2)$ , the smaller the charge transfer error will be.

In many correlated double sampling schemes, the right side of  $C_1$  in Figure 2.8 is never disconnected from the op-amp input node (CDS circuits with error storage capacitors are exceptions), so that  $v(n-1/2) = V_{os} + f^{-1}[v_{out}(n-1/2)]$ . Assume the op-amp is fully differential and the input/output relationship can be written in the form

$$v = V_{os} + f^{-1}(v_{out}) \cong V_{os} + \mu \cdot v_{out} + \alpha \cdot v_{out}^{3}$$

(2.10)

Where  $\alpha$  is a constant coefficient from the Taylor expansion of  $f^{-1}$ . Then we have

$$v_e \cong \zeta \cdot [v_{out}(n) - v_{out}(n - 1/2)],$$

(2.11)

where

Figure 2.9: a: op-amp nonlinear transfer characteristics; b: op-amp gain vs. op-amp output.

$$\zeta = \mu + \alpha \cdot [v_{out}^2(n) - v_{out}(n) \cdot v_{out}(n - 1/2) + v_{out}^2(n - 1/2)]. \tag{2.12}$$

From Eq. (2.11), we can conclude that the closer  $v_{out}(n)$  is to  $v_{out}(n-1/2)$ , the smaller the charge transfer error and the nonlinear term will be. It should be pointed out that the reduced charge transfer error also leads to the reduced gain error in SC amplifiers and reduced pole error in SC integrators with CDS.

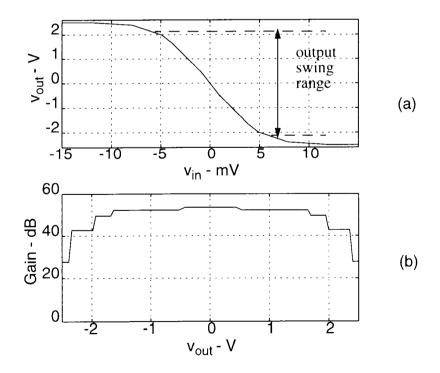

To verify the effectiveness of harmonic distortion reduction in gain-compensated SC circuits, simulations were performed for the SC amplifier shown in Figure 2.5a, and the

Figure 2.10: FFT spectrum of a: the uncompensated SC amplifier of Figure 2.3; b: gain- and offset-compensated SC amplifier of Figure 2.5.

uncompensated SC amplifier in Figure 2.3 for comparison. An op-amp is assumed with the piece-wise linear voltage transfer characteristics shown in Figure 2.9, and with an input referred offset voltage of 5 mV. The op-amp unity-gain frequency is assumed to be infinite for complete settling during each clock phase. The output voltage swing is 2.2  $V_{p-p}$  and the closed-loop voltage gain is -2. Figure 2.10 shows the resulting output spectra for the two SC amplifiers. The gain- and offset-compensated amplifier shows about 15 dB reduction on the second-order harmonic, and 8 dB reduction on the third-order harmonic. However, for higher-order harmonics at higher frequencies, the suppression decreases rapidly, and even amplification occurs for harmonics whose frequencies are higher than one-tenth of the clock frequency. This is due to fact that in the circuit of Figure 2.5,  $v_{out}(n-1/2) \cong v_{out}(n-1)$ , and the error voltage in Eq. (2.11) has a high-pass filtered spectrum. More detailed analysis and discussion will be given in the next chapter.

#### 2.6 Conclusions

The error voltage at the op-amp input node contains the input-referred noise, the dc offset and the induced signal due to the finite op-amp gain. The goal of correlated double sampling is to reduce this error. Since the 1/f noise and dc offset are narrow-band signals, and the correlation between adjacent samples is strong, they can be greatly reduced by an operation similar to differentiation, i.e., subtraction of the unwanted quantity from the next sample. For the finite op-amp gain induced signal, the same argument can be applied for over-sampled systems, where the input signal frequency is much lower than the clock frequency. However, for applications in which Nyquist sampling must be used, this kind of technique is no longer effective. This leads to the discussion of predictive correlated double sampling, where the correlated sampling action is made when the op-amp has a predicted value of the output for the next clock phase.

# **Chapter 3. Predictive Correlated Double Sampling**

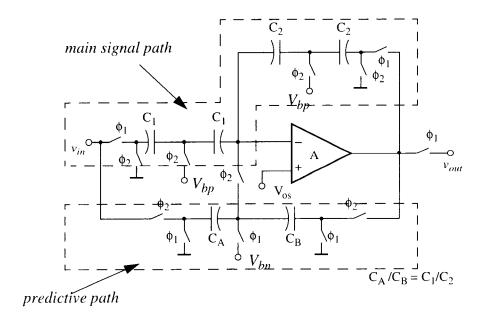

In the last chapter, basic correlated double sampling techniques were introduced. They are very effective in reducing the input-referred narrow-band noise, as well as compensating the finite op-amp dc gain in a narrow signal frequency range. However, in some SC circuits such as track-and-hold or sample-and-hold stages, Nyquist-rate data converters, post filters of  $\Delta\Sigma$  ADCs, etc., the input signal frequencies are close to (or even higher than) half the sampling frequency. This makes the CDS techniques introduced in chapter 2 ineffective when it comes to gain compensation and harmonic distortion suppression. To achieve gain-compensation over the entire frequency band, predictive CDS techniques ought to be used. A predictive CDS scheme is a circuit in which the opamp predicts its output for the next clock period during the present clock period, so that the adjacent two samples are nearly the same. The predictive operation results in a maximum correlation between the unwanted signal and the signal that is subtracted during the double sampling intervals. Since predictive CDS schemes can compensate for the op-amp inputreferred offset and reduce the finite op-amp gain effect over a wide signal frequency range, they are also called wideband gain- and offset-compensated (GOC) circuits. In this chapter, some novel predictive gain- and offset-compensated T/H stages are proposed, and then some existing and some newly proposed predictive CDS schemes for SC gain stages and integrators are described and compared.

# 3.1 Gain- and Offset-Compensated Track-and-Hold Stages

High-accuracy and high-speed CMOS track-and-hold stages are widely used in data acquisition systems, pipeline ADCs, time-interleaving ADCs and other applications. The design challenges often come from the op-amp's dc offse, finite gain and finite slew rate. Here, some novel fully-differential track-and-hold stages are proposed. The gain of the stages does not depend on capacitor matching, and they use a predictive CDS scheme to

reduce the effects of op-amp offset and finite dc gain. By incorporating an improved switching scheme, the slew rate requirement for the op-amp can be relaxed as well. Due to these properties, they are well suited, e.g., for the construction of the front stage in a parallel (time-interleaving) system. Simulations indicate that these circuits are capable of high-speed and high-accuracy operation without requiring high-quality components.

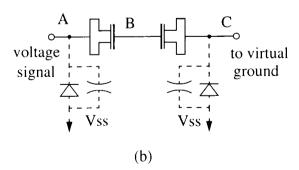

## 3.1.1. A Non-Predictive Track-and-Hold Stage

To improve the track-and-hold stage in Figure 2.4b, a gain- and offset-compensated S/H (Figure 3.1a) was proposed in 1987 by Wang and Temes [19]. It does not require

Figure 3.1: Gain- and offset-compensated track-and-hold stage. a: circuit diagram; b: input and output waveforms.  $(C_0 / C = 4)$

resetting the output voltage in every clock phase, so that the op-amp does not have to slew drastically during each clock transition. The circuit compensates the op-amp offset voltage  $V_{os}$  and provides reduced sensitivity to the finite dc gain A of the op-amp when the input signal frequency is much lower than the clock frequency. Analysis reveals that the output during the holding phase is

$$v_{out}(z) \approx \frac{1 - \mu \cdot C/C_o}{1 + \mu \cdot (1 - z^{-1} - z^{-1} \cdot C/C_o)} \cdot v_{in}(z) + \mu \cdot V_{os}(z).$$

(3.1)

where  $\mu = 1/A$ . At low frequencies ( $z \approx 1$ ), if  $\mu$ ,  $C/C_0 \ll 1$ ,  $v_{out}$  follows  $v_{in}$  closely. However, if the input signal frequency is high, close to  $f_s/2$  ( $z \approx -1$ ), Eq. (3.1) indicates a gain error that is even greater than for an uncompensated circuit. This drawback stems from the absence of accurate tracking. As Figure 3.1b shows, the output voltage does not actually track the input during the tracking time interval when  $\phi_1$  is high. In fact, the output voltage changes in a direction opposite to that of the actual input signal with a gain  $C/C_0$ . It undertakes a voltage jump  $C/C_0 \cdot [v_{in}(n) - v_{in}(n-1/2)]$  during the nth transition from HOLD to TRACK, and a voltage jump  $(1 + C/C_0)[v_{in}(n) - v_{in}(n-1)]$  during the nth transition from TRACK to HOLD. This reduces both the speed and the available swing during the operation. Increasing  $C_0/C$  will slightly ease this problem at the cost of larger silicon area and slower slewing and settling when the circuit enters the HOLD mode.

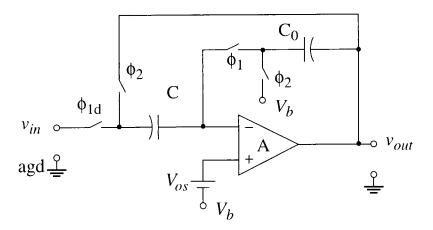

### 3.1.2. Predictive CDS Track-and-Hold Stage

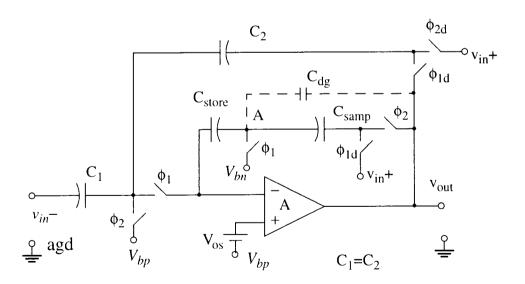

Having identified the problem of the gain- and offset-compensated T/H in Figure 3.1, a straightforward improved circuit is shown in Figure 3.2. The input signal is sampled using a delayed-cutoff clock signal  $\phi_{1d}$  to reduce the signal-dependent clock feedthrough noise. The operation of the stage is as follows. When  $\phi_1$  goes high, the circuit enters the TRACK mode:  $v_{out}$  changes from the earlier held value of  $v_{in}$  to the present input voltage and tracks it. During the interval when  $\phi_1$  remains high,  $v_{out} = v_{in}$  is valid under

ideal conditions. As  $\phi_2$  goes high and the HOLD interval begins, the input capacitor  $C_1$  is therefore precharged to a voltage

$$v_{c_1} = v_{in} - V_{os} + v_{in}/A. (3.2)$$

As Eq. (3.2) shows, when  $\phi_2$  goes high and the left-side terminal of  $C_1$  is switched to the output node, the output voltage becomes

Figure 3.2: Predictive gain- and offset-compensated T/H. a: the circuit configuration; b: the input and output signal waveforms.

$$v_{out} = V_{os} - v_{out}/A + v_{c1} = v_{in}(1 + 1/A) - v_{out}/A$$

(3.3)

This gives  $v_{out} = v_{in}$ . Thus, even in the presence of finite gain and nonzero offset of the opamp, the held value of the output voltage is identical to the input signal sampled at the time instant when  $\phi_{1d}$  went low.

The operation described above does not depend on having a high oversampling ratio, and hence the circuit is inherently suitable for high-frequency applications. However, the derivation assumed that  $v_{out} = v_{in}$  holds exactly during tracking. In fact,  $V_{os}$  and A do affect the tracking output slightly, as a more exact analysis reveals. Assuming  $C_1 = C_f = C_2 / 2 = C$ , the z-transform of the T/H output when  $\phi_2 = 1$  is then found to be

$$V_{out}^{(2)}(z) = \frac{1}{1 + (4 + z^{-1})/(A(A+5))} V_{in}(z) + \frac{V_{os}(z)}{A+5+(4+z^{-1})/A}.$$

(3.4)

If  $A \gg 5$ ,  $v_{out}^{(2)}$  can be approximated by

$$V_{out}^{(2)}(z) \approx \frac{V_{in}(z)}{1 + (4 + z^{-1})/A^2} + V_{os}(z)/A.$$

(3.5)

Thus, the error terms due to the finite gain and the nonzero offset are both reduced by a factor 1/A, thanks to the predictive correlated double sampling (CDS) used in the circuit. (The error in  $v_{out}^{(1)}$  is only the op-amp input-referred error of  $v_{out}^{(2)}$ !) The mismatch between the capacitors which are nominally equal to C and C also affects the compensation. However, this effect is usually negligible, since it only appears during the tracking mode, and hence the error which it causes in the held signal is second-order small. Unlike in earlier T/Hs, the error in the output given in Eq. (3.5) changes only slightly with frequency, so the speed limitation of the stage is mainly due to the unavoidable settling time of the op-amp.

The circuit of Figure 3.2 is easily converted to a more practical fully-differential operation, which also makes the voltage inversion used in the single-ended circuit unnecessary (Figure 3.3). In Figure 3.3,  $V_{com}$  is the desired common-mode input voltage of the op-amp. In the circuit, we also included two "deglitching" capacitors  $C_{dg1}$  and  $C_{dg2}$ , which provide feedback for the op-amp during the time interval when the non-overlapping clock phases  $\phi_1$  and  $\phi_2$  are both low [20], and hence reduce the sharp voltage spikes ("glitches") which would otherwise be generated during this interval. Since the switches at the input are opened by  $\phi_{1d}$  somewhat earlier later the other switches operated by  $\phi_1$ , the clock-feedthrough noise becomes nearly signal-independent and is thus suppressed by the op-amp common-mode rejection.

Figure 3.3: Fully-differential track-and-hold circuit.

The proposed T/H stages can also be converted into the more commonly used S/H stage by cascading a master and a slave T/H, or by using the "ping-pong" architecture shown in Figure 3.4. Here, the two T/H stages operate in tandem, and the output voltage

Figure 3.4: S/H stage using two T/H blocks.

Figure 3.5: Fully-differential track-and-hold circuit with improved switching scheme.

$v_{out}$  contains only the held outputs. This operation requires two T/H circuits, but it doubles the effective sampling rate. Since both stages have very accurately controlled voltage gains  $A_v = 1$ , and both have very little offset and finite-gain errors, the mismatch error usually present in ping-pong structures is likely to be negligible in most applications. However, the MOS switch clock-injection mismatch between the channels may introduce a fixed tone at  $f_s$ , as will be shown later in Sec. 3.1.3.

Figure 3.5 shows an improved switching scheme for the proposed T/H stage. An improvement in speed and accuracy is achieved by precharging all capacitors appropriately during the HOLD mode. This is achieved by splitting each of the input tracking capacitors  $C_2$  and  $C_3$  of Figure 3.3 into two equal-value capacitors ( $C_3 - C_6$  in Figure 3.5) and using them differently. Consider the transition into the tracking mode, which is the critical part of the operation. When  $\phi_1$  goes high,  $C_1$  sends a charge  $q_1 = C_1 \left[ v_{in}(n) - v_{in}(n-1) \right]$  into node A. This is now balanced by an equal but opposite charge through  $C_4$ . Since  $C_{f1}$  was precharged to  $v_{in}(n)$  during the hold interval when  $\phi_2 = 1$ , and since  $C_3$  (which is precharged to  $-v_{in}(n)$ ) does not contribute charge to node A when  $\phi_1 \rightarrow 1$ , the capacitors need not be charged by the op-amp to achieve  $v_{out}(n) = v_{in}(n)$ , when  $\phi_1$  goes high. This reduces the slewing as well as the settling time of the op-amp when tracking is resumed.

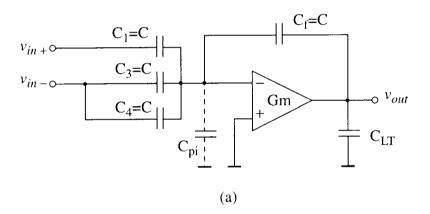

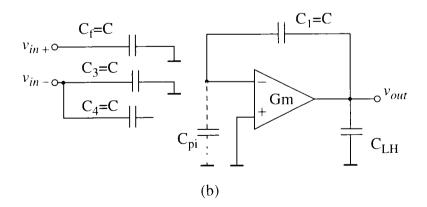

Next, we consider the speed requirements for the op-amp. Figure 3.6 shows the circuit configurations of the T/H of Figure 3.5 during both clock phases. They will be used to calculate the op-amp's settling time constants during the track and hold operations. For simplicity, only half of the fully-differential circuit is shown. The parasitic capacitances at the OTA input are denoted as  $C_{pi}$ , and the capacitive loads at the op-amp output during tracking and holding are denoted as  $C_{LT}$  and  $C_{LH}$ , respectively. Without loss of generality, a single-stage OTA is assumed, with its dominant pole residing at the output node. Let the

transconductance of the OTA be Gm, then the settling time constant during tracking phase can be obtained as

$$\tau_{track} = \frac{(3C + C_{pi}) + C_{LT}/\beta_{track}}{Gm},$$

(3.6)

where  $\beta_{track}$  is the op-amp feedback factor during the track phase, defined as

$$\beta_{track} = \frac{C_f}{C_f + C_1 + C_3 + C_4 + C_{pi}} \approx \frac{1}{4}.$$

(3.7)

Similar analysis for the holding phase yields

Figure 3.6: Op-amp capacitive load for the circuit in Figure 3.5. a: during tracking; b: during holding.

$$\tau_{hold} = \frac{C_{pi} + C_{LH} \cdot (1 + C_{pi}/C)}{Gm}$$

(3.8)

It should be noted that in most T/H applications (such as a front stage in a flash ADC), the op-amp's capacitive load during the track phase  $(C_{LT})$  is usually much smaller than that during the hold phase  $(C_{LH})$ . Equalizing  $\tau_{tack}$  and  $\tau_{hold}$  can be easily achieved by optimizing the values of C,  $C_{LT}$  and  $C_{LH}$ . The speed of tracking, nonetheless, is greatly affected by the small feedback factor during tracking as Eq. (3.7) shows. Also, because the input signal is sampled on  $C_1$  between input  $v_{in}$  and the op-amp virtual ground, slow opamp settling during tracking directly affects the accuracy of the signal being sampled.

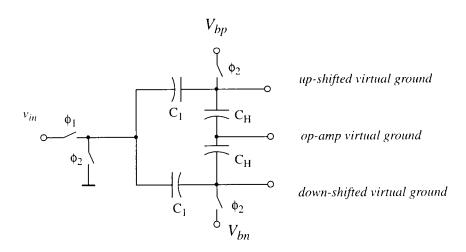

To alleviate these problems, the T/H stage can be further modified as shown in Figure 3.7. Delayed cut-off clock signals  $\phi_{1d}$  and  $\phi_{2d}$  are used to reduce the signaldependent charge-injection noise. The circuit uses a capacitor  $C_{store}$  to store the error voltage  $(V_{os} + V_{out}/A)$  at the op-amp input terminal during the tracking. Also during the tracking phase (Figure 3.7b),  $C_1$  and  $C_2$  together with the op-amp forms an inverting unitygain stage. (Assuming  $C_1 = C_2$  and neglecting the small amount of charge entering  $C_{store}$ .) Interchanging the two terminals of the differential input signal, the op-amp output  $v_{out}$  is actually equal to  $v_{in}$  without being inverted. Meanwhile,  $C_{samp}$  samples the input signal referred to the analog ground, rather than the op-amp virtual ground as in the circuit of Figure 3.5. Next, when  $\phi_2$  goes high and the circuit enters its hold phase,  $C_{samp}$  is switched in series with  $C_{store}$  and acts as the feedback capacitor in the unity-feedback configuration. At the same time,  $C_1$  and  $C_2$  are precharged to  $-v_{in}$  and  $+v_{in}$ , respectively, so that the opamp does not have to provide the slewing current for them when tracking resumes in the next clock phase. Notice that the feedback factor during tracking is now increased to approximately 1/3, which means that the settling is faster than that of the circuit in Figure 3.5.

The kT/C noise in the held output now contains the noise from the two switched capacitors  $C_{samp}$  and  $C_{store}$ . However, since  $C_1$  and  $C_2$  now can be smaller than  $C_{samp}$ , to

Figure 3.7: A predictive gain- and offset-compensated T/H using an error storage capacitor. a: the basic circuit; b: circuit configuration during tracking; c: circuit configuration during holding.

achieve the same dynamic range, the penalty from increased capacitor area and op-amp capacitive load should not be significant. Detailed analysis of the kT / C noise in this circuit is given in Appendix A.

The circuit of Figure 3.7a has a capacitive load about 3C at the input nodes during the track mode. This may impose some added driving requirements on the signal source. To alleviate this problem, an alternative circuit may be used (Figure 3.8). In Figure 3.8,  $C_1$  and  $C_2$ , instead of being precharged to  $v_{in}$  during the hold phase  $(\phi_2)$ , remain at the voltage of the previous sample  $v_{in}(n-1)$ . When next  $\phi_1$  goes high, a charge  $C_1[v_{in}(n) - v_{in}(n-1)]$  enters  $C_2$ , so that the output tracks the input as in the circuit of Figure 3.7a. The disadvantage of this circuit is the slewing requirement for the op-amp at the beginning of each tracking phase.

The finite-gain compensation of the correlated-double-sampling circuits described is achieved by sampling the error voltage  $(v_{out}/A, \text{ or } f^{-1}[v_{out}])$  in general at the op-amp

Figure 3.8: An alternative predictive GOC T/H.

input node during one clock phase, and then subtracting this error voltage from the output during the next clock phase. In particular, predictive CDS circuits sample the error voltage

Figure 3.9: High-speed T/H with a self-settling phase. a: the circuit; b: the clock signals; c: circuit configuration during self-settling interval ( $\phi_3$  is low).