## AN ABSTRACT OF THE THESIS OF

| ARTHUR GRAYSON ALBIN for the DOCTOR OF P  | HILUSUPH I   |

|-------------------------------------------|--------------|

| (Name) (Degr                              | ee)          |

| (ivaine)                                  |              |

| in OCEANOGRAPHY presented onMarch         | 14, 1968     |

| (Major)                                   | (Date)       |

| (IVIA) OI )                               |              |

| Title: THE ANALYSIS AND RECOMMENDED DESIG | N OF A HIGH- |

| Title. Till Mivitalions 1200              |              |

| RESOLUTION DIGITAL DATA ACQUISITION       | SYSTEM FOR   |

| RESOLUTION DIGITAL                        |              |

| THE IN SITU MEASUREMENT OF VARIOUS 1      | PHYSICAL AND |

|                                           |              |

| CHEMICAL PARAMETERS OF SEA WATER          |              |

| Redacted for Privacy                      |              |

| Abstract approved:                        |              |

| Stephen J. Neshyba                        | _            |

| Redacted for Privacy                      |              |

| C # 0 - C - 7 / //                        |              |

| Harry Freund                              |              |

|                                           |              |

The lack of availability of a single, complete paper on the analysis of a digital data acquisition system for in situ oceanographic measurements brought about the present work. In order to compile an accurate technical paper on such a complex system, it was necessary to design, construct, and calibrate a system for the in situ measurement of various physical and chemical properties of sea water.

A unique digital encoding circuit was developed which utilizes the basic principles of null balance, resistance ratio bridge and potentiometer measurements. The circuit is a uniquely loaded binary ladder resistance network. Variation of the loading allows resistance

ratio and potentiometric measurements to be made over different ranges with a constant high degree of resolution.

The developed system has the capability of measuring any parameter which can be converted into a varying voltage, current, or resistance. The range over which the measurement can be made is adjustable; and the resolution equals  $\pm 0.006\%$  of the full range value. The resolution is constant over the full range, as a result of the analog-to-digital converter linearity characteristics.

The Analysis and Recommended Design of a High-Resolution Digital Data Acquisition System for the in situ Measurement of Various Physical and Chemical Parameters of Sea Water

bу

Arthur Grayson Albin

A THESIS

submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

June 1968

| PPROVED:<br>Redacted | for Privacy                                  |

|----------------------|----------------------------------------------|

| Associate            | Professor of Oceanography in charge of major |

| Redact               | ed for Privacy                               |

| Professor            | of Chemistry in charge of major              |

| Redacted for         | r Privacy                                    |

| Charman              | of Department of Oceanography                |

|                      | Redacted for Privacy                         |

| Dean of C            | Graduate School                              |

Date thesis is presented \_\_\_\_\_\_ March 14, 1968

Typed by Gwendolyn Hansen for Arthur Grayson Albin

### ACKNOW LEDGMENTS

This research was performed under the joint direction of Dr. Harry Freund and Dr. Stephen J. Neshyba. I am grateful to Dr. Freund and Dr. Neshyba for their guidance and assistance throughout this work.

Professor Robert R. Michael and Dr. Kilho Park are to be thanked for their many valuable suggestions.

To the other members of the graduate committee, Dr. W. V. Burt, Dr. June G. Pattullo, Dr. R. L. Smith, and Dr. E. J. Dornfeld, I would like to extend my sincere appreciation.

To my wife, Inga, for her continued encouragement and assistance without which this thesis may never have been written, I am so grateful.

It is to be acknowledged that technical information supplied by Mr. Alec M. Dingee of the Geodyne Corporation has made this investigation possible.

This research was supported by the Navy Office of Naval Research under Contract NONR 1286(10).

# TABLE OF CONTENTS

|                                                    | Page |

|----------------------------------------------------|------|

| INTRODUCTION                                       | 1    |

| HISTORICAL                                         | 4    |

| METHOD OF APPROACH                                 | 8    |

| Typical Digital System                             | . 8  |

| Need for System Analysis                           | 10   |

| Selected Approach                                  | 11   |

| Converter Operation                                | 13   |

| Transducers Considered                             | 15   |

| Unique Loaded Ladder Circuit                       | 16   |

| Resistance Conversion Equation                     | 17   |

| Voltage Conversion Equation                        | 18   |

| Type of Circuits Used                              | 19   |

| FOUR-BIT ANALOG-TO-DIGITAL CONVERTER               |      |

| PROTOTYPE                                          | 21   |

| General Description                                | 21   |

| Clock Generator                                    | 23   |

| A-Counter                                          | 27   |

| "Set" Gates                                        | 27   |

| "Clear" Gates                                      | 33   |

| Reset Logic                                        | 33   |

| D-Register                                         | 36   |

| Neon Lamp Indicator                                | 36   |

| Difference Amplifier                               | 40   |

| Comparator                                         | 42   |

| Reference Voltage Source                           | 44   |

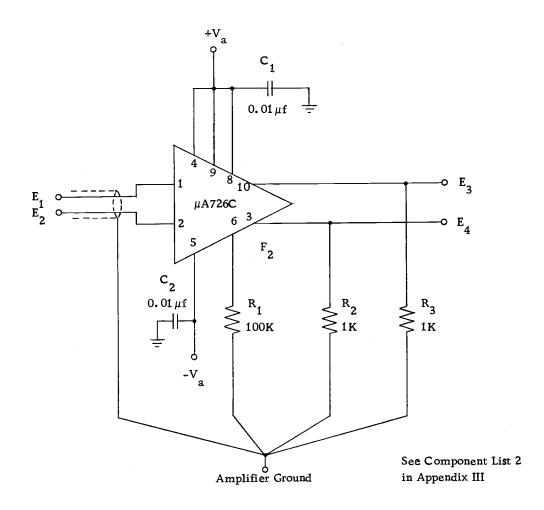

| Input Circuit                                      | 46   |

| Resistive Network and Relays                       | 48   |

| Balancing Sequence Example                         | 50   |

| FOURTEEN-BIT DIGITAL DATA ACQUISITION SYSTEM       | 54   |

| Rechargeable Battery Supply and Voltage Regulators | 54   |

| Fourteen-Bit Analog-to-Digital Converter           | 59   |

| Start Command Generator                            | 60   |

| Clock Generator                                    | 63   |

|                                            | Page |

|--------------------------------------------|------|

| Reset Logic                                | 63   |

| A-Counter                                  | 67   |

| "Set" Decode Matrix                        | 67   |

| "Clear" Matrix                             | 67   |

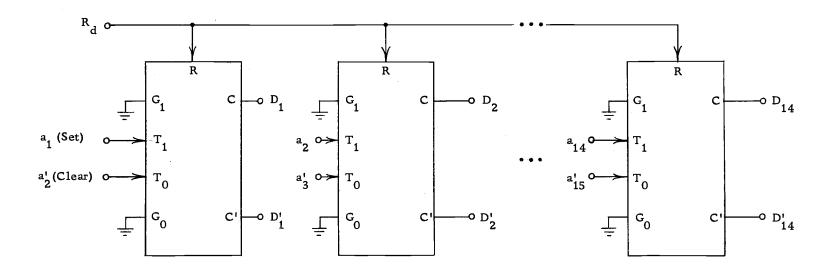

| D-Register                                 | 70   |

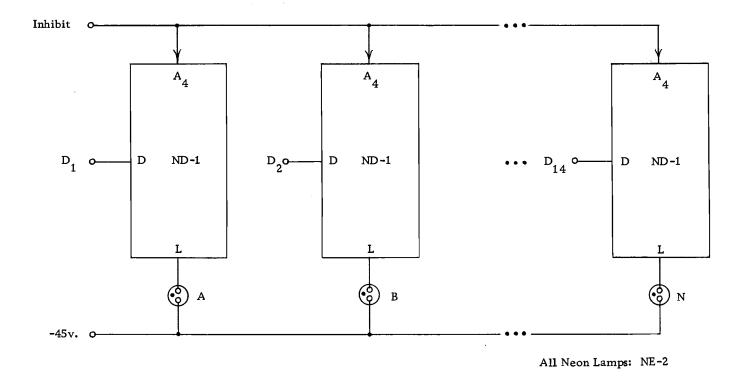

| Neon Lamp Indicator                        | 70   |

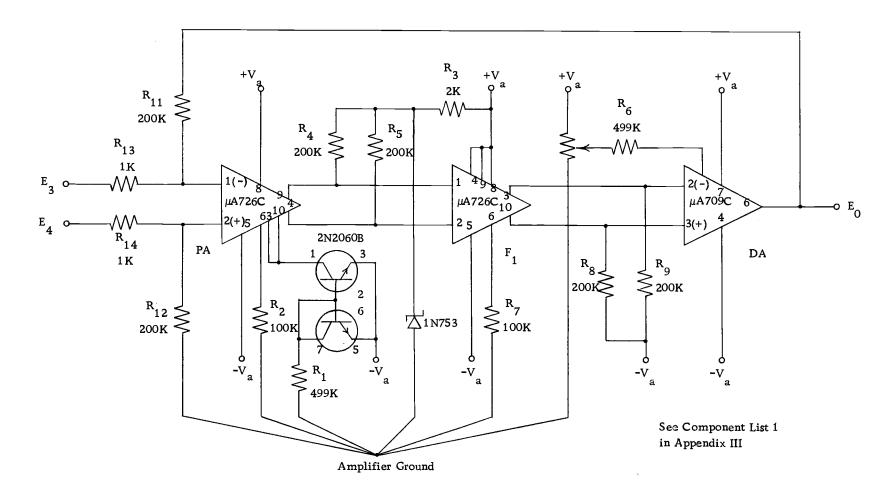

| Difference Amplifier                       | 70   |

| Comparator                                 | 76   |

| Precision Reference Voltage Source         | 76   |

| Precision Binary Ladder Network and Relays | 80   |

| Low-Level Scanner                          | 82   |

| Programmer                                 | 82   |

| Low-Level Relays                           | 84   |

| Range-Setting Load Resistors               | 88   |

| Transducers                                | 94   |

| Temperature                                | 94   |

| Pressure                                   | 94   |

| Oxygen                                     | 95   |

| DATA AND CALCULATIONS                      | 96   |

| Measured Values for C <sub>s1</sub>        | 100  |

| Measured Values for D <sub>s1</sub>        | 100  |

| Calculated Value for C <sub>s1</sub>       | 101  |

| Calculated Value for D <sub>s1</sub>       | 102  |

| DISCUSSION AND CONCLUSION                  | 103  |

| BIBLIOGRAPHY                               | 105  |

| APPENDIX I. Equations and Symbols          | 108  |

| a. Digital Logic                           | 108  |

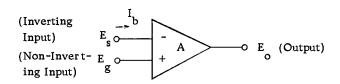

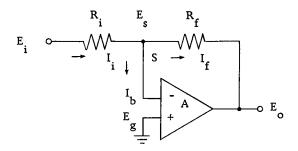

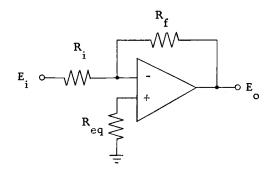

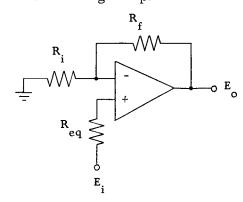

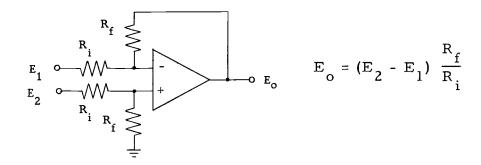

| b. Analog Operational Amplifiers           | 110  |

| APPENDIXII. a. Low-Level Reed Relay        | 115  |

| b. Calculation of R <sub>s1</sub>          | 115  |

| APPENDIX III. Component Lists              | 119  |

# LIST OF TABLES

| Table                                                           | Page |

|-----------------------------------------------------------------|------|

| 1. Calibration Data for $R_b = 100.067 \Omega$                  | 98   |

| 2. Calibration Data for $R_b = 500.15 \Omega$                   | 99   |

| 3. Measured and Calculated Values for $C_{410}$ and $D_{410}$ . | 103  |

## LIST OF FIGURES

| Figure |                                                                                 | Page       |

|--------|---------------------------------------------------------------------------------|------------|

| 1.     | Block Diagram of a Typical Digital Measuring System.                            | 9          |

| 2.     | Basic Block Diagram of A/D Converter in Resistance Ratio Bridge Operating Mode. | 12         |

| 3.     | Basic Block Diagram of A/D Converter in Potentiometer Operating Mode.           | 14         |

| 4.     | Block Diagram of Four-Bit Analog-to-Digital Converter Prototype.                | 22         |

| 5.     | Prototype Clock Generator.                                                      | 24         |

| 6.     | Astable Multivibrator Circuit, MV-2.                                            | 25         |

| 7.     | Bistable Multivibrator Circuit, FF-2.                                           | 26         |

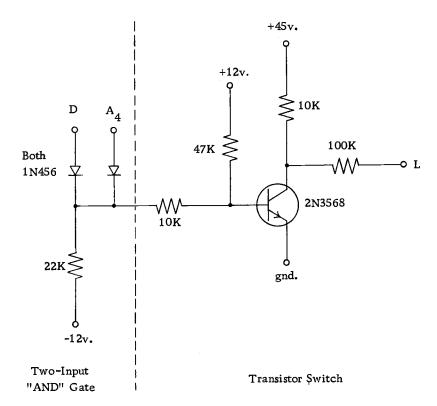

| 8.     | Three-Input Transistor "AND" Gate Circuit, CG-1.                                | 28         |

| 9.     | Prototype A-Counter.                                                            | <b>2</b> 9 |

| 10.    | Prototype Clock Generator and A-Counter Timing Diagram.                         | 30         |

| 11.    | Diode "Set" and "Clear" Gates.                                                  | 31         |

| 12.    | Diode "Set" and "Clear" Gate Circuit, DL-2.                                     | 32         |

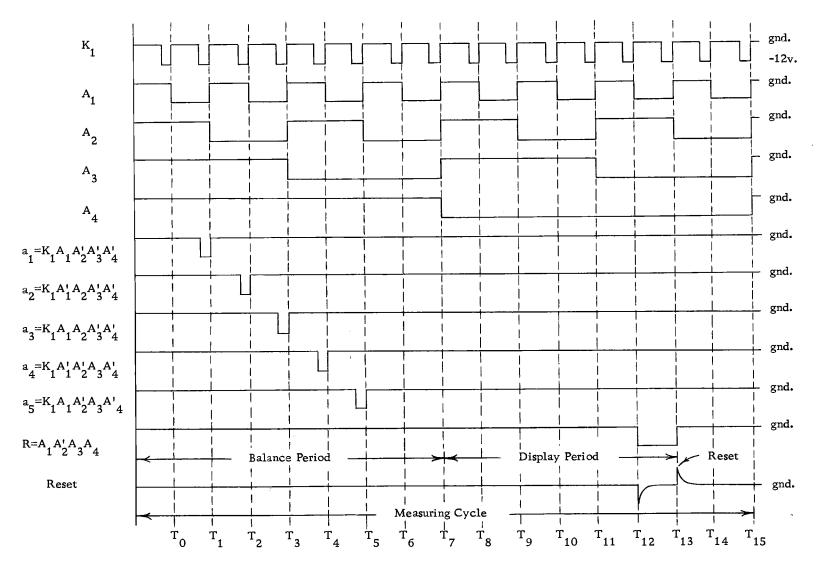

| 13.    | Prototype Diode "Set" and Reset Logic Timing Diagram.                           | 34         |

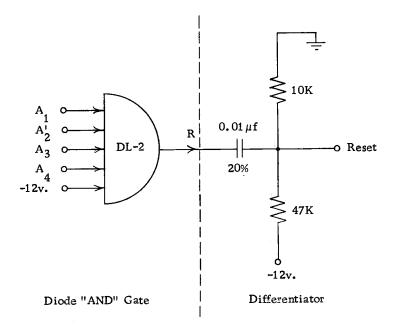

| 14.    | Prototype Reset Logic Circuit.                                                  | 35         |

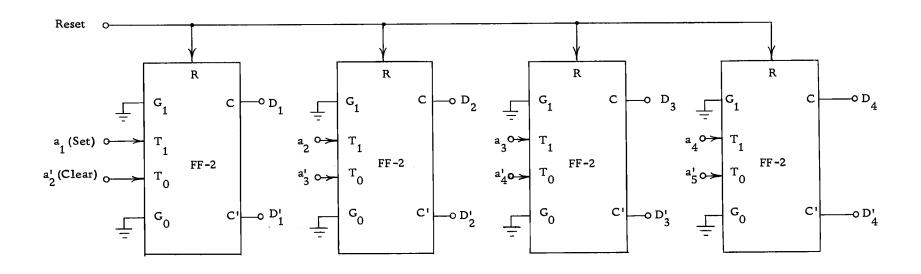

| 15.    | Prototype D-Register.                                                           | 37         |

| 16.    | Prototype Neon Lamp Indicator.                                                  | 38         |

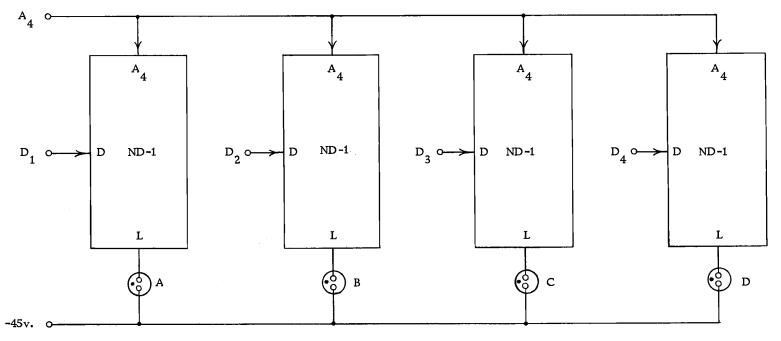

| 17     | Neon Lamp Driver Circuit, ND-1.                                                 | 39         |

| Figure       |                                                                               | Page       |

|--------------|-------------------------------------------------------------------------------|------------|

| 18,          | 8. Prototype Difference Amplifier.                                            |            |

| 19.          | Prototype Comparator.                                                         | 43         |

| 20.          | Prototype Reference Voltage Source.                                           | 45         |

| 21.          | Prototype Resistive Network and Relays.                                       | 49         |

| 22.          | Prototype Balancing Sequence Timing Diagram.                                  | 51         |

| 23.          | Block Diagram of Fourteen-Bit Digital Data<br>Acquisition System.             | 55         |

| 24.          | Block Diagram of Rechargable Battery Supply and Amplifier Voltage Regulators. | 56         |

| 25.          | Amplifier Voltage Regulators.                                                 | 58         |

| 26.          | Start Command Generator.                                                      | 61         |

| 27.          | "NAND" Gate Circuit, AN-1.                                                    | 62         |

| 28.          | Clock Generator.                                                              | 64         |

| <b>2</b> 9.  | Clock Generator and Reset Logic Timing Diagram.                               | 65         |

| 30.          | Reset Logic Circuit.                                                          | 66         |

| 31.          | Diode "Set" Decode Matrix.                                                    | 68         |

| 32.          | Diode "Clear" Matrix.                                                         | 69         |

| 33.          | D-Register,                                                                   | 71         |

| 34.          | Neon Lamp Indicator.                                                          | 72         |

| 35,          | Temperature Stabilized Difference Amplifier.                                  | 74         |

| 36.          | Temperature Stabilized Differential Follower.                                 | 75         |

| 3 <b>7</b> . | Comparator and Comparator Amplifier.                                          | 77         |

| 38.          | Precision Reference Voltage Source.                                           | <b>7</b> 9 |

| Figu | re                                                               | Page |

|------|------------------------------------------------------------------|------|

| 39.  | Precision Binary Ladder Network and Relays.                      | 81   |

| 40.  | Low-Level Scanner.                                               | 83   |

| 41.  | Programmer B-Counter.                                            | . 85 |

| 42.  | Programmer Decode Logic.                                         | 86   |

| 43.  | Low-Level Multiplexer and Transducers.                           | 87   |

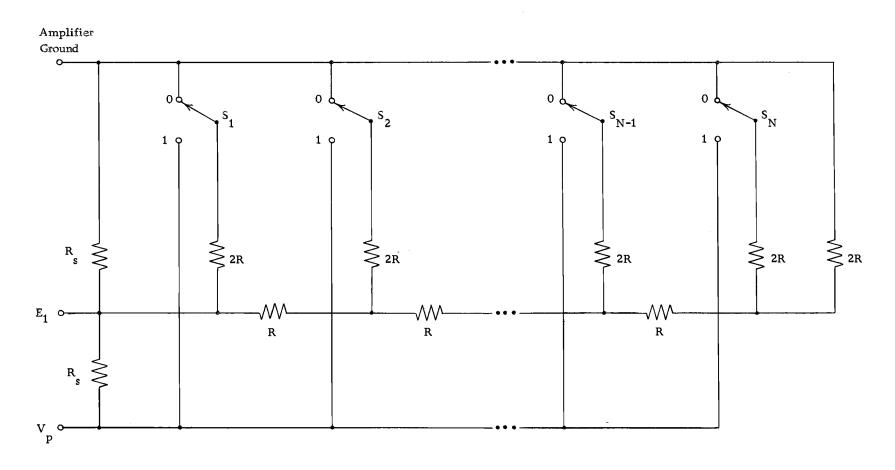

| 44.  | Binary Ladder Network with Range-Setting Load Resistors, $R_s$ . | 89   |

| 45.  | Low-Level Reed Relay.                                            | 116  |

THE ANALYSIS AND RECOMMENDED DESIGN OF A HIGH-RESOLUTION DIGITAL DATA ACQUISITION SYSTEM FOR THE IN SITU MEASUREMENT OF VARIOUS PHYSICAL AND CHEMICAL PARAMETERS OF SEA WATER

#### INTRODUCTION

The many physical and chemical properties of each parcel of sea water in an ocean should be measured continuously and accurately if one is to completely understand the ocean environment. This requirement was almost impossible to attain until the recent advent of digital measuring systems capable of making numerous, highly accurate measurements at an extremely high rate. Oceanographers, unfortunately, have not been able to help in the development or improvement of such systems, as they have difficulties in communicating with the developers. In part, this has been due to the lack of availability of a complete analysis on a digital measuring system from which an oceanographer could attain a basic understanding of this type of data acquisition. An objective of this thesis is to make available, for general use, an analysis of such a system.

Oceanographic in situ measurements are made in a remote and hostile environment. To obtain accurate data at a sufficiently high sampling rate, the analog data is best converted into a digital format by an in situ measuring and encoding system. Invariably, the digital measuring system consists of a transducer to convert the parameter

being measured into an electrical signal, an analog-to-digital converter to encode the analog transducer signal into a digital form, and a display or recorder to monitor or store the digital data.

The analog-to-digital converter and its digital encoding circuitry are the heart of a digital measuring system. The accuracy and stability of the digital data are directly influenced by the characteristics of the analog-to-digital converter. The encoding circuitry and technique are determined, in part, by the type and magnitude of transducer signals to be encoded. This indicates that it is quite important to consider the transducer characteristics along with the analog-to-digital converter, when a digital measuring system is being analyzed or designed. Furthermore, encoding techniques require a finite amount of time to obtain a single measurement, thus making a digital measuring system inherently discontinuous in its method of measurement. To define all variables in both space and time, a digital measuring system should have a sufficiently high sampling rate. Measurements thus obtained are considered to be discretely continuous, as opposed to the continuous measurements obtained by an analog measuring system which does not utilize timesharing multiplexing techniques.

Oceanographers need real-time information concerning ocean parameters, both at the surface and at depth. When the total expanse of an ocean is taken into consideration, only high speed digital

measuring, telemetering, and computing techniques are capable of performing such a feat. It is, therefore, quite important that oceanographers become proficient in the methods of digital data acquisition.

The availability of a complete analysis of a digital measuring system for oceanographic in situ measurements would allow an oceanographer to become familiar with this method of data acquisition and to interact productively with electronic instrument developers. The generation, analysis, and documentation of a digital measuring system is the purpose of this investigation.

#### HISTORICAL

In 1948, Jacobson (14, p. 714) published a paper on an instrument for the continuous recording of salinity, temperature, and depth in sea water, which he developed at the Woods Hole Oceanographic Institute. His instrument did not require the use of any encoding or signal multiplexing techniques, as the resistive transducers were directly coupled through a nine conductor cable to separate shipboard servo-recorders. Pritchard (22, p. 146), Alexiou (1, p. 46), and LaFond (15, p. 137) similarly used a multiconductor cable and direct transducer coupling in their continuous in situ analog measuring systems.

This method of <u>in situ</u> data gathering is hampered by the need for an expensive multiconductor cable; and the accuracy of the data is less than that normally required, due to such factors as variable line resistance, slip-ring noise, and analog recorder inaccuracies (16, p. 36).

The following discretely continuous measuring systems were developed using time-sharing multiplexing and FM modulation techniques. Hamon (12, p. 72), in Australia, reported in 1955 on the use of a single conductor cable in connection with his temperature-salinity-depth recorder. He used a method of time-sharing multiplexing and FM telemetry to sequentially sample the transducers

and reference elements. The data, in the form of a single channel FM modulated carrier, was telemetered through a single conductor cable to a shipboard recording unit. Snodgrass (25, p. 142) reported in 1957 on the use of a single conductor cable in connection with the electronic bathythermometer, which he developed at Scripps Institution of Oceanography.

The following continuous measuring systems were developed using only FM modulation techniques. In 1962, Campbell (3, p. 53) and his associates at the Bendix/Pacific Corporation reported on a FM/FM modulation technique used in their multiple sensor acoustical telemetering system. Since 1963, the Hytech division of the Bissett-Berman Corporation, San Diego, California, has made available their FM modulated single-wire system for measuring "salinity", temperature, and depth in situ. The system is described by Brown (2, p. 26) in a paper discussing its application to the General Dynamics/Convair Monster Buoy Project (6, p. 8).

There are many advantages and disadvantages with regard to these last two FM methods of in situ data gathering and telemetry.

The most important advantage lies in the continuity of the measurements and the relative simplicity of the system. The most important disadvantages are a low but acceptable accuracy and a long measuring time to obtain the required level of accuracy.

A completely digital data acquisition system for making in situ

oceanographic measurements was first introduced around 1962 by the Geodyne Corporation of Waltham, Massachusetts (7). Their system involves the use of analog-to-digital conversion and time-sharing multiplexing techniques to make numerous in situ temperature measurements. This system was described in a short article explaining its application to a Woods Hole buoy project (21, p. 41). Recently, the Geodyne Corporation has made available an expanded system using the same measuring techniques to measure in situ conductivity (salinity), temperature, pressure (depth), and other physical and chemical parameters (8). This newer system is capable of telemetering the digital data over a single conductor coaxial cable to surface vessel or land based digital processing equipment. During 1966, the Amecom division of Litton Systems Incorporated, in Silver Springs, Maryland, made available a digital system for measuring in situ conductivity, temperature, and pressure (18). The system was described, in general, by Murdock (20) in his paper presented at the 1966 Northeast Electronics Research and Engineering Meeting. This digital system is also capable of telemetering the digital data over a single conductor cable.

In both of the two digital systems referred to above, the technical details regarding them are proprietary in nature and are not readily available. One is left to assess the relative value of the systems and their similar digital measuring technique from company

supplied specifications. One cannot always rely upon such information, as pointed out by Daulphinee (5, p. 748). However, it seems that this method of in situ data retrieval offers the highest degree of accuracy, resolution, stability, and ease of data transmission of any method developed to date. The systems do have, however, the disadvantages of extreme complexity and lack of truly continuous measurements due to the use of digital encoding and time-sharing multiplexing techniques.

In the past, work has been confined to the measurement of temperature, salinity, and pressure, as these are the parameters which are most important to density calculations. More recently, the non-conservative, as well as the conservative parameters have become important in budget studies. In situ data acquisition systems, which have been developed to date, have been oriented toward the measurement of conductivity (salinity), which is best performed by alternating current measuring techniques. Unfortunately, these measuring systems are not easily adapted to the measurement of non-conservative parameters, which are best measured by direct current measuring techniques. A system analysis of a digital measuring system allows one to select or develop a more universal method of digitization, which will accommodate a larger variety of measurable parameters.

## METHOD OF APPROACH

## Typical Digital System

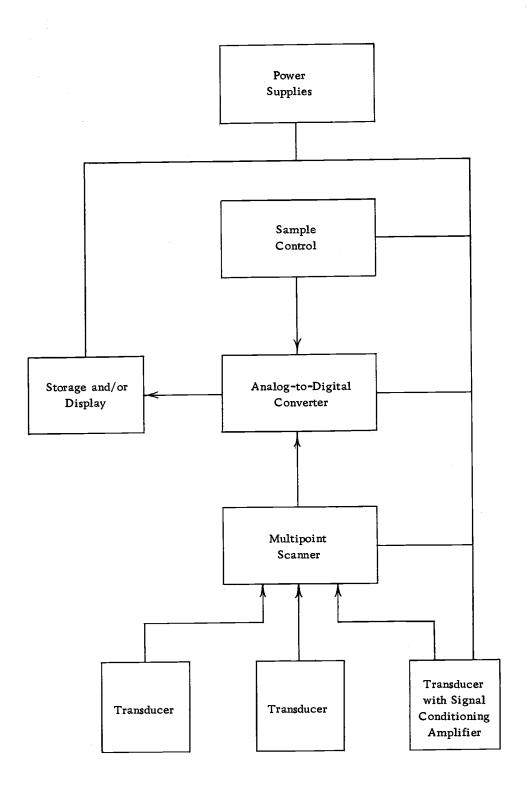

A typical digital measuring system consists of the following subsystems, as diagrammed in Figure 1: power supplies, sample control, analog-to-digital converter, storage and/or display, multipoint scanner, and transducers (some with signal conditioning amplifiers). The innerconnecting lines between the subsystems in the diagram are arrowed to indicate the path and direction of information flow.

The power supplies provide a set of stable voltages to each of the remaining subsystems. A sample control unit activates the analog-to-digital converter at a controllable rate, or at preset times, to start a sampling and measuring sequence. The storage and/or display section stores, records, and/or displays the digital data output of the analog-to-digital converter. Electrical analog signals, corresponding to the parameters being measured, are generated by the different transducers. The signals are sequentially fed to the analog-to-digital converter by a multipoint scanner. Once at the converter, an analog signal is encoded into a digital format. In any digital measuring system, it is important that the digital data be directly related to the analog data. It is desirable that this relationship be linear over the measuring range.

Figure 1. Block Diagram of a Typical Digital Measuring System.

## Need for System Analysis

A measuring system should be considered as a whole in order to attain the highest levels of measuring accuracy, stability, and reliability. In systems which are built up from standard subsystem units, the electrical connection between subsystems is often quite difficult to successfully make and match, and usually leads to total system degradation. When a measuring system can be analyzed and designed as a unit, the interfacing becomes quite natural; and total system performance is usually at its highest level.

By considering the measuring system as a whole, one can first look at the type and magnitude of transducer signals to be measured. When small signal variation transducers such as resistance thermometers and strain gauges are to be measured accurately, the transducer signal either should not be amplified before being encoded or a very stable amplifier must be used. If no amplification is used, the possible methods of encoding become limited. If the d.c. voltage and current outputs from electrochemical cells are to be measured also, the type of analog-to-digital conversion becomes even more restricted.

One approach in deciding upon the type of analog-to-digital conversion to be used would be to note the type of high accuracy laboratory measuring techniques which are ordinarily used in making

these measurements. Resistive transducers with small output variations are usually monitored by resistance ratio measuring techniques. Direct current voltage and current transducers are usually measured by potentiometric techniques. Both of these laboratory measuring techniques are null methods of measurement and utilize inherently accurate and stable resistive ratio networks. It is important to note that the highest degree of accuracy and stability of any standard laboratory method of measurement is attained through the use of direct comparison, null balance, ratio measurements. Therefore, an ideal analog-to-digital converter for making these measurements would be one which utilizes the direct comparison, null balance methods of resistance ratio bridge and potentiometer measurements.

## Selected Approach

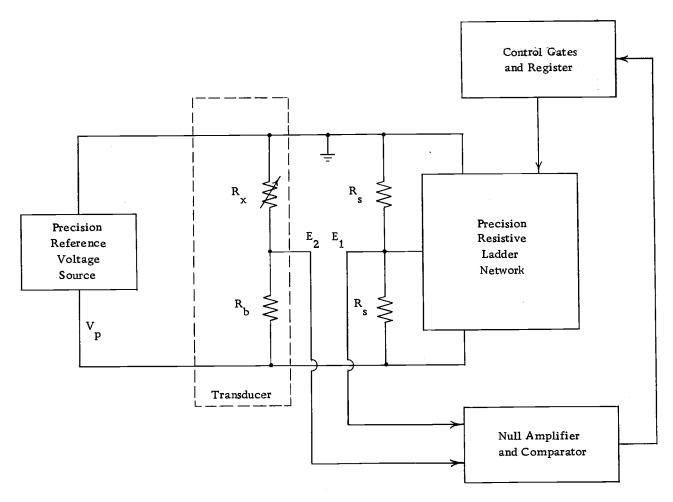

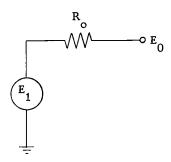

The analog-to-digital (A/D) converter, which was designed for this purpose, is unique in that it can be combined with appropriate transducers to form a combination self-balancing resistance ratio bridge or potentiometer. In either case, blanace is attained through the digitally controlled adjustments of a precision resistive ladder network. In the case of operation as a resistance ratio bridge (Figure 2), the precision ladder network forms the equivalent of two adjacent legs in a bridge circuit. Both legs formed by the ladder

Figure 2. Basic Block Diagram of A/D Converter in Resistance Ratio Bridge Operating Mode.

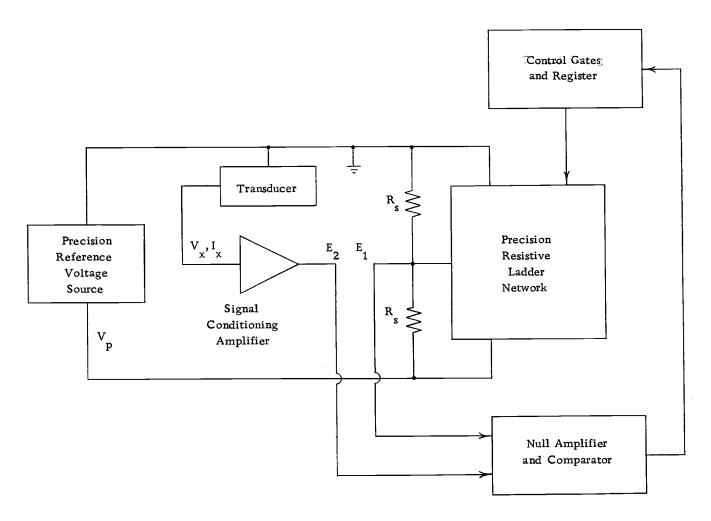

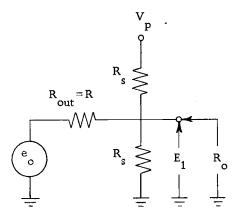

network are simultaneously adjusted to obtain bridge balance. In the potentiometric operating mode (Figure 3), the ladder network can be looked upon as a precision linear voltage divider. The voltage across the ladder network is held at a constant known value by a precision reference voltage source. Balance is attained when the network output voltage,  $E_1$ , equals the unknown voltage,  $E_2$ .

A direct current (d. c.) bridge circuit was chosen, contrary to the alternating current (a. c.) bridges used by others (2, 8, 20).

This decision was made in order to measure pure d. c. voltage and current outputs from electrochemical cells by a more direct method.

## Converter Operation

The block diagrams in Figures 2 and 3 show the innerconnection and information flow direction between the different units.

The precision resistive ladder network is the most important part

of the A/D converter. It is a set of precision resistors which are

perfectly matched to assure maximum accuracy and stability. The

precision reference voltage source maintains a constant voltage

across the ladder network, which is important during the potentiometric mode of operation. The null amplifier compares the known

voltage output of the ladder network with the unknown voltage being

measured. The comparator, driven by the null amplifier, directs

the control gates and register with "yes" or "no" logic signals, which

Figure 3. Basic Block Diagram of A/D Converter in Potentiometer Operating Mode.

in turn performs the necessary adjustments on the ladder network to bring about a null between the two voltages.

The converter uses the technique of successive approximation to obtain bridge or potentiometer balance. The following sequence of events is typical of a balancing cycle. The ladder network is first set to half-range by the control gates and register. The bridge or potentiometer output voltages are amplified and compared by the comparator to determine the overbalance or underbalance of the circuit. If the circuit is overbalanced ( $\mathbf{E_1} \!\! > \! \mathbf{E_2}$ ), the comparator generates a "yes" logic signal, which is fed back to the control register. This feedback signal then directs the second positioning of the ladder network to the one-quarter range position. If the circuit is underbalanced ( $\mathbf{E_1} \!\! < \! \mathbf{E_2}$ ), a "no" logic signal is developed; and the ladder network is set to the three-quarter range position. Continued comparison of the bridge or potentiometer voltages results in sequential adjustments of the ladder network by either plus or minus one-half of the preceding step until circuit balance is attained.

### Transducers Considered

The specific transducers to be considered in this investigation are a platinum resistance thermometer, a strain gauge pressure transducer, and a membrane polarographic oxygen cell. The first two fall into the category of resistive transducers with extremely

small output variations. The third is in the class of electrochemical cells with pure d.c. outputs.

As was pointed out earlier, a d. c. potentiometer is used to accomodate transducers similar to the oxygen cell. To measure the very small variations of transducers in the first category, a unique loaded ladder circuit was designed.

## Unique Loaded Ladder Circuit

This circuit is unique in that it utilizes two equal loading resistors,  $R_s$ , to set the voltage range over which the precision resistive ladder network output,  $E_1$ , will vary (Figure 2). The defining equation, which will be derived in a later section, relates the loaded ladder network output,  $E_1$ , with the analog-to-digital converter binary output, p. In its simplified form, the equation is:  $E_1 = A_s p + B_s$ , where  $A_s$  and  $B_s$  are constants. It is important that the equation is linear, as this will permit simplified data processing and assure constant sensitivity throughout the measuring range.

Since a direct comparison and null method of measurement is used, the binary output, p, which is the data in digital form, can be related to the parameter being measured by equating  $E_1$  with the transducer output,  $E_2$ .

The exact equation for  $E_1$  is:

$$E_1 = \frac{V_p}{2} \left[ 1 - \frac{R_o}{R} \left( 1 - \frac{p}{2^{N-1}} \right) \right]$$

where: p = Binary output

R = Characteristic output resistance of ladder network

R<sub>s</sub> = Range setting load resistance

$R_0 = \frac{RR_s}{R_s + 2R} = Constant for a particular range setting$

N = Number of stages in ladder network.

For a particular range setting where  $R_s$  is fixed, the equation reduces to the basic form:

$$E_1 = \frac{V_p^R_o}{2^N_R} p + \frac{1}{2} (1 - \frac{R_o}{R}) V_p$$

$$E_1 = A_s p + B_s$$

or

$$\frac{E_1}{V_p} = C_s p + D_s$$

where: A, B, C and D are constants for a particular range setting.

In the case of temperature measurement with a resistance thermometer, the thermometer element,  $R_{x}$ , is a function of temperature, while  $R_{b}$  as shown in Figure 2 is constant.

Therefore, the equation for E2 becomes:

$$E_2 = \frac{R_x}{R_x + R_b} V_p$$

where:  $R_{x} = f(T)$

V = Constant voltage from voltage source,

Upon equating the equation for  $E_2$  with that for  $E_1$ ,  $V_p$  cancels out and the conversion equation becomes:

$$\frac{R_x}{R_x + R_b} = C_T p + D_T$$

where:  $C_T$  and  $D_T$  are particular constants for the set temperature range.

Solving for  $R_{\mathbf{x}}$  in order to relate temperature with the binary output, p, gives:

$$R_{x} = R_{b}(C_{T}p + D_{T}) + R_{x}(C_{T}p + D_{T})$$

$$R_{x} = f(T) = \frac{R_{b}(C_{T}p + D_{T})}{1 - (C_{T}p + D_{T})}$$

## Voltage Conversion Equation

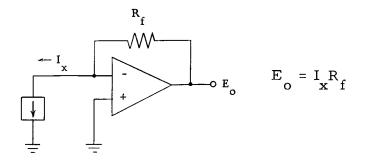

In the case of oxygen measurement with a polarographic cell,  $E_2 = I_x R_f = V_x$ , which is a function of the partial pressure of dissolved oxygen,  $O_2$ .  $R_f$  is a constant known resistance in the signal conditioning amplifier (Appendix Ib).

Upon equating  $E_1$  to  $E_2$ , the conversion equation becomes:

$$V_{x} = I_{x}R_{f} = f(O_{2}) = A_{O}p + B_{O}$$

where: A and B are particular constants for the set oxygen range.

The relationship between T and  $R_x$ ,  $O_2$  and  $V_x$  are found by the calibration of the particular transducers. System calibration then gives the high resolution calibration between the digital data output, p, and T,  $O_2$ , or any other measurable parameter which can be converted into a resistance, current, or voltage.

### Type of Circuits Used

The electronic circuitry of the digital control section in this system is the same as that used by the Geodyne Corporation in their Model 605 digitizer. The space requirements of the control section have been reduced to a minimum through the use of "cordwood" packaging techniques.

At the time the control section was assembled, digital integrated circuits were not available in low-cost units. The use of such units could reduce the space requirements even further. Linear integrated circuits have been used in the power supply voltage regulators,

voltage reference source, and null amplifier to give state-of-the-art sensitivity, stability, and size reduction.

# FOUR-BIT ANALOG-TO-DIGITAL CONVERTER PROTOTYPE

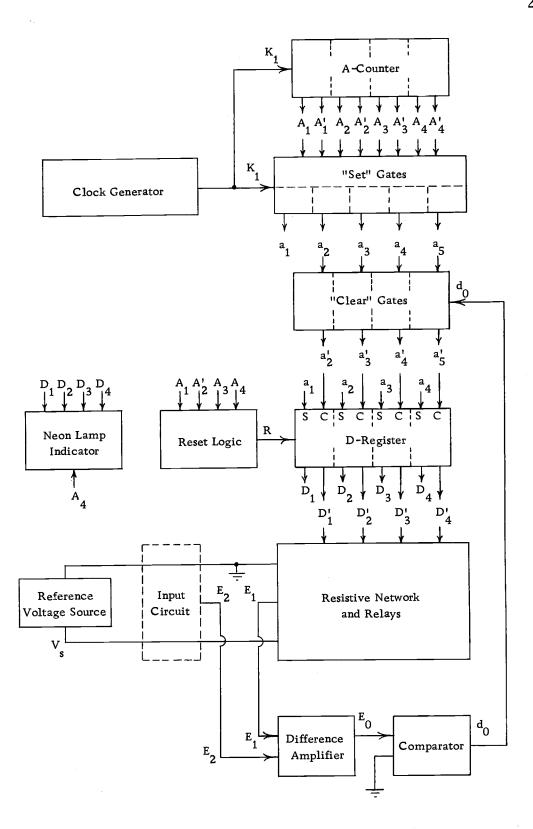

The diagram presented in Figure 4 shows the analog-to-digital converter in more detail. The figure is a block diagram of the fourbit A/D converter prototype. This prototype was designed and built to test the circuits and unique encoding technique which are to be used in the high resolution converter. A short description of the flow pattern between the individual blocks of Figure 4 is found below. A more detailed description of each block will then follow.

## General Description

The A-counter generates the signals  $A_1$ ,  $A_1$ , thru  $A_4$ ,  $A_4$  by counting the pulses of the clock generator output,  $K_1$ . The pulses in the  $K_1$  signal simultaneously activate the "set" gates in order to synchronize the operations of the two units.

The diode "set" gates produce the signals  $a_1 - a_5$  from the A-counter outputs,  $A_1$ ,  $A_1' - A_4$ ,  $A_4'$ . The signals  $a_1 - a_4$  are respectively fed to the "set" inputs of the four flip-flops in the D-register. The diode "clear" gates produce the signals  $a_2' - a_5'$  from the comparator output,  $d_0$ , and the set gate outputs,  $a_2 - a_5$ . Similarly, the signals  $a_2' - a_5'$  are respectively fed to the "clear" inputs of the four flip-flops in the D-register.

Figure 4. Block Diagram of Four-Bit Analog-to-Digital Converter Prototype.

The reset logic gate generates a reset signal, R, from the A-counter outputs, A<sub>1</sub>, A'<sub>2</sub>, A<sub>3</sub>, and A<sub>4</sub> to reset all flip-flops in the D-register. A reset pulse is generated after every cycle of the A-counter, which is also a complete bridge or potentiometer measuring cycle.

The neon lamp indicator displays the state of each flip-flop in the D-register after every balancing part of the measuring cycle. The inputs  $D_1$ - $D_4$  respectively activate the four lamp drivers. To reduce lamp flickering, the  $A_4$  input blanks all the lamps during the balancing sequence and displays the state of  $D_1$ - $D_4$  after the balancing part of the measuring cycle has taken place (Figure 13).

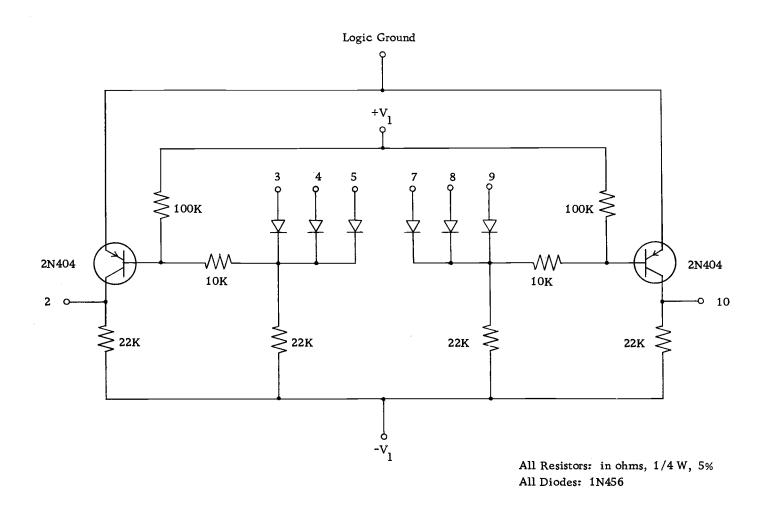

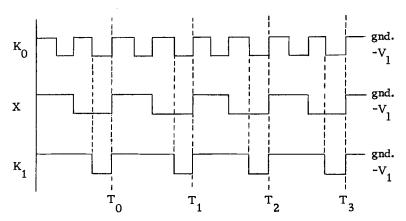

## Clock Generator

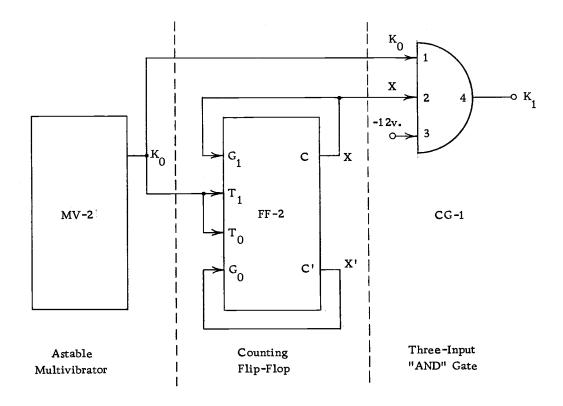

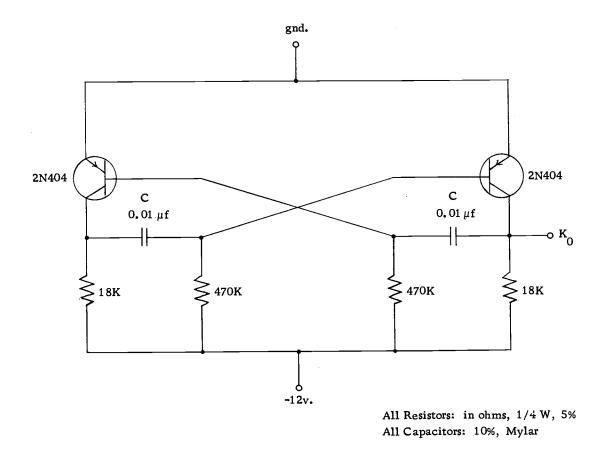

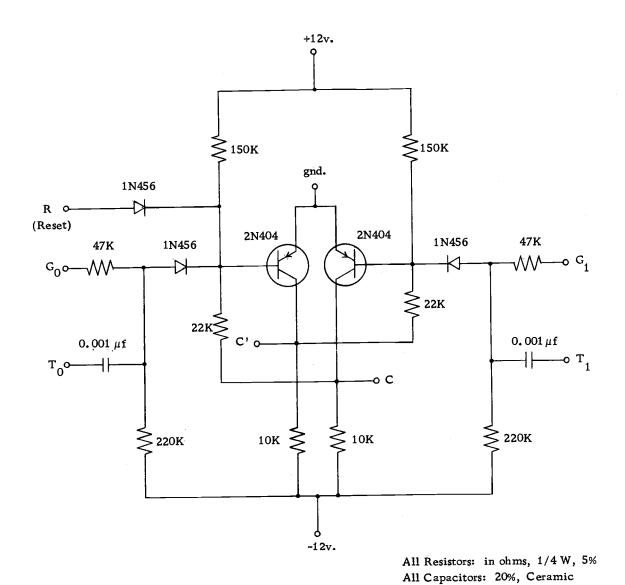

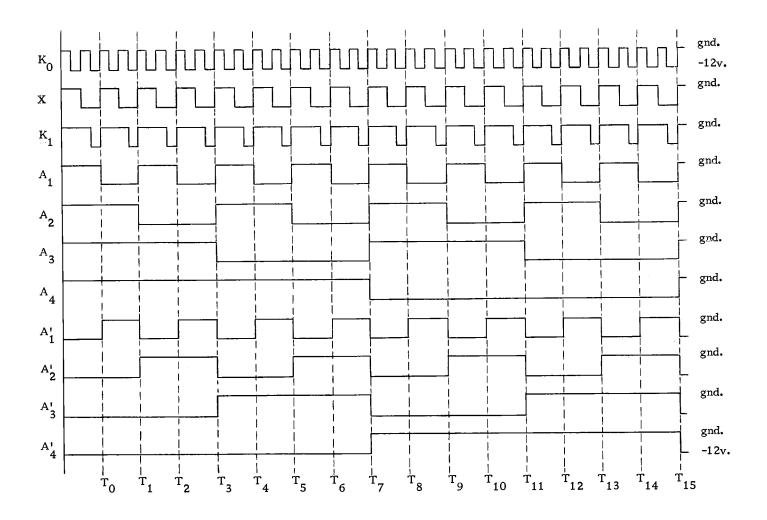

The prototype clock generator consists of an astable multivibrator, a counting flip-flop, and a three-input transistor "AND" gate (Figure 5). The astable multivibrator, MV-2, is a free running square wave generator (Figure 6), which determines the frequency of operation of the entire digitizer and sets the sampling rate at five samples per second. The output of the astable multivibrator,  $K_0$ , triggers the bistable multivibrator inputs,  $T_1$  and  $T_0$  (Figure 7). The bistable multivibrator is wired as a counting flip-flop. It, therefore, divides the  $K_0$  input by two to produce the half frequency square wave output X, and its compliment X'. The three-input

Figure 5. Prototype Clock Generator.

Figure 6. Astable Multivibrator Circuit, MV-2.

Figure 7. Bistable Multivibrator Circuit, FF-2.

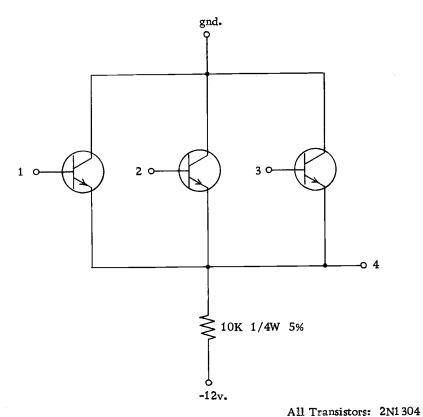

transistor "AND" gate, Figure 8, then forms the waveform  $\ K_1$  by the logical "AND" operation of  $\ K_0 \cdot X$  (Appendix Ia). The pulses in the  $\ K_1$  waveform simultaneously activate the A-counter and the diode "set" gates.

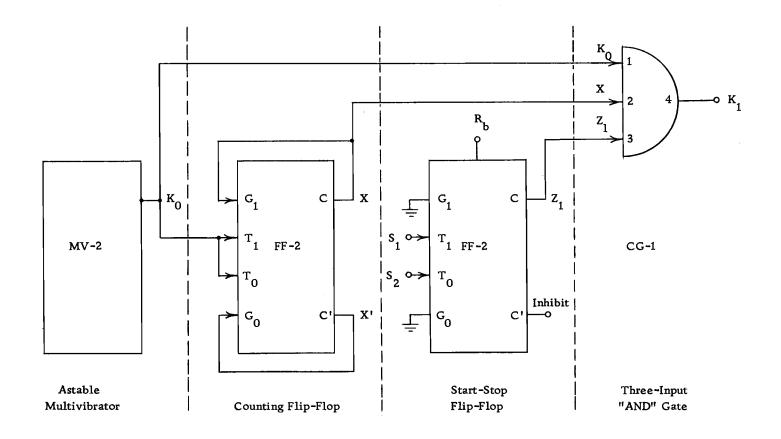

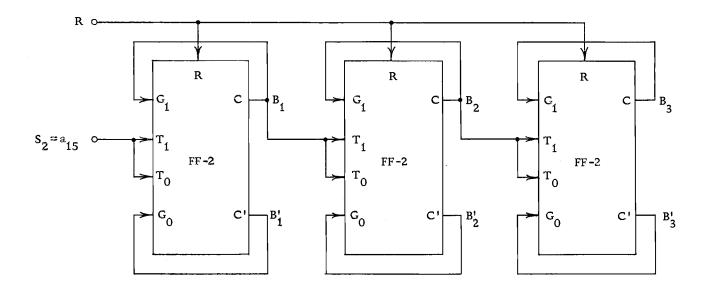

#### A-Counter

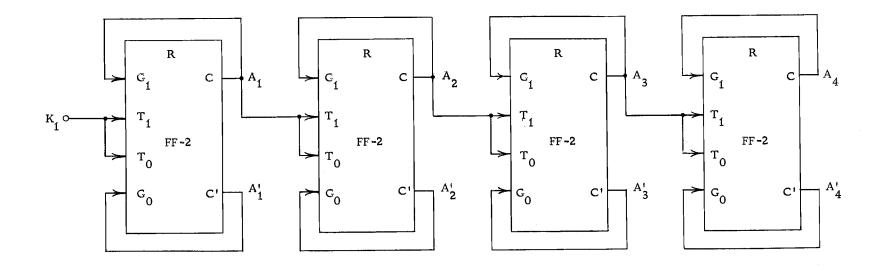

The prototype A-counter is made up of four bistable multivibrators (Figure 7), which are individually wired as counting flipflops. The four counting flip-flops are then interconnected to form a straight binary counter (Figure 9), with sixteen different possible states as indicated in Figure 10. The first counting flip-flop is triggered at its  $T_1$  and  $T_0$  inputs by each positive step in the clock pulse train,  $K_1$ . One of the outputs of this first flip-flop is labelled  $A_1$  and the other, which is the compliment of  $A_1$ , is labelled  $A_1'$ . The unprimed output of each counting flip-flop in turn triggers the following flip-flop during the positive step of its waveform to generate the successive half frequency waveforms  $A_2$ ,  $A_3$ ,  $A_4$ , and their compliments (Figure 10).

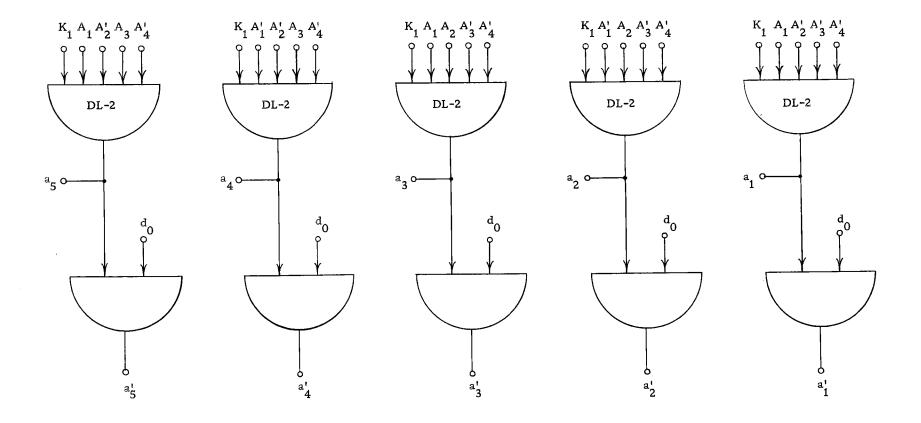

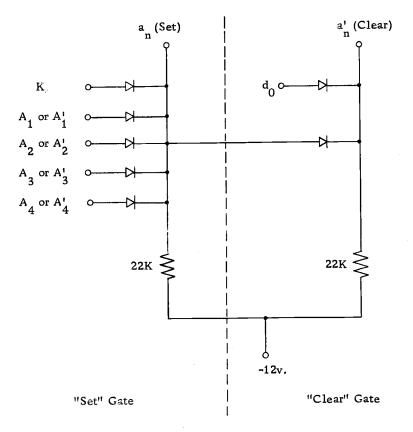

# "Set" Gates

The prototype "set" gates (Figure 11), consist of five five-input diode "AND" gates. Each "set" gate (Figure 12), has the clock waveform  $K_1$ , as one input. The other four inputs are a

All Transistors. 211150-

Figure 8. Three-Input Transistor "AND" Gate Circuit, CG-1.

Figure 9. Prototype A-Counter.

Figure 10. Prototype Clock Generator and A-Counter Timing Diagram.

Figure 11. Diode "Set" and "Clear" Gates.

All Resistors: in ohms, 1/4 W, 5% All Diodes: 1N456

Figure 12. Diode "Set" and "Clear" Gate Circuit, DL-2.

combination of four of the eight A-counter outputs which correspond to one of the sixteen different states of the A-counter.

For example, the output of the first diode "set" gate,  $a_1$ , is generated by the logical "AND" operation of  $K_1 \cdot A_1 \cdot A_1 \cdot A_2 \cdot A_3 \cdot A_4$ . Similarly,  $a_2$  through  $a_5$  are formed by the "AND" operation of  $K_1$  and the outputs of the A-counter which correspond to the second through fifth state of the counter (Figure 13).

# "Clear" Gates

The prototype "clear" gates, Figure 11, consist of five two-input diode "AND" gates. Each "clear" gate, Figure 12, has the do signal from the comparator as one input. The other input to each of the five "clear" gates is a thru a formed by the logical "AND" operation of do and a thru a formed by the logical "AND" operation of do and a thru a formed by the logical "AND" operation of do and a formed by the logical "AND" operation of do and a formed by the logical "AND" operation of do and a formed by the logical "AND" operation of do and a formed by the logical "AND" operation of do and a formed by the logical "AND" operation of do and a formed by the logical "AND" operation of do and a formed by the logical "AND" operation of do and a formed by the logical "AND" operation of do and a formed by the logical "AND" operation of do and a formed by the logical "AND" operation of do and a formed by the logical "AND" operation of do and a formed by the logical "AND" operation of do and a formed by the logical "AND" operation of do and a formed by the logical "AND" operation of do and a formed by the logical "AND" operation of do and a formed by the logical "AND" operation of do and a formed by the logical "AND" operation of do and a formed by the logical "AND" operation of do and a formed by the logical "AND" operation of do and a formed by the logical "AND" operation of do and a formed by the logical "AND" operation of do and a formed by the logical "AND" operation of do and a formed by the logical "AND" operation of do and a formed by the logical "AND" operation of do and a formed by the logical "AND" operation of do and a formed by the logical "AND" operation of do and a formed by the logical "AND" operation of do and a formed by the logical "AND" operation of do and a formed by the logical "AND" operation of do and a formed by the logical "AND" operation of do and a formed by the logical "AND" operation of do and a formed by the logical "AND" operation of do and a formed by the logical "AND" operation of do and a for

#### Reset Logic

The prototype reset logic circuit (Figure 14) is made up of a single four-input diode "AND" gate and a differentiator. The gate output, R, becomes negative when the logical "AND" operation of

Figure 13. Prototype Diode "Set" and Reset Logic Timing Diagram.

All Resistors: in ohms, 1/4 W, 5%

Figure 14. Prototype Reset Logic Circuit.

A<sub>1</sub>· A<sub>2</sub>· A<sub>3</sub>· A<sub>4</sub> is satisfied. The R output is then differentiated to generate a sharp negative and positive spiked waveform labelled reset (Figure 13). It is the positive spike of the reset waveform which simultaneously resets all the flip-flops in the D-register.

#### D-Register

The prototype D-register (Figure 15), is composed of four bistable multivibrators, FF-2 (Figure 7), individually wired as set-clear flip-flops. A common line running between them carries the reset input. The trigger inputs  $T_1$  and  $T_0$  of the first set-clear flip-flop are connected to the diode "set" and "clear" outputs  $a_1$  and  $a_2'$ , respectively. The outputs of the first set-clear flip-flop are labelled  $D_1$  and  $D_1'$ .

The state of the first flip-flop output,  $D_1'$ , (either 0 v. or -12 v.), just before display is dependent upon whether or not a negative  $a_2'$  "clear" pulse arrives after the negative  $a_1$  "set" pulse. The  $D_2$ ,  $D_3$ , and  $D_4$  outputs and their compliments are similarly formed.

# Neon Lamp Indicator

The prototype neon lamp indicator, (Figure 16), is made up of four neon lamp drivers, ND-1, (Figure 17). Each neon lamp driver consists of a two-input "AND" gate and a transistor switch.  $A_4$  is a

Figure 15. Prototype D-Register.

All Neon Lamps: NE-2

Figure 16. Prototype Neon Lamp Indicator.

All Resistors: in ohms, 1/4 W, 5%

Figure 17. Neon Lamp Driver Circuit, ND-1.

common input to each "AND" gate. The other input is one of the four D-register outputs,  $D_1$ - $D_4$ . When the logical "AND" operation of  $A_4$ - $D_1$  is satisfied, for example, the gate output becomes negative which turns the NPN transistor switch off. With the transistor off, the output voltage rises toward +45 volts turning on neon lamp A, which is connected between the output, L, and a -45 volt supply (in this way, a 50 v. transistor controls a 90 v. neon lamp). Similarly, the neon lamps B thru D are controlled by the "AND" operation of  $A_4$  and  $D_2$  thru  $D_4$ , respectively. The neon lamps are, therefore, kept from flickering during the balancing period by the common input  $A_4$  (Figure 13).

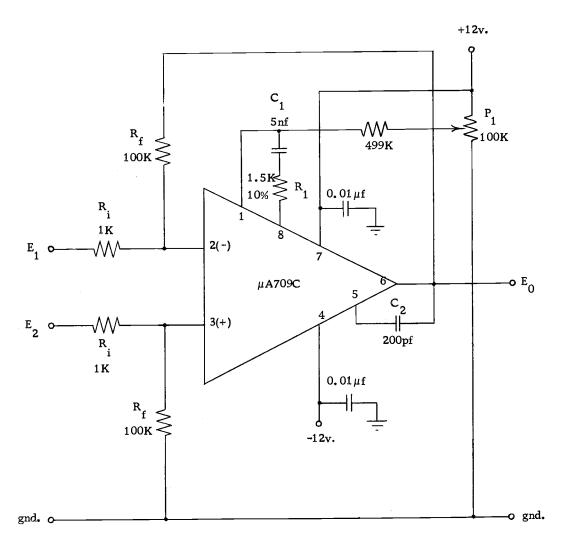

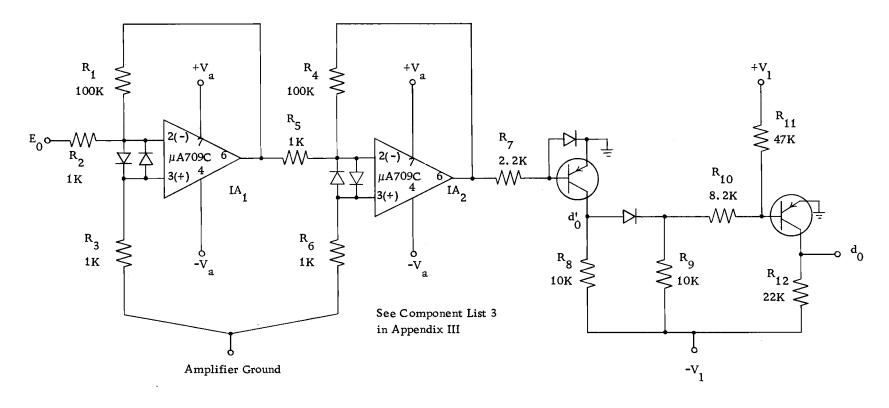

# Difference Amplifier

The prototype difference amplifier, (Figure 18), is a Fairchild (Fairchild Semiconductor Company, Mountain View, California),  $\mu$ A709C integrated circuit (IC) operational amplifier operating in the operational mode with a fixed differential gain of 100. The operational amplifier uses feed-back resistors of 100 K $\Omega$  and input resistors of  $1k\Omega$  to obtain the fixed differential gain of 100 or 40 db, (Appendix Ib). Through the use of current injection, amplifier input offset voltage is reduced to zero by adjusting the 100 K $\Omega$  potentiometer,  $P_1$ . The amplifier is frequency compensated by  $C_2$ ,  $C_1$ , and  $R_1$  to give a 20 db per decade roll-off starting at the upper frequency break point

All Resistors: in ohms, 1/4 W, 1%

100ppm/°C, unless

otherwise specified

All Capacitors: Disc Ceramic 20%

Figure 18. Prototype Difference Amplifier.

of 5 KHz. A unity gain bandwidth of 500 KHz is, therefore, obtained and assures amplifier stability for any resistive load.

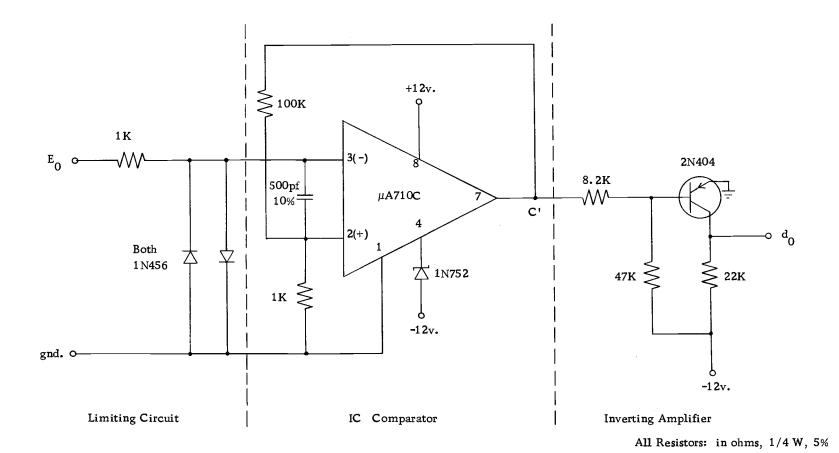

## Comparator

The prototype comparator (Figure 19), consists of a limiting circuit, a Fairchild  $\mu A710C$  IC comparator, and a transistor inverting amplifier.

The difference amplifier output,  $E_0$ , is connected to the inverting input of the IC comparator through the  $1~\mathrm{K}\Omega$  resistor of a resistor-diode limiting circuit. This circuit limits the voltage swing at the comparator input to  $\pm 0.7$  v., thereby keeping the  $\pm 10$  v. signal from exceeding the ±5 v. comparator input voltage range. The non-inverting input is connected to ground through another 1  $K\Omega$ resistor. A 500 pf capacitor between the two comparator inputs bypasses to ground any high frequency signal which may appear at the inverting input. The  $100~\mathrm{K}\Omega$  positive feedback resistor connected from the output to the non-inverting input of the comparator decreases the possibility of self-induced oscillation. Oscillation is sometimes caused by a slight voltage drop induced across the input resistor when the comparator starts to draw input current upon switching. The use of a positive feedback resistor has the disadvantage of inducing a larger hystersis band into the comparator (10, p. 165).

The comparator amplifier inverts and amplifies the -0.5 v.

Figure 19. Prototype Comparator.

and +3.2 v. IC comparator output voltage levels. It produces at its output, d<sub>0</sub>, the inverted and amplified voltages 0 v. and -12 v., respectively, which are compatible with the logic voltage levels of the other logic units.

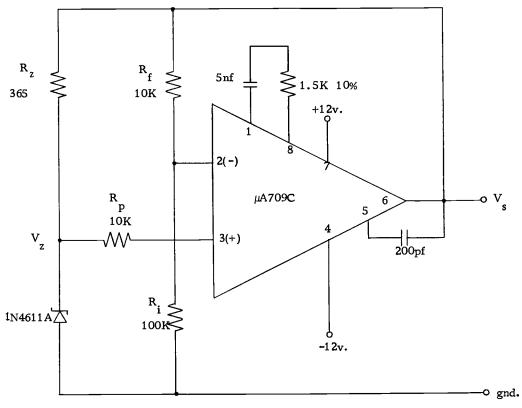

#### Reference Voltage Source

The prototype reference voltage source (Figure 20), uses a Fairchild temperature compensated (±0.002%/°C at 1-3 ma) silicon zener reference diode, 1N4611A, as a voltage reference element in the positive feedback loop of a Fairchild µA709C IC operational amplifier. The amplifier serves both as a high gain error amplifier and a current buffer amplifier, with a 10 ma current output capability. This circuit is a modification of the one described by Giles (10, p. 144). The modification involves placing the reference diode in the positive feedback loop. In this way, a constant diode current is drawn from the constant output voltage if the series resistor, R<sub>z</sub>, is both time and temperature stable. This method greatly increases the voltage stability of the reference diode.

The amplifier is operated in the operational mode as a non-inverting amplifier (Appendix Ib). The inverting input of the amplifier is connected to the output through a 10 K $\Omega$  feedback resistor,  $R_f$ . The 100 K $\Omega$  input resistor,  $R_i$ , which is also connected to the inverting input, is returned to ground. This sets the gain of the

All Resistors: in ohms, 1/4 W, 1%, 100ppm/°C,

Unless Otherwise Specified

All Capacitors: Disc Ceramic 20%

Figure 20. Prototype Reference Voltage Source.

non-inverting amplifier to 1.1. The non-inverting input is connected to the cathode of the reference diode through a 10 K $\Omega$  resistor, R $_p$ , while the anode is returned to ground. With a zener voltage,  $V_z = 6.55 \, v.$ , at a diode current of 2 ma, the output voltage,  $V_s$ , becomes 7.21 v.  $(6.55 \, v. \, x \, 1.1)$ . By connecting the cathode of the reference diode to the non-inverting input of a non-inverting amplifier, the reference diode is negligibly loaded, since the input impedance to such an amplifier is in the tens of megohms (9, p. 84). The amplifier current output capability of 10 ma, therefore, allows up to 10 ma to be drawn by a load without any appreciable voltage variation being induced across the reference diode. The voltage regulation of the reference voltage source is extremely high and is only slightly affected by temperature drifts of the reference element and amplifier.

# Input Circuit

The prototype input circuit for the bridge operating mode is different from the circuit for the potentiometer mode. In the resistance ratio bridge operating mode, the input circuit is simply two resistors as indicated in Figure 2. The unknown resistance,  $R_{\mathbf{x}}$ , is placed in series with the known resistance,  $R_{\mathbf{b}}$ , to form two adjacent arms of the bridge circuit.

For measuring temperature, a platinum thermometer of

resistance  $R_x$  is used along with a fixed series resistance,  $R_b$ . The value of  $R_b$  is made equal to the mid-range value of  $R_x$  to obtain maximum bridge output (4, p. 129).

For measuring pressure, both resistors are made variable. This is accomplished by using a two-element strain gauge pressure transducer with one element (serving as  $R_{x}$ ) undergoing tension and the other (serving as  $R_{b}$ ) undergoing compression. Both elements are equal in resistance at a gauge pressure of zero psig.

In the potentiometer operating mode, the input circuit is a current or voltage output transducer with its associated signal conditioning amplifier (Figure 3). For measuring the current output from an oxygen cell, the conditioning amplifier is an operational amplifier connected as a current-to-voltage converter (Appendix Ib). The value of the feedback resistor,  $R_f$ , is calculated from the current output of the cell and the desired amplifier output voltage.

For measuring the voltage output from an electrochemical cell, the conditioning amplifier is an operational amplifier operated as a non-inverting amplifier (Appendix Ib). The values of the feedback and input resistors are calculated from the voltage output of the electrode and the desired amplifier output voltage.

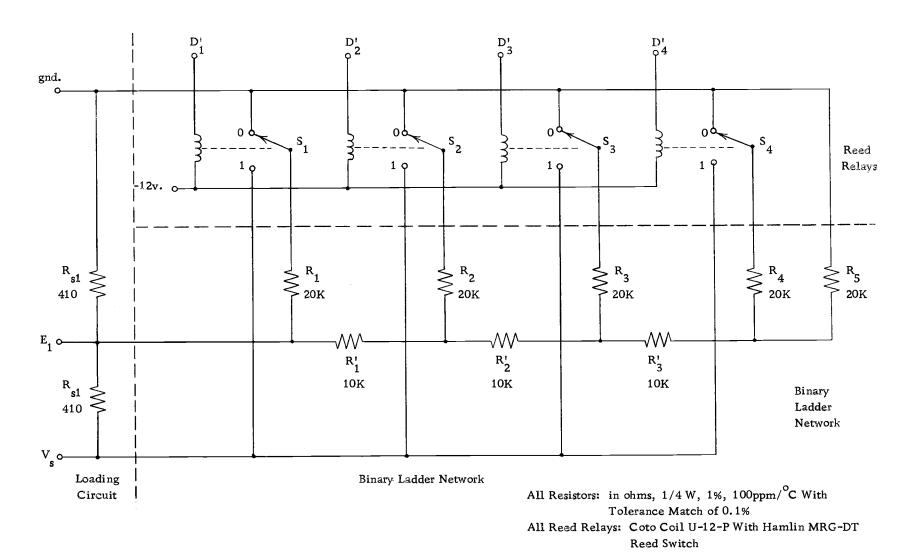

#### Resistive Network and Relays

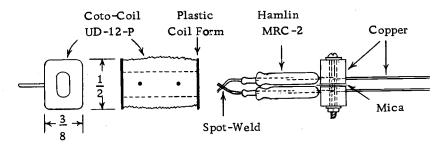

The prototype resistive network and relays consist of four Coto-Coil (Coto-Coil Co., Inc., Providence, Rhode Island) miniature SPDT reed relays, a four-bit binary ladder network, and a unique two-resistor loading circuit, Figure 21. The two-resistor loading circuit,  $R_{s1}$  and  $R_{s1}$ , loads the output of the binary ladder network and sets the voltage range over which the resistive network output voltage,  $E_1$ , can vary.

The four reed relays are activated sequentially by the D-register outputs  $D_1'$  thru  $D_4'$ . The first reed relay, which is activated by  $D_1'$  at time  $T_1$ , switches the most significant bit (MSB) switch,  $S_1$ , of the binary ladder network. The switching of  $S_1$  to the "1" position places the  $E_1$  output voltage at its half-range value. If  $S_1$  is left in the "1" position and the second MSB switch,  $S_2$ , is switched to the "1" position by  $D_2'$  at time  $T_2$ , the  $E_1$  output is set to its three-quarter range value. But, if  $S_1$  is switched back to the "0" position and  $S_2$  is switched to the "1" position at time  $T_2$ , the  $E_1$  output is set to its one-quarter range value. Similar adjustments of the next most significant bit switches,  $S_3$  and  $S_4$ , at time  $T_3$  and  $T_4$  will vary the  $E_1$  output around the preceding set value by plus or minus one-half of the preceding step. In this way, the resistive network produces an

Figure 21. Prototype Resistive Network and Relays.

output voltage,  $E_1$ , which changes by equal steps from the middle, to any point between the top or bottom of the voltage range set by the loading circuit,  $R_{s1}$  and  $R_{s1}$ .

### Balancing Sequence Example

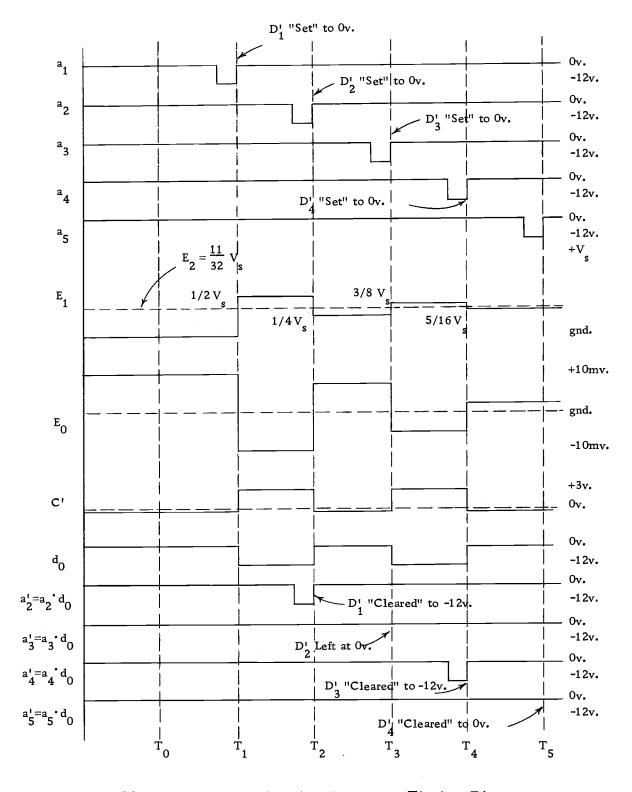

Consider an example where both  $R_{s1}$ 's of the loading circuit are removed ( $R_{s1} = \infty \Omega$ ), and an arbitrary value of transducer output,  $E_2$ , is  $+11/32~V_s$  (Figures 4 and 21). In this case, the range over which  $E_1$  can vary is from ground to  $+V_s$ , and the number of equal steps from ground to  $+V_s$  is 16 (i. e.,  $2^4$  from two possible states for each of the four ladder bits). The following will take place once a measuring cycle has started. We will assume that prior to this time a similar measuring cycle has taken place after which the reset signal has returned all reed switches,  $S_1$  thru  $S_4$ , to the "0" position.

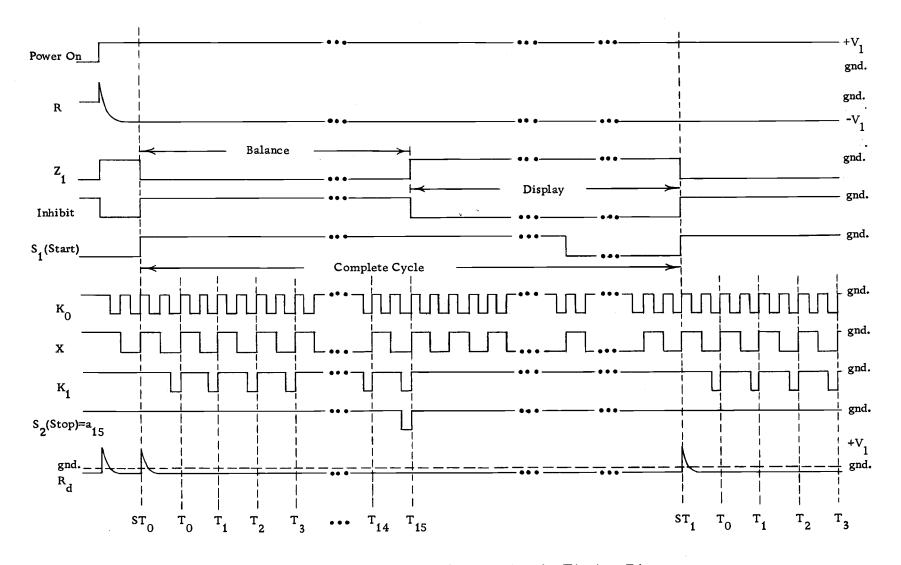

At time  $T_1$ , as shown in Figure 22, the positive step (-12 v. to 0 v.) of the negative pulse in the  $a_1$  "set" waveform will set the first flip-flop in the D-register, thereby changing the  $D_1'$  output from the reset level of -12 v. to 0 v. The most significant bit (MSB) switch,  $S_1$ , is then switched from its reset position, "0", to its activated position, "1", see Figure 21. At this time,  $E_1$  will take on a value of + 1/2  $V_s$ . This value is larger than that of  $E_2$  (+11/32  $V_s$ ), which will cause  $E_0$  to become negative according to the

Figure 22. Prototype Balancing Sequence Timing Diagram.

.....

. The second second

transfer equation for the difference amplifier,  $E_0 = 100 \ (E_2 - E_1)$ . The negative  $E_0$  signal will cause the IC comparator to switch to its positive output state where C' equals + 3. 2 v. This logic level is inverted and amplified by the comparator inverter amplifier to produce the negative (-12 v.) output,  $d_0$ . The logical "AND" operation of  $a_2 = a_2 \cdot d_0$  is performed by the first diode "clear" gate and in this case is satisfied, thereby generating a negative pulse in the  $a_2'$  waveform. The positive step in the  $a_2'$  waveform at time  $T_2$  "clears" the first flip-flop in the D-register. The  $D_1'$  output then returns to -12 v. and  $S_1$  returns to the "0" position. Also, at time  $T_2$ , the positive step in the  $a_2$  waveform sets the second D-register flip-flop, thereby positioning  $S_2$  in the "1" position.

As a result of the simultaneous switchings of  $S_1$  and  $S_2$  at time  $T_2$ ,  $E_1$  takes on the value of  $\pm 1/4~V_s$ . This value of  $E_1$  is less than  $E_2$ , which causes  $E_0$  to go positive. The comparator output, C', is switched to -0.5 v. and  $d_0$  rises to ground level. The "AND" operation of  $a'_3 = a_3 \cdot d_0$  is not satisfied and no negative pulse is introduced into the  $a'_3$  signal.  $D'_2$  remains at zero volts at time  $T_3$ , and  $S_2$  is also left in the "1" position. At time  $T_3$ ,  $a_4$  automatically sets  $D'_4$  to ground level which activates  $S_3$  to the "1" position.

As a result of no return switching action of S2 and the

automatic switching of  $S_3$  from "0" to "1" at time  $T_3$ ,  $E_1$  assumes the value of +3/8  $V_s$ . This value is larger than  $E_1$  which causes  $E_0$  to go negative. C' is then switched to +3.2 v. and  $d_0$  to -12 v., which allows a negative pulse to be formed in the  $a'_4$  signal prior to time  $T_4$ . The positive step of the  $a'_4$  negative pulse "clears"  $D'_3$  to the -12 v. level and returns  $S_3$  to the "0" position. Also, at time  $T_4$ ,  $a_4$  automatically sets  $D'_4$  to zero volts which activates  $S_4$  to the "1" position.

Resulting from the above two switchings at time  $T_4$ ,  $E_1$  assumes the value of +5/16  $V_s$ . This value is less than  $E_1$  which causes  $d_0$  to go to zero volts. The "AND" operation of  $a_5' = a_5 \cdot d_0$  is not satisfied and no negative pulse is developed in the  $a_5'$  signal at time  $T_5$ . This then leaves  $D_4'$  at ground level and  $S_4$  in the "1" position.

Looking back, we note that  $S_1$  is at "0",  $S_2$  at "1",  $S_3$  at "0", and  $S_4$  at "1", giving the final digital output of 0101. This indicates that  $E_2$  is between the value of + 5/16  $V_s$  and + 6/16  $V_s$  or equal to + 11/16  $\pm$  1/16  $V_s$ .

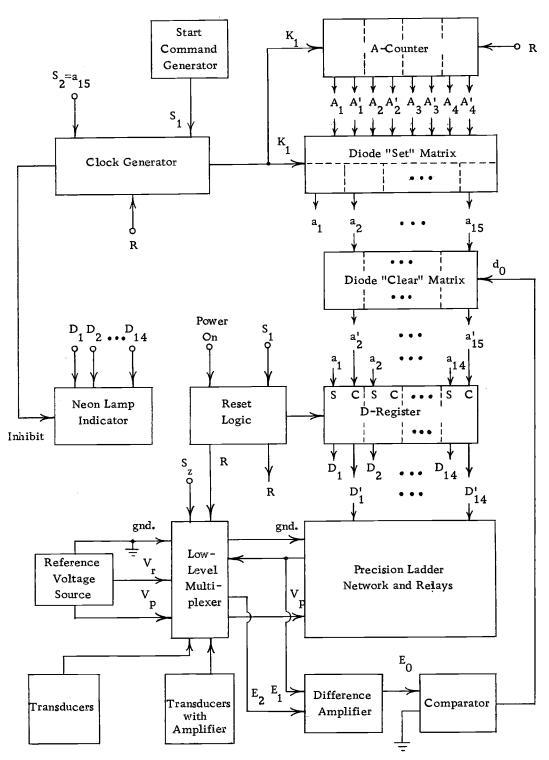

#### FOURTEEN-BIT DIGITAL DATA ACQUISITION SYSTEM

The fourteen-bit digital data acquisition system was designed to automatically measure various physical and chemical properties of sea water. The digital data output is presented in both serial and parallel form for telemetry or direct readout and recording equipment. The system consists of a rechargeable battery supply and amplifier voltage regulators, a fourteen-bit analog-to-digital converter, a low-level scanner, and the transducers with their associated signal conditioning amplifiers, Figure 23.

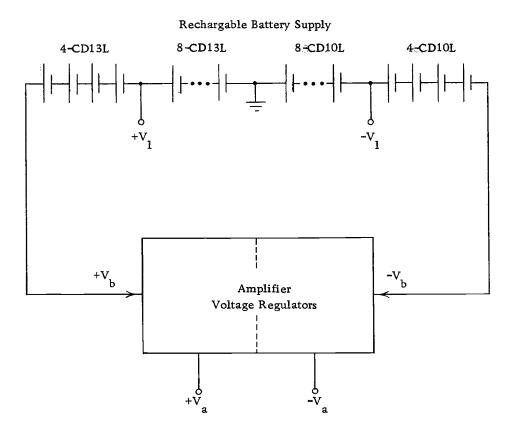

# Rechargeable Battery Supply and Voltage Regulators

The rechargeable battery supply is a set of series connected "1/2 D" and "D" size Burgess (Burgess Battery Company, Freeport, Illinois) sealed nickel-cadmium rechargeable cells. Twelve "D" size cells (CD10L), having a ten hour discharge capacity of 4.0 ampere-hours, are connected in series to form the negative battery supply voltage  $-V_b$ . Twelve "1/2 D" size cells (CD13L), having a ten hour discharge capacity of 2.3 ampere-hours, are similarly connected in series to form the positive battery supply voltage,  $+V_b$ , (Figure 24). The lower positive and negative voltages  $(+V_1)$ , to power the logic circuits, are tapped off between the eighth and ninth cell of each battery supply. The use of such high capacity cells gives

Figure 23. Block Diagram of Fourteen-Bit Digital Data Acquisition System.

Figure 24. Block Diagram of Rechargable Battery

Supply and Amplifier Voltage Regulators.

a battery life of approximately 12 hours between charges. In this way, having two battery packages available, allows the system to be operated continuously.

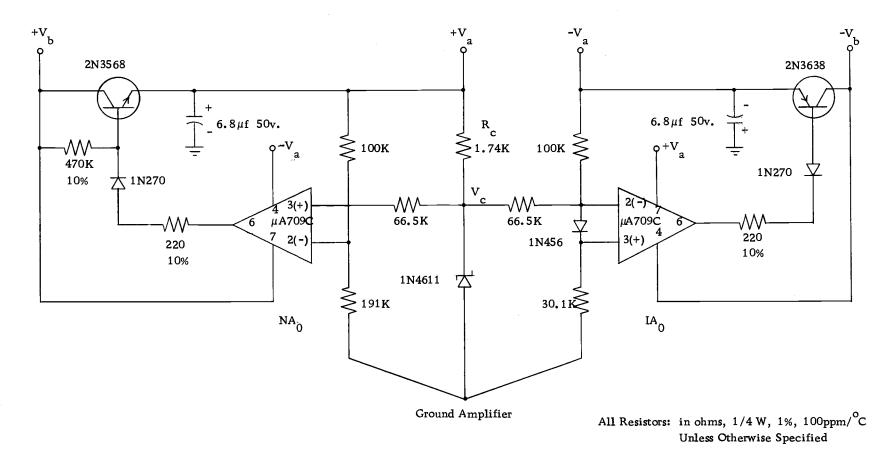

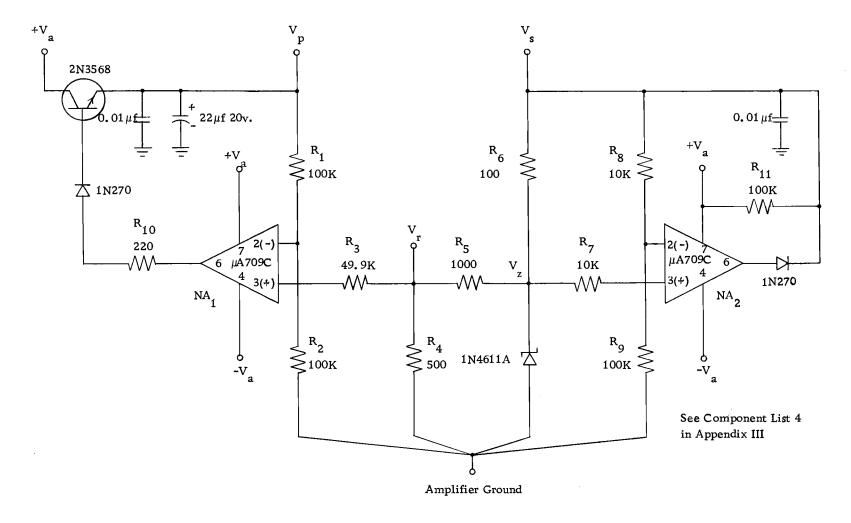

A  $\mu$ A709C IC operational amplifier is used as both an error amplifier and a current buffer in each of the two amplifier voltage regulators. A series voltage regulator transistor, driven by the error amplifier, increases the current capacity of each amplifier. The regulator circuit is drawn in Figure 25. To simplify the following circuit diagrams, the frequency compensating and supply voltage bypass components for each operational amplifier will be eliminated from the diagrams. It will be assumed, hereafter, that each  $\mu$ A709C IC operational amplifier is compensated and bypassed as described in the preceding section on the prototype difference amplifier (p. 40).

The circuit is unique in that it requires only one voltage reference element for the regulation of two voltages of opposite polarity. This is accomplished by using one operational amplifier as a non-inverting amplifier and the other as an inverting amplifier. The non-inverting amplifier,  $NA_{o}$ , amplifies the positive zener reference voltage,  $+V_{c} = +6.56v$ , to produce the positive amplifier supply voltage,  $+V_{a} = +10.0v$ . A constant zener current of 2ma is drawn from this stable positive voltage through the zener series resistor,  $R_{c}$ . The inverting amplifier,  $IA_{o}$ , inverts and

Figure 25. Amplifier Voltage Regulators.

amplifies the zener voltage to produce a negative amplifier supply voltage,  $-V_a = -10.0v$ . Cross coupling the two regulators, by connecting the negative supply terminal of  $NA_o$  to  $-V_a$  and the positive supply terminal of  $IA_o$  to  $+V_a$ , increases the voltage regulation.

A high-speed silicon diode is placed across the inputs of  $IA_o$ , as a means of protecting the amplifier for the case where  $+V_b$  might be connected before  $-V_b$ . In this situation, the voltage at pin 2 tends to rise toward  $V_c = 6.56 \, \text{v.}$ , while the voltage at pin 3 is held at ground level. If the diode did not limit the voltage rise, the amplifier input voltage limitations would be exceeded; and the amplifier might be damaged. The  $220\Omega$  resistors perform the function of current limiting, while the 1N270 germanium diodes prevent latchup. The  $470 \, \text{K}$  resistor provides a small bias current to the NPN voltage regulator transistor, thereby assuring reliable start-up.

#### Fourteen-Bit Analog-to-Digital Converter

The fourteen-bit analog-to-digital converter uses, in general, the same logic units, basic circuitry, and balancing technique as were tested in the four-bit prototype. The larger converter is many times more complicated than the prototype, due to its ten additional bits of information. To obtain these additional bits, it was necessary not only to increase the digital control capacity, but also to increase the

sensitivity and stability of the precision reference voltage source, the precision resistive ladder network, and the difference amplifier. The clock generator was modified to include the features of starting upon the reception of a command pulse and stopping upon the completion of a balancing sequence. This, of course, starts and stops the converter, which allows the sampling rate to be determined by an external generator.

Figure 23 includes a block diagram of the fourteen-bit analogto-digital converter; and the following is a block-by-block description to point out the similarities and differences between this converter and the prototype.

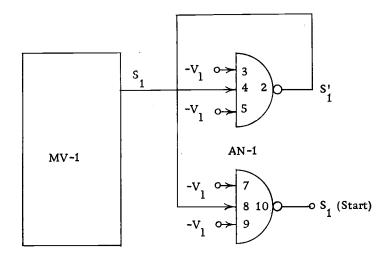

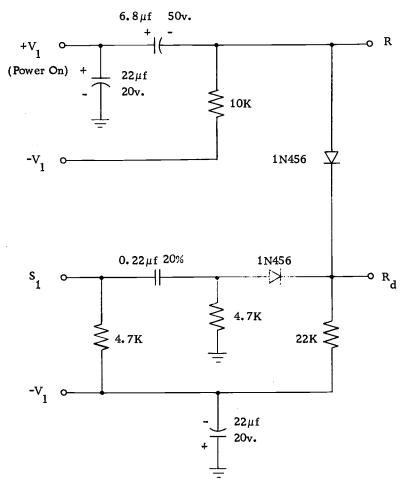

#### Start Command Generator

The generator is a low frequency (4 Hz.) free-running multivibrator, MV-1, followed by two three-input transistor "NAND" gates, AN-1, Figure 26. The  $S_1$  output provides, simultaneously, a start command pulse to the clock generator and a reset pulse to the reset logic. The multivibrator differs from MV-2 (Figure 6), only in that the timing capacitors, C, have been increased to 0.5  $\mu f$  in order to lower the frequency from 150 Hz. to 4 Hz. This frequency then determines the sampling rate of the system. By performing two "NAND" operations (Appendix Ia), AN-1, Figure 27, simply amplifies the multivibrator output  $S_1$ , to obtain the necessary drive

Figure 26. Start Command Generator.

Figure 27. "NAND" Gate Circuit, AN-1.

capability for the S<sub>1</sub> (start) signal.

#### Clock Generator

The clock generator differs from the prototype clock generator (Figure 5), in that a start-stop flip-flop has been inserted between the counting flip-flop and the three-input "AND" gate to control the generator output  $K_1$ , Figure 28.

The start-stop flip-flop is a standard FF-2 connected in the set-clear mode. A positive step in the  $S_1$  (start) input sets the flip-flop output, C, to ground level, thereby gating CG-1 open and allowing  $K_1$  to flow. Upon reception of a positive step in the  $S_2$  (stop) input, the output is cleared to  $-V_1$  which closes CG-1 and stops the  $K_1$  pulse train, Figure 29. The  $S_2$  input signal is the same signal as the diode "set" matrix output,  $a_{15}$ .

#### Reset Logic

A circuit diagram of the reset logic is shown in Figure 30. The circuit consists of two differentiators and one two-input "AND" gate. The "AND" gate allows the output,  $R_d$ , to be the sum of the two differentiator outputs. As indicated in Figure 29, a positive step in the "power on" input produces a positive reset pulse in both R and  $R_d$ , thereby resetting all flip-flops in the converter when the power is first turned on. A positive step in the  $S_1$  input produces

Figure 28. Clock Generator.

Figure 29. Clock Generator and Reset Logic Timing Diagram.

All Resistors: in ohms, 1/4 W, 5%

Figure 30. Reset Logic Circuit.

a positive reset pulse in  $R_{d}$  only, thereby resetting the flip-flops in the D-register at the beginning of each balancing sequence.

#### A-Counter

The A-counter is identical to the prototype A-counter (Figure 9), with the exception that a common reset input, R, is connected to the reset input of each flip-flop. The only time the A-counter is reset is when power is first turned on. After every sixteen cycles of the  $K_1$  input, which constitutes one full counter cycle, the  $K_1$  input is stopped by the start-stop flip-flop. This leaves the counter in its original reset state, ready for the next balancing cycle.

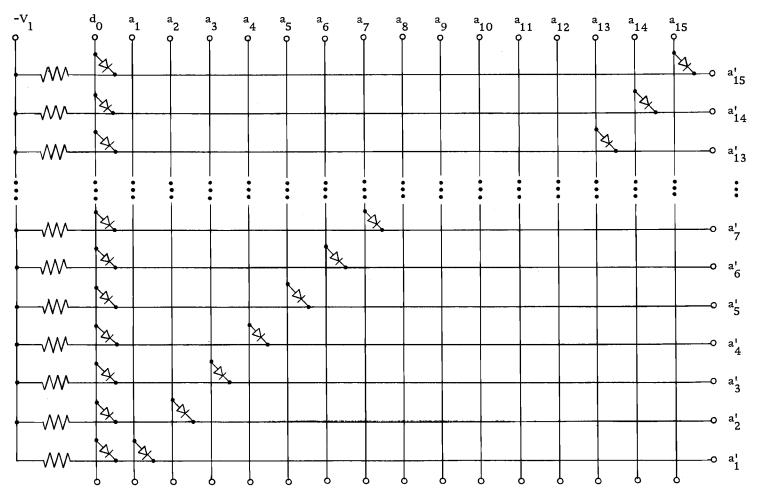

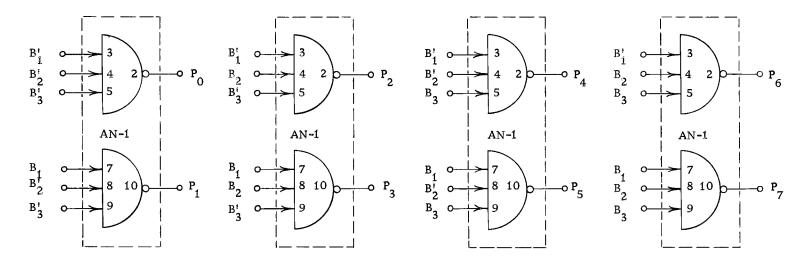

#### "Set" Decode Matrix

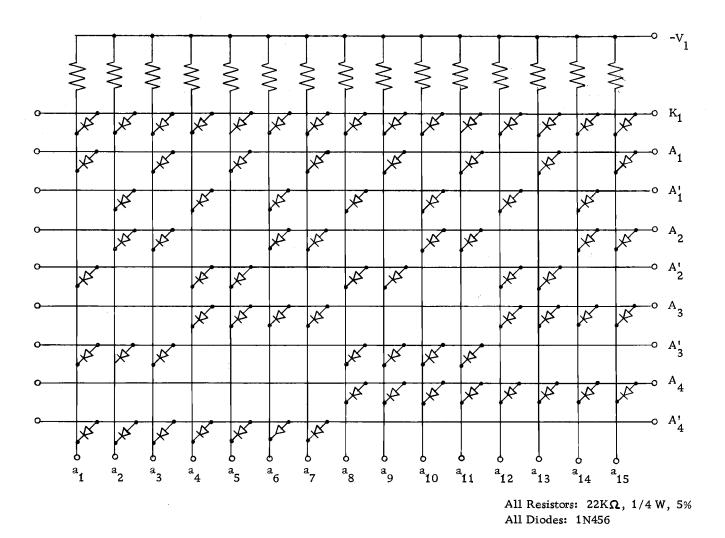

The diode "set" decode matrix is simply an extension of the prototype diode "set" gates. The diode matrix consists of fifteen five-input diode "AND" gates. A circuit diagram is drawn in Figure 31. As indicated in the diagram, the "set" outputs a thru a 15 are derived from the A-counter outputs, which correspond to the second thru sixteenth count of the A-counter.

## "Clear" Matrix

Similarly, the diode "clear" matrix is an extension of the prototype diode "clear" gates. Figure 32 is a circuit diagram of

Figure 31. Diode "Set" Decode Matrix.

All Resistors:  $22K\Omega$ , 1/4 W, 5% All Diodes: 1N456

Figure 32. Diode "Clear" Matrix.

the diode matrix, which consists of fifteen two-input diode "AND" gates. As indicated in the diagram, the outputs  $a_1'$  thru  $a_{15}'$  are derived from the common feedback input  $d_0$  and the diode "set" matrix outputs  $a_1$  thru  $a_{15}$ , respectively.

## D-Register

The D register consists of fourteen flip-flops connected together exactly as the four in the prototype D-register. Its operation is identical to the prototype's. The only difference between the two is the ten additional flip-flops (Figure 33).

# Neon Lamp Indicator

This is a complete reproduction of the prototype neon lamp indicator in both function and operation. Of course, ten additional driver units were added to increase the display capacity to fourteen bits (Figure 34). The indicator is essentially a straight binary weighted readout. An inhibit signal from the clock generator replaces the A<sub>4</sub> signal used in the prototype. Its function is still one of eliminating lamp flickering during the balancing period.

# Difference Amplifier

The difference amplifier, however, is completely different from the prototype difference amplifier. Since the stability and

Figure 33. D-Register.

Figure 34. Neon Lamp Indicator.

accuracy of this amplifier directly influences the overall conversion accuracy, the amplifier stablity and accuracy must be made as high as possible. The difference amplifier chosen for this purpose is described by Giles (10, p. 137), as having an input offset voltage drift of only  $0.2\mu v/^{\circ}C$  and an open loop gain of three million (Appendix Ib). These characteristics are better than those of most chopper stabilized amplifiers available today. The closed loop gain accuracy and stability are dependent upon the accuracy and stability of the input and feedback resistors. For this reason, the resistors in the amplifier are matched for both resistance and temperature coefficient (Appendix III).

The amplifier consists of one Fairchild  $\mu A709C$  IC operational amplifier preceded by two Fairchild  $\mu A726C$  IC temperature stabilized matched silicon transistor pairs (Figure 35). One matched pair performs the function of a low current preamplifier, while the other performs the function of a voltage follower. Their characteristics and operation are described in the reference cited above. Two well matched 200 K $\Omega$  resistors are used as feedback resistors and two equally well matched 1 K $\Omega$  resistors are used as input resistors to set the differential gain of the amplifier to 200.

A highly stable differential voltage follower (Figure 36), is placed in front of the difference amplifier to decrease the effect of a changing transducer resistance on the differential gain of the

Figure 35. Temperature Stabilized Difference Amplifier.

Figure 36. Temperature Stabilized Differential Follower.

amplifier. The follower effectively reduces the source resistance from a value of around 200  $\Omega$  to a value of less than one ohm. A disadvantage for the use of this follower is its added input offset voltage temperature drift of 0.2 $\mu$ v/°C. Since this value is equal to that of the difference amplifier's, it increases the total amplifier drift to 0.4 $\mu$ v/°C. As in the prototype difference amplifier, the output voltage,  $E_0$ , is balanced to zero by adjusting  $P_1$  when the inputs are grounded. This is accomplished by removing the  $\mu$ A726C in the differential follower,  $F_2$ , and shorting pins 3 and 10 to amplifier ground.  $P_1$  is then adjusted until  $E_0$  equals zero.

# Comparator

The  $\mu A710C$  IC comparator used in the prototype comparator has been replaced by two cascaded  $\mu A709C$  IC operational amplifiers to obtain a narrower hysteresis band (Figure 37). Each inverting amplifier has a gain of 100 and, as in the case of the prototype comparator, has its inputs protected by two voltage limiting diodes. The comparator amplifier is different from the prototype, but its function of amplification and voltage level shifting remains the same.

## Precision Reference Voltage Source

The reference voltage source is basically the same as the one used in the prototype. However, since a lower excitation voltage is

Figure 37. Comparator and Comparator Amplifier.

required for the high sensitivity transducers, a few additions and modifications were made. In the prototype reference voltage source, the functions of zener current regulation, voltage error amplification, and current buffering were performed by the same amplifier. In this reference voltage source, it is not possible to use only one amplifier since the required transducer excitation voltage is less than the voltage of the reference element. Therefore, as indicated in Figure 38, amplifier NA<sub>2</sub> performs the function of zener current regulation, while amplifier NA<sub>1</sub> operates as a voltage amplifier and current buffer.

The reference element is the same low temperature coefficient ( $\pm 20 \text{ ppm/°C}$ ) unit used in the prototype. The amplifier feedback resistors are low temperature coefficient ( $\pm 50 \text{ ppm/°C}$ ) components. Resistors R<sub>4</sub>, R<sub>5</sub>, and R<sub>6</sub>, which are associated with the reference element, are lower temperature coefficient ( $\pm 20 \text{ ppm/°C}$ ) units in order to minimize any temperature effects on V<sub>r</sub> and V<sub>p</sub>. Resistors R<sub>4</sub> and R<sub>5</sub> form a voltage divider to tap V<sub>r</sub> from V<sub>z</sub>. V<sub>r</sub> is equal to  $1/3\text{V}_z$  and is used as the reference voltage to measure the confidence level of conversion. The transducer excitation voltage, V<sub>p</sub>, is set equal to  $2\text{V}_r$  by amplifier NA<sub>1</sub>. Therefore, both V<sub>r</sub> and V<sub>p</sub> are less than the reference element voltage, V<sub>z</sub>. The resistors, capacitors, diodes, and transistor associated with the outputs of the amplifiers perform the same

Figure 38. Precision Reference Voltage Source.

function as those used and described in the previous section on the amplifier voltage regulators.

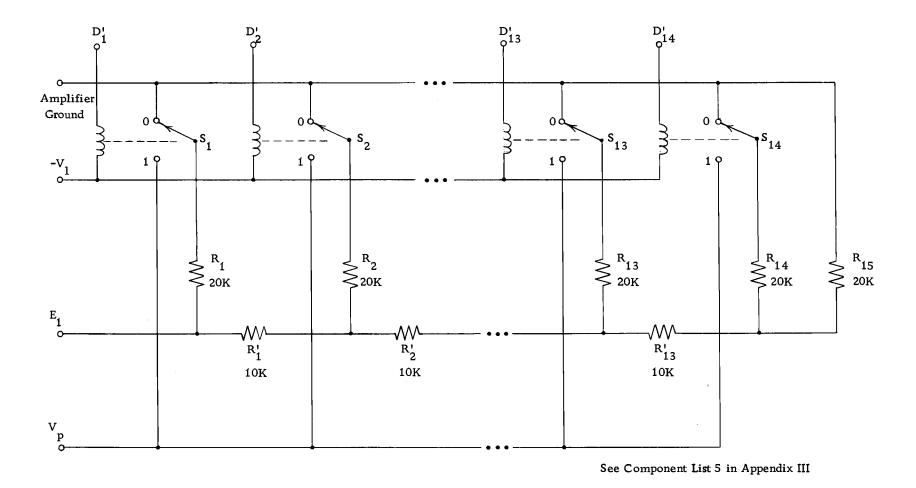

## Precision Binary Ladder Network and Relays

This section is essentially an extension of the four-bit prototype ladder network to include ten extra bits. The resistors making up the network are of much better quality, however, and are well matched for both initial resistance and temperature coefficient. The ladder network used is described and analyzed by Susskind (27, p. 5-35). It consists of fifteen 20 K $\Omega$  and thirteen 10 K $\Omega$  ESI (Electro Scientific Industries, Inc.; Portland, Oregon ) RF2R open-frame precision wirewound resistors (Figure 39). The initial resistance of the resistors was  $\pm 0.01\%$ , with a stability of  $\pm 50$  ppm/year. The temperature coefficient was 0 to -2 ppm/°C at 25°C; and temperature tracking is assured, since the resistors were all wound from the same spool of material. The resistors were matched for both resistance variation and temperature coefficient, as indicated in component List 5 of Appendix III. The above tight specifications and close matching were required, in order to assure a 14-bit ladder conversion accuracy of one-half of the least significant bit  $(\pm 1/2 LSB)$ over the anticipated environmental conditions. The resistors were spot-welded together with the same material as was used in making their leads. In this way, thermally generated EMF's, due to

Figure 39. Precision Binary Ladder Network and Relays.

dissimilar metal junctions, and contact resistances were held to a minimum.

The fourteen SPDT reed relays are the same as those used in the prototype. Since the reed switch material is a ferromagnetic alloy and the relay solenoid around the switch dissipates up to a quarter of a watt, every reed switch-to-resistor connection is a potential thermal EMF generator. This condition has been minimized by making the connection with a fine copper wire and insulating the switch-to-wire junction as described by Sommer (26, p. 86).

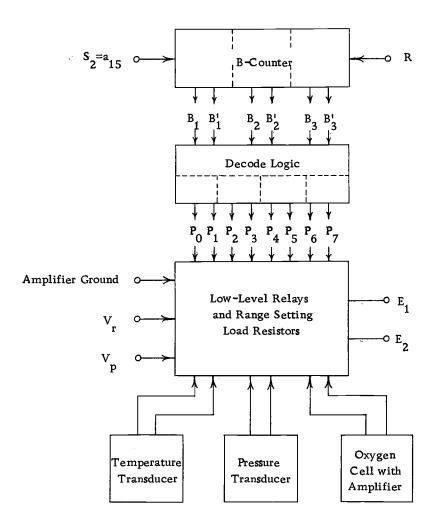

## Low-Level Scanner

The scanner performs the functions of programmable transducer sampling and range selection. Consisting of a binary counter and its associated decoding logic, it controls the sampling sequence. Since the scanner switches very low-level transducer signals, the programmer-controlled reed relays are extremely low-level units of special design. A pair of range setting load resistors are connected to line  $E_1$  to select the proper ladder output voltage range for the transducer being sampled (Figure 40).

#### Programmer

The programmer B-counter is similar in function and operation to the converter A-counter. It consists of only three counting

Figure 40. Low-Level Scanner.

flip-flops giving a total of eight ( $2^3$ ) different decodable states per cycle (Figure 41). The counter is triggered by input  $S_2$ , which progresses the programmer by one step after every converter balancing sequence.

Decoding logic consisting of four AN-1's, (Figure 42), allows each state of the B counter to be decoded. The programmer outputs  $P_0$  thru  $P_7$  are thus generated to form a series of eight sequential sampling control pulses.

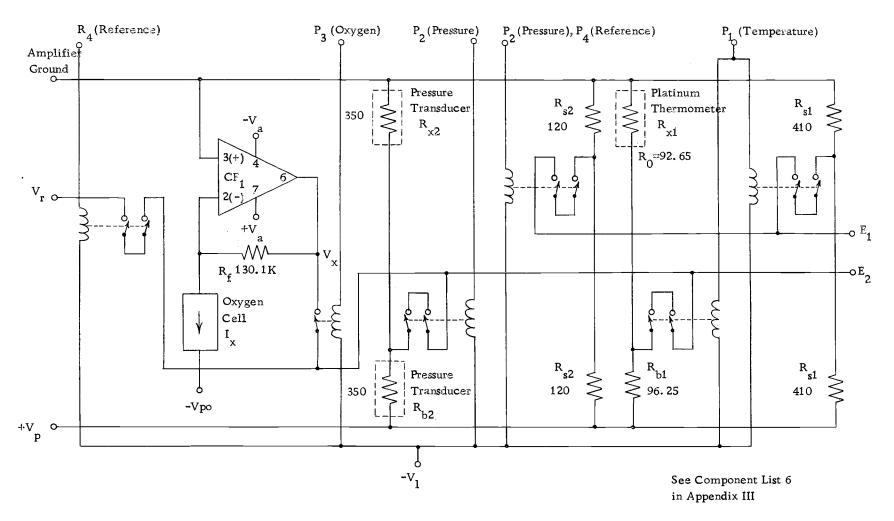

# Low-Level Relays

The low-level relays are actuated by the programmer outputs,  $P_0-P_7$ . Upon connecting one or more outputs to a single relay, one can program the frequency and duration of operation of that relay. In order to sample each transducer, two relays are required. They are actuated simultaneously by the same programmer outputs (Figure 43). One relay connects the transducer to line  $E_2$ , while the other connects the appropriate range setting load resistors  $R_s$  to  $E_1$ .

The relays were specially designed to minimize effects of contact resistance drift and thermally generated EMF. Two series-connected mercury wetted reed switches are used to minimize contact resistance drift, while matched pair and thermal blocking techniques are used to reduce the thermally generated EMF (Appendix IIa). The low-level relays have a constant contact resistance of approximately

Figure 41. Programmer B-Counter.

Figure 42. Programmer Decode Logic.

Figure 43. Low-Level Multiplexer and Transducers.

100 milliohms. A maximum EMF of  $10\,\mu v$ , was generated across the copper switch leads when a relay was operated continuously at a solenoid voltage of  $14\,v$ , in a  $5\,^{\circ}$ C air environment. This was approximately one-seventeenth of the EMF generated by a single, un-blocked mercury wetted reed switch operated under similar conditions.

## Range-Setting Load Resistors

The circuit as drawn in Figure 43 shows the connections between the programmer outputs, low-level relays, range-setting load resistors, and transducers. The portion of the zero to  $V_p$  voltage range over which the binary ladder output voltage,  $E_1$ , will vary is determined by the value of the range-setting load resistors,  $R_s$ . The following formulas were derived to relate the parameters  $E_1$ ,  $R_s$ , and p.

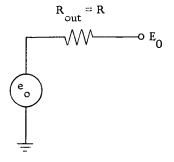

The loaded ladder network in Figure 44 reduces to the following equivalent circuit of a straight binary ladder network derived by Smith (24, p. 1054) and Susskind (27, p. 5-35), when the rangesetting load resistors are removed (i.e.,  $R_g = \infty$ ).

Figure 44. Binary Ladder Network with Range-Setting Load Resistors,  $R_s$ .

$$e_0$$

= Equivalent voltage source =  $\frac{\sqrt{p}}{2^N}$  p

p = Binary number,

$$S_1 S_2 ... S_N$$

$$= \sum_{n=1}^{N} S_{N-n+1} 2^{n-1}$$

N = Number of ladder stages

$$S_{N-n+1}$$

= Switch position = 0 or 1

Adding equal range-setting load resistors to the above equivalent circuit gives the following partial equivalent circuit for Figure 44.

When  $S_1$  thru  $S_N$  are all "0", e is zero,  $R_{out}$  is essentially connected to ground, and  $E_1$  is at its minimum value as calculated from the voltage divider equations:

$$E_{1(min)} = \frac{V_p R \parallel R_s}{R_s + R \parallel R_s} , \qquad R \parallel R_s = \frac{R R_s}{R + R_s}$$

$$E_{1(\min)} = \frac{V_{p} \left(\frac{RR_{s}}{R+R_{s}}\right)}{\frac{RR}{R_{s} + \frac{s}{R+R_{s}}}} = \frac{V_{p}RR_{s}}{RR_{s} + R_{s}(R+R_{s})} = \frac{V_{p}R}{R_{s} + 2R}$$

$$E_{1(min)} = \frac{2V_pR}{2(R_s + 2R)} = \frac{V_p(R_s + 2R - R_s)}{2(R_s + 2R)}$$

$$E_1(min) = \frac{V_p}{2}(1 - \frac{R_s}{R_s + 2R}) = \frac{V_p}{2} [1 - \frac{RR_s}{R(R_s + 2R)}]$$