#### AN ABSTRACT OF THE THESIS OF

Mark R. Milden for the degree of Master of Science in

Electrical and Computer Engineering presented on February 10, 1984.

Title: An Approach for Selecting a Language for Computer Hardware

Description and Simulation.

Redacted for Privacy

Abstract approved:

V. Michael Powers

This paper corrects an apparent deficiency in the published information concerning Hardware Description Languages (HDLs) by introducing and discussing an approach for selecting an HDL for use in a design project. Although three classes of HDLs are discussed in this paper, High-Level Languages (HLLs), General Purpose Simulation Languages (GPSLs) and Computer Hardware Description Languages (CHDLs), the CHDL class has been most heavily emphasized. These have been emphasized because they have been found to be the most suitable for use as a digital design tool. The emphasis is realized by including a chapter reviewing CHDL fundamentals, by presenting several CHDL examples and by aiming the HDL selection approach toward choosing a CHDL. HLLs and GPSLs are appropriate selections for some digital design environments. Therefore these classes of HDL have also been discussed in this paper.

## AN APPROACH FOR SELECTING A LANGUAGE FOR COMPUTER HARDWARE DESCRIPTION AND SIMULATION

Ъу

Mark R. Milden

#### A THESIS

submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Master of Science

Completed February 10, 1984

Commencement June 1984

#### APPROVED:

# Redacted for Privacy

Associate Professor of Electrical and Computer Engineering in charge of major

| or major                                                  |

|-----------------------------------------------------------|

| Redacted for Privacy                                      |

| Head of Department of Electrical and Computer Engineering |

| Redacted for Privacy                                      |

| Dean of Graduate penool                                   |

|                                                           |

|                                                           |

| Date thesis is presented February 10, 1984                |

| Typed by Jackie Morse for Mark R. Milden                  |

### TABLE OF CONTENTS

|    |       |                                                          | Page |

|----|-------|----------------------------------------------------------|------|

| 1. | INTRO | DUCTION                                                  | 1    |

| 2. | CHDL  | REVIEW                                                   | 6    |

|    | 2.1.  | Early Languages                                          | 6    |

|    | 2.2.  | General Characteristics of CHDLs                         | 21   |

|    | 2.3.  | Review of Two CHDLs                                      | 26   |

| 3. | AVAIL | ABLE HDLs                                                | 45   |

|    | 3.1.  | High-Level Programming Languages                         | 45   |

|    | 3.2.  | General Purpose Simulation Languages                     | 52   |

|    | 3.3.  | Computer Hardware Description Languages                  | 57   |

| 4. | AN HI | OL SELECTION APPROACH                                    | 108  |

|    | 4.1.  | Should an HDL be Used?                                   |      |

|    | 4.2.  | Selecting a Class of HDL                                 | 115  |

|    | 4.3.  | Selection of an Individual HDL: Technical Considerations | 119  |

|    | 4.4.  | Selection of an Individual HDL: Practical Considerations | 137  |

| 5. | SUMM  | ARY                                                      | 142  |

|    | BIBL  | IOGRAPHY                                                 | 144  |

## LIST OF FIGURES

| Figur | <u>Figure</u>                                         |      |  |

|-------|-------------------------------------------------------|------|--|

| 1.    | RTL Description of a Simple Computer                  | 12   |  |

| 2.    | APL Description of Complete Instruction Fetch         | 16   |  |

| 3.    | LOTIS Description of Simple Computer Sequence         | 20   |  |

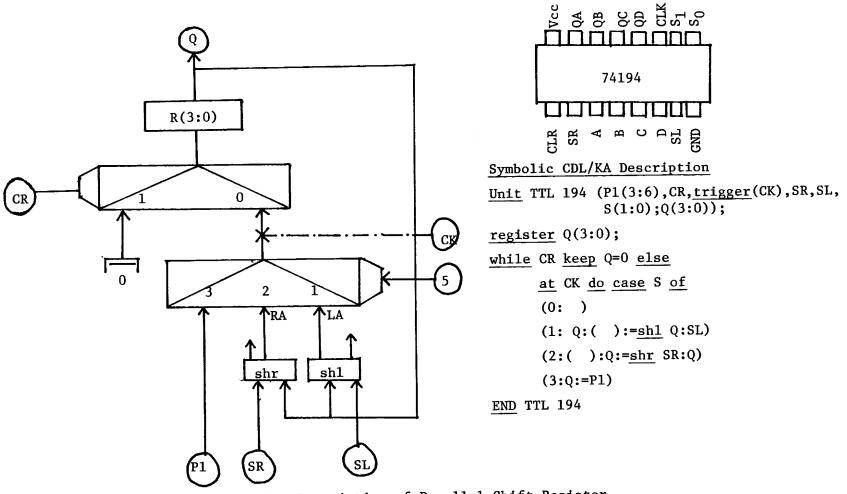

| 4.    | Example CDL Description                               | 34   |  |

| 5.    | Example DDL Description                               | 44   |  |

| 6.    | HLL Descriptions and Corresponding CDL Description    | 51   |  |

| 7.    | GPSS Program to Simulate Bank Teller Window           | 55   |  |

| 8.    | SIMSCRIPT II Program to Simulate Bank Teller Window   | 56   |  |

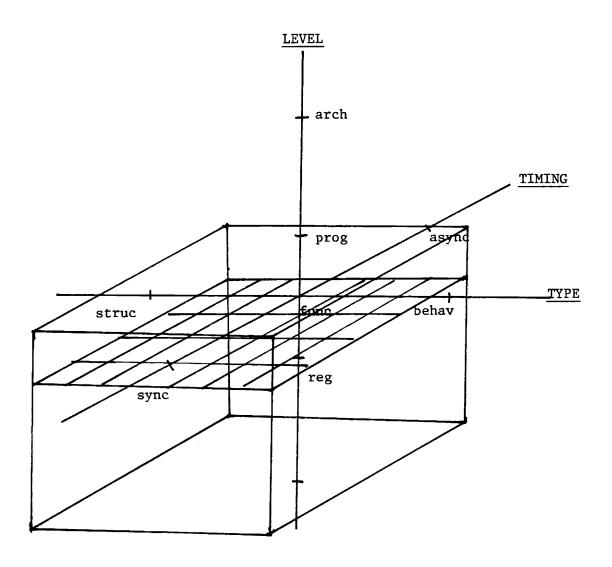

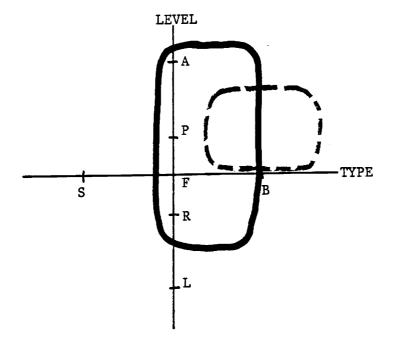

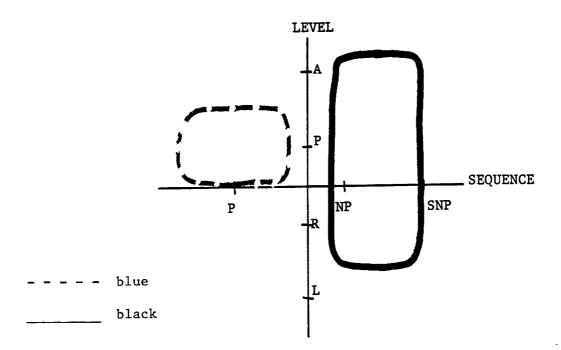

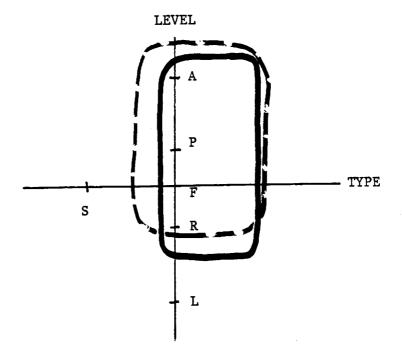

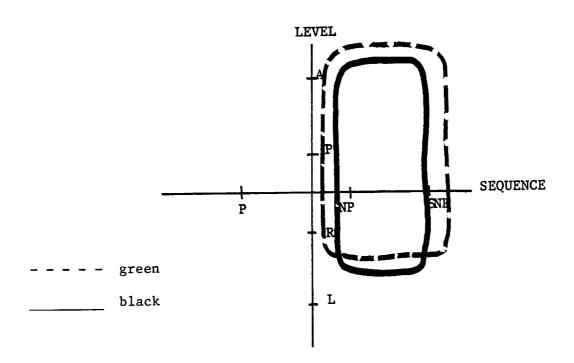

| 9.    | Three-Dimensional View of CHDL-Space                  | 63   |  |

| 10.   | ADLIB Descriptions of Two Logic Components            | 67   |  |

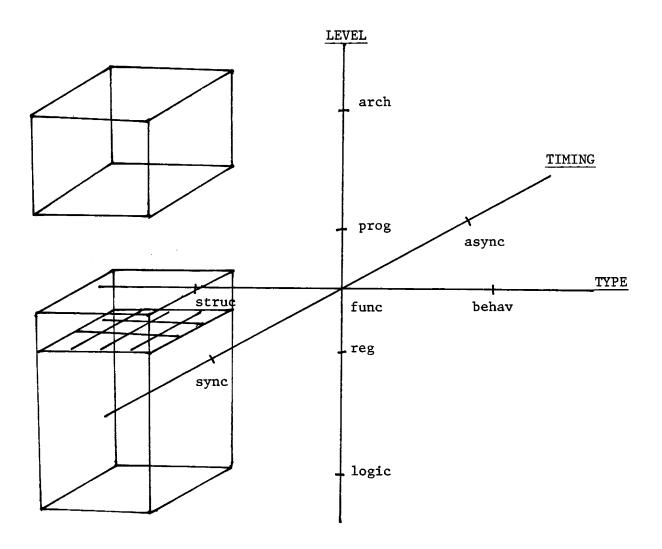

| 11.   | ADLIB Representation in CHDL-Space                    | 68   |  |

| 12.   | AHPL Description of 8's Complement Logic Network      | 72   |  |

| 13.   | AHPL Representation in CHDL-Space                     | 73   |  |

| 14.   | CDL Representation in CHDL-Space                      | 75   |  |

| 15.   | DDL Representation in CHDL-Space                      | . 78 |  |

| 16.   | FLOWWARE Description of a Serial Parity Bit Generator | . 80 |  |

| 17.   | FLOWWARE Representation in CHDL-Space                 | . 81 |  |

| 18.   | ISPS Description of an 8-bit Multiplier               | 83   |  |

| 19.   | ISPS Description of the Manchester Mark 1 Computer    | - 85 |  |

| 20.   | ISPS Representation in CHDL-Space                     | - 86 |  |

| 21.   | KARL Description of Parallel Shift Register           | - 89 |  |

| 22 -  | KARL Representation in CHDL-Space                     | - 90 |  |

## LIST OF FIGURES (con't)

| <u>Figure</u> |                                                 |     |

|---------------|-------------------------------------------------|-----|

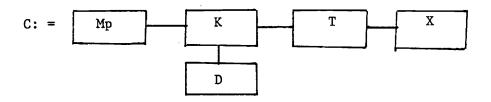

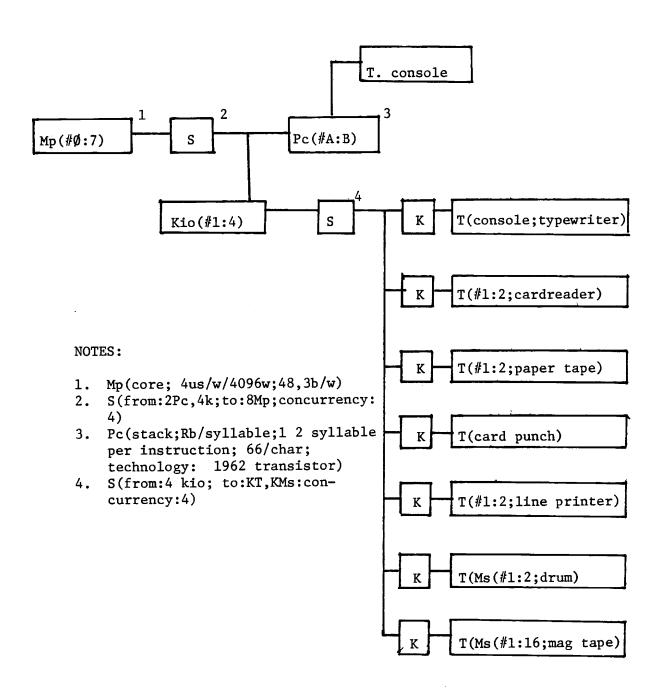

| 23.           | PMS Description of B5000 Computer               | 92  |

| 24.           | PMS Representation in CHDL-Space                | 93  |

| 25.           | SDL Description of 16-bit Shift Register        | 96  |

| 26.           | SDL Representation in CHDL-Space                | 97  |

| 27.           | Partial SLIDE Description of UNIBUS             | 99  |

| 28.           | SLIDE Representation in CHDL-Space              | 100 |

| 29.           | Two-Dimensional View of Example Design Criteria | 133 |

| 30.           | CDL Overlaid With Design Criteria               | 134 |

| 31.           | ISPS Overlaid With Design Criteria              | 135 |

| 32.           | DDL Overlaid With Design Criteria               | 136 |

## LIST OF TABLES

| <u>Table</u> | <u> </u>                | Page |

|--------------|-------------------------|------|

| 1.           | CDL Primitive Operators | 31   |

| 2.           | DDL Primitive Operators | 38   |

| 3.           | CHDL Summary            | 105  |

## AN APPROACH FOR SELECTING A LANGUAGE FOR COMPUTER HARDWARE DESCRIPTION AND SIMULATION

#### 1. INTRODUCTION

The introduction of VLSI into the world of digital design has provided hardware engineers with a good reason to develop a new approach for designing digital hardware. In the days of SSI and MSI it was possible for a designer to keep track of the overall structure and behavior of a hardware design by using logic diagrams, Boolean equations and his own memory. As systems grow in complexity in the VLSI era, it becomes increasingly more difficult for a designer to keep track of a design, resolve design problems or communicate the design to others without the assistance of a computer. A new hardware design approach must include the ability for computer-aided design (CAD) work.

With many of the current design approaches it is popular to partition the digital design world into several layers of abstraction. The lower levels of this hierarchy (the circuit and logic levels) are well defined and in use throughout industry on design projects. The next higher level, the register transfer (RT) level, is a relatively new level with respect to its use in digital hardware design projects. However, there are several advantages to doing design work at the RT level. The purpose for moving up to this level is to abstract (i.e., disassociate from any specific entity) [W077] the structure and behavior of the lower levels and focus the design onto a higher-level picture of a digital system.

A new design approach that utilizes the RT level of abstraction is beginning to gain acceptance with designers.

The design tools that are needed to allow useful work at the RT level are: a concise, yet precise, hardware description at this level and a method for performing RT level simulations of the hardware description. The need for a concise method of describing a digital design with thousands of gates is very apparent. This description must also be a precise one in order to reduce ambiguity in the design and allow for development of the software in unison with the hardware. The use of simulation aids designers by increasing their understanding of how a design will actually behave, and thereby allowing them to locate and concentrate on the critical areas of the design. Simulation will also reduce the number of prototypes that will need to be built, saving money in design costs and getting the product out the door in less time.

There are three classes of formal languages that can fulfill both the description and simulation requirements of the register transfer level design tools. These classes are grouped together into a set called Hardware Description Languages (HDLs). The three individual classes of languages that make up the set of HDLs are: the High-Level Languages (HLLs), the General Purpose Simulation Languages (GPSLs) and the Computer Hardware Description Languages (CHDLs).

HDLs provide a means of attaining computer assistance in hardware design. Thus, the use of an HDL-based design approach is an efficient method for dealing with the complexity of VLSI design projects. An HDL design approach is realized by implementing an HDL on a host computer which then becomes an HDL-based design system. Several papers have been published that present the many advantages of using an HDL design system for digital hardware design [Br66, Br72, Ba75, Sh79a].

There are several implementation-related questions that need to be answered when developing an HDL-based design system. The purpose of this paper is to answer one of these questions. This topic question is:

HOW SHOULD AN HDL BE SELECTED FOR USE IN A DESIGN SYSTEM?

This is an important question to answer as it deals with the selection of the best available language for satisfying the requirements of a proposed design system. It is also a question that has not been well addressed in the current HDL-related literature. To answer this topic question a three-step approach for selecting an HDL will be presented.

The first step of this approach is to select one of three classes of HDLs as being best suited for a design task. This is done by comparing the advantages and disadvantages of using each class for hardware design purposes. The second step is to select a small group of languages that possess a majority of the technical features needed to make a language useful for the particular design environment. The third, and final, step of this selection approach is to develop an order of preference within the group of useful languages based on some practical considerations.

This approach will include making a selection from any of the three HDL classes. However, the CHDL class will be the most heavily emphasized because of the design industry's lack of familiarity with CHDLs and the languages' superior suitability for hardware description and simulation purposes. This emphasis will be carried out throughout the entire paper.

This paper has been written with two secondary purposes in mind. The first of these is to increase a designer's familiarity with CHDLs by reviewing some of the historical background, general language constructs and specific examples of this class of HDL.

The second purpose is to compile a bibliography of CHDL-related literature to serve as a useful starting point for further research.

Chapter Two is devoted entirely to a review of CHDLs, as they are relatively new and not well known by designers. On the other hand, HLLs and GPSLs are older and thus better known by the design industry. This chapter provides information aimed at helping the reader to more familiarity with the fundamentals of CHDLs. It includes an examination of three early CHDLs, a look at the syntax of a general CHDL and description and examples of two popular CHDLs.

Chapter Three presents some of the languages that are available for use in hardware description and simulation projects. This is accomplished by discussing the advantages and disadvantages of using each of the three classes of HDLs and then examining specific languages from each class. HLLs and GPSLs are discussed first as they are already familiar to most designers. Only two example languages are presented for each of these classes because languages

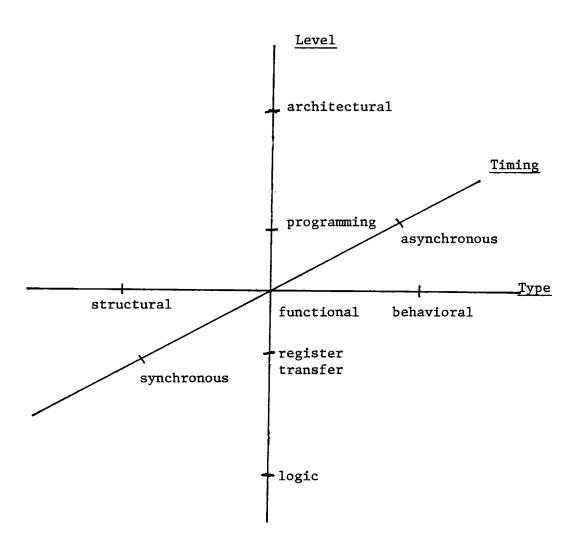

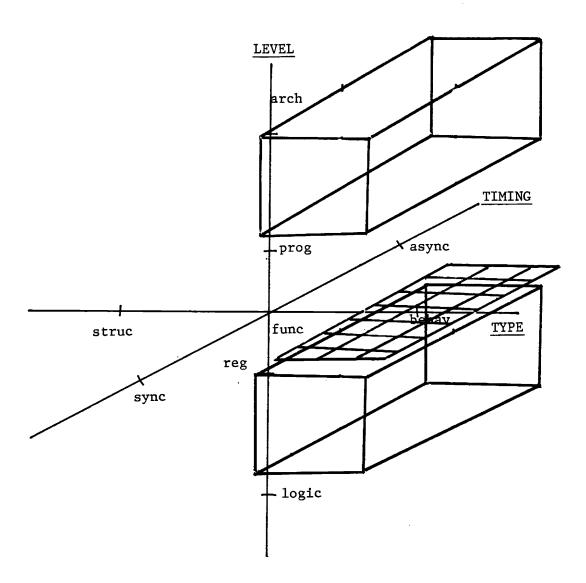

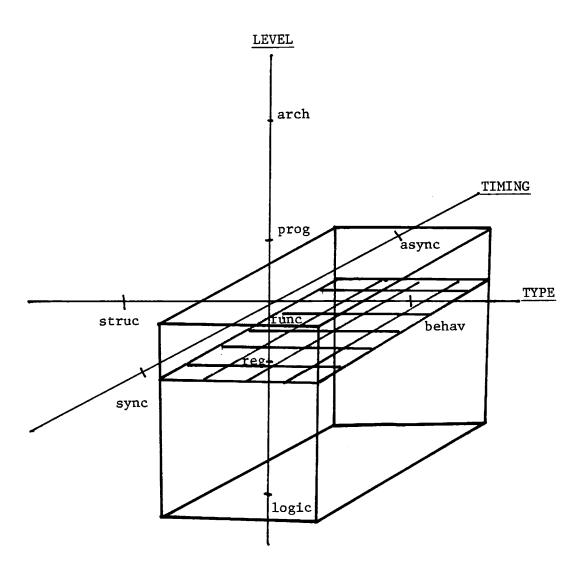

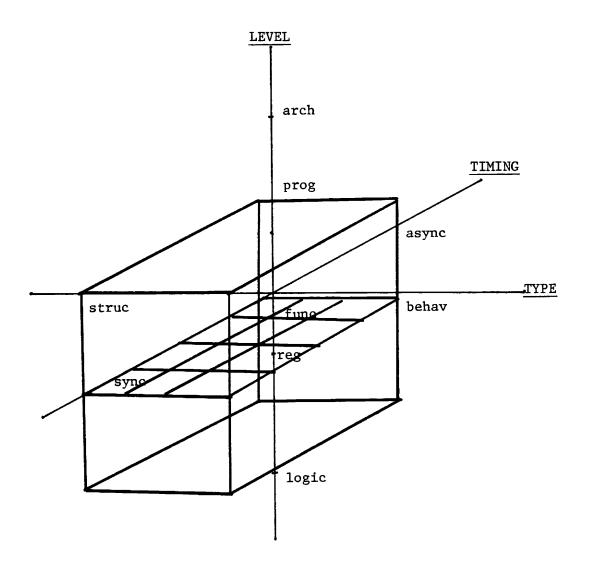

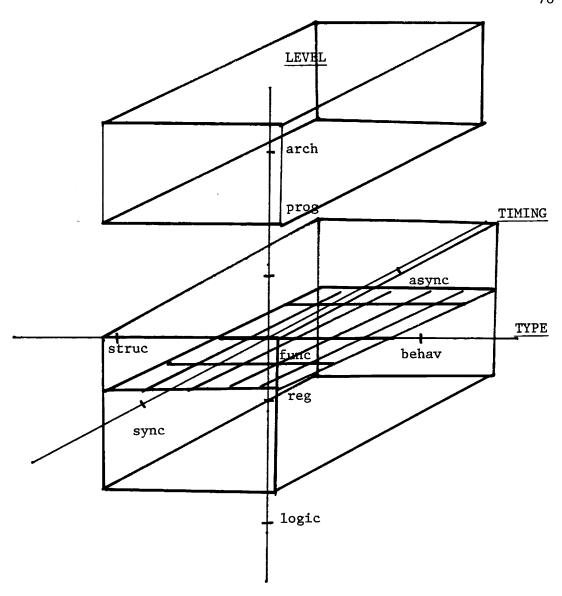

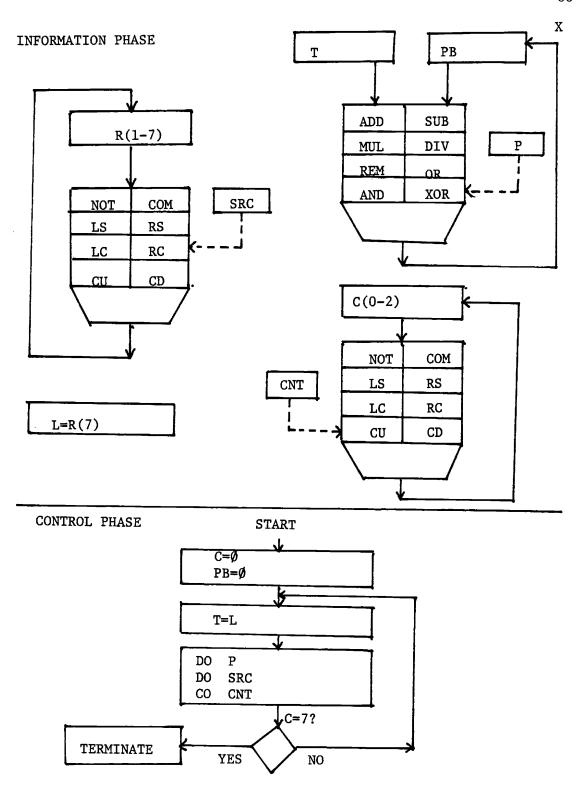

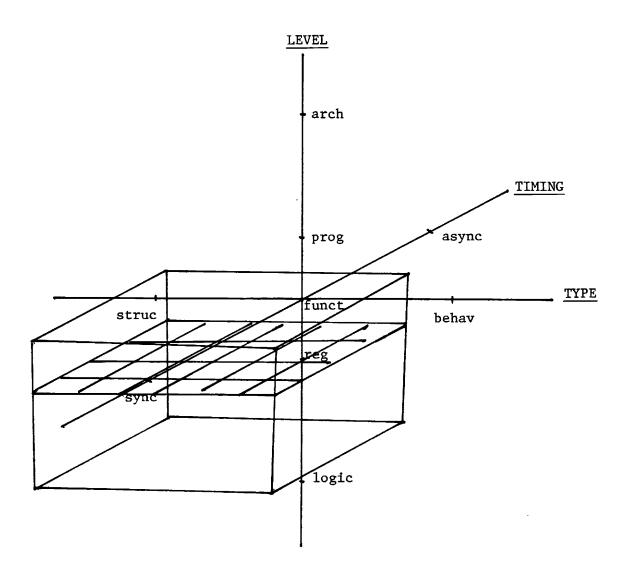

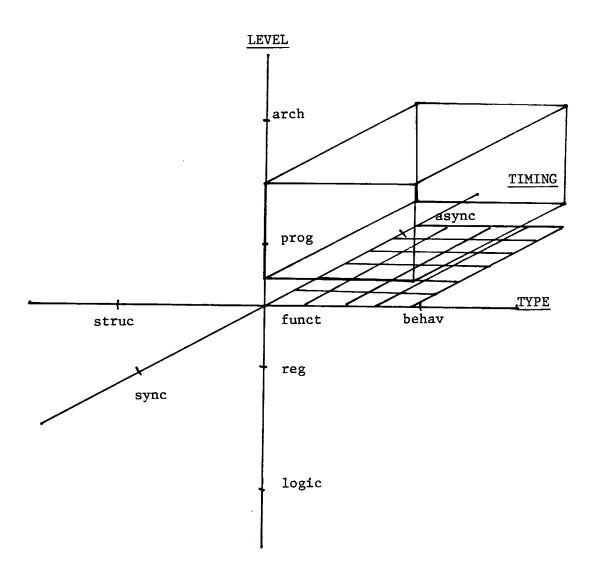

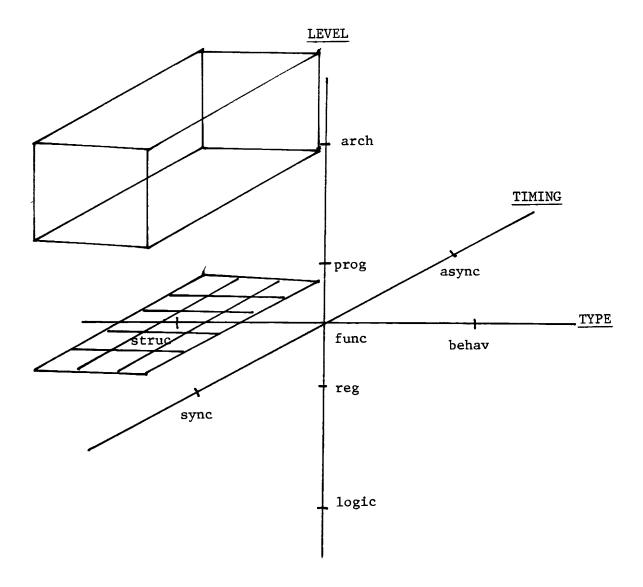

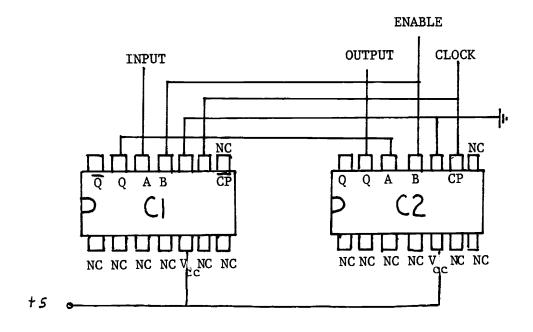

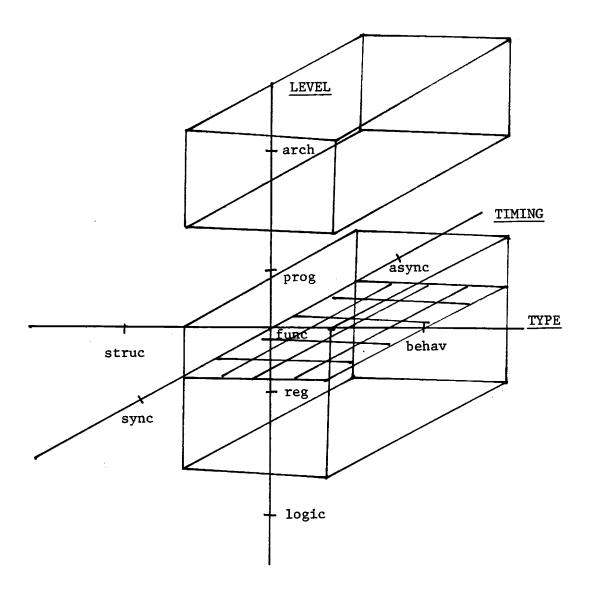

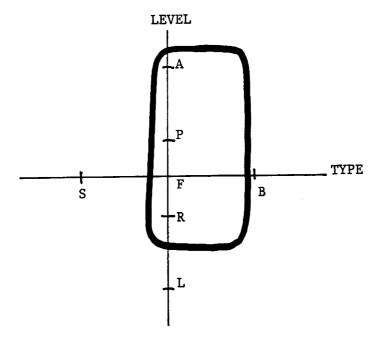

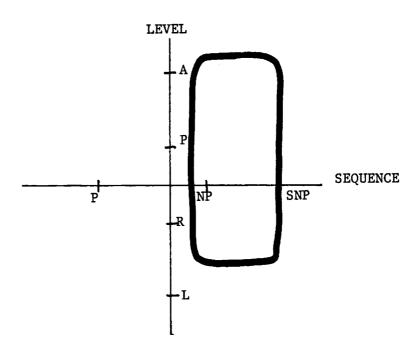

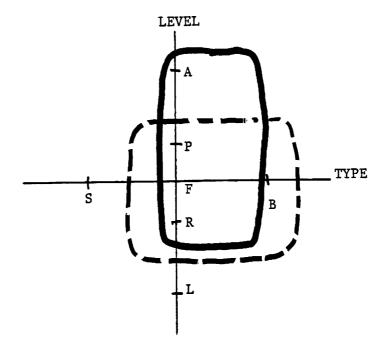

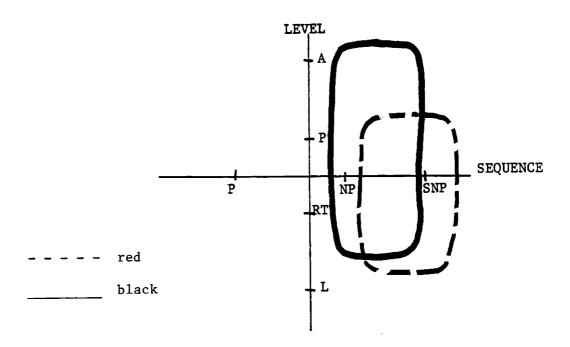

within each class are very similar both in structure and use. CHDLs offer a wide range of structures and uses. No single language can be used to describe the entire class, so ten individual examples are presented. This section also introduces a four-dimensional CHDL space. This is used in Chapter Four to aid in the selection of languages based on technical considerations. Following the ten relatively detailed examples, 14 other languages are briefly discussed to provide a more complete listing of available CHDLs. All 24 CHDLs are summarized in Table 3, located at the end of this chapter.

Chapter Four introduces and discusses the HDL selection approach. This chapter is divided into four sections; the first two are aimed at all three classes of HDLs while the last two emphasize the CHDL class. The first section reviews some of the reasons for using an HDL for design purposes. Section 2 discusses the selection of an appropriate class of HDL for particular design environments. Sections 3 and 4 examine the selection of individual languages based on the fact that a CHDL is to be selected. An example of selecting an HDL for use in an academic environment is developed throughout this chapter.

Finally, Chapter Five gives a summary of the ideas presented in this paper.

#### 2. CHDL REVIEW

While most hardware designers have had some hands-on experience with HLLs, very few have ever worked with a CHDL. To increase a designer's familiarity with this class of languages, several aspects of CHDLs will be reviewed. This chapter has been organized into three main areas, each presented in a separate section. The first of these sections discusses three "historic" CHDLs. Special emphasis is given to constructs that were introduced by these languages and have become common features of modern CHDLs. The second section uses many of these original constructs to develop a set of general features that can be used to characterize individual languages. The final section of this chapter will review two popular CHDLs with respect to the features presented in Section 2.2.

#### 2.1. Early Languages

The languages from the first generation of CHDLs can be classified into three groups. This classification scheme is based on the approach used to develop a particular language. The first group includes those languages that were developed from scratch as dedicated hardware description languages. The second group includes the languages that were developed as high-level programming languages that had some applications in the hardware description area. The final group includes those CHDLs that were adapted from high-level programming languages and converted into hardware oriented languages with the addition of special data structures for hardware description.

This section will review one language from each of these groups. The languages chosen (RTL, APL and LOTIS) are usually referred to as the first CHDL to appear from each of the corresponding groups. For each language an explanation of the reasons leading up to the development of the language and a brief look at some of the unique features of the language will be given. The purpose of these introductions is to present some general features common to all CHDLs rather than to examine the languages in detail.

#### A. Introduction to RTL

Perhaps the earliest example of any CHDL is the Register Transfer Language (RTL). This notational scheme was developed in the 1950s and early 1960s by I.S. Reed. The RTL language was first presented in an ACM report in 1952 [Re52] and then used 10 years later in two textbooks on digital computer design [BL62,Ch62]. The philosophy behind the development of RTL was that all operations of a digital computer could be expressed by means of transfers between the registers of the system. RTL was created as a notational means for recording these transfers and thus became an early description language for digital computers.

In a design procedure based on the use of RTL the following three design phases were introduced: [BL62]

(1) The System Design phase - which outlines the overall configuration of the machine and the class of hardware structures to be used.

- (2) The Structural Design phase which describes the system in terms of the transfer relations between the registers.

- (3) The Logic Design phase which realizes the transfer relations by means of Boolean equations.

The RTL language was the key factor in making this digital design process work. In fact, the entire structural phase depended on the use of RTL to provide the register transfer descriptions. The descriptions at this level detailed the registers and the allowable transfers between those registers. A digital machine was regarded as a set of registers communicating with one another by means of the transfer operations allowed for that machine. Thus, the operation of a computer could be described by a set of transfer relations written in RTL.

The main advantage to using this type of descriptive technique for design work is in the notation. The RTL description is a short-hand way of designating a potentially complex set of Boolean equations, which may themselves specify a complex set of electronic operations. These transfer descriptions are intended to provide only the minimum amount of detail necessary to specify the machine at the register transfer level.

Once the RTL description is available, the individual transfers may be implemented by translating the transfer relations into Boolean equations and then by realizing the equations as logic components. Although RTL did not provide a means for automatically translating the register transfer descriptions into logic equations, an algorithm for completing this translation by hand was presented

with the RTL language [BL62].

The basic statement of the RTL language is the transfer statement. All of the various RTL statements are of this same format. The general form of this statement is:

CONTROL CONDITION / f(set of registers) — destination register

The control condition is used to allow for synchronous operations

by requiring a clock-like condition signal to be set true before the

register transfer is allowed to take place. The · / · symbol is used

to denote the division between the condition section and the register

transfer section. The actual transfer operation is some function of

one or more registers with the result being sent to a single destination register for storage. A typical example of an RTL statement,

shown below, reads as follows: when the signals f and p are both

$$f \cdot p / A \longrightarrow B$$

set true then the content of register A is transferred to register B.

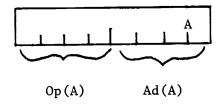

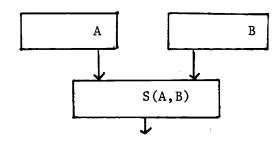

The RTL language allows for only four elements that can store information. These four elements are memories, registers, subregisters and dependent registers. The most important of these is the register which is denoted by a capital letter. The memory unit is thought of as an array of registers and is usually denoted by a capital M. A particular word in the memory is referenced by placing the address of the word into a general purpose register that can serve as an address register. A subregister is a section of a register and is denoted by a two letter identifier followed by the register of interest as a parameter. A dependent register is a

special type of register that is dependent on inputs from two or more registers, such as an adder. The notations for both the sub-register and the dependent register are given below. Single bits of any of these elements can be specified by using a numeric subscript following the identifier for that element. The subscript represents the particular bit or bits of interest.

RTL has no provisions for declaring the word lengths of memory or the sizes of individual registers or subregisters. Declarations such as these, which are very important to provide a precise RTL description, are made by developing a block diagram of the object machine and including the necessary information on that diagram. When a designer wants to create an RTL description of some machine he must first develop the block diagram for that machine. diagram should include identifying names for all of the registers and memories that will be referenced by the RTL description. sizes of the individual registers (in terms of the number of bits stored by each) and the allowable data paths between the registers must also be indicated on the block diagram. Once the block diagram (or an equivalent type of documentation) has been completed, the RTL description can be easily worked out. The block diagram serves as the structural description of the system and the RTL description serves as a behavioral one.

One of the most important functions for a behavioral description of a digital computer is to describe the instruction fetch, interpretation and execution sequences used by a particular design. These sequences are basic to the functioning of a computer and the

Subregister Identifiers

Dependent register: S(A,B)=A+B defines S(A,B) as an adder.

designer must have a detailed understanding of how these sequences behave. This understanding should include the register transfers for each of the sequences and a timing study to determine if any timing problems exist.

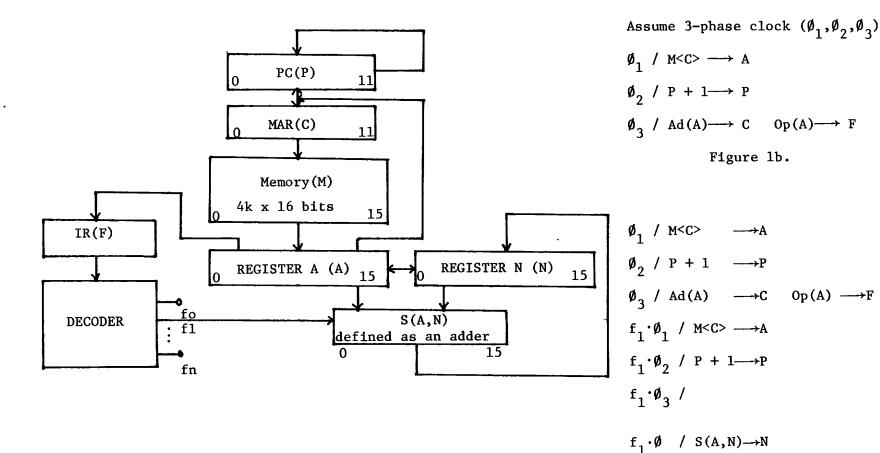

RTL has features to provide a means for performing such timing studies. Timing is carried out by defining an amount of time equal to one clock cycle and then writing all register transfers in reference to that amount of time. Multiple phase clocks can also be denoted in RTL.

Two sample sequences of the simple computer shown in Figure 1 have been written in the RTL notation. The first sequence (Figure 1b) describes an instruction fetch routine for the computer. The second sequence (Figure 1c) describes a typical machine instruction involving both an instruction and operand fetch.

The typical addition instruction for this computer might read as follows: add the number in memory location X to that in register A and store the sum back into register A. This instruction will take three clock cycles to complete: the first to obtain and interpret the instruction, the second to fetch the operand and the third to execute the addition. Notice that after the instruction

Figure 1c.

$f_1 \cdot \emptyset_2$  /

$f_1 \cdot \emptyset_3 /$

RTL Description of a Simple Computer Figure 1

has been decoded, the control line f is asserted and ANDed with the clock phases to allow activation of the remaining statements. No information concerning the amount of time required to complete an operation is given in these examples. After the instruction has been decoded, the correct control lines will be asserted ( $f_1$  in this case). This control line is ANDed with the clock to provide a new set of control signals for the next sequence of register transfers.

The RTL language introduced many major concepts to the family of CHDLs. The most important of these was the idea of, and a method for, describing the behavior of a digital machine. The language also allowed for timing considerations, individual bit operations, and concurrent activities. All of these features were first introduced by RTL and are still considered to be essential features of today's CHDLs.

Despite the initial promise of Reed's language there were several items lacking from it. RTL lacked a structural description that could be incorporated into the language descriptions, a method for describing iterative sequences (i.e. branches), a method for decoding instructions efficiently and a method for describing complex addressing modes. Several second-generation CHDLs were developed, based on the RTL language, to correct these faults [Sc64b,Ga62,Pr64,St70].

#### B. Introduction to APL

The earliest example of a programming language that was used for hardware descriptions was A Programming Language (APL). APL

was developed in the early 1960s by K.E. Iverson [Iv62a, Iv62b]. The original purpose of APL was to provide an effective notation for the description of programs for digital computers. A new type of language was needed to move away from the lengthy English and imprecise flow-chart descriptions popular at the time. This new language needed to be precise, concise, provide symbols that were similar to the types of data they were to represent and be independent of any particular data representation. While this language was developed for program descriptions it possessed many of the same features desired in a hardware description language.

In the design and development of a computer it is important to have a very precise description of the system so that hardware and software designers can work toward their common goal without needing to know the details of what the other groups are doing. This can be accomplished by using a language that fits the needs of both design groups. APL was proposed as such a language at a conference in 1962 [Iv62b].

If a program for a digital computer is considered to be a sequence of instructions and if those instructions are considered to be a sequence of register transfers, then the method of applying APL to hardware descriptions comes to light. APL deals with register transfers by using one and two dimensional arrays (to represent registers and memories) and by representing data in binary notation. In APL, a single register transfer description is called a microprogram statement and a sequence of these is called a microprogram (which is equivalent to an instruction).

The APL language provides a rich set of data operators, an efficient facility for handling arrays of various sizes and an indexing facility. This made the APL language popular for hardware descriptions. Unfortunately, APL was also developed with conciseness in mind which usually lead to some long and complex statements. This fact combined with APL's non-standard precedence algorithm (right to left) makes APL descriptions hard to read. As an example of this an APL description of a complete instruction fetch microprogram is provided in Figure 2. There are several good sources explaining APL statements and data structures from a programming language approach [Pa76a, Le78, Iv62a].

In addition to providing hard-to-read hardware descriptions, the APL language has some other drawbacks. The most obvious of these is the inability to describe any parallel system. Other drawbacks include a lack of timing capabilities, no way to declare register sizes and a non-block structure. These problem areas have been accounted for in newer CHDLs that are based on the APL language [HP73].

APL was an important step in the development of CHDLs as it increased the number of data operators available beyond the set provided by the RTL language. At this point designers had two languages to work with. Designers preferred the RTL format and readability and the APL data operators and array handling capabilities. These two areas were combined with the introduction of the LOTIS language.

Lines 2-8 Channel trapping

Lines 9-10 Instruction fetch

Lines 11-18 Instruction preparation (with indirect addressing)

APL Description of Complete

Instruction Fetch

Figure 2

(taken from example presented in Iverson, 1962a)

#### C. Introduction to LOTIS

A third example of an early CHDL is the LOTIS language that was introduced by H.P. Schlaeppi in 1964 [Sc64a]. LOTIS is a formal language for describing the LOgical structure, the TIming and the Sequence of digital machines. This was developed to provide the designer with a precise notation for expressing both the structural and the behavioral properties of a digital design. LOTIS was the first CHDL to provide for structural description facilities [Sc64a].

The development of the LOTIS language was based on the following five goals:

- (1) The language should be able to describe both structure and behavior.

- (2) The elements of the language should correspond directly to the hardware units they are to represent.

- (3) The notation of the register transfer level should abstract the details of the lower design levels.

- (4) The description of a machine using the LOTIS language should have a hierarchical structure.

- (5) Timing and concurrent events should be represented by this language.

The LOTIS language was developed from the ALGOL programming language. LOTIS combines the structure of ALGOL with several new data types and operators to create a hardware description language that meets each of the five goals. This development approach differentiates LOTIS from RTL which was developed from scratch and from APL which was developed as a high-level programming language.

LOTIS was an important step in the development of CHDLs since it effectively combined the best features of the earlier two languages. The type of easy-to-read statement formats and the timing capabilities presented by the RTL language were incorporated into LOTIS. The improved and varied data operators provided by a programming language (ALGOL rather than APL) were also used for the LOTIS language.

The description of a machine in this language is composed of a declaration section and a procedure section. The declarations are used to define the structure, logical and temporal properties of hardware units and also to assign names to those structural units. The procedural section is used to describe the behavior of the machine in terms of the declared hardware units.

The behavioral elements of LOTIS are register-to-register transfers. Each of these transfers is accomplished via a data path.

These data paths, in combination with the declared hardware units, detail the structure of the digital machine. The data paths are defined by assignment statements in the procedural section of the LOTIS description. A group of these assignment statements makes up a sequence which is equivalent to an instruction.

Timing in a LOTIS description can be described either explicitly by associating a transfer timing delay with an assignment statement, or implicitly by using a delay time that was declared for the particular operator occurring in the assignment statement. The latter mode allows for descriptions of asynchronous events in an efficient manner. Timing can also be expressed by assuming time

intervals for each statement (such as one clock cycle for a simple register transfer); this form is useful for synchronous operations.

LOTIS was the first language to allow simulation of its computer descriptions on another computer. While the LOTIS description needed much additional overhead, including an initialization procedure and commands specifying what the simulation is to do, the first groundwork for simulating digital designs had been laid.

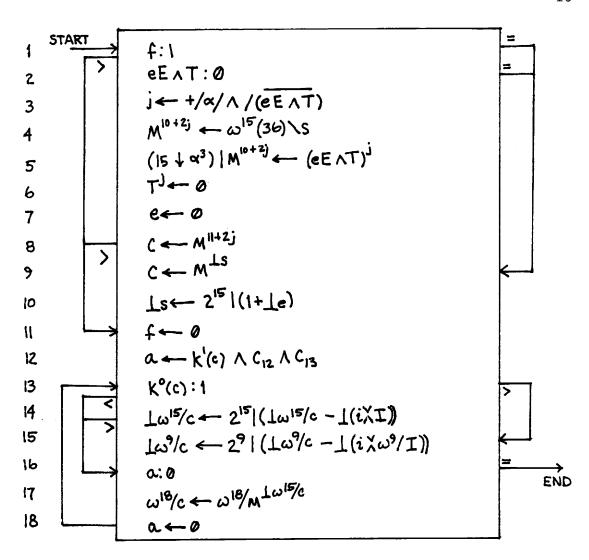

An example of an instruction fetch and an addition sequence for a simple computer are given in Figure 3.

From studying the reasons for developing the three previously described languages, a group of these that are common to each language stand out. These reasons or goals for CHDLs are:

- 1. To describe digital hardware of the register transfer level.

- 2. To provide behavioral descriptions of digital systems.

- To make the behavioral description as precise and concise as possible.

These goals still remain today and are addressed by all of the languages presented later in this paper.

Many improvements in the next-generation CHDLs quickly made these first three languages impractical for industry use. With the added improvements, CHDLs have acquired some very complex characteristics. A discussion about some of the general characteristics of CHDLs will be presented in the next section.

```

cpu simple /

m(12b,16);

2(16) = [0-(4), ad(12)];

n(16);

Declaration

Section

c(12);

p(12);

f(4);

s(16);

seq instrfetch /

1: a := m(c) /

2: p := p + 1 /

3: c := ad; f : = op / fin

Procedure

Section

seq add /

1: a := m(c) /

2: p := p + 1 /

3: n := a + n / fin

```

LOTIS Description of Simple Computer Sequences Figure 3 (taken from an example in Schlaeppi, 1964a)

#### 2.2. General Characteristics of CHDLs

A CHDL can be characterized as having an alphabet, a syntax, and a set of semantics. An alphabet is a set of symbols that are used in the language. The syntax is a set of rules to be followed for combining the allowed symbols into meaningful language statements. The semantics are a set of interpretations for all possible statements. Since each CHDL is developed by a different person or for a different purpose, these three areas will be different for each language. Thus the alphabet, syntax and semantics of a language can be combined to act as a fingerprint for that language.

To describe a CHDL in terms of its alphabet, syntax and semantics is a very logical and straightforward process. However a complete description of this form would be much too long for this paper's purpose. Thus a short list of general syntactical and semantical features has been selected for discussion. This list will primarily include areas that an engineer would use as comparison points when selecting a CHDL. The discussion of these points will also serve to show how CHDLs differ from other classes of HDLs. The set of features chosen are:

Alphabet

Representation of Constants

Identifiers

Primitive Elements

Primitive Operators

Statement Types

Complex Operators

Order of Execution

Structure

Organization of Description

The ALPHABET of a language is a set of symbols that can be used to create descriptions in that language. Nearly all modern CHDLs use a subset of the ASCII character set. The following characters are common to all text-oriented CHDLs. Only additions to this character set will be shown in the language reviews following this section.

upper-case English letters (A,B,C,...,Z)lower-case English letters (a,b,c,...,z)decimal digits (0,1,2,...,9)common punctuation (,/./;/:/(/)/+/-/=)

It should be noted that while these characters exist in all languages they do not have standard meanings in all languages.

The method a CHDL uses to represent CONSTANTS varies greatly from language to language. The most common constants are the Boolean scalars (0 and 1) and the decimal integers (0,1,...,9). Other types of constants such as Boolean vectors, floating-point numbers characters and character strings are allowed by some languages. Integer representation is often allowed in several common bases, including binary, octal, decimal and hexadecimal. The use of such notational flexibility is useful in making descriptions in that language shorter and easier to read.

An IDENTIFIER is a symbol used to name a variable or primitive element. Typically an identifier is a single letter or a letter

followed by other letters or digits. The use of a complex identifer scheme is useful for allowing mnemonic variable names to be assigned.

The PRIMITIVE ELEMENTS of a language are those data structures that are used to hold and carry system information. These elements are called primitives because they are used as building blocks to construct higher level data structures and cannot themselves be broken down into lower level elements. For example, in most CHDLs a group of registers (a primitive element) can be combined to form a processor while they cannot be reduced to the gate or circuit levels. Primitive elements can be split into two classes depending on their storage capability. Some elements are memoryless, such as wires, buses and decoders. This type of element is used to transmit information. Other elements have memory, such as registers and memories, and are used to hold information. The complexity of primitive elements can vary from single-bit object (wires and flipflops), to bit vectors (buses and registers), to bit arrays (memories). Examples of some primitive elements can be found in the review of the two CHDLs in Section 3.

The PRIMITIVE OPERATORS found in each language are closely related to the particular elements used in that language. The operators are entities that produce new information by translating bit patterns stored in the elements according to a set of assigned meanings. The meanings are usually well understood by designers (e.g. AND, OR, NOT, ADD) but also typically have different representations for each language. Operators can vary in both size and type of transformation performed. The size can range from

single-bit operations and register operations up to memory (array) operations. A set of CHDL operators is developed by selecting one or more operators from each of the following groups:

Logical (AND, OR, NOT)

Arithmetic (ADD, SUB)

Comparison (GT, GE, LT, LE, EQ)

Rotational (SHIFT, ROTATE, CONCATENATION)

Special (COUNT-UP, SWAP)

The various STATEMENT TYPES are formed by combining constants, primitive elements and primitive operators together. These statements are used to describe the operation of the system and the interconnection of the system components. There are five common types of statements used by most CHDLs.

DECLARATION

DATA TRANSFER

CONDITIONAL

SEQUENCING

TIMING

Declaration statements are used to describe the system components and their interconnections. Data Transfer statements describe the action of operators. These statements also include information specifying when a statement is active. Conditional statements are used to allow iterative and decision making capabilities to the system description. Sequencing statements allow for correct operation of an algorithm providing for serial or parallel activities and unconditional jumps. Timing statements are used to

explicitly declare timing characteristics for components or activities of the system. To describe hardware completely a CHDL should have facilities for expressing each of these types of statements, although some languages may combine two or more statement types to create a more general statement format.

COMPLEX OPERATORS are formed as a collection of one or more statements. These operators can take the form of functions, procedures and subroutines. The use of these complex operators can be an efficient way to increase the readability and conciseness of a description.

The ORDER OF EXECUTION can be used to partition CHDLs into two groups. The first group consists of non-procedural languages, where some or all description statements require an attached condition label to be set true before the statement can be executed. The second group consists of procedural languages, those CHDLs where statements are executed in the order in which they are written in the description. For non-procedural languages sequencing is performed by modifying control variables used in the statement label to enable or disable a statement. The control variables can be changed explicitly by a condition statement or a data transfer statement, or implicitly by an independent hardware element such as a clock or decoder. Sequential and concurrent actions are allowed with both classes of languages although the statement forms will be slightly different.

The STRUCTURE of a description is that part of a language that allows for the physical aspects of the design to be reflected into

the description. Early CHDLs used a single block format in which all variables were global. Newer languages use the multiple hierarchical block structures common to most programming languages. Block structures can convey some of the modular aspects of a design and allow the description of multiple levels of detail within the same description.

The ORGANIZATION of a DESCRIPTION includes any conventions that might need to be followed when writing a description in a particular language. These conventions can include such things as rules for naming elements, an ordering of which statements should occur before others, and required components to perform specific tasks. Every CHDL uses a slightly different set of conventions thus making some languages better suited for special types of hardware design projects. Careful consideration should be given to this aspect when selecting or using a CHDL.

The list of CHDL characteristics presented in this section can be used as a guideline for learning about a particular language. These characteristics begin with fundamental language constructs and then use them to build a foundation on which to develop the more complex features and structures of a language. This approach will be used in Section 3 to review two common CHDLs.

#### 2.3. Review of Two CHDLs

This section will review two important CHDLs to help the reader gain an understanding of some of the features and structures present in this class of HDL. The languages selected for use here, the

Computer Design Language (CDL) and the Digital System Design Language (DDL), were chosen because of their easily accessible documentation and thus, their relative popularity (or vice versa). The partial hardware descriptions presented for each language (different systems are described) should be especially helpful in giving a designer a feeling for the structure of CHDLs.

## The Computer Design Language [Ch65, Ch70, Ch72a, Ch72b]

This language was developed to describe the structure and behavior of a digital system. The ease of reading CDL descriptions and the language's simple structure have made this language one of the most popular CHDLs [Sh79a].

The ALPHABET of CDL includes the standard set of ASCII characters and the following non-standard characters.

The blank is not a part of the CDL alphabet but it can be included in CDL descriptions (as with most CHDLs) to increase readability.

CONSTANTS in CDL are from one of two categories. The first consists of the Boolean constants 0 and 1 which correspond to FALSE and TRUE respectively. The second category includes integers from several common bases. The radices 2, 4, 8, 10 and 16 are allowed in CDL descriptions. The following examples are all valid CDL constants.

A CDL IDENTIFIER (or variable name) may contain up to six characters, the first of which must be alphabetic. An identifier may be followed by a subscript to indicate a specific bit position,

a range of values or a value from an array. The following examples are valid CDL identifiers.

A, START, MAR(16), ADDR1(0-11), M(16,0-15)

All PRIMITIVE ELEMENTS used in a CDL description must be defined and assigned a name with one of several types of declaration statements. These statements have the form

Element, body,

where the "Element" represents the type of elements being declared and the "body" of the statement is used to list the names and sizes of hardware components included in a description. A list of the element types and a brief definition of each is given below.

FLIP-FLOP A single bit storage element.

REGISTER A set of synchronized flip-flops.

SUBREGISTER A smaller section of a register.

CASREGISTER A cascaded set of registers.

MEMORY An array of synchronized flip-flops.

SWITCH An external input device.

LIGHT An external output device.

TERMINAL A combinational logic network.

DECODER A device to select specific output lines.

CLOCK A clock.

DELAY A delay element.

Several of these elements are of special interest because of the frequency of their use or special abilities they possess. The first of these are the REGISTER and MEMORY elements which are the most frequently used elements in CDL descriptions. The subscripts of the following examples are used to denote size and bit positions.

REGISTER, ACC(0-15), MAR(0-11), BUF(5-1), MEMORY, M(MAR) = M(0-1023, 0-15),

The SUBREGISTER is a useful element type that was first explicitly introduced with CDL. A subregister is a part of an already defined register that needs to be accessed separately from the entire register. The name of the subregister begins with the name of the "parent" register followed by the mnemonic for the subregister given in parenthesis. The size of the subregister and the particular bits of the "parent" register is specified in a manner similar to the REGISTER declaration statement. Thus,

SUBREGISTER, ACC(HEAD) = ACC(0-7), ACC(TAIL) = ACC(8-15), declares the subregisters ACC(HEAD) and ACC(TAIL).

Two other elements that first appeared with CDL are external input and output devices, the SWITCH and LIGHT elements respectively. Both of these elements are considered to be accessible by an operator. These elements can be used to simulate the external operations of a digital system, such as start-up and power-failure procedures. Switches can have one or more positions and similarly lights can have one or more light conditions. The following examples are valid CDL declarations.

SWITCH, POWER(ON, OFF), START(ON),

LIGHT, WARNING (YELLOW, RED, GREEN), POWER (GREEN),

The PRIMITIVE OPERATORS found in CDL are symbols that represent the functions performed by various logic networks in one clock cycle. The operators that are encountered frequently have been given

specific symbols and are shown in Table 1.

Two types of STATEMENTS are allowed in CDL descriptions. The first type includes the previously discussed declaration statements which are used to declare system elements. The second type includes the execution statements that describe a system's register transfer activities. The general format of an execution statement is:

/ label / operation<sub>1</sub>, operation<sub>2</sub>,..., operation<sub>n</sub>,

The "label" is some logic function that must be evaluated as being true before the associated operations can be executed. Only the first operation is required; all others are optional. An example of an execution statement is given below. Conditional operations

/ F\*P(1) / A  $\longleftarrow$  A add B, PC  $\longleftarrow$  Countup PC, are also used in CDL descriptions. An example of an execution statement with a condition operation is also shown.

/ F\*P(2) / IF (C=0) THEN (A  $\leftarrow$  A sub B),

CDL allows for one type of COMPLEX OPERATOR. This is the BLOCK/DO statement combination which allows a set of operations to be labeled and referenced by a symbolic name. A BLOCK statement is used to label the set of operations in the declaration section of a description. Then a DO statement is used to reference that BLOCK in the executable portion of a description.

CDL uses a non-procedural ORDER OF EXECUTION mechanism. This means that every execution statement must have a label associated with it to determine the correct order of statement sequencing.

It is useful to describe a sequence of statements in a procedural manner when the designer is not concerned with control signal

| GROUP                   | SYMBOL      | NAME            | EXAMPLE OF USE                           |

|-------------------------|-------------|-----------------|------------------------------------------|

|                         | <del></del> | TRANSFER        | A ← B                                    |

| LOGICAL                 | •           | NOT             | A ← A                                    |

|                         | +           | OR              | $A \leftarrow A + B$                     |

|                         | *           | AND             | A ← — A * B                              |

|                         | $\oplus$    | EX-OR           | A ← A ⊕ B                                |

|                         | 0           | COINCIDENCE     | A ← A ⊘ B                                |

| ARITHMETIC              | add         | ADD             | $A \longleftarrow A \text{ add } B$      |

|                         | sub         | SUB             | A ← A sub B                              |

| COMPARISON <sup>1</sup> | = .         | EQUAL           | IF (A=)) THEN $(A \leftarrow B)^2$       |

|                         | <b>≠</b>    | NOT EQUAL       | IF $(A\neq 0)$ THEN $(B \leftarrow A)^2$ |

| ROTATIONAL              | shl         | SHIFT LEFT      | A ← sh1 A                                |

|                         | shr         | SHIFT RIGHT     | A - shr A                                |

|                         | cil         | CIRCULATE LEFT  | A ← cil A                                |

|                         | cir         | CIRCULATE RIGHT | A ← cir A                                |

| SPECIAL                 | countup     | INCREMENT       | A countup A                              |

|                         | countdn     | DECREMENT       | A ← countdn A                            |

NOTES: 1. In some more recent versions of CDL the comparison operators .NE., .EQ., .GT., .LT., .GE., .LE. were added to the language.

2. These are conditional operations.

CDL Primitive Operators

Table 1

analysis. CDL descriptions can also be written in a procedural manner if some slight description modifications are made. These differences have been listed below for a procedural description.

- Declaration statements for generating control signals are not needed.

- The order of statement execution is dependent on the order in which the statements appear.

- A GOTO statement is created to change the order of execution from the ordered form.

- 4. Labels are required only for the statements that are used with the GOTO statements.

- A semicolon is employed to indicate the end of an execution statement.

CDL uses a single BLOCK STRUCTURE. This limits the suitability of using CDL to describe digital systems in a modular fashion.

There are no subroutines allowed in a CDL description. The variables (elements) used in a CDL description are global to the entire description due to the single block structure. It is also not possible to declare special hardware elements, such as ICs, with CDL.

The ORGANIZATION of a CDL description consists of a list of declaration statements followed by a list of execution statements. There is no provision for partitioning the description into blocks of related statements (subsystems).

To sum up the CDL features discussed above, portions from a CDL description of a simple digital computer [Ch72a] have been

given in Figure 4. For comparison with other languages CDL is again summarized in Section 3.3.

# The Digital System Design Language [DD68,Di71]

This language was developed to describe and simulate combinational and sequential logic networks by meeting four diverse goals. The first of these was to keep the language from being restricted to any single computer organization, timing mode or design procedure. This was important to insure that DDL remained a viable design tool as technology changed. The second goal was to make the language capable of describing digital systems at both an architectural "block" level and at a logical "gate" level. This feature will allow several groups of digital designers to use DDL and thus facilitate communication on a design team. The third goal was that the language should serve as the initial input for an automatic design process. The final goal was to have DDL description follow the actual system's structure as much as possible; if a system uses a multi-level block structure then the DDL description should be in a multi-level block format.

DDL can be a very useful tool for the design, documentation and simulation of digital systems. Descriptions can be made for both sequential and concurrent activities. The large number of operators, the conciseness of the language and the block structure of DDL make a good tool for dealing with systems in a complete and organized manner.

The ALPHABET of DDL includes the standard set of 70 ASCII characters and the following non-standard characters.

```

$ buffer register

Register, R(0-23),

A(0-23),

$ accumulator

$ address register

C(0-14),

$ OP-code part of register R

Subregister, R(OP)=R(0-5),

R(I)=R(6),

$ indirect addressing bit

Memory, M(C)=M(0-32767,0-23),

$ three-phase clock

Clock, P(1-3),

/FETCH*P(1)/ C\leftarrow-D, IF (G=0) THEN F\leftarrow-8),

/FETCH*P(2)/ R\leftarrowM(C), D countup D,

/FETCH*P(3)/F \leftarrow R(OP), C R(ADDR),

/ADD*P(2)/R \leftarrow M(C),

ADD*P(3)/ A add R, F 9,

/JMP*P(3)/D \leftarrow R(ADDR), F \leftarrow 9,

/JOP*P(3)/ IF (A(0)) THEN (D \leftarrow R(ADDR)), F \leftarrow 9,

/SHR*P(3)/A \leftarrow shr A, F \leftarrow 9,

/CIL*P(3)/ A—cil A, F—9,

END

```

Example CDL Description

Figure 4

(taken from example CDL description in Chu, 1972a)

The blank is not a part of the DDL alphabet but it can be included in DDL descriptions to increase readability.

CONSTANTS in DDL take the general form,

#### n R k

where "n" specifies the value of the constant in one of three numbering systems, "R" specifies the particular numbering system and "k" is a positive decimal integer giving the number of bits in the binary form of the constant. A constant can be written in binary, octal or decimal notation (R=B, 0 or D respectively). When a constant is expressed in binary the question mark, "?", may be used to indicate that the value of a bit is unknown or a "don't-care." The following examples are all valid DDL constants.

| REPRESENTATION | BINARY EQUIVALENT |

|----------------|-------------------|

| 10D4           | 1010              |

| 1204           | 1010              |

| 0101B3         | 101               |

| 10?0B4         | 10x0              |

A DDL IDENTIFIER (or variable name) may contain up to eight characters, the first of which must be alphabetic. An identifier can be followed by a subscript to indicate a specific bit position, a range of values or a value from an array. The following examples are valid DDL identifiers.

# A , START , MAR[16], ADDR1[0:11] , M[16,0:15]

ALL PRIMITIVE ELEMENTS used in a DDL description must be defined and assigned a name with one of several types of declaration statement. These statements have the form

<DT> body.

Where "DT" represents the declaration type, the body of the statement denotes the hardware elements that exist of type DT and the period signifies the end of the statement.

The declaration type consists of at least the first two letters of words that describe the hardware types. For example when registers are being declared, at least "RE" must appear inside the angle brackets. The body of the statement is used to either list the names and sizes of hardware components or to indicate how already declared units are interconnected. A list of the types of elements and a brief definition for each is given below.

| <re></re> | REGISTER | A set of synchronized flip-flops.    |

|-----------|----------|--------------------------------------|

| <me></me> | MEMORY   | An array of synchronized flip-flops. |

| <te></te> | TERMINAL | A set of wires.                      |

| <ti></ti> | TIME     | A clock                              |

| <de></de> | DELAY    | A delay element.                     |

| <bo></bo> | BOOLEAN  | A combination logic circuit.         |

| <el></el> | ELEMENT  | An off-the-shelf component.          |

REGISTER and MEMORY element types are the most frequently used elements in DDL descriptions; valid examples of these declaration statements are given below. Subregisters are implicitly declared

<RE> GO, MAR[16], IR[0:4]

<ME> ME0:4095, 16]

in a REgister declaration statement with the use of the concatenation operator. In the following example the subregisters IR and ADDR are declared as portions of register BUF.

$\langle RE \rangle$  BUF[16] = IR[4] o ADDR[12]

Another useful type of data element that first appeared with DDL is the ELEMENT declaration. This declaration provides a means of introducing a hardware block into a system description without indicating how the block is constructed or what functions it performs. In this statement the block is named and its output and input terminals are defined.

< EL> JKFF(Q1, NQ1: C, J1, K1)

It should be noted that connections to these "block boxes" may be defined and translated into Boolean equations, but simulation of descriptions that include these blocks are not allowed.

DDL contains a large number of PRIMITIVE OPERATORS to aid in developing clear and concise hardware descriptions. The terminals of the primitive elements serve as the operands of operations which express the interconnections and interactions between those elements. The operators determine the nature of these activities. A list of the frequently used operators is provided in Table 2.

There are several different types of STATEMENTS allowed in DDL descriptions. These can be divided into two groups. The first includes the declaration statements already described, while the

| GROUP      | SYMBOL          | NAME                 |       | EXAMPLE                                                                                |

|------------|-----------------|----------------------|-------|----------------------------------------------------------------------------------------|

|            | =               | CONNECTION A         | A = B | (A is connected to B)                                                                  |

|            | <del></del>     | TRANSFER A           | A←—B  | (contents of B goto A)                                                                 |

| LOGICAL    | -               | NOT                  |       | $A \leftarrow \neg A$                                                                  |

|            | V               | OR                   |       | $A \leftarrow A \lor B$                                                                |

|            | <b>\'</b> .     | AND                  |       | A ← A ∧B                                                                               |

|            | <b>⊕</b>        | EX-OR                |       | A ← A ⊕ B                                                                              |

|            | $\odot$         | COINCIDENCE          |       | $A \longleftarrow A \bigcirc B$                                                        |

|            | 4               | NOR                  |       | $A \leftarrow\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ |

|            | 1               | NAND                 |       | A A 7 B                                                                                |

| ARITHMETIC | +               | ADD                  |       | $A \leftarrow A + B$                                                                   |

|            | -               | SUB                  |       | A - B                                                                                  |

| COMPARISON | ۷, ۷            | LT,LE                |       |                                                                                        |

|            | <b>&gt;</b> , ≥ | GT,GE                |       |                                                                                        |

|            | ≐,≠             | EQ,NE                |       |                                                                                        |

| ROTATIONAL | ×1,             | SHIFT/CIRCULATE RIGI | HT    | $A \leftarrow cl$                                                                      |

|            | <1x             | SHIFT/CIRCULATE LEFT | Γ     | A — 21 A                                                                               |

|            | (where          | x is either blank,   | 0, 1, | c or e)                                                                                |

| SPECIAL    | X               | EXTENSION            |       | A ←                                                                                    |

|            | 0               | CONCATENATION        |       | IR[3]=OP[0] X[2]                                                                       |

|            | \               | SELECTION            |       | V <b>\</b> A                                                                           |

|            |                 | REDUCTION            |       | V/A                                                                                    |

|            | ¢,\$            | COUNTUP, COUNTON     |       | A <b>~ \$</b> A                                                                        |

DDL Primitive Operators

Table 2

second consists of the functional statements that are used to describe the behavior of a system. This second group includes Register Transfer, Connection, IF-THEN-ELSE, IF-VALUE and FOR statements.

The Register Transfer and Connection statements rarely appear without some condition that determines whether the operation is performed or not. Boolean expressions are used to represent these conditions. Identifiers in the expressions refer to registers, clocks and terminals previously declared.

The IF-THEN-ELSE statement is used to relate the activation conditions to the register transfer and connection statements. In DDL these statements appear as vertical lines enclosing a Boolean expression of the condition to be satisfied. The ELSE portion is expressed as a semicolon. A period is used to indicate the end of the statement. Thus,

$$F \leftarrow A \mid B$$

; C.

reads as follows: If A is true, then B is transferred to F, else C is transferred to F.

An IF-VALUE statement is used to describe the decoding of multivalued conditions. The general form of the expression is,

Boolean expression value 1 operation a value 2 operation b.

If the Boolean expression has a value of "value 1" then operation a is performed where " " represents "if" and " " represents "then do." To show an example of this type of statement assume a three-way multiplexer, A, which must select one of three different registers.

<RE> ACC[10], MAR[10], PC[10], BUF[10].

$\overline{A}$  0 ACC  $\leftarrow$  BUF 1 MAR  $\leftarrow$  BUF 2 PC  $\leftarrow$  BUF.

An optional ELSE condition can be added to the end of an IF-VALUE statement if desired. This type of statement can easily be thought of as a decoder.

When a designer needs to specify a parallel data transfer it usually involves the entire register, in which case no subscripts are needed. If a data transfer is valid for only certain subscript value or range of values, a FOR statement can be used. The general form of this statement is as follows;

{ index variable = list of values} operations in terms of the index.

This statement is used to provide a more concise system description.

As an example of this the following two equivalent examples are given.

The DDL language allows for two types of COMPLEX OPERATORS.

The first is the OPerator statement, which is used to define a block of combinational circuitry whose outputs will be used by one facility at one time and a different facility at some other time.

This can be considered as a time-shared circuit that has been developed to reduce the amount of duplicate hardware in a design.

A full adder could be described as an operator as shown.

<OP> ADDER(SUM, CARRY).

<TE> A,B,CIN,SUM,CARRY.

<BO> CARRY=A·B+B·CIN+A·CIN

SUM=A·B·C+(A+B+C)·CARRY.

In this statement the variables SUM and CARRY are local "dummy" variables that represent the output of the adder. The facilities declared by the terminal statement, which should be thought of as wires, are local to the operator block only.

The second type of complex operator is the IDentifier declaration. This statement is used when a series of operations is repeated often in a description. The \lambda ID \rangle statement gives a name to the series of operations and allows that name to be used in place of a long or complex set of operations. This statement is primarily used to reduce the amount of writing needed to make a DDL description.

The ORDER OF EXECUTION for DDL is dependent on the state transitions of subsystems called automatons. Since these transitions must be declared explicitly, DDL is a non-procedural language. This sequencing mechanism will be further explained in the next paragraph.

DDL is a BLOCK STRUCTURED language. It has been developed to accurately describe the modular structure of digital hardware designs. Many hardware systems can be considered to be a collection of semi-independent subsystems interacting with each other via some overall system facilities. This type of design structure is efficiently described in DDL with the use of the following four types of statements; SYstem, AUtomaton, STate and SEgment.

The overall system is declared with a SYstem declaration. This all encompassing block is used to provide all of the needed global elements and intercommunication systems. There is only one system declaration per description.

The subsystems that comprise the entire system are labeled with an AUtomaton declaration. A subsystem is typically a single finite state machine and it's private facilities. The body of an AU 7statement can contain facility declarations, operation statements and state and segment declarations.

A STate declaration is used to express the states of a finite state machine. Each state must have a set of operations to perform and specify a next state transition. A new operator is used to specify a state transfer. It is called the "go to" operation (----) and the only operand is the name of the next state to be activated.

If a group of states is divided into two or more groups of related activities they may be labeled separately with a SEgment declaration. An example of this would be a finite state machine that includes an input processing segment, a data manipulation segment and an output processing segment. An example of a DDL description using these four statements is shown in Figure 5.

The ORGANIZATION of a DDL description is based on the finite state machines used in a particular hardware design. The main system consists of declared facilities (RE, ME, TE, etc.) and one or more automaton. Similarly, the individual automaton consists of locally declared facilities and one or more states (with related groups of states split into segments if possible). This arrangement

provides for a very modular description of hardware. The timing in an automaton is carried out by IF-THEN-ELSE statements and state transitions. The timing mode can be synchronous, asynchronous or a combination of the two in any particular automaton. DDL allows for global and primitive facilities in its descriptions.

To show how the DDL constructs discussed in this section fit together in an actual hardware description, selected portions from a DDL description of a simple digital computer have been presented in Figure 5.

This section has developed specific information on two types of CHDLs. By using the construct discussions and the partial hardware descriptions, the features and structures presented in this section can be extended to develop an intuitive picture for other CHDLs introduced in the next chapter.

```

<SY>

EDC: \langle TI \rangle P(1E-6).

ME> M[0:1023,16].

IR[16]=OP[0:3] \bullet IX[2] ADR[10], CAR[10],

<RE>

ACC[16],MAR[10],....

<AU> CPU:P: <ID> Z=0D16.

\langle ST \rangle IFL: CLEAR RUN\leftarrow 0, CLEAR\leftarrow 0, CAR\leftarrow 0,...

| RUN | MAR \leftarrow CAR, \updownarrow CAR, \rightarrow 1F2; \rightarrow 1F1...

EX: \[ OP \ \[ O \ \] IN \[ M[MAR] \( ---- \) INPUT, IN\( ---- \) O, ...

L1 | 70UT | OUTPUT --- M[MAR], OUT---,

| 4 ACC←—M[MAR],—→IF1

| 5 ACC←—ACC+M[MAR],—→IF1

| 6 ACC←—ACC-M[MAR],—→IF1

[7 M[MAR] \leftarrow ACC, \rightarrow IF1]

8 ACC←—ACC.M[MAR],—→IF1

EXBIX: IN: M[MAR] INPUT, $\pi$ ADR, IN\(-0\),\to\EX.

```

Example DDL Description

Figure 5

(taken from example DDL description in Dietmeyer, 1971)

...(end of ST,AU,SY)

#### 3. AVAILABLE HDLS

Before selecting an HDL for design purposes, it is important to be aware of what types of formal languages can be chosen to describe and simulate digital systems. This awareness could include knowing the advantages and disadvantages of using each type of language.

The purpose of this chapter is to provide this kind of information for three classes of computer languages. Each class is capable of describing digital hardware at or above the register transfer level, thus they can be considered to be HDLs. The three classes of languages are:

- 1. High-Level Programming Languages (HLLs)

- 2. General Purpose Simulation Languages (GPSLs)

- 3. Computer Hardware Description Languages (CHDLs)

This chapter is divided into three sections, with a separate section being dedicated to each class of HDL. Each section includes a discussion of the advantages and disadvantages of using the particular class of HDL and specific examples of languages from that class. A glance at the names of the three types of HDLs may make it seem that the CHDL is the best suited for describing computer hardware. However, this is not always the case.

## 3.1. High-Level Programming Languages

HLLs were first developed in the 1950s and 1960s (FORTRAN in 1954, ALGOL in 1960 and many more since then) to abstract the details of implementing machine and assembly language programs. The

object of the HLL was to allow the programmer to concentrate on the algorithm itself rather than on its machine implementation for a particular type of computer.

The same type of situation now exists in regards to digital system design. Logic level descriptions are becoming so large and complex that they can no longer be easily understood. The design industry can benefit from using a high-level description language that concentrates on the design itself rather than on the logic needed to implement the design. HDLs have been suggested as suitable languages for hardware descriptions because they are sufficiently general to provide the constructs necessary to describe digital hardware functions at the register transfer level [RD83].

As a general class, HLLs have facilities for performing loops, making conditional decisions and involving subroutines and procedures. Each of these features is vital for the development of a precise hardware description.

Many HLLs possess special features that make them particularly attractive for hardware descriptions. For example: [Li77]

ALGOL has a block structure useful for control procedures.

APL has a concise vector notation useful for working with registers.

C has both a block structure and a wide variety of useful operators.

PASCAL has an ALGOL-like block structure.

PL/I has a structure useful for declaring variables in a modular fashion.

In addition to providing many of the language constructs needed to represent hardware, there are several practical reasons for using HLLs. The first of these is the availability of HLLs in the design environment. Nearly every company with a fair-sized computer has access to at least one type of HLL. The use of a language that is known to be available is a plus in the planning stages of developing an HDL based design system.

A second advantage is that HLLs tend to be well known by engineers. This means that no time would be lost trying to teach designers a new language. If a specialized design language were used, time would have to be spent familiarizing designers with the new language and its uses. Working out any system bugs could be a long and tedious process. The use of an already known HLL can reduce these problems.

Related to the familiarity of an HLL is the abundance of software support packages available. A large portion of a design system is implemented via software. Software programs for performing data transformations or developing graphics capabilities may already exist or if not could be quickly written.

Another valuable advantage to using HLLs is that they come with verified compilers [RD83]. When an HLL description is being run on a computer, the compiler acts as the simulator. Using a proven HLL compiler to simulate a system will eliminate the need to verify that the simulator for a specialized description language is working correctly.

A final and perhaps the most important reason for using HLLs is that they are relatively low cost. HLL software packages have been on the market for so long that their cost is considerably lower than that of the software for newer forms of description languages.

In spite of the practical advantages of using an HLL, there are several serious drawbacks to using one for the description of hardware. While many HLLs have some of the constructs needed to describe computer systems, none seems to have all of the ones that are needed. There are also several hardware properties that all HLLs have difficulty expressing.

The biggest of these problems is in trying to use an HLL to describe concurrent operations. Most programming languages were developed to describe algorithms as procedures which are executed in a sequential manner. Thus developing hardware descriptions where concurrent operations are commonplace is an ineffective use of many HLLs.

Another disadvantage is that descriptions in an HLL tend to be much longer than in the other classes of HDLs. This is an important consideration since the longer a description is the more difficult it is to read and understand. As an example of the difference in size between an HLL description and a CHDL description, the way in which a 6-bit register is declared will be examined. For a CHDL description the declaration would take one line of code. To declare a 6-bit register in FORTRAN requires the use of an INTEGER statement which sets up the register as an integer variable having the word length of the host computer. In the actual hardware no

number with more than 6 bits could be stored in the register. A FORTRAN description must insure the same property holds by masking and shifting the right-most bits so that no overflow conditions violate the conditions of the register. This can take up to four lines of FORTRAN code for each register declaration. Possible language codings for this example are shown below. Simplifications of this coding result in shorter but imprecise descriptions.

CDL FORM

FORTRAN FORM

REGISTER, A(0-5),

INTEGER A

EQUIVALENCE (A, REALA)

DATA MASK/ZFC0000/

REALA=AND (MASK, A)

A final disadvantage of using an HLL is that once the description is complete it is less likely to resemble the hardware it describes than a CHDL description. It can be very difficult to obtain an intuitive feeling for how the hardware behaves from an HLL description. In addition, very little structural information can be described by an HLL (except as comment statements).

As a summary of an HLL's usefulness for describing computer hardware, the advantages and disadvantages will be again listed. The advantages are:

- Several of the constructs needed to describe hardware are available.

- 2. HLLs are frequently found in industry.

- HLLs are already known by a large percentage of the designers.

- 4. They have a relative low cost.

- 5. The compiler acts as a simulator.

- 6. There is a large amount of HLL software available.

### The disadvantages are:

- 1. HLLs cannot be used to describe several important hardware features.

- 2. The descriptions are long and imprecise.

- The descriptions don't easily reflect the structure of hardware.

### Examples

Two languages have been selected to represent the class of HLLs. The first language is the scientific-oriented language FORTRAN which is one of the oldest and most frequently used programming languages. The second language is C which is a newer general purpose programming language that is becoming popular within the computer industry.

FORTRAN (FORmula TRANslation) [Ca83,Ni80] is a high level programming language that was first introduced by J.W. Backus in 1954. Several improved versions of this language have been developed, the most recent of which is FORTRAN77. This language is one of the most frequently used for the programming of scientific algorithms. Figure 6 presents a section of a hardware description in the FORTRAN language.

The C programming [HK82] language was developed at Bell Labs in 1972. It is a descendent of the ALGOL (1960), CPL (1963), BCPL (1967) and B (1970) programming languages. This language allows the specification of algorithms at a slightly lower level of detail

| FORTRAN                       | <u>c</u>                          | CDL                     |

|-------------------------------|-----------------------------------|-------------------------|

| INTEGER A, B, OP, ADDR        | int a,b,op,addr <sup>1</sup>      | REGISTER,               |